(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-173383

(P2007-173383A)

(43) 公開日 平成19年7月5日(2007.7.5)

(51) Int.CI.

H01L 21/76

(2006.01)

F 1

H01L 21/76

テーマコード(参考)

L

5 F 0 3 2

審査請求 未請求 請求項の数 10 O L (全 10 頁)

(21) 出願番号

特願2005-366726 (P2005-366726)

(22) 出願日

平成17年12月20日 (2005.12.20)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100065248

弁理士 野河 信太郎

(72) 発明者 小田部 隆宏

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

F ターム(参考) 5F032 AA35 AA44 AA45 AA46 DA03

DA04 DA22 DA23 DA24 DA33

DA74

(54) 【発明の名称】トレンチ素子分離領域の形成方法、窒化シリコン膜ライナーの形成方法、半導体装置の製造方法

## (57) 【要約】

【課題】簡易かつ精度よく、トレンチ側壁上部の窒化シリコン膜ライナーの除去を行うことができる、トレンチ素子分離領域の形成方法を提供する。

【解決手段】本発明では、(a)半導体基板をエッチングして素子分離用トレンチを形成する工程と、(b)得られた基板を覆うように第2窒化シリコン膜を形成する工程と、(c)第2窒化シリコン膜を覆い、前記トレンチの途中の深さで埋め込みを終えるように第3酸化シリコン膜を異方性の成膜法によって形成する工程と、(d)第3酸化シリコン膜を等方性エッティングし、トレンチ側壁上部の第2窒化シリコン膜が露出するまで除去する工程と、(e)露出した第2窒化シリコン膜をエッティングして除去する工程を備える方法によって、トレンチ側壁上部の窒化シリコン膜ライナーの除去を行う。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

- (a) 半導体基板に素子分離用トレンチ形成のための窓を有する第1酸化シリコン膜及び第1窒化シリコン膜を含むパターンをマスクとして、半導体基板をエッティングして素子分離用トレンチを形成する工程と、

(b) 前記トレンチ内に露出したシリコン基板表面に第2酸化シリコン膜を形成し、更に第2酸化シリコン膜及び前記パターン表面に第2窒化シリコン膜を形成する工程と、

(c) 第2窒化シリコン膜を覆い、前記トレンチの途中の深さで埋め込みを終えるように第3酸化シリコン膜を異方性の成膜法によって形成する工程と、

(d) 第3酸化シリコン膜を等方性エッティングし、トレンチ側壁上部の第2窒化シリコン膜が露出するまで除去する工程と、

(e) 露出した第2窒化シリコン膜をエッティングして除去する工程と、

(f) 前記トレンチを埋め込むように第4酸化シリコン膜を形成する工程と、

(g) 第2又は第1窒化シリコン膜をストップとして、第4酸化シリコン膜を平坦化する工程と、

(h) 第2及び第1窒化シリコン膜、又は第1窒化シリコン膜をエッティングして除去してトレンチ素子分離領域を形成する工程とを含むことを特徴とするトレンチ素子分離領域の形成方法。

**【請求項 2】**

工程(c)において、第3酸化シリコン膜は、前記トレンチを埋め込む深さが半導体基板表面下1nm～100nmとなるように形成される請求項1に記載の方法。 20

**【請求項 3】**

工程(c)において、第3酸化シリコン膜は、トレンチ側壁での厚さが1nm～60nmになるように形成される請求項1に記載の方法。

**【請求項 4】**

工程(e)において、第2窒化シリコン膜は、半導体基板表面から深さ50nm～150nmまでの範囲において除去される請求項1に記載の方法。

**【請求項 5】**

工程(c)において、異方性の成膜法は、HDP-CVD法である請求項1に記載の方法。 30

**【請求項 6】**

工程(g)において、第4酸化シリコン膜の平坦化は、化学的機械的研磨によって行われる請求項1に記載の方法。

**【請求項 7】**

工程(d)での第3酸化シリコン膜のエッティングは、工程(c)での第3酸化シリコン膜の形成に用いる装置と同一の装置を用いて連続的に行う請求項1に記載の方法。

**【請求項 8】**

工程(e)での第2窒化シリコン膜のエッティングは、工程(c)での第3酸化シリコン膜の形成と、工程(d)での第3酸化シリコン膜のエッティングに用いた装置と同一の装置を用いて連続的に行う請求項1に記載の方法。 40

**【請求項 9】**

- (a) 半導体基板をエッティングして素子分離用トレンチを形成する工程と、

(b) 得られた基板を覆うように第2窒化シリコン膜を形成する工程と、

(c) 第2窒化シリコン膜を覆い、前記トレンチの途中の深さで埋め込みを終えるように第3酸化シリコン膜を異方性の成膜法によって形成する工程と、

(d) 第3酸化シリコン膜を等方性エッティングし、トレンチ側壁上部の第2窒化シリコン膜が露出するまで除去する工程と、

(e) 露出した第2窒化シリコン膜をエッティングして除去する工程を含むことを特徴とする窒化シリコン膜ライナーの形成方法。

**【請求項 10】**

10

20

30

40

50

請求項 1 ~ 9 に記載の方法を用いた半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トレンチ素子分離領域の形成方法、窒化シリコン膜ライナーの形成方法、及び半導体装置の製造方法に関する。 10

【背景技術】

【0002】

従来、トレンチ素子分離領域の形成方法として、以下の方法が知られている（例えば、特許文献 1 を参照。）

(a) 半導体基板に素子分離用トレンチ形成のための窓を有する第 1 窒化シリコン膜を含むパターンをマスクとして、半導体基板をエッティングして素子分離用トレンチを形成する。

(b) 前記トレンチ内壁を覆うように第 2 窒化シリコン膜を形成する。

(c) 第 2 窒化シリコン膜を覆い、かつ前記トレンチを完全に埋め込むように第 1 酸化シリコン膜を形成する。

(d) 第 1 酸化シリコン膜をエッティングし、前記トレンチ側壁上部の第 2 窒化シリコン膜が露出するまで除去する。

(e) 露出した第 2 窒化シリコン膜をエッティングして除去する。

(f) 前記トレンチを埋め込むように第 2 酸化シリコン膜を形成する。

(g) 第 1 窒化シリコン膜をストップとして、第 2 酸化シリコン膜を化学機械研磨する。

(h) 露出した第 1 窒化シリコン膜をエッティングして除去する。

【0003】

以上の工程によって、トレンチ内壁に第 2 窒化シリコン膜を有するトレンチ素子分離領域が得られる。第 2 窒化シリコン膜は、トレンチ内の第 1 酸化シリコン膜が収縮して素子形成領域に加える圧縮応力を緩和する機能を有している。このような機能から、トレンチ内壁に形成された窒化シリコン膜は、窒化シリコン膜ライナーと呼ばれている。 20

【0004】

上記方法では、トレンチ側壁上部において、第 2 窒化シリコン膜からなる窒化シリコン膜ライナーが除去されているが、これは、トレンチ内壁全体に窒化シリコン膜ライナーが形成されていると、基板表面の第 1 窒化シリコン膜を除去する際に、窒化シリコン膜ライナーも一部除去されて、凹部（devo t）が形成されることがあるためである。 30

【特許文献 1】特開 2004-207564 号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

凹部形成を避けるために、トレンチ側壁上部において窒化シリコン膜ライナーの除去を行っているが、窒化シリコン膜ライナーの除去深さ（除去された部分の基板表面からの長さ）がばらつくと、素子形成領域に加わる応力の大きさがばらつき、その結果、素子形成領域にトランジスタを形成したときのドレイン電流の大きさがばらつくことになる。従って、窒化シリコン膜ライナーの除去深さのばらつきを減少させることが望まれている。 40

【0006】

本発明はこのような事情に鑑みてなされたものであり、簡易かつ精度よく、トレンチ側壁上部の窒化シリコン膜ライナーの除去を行うことができる、トレンチ素子分離領域の形成方法を提供するものである。

【課題を解決するための手段及び発明の効果】

【0007】

本発明のトレンチ素子分離領域の形成方法は、(a) 半導体基板に素子分離用トレンチ形成のための窓を有する第 1 酸化シリコン膜及び第 1 窒化シリコン膜を含むパターンをマスクとして、半導体基板をエッティングして素子分離用トレンチを形成する工程と、(b) 50

前記トレンチ内に露出したシリコン基板表面に第2酸化シリコン膜を形成し、更に第2酸化シリコン膜及び前記パターン表面に第2窒化シリコン膜を形成する工程と、(c)第2窒化シリコン膜を覆い、前記トレンチの途中の深さで埋め込みを終えるように第3酸化シリコン膜を異方性の成膜法によって形成する工程と、(d)第3酸化シリコン膜を等方性エッティングし、トレンチ側壁上部の第2窒化シリコン膜が露出するまで除去する工程と、(e)露出した第2窒化シリコン膜をエッティングして除去する工程と、(f)前記トレンチを埋め込むように第4酸化シリコン膜を形成する工程と、(g)第2又は第1窒化シリコン膜をストップとして、第4酸化シリコン膜を平坦化する工程と、(h)第2及び第1窒化シリコン膜、又は第1窒化シリコン膜をエッティングして除去してトレンチ素子分離領域を形成する工程とを含むことを特徴とする。

10

## 【0008】

本発明者らは、異方性の成膜法によって前記トレンチを途中まで第3酸化シリコン膜で埋め込み(工程(c))、第3酸化シリコン膜を等方性エッティングすることによって、トレンチ側壁の第3酸化シリコン膜を除去して、トレンチ側壁上部の窒化シリコン膜を露出させる(工程(d))ことができることを見出し、本発明の完成に到った。

## 【0009】

第3酸化シリコン膜は、トレンチの途中の深さで埋め込みを終えるため、特許文献1の方法と比較して、成膜量を減らすことができる。また、第3酸化シリコン膜のエッティング量も減少させることができる。従って、本発明によれば、成膜・エッティングに必要な材料や時間を減少させることができる。

20

## 【0010】

また、本発明によれば、第3酸化シリコン膜について、以下の二種類のばらつきを減少させることができる。

## (1) パターン疎密によるばらつき

HDP CVD法などによる成膜では、一般に、膜の堆積速度は、密(狭い)パターンの部分で大きく、疎(広い)パターンの部分では小さい。一方、エッティングの速度は、一般に、パターン疎密による影響を受けにくい。従って、形成する膜の厚さが大きくなるほど、密パターンの部分と疎パターンの部分とで、エッティング後に残る膜の厚さの差が大きくなる。本発明では、トレンチの途中の深さで第3酸化シリコン膜の埋め込みを終えるため、特許文献1の場合よりも、成膜量が小さくなる。従って、本発明によれば、密パターンの部分と疎パターンの部分と間の、エッティング後に残る膜の厚さの差(ばらつき)を減少させることができる。

30

## (2) 面内ばらつき

基板面全体で厳密に均一に成膜やエッティングを行うことは極めて困難であり、成膜・エッティングともに、通常は、一定のばらつきが発生する。このばらつきは、成膜量・エッティング量が大きくなるほど、それぞれ大きくなる。本発明によれば、第3酸化シリコン膜の成膜量及びエッティング量の両方を、特許文献1の場合よりも、少なくすることができる。従って、本発明によれば、面内ばらつきを減少させることができる。

## 【0011】

第3酸化シリコン膜の、エッティング後の膜厚のばらつきが減少すると、第2窒化シリコン膜からなる窒化シリコン膜ライナーのトレンチ側壁上部での除去量(除去深さ)のばらつきも減少する。従って、本発明によれば、精度よく、窒化シリコン膜ライナーを形成することができる。

40

## 【0012】

本発明は、別の観点では、(a)半導体基板をエッティングして素子分離用トレンチを形成する工程と、(b)得られた基板を覆うように第2窒化シリコン膜を形成する工程と、(c)第2窒化シリコン膜を覆い、前記トレンチの途中の深さで埋め込みを終えるように第3酸化シリコン膜を異方性の成膜法によって形成する工程と、(d)第3酸化シリコン膜を等方性エッティングし、トレンチ側壁上部の第2窒化シリコン膜が露出するまで除去する工程と、(e)露出した第2窒化シリコン膜をエッティングして除去する工程を含む窒化

50

シリコン膜ライナーの形成方法を提供するものである。本明細書中でのトレンチ素子分離領域の形成方法についての説明は、基本的に、この窒化シリコン膜ライナーの形成方法についても当てはまる。

**【発明を実施するための最良の形態】**

**【0013】**

以下、本発明の一実施形態を図面を用いて説明する。図面は、説明の便宜のために用いられるものであり、本発明の範囲は、図面に示す実施形態に限定されない。また、以下の説明中での成膜やエッティングの方法や条件、及び各種寸法は、例示であって、ここに示したものに限定されない。

**【0014】**

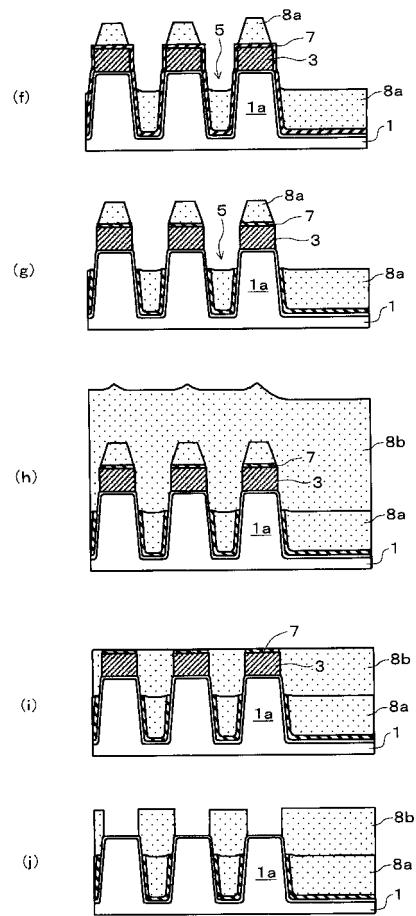

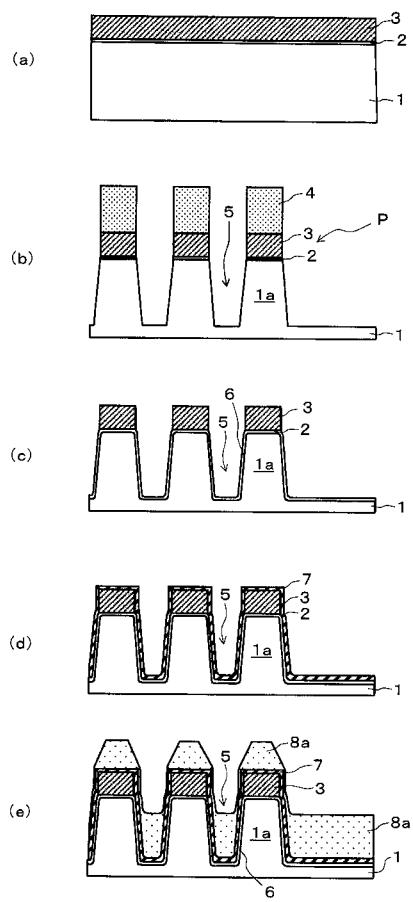

1. 素子分離用トレンチ形成工程（工程（a））

図1(a), (b)に示すように、この工程では、半導体基板1に素子分離用トレンチ5形成のための窓を有する第1酸化シリコン膜2及び第1窒化シリコン膜3を含むパターンPをマスクとして、半導体基板1をエッティングして素子分離用トレンチ5を形成する。この工程は、具体的には、以下のように実施することができる。

まず、半導体基板1上に第1酸化シリコン膜2及び第1窒化シリコン膜3を順次形成し、図1(a)に示す構造を得る。

**【0015】**

半導体基板1は、シリコン基板などからなり、本実施形態では、半導体基板1がシリコン基板である場合を例にとって、説明を進めるが、別の種類の基板を用いる場合でもエッティングガス等を適宜変更することによって、本発明は実施可能である。

**【0016】**

第1酸化シリコン膜2は、熱酸化等により形成することができ、厚さ2～20nm、例えば厚さ10nmで形成することが好ましい。熱酸化は、半導体基板1を800～1100で熱処理することによって行うことができる。第1窒化シリコン膜3は、厚さ50nm～150nm、例えば厚さ100nmで形成することが好ましい。第1窒化シリコン膜3は、LPCVD(低圧化学気相堆積)法などにより形成することができ、このLPCVDは、例えば、ソースガスとしてSiH<sub>2</sub>CL<sub>2</sub>とNH<sub>3</sub>を用い、温度750で行うことができる。第1酸化シリコン膜2は、不要な場合には省略し、半導体基板1上に第1窒化シリコン膜3を形成してもよい。

**【0017】**

次に、第1窒化シリコン膜3及び第1酸化シリコン膜2を順次パターニングして、半導体基板1に素子分離用トレンチ5形成のための窓を有する第1酸化シリコン膜2及び第1窒化シリコン膜3を含むパターンPを形成する。さらに、パターンPをマスクとして用いて半導体基板1をエッティングして半導体基板1に素子分離用トレンチ5を形成し、図1(b)に示す構造を得る。

**【0018】**

第1窒化シリコン膜3及び第1酸化シリコン膜2のパターニングは、第1窒化シリコン膜3の上にレジストパターン4を形成し、レジストパターン4をエッティングマスクとし、第1窒化シリコン膜3、第1酸化シリコン膜2を順次エッティングすることによって行うことができる。第1酸化シリコン膜2のエッティングは、レジストパターン4をマスクとして行ってもよいし、パターニングされた第1窒化シリコン膜3をマスクとして行ってもよい。

**【0019】**

レジストパターン4は、第1窒化シリコン膜3の上に、レジスト膜を塗布し、このレジスト膜を露光現像することにより形成することができる。レジストパターン4は、素子形成領域(活性領域)1a上に形成され、その窓(すなわち、開口部)が素子分離領域を画定する。

**【0020】**

第1窒化シリコン膜3及び第1酸化シリコン膜2のエッティングは、例えばCF<sub>4</sub>、CH<sub>4</sub>

10

20

30

40

50

$F_3$ 、Ar、 $O_2$ の混合ガスをエッティングガスとして用いて行なうことができる。半導体基板1のエッティングは、例えば $Cl_2$ 、 $O_2$ の混合ガスをエッティングガスとして用いて行なうことができる。半導体基板1は、160～400nm、例えば深さ300nmエッティングされ、トレンチ5が形成される。

#### 【0021】

レジストパターン4は、第1窒化シリコン膜3をエッティングした後に除去してもよく、第1酸化シリコン膜2又は半導体基板1をエッティングした後に除去してもよい。半導体基板1のエッティングの際にレジストパターン4が残っていても、半導体基板1は、パターンPに従ってエッティングされるので、この場合も、パターンPをマスクとして用いていることになる。

10

#### 【0022】

### 2. 第2酸化シリコン膜、第2窒化シリコン膜形成工程（工程（b））

図1(c)、(d)に示すように、この工程では、トレンチ5内に露出したシリコン基板1表面に第2酸化シリコン膜6を形成し、更に第2酸化シリコン膜6及びパターンP表面に第2窒化シリコン膜7を形成する。この工程は、具体的には、以下のように実施することができる。

まず、トレンチ5内に露出したシリコン基板1表面に第2酸化シリコン膜6を形成し、図1(c)に示す構造を得る。

#### 【0023】

第2酸化シリコン膜6は、熱酸化などにより形成することができ、厚さ1～20nm、例えば厚さ10nmで形成することが好ましい。熱酸化は、半導体基板1を800～1100で熱処理することによって行なうことができる。第2酸化シリコン膜6は、不要な場合には省略することもできる。

20

#### 【0024】

次に、得られた基板を覆うように第2窒化シリコン膜7を形成し、図1(d)に示す構造を得る。第2窒化シリコン膜7によって、第2酸化シリコン膜6及び前記パターンP表面が覆われる。

#### 【0025】

第2窒化シリコン膜7は、厚さ5nm～50nm、例えば厚さ20nmで形成することが好ましい。第2窒化シリコン膜7は、LPCVD等により形成することができ、このLPCVDは、例えばソースガスとしてSiH<sub>2</sub>CL<sub>2</sub>とNH<sub>3</sub>を用い、温度750で行なうことができる。

30

#### 【0026】

第2窒化シリコン膜7は、引張応力を有しており、後で形成する第3酸化シリコン膜8aが熱処理によって収縮して半導体基板1の素子形成領域1aに与える圧縮応力を緩和する。この機能を十分に発揮させるために、第2窒化シリコン膜7は、その応力値が0.5～2GPaとなるように形成することが好ましい。第2窒化シリコン膜7によって素子形成領域1aに加わる圧縮応力が緩和され、圧縮応力によるドレイン電流の低下が抑えられる。第2窒化シリコン膜7が加工されて、窒化シリコン膜ライナーとなる。

40

#### 【0027】

### 3. 第3酸化シリコン膜形成工程（工程（c））

次に、第2窒化シリコン膜7を覆い、トレンチ5の途中の深さで埋め込みを終えるように第3酸化シリコン膜8aを異方性の成膜法によって形成し、図1(e)に示す構造を得る。

#### 【0028】

第3酸化シリコン膜8aは、異方性の成膜法によって形成される。異方性の成膜法を用いることにより、トレンチ5側壁上部に形成される第3酸化シリコン膜8aの膜厚を薄くすることができ、後工程において第2窒化シリコン膜7を露出させやすいからである。

#### 【0029】

第3酸化シリコン膜8aは、好ましくは、トレンチ5を埋め込む深さが半導体基板1表

50

面下  $1 \text{ nm} \sim 100 \text{ nm}$  (好ましくは  $5 \text{ nm} \sim 15 \text{ nm}$ ) となるように形成される。例えば、トレンチ深さが  $300 \text{ nm}$  の場合、トレンチ 5 内での第 3 酸化シリコン膜 8 a の厚さは、 $200 \sim 299 \text{ nm}$  (好ましくは  $285 \text{ nm} \sim 295 \text{ nm}$ ) とすることが好ましい。このとき、第 3 酸化シリコン膜 8 a は異方性の成膜法によって形成されるので、トレンチ 5 側壁での厚さを薄くすることができ、成膜条件を適宜調節することにより、例えば、厚さ  $1 \text{ nm} \sim 60 \text{ nm}$  にすることができる。

#### 【0030】

異方性の成膜法としては、HDP-CVD 法（高密度プラズマ化学気相成長法）や、塗布系の成膜法が挙げられる。HDP-CVD 法は、ICP（誘導結合プラズマ）や ECR（電子サイクロotron 共鳴）によるプラズマ等の高密度プラズマを用いた方法である（それぞれ、「ICP-CVD 法」、「ECR-CVD 法」と呼ぶ。）。この方法によれば、成膜と同時に Ar, He, H<sub>2</sub> 等のガスによるスパッタエッチングが行われるので、異方性の成膜が可能である。10

#### 【0031】

HDP-CVD 法による第 3 酸化シリコン膜 8 a の成膜は、例えば、ソースガスとして SiH<sub>4</sub> と O<sub>2</sub> と He の混合ガス、又は SiH<sub>4</sub> と O<sub>2</sub> と H<sub>2</sub> の混合ガスを用いて行うことができる。一例として、ICP-CVD 法による場合の成膜条件を以下に示す。

- ・ガス種 / 流量 : SiH<sub>4</sub> /  $30 \sim 180 \text{ sccm}$ , O<sub>2</sub> /  $80 \sim 500 \text{ sccm}$ , He /  $0 \sim 500 \text{ sccm}$

- ・低周波プラズマ ( $200 \sim 600 \text{ Hz}$ ) [成膜する為のプラズマ] :  $1000 \sim 500 \text{ W}$

- ・高周波プラズマ ( $5 \sim 30 \text{ MHz}$ ) [エッチングする為のプラズマ] :  $500 \sim 300 \text{ W}$

#### 【0032】

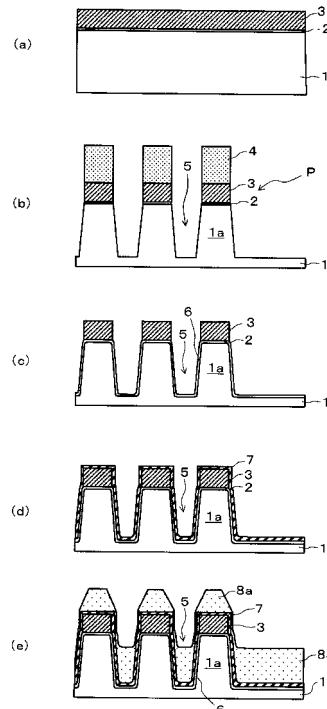

#### 4. 第 2 室化シリコン膜露出工程（工程 (d)）

次に、第 3 酸化シリコン膜 8 a を等方性エッチングし、トレンチ 5 側壁上部の第 2 室化シリコン膜 7 が露出するまで除去し、図 2 (f) に示す構造を得る。「等方性エッチング」とは、基板表面に水平な方向にも実用的な速度で進行する性質のエッチングを意味しており、水平方向と垂直方向の進行速度が完全に一致する性質のエッチングには限定されない。30

#### 【0033】

工程 (c) でトレンチ 5 側壁に第 3 酸化シリコン膜 8 a が比較的薄い膜厚で形成されており、トレンチ 5 下部は第 3 酸化シリコン膜 8 a が埋め込まれているので、第 3 酸化シリコン膜 8 a を等方性エッチングすることによって、トレンチ 5 側壁上部の第 2 室化シリコン膜 7 が露出する。等方性エッチングは、例えば、半導体基板 1 表面から、深さ  $50 \text{ nm} \sim 150 \text{ nm}$ までの範囲、例えば深さ  $50 \text{ nm}$  までの範囲において第 2 室化シリコン膜 7 が露出するまで行う。

#### 【0034】

等方性エッチングは、ウェットエッチングで行っても、ドライエッチングで行ってもよいが、ウェットエッチングが好ましい。

ウェットエッチングは、一例として、以下の条件で行うことができる。40

- ・エッチング液 : 希フッ酸

- ・エッチング時間 : 80 秒

ドライエッチングは、一例として、以下の条件で行うことができる。

- ・RF-Power :  $300 \sim 1200 \text{ W}$

- ・真空度 :  $30 \sim 120 \text{ Pa}$

- ・ガス種 / 流量 : CF<sub>4</sub> /  $150 \sim 400 \text{ sccm}$ , O<sub>2</sub> /  $150 \sim 400 \text{ sccm}$ , N<sub>2</sub> /  $30 \sim 150 \text{ sccm}$

#### 【0035】

本工程での第 3 酸化シリコン膜 8 a のエッチングは、工程 (c) での第 3 酸化シリコン

10

20

30

40

50

膜 8 a の形成に用いる装置と同一の装置を用いて連続的に行なうことが好ましい。例えば、I C P - C V D 装置を工程 ( c ) で示した成膜条件で動作させることによって第 3 酸化シリコン膜 8 a を形成し、その後、本工程の上記ドライエッティング条件で同一の装置を動作させることによって、装置から基板を取り出すことなく、連続的に、第 3 酸化シリコン膜 8 a の形成とエッティングを行うことができる。

## 【 0 0 3 6 】

## 5 . 露出した第 2 室化シリコン膜の除去工程 ( 工程 ( e ) )

次に、露出した第 2 室化シリコン膜 7 をエッティングして除去し、図 2 ( g ) に示す構造を得る。第 2 室化シリコン膜 7 が除去される範囲は、工程 ( d ) での第 3 酸化シリコン膜 8 a の等方性エッティング量を制御することによって、制御可能である。第 2 室化シリコン膜 7 は、好ましくは、半導体基板 1 表面から深さ 5 0 n m ~ 1 5 0 n m までの範囲において除去される。

## 【 0 0 3 7 】

本工程は、通常、等方性エッティングによって行われるが、酸化シリコンと実質的に反応しないエッティングガスを用いた異方性エッティングによって行ってもよい。

## 【 0 0 3 8 】

等方性エッティングは、ウエットエッティングで行っても、ドライエッティングで行ってもよいが、ウエットエッティングが好ましい。ウエットエッティングは、加熱磷酸 ( H<sub>3</sub>P O<sub>4</sub> ) などによって行なうことができる。

ドライエッティングは、一例として、以下の条件で行なうことができる。以下に示す条件では、第 3 酸化シリコン膜 8 a と第 2 室化シリコン膜 7 の両方のドライエッティングが可能である。

- ・ R F - P o w e r : 2 0 0 0 ~ 5 0 0 0 W

- ・ 真空度 : 3 0 ~ 6 0 0 P a

- ・ ガス種 / 流量 : N F<sub>3</sub> / 5 0 0 ~ 2 0 0 0 s c c m , O<sub>2</sub> / 5 0 ~ 5 0 0 s c c m

## 【 0 0 3 9 】

本工程での第 2 室化シリコン膜 7 のエッティングは、工程 ( c ) での第 3 酸化シリコン膜 8 a の形成と、工程 ( d ) での第 3 酸化シリコン膜 8 a のエッティングに用いた装置と同一の装置を用いて連続的に行なうことが好ましい。例えば、I C P - C V D 装置を工程 ( c ) で示した成膜条件で動作させることによって第 3 酸化シリコン膜 8 a を形成し、その後、本工程の上記ドライエッティング条件で同一の装置を動作させることによって、装置から基板を取り出すことなく、連続的に、第 3 酸化シリコン膜 8 a の形成とエッティング、及び第 2 室化シリコン膜 7 のエッティングを行なうことができる。

## 【 0 0 4 0 】

## 6 . 第 4 酸化シリコン膜形成工程 ( 工程 ( f ) )

次に、トレンチ 5 を埋め込むように第 4 酸化シリコン膜 8 b を形成し、図 2 ( h ) に示す構造を得る。第 4 酸化シリコン膜 8 b は、第 3 酸化シリコン膜 8 a と同じ方法で、厚さ 1 0 0 ~ 4 0 0 n m 、例えば 2 5 0 n m で形成することができる。別の観点では、第 4 酸化シリコン膜 8 b は、トレンチ 5 上方での第 4 酸化シリコン膜 8 b の表面が半導体基板 1 の表面よりも高い位置になるように形成され、好ましくは、第 1 室化シリコン膜 3 上の第 2 室化シリコン膜 7 の表面よりも高い位置になるように形成される。この場合、後工程での第 4 酸化シリコン膜 8 b の平坦化が行いやすいからである。

## 【 0 0 4 1 】

## 7 . 第 4 酸化シリコン膜平坦化工程 ( 工程 ( g ) )

次に、第 2 室化シリコン膜 7 又は第 1 室化シリコン膜 3 をストップとして、第 4 酸化シリコン膜を平坦化させ、図 2 ( i ) に示す構造を得る。通常は、第 2 室化シリコン膜 7 がストップとなるが、本工程の前に第 2 室化シリコン膜 7 を別工程によって除去している場合や、本工程で平坦化を過剰に行って第 2 室化シリコン膜 7 が除去される場合などには、第 1 室化シリコン膜 3 がストップとなる。

## 【 0 0 4 2 】

10

20

30

40

50

平坦化は、C M P（化学的機械研磨）によって行うことができる。C M Pは、酸化シリコン膜に対する研磨速度（研磨による膜厚減少速度）が、窒化シリコン膜に対する研磨速度よりも大きくなる条件で行う。C M Pは、例えば、酸化シリコンまたは酸化セリウムを砥粒とする研磨剤を用いて行うことができる。

平坦化は、C M P以外の方法、例えば、R I Eエッティングによるエッチバックにより、行ってもよい。

#### 【0043】

本工程の前又は後に、900～1100 例えば1000、30分のアニールを行い、第3及び第4酸化シリコン膜8a, 8bを緻密化する工程を備えてよい。

#### 【0044】

#### 8 . 第2及び第1窒化シリコン膜除去工程（工程（h））

次に、第2及び第1窒化シリコン膜7, 3、又は第1窒化シリコン膜3をエッティングして除去し、図2（j）に示す構造を得る。本工程では、通常は、第2及び第1窒化シリコン膜7, 3を除去するが、本工程以前の工程で第2窒化シリコン膜7を既に除去している場合には、第1窒化シリコン膜3を除去する。

#### 【0045】

エッティングは、加熱磷酸（H<sub>3</sub>PO<sub>4</sub>）を用いて行うことができる。なお、トレンチ5の側壁下部に形成された第2窒化シリコン膜7は、第4酸化シリコン膜8bで覆われているのでエッティングされない。従って、第2窒化シリコン膜7がエッティングされることによる凹部の発生は防止される。

#### 【0046】

以上で、本実施形態のトレンチ素子分離領域の形成を完了する。この後、半導体基板上に種々の半導体素子を形成することによって、半導体装置を製造することができる。

上記実施形態から1又は複数個の特徴を適宜抜き出して、単独で又は組み合わせて、本発明に採用することができる。

#### 【実施例】

#### 【0047】

実際に本発明の方法、背景技術に示した方法を用いてトレンチ素子分離領域を形成した。第2窒化シリコン膜7の厚さは、20nmとした。

幅1μmの素子分離領域及び幅0.18μmの素子分離領域の、トレンチ5側壁上部での第2窒化シリコン膜7の除去深さは、それぞれ、表1のようになった。

#### 【表1】

|            | 除去深さ        |                |

|------------|-------------|----------------|

|            | 幅1μmの素子分離領域 | 幅0.18μmの素子分離領域 |

| 本発明の方法     | 100nm       | 70nm           |

| 背景技術に示した方法 | 100nm       | 50nm           |

表1により、本発明によれば、素子分離領域の幅の違いによる除去深さのばらつきを減少させることができることが分かる。

#### 【図面の簡単な説明】

#### 【0048】

【図1】（a）～（e）は、本発明の一実施形態のトレンチ素子分離領域の形成工程を示す断面図である。

【図2】（f）～（j）は、本発明の一実施形態のトレンチ素子分離領域の形成工程を示す断面図である。

#### 【符号の説明】

#### 【0049】

1：半導体基板 1a：素子形成領域 2：第1酸化シリコン膜 3：第1窒化シリコン膜 4：レジストパターン 5：素子分離用トレンチ 6：第2酸化シリコン膜 7：第

2 窒化シリコン膜 8 a : 第 3 酸化シリコン膜 8 b : 第 4 酸化シリコン膜 P : 素子分離用トレンチ形成用パターン

【図 1】

【図 2】