(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5985529号

(P5985529)

(45) 発行日 平成28年9月6日(2016.9.6)

(24) 登録日 平成28年8月12日(2016.8.12)

(51) Int.Cl.

F 1

G06F 11/14 (2006.01)

G06F 11/14

6 4 1 D

G06F 1/30 (2006.01)

G06F 1/30

M

G06F 3/08 (2006.01)

G06F 3/08

H

請求項の数 20 (全 11 頁)

(21) 出願番号 特願2014-50327 (P2014-50327)

(22) 出願日 平成26年3月13日 (2014.3.13)

(65) 公開番号 特開2014-179095 (P2014-179095A)

(43) 公開日 平成26年9月25日 (2014.9.25)

審査請求日 平成27年1月28日 (2015.1.28)

(31) 優先権主張番号 13/803,015

(32) 優先日 平成25年3月14日 (2013.3.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 500373758

シーゲイト テクノロジー エルエルシー

Seagate Technology

LLC

アメリカ合衆国、95014 カリフォルニア州、クパチーノ、サウス・ディ・アンザ・ブールバード、10200

10200 South De Anza Blvd Cupertino CA

95014 United States of America

(74) 代理人 110001195

特許業務法人深見特許事務所

最終頁に続く

(54) 【発明の名称】ハイバネーションからの迅速な再開のための装置、方法およびデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

装置であって、

データ記憶デバイス(DSD)を備え、前記DSDは、回路を含み、

前記回路は、

前記DSD内の第1の不揮発メモリにおけるハイバネーションデータの第1のメモリ場所を、前記DSDのハイバネーションパーティションに基づき前記第1のメモリ場所の指示をホストから受信することなく判定し、

前記ハイバネーションデータを前記DSD内の第2の不揮発メモリにおける第2のメモリ場所に記憶する、

10 ように構成される、装置。

## 【請求項 2】

インターフェースであって、前記DSDが、前記ホストから物理的に取り外されることと、前記インターフェースが前記ホストに連結されると前記ホストから指令を受信することと、を許容するように構成された、インターフェースを更に備える、請求項1に記載の装置。

## 【請求項 3】

パーティションテーブルを検索することによって、前記データ記憶デバイスのハイバネーションパーティションを識別するように構成された回路を更に備える、請求項1または請求項2に記載の装置。

**【請求項 4】**

前記ハイバネーションデータが前記第2のメモリ場所に記憶された後で、更なるハイバネーションデータを受信し、前記更なるハイバネーションデータを前記第2のメモリ場所に記憶するように構成された回路を更に備える、請求項3に記載の装置。

**【請求項 5】**

前記第2のメモリ場所が、前記第1の場所よりも速いアクセス時間有することを更に含む、請求項4に記載の装置。

**【請求項 6】**

前記第1のメモリ場所が、ディスクデータ記憶媒体であり、前記第2のメモリ場所が、不揮発性ソリッドステート記憶媒体であることを更に含む、請求項5に記載の装置。 10

**【請求項 7】**

前記更なるハイバネーションデータが、データを前記第1のメモリ場所に記憶するための命令を含むことを更に含む、請求項4に記載の装置。

**【請求項 8】**

指定されたパーティションタイプに基づいて、前記ハイバネーションデータの場所を判定するように構成された回路を更に備える、請求項3に記載の装置。

**【請求項 9】**

ハイバネーションデータを求めて前記DSDの前記パーティションの各々を検索するように構成された回路を更に備える、請求項8に記載の装置。

**【請求項 10】**

前記ハイバネーションパーティションと関連付けられたハイバネーションパーティションタイプを識別するパーティションテーブルを含む、パーティション識別システムを更に備える、請求項3に記載の装置。 20

**【請求項 11】**

前記パーティションテーブルが変更されたかどうかを判定し、

前記パーティションテーブルが変更された場合、ハイバネーションデータの第1のメモリ場所を、前記ホストから前記第1のメモリ場所の指示を受信することなく判定することを繰り返す、

ように構成された回路を更に備える、請求項10に記載の装置。

**【請求項 12】**

ホストから取り外し可能なデータ記憶デバイス(DSD)内部で、前記DSD内の第1の不揮発メモリにおけるハイバネーションデータの第1のメモリ場所を、前記DSDのハイバネーションパーティションに基づき、ホストから前記第1のメモリ場所の指示を受信することなく判定することと、

前記ハイバネーションデータを前記DSD内の第2の不揮発メモリにおける第2のメモリ場所に記憶することと、

を含む、方法。

**【請求項 13】**

前記第1のメモリ場所を有するハイバネーションパーティションを、パーティションタイプに基づいて判定することを更に含む、請求項12に記載の方法。 40

**【請求項 14】**

前記第1のメモリ場所向けの更なるデータを前記ホストから受信することと、前記第2のメモリ場所にある前記ハイバネーションデータを前記更なるデータで更新すること、を更に含む、請求項13に記載の方法。

**【請求項 15】**

パーティション識別記録が変更されたかどうかを判定することと、

前記パーティション識別記録が変更された場合、前記第1のメモリ場所の場所を判定することを繰り返すことと、

を更に含む、請求項12に記載の方法。

**【請求項 16】**

50

前記第1のメモリ場所より速いアクセス時間有する前記第2のメモリ場所のためのメモリ記憶場所を選択することを更に含む、請求項1-2に記載の方法。

【請求項1-7】

第1の不揮発メモリと、

前記第1の不揮発メモリとは異なる少なくとも1つのプロパティを有する第2の不揮発メモリと、

前記第1の不揮発メモリにあるハイバネーションパーティションを格納すべきものと意図されたハイバネーションデータの第1のデータ記憶場所を、ホストから前記第1のデータ記憶場所の指示を受信することなく判定し、

前記ハイバネーションデータを、前記第2の不揮発メモリの第2のデータ記憶場所に記憶する、10

ように構成された、コントローラと、

を備える、デバイス。

【請求項1-8】

前記少なくとも1つの異なるプロパティが、前記第1の不揮発メモリのアクセス速度と比較した前記第2の不揮発メモリのアクセス速度であることを更に含む、請求項1-7に記載のデバイス。

【請求項1-9】

前記少なくとも1つの異なるプロパティが、前記第1の不揮発メモリの信頼性と比較した前記第2の不揮発メモリの信頼性であることを更に含む、請求項1-7に記載のデバイス。20

【請求項2-0】

ホストから指令およびデータを受信するように構成され、前記デバイスが前記ホストから分離されることを許容するようにも構成される、インターフェースと、

パーティションテーブル中で識別されたハイバネーションパーティションを検索することによって、前記第1のデータ記憶場所を識別し、

更なるハイバネーションデータを受信して、前記更なるハイバネーションデータを前記第2のデータ記憶場所に記憶する、

ように更に構成された、前記コントローラと、

を更に備える、請求項1-7から請求項1-9のいずれか1項に記載のデバイス。30

【発明の詳細な説明】

【技術分野】

【0001】

背景

本開示は、コンピュータシステムおよび記憶デバイスの中でのハイバネーション機能に関する。

【発明の概要】

【課題を解決するための手段】

【0002】

データ記憶デバイスは、ハイバネーションデータの第1のメモリ場所を、ホストからこの第1のメモリ場所の指示を受信することなく判定し、このハイバネーションデータをデータ記憶デバイスの第2のメモリ場所に記憶するように構成された回路を含み得る。40

【0003】

ある方法は、ホストから取り外し可能なデータ記憶デバイス(DSD)内部で行われ、ハイバネーションデータの第1のメモリ場所を、ホストからこの第1のメモリ場所の指示を受信することなく判定し得る。この方法は、ハイバネーションデータを、データ記憶デバイスの第2のメモリ場所に記憶し得る。

【0004】

あるデバイスは、第1のメモリと、この第1メモリとは異なる少なくとも1つのプロパティを有する第2のメモリと、コントローラとを含み得る。このコントローラは、第1の50

メモリでのハイバネーションデータの第1のデータ記憶場所を、ホストからこの第1のデータ記憶場所の指示を受信することなく判定し、このハイバネーションデータを第2のメモリの第2のデータ記憶場所に記憶するように構成することが可能である。

**【図面の簡単な説明】**

**【0005】**

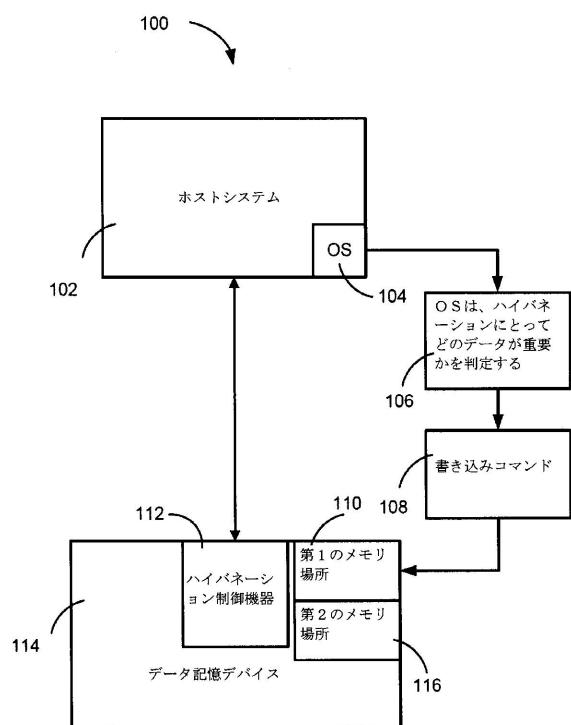

【図1】ハイバネートから迅速に再開するシステムの例示の実施形態の図である。

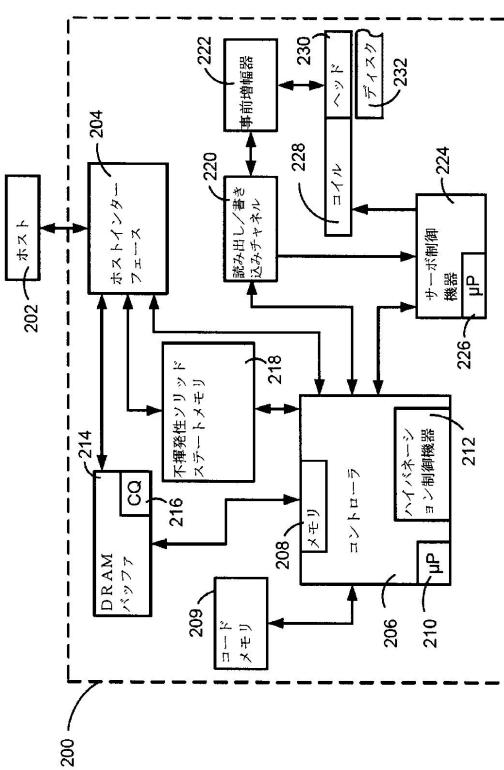

【図2】ハイバネートから迅速に再開するシステムの別の例示の実施形態の図である。

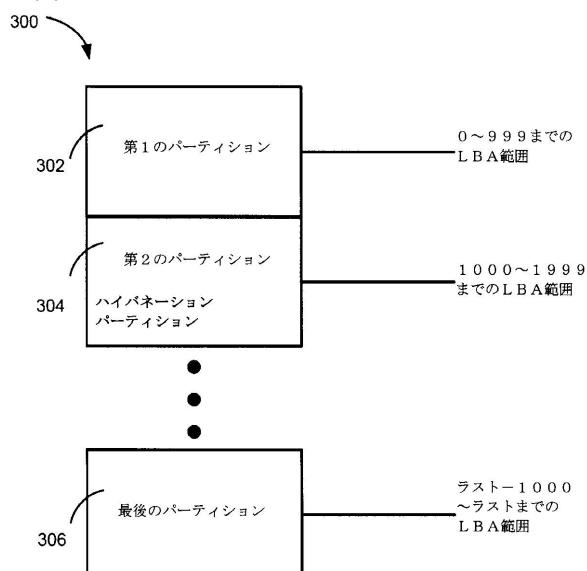

【図3】ハイバネートから迅速に再開する記憶パーティションの例示の実施形態の図である。

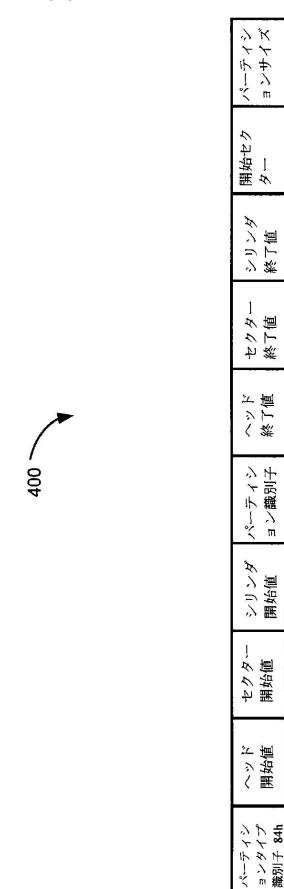

【図4】ハイバネートからの迅速な再開に対するサンプルパーティションテーブルである

10

。

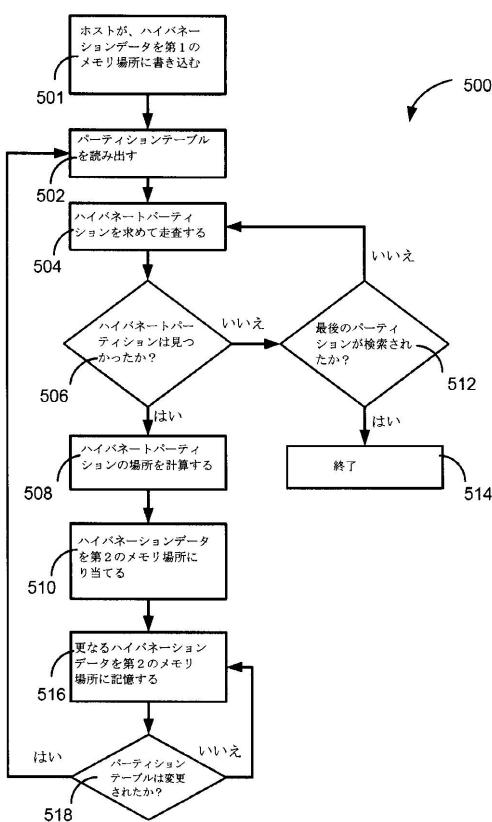

【図5】ハイバネートから迅速に再開する方法の例示の実施形態のフローチャートである

。

**【発明を実施するための形態】**

**【0006】**

実施形態の以下の詳細な説明において、本明細書の一部を形成し、その明細書において特定の実施形態の例示として示される、添付の図面に対する参照がなされる。他の実施形態が利用され得ることと、構造的変更が本開示の範囲から逸脱することなくなされ得ることとが理解されるべきである。

**【0007】**

20

コンピュータシステムは、オペレーティングシステムのステータスを保存しながらも、電力を節約するためにハイバネーション状態に置かれ得る。しかしながら、ユーザがコンピュータをハイバネーションから脱出させてからコンピュータが完全に目覚めて作動するまでの、20～30秒の長さにもなりかねない時間間隔のために、問題が起りかねない。オペレーティングシステムは、ドライバ、およびデータ記憶デバイス(DSD)とのインターフェースを有して、起動時間をより早くするためにDSDに情報を提供することが可能である。しかしながら、このようなドライバおよびインターフェースは、煩雑であり得る。したがって、起動時間を減少させ、追加のドライバおよびインターフェースに対する必要性を排除するシステムおよび方法を、本明細書で提示する。

**【0008】**

30

図1を参照すると、ハイバネートから迅速に再開するシステムの例示の実施形態が示されており、一般的に100と示されている。ホスト102システムは、デスクトップ、ラップトップ、タブレット、電話、またはハイバネーションシステムを使用し得る他の任意の計算システムであり得る。ホストシステム102は、106で、ハイバネーション状態にあるときに記憶すべき重要なデータを判定することが可能なオペレーティングシステム(OS)104を含み得る。ハイバネーションデータは、108で、DSD114の第1のメモリ場所110に、書き込むことが可能である。第1のメモリ場所110は、不揮発性ソリッドステート媒体、ディスク記憶媒体、または他の任意の記憶媒体であり得る。

**【0009】**

さらに、ホストシステム102は、ハイバネーション制御機器112と通信状態にあり得るが、これは、ソフトウェア、コントローラ、ハードウェアロジック、ディスクリート回路、またはこれらの任意の組み合わせを用いて実現され得る。DSD114は、ハイブリッドデバイス、ソリッドステートデバイス、光学デバイス、磁気デバイス、他の任意のタイプのデータ記憶デバイス、またはこれらの任意の組み合わせであり得る。

**【0010】**

ホストシステム102は、ハイバネーションデータをDSD114に送り、また、DSD114に、このハイバネーションデータをハイバネーションパーティションに記憶するように命令し得る。一部の実施形態では、このハイバネーションパーティションは、パーティション識別子(ID)を介して指定することが可能である。各々のパーティションは、パーティションIDを有することが可能であるが、パーティションIDは、OSのタイ

40

50

プに基づいて異なり得る。例えば、マイクロソフトウインドウズ7OSでは、ハイバネーションパーティションのパーティションIDは84hである。DSD114は、どのパーティションID値がハイバネーションパーティションを示すかを知り得るが、DSD114は、ハイバネーションパーティションが配置される論理ブロックアドレス(LBA)範囲または物理的場所を本質的には知り得ない。

#### 【0011】

動作中、ハイバネーション制御機器112は、ホスト102からの通知なしで、ハイバネーションデータの場所を単独で判定するように構成することが可能である。ハイバネーション制御機器112は、ハイバネーションデータの場所をパーティショントラップに基づいて判定し得る。

10

#### 【0012】

1つの例では、ハイバネーション制御機器112は、ハイバネーションパーティションに対応するパーティションIDを求めてマスターブート記録(MBR)を走査することが可能である。ハイバネーションパーティションが見つかれば、ハイバネーション制御機器112は、ハイバネーションパーティションに対する論理ブロックアドレス(LBA)範囲を判定することによって、ハイバネーションパーティションの場所を計算し得る。この例では、DSD114にとって、ハイバネーションパーティションまたはハイバネーションデータを突き止めるためには、ホストのヒントは必要ない。ハイバネーションパーティションは、不揮発性のソリッドステート媒体、ディスク記憶媒体、または他の任意の記憶媒体を含み得る。

20

#### 【0013】

ハイバネーション制御機器112は、適切なパーティションを選択して、次に、読み出しあり書き込み用の後続の第2のメモリ場所116を指定することによって、第2のメモリ場所116にハイバネーションデータを割り当て得る。LBA範囲の第2のメモリ場所116は、第1のメモリ場所よりも速いアクセス時間を有し得、かつ多層DSDのいずれかの層に配置され得る不揮発性のソリッドステート媒体を含み得る。例として、多層メモリシステムの層1および層2が、層3よりも早い場合、第1のメモリ場所を層3に配置することが可能であり、第2のメモリ場所を層1または層2に配置し得る。第2のメモリパーティションは、不揮発性のソリッドステート媒体、ディスク記憶媒体、または他の任意の記憶媒体を含み得る。

30

#### 【0014】

図2を参照すると、ハイバネートから迅速に再開するデータ記憶デバイスの実施形態が図示され、一般的に200と示されている。このデータ記憶デバイス200は、データ記憶デバイス200をホスト200から物理的に取り外すことを許容するコネクタを含み得るインターフェース204を介してホストデバイス202と通信することが可能である。インターフェース204は、ハードウェア回路、ロジック、ファームウェア、またはこれらの任意の組み合わせを含み得る。ある特定の実施形態では、インターフェース204は、データ記憶デバイスを、USB、IEEE1394、CompactFlash、SATA、eSATA、PATA、SCSI、SAS、またはファイバチャネルなどの別のコンピュータシステムに取り付けることを許容するインターフェースを備える。データ記憶デバイス200は、ホスト202の筐体の内部または外部にあり得る。

40

#### 【0015】

データ記憶デバイス200は、関連付けられたメモリ208およびプロセッサ210を持つプログラム可能コントローラ206を含むことが可能である。プログラム可能コントローラ206は、メモリ209およびバッファ214に連結され得る。メモリ209は、ファームウェアコード、すなわちブートコードを記憶することが可能な、FlashまたはEEPROMなどの、不揮発性ソリッドステートメモリであって、コントローラが、ディスク232に対するスピンドルアップシーケンスなどの、データ記憶デバイス200の機能を実施することを許容する。バッファ214は、読み出し動作および書き込み動作中にユーザデータを一時的に記憶することが可能であり、また、複数の処理待ちアクセス動作を

50

実行待ち状態に一時的に記憶することが可能な指令待ち行列（C Q）216を含むことが可能である。C Q 216は、不揮発性メモリまたは揮発性メモリに配置し得る。

#### 【0016】

さらに、図2は、データ記憶デバイス200が、書き込み動作中にデータを符号化し、読み出し動作中にディスク（複数可）232から受信したユーザデータを再現する読み出し／書き込み（R/W）チャネル220を含むことが可能であることをさらに示す。プリアンプ／ドライバ回路（プリアンプ）222は、書き込み電流をヘッド（複数可）230に印加し、また、リードバック信号を事前増幅し得る。サーボ制御回路224は、サーボデータを用いて適切な電流をコイル228に提供し、ヘッド（複数可）230を位置付けすることができる。コントローラ206は、コマンドキュー216におけるさまざまな保留コマンドの実行の間に、（複数の）ディスク232上の所望の位置に（複数の）ヘッド230を動かすように、プロセッサ226と通信することができる。10

#### 【0017】

ある特定的な実施形態では、データ記憶デバイス200はまた、コントローラ206の内部にあるファームウェア、ロジック、もしくは回路であり得る、またはこのコントローラの外部にあり得る、ハイバネーション制御機器212を含み得る。ハイバネーション制御機器212は、図1に示すハイバネーション制御機器112であり得、DSD200は、図1に示すDSD114であり得る。ホスト202は、ホストインターフェース204を介してDSD200に指令を送って、DSD200のデータ記憶媒体のうちの1つ以上のハイバネーションパーティションに配置され得る第1のメモリ場所にハイバネーションデータを記憶し得る。このハイバネーションパーティションは、不揮発性のソリッドステート媒体218、ディスク記憶媒体232、または他の任意の記憶媒体を含み得る。20

#### 【0018】

動作中、ハイバネーション制御機器212は、ホストからの通知なしで、ハイバネーションデータの場所を単独で判定するように構成することが可能である。例えば、ハイバネーション制御機器212は、ハイバネーションデータの場所をパーティションタイプに基づいて判定することが可能である。これを実現するために、ハイバネーション制御機器212は、ハイバネーションパーティションに対応するパーティションIDを求めてマスターント記録（MBR）を走査し得る。ハイバネーションパーティションが見つかれば、ハイバネーション制御機器212は、ハイバネーションパーティションに対する論理プロックアドレス（LBA）範囲を判定することによって、ハイバネーションパーティションの場所を計算し得る。したがって、DSD200にとって、ハイバネーションパーティションまたはハイバネーションデータを突き止めるためには、ホストのヒントは必要ない。ハイバネーション制御機器212は、別のパーティションまたはデータ記憶媒体などの適切な場所を選択して、次に、ハイバネーションパーティションのために意図される後続の読み出しあり書き込み用の第2のメモリ場所を指定することによって、第2のメモリ場所にハイバネーションデータを割り当てる。第2のメモリ場所は、第1のメモリ場所よりも速いアクセス時間を有し得る。第2のメモリ場所は、不揮発性のソリッドステート媒体、ディスク記憶媒体、または他の任意の記憶媒体を含み得る。30

#### 【0019】

DSD200またはその中のデータ記憶媒体のいずれかのメモリ記憶容量は、論理的または物理的パーティションに分割され得る。パーティションは、類似のまたは互いに異なった機能を有し得るが、不揮発性のソリッドステート媒体218またはディスク記憶媒体232などの、DSD200中の利用可能なデータ記憶メモリのうちのいずれかに配置され得る。40

#### 【0020】

図3を参照すると、ハイバネットから迅速に再開する記憶パーティションの例示の実施形態の図が示されており、一般的に300と示される。図3の例では、第1のパーティション302、第2のパーティション304、第nのパーティション306などの、DSDと関連付けられたいくつかのパーティションがあり得る。各々のパーティションは、パー50

ティションのうちの少なくとも 1 つがハイバネーションパーティションとして指定されるパーティションタイプを割り当てられ得る。図 3 に示す例では、第 2 のパーティション 304 は、ハイバネーションパーティションとして指定され、また、1000 から 1999 までなどの論理ブロックアドレス (LBA) の関連付けられた範囲を有し得る。

#### 【0021】

この割り当てられたパーティションタイプは、OS によって定義もしくは作成され、または OS の具体的な要件に順守するように作成され得る。各々のパーティションは、異なったパーティションタイプを有し、また、あるパーティションをハイバネットパーティションとして指定する 1 つ以上のパーティションまたはパーティションタイプが存在し得る。割り当てられたパーティションタイプは、図 4 に示す例となるマスターブート記録 (MBR) などのパーティション記録中に指定され得る。10

#### 【0022】

図 4 を参照すると、一般的に 400、すなわち、マスターブート記録 (MBR) パーティションテーブルという形態のパーティション記録の例が、示されている。このようなテーブルは、DSD 内のパーティションに関連する識別情報および他の有用な情報を記憶することが可能である。この例 400 では、左から右へ、テーブル中のエントリは、パーティションタイプ識別子、ヘッド開始値、セクター開始値、シリンド開始値、パーティション識別子 (CEh)、ヘッド終了値、セクター終了値、シリンド終了値、開始セクター値、およびパーティションサイズ値を含むことが可能である。このような例となるテーブルは、シリンド - ヘッド - セクター別のデータ記憶媒体と共に使用可能であり、また、このデータ記憶媒体のパーティションにアクセスしてこれらを用いるために必要な情報を提供することが可能である。しかしながら、このテーブルの変形形態を、DSD のタイプおよび関連付けられた OS に基づいて、必要に応じて、これより多いまたは少ないエントリを持つように構築することが可能である。20

#### 【0023】

本明細書中のシステムおよび機能は、パーティションタイプを示すいかなるタイプのシステムとも連動することが可能である。パーティションテーブルまたは記録は、DSD のメモリに記憶し得るが、これによって、DSD または OS は、このパーティション記録を検索して、どのパーティションがハイバネットパーティションとして指定されているかを判定することを許容することが可能である。加えて、DSD または OS を、他のパーティションタイプを選択して、これと関連付けられたデータ記憶を、現在の物理的場所よりも早いまたは信頼性の高いレベルのデータ記憶に促進するように選ぶことが可能である。30

#### 【0024】

更に、DSD は、MBR または GUID パーティションテーブル (GPT) などの異なった識別システムを用い得る。MBR 識別システムは、最大で 4 つの一次パーティションを持つ DSD をサポートすることが可能であり、また、GPT 識別システムは、無制限の数のパーティションを持つ DSD をサポートすることが可能である。更に、本明細書に説明するこれらの DSD は、基本入出力システム (BIOS) の代わりであるユニファイド・エクステンシブル・ファームウェア・インターフェース (UEFI) イニシアティブに適合することが可能である。40

#### 【0025】

図 5 を参照すると、ハイバネットから迅速に再開する方法の例示の実施形態のフローチャートが図示されており、一般的に 500 と示される。この方法 500 は、DSD が、どのデータ記憶エリアがハイバネーションデータのために用いられるかを、ホストからの干渉や指示なしで自己判定することを許容する。方法 500 は、501 で、ホストが、データを第 1 のメモリ場所に記憶するように DSD に指令を送ることを含み得る。DSD は、502 でパーティションテーブルを読み出し、504 でハイバネーションパーティションを判定するためにこのパーティションテーブルを走査し得る。DSD は、506 で、パーティションテーブル中のパーティションの各々のパーティション ID を見ることによってハイバネーションパーティションを検索することが可能である。パーティションテーブル50

は、マスターブート記録（MBR）などの、上述した例に類似し得る。ハイバネーションパーティションが見つからなければ、512で、DSDは、ハイバネーションパーティションが見つかるまでパーティションを検索し続け得る。ハイバネーションパーティションが見つからず、かつすべてのパーティションが検索された場合、検索は514で終了し得る。DSDは、いつでも走査を終了し得る。

#### 【0026】

ハイバネーションパーティションが見つかれば、DSDは、508で、ハイバネーションパーティションの場所を計算することが可能である。ハイバネーションパーティションの場所は、ハイバネーションパーティションのLBA範囲を判定することによって計算し得る。510で、DSDは、次に、適切なメモリ場所を選択し、次に、ハイバネーションデータを記憶するようにこの選択したメモリ場所を指定することによって、ハイバネーションデータを第2のメモリ場所に割り当て得る。この選択されたメモリ場所は、不揮発性のソリッドステート媒体を含み、また、第1のメモリ場所よりも早いアクセス時間有し得る。DSDは、516で、この選択されたメモリ場所におけるハイバネーションパーティション用に意図されたデータを記憶し得る。また、DSDは、516で、更なるハイバネーションデータまたはパーティションを検索し、また、更なるハイバネーションデータを、選択されたメモリ場所に記憶し得る。

#### 【0027】

いくつかの事例では、ホストがDSDに書き込みをすると、パーティションテーブルが変更され得る。518で、DSDは、パーティションテーブルが変化したかどうかを絶えずチェックすることが可能である。パーティションテーブルが変化していない場合、DSDは、516で、ハイバネーションデータを選択されたメモリ場所に記憶し続け得る。パーティションテーブルが変化していれば、DSDは、変化したパーティションテーブルを502で読み出して、このプロセスを最初から開始することが可能である。DSDは、パーティションテーブルが変化したかどうかを絶えずチェックするのではなく、むしろ、周期的にチェックしたり、非周期的にチェックしたり、トリガ事象（指令、電力事象、またはエラー表示など）に応答してチェックしたり、または、パーティションテーブルに対する変化をチェックしなかったりし得る。

#### 【0028】

本明細書に説明する実施例では、DSDは、ホストとは無関係にハイバネーションパーティションの場所を判定することが可能であり、また、ハイバネーションデータを優先的に記憶する異なったメモリ場所があるかどうかを判定することが可能であるため、ハイバネーションパーティションの場所を判定するために、ホストから干渉も、命令も、ヒントも必要としない。更に、本明細書中の方法および機能は、図1のDSD114または図2のDSD200を介して実現され得る。

#### 【0029】

本明細書に提供される説明および例は、本開示をどのようにデータ記憶システムに応用可能であるかについての少数の例にすぎない。本明細書に説明される方法およびシステムが、計算システムおよびデータ記憶システムに応用可能な関連が他にも多く存在する。例えば、本明細書に説明される方法およびシステムは、計算システム、およびハイブリッドストレージを有するデータ記憶デバイスにとって、この計算システムまたはこのデータ記憶デバイスが、少なくとも1つの不揮発性ソリッドステートデータ記憶媒体および少なくとも1つのディスク記憶媒体を有する場合、またはハイブリッドデータ記憶デバイスが、異なるプロパティを持つ2つの異なるタイプの不揮発性メモリを有し、かつこれらのタイプのメモリのうちの一方がハイバネーションデータを優先的に記憶する場合などに、特に有用である。

#### 【0030】

限定されるものではないが、特定用途向け集積回路、プログラム可能な論理アレイ、および他のハードウェアデバイスを含む専用ハードウェアの実装は、本明細書に記載された方法を実装するように同様に構築され得る。更に、本明細書に説明される方法は、実行さ

10

20

30

40

50

れると、プロセッサに対して、本明細書に説明される方法および機能を実施させる命令を含む、コンピュータ可読媒体として実現され得る。

### 【0031】

本明細書に記載された実施形態の実例は、さまざまな実施形態の構造の一般的な理解を与えることを意図される。実例は、本明細書に記載された構造もしくは方法を利用する装置およびシステムの要素や特徴の全ての完全な記載として供されることを意図されない。多くの他の実施形態は、開示を検討すれば、当業者に明らかであろう。他の実施形態は、構造的および論理的置換や変更が開示の範囲から逸脱することなくなされ得るように、利用され得、開示から導かれ得る。その上、特定の実施形態が本明細書に例示され記載されたが、同じまたは類似目的を達成するように設計された任意の後続の配置が、示された特定の実施形態に置換され得ることが理解されるべきである。10

### 【0032】

この開示は、さまざまな実施形態の任意のおよび全ての後続の適応または変形を包含することが意図される。上記実施形態の組み合わせ、および本明細書に特に記載されていない他の実施形態は、説明を再検討すれば、当業者に明らかになるであろう。更に、実例は、単に代表するものであり、縮尺に合わせて描かれていない可能性がある。実例の範囲内の一定部分は、誇張され得る一方で、他の部分は縮小され得る。したがって、開示および図面は、限定的なものではなくて、例示的なものとして、みなされるべきである。

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ロバート・デール・マーフィー

アメリカ合衆国、80503 コロラド州、ロングモント、ベニス・レーン、1635

(72)発明者 ロバート・ウィリアム・ディクソン

アメリカ合衆国、80503 コロラド州、ロングモント、ウィッジン・ドライブ、310

審査官 滝谷 亮一

(56)参考文献 特開2014-115977(JP,A)

特表2012-514787(JP,A)

特開2001-134338(JP,A)

特開2001-134384(JP,A)

特表2011-508341(JP,A)

米国特許出願公開第2010/0106886(US,A1)

米国特許出願公開第2008/0082743(US,A1)

米国特許出願公開第2009/0327608(US,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 11/14

G06F 1/30

G06F 3/08