(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4685310号

(P4685310)

(45) 発行日 平成23年5月18日(2011.5.18)

(24) 登録日 平成23年2月18日(2011.2.18)

(51) Int.Cl.

H03M 1/12 (2006.01)

G 11 C 27/02 (2006.01)

F 1

H03M 1/12

G 11 C 27/02 601Z

請求項の数 19 (全 18 頁)

(21) 出願番号 特願2001-527292 (P2001-527292)

(86) (22) 出願日 平成12年9月25日 (2000.9.25)

(65) 公表番号 特表2003-510933 (P2003-510933A)

(43) 公表日 平成15年3月18日 (2003.3.18)

(86) 國際出願番号 PCT/SE2000/001854

(87) 國際公開番号 WO2001/024192

(87) 國際公開日 平成13年4月5日 (2001.4.5)

審査請求日 平成19年9月20日 (2007.9.20)

(31) 優先権主張番号 9903532-1

(32) 優先日 平成11年9月28日 (1999.9.28)

(33) 優先権主張国 スウェーデン(SE)

(73) 特許権者 598036300

テレフォンアクチーボラゲット エル エ

ム エリクソン (パブル)

スウェーデン国 ストックホルム エスー

164 83

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

最終頁に続く

(54) 【発明の名称】種々の電荷サンプリング回路

## (57) 【特許請求の範囲】

## 【請求項 1】

電荷サンプリング (CS) 回路 (1) であって、制御信号発生器 (4) を備え、サンプリング段階で前記制御信号発生器 (4) からのサンプリング信号に応じて前記電荷サンプリング回路 (1) へのアナログ入力信号を制御して積分器 (3) で積分し、ここで前記アナログ入力信号の電流を積分して積分電荷を生成してサンプリング段階の終わりに比例電圧または電流のサンプルを信号出力に生成し、

前記サンプリング段階は時刻  $t_1$  から時刻  $t_2$  までであって、ここで前記サンプルは時刻  $t_s = (t_1 + t_2) / 2$  での前記アナログ信号の瞬時値を表し、一定部分と周波数依存部分  $(\sin(2\pi f_i t)) / (2\pi f_i t)$  から成る係数だけ前記瞬時値とは異なる、ただし、 $f_i$  は前記アナログ信号の第  $i$  成分の周波数であり、 $t = (t_2 - t_1) / 2$ 、すなわち、前記サンプリング段階の幅の半分であることを特徴とする、電荷サンプリング (CS) 回路 (1)。

## 【請求項 2】

請求項 1 記載の電荷サンプリング (CS) 回路 (1) であって、

アナログ入力信号のための信号入力と、前記積分器 (3) の信号入力に接続する信号出力と、前記制御信号発生器 (4) のサンプリング信号出力に接続して前記発生器 (4) からの前記サンプリング信号がサンプリング段階にあるときだけ前記スイッチを制御して導通させる制御入力を有するサンプリング・スイッチ (2) を特徴とする、電荷サンプリング (CS) 回路 (1)。

## 【請求項 3】

請求項 1 または 2 記載の電荷サンプリング回路であって、

前記制御信号発生器 (4) は前記積分器 (3) を制御して、前記発生器 (4) からのリセット信号を前記積分器 (3) の制御入力に与えるまで前記サンプルを保持することを特徴とする、電荷サンプリング回路。

## 【請求項 4】

請求項 1 乃至 3 のいずれか 1 項に記載の第 1 および第 2 の C S 回路を特徴とする差動電荷サンプリング (C S) 回路であって、

ここで前記 C S 回路の全ての制御信号発生器を共通の制御信号発生器 (4) に置き換える、前記第 1 の C S 回路の信号入力は前記差動 C S 回路の第 1 のアナログ入力であり、前記第 2 の C S 回路の信号入力は差動アナログ信号用の前記差動 C S 回路の第 2 の入力であり、前記第 1 の C S 回路の信号出力と前記第 2 の C S 回路の信号出力は前記差動 C S 回路の第 1 の信号出力と第 2 の信号出力である、差動電荷サンプリング (C S) 回路。

10

## 【請求項 5】

請求項 4 記載の差動電荷サンプリング回路であって、

前記第 1 の C S 回路の積分器 (3) と前記第 2 の C S 回路の積分器 (3) は 2 入力を持つ単一差動積分器を形成して、前記アナログ信号の差動電流を積分し、前記第 1 の信号出力と第 2 の信号出力で差動サンプルを生成することを特徴とする、差動電荷サンプリング (C S) 回路。

## 【請求項 6】

請求項 1 乃至 3 のいずれか 1 項に記載の多数の C S 回路を備える並列 C S 回路であって、

20

全ての第 1 の信号入力をまとめて前記並列 C S 回路の第 1 のアナログ信号入力として接続し、前記 C S 回路の全ての制御信号発生器を共通の制御信号発生器に置き換え、マルチプレクサは前記 C S 回路の信号出力にそれぞれ接続する前記数の信号入力と、前記共通の制御信号発生器の多重化信号出力に接続する制御入力と、信号出力とを有して、前記 C S 回路の出力が保持段階にあるとき前記 C S 回路の出力を多重化して前記並列 C S 回路の出力に与え、ここで前記並列 C S 回路はサンプリング速度を高め、2 連続サンプリング点の間の時間間隔を短くし、前記並列 C S 回路は单一端回路であることを特徴とする、並列 C S 回路。

30

## 【請求項 7】

請求項 4 または 5 記載の多数の C S 回路を備える並列 C S 回路であって、

全ての第 1 の信号入力をまとめて前記並列 C S 回路の第 1 のアナログ信号入力として接続して差動アナログ信号の第 1 の端を受け、全ての第 2 の信号入力をまとめて前記並列 C S 回路の第 2 のアナログ信号入力として接続して前記差動アナログ信号の第 2 の端を受け、前記 C S 回路の全ての制御信号発生器を共通の制御信号発生器に置き換え、マルチプレクサは前記 C S 回路の信号出力対にそれぞれ接続する前記数の信号入力対と、前記共通の制御信号発生器の多重化信号出力に接続する制御入力と、信号出力対とを有して、前記 C S 回路の出力対が保持段階にあるとき前記 C S 回路の出力対を多重化して前記並列 C S 回路の出力対に与え、ここで前記並列 C S 回路はサンプリング速度を高め、2 連続サンプリング点の間の時間間隔を短くし、前記並列 C S 回路は差動回路であることを特徴とする、並列 C S 回路。

40

## 【請求項 8】

請求項 6 または 7 記載の並列 C S 回路であって、

前記制御信号発生器は、クロック入力と、前記数のサンプリング信号出力と、前記数のリセット信号出力と、前記数の多重化信号出力とを有して、前記 C S 回路のスイッチの制御入力に接続するサンプリング信号出力で前記数のサンプリング信号をそれぞれ生成し、前記 C S 回路の積分器の制御入力に接続する前記リセット信号出力で前記数のリセット信号をそれぞれ生成し、前記多重化信号出力で前記数の多重化信号を生成し、前記リセット信号と前記サンプリング信号と前記多重化信号を均一に時間的に交互配置することを特徴

50

とする、並列 C S 回路。

【請求項 9】

請求項 1 乃至 3 , 6 のいずれか 1 項に記載の C S 回路であって、

アナログ信号を受ける信号入力と、 $(2 f_i t) / (\sin(2 f_i t))$  に比例する周波数応答を持つ信号出力とを有するアナログ周波数補償回路を備え、ここで前記信号出力は前記 C S の信号入力に接続することを特徴とする、 C S 回路。

【請求項 10】

請求項 4 , 5 , 7 のいずれか 1 項に記載の C S 回路であって、

アナログ信号を受ける信号入力対と、 $(2 f_i t) / (\sin(2 f_i t))$  に比例する周波数応答を持つ信号出力対とを有するアナログ周波数補償回路を備え、ここで前記信号出力対は前記 C S の第 1 の信号入力と第 2 の信号入力に接続することを特徴とする、 C S 回路。

10

【請求項 11】

請求項 1 乃至 3 , 6 のいずれか 1 項に記載の C S 回路であって、

$(2 f_i t) / (\sin(2 f_i t))$  に比例する周波数応答を持ち、前記 C S 回路の信号出力をデジタル信号に変換する A / D 変換器の後に接続するデジタル周波数補償回路を特徴とする、 C S 回路。

【請求項 12】

請求項 4 , 5 , 7 のいずれか 1 項に記載の C S 回路であって、

$(2 f_i t) / (\sin(2 f_i t))$  に比例する周波数応答を持ち、前記 C S 回路の信号出力対をデジタル信号に変換する A / D 変換器の後に接続するデジタル周波数補償回路を特徴とする、 C S 回路。

20

【請求項 13】

請求項 5 に記載の第 1 および第 2 の B P C S 回路 ( 3 9 , 4 2 ) を備える 2 ステップ B P C S 回路であって、

前記第 1 の B P C S 回路 ( 3 9 ) 内の差動アナログ信号の第 1 の端と第 2 の端をそれぞれ受けて、前記第 1 の B P C S 回路の信号出力または出力対で信号サンプルを第 1 のサンプリング速度で生成する第 1 の信号入力と第 2 の信号入力と、

前記第 1 の B P C S 回路 ( 3 9 ) からの信号を時間的に対称に前記第 1 のサンプリング速度に等しいクロック信号の周波数でその信号出力または出力対でチョッピングするチョッピング回路 ( 4 0 ) と、

30

前記チョッピング回路からの信号を差動的にその信号出力対で増幅する差動出力増幅器 ( 4 1 ) と、

前記第 2 の B P C S の第 1 の信号入力と第 2 の信号入力は前記増幅器 ( 4 1 ) の信号出力対に接続して、信号サンプルを第 2 のサンプリング速度で信号出力または出力対で生成する、

ことを特徴とする、 2 ステップ B P C S 回路。

【請求項 14】

請求項 1 3 記載の 2 ステップ B P C S 回路であって、

前記第 1 の B P C S 回路 ( 3 9 ) が用いる第 1 のクロック信号を受けるクロック入力を有し、また前記チョッピング回路のクロック入力と前記第 2 の B P C S 回路のクロック入力に同時に与える第 2 のクロック信号を生成するクロック信号発生器 ( 4 3 ) を特徴とする、 2 ステップ B P C S 回路。

40

【請求項 15】

請求項 1 乃至 1 4 のいずれか 1 項に記載の前記 B P C S 回路のいずれかの種類におけるビルディング・ブロックの構成であって、

ドレンを信号入力とし、ゲートを制御入力とし、ソースを信号出力とする、 n - M O S トランジスタを備える前記スイッチの n - M O S 構成と、

ドレンを互いに接続して信号入力とし、ソースを互いに接続して信号出力とし、前記 n - M O S トランジスタのゲートを制御入力とする、 n - M O S トランジスタおよび p - M

OSトランジスタと、入力を前記n-MOSトランジスタのゲートに接続し、出力を前記p-MOSトランジスタのゲートに接続するインバータと、を備える前記スイッチのCMOS構成と、

ドレンを信号入力とし、ゲートを制御入力とし、ソースを信号出力とするn-MOSトランジスタを備える前記W&S要素の構成と、

第1の端を信号入力とし、第2の端を接地するコンデンサと、必要に応じて前記信号入力と前記コンデンサの第1の端の間に挿入するオプションの抵抗器と、ドレンとソースを前記コンデンサの第1の端と第2の端にそれぞれ接続し、ゲートを制御入力とするn-MOSトランジスタと、を備える前記積分器の受動構成と、

信号入力と信号出力をそれぞれ前記差動積分器の第1の信号入力と第1の信号出力とする前記積分器の第1の受動構成と、信号入力と信号出力をそれぞれ前記差動積分器の第2の信号入力と第2の信号出力とする前記積分器の第2の受動構成と、を備える前記差動積分器の受動構成と、

正入力を接地し、負入力を前記積分器の信号入力とし、出力を前記積分器の信号出力とする差動入力单一出力増幅器と、第1の端を前記差動入力单一出力増幅器の負入力に接続するコンデンサと、入力を前記積分器の制御入力とするインバータと、信号入力を前記差動入力单一出力増幅器の負入力に接続し、制御入力を前記積分器の制御入力に接続し、信号出力を前記差動入力单一出力増幅器の出力に接続する前記スイッチの第1のn-MOSまたはCMOS構成と、信号入力を前記コンデンサの第2の端に接続し、制御入力を前記積分器の制御入力に接続し、信号出力を接地する前記スイッチの第2のn-MOSまたはCMOS構成と、信号入力を前記コンデンサの第2の端に接続し、制御入力を前記インバータの出力に接続し、信号出力を前記差動入力单一出力増幅器の出力に接続する前記スイッチの第3のn-MOSまたはCMOS構成と、必要に応じて前記積分器の信号入力と前記差動入力单一出力増幅器の負入力の間に挿入するオプションの抵抗器と、を備える前記積分器の能動構成と、

負入力と、正入力と、正出力と、負出力を前記差動積分器の第1の信号入力と、第2の信号入力と、第1の信号出力と、第2の信号出力とする差動入力差動出力増幅器と、第1の端を前記差動入力差動出力増幅器の負入力に接続する第1のコンデンサと、第1の端を前記差動入力差動出力増幅器の正入力に接続する第2のコンデンサと、入力を前記差動積分器の制御入力とするインバータと、信号入力を前記差動入力差動出力増幅器の負入力に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を前記差動入力差動出力増幅器の正出力に接続する、前記スイッチの第1のn-MOS構成またはCMOS構成と、信号入力を前記第1のコンデンサの第2の端に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を接地する前記スイッチの第2のn-MOS構成またはCMOS構成と、信号入力を前記第1のコンデンサの第2の端に接続し、制御入力を前記インバータの出力に接続し、信号出力を前記差動入力差動出力増幅器の正出力に接続する前記スイッチの第3のn-MOS構成またはCMOS構成と、信号入力を前記差動入力差動出力増幅器の正入力に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を前記差動入力差動出力増幅器の負入力に接続する前記スイッチの第4のn-MOS構成またはCMOS構成と、信号入力を前記第2のコンデンサの第2の端に接続し、制御入力を前記差動積分器の制御入力に接続し、信号出力を接地する前記スイッチの第5のn-MOS構成またはCMOS構成と、信号入力を前記第2のコンデンサの第2の端に接続し、制御入力を前記インバータの出力に接続し、信号出力を前記差動入力差動出力増幅器の負出力に接続する前記スイッチの第6のn-MOS構成またはCMOS構成と、必要に応じて前記差動積分器の第1の信号入力と前記差動入力差動出力増幅器の負入力の間に挿入する第1のオプションの抵抗器と、必要に応じて前記差動積分器の第2の信号入力と前記差動入力差動出力増幅器の正入力の間に挿入する第2のオプションの抵抗器と、を備える前記差動積分器の能動構成と、

を特徴とするビルディング・ブロックの構成。

【請求項16】

10

20

30

40

50

請求項 1 3 または 1 4 記載の第 1 および第 2 の B P C S 回路を備えるフロントエンド・サンプリング無線受信装置であって、

前記クロック周波数の 2 倍以下の帯域幅を持ち、無線信号を受信して濾波する低域フィルタ (45) と、

差動的に増幅された無線信号を前記濾波された信号から生成する低雑音増幅器 (46) と、

I クロック信号をその信号出力に生成するローカル発振器 (49) と、

信号入力を前記ローカル発振器 (49) に接続して、前記 I クロック信号と同じ振幅で / 2 位相シフトした Q クロック信号をその信号出力に生成する / 2 移相器 (48) と、

を備え、

前記低雑音増幅器 (46) の信号出力対の 2 端を前記第 1 の B P C S 回路 (47A) と第 2 の B P C S 回路 (47B) にそれぞれ接続し、前記 I クロック信号出力を前記第 1 の B P C S 回路 (47A) のクロック入力に接続し、前記 Q クロック信号出力を前記第 2 の B P C S 回路 (47B) のクロック入力に接続して、前記無線信号のベースバンド I サンプルを前記第 1 の B P C S 回路 (47A) の信号出力または出力対で生成し、前記無線信号のベースバンド Q サンプルを前記第 2 の B P C S 回路 (47B) の信号出力または出力対で生成する、

ことを特徴とする、フロントエンド・サンプリング無線受信装置。

#### 【請求項 17】

請求項 1 6 記載のフロントエンド・サンプリング無線受信装置であって、

前記第 1 および第 2 の B P C S 回路 (47A, 47B) の前記ローカル発振器 (49) と前記移相器 (48) と前記クロック発生器を組み合わせて、差動 I クロック信号および Q クロック信号を一層効果的にまた正確に生成し、

前記ベースバンド I サンプルおよび Q サンプルを、2 個の別個のアナログ・デジタル変換器によりまたは単一の多重化アナログ・デジタル変換器によりデジタル信号に変換し、

前記デジタル信号をデジタル信号処理 (D S P) ユニットで処理し、

前記フロントエンド・サンプリング無線受信装置は非常に簡単化されたアナログ部を有する優れたアナログ無線受信装置であり、また D S P の能力を高度に利用する、ことを特徴とする、フロントエンド・サンプリング無線受信装置。

#### 【請求項 18】

電荷サンプリングの方法であって、

サンプリング段階でアナログ入力信号を積分し、すなわち、アナログ入力信号の電流を積分して積分電荷を生成し、

前記サンプリング段階の終わりに前記積分電荷の比例電圧または電流サンプルを生成し、

ここで、前記サンプリング段階が時刻  $t_1$  から時刻  $t_2$  までの場合、前記サンプルは時刻  $t_s = (t_1 + t_2) / 2$  での前記アナログ信号の瞬時値を表し、一定部分と周波数依存部分  $(\sin(2\pi f_i t)) / (2\pi f_i t)$  から成る係数だけ前記瞬時値とは異なる、ただし、 $f_i$  は前記アナログ信号の第  $i$  成分の周波数であり、 $t = (t_2 - t_1) / 2$  、すなわち、前記サンプリング段階の幅の半分である、ステップを特徴とする、電荷サンプリングの方法。

#### 【請求項 19】

請求項 1 8 記載の電荷サンプリングの方法であって、

前記アナログ入力信号は差動アナログ信号であり、前記積分電荷の前記比例電圧または電流サンプルは差動信号であることを特徴とする、電荷サンプリングの方法。

#### 【発明の詳細な説明】

##### 【0001】

(発明の分野)

10

20

30

40

50

現在、アナログ・ディジタル（A / D）変換には電圧サンプリングが用いられている。電圧サンプルには、信号源とコンデンサとの間にサンプリング・スイッチが設けられている。2つのサンプリング時刻の間、コンデンサ電圧は信号電圧を正確に追跡する。サンプリング時刻にスイッチを切ってコンデンサ電圧を保持する。信号の周波数が増加すると、この2つのプロセスは非常に困難になる。所定の精度では、熱雑音とスイッチング雑音によって最小許容容量が規定され、追跡速度によって最大許容容量またはスイッチ抵抗が規定される。この最大が最小より小さいと不可能になる。また、クロックのジターと有限のターンオフ速度（非ゼロのサンプリング隙間）のためにサンプリングのタイミングが不正確になる。実際のところ、電圧サンプリング回路の帯域幅は信号の帯域幅よりかなり大きくなければならない。このため、高周波無線信号を直接サンプリングすることが非常に困難である。サブサンプリングを行えばサンプリング速度は減少するが、サンプリング回路の帯域幅は減少しないし、クロックのジターを小さくしましたサンプリング隙間を小さくしたいという要求も減らない。10

#### 【0002】

##### （発明の概要）

本発明の目的は、上に述べた問題を解決するための改善されたサンプリング回路とアナログ信号のサンプリング方法を提供することである。

前記目的を達成する本発明の電荷サンプリング（C S）回路は制御信号発生器を備え、サンプリング段階で制御信号発生器からのサンプリング信号に応じて電荷サンプリング回路へのアナログ入力信号を制御して積分器で積分する。すなわち、アナログ入力信号の電流を積分して積分電荷を生成して、サンプリング段階の終わりに比例電圧または電流サンプルを信号出力に生成する。20

#### 【0003】

本発明の更に特定の目的は、帯域通過サンプリングのための方法とサンプリング回路を提供することである。

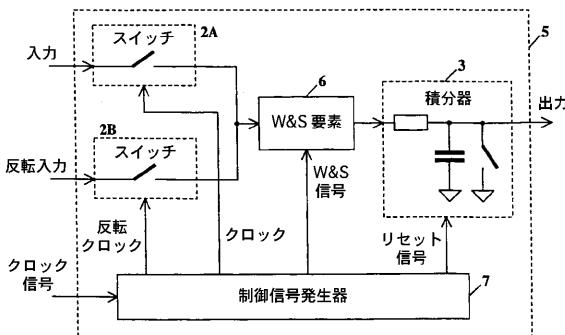

この目的を達成する帯域通過サンプリング（B P C S）回路は制御信号発生器を備え、重みおよびサンプリング（weighting-and-sampling）（W & S）段階で制御信号発生器からのW & S信号に応じて、差動アナログ信号の第1の端と第2の端を制御してW & S要素で重みを付ける。この場合、前記W & S信号がW & S段階にあるときだけアナログ信号の電流は前記W & S要素を通過し、前記制御信号発生器はW & S段階でW & S要素の出力信号を制御して積分器で積分する。すなわち、W & S要素の出力信号の電流を積分して積分電荷を生成して、W & S段階の終わりに比例電圧または電流サンプルを信号出力に生成する。30

#### 【0004】

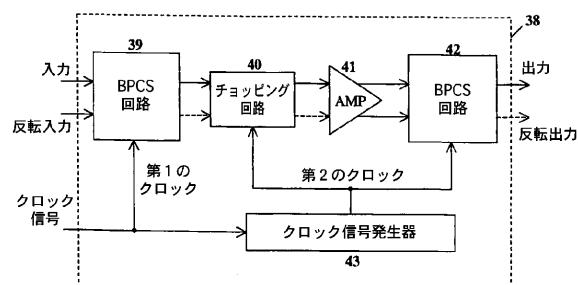

本発明の別の特定の目的は、2ステップB P C S回路を提供することである。これを達成する本発明の2ステップB P C S回路は、第1のサンプリング速度で信号サンプルを生成する本発明の第1のB P C S回路と、第1のサンプリング速度に等しいクロック信号の周波数で時間的に対称に第1のB P C S回路からの信号をその信号出力または出力対でチョッピングするチョッピング回路と、チョッピング回路からの信号を差動的に増幅する差動出力増幅器とを備える。ここで、前記第2のB P C Sの第1の信号入力と第2の信号入力は前記増幅器（41）の信号出力対に接続して、信号サンプルを第2のサンプリング速度で信号出力または出力対に生成する。40

#### 【0005】

本発明の更に別の特定の目的は、フロントエンド・サンプリング無線受信機を提供することである。これを達成する本発明のフロントエンド・サンプリング無線受信機は、クロック周波数の2倍以下の帯域幅で無線信号を受信して濾波する低域フィルタと、濾波された信号から差動的に増幅された無線信号を生成する低雑音増幅器と、Iクロック信号をその信号出力に生成するローカル発振器と、ローカル発振器に接続する信号入力を有してIクロック信号に対して振幅は同じで位相は / 2シフトしたQクロック信号をその信号出力に生成する / 2位相シフタとを備える。ここで、前記低雑音増幅器の信号出力対の2端50

を第1のB P C S回路と第2のB P C S回路にそれぞれ接続し、前記エクロック信号出力を前記第1のB P C S回路のクロック入力に接続し、Qクロック信号出力を第2のB P C S回路のクロック入力に接続して、無線信号のベースバンドIサンプルを第1のB P C S回路の信号出力または出力対に生成し、無線信号のベースバンドQサンプルを前記第2のB P C S回路の信号出力または出力対に生成する。

【0006】

本発明に係る電荷サンプリング回路の利点は、電荷サンプリング回路の帯域幅を信号の帯域幅より非常に大きくする必要がないことである。別の重要な背景は、無線信号では、搬送波周波数がいかに高くても、信号帯域幅（ベースバンド）はDCと搬送波周波数の間の全帯域のごく小部分である、ということである。したがって全帯域を変換する必要がなく、信号を持つ帯域だけでよい。

10

【0007】

所定の精度において、C S回路またはB P C S回路でサンプリングする信号の周波数は電圧サンプリング回路の周波数より幾分高いかまたは非常に高い。

C S回路またはB P C S回路に用いるサンプリング・コンデンサは電圧サンプリング回路に用いるものより幾分大きいかまたは非常に大きいので、雑音が低く、クロックと充電のフィードスルーが低いという利点を与える。

各B P C S回路は同時にフィルタとミクサとサンプラなので、無線受信機は非常に簡単化される。

【0008】

20

B P C S回路は無線周波数帯域で直接動作するので、フロントエンド・サンプリングおよびA / D変換を持つ高度にデジタル化された無線受信機が可能になる。

B P C S回路の中心周波数も帯域幅も容易にプログラムすることができる。帯域幅は必要なだけ狭くすることができる。これは無制限のQ値を有することに等しい。

C SおよびB P C S回路は簡単であり、C M O Sまたはその他のプロセスで容易に実現することができる。

【0009】

この方法は、簡単で且つ高度にデジタル化された構造を必要とするシステム・オン・チップにとって非常に有用である。

本明細書で用いる「備える」という用語は、機能、全体（integers）、ステップ、構成要素が存在することを述べるものであり、1つ以上の他の機能、全体、ステップ、構成要素またはこれらのグループの存在または追加を妨げるものではないことを強調したい。

30

【0010】

（図面の詳細な説明）

本発明は、所定の時間窓内でその電流を積分することにより信号をサンプリングする電荷サンプリング（C S）回路または帯域通過電荷サンプリング（B P C S）回路であり、生成される電荷は窓の中心時刻での信号のサンプルを表す。

【0011】

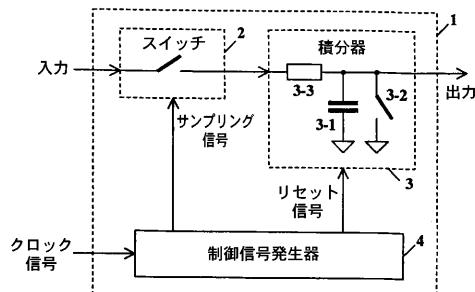

図1Aは、本発明に係る電荷サンプリング（C S）回路1の第1の実施の形態を示す。これは、サンプリング・スイッチ2と、積分器3と、制御信号発生器4を備える。スイッチ2は、信号入力と、信号出力と、制御入力とを有する。アナログ信号がスイッチの信号入力に入る。これは電荷サンプリング回路1の信号入力であり、サンプリング信号は制御信号発生器4から制御入力に与えられる。サンプリング信号がサンプリング段階にあるときだけスイッチが導通する（すなわち、スイッチの信号入力が信号出力に接続する）。積分器3は、信号入力と、信号出力と、制御入力とを有する。スイッチ2の信号出力は積分器3の信号入力に与えられ、制御信号発生器4からのリセット信号は積分器3の制御入力に与えられる。サンプリング段階でC S回路1へのアナログ入力信号の電流を積分し、サンプリング段階の終わりに、積分電荷は比例電圧または電流サンプルをC S回路の信号出力に生成する。リセット信号が始まるリセット段階までこのサンプルは保持され、その間の時間間隔が保持段階である。これらの段階を繰り返すとサンプルのシーケンスが生成され

40

50

、この信号出力は前記 C S 回路の信号出力である。前に述べたように、制御信号発生器 4 は、 C S 回路のクロック入力であるクロック入力と、スイッチ 2 の制御入力に接続するサンプリング信号出力と、積分器 3 の制御入力に接続するリセット信号出力とを有する。

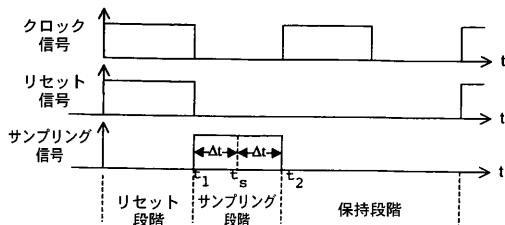

#### 【 0 0 1 2 】

この実施の形態では、積分器 3 は、コンデンサ 3 - 1 と、リセット・スイッチ 3 - 2 と、オプションの抵抗器 3 - 3 を備える。しかし他の実施の形態では、積分器 3 は異なる構成を有してよい。アナログ信号はサンプリング・スイッチ 2 の入力に与えられる。上に述べたように、電荷サンプリング・プロセスはリセットとサンプリング ( $t_1$  から  $t_2$ ) と保持の 3 連続段階を含む。時間  $t_1$  から  $t_2$  はサンプリング窓と定義される。図 1 B はその動作波形を示す。リセット段階でリセット・スイッチ 3 - 2 だけが導通してコンデンサ 3 - 1 をリセットする。サンプリング段階でサンプリング・スイッチ 2 だけが導通して信号電流をコンデンサ 3 - 1 に積分する。時定数は、信号が電圧源から来るとき（これが普通）に直線充電を行うのに十分の大きさを有する。スイッチ 2 の導通抵抗が非常に小さい場合はオプションの抵抗 3 - 3 を追加してよい。保持段階で両スイッチは切断状態であり、更に用いるために積分器 3 の出力電圧を保持する。1 対の相互接続された C S 回路で差動 C S 回路を形成すると、差動入力信号を用いてまた制御信号発生器 4 を共用することにより差動出力を与えて、コモン・モードの影響を打ち消す。C S 回路または回路対を並列に用いると、サンプリング信号とリセット信号を時間的に交互配置することによりサンプリング速度を高め、また 2 つのサンプリング点の間の時間間隔をサンプリング窓より小さくすることができる。信号電流は  $I(t) = I_i \sin(\omega_i t + \phi_i)$  、  $i = 1, 2, \dots$  10, m、で表すことができる。全積分電荷は  $Q = Q_i$  、ただし、  $Q_i = (I_i / \omega_i) (\cos(\omega_i t_1 + \phi_i) - \cos(\omega_i t_2 + \phi_i))$  である。  $t_s$  がサンプリング窓の中心時刻で、  $2\pi t = (t_2 - t_1)$  が窓の幅の場合は  $Q_1 = (2 \sin(\omega_i t / \omega_i) I_i \sin(\omega_i t_s + \phi_i)) = 2\pi t (\sin(\omega_i t) / (\omega_i t)) I_i \sin(\omega_i t_s + \phi_i)$  である。

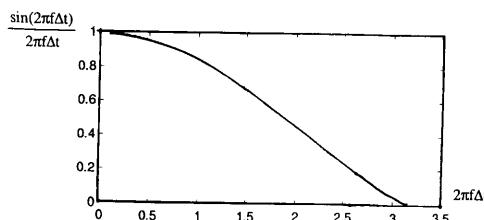

#### 【 0 0 1 3 】

$t_s$  での第  $i$  成分の瞬時値  $I_i(t_s) = I_i \sin(\omega_i t_s + \phi_i)$  と比べると、差は  $k_i = 2\pi t (\sin(\omega_i t / \omega_i) - \sin(\omega_i t_s / \omega_i))$  であり、サンプリング係数は周波数  $\omega_i$  と  $t$  に依存する。この係数を用いると、時刻  $t_s$  で第  $i$  周波数成分を正確にサンプリングすることができる。全ての周波数成分を  $t_s$  でサンプリングするので、コンデンサ上の全電荷は当然  $t_s$  での信号サンプルを表す。すなわち、  $t_s$  は等価サンプリング時点である。図 1 C 30 に示すように、C S 回路の周波数応答は関数  $\sin(\omega_i t / \omega_i - \omega_i t_s)$  に依存する。解像度に関係なく、その 3 dB 帯域幅は  $f_{3dB} = 1.4 / (2\pi t)$  (すなわち、450 ps のサンプリング窓で 1 GHz) である。しかし電圧サンプリングでは、1 GHz で 8 ビットの解像度を得るためにサンプリング隙間は 1 ps より小さくなければならない。関数  $\sin(\omega_i t / \omega_i - \omega_i t_s)$  は正確に定義されるので周波数の補償は可能である。1 つの方法は、サンプリングの前に  $(\omega_i t) / \sin(\omega_i t)$  の周波数応答を持つネットワークにアナログ信号を通すことである。別の方法は、A / D 変換の後にデジタル信号処理プロセッサ (DSP) を用いて周波数応答を補償することである。

#### 【 0 0 1 4 】

また、帯域通過電荷サンプリング (B P C S) 回路は 2 個のスイッチと、重みおよびサンプリング (W & S) 要素と、積分器と、制御信号発生器とを備える。制御信号発生器は、クロックと、反転クロックと、W & S 信号と、リセット信号とを生成する。差動信号の 2 端を 2 個のスイッチ入力にそれぞれ与える。クロックと反転クロックによりそれぞれ制御される 2 個のスイッチは交互に導通する。両スイッチの出力を W & S 要素の入力に与え、W & S 要素の出力を積分器の入力に与える。これはリセットとサンプリングと保持の 3 連続段階で動作する。リセット段階ではリセット信号で積分器をリセットする。各サンプリング段階は  $n$  クロック・サイクルを含み、その間に信号電流を W & S 要素で重みを付けて積分器で積分する。保持段階で積分器の出力を保持する。

#### 【 0 0 1 5 】

10

20

30

40

50

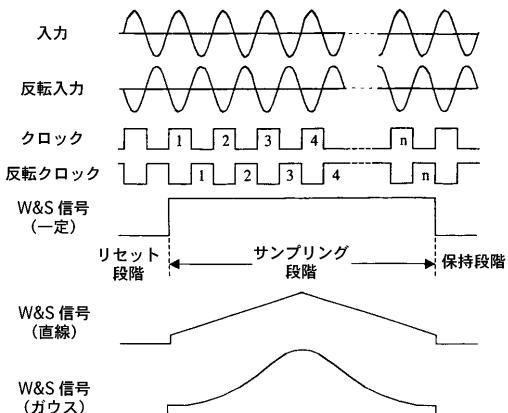

帯域通過電荷サンプリング (B P C S) 回路 5 を図 2 A に示す。これは 2 個のスイッチ 2 A および 2 B と、重みおよびサンプリング (W & S) 要素 6 と、積分器 3 と、制御信号発生器 7 とを備える。制御信号発生器 7 は、クロックと、反転クロックと、W & S 信号と、リセット信号とを生成する。差動アナログ信号の 2 端をスイッチ 2 A および 2 B の入力にそれぞれ与える。スイッチ 2 A および 2 B はクロックと反転クロックによりそれぞれ制御されて交互に導通する。スイッチ 2 A および 2 B の出力を共に W & S 要素 6 の入力に与える。W & S 要素 6 を通る電流は W & S 信号で制御する。W & S 要素 6 の出力を積分器 3 の入力に与える。各 B P C S プロセス毎に、リセットとサンプリングと保持の 3 連続段階を行う。図 2 B は動作波形を示す。リセット段階で積分器をリセットする。各サンプリング段階は  $n$  クロック・サイクルを含み、サンプリング窓を形成する。W & S 要素を通る信号電流は、サンプリング窓の外ではゼロであり、サンプリング窓の中では重み関数（一定、直線、ガウス、またはその他の関数）に従ってこれに重みを付ける。重み関数は W & S 要素 6 と W & S 信号の組み合わせに依存する。図 2 B に示す 3 つの W & S 信号は 3 つの重み関数（一定、直線、ガウス）に対応し、特に W & S 要素で用いて電流を W & S 信号で線形制御する。保持段階で、更に用いるために積分器 3 の出力電圧を保持する。

10

## 【0016】

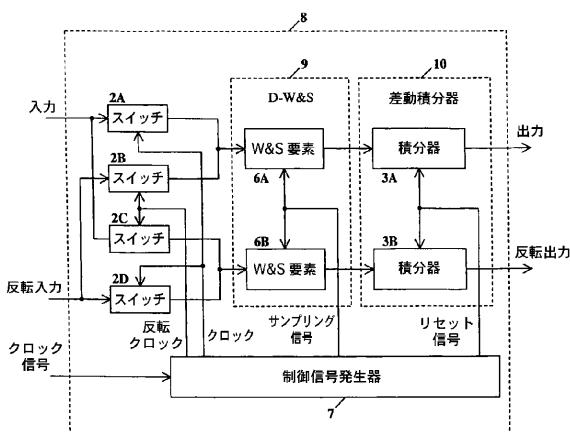

差動 B P C S 回路 8 を図 3 に示す。これは図のように接続される 4 個のスイッチ 2 A, 2 B, 2 C, 2 D と、差動 W & S (D - W & S) 要素 9 と、差動積分器 10 と、制御信号発生器 7 とを備える。図に示す型の D - W & S 要素 9 は 2 個の並列 W & S 要素 6 A および 6 B を備え、また図に示す型の差動積分器は 2 個の並列積分器 3 A および 3 B を備える。D - W & S 要素 9 と差動積分器 10 は他の型でもよい。差動 B P C S 回路 8 は単一端の B P C S 回路 5 と同様に動作するが、異なる点は 2 つの出力を差動的に生成することである。差動 B P C S 回路 8 はコモン・モードの影響を効果的に打ち消し、より正確な結果を得ることができる。

20

## 【0017】

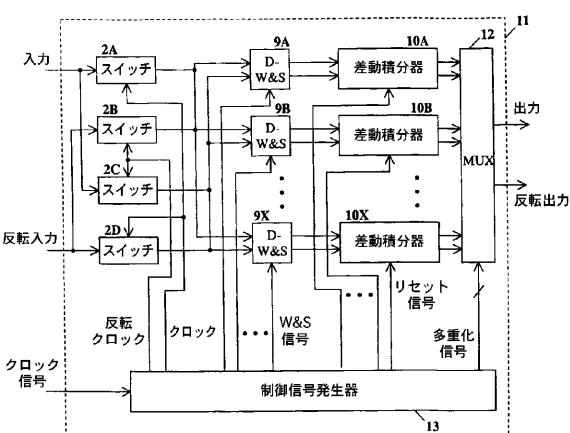

図 4 は並列差動 B P C S 回路 11 を示す。これは図のように接続される 4 個のスイッチ 2 A, 2 B, 2 C, 2 D と、多数の D - W & S 要素 9 A, 9 B, . . . , 9 X と、多数の差動積分器 10 A, 10 B, . . . , 10 X と、マルチプレクサ (MUX) 12 と、制御信号発生器 13 とを備える。D - W & S 要素と差動積分器の各対 9 A + 10 A, 9 B + 10 B, . . . , 9 X + 10 X はスイッチ 2 A, 2 B, 2 C, 2 D と共に差動 B P C S 回路 8 と同様に動作する。これらの対への W & S 信号とリセット信号は制御信号発生器 13 で生成して均一に時間的に交互配置する。MUX 12 は制御信号発生器 13 からの多重化信号により制御され、保持段階で差動積分器 10 A, 10 B, . . . , 10 X の出力を多重化して差動出力に与える。全体として、並列 B P C S 回路は一層高いサンプリング速度を与える、2 連続サンプリング点の間の時間間隔をサンプリング窓よりも小さくすることができる。スイッチ 2 C および 2 D を除き、また差動 W & S 要素と差動積分器を単一端のものに置き換えると、並列単一端 B P C S 回路になる。

30

## 【0018】

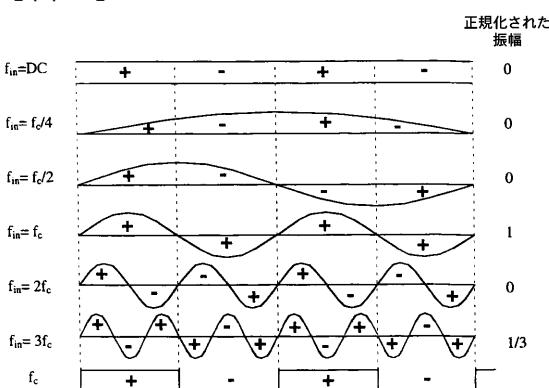

B P C S 回路の濾波機能を図 5 に示す。上から順に、周波数は  $D C$  から  $3 f_c$  まで増加する。ただし、 $f_c$  はクロック周波数である。負のクロック位相では同じ信号が逆に接続されることに注意していただきたい。図では信号の符号を変えてこれを表している。 $n$  クロック・サイクルの間積分して生成された電荷の正規化された振幅（すなわち、面積の和）を図 5 にそれぞれ示す。明らかであるが、 $f_c$  より非常に高いまたは低い周波数を持つ入力信号では、電荷はほとんど完全に互いに打ち消されるので出力はほぼゼロである。 $f_c / 4, f_c / 2, 2 f_c, . . .$  などの周波数の入力信号では、その位相に関わらず電荷は完全に打ち消される。 $f_c$  に近い周波数の入力信号では、電荷は部分的に打ち消される。 $f_{in} = f_c$  のときは、 $f_c$  と同相の場合は電荷は完全に加算され、 $f_c$  から  $/ 2$  の位相の場合（図 5 に示さず）は電荷は完全に打ち消される。信号の電荷を効果的に積分することができる帯域幅がある。この帯域幅の外では信号の電荷は完全にすなわち実質的に打ち消される。これは明らかに濾波機能である。これは、帯域幅の外の周波数の雑音も打ち消す

40

されることを意味する。

【0019】

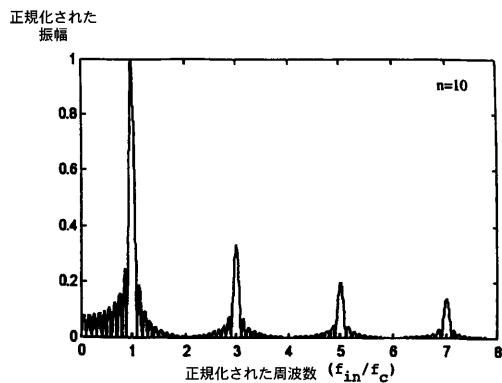

B P C S の理想的な周波数応答を図 6 A に示す。これはサンプリング窓の中の信号電流の数学的に正確な積分に対応する。図 6 A では、 $n = 10$  のとき一定重みと仮定する。これは、10 クロック・サイクルのサンプリング窓の中で電流の重みを一定に保つことを意味する。また図 6 A は  $f_{in} = 0$  から  $f_{in} = 8 f_c$  までの周波数応答を示す。ここで、y 軸は全周波数範囲内の最大出力振幅で正規化された種々の周波数の最大出力振幅であり、x 軸は  $f_c$  で正規化された入力周波数である。図から分かるように、 $f_{in} > 2 f_c$  の後は同じ周波数応答が繰り返されるが振幅は小さくなる。 $2(p-1)f_c \leq f_{in} \leq 2pf_c$  では、出力周波数  $f_{out}$  は  $|f_{in} - (2p-1)f_c|$  に等しい。ただし  $p$  は整数 (1) である。

10

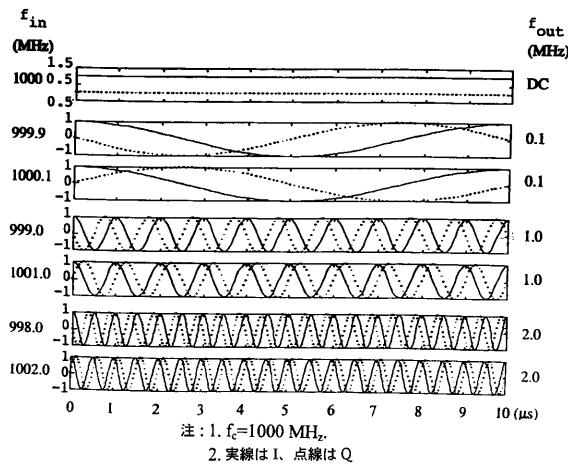

$f_{in} = (2p-1)f_c$  のとき出力は DC 電圧であり、その振幅は  $f_{in}$  と  $f_c$  の位相関係に依存する。所定の  $p$  では、 $(2p-1)f_c - f_{in1} = f_{in2} - (2p-1)f_c$  のとき、入力周波数  $f_{in1} (< (2p-1)f_c)$  と  $f_{in2} (> (2p-1)f_c)$  について同じ出力周波数が生成されるが、位相は異なる。図 6 B は、 $f_c = 1000 \text{ MHz}$  のとき種々の入力周波数での出力サンプル波形を I 相 (実線) と Q 相 (点線) について示す。これは、B P C S 回路が同時にフィルタとミクサとサンプラーであることを示す。

【0020】

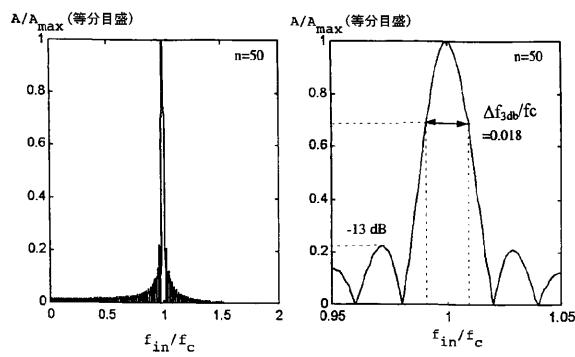

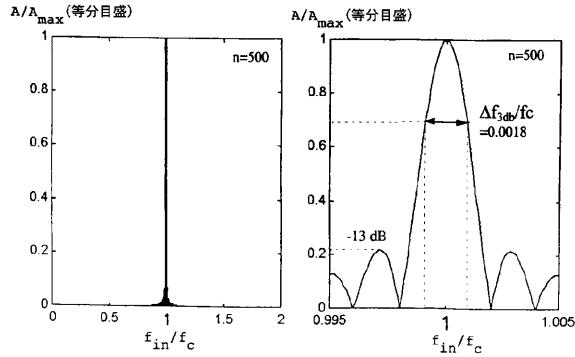

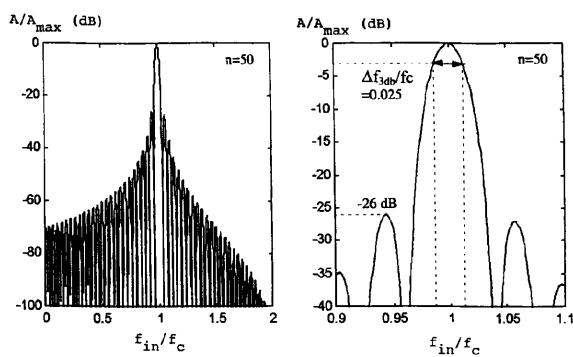

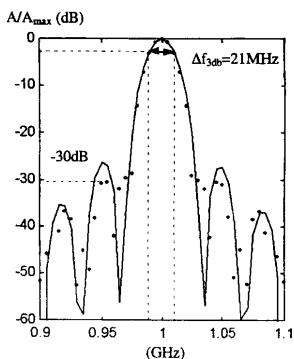

図 7 A と図 7 B は、 $n = 50$  と  $n = 500$  のときの一定重み B P C S 回路の理想的な周波数応答をそれぞれ示す。図 7 A は  $n = 50$  のとき、範囲  $0 < f_{in} < 2 f_c$  と、小さな範囲  $0.95 f_c < f_{in} < 1.05 f_c$  の周波数応答を示す。図 7 B は  $n = 500$  のとき、範囲  $0 < f_{in} < 2 f_c$  と、小さな範囲  $0.995 f_c < f_{in} < 1.005 f_c$  の周波数応答を示す。図から分かるように、 $N = 50$  のとき  $f_{3dB} = 0.018 f_c$  であり、 $N = 500$  のとき  $f_{3dB} = 0.0018 f_c$  である。すなわち、帯域幅は  $n$  に逆比例する。遠端の周波数成分の振幅は  $n$  の増加と共に減少するが、最大隣接ピークはどちらの場合もほとんど変わらず、-13 dB 付近である。

20

【0021】

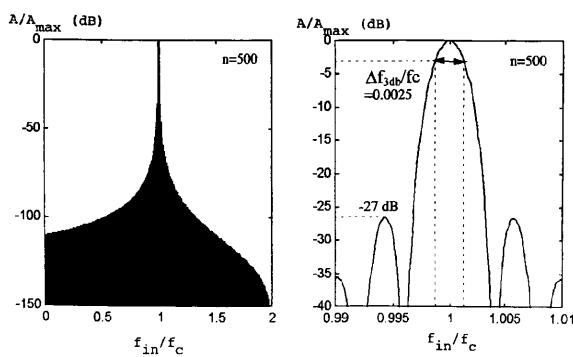

$n = 50$  と  $n = 500$  のときの直線重み B P C S 回路の理想的な周波数応答を図 8 A と図 8 B にそれぞれ示す。直線重みは、サンプリング段階で電流の重みが最初は直線的に増加し、次に、サンプリング窓の中心に対称に直線的に減少することを意味する。図 8 A は、 $n = 50$  のとき、範囲  $0 < f_{in} < 2 f_c$  と、小さな範囲  $0.9 f_c < f_{in} < 1.1 f_c$  の周波数応答を示す。図 8 B は  $n = 500$  のとき、範囲  $0 < f_{in} < 2 f_c$  と、小さな範囲  $0.99 f_c < f_{in} < 1.01 f_c$  の周波数応答を示す。図から分かるように、 $n = 50$  のとき  $f_{3dB} = 0.025 f_c$  であり、 $n = 500$  のとき  $f_{3dB} = 0.0025 f_c$  であって、一定重みの場合に比べてやや増加している。遠端の周波数成分の振幅は  $n$  の増加と共に急速に減少する。一定重みの場合に比べて、最大隣接ピークは -26 dB と -27 dB にそれぞれ減少する。

30

【0022】

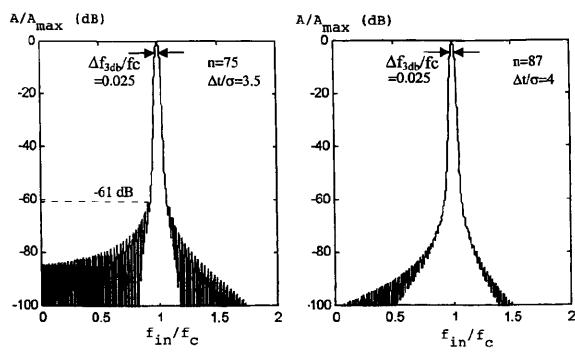

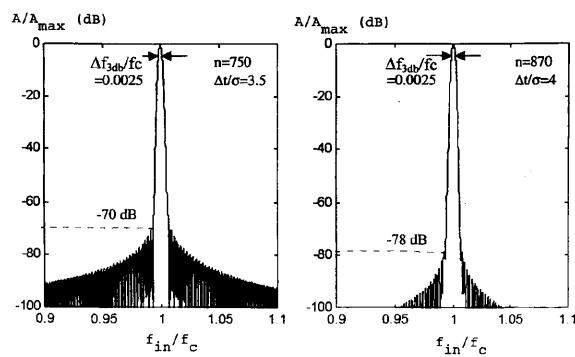

図 9 A と図 9 B は、ガウス重み B P C S 回路の理想的な周波数応答を示す。ガウス重みは、サンプリング段階で電流の重みが、サンプリング窓の中心に対称に所定の  $\sigma$  でガウス関数  $e \propto p (-t^2 / 2\sigma^2)$  に従って変化することを意味する。比  $t / \sigma$  は重みパラメータである。ただし、 $t$  はサンプリング窓の半分、 $\sigma$  は標準偏差である。図 9 A は、範囲  $0 < f_{in} < 2 f_c$  で、 $n = 75$  のとき  $t / \sigma = 3.5$  と、 $n = 87$  のとき  $t / \sigma = 4$  におけるそれぞれの周波数応答を示す。3 dB 帯域幅は共に  $0.025 f_c$  である。図 9 B は、範囲  $0.9 f_c < f_{in} < 1.1 f_c$  で、 $n = 750$  のとき  $t / \sigma = 3.5$  と、 $n = 870$  のとき  $t / \sigma = 4$  におけるそれぞれの周波数応答を示す。3 dB 帯域幅は共に  $0.0025 f_c$  である。遠端の周波数成分と隣接ピークの振幅はガウス重みと共に実質的に減少する。最大隣接ピークは -61 dB から -78 dB の範囲である。

40

【0023】

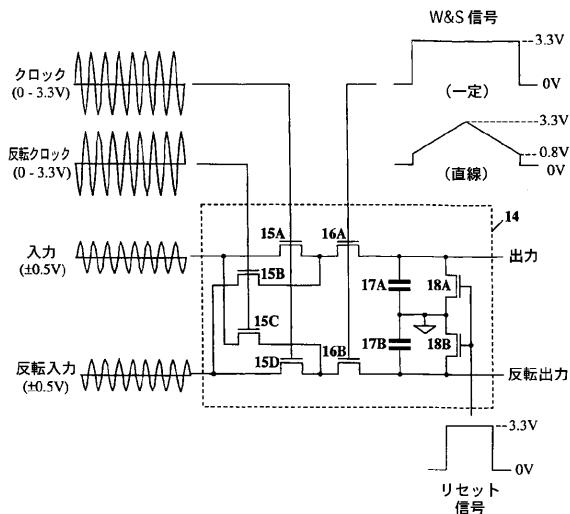

n - M O S トランジスタを用いた差動 B P C S 回路 8 のコアの実施の形態 14 を図 10 に示す。クロックされるスイッチは n - M O S トランジスタ 15 A, 15 B, 15 C, 15

50

Dである。W & S要素はn - MOSトランジスタ16Aと16Bである。リセット・スイッチはn - MOSトランジスタ18Aと18Bである。コンデンサはオンチップMOSコンデンサ17Aと17Bである。クロックは正弦波であるが、準方形波を用いてもよい。実施の形態14は全てのCMOSプロセスで動作する。しかし0.8 $\mu$ m CMOSプロセスのパラメータはHSPICEシミュレーションで用いられる。次の3つの実施の形態は、特定の成分値とW & S信号パラメータを持つ実施の形態14に基づいている。

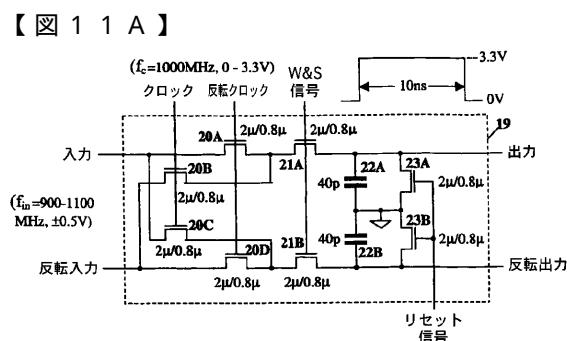

#### 【0024】

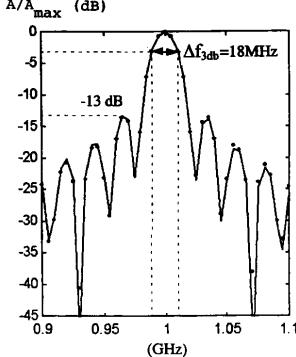

$n = 10$ のとき、 $f_c = 1000\text{MHz}$ における一定重みの実施の形態19を図11Aに示す。クロックされるスイッチはn - MOSトランジスタ20A, 20B, 20C, 20Dである。W & S要素はn - MOSトランジスタ21Aと21Bである。リセット・スイッチはn - MOSトランジスタ23Aと23Bである。これらは全て最小のサイズ、2 $\mu$ m / 0.8 $\mu$ m(幅 / 長さ)を有する。コンデンサはMOSコンデンサ22Aと22Bで、共に40pFである。一定重みW & S信号の幅は、 $n = 10$ に対応する10nsである。最大差動出力サンプル電圧は約100mVである。図11Bは、 $f_{in} = 900 - 1100\text{MHz}$ における理論的周波数応答を実線で、HSPICEシミュレーションによる周波数応答を点線で示す。シミュレーションによる周波数応答は理論的周波数応答にほぼ従う。両方とも、最大隣接ピークは-13dBで、 $f_{3dB} = 18\text{MHz}$ である。

#### 【0025】

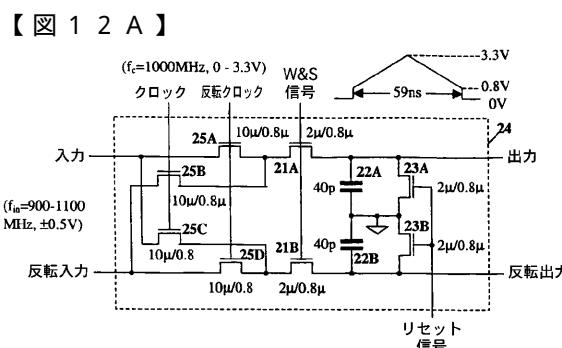

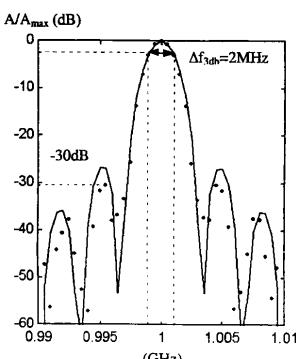

$n = 59$ のとき、 $f_c = 1000\text{MHz}$ における直線重みの実施の形態24を図12Aに示す。クロックされるスイッチはn - MOSトランジスタ25A, 25B, 25C, 25Dで、全て大きなサイズの10 $\mu$ m / 0.8 $\mu$ mを有する。これにより、信号電流はスイッチではなくW & S要素により左右される。W & S要素はn - MOSトランジスタ21Aと21Bで、2 $\mu$ m / 0.8 $\mu$ mである。リセット・スイッチはn - MOSトランジスタ23Aと23Bで、2 $\mu$ m / 0.8 $\mu$ mである。コンデンサはMOSコンデンサ22Aと22Bで、共に40pFである。直線重みW & S信号の幅は、 $n = 59$ に対応する59nsである。最大差動出力サンプル電圧は約100mVである。図12Bは、 $f_{in} = 900 - 1100\text{MHz}$ における理論的周波数応答を実線で、HSPICEシミュレーションによる周波数応答を点線で示す。シミュレーションによる周波数応答は基本的に理論的周波数応答に従う。両方とも、 $f_{3dB} = 21\text{MHz}$ である。しかし実施の形態24では、最大隣接ピークは-30dBで、理論的応答のピークより小さい。これは、n - MOSトランジスタ21Aまたは21Bのコンダクタンスが直線W & S信号と共に直線的に変わらないからである。実際の重み関数は直線とガウスの中間である。

#### 【0026】

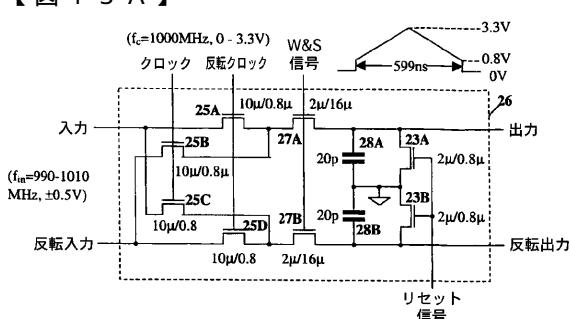

$n = 599$ のとき、 $f_c = 1000\text{MHz}$ における直線重みの実施の形態26を図13Aに示す。クロックされるスイッチはn - MOSトランジスタ25A, 25B, 25C, 25Dで、10 $\mu$ m / 0.8 $\mu$ mである。W & S要素はn - MOSトランジスタ27Aと27Bで、2 $\mu$ m / 16 $\mu$ mである。注意すべきであるが、27Aと27Bの長さを16 $\mu$ mの大きさにして、かかる長い充電時間(599ns)中、信号電流とコンデンサ電圧を制限する。リセット・スイッチはn - MOSトランジスタ23Aと23Bで、2 $\mu$ m / 0.8 $\mu$ mである。コンデンサはMOSコンデンサ28Aと28Bで、共に20pFである。直線重みW & S信号の幅は、 $n = 599$ に対応する599nsである。最大差動出力サンプル電圧は約100mVである。図13Bは、 $f_{in} = 990 - 1010\text{MHz}$ における理論的周波数応答を実線で、HSPICEシミュレーションによる周波数応答を点線で示す。シミュレーションによる周波数応答は基本的に理論的周波数応答に従う。両方とも、 $f_{3dB} = 2\text{MHz}$ である。上に述べたのと同じ理由から、実施の形態26の最大隣接ピークは-30dBであり、理論的応答のピークより小さい。

#### 【0027】

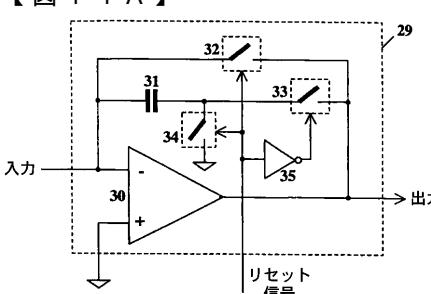

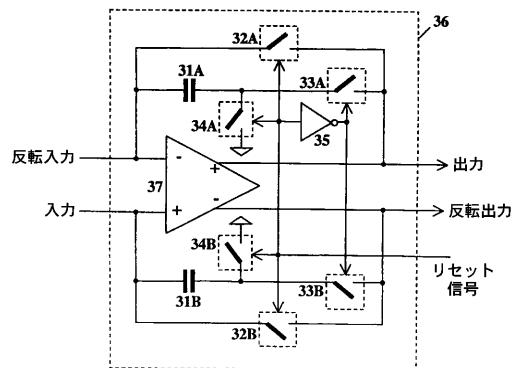

図14Aと図14Bは、出力の揺れと直線性を改善する能動積分器それぞれを示す。単一端の能動積分器29を図14Aに示す。これは、図のように接続された差動入力单一出力增幅器30と、インバータ35と、コンデンサ31と、スイッチ32, 33, 34とを備

10

20

30

40

50

える。能動積分器は信号入力を常に実質的に接地に保って、コンデンサ電圧が信号電流に与える影響を除去する。増幅器 30 の帯域幅は信号のベースバンドをカバーするだけではなく、搬送波をカバーする必要はない。これは実現可能である。インバータ 35 はリセット信号を入力として用いて遅れを持つ反転リセット信号を生成してスイッチ 33 を制御し、リセット信号はスイッチ 32 と 34 を制御する。リセット段階でスイッチ 32 と 34 は導通してスイッチ 33 は切れる。コンデンサ 31 の電圧はリセットされて増幅器 30 の入力オフセット電圧になる。サンプリング段階でスイッチ 32 と 34 は切れてスイッチ 33 は導通する。コンデンサ 31 は信号電流により充電される。同時に、増幅器 30 のオフセット電圧は打ち消される。差動能動積分器 36 を図 14 B に示す。これは差動入力差動出力増幅器 37 と、2 個のコンデンサ 31 A と 31 B と、インバータ 35 と、スイッチ 32 A, 32 B, 33 A, 33 B, 34 A, 34 B を備える。これは基本的に積分器 29 と同様に動作するが、異なる点は差動入力信号を用いて差動出力を生成することである。積分器 29 は図 1 A の積分器 3 の代わりに用いよく、積分器 36 は図 3 の積分器 10 の代わりに用いてよい。

#### 【0028】

図 15 は 2 ステップ B P C S 回路 38 を示す。これは第 1 の B P C S 回路 39 と、チョッピング回路 40 と、増幅器 41 と、第 2 の B P C S 回路 42 と、第 2 のクロックを生成するクロック信号発生器 43 を備える。第 1 の B P C S 回路 39 と第 2 の B P C S 回路 42 は B P C S 回路 5, 8, 11, 19, 24, 26 のどの型でもよい。第 1 の B P C S 回路 39 の 2 入力に差動アナログ信号の 2 端をそれぞれ与え、そのクロック入力に第 1 のクロックを与える。第 1 のサンプリング速度を持つ信号サンプルを第 1 の B P C S 回路 39 で生成してチョッピング回路 40 に与え、第 2 のクロックで制御してサンプルを時間的に対称にチョッピングする。チョッピング周波数と同じ新しい搬送波周波数を持つチョッピングされた信号をチョッピング回路 40 から増幅器 41 に与え、増幅された差動信号を第 2 の B P C S 回路 42 の 2 入力にそれぞれ与える。第 2 のクロックの制御により、第 2 の B P C S 回路 42 は第 2 のサンプリング速度を持つ最終サンプル出力を生成する。2 ステップ B P C S 回路 38 は性能のトレードオフに柔軟性を与える。2 ステップ B P C S 回路 38 に基づいて、更に多くのステップの B P C S 回路を構築することができる。

#### 【0029】

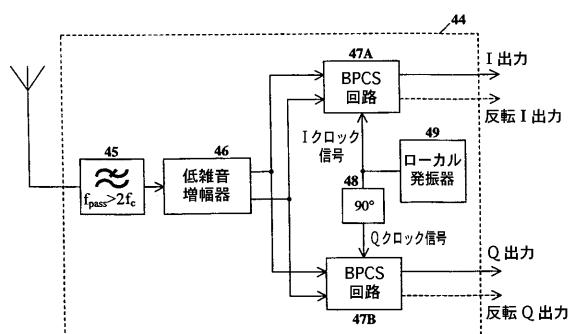

フロントエンド・サンプリング無線受信機構構造 44 を図 16 に示す。これは、 $f_{pass} < 2 f_c$  を持つ低域フィルタ 45 と、差動出力低雑音増幅器 (LNA) 46 と、2 つの B P C S 回路 47 A と 47 B と、90° 移相器 48 と、ローカル発振器 49 を備える。アンテナからの無線信号は低域フィルタ 45 の入力に入る。2  $f_c$  を超える周波数成分は大幅に減衰する。低域フィルタ 45 の出力を LNA 46 に与え、十分大きな振幅を持つ差動出力を生成する。差動出力を B P C S 回路 47 A と 47 B の入力に同時に与える。同時に、ローカル発振器 49 が生成する I クロック信号を B P C S 回路 47 A に与え、90° 移相器が I クロック信号から生成する Q クロック信号を B P C S 回路 47 B に与える。B P C S 回路 47 A と 47 B は I サンプルと Q サンプルをそれぞれ生成する。サンプル出力は、直ぐデジタル・データに変換してもよいし、更に処理してもよい。B P C S 回路 47 A と 47 B は B P C S 回路 5, 8, 11, 19, 24, 26 のどれでもよい。これらの回路内の積分器は受動積分器でもよいし能動積分器でもよい。無線受信機構構造 44 はフロントエンドに濾波機能と混合機能とサンプリング機能を同時に有するので、A / D 変換の性能要求が緩和され、アナログ・フィルタが不要になり、D S P の機能が高度に利用される。原理的に、任意の狭い帯域幅 (すなわち、任意の高い Q 値) が可能である。濾波機能の中心周波数は容易にプログラムすることができる。これは広い応用範囲を持つ優れた無線通信機構構造である。

#### 【0030】

C S および B P C S 回路に用いられるサンプリング・コンデンサは電圧サンプリング回路に用いられるものよりはるかに大きいので、雑音が少なく、充電とクロックのフィードスルーが低い。

10

20

30

40

50

B P C S 回路は同時に、無線周波数で動作するフィルタとミクサとサンプラーである。中心周波数と帯域幅と隣接選択性は、クロック周波数と数  $n$  と W & S 信号波形により設定することができる。これはフロントエンド・サンプリング無線受信機とシステム・オン・チップに特に有用である。

【0031】

理解されるように、この明細書では本発明の多くの特徴と機能を、本発明の機能の詳細と共に示したが、この開示は単なる例であって、特許請求の範囲に規定されている本発明の範囲内で詳細を変更することできる。

【図面の簡単な説明】

【図 1 A】 本発明に係る電荷サンプリング (C S) 回路の第 1 の実施の形態のブロック図である。 10

【図 1 B】 図 1 A の電荷サンプリング (C S) 回路の動作波形を示す。

【図 1 C】 図 1 A の電荷サンプリング (C S) 回路の周波数応答を示す。

【図 2 A】 本発明に係る帯域通過電荷サンプリング (B P C S) 回路の第 1 の実施の形態のブロック図である。

【図 2 B】 図 2 A の帯域通過電荷サンプリング (B P C S) 回路の動作波形を示す。

【図 3】 本発明に係る差動 B P C S 回路の第 1 の実施の形態のブロック図である。

【図 4】 本発明に係る並列差動 B P C S 回路の第 1 の実施の形態のブロック図である。

【図 5】 本発明に係る B P C S 回路の濾波機能を示す。

【図 6 A】  $n = 10$  のときの、本発明に係る一定重み B P C S 回路の理想的な周波数応答である。 20

【図 6 B】  $n = 10$  のときの、本発明に係る一定重み B P C S 回路の出力サンプル波形である。

【図 7 A】  $n = 50$  のときの、一定重み B P C S 回路の理想的な周波数応答である。

【図 7 B】  $n = 500$  のときの、一定重み B P C S 回路の理想的な周波数応答である。

【図 8 A】  $n = 50$  のときの、直線重み B P C S 回路の理想的な周波数応答である。

【図 8 B】  $n = 500$  のときの、直線重み B P C S 回路の理想的な周波数応答である。

【図 9 A】  $n = 75$  と  $n = 87$  のときの、ガウス重み B P C S 回路の理想的な周波数応答である。 30

【図 9 B】  $n = 750$  と  $n = 870$  のときの、ガウス重み B P C S 回路の理想的な周波数応答である。

【図 10】 図 3 の差動 B P C S 回路の、第 1 の実施の形態の回路図である。

【図 11 A】 1000 MHz において一定重みで  $n = 10$  のときの、図 10 に係る回路図を示す。

【図 11 B】 図 11 A の回路の生成された周波数応答を示す。

【図 12 A】 1000 MHz において直線重みで  $n = 59$  のときの、図 10 に係る回路図を示す。

【図 12 B】 図 12 A の回路の生成された周波数応答を示す。

【図 13 A】 1000 MHz において直線重みで  $n = 599$  のときの、図 10 に係る回路図を示す。 40

【図 13 B】 図 13 A の回路の生成された周波数応答を示す。

【図 14 A】 単一端の能動積分器の回路図である。

【図 14 B】 差動能動積分器の回路図である。

【図 15】 2 ステップ P B C S 回路のブロック図である。

【図 16】 フロントエンド・サンプリング無線受信機構造のブロック図である。

【図1A】

【図1B】

【図1C】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6 A】

【図6 B】

【図7 A】

【図7 B】

【図8 A】

【図8 B】

【図9 A】

【図9 B】

【図10】

【図11B】

【図12A】

【図12B】

【図13B】

【図13A】

【図14A】

【図14B】

【図16】

【図15】

---

フロントページの続き

(74)代理人 100094673

弁理士 林 銀三

(74)代理人 100107467

弁理士 員見 正文

(72)発明者 ユアン、ジレン

スウェーデン国 ルンド、イリオングレンデン 209

審査官 柳下 勝幸

(56)参考文献 特開平08-273388 (JP, A)

特開平10-163912 (JP, A)

特開平11-027569 (JP, A)

特開昭62-145927 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00-01/88

G11C 27/02