(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4986247号

(P4986247)

(45) 発行日 平成24年7月25日(2012.7.25)

(24) 登録日 平成24年5月11日(2012.5.11)

(51) Int.Cl.

G06F 9/445 (2006.01)

G06F 9/54 (2006.01)

F 1

G06F 9/06 610J

G06F 9/06 640B

請求項の数 15 (全 25 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2009-132708 (P2009-132708)  |

| (22) 出願日  | 平成21年6月2日 (2009.6.2)          |

| (65) 公開番号 | 特開2010-282252 (P2010-282252A) |

| (43) 公開日  | 平成22年12月16日 (2010.12.16)      |

| 審査請求日     | 平成23年11月30日 (2011.11.30)      |

早期審査対象出願

|           |                                                              |

|-----------|--------------------------------------------------------------|

| (73) 特許権者 | 505381024<br>株式会社ユビキタス<br>東京都新宿区西新宿 6-1 O-1 日土地<br>西新宿ビル 20F |

| (74) 代理人  | 100102406<br>弁理士 黒田 健二                                       |

| (74) 代理人  | 100100240<br>弁理士 松本 孝                                        |

| (72) 発明者  | 橋本 健一<br>東京都新宿区西新宿 1-25-1 新宿セ<br>ンタービル 株式会社ユビキタス内            |

| 審査官       | 稻垣 良一                                                        |

最終頁に続く

(54) 【発明の名称】プログラム、制御方法、並びに制御装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ソフトウェアの起動を制御する方法であって、メモリを管理する機能を有するプロセッサに、

所定の動作状態にあるソフトウェアの前記所定の動作に必要な物理ページに対して、全ての物理ページでページフォルトが発生するように、メモリ管理用のページテーブルエントリを書き換えるステップ、

前記書き換えるステップの後に、前記所定の動作状態にあるソフトウェアのメモリイメージを保存するステップ、および

前記ソフトウェアが起動する時、前記メモリ管理用のページテーブルエントリを使用して、各ページテーブルエントリでページフォルトを発生させ、そのページフォルトが発生したページを順次読み出すステップ

を実行させる、ソフトウェアの起動制御方法。

## 【請求項 2】

請求項 1 に記載のソフトウェアの起動制御方法において、

前記メモリは、RAM および不揮発性メモリを含み、

前記書き換えるステップは、前記RAMが記憶しているページテーブルエントリを書き換えるステップを含み、

前記保存するステップは、前記所定の動作状態にあるソフトウェアのデータ、プログラムコード、ページテーブルエントリを書き換えられたメモリ管理用テーブル、ページフォ

10

20

ルトハンドラ、割込ベクタ、およびレジスタを、前記不揮発性メモリに記憶させるステップを含む

方法。

### 【請求項 3】

請求項 2 に記載のソフトウェアの起動制御方法において、

前記書き換えるステップは、各ページテーブルエントリが示す物理ページが存在するか否か、および前記物理ページが前記RAM内にあるかを判断するステップ、前記RAMが記憶している前記ページテーブルエントリのうち前記物理ページが存在するページテーブルエントリを、前記物理ページへのアクセスを禁止する情報に書き換えるステップ、および前記書き換えるステップにより前記物理ページへのアクセスを禁止する情報に書き換えられたことを識別するマーキングを実行するステップを含み、

前記読み出すステップは、前記ページフォルトが発生した物理ページに前記マーキングがされているかを判断し、前記マーキングがされたと判断された物理ページを読み出す方法。

### 【請求項 4】

請求項 2 または 3 に記載のソフトウェアの起動制御方法において、

前記読み出すステップは、

ページフォルトが発生したとき、前記割込ベクタが前記ページフォルトハンドラを呼び出し、前記ページフォルトハンドラが、ページフォルトが発生したアドレスからページを計算し、そのページを前記不揮発性メモリから読み出すステップを含む

方法。

### 【請求項 5】

請求項 1 または 2 に記載のソフトウェアの起動制御方法において、

前記プロセッサが、組み込み型のコンピュータのプロセッサである

方法。

### 【請求項 6】

情報処理装置であって、

メモリ、前記メモリを管理する機能を有するプロセッサ、およびプログラムコードを有し、

前記プログラムコードは、ソフトウェアの起動を制御するために前記プロセッサに、

所定の動作状態にあるソフトウェアの前記所定の動作に必要な物理ページに対して、全

ての物理ページでページフォルトが発生するように、メモリ管理用のページテーブルエントリを書き換えるステップ、

前記書き換えるステップの後に、前記所定の動作状態にあるソフトウェアのメモリイメージを保存するステップ、および

前記ソフトウェアが起動する時、前記メモリ管理用のページテーブルエントリを使用して、各ページテーブルエントリでページフォルトを発生させ、そのページフォルトが発生したページを順次読み出すステップ

を実行させる、情報処理装置。

### 【請求項 7】

請求項 6 に記載の情報処理装置において、

前記メモリは、RAM および不揮発性メモリを含み、

前記書き換えるステップは、前記RAMが記憶しているページテーブルエントリを書き換えるステップを含み、

前記保存するステップは、前記所定の動作状態にあるソフトウェアのデータ、プログラムコード、ページテーブルエントリを書き換えられたメモリ管理用テーブル、ページフォルトハンドラ、割込ベクタ、およびレジスタを、前記不揮発性メモリに記憶させるステップを含む

装置。

### 【請求項 8】

10

20

30

40

50

請求項 7 に記載の情報処理装置において、

前記書き換えるステップは、各ページテーブルエントリが示す物理ページが存在するか否か、および前記物理ページが前記RAM内にあるかを判断するステップ、前記RAMが記憶している前記ページテーブルエントリのうち前記物理ページが存在するページテーブルエントリを、前記物理ページへのアクセスを禁止する情報に書き換えるステップ、および前記書き換えるステップにより前記物理ページへのアクセスを禁止する情報に書き換えられたことを識別するマーキングを実行するステップを含み、

前記読み出すステップは、前記ページFAULTが発生した物理ページに前記マーキングがされているかを判断し、前記マーキングがされたと判断された物理ページを読み出す装置。

10

#### 【請求項 9】

請求項 7 または 8 に記載の情報処理装置において、

前記読み出すステップは、

ページFAULTが発生したとき、前記割込ベクタが前記ページFAULTハンドラを呼び出し、前記ページFAULTハンドラが、ページFAULTが発生したアドレスからページを計算し、そのページを前記不揮発性メモリから読み出すステップを含む装置。

#### 【請求項 10】

請求項 6 または 7 に記載の情報処理装置において、

前記プロセッサが、組み込み型のコンピュータのプロセッサである装置。

20

#### 【請求項 11】

記憶媒体にコンピュータ読み取り可能に記憶されるプログラムであって、

メモリを管理する機能を有するプロセッサに、

所定の動作状態にあるソフトウェアの前記所定の動作に必要な物理ページに対して、全ての物理ページでページFAULTが発生するように、メモリ管理用のページテーブルエントリを書き換えるステップ、

前記書き換えるステップの後に、前記所定の動作状態にあるソフトウェアのメモリイメージを保存するステップ、および

前記ソフトウェアが起動する時、前記メモリ管理用のページテーブルエントリを使用して、各ページテーブルエントリでページFAULTを発生させ、そのページFAULTが発生したページを順次読み出すステップ

30

を含むソフトウェアの起動を制御する方法を実行させる、プログラム。

#### 【請求項 12】

請求項 11 に記載のプログラムにおいて、

前記メモリは、RAMおよび不揮発性メモリを含み、

前記書き換えるステップは、前記RAMが記憶しているページテーブルエントリを書き換えるステップを含み、

前記保存するステップは、前記所定の動作状態にあるソフトウェアのデータ、プログラムコード、ページテーブルエントリを書き換えられたメモリ管理用テーブル、ページFAULTハンドラ、割込ベクタ、およびレジスタを、前記不揮発性メモリに記憶させるステップを含む

40

プログラム。

#### 【請求項 13】

請求項 12 に記載のプログラムにおいて、

前記書き換えるステップは、各ページテーブルエントリが示す物理ページが存在するか否か、および前記物理ページが前記RAM内にあるかを判断するステップ、前記RAMが記憶している前記ページテーブルエントリのうち前記物理ページが存在するページテーブルエントリを、前記物理ページへのアクセスを禁止する情報に書き換えるステップ、および前記書き換えるステップにより前記物理ページへのアクセスを禁止する情報に書き換えられたことを識別するマーキングを実行するステップを含み、

50

られたことを識別するマーキングを実行するステップを含み、

前記読み出すステップは、前記ページフォルトが発生した物理ページに前記マーキングがされているかを判断し、前記マーキングがされたと判断された物理ページを読み出す

プログラム。

【請求項 1 4】

請求項 1 2 または 1 3 に記載のプログラムにおいて、

前記読み出すステップは、

ページフォルトが発生したとき、前記割込ベクタが前記ページフォルトハンドラを呼び出し、前記ページフォルトハンドラが、ページフォルトが発生したアドレスからページを計算し、そのページを前記不揮発性メモリから読み出すステップを含む

プログラム。

10

【請求項 1 5】

請求項 1 1 または 1 2 に記載のプログラムにおいて、

前記プロセッサが、組み込み型のコンピュータのプロセッサである

プログラム。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明はプログラム、制御方法、並びに制御装置に関し、特に、ソフトウェアの起動を制御するときに好適なプログラム、制御方法、並びに制御装置に関する。

20

【背景技術】

【0 0 0 2】

パーソナルコンピュータにおいて、OS (Operating System) を起動させ、所望のソフトウェアを動作させるまでには数分単位の起動時間が必要であった。これを高速に起動させる手法として、ハイバネーション ( hibernation ) と呼ばれる手法が存在する ( 例えば、特許文献 1 参照 ) 。

【0 0 0 3】

特許文献 1 には、起動後の C P U ( central processing unit ) や I / O ( input / output ) レジスタ、R A M ( Random Access Memory ) イメージが、ハードディスクドライブ ( H D D ) やフラッシュメモリに格納されることが記載されている。そして、次に起動されるときに、格納されている R A M イメージが復帰され、その後、C P U や I / O レジスタが再設定されることが記載されている。このように起動することで、OS の起動を高速化させることができ、特許文献 1 では提案されている。このような提案に基づくハイバネーションと称される手法は、既にパーソナルコンピュータで適用されている。

30

【0 0 0 4】

また、組み込み型のコンピュータ、例えば、テレビジョン受像器、ハードディスクレコーダといった電子機器に組み込まれているコンピュータにおいても、ハイバネーションの手法が応用されている。

【先行技術文献】

【特許文献】

40

【0 0 0 5】

【特許文献 1】特開 2 0 0 5 - 1 4 9 2 2 5 号公報

【特許文献 2】特開 2 0 0 7 - 3 3 4 3 8 3 号公報

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 6】

ハイバネーションを適用し、OS を起動させる場合と OS を通常通りに起動させる場合とを比較した場合、ハイバネーションを適用して OS を起動させる方が、より高速に起動させることができる。しかしながら、R A M の容量増加に伴って保存すべき R A M イメージのサイズも増加してしまい、起動時に、その R A M イメージの展開時間も増加してしま

50

う。結果として、RAMの大容量化に伴い高速起動が困難になってしまう。

【0007】

また、パーソナルコンピュータは、CPUの性能も比較的高いため、仮にRAMイメージのサイズが増加してしまっても、そのRAMイメージを処理する性能が確保される。しかしながら、組み込み型のコンピュータの場合、CPUの性能が比較的低いものが使われることが多い。そのため、組み込み型のコンピュータの場合、RAMイメージが増加すれば、ハイバネーションの手法を適用しても、起動時の速度は低下してしまう。すなわち、組み込み型のコンピュータの場合、RAMイメージの増加による速度の低下は、より顕著に表れてしまう。

【0008】

また、RAMイメージを圧縮することで、RAMイメージのサイズを小さくすることも提案されているが、起動時に伸張する処理が必要となる。この伸張処理にかかるCPUへの負荷や、伸張処理にかかる時間を考慮すると、起動の高速化という点では効果的な方法ではない。

【0009】

このようなことを考慮し、特許文献2では、ハイバネーションのイメージの全ての転送を完了する前に、OSの実行を開始する手法が提案されている。しかしながら、この手法では、特別なハードウェアを搭載し、先行転送するページを予め特定しておく必要があるため、その特別なハードウェアの分だけコストが高くなるなどの問題点があった。

【0010】

本発明は、このような状況に鑑みてなされたものであり、起動時間を短縮することができるようとするものである。

【課題を解決するための手段】

【0011】

本発明の一側面のプログラムは、メモリを管理する機能を有する制御装置に、所定のソフトウェアの動作に必要なページに対して、全てのページでページフォルトが発生するようページテーブルエントリを書き換え、前記ソフトウェアが起動時に、前記ページテーブルエントリで、ページフォルトが発生し、そのページフォルトが発生したページを順次読み出すステップを含む。

【0012】

前記所定のソフトウェアが起動された後、前記ページテーブルエントリを書き換え、その起動時のデータ、プログラムコード、テーブル、ページフォルトハンドラ、割り込みベクタ、およびレジスタを、前記メモリに記憶させるようにすることができる。

【0013】

前記メモリのうち、書き換えの対象となる前記ページテーブルエントリを記憶しているのはRAMであり、順次読み出される前記ページを記憶しているのは不揮発メモリであるようにすることができる。

【0014】

組み込み型のコンピュータが読み込むようにすることができる。

【0015】

本発明の一側面の制御方法は、メモリを管理する機能を有する制御装置の制御方法において、所定のソフトウェアの動作に必要なページに対して、全てのページでページフォルトが発生するようページテーブルエントリを書き換え、前記ソフトウェアが起動時に、前記ページテーブルエントリで、ページフォルトが発生し、そのページフォルトが発生したページを順次読み出すステップを含む。

【0016】

本発明の一側面の制御装置は、メモリを管理する機能を有する制御装置において、所定のソフトウェアの動作に必要なページに対して、全てのページでページフォルトが発生するようページテーブルエントリを書き換える書き換え手段と、前記ソフトウェアが起動時に、前記ページテーブルエントリで、ページフォルトが発生し、そのページフォルトが

10

20

30

40

50

発生したページを順次読み出す読み出し手段とを備える。

【0017】

本発明の一側面のプログラム、制御方法、並びに制御装置は、所定のソフトウェアの動作に必要なページに対して、全てのページでページフォルトが発生するようにページテーブルエントリが書き換えられ、ソフトウェアが起動時に、ページテーブルエントリで、ページフォルトが発生し、そのページフォルトが発生したページが順次読みだされる。

【発明の効果】

【0018】

本発明の一側面によれば、OSの起動時間を短縮することが可能となる。

【図面の簡単な説明】

10

【0019】

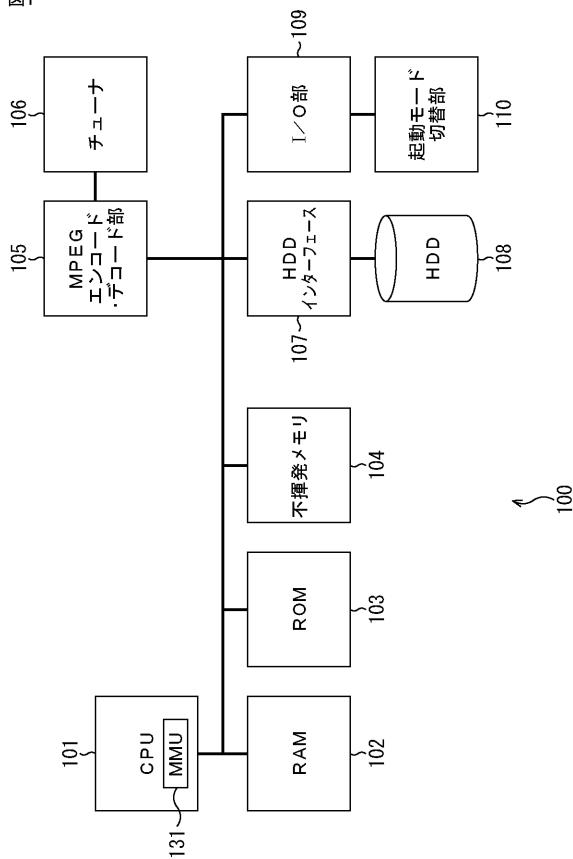

【図1】本発明を適用した情報処理装置の一実施の形態の構成を示す図である。

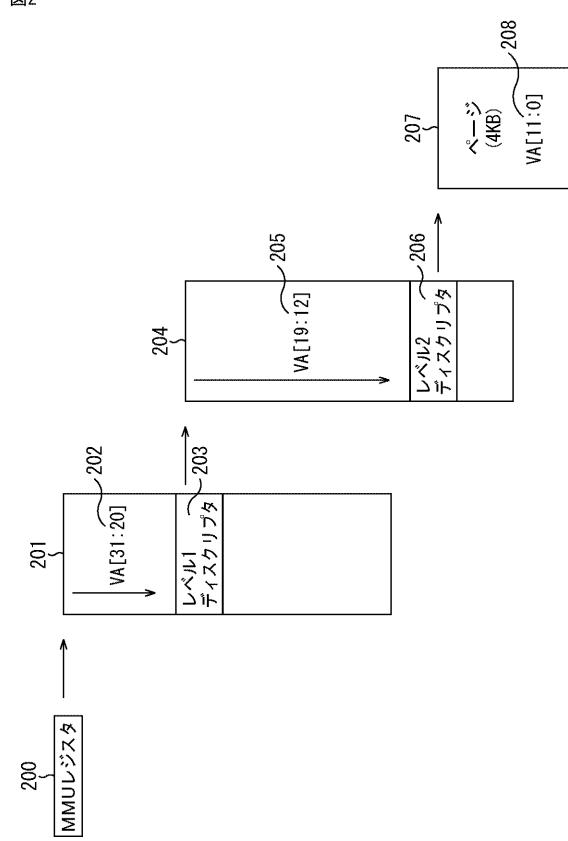

【図2】MMUのモデルを示す図である。

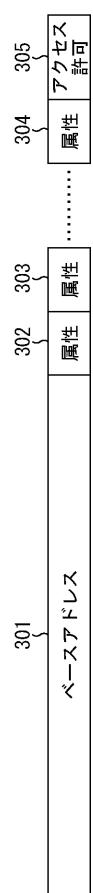

【図3】ディスクリプタについて説明するための図である。

【図4】物理ページの読み込みについて説明するための図である。

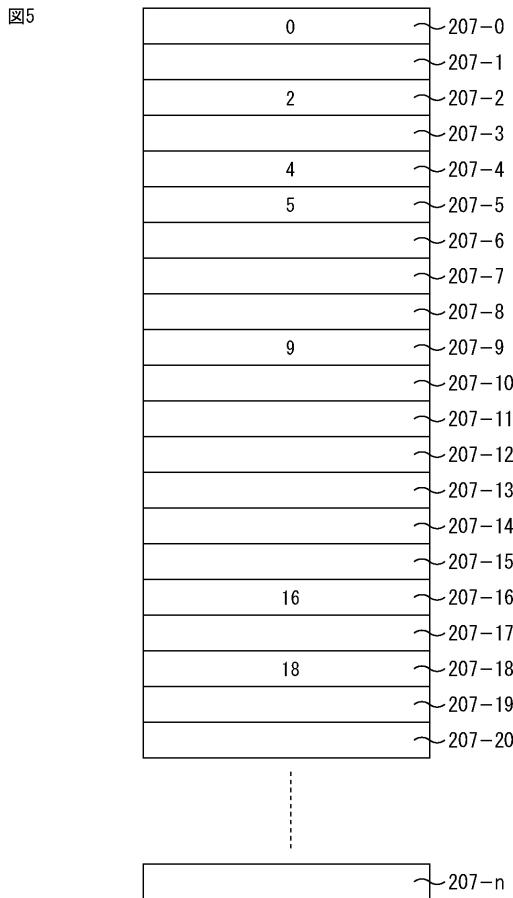

【図5】物理ページの読み込みについて説明するための図である。

【図6】物理メモリマップについて説明するための図である。

【図7】起動の処理について説明するためのフローチャートである。

【図8】起動の処理について説明するためのフローチャートである。

【図9】起動の処理について説明するためのフローチャートである。

20

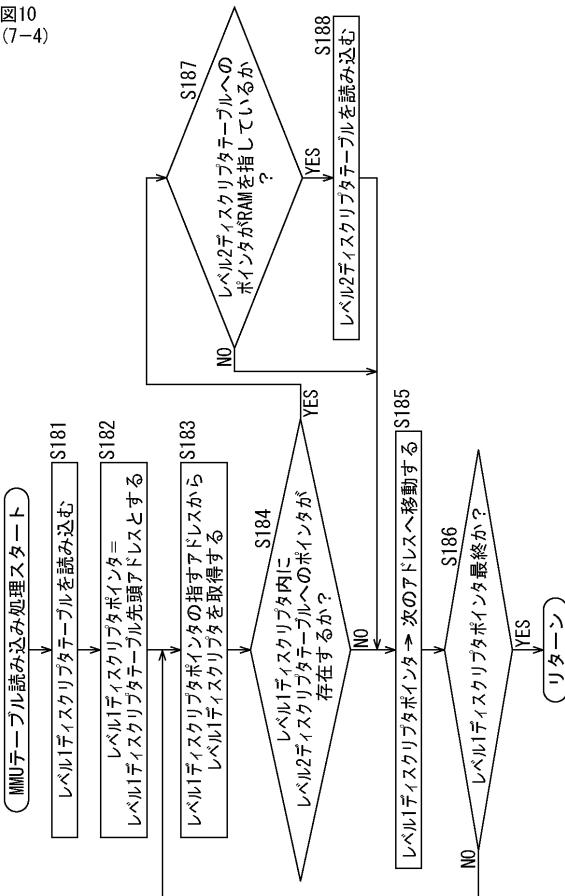

【図10】起動の処理について説明するためのフローチャートである。

【図11】起動の処理について説明するためのフローチャートである。

【発明を実施するための形態】

【0020】

以下に、本発明の実施の形態について図面を参照して説明する。

【0021】

まず、本発明の概略を説明する。本発明は、Memory Management Unit(以下、MMUと略記する)を搭載したCPU (central processing unit) 上で動作するOS (Operating System) やアプリケーション等のソフトウェアを高速に起動させるための手法である。

【0022】

30

高速起動の対象となるソフトウェアが、一度、通常通りの方法で起動され、その状態のRAM (Random Access Memory) イメージが不揮発メモリ等に保存される。RAMイメージが、不揮発メモリ等に保存されるとき、MMUのテーブルが書き換えられ、全てのページでページフォルトが発生するよう変更される。対象とされるソフトウェアには、ページフォルトハンドラが用意されており、ページフォルトが発生した場合、そのページフォルトが発生したページのみが、不揮発メモリからロードされる。

【0023】

任意のソフトウェアが起動され、プログラムコードが実行されたり、そのソフトウェアが動作に必要なデータを読み出すために、RAMにアクセスしたりした場合、毎回ページフォルトが発生し、必要なページが不揮発メモリからRAMに逐次ロードされることになる。これにより、従来のハイバネーション起動とは異なり、全てのRAMイメージを不揮発メモリからメインRAMに予めロードする必要が無くなり、動作に必要な必要最小限のRAMイメージのみをロードすることが可能になる。よって、高速に所望のソフトウェアを起動・動作させることが可能となる。

40

【0024】

本発明を使用することで、従来は数十秒～数分を要していたOSやソフトウェア(以下、単にソフトウェアとする)の起動時間を数秒程度に短縮することが可能となることが、本出願人により確認されている。以下に、具体的に説明する。

【0025】

[情報処理装置の構成について]

50

図1は、本発明を適用した情報処理装置の一実施の形態の構成を示す図である。本発明を適用した情報処理装置は、パーソナルコンピュータ( PC )に適用できることは勿論のこと、組み込み型のコンピュータを有する装置にも適用できる。組み込み型のコンピュータを含む装置としては、テレビジョン受像器、ハードディスクレコーダといった電子機器がある。ここでは、ハードディスクレコーダに対して本発明を適用したときを例にあげて説明する。

#### 【0026】

図1は、本発明を適用した情報処理装置としてのハードディスクレコーダの構成を示す図である。図に示したハードディスクレコーダ100は、CPU101、RAM102、ROM(Read Only Memory)103、不揮発メモリ104、MPEG(Moving Picture Experts Group)エンコード・デコード部105、チューナ106、HDDインターフェース107、HDD108、I/O部109、起動モード切替部110を備える。

10

#### 【0027】

CPU101は、ハードディスクレコーダ100の各部を制御する。このCPU101は、Memory Management Unit(以下、MMUと記述する)を搭載し、RAM102を小分割して小単位(ページ)で管理できる仕組みを有している。なお、ここでは、MMU131がCPU101に含まれるとして説明を続けるが、MMU131が、CPU101に含まれず、外部に備えられている構成とすることも可能である。また、MMU131の形式には特に制限はないが、ページ単位にアクセスの許可・禁止の属性が設定可能で、アクセス禁止のページにアクセスした場合は、ページフォルトの例外が発生できる構成とされている。また、CPU101のMMU131は、4キロバイト(以下、4KBと記述する)を1ページとして管理するとして説明を続ける。

20

#### 【0028】

RAM102は、SRAM(Static Random Access Memory)やDRAM(Dynamic Random Access Memory)などで構成することが可能である。RAM102は、CPU101が使用する主記憶装置として機能し、そのような機能を有していれば、RAM102として用いることが可能である。

#### 【0029】

ROM103は、FLASH ROMやMask ROMなどの読み込み専用のメモリである。ROM103は、OSやアプリケーションソフトウェアが格納され、そのような格納が行えれば、どのような種類のROMが用いられても本発明においては良い。

30

#### 【0030】

不揮発メモリ104は、ハードディスクレコーダ100の電源が切られても、記憶している内容が保持されるメモリである。例えば、FLASH ROMや、バックアップ機能付きのSRAM、DRAMなどで構成することが可能である。

#### 【0031】

不揮発メモリ104には、後述するソフトウェアが起動した後に、RAM102に格納されたソフトウェアのメモリイメージが格納される。そのため、不揮発メモリ104の容量は、RAM102の容量以上の容量とされることが好ましい。ただし、データ圧縮等によりデータを縮小するようにした場合、不揮発メモリ104の容量は、RAM102の容量以下の容量でも良い。また、不揮発メモリ104は、HDD108と兼用することも可能である(HDD108を不揮発メモリ108として利用することも可能である)。

40

#### 【0032】

MPEGエンコード・デコード部105は、動画の圧縮・伸張を行う。動画は、チューナ106を介して供給される。チューナ106は、ユーザの指示に基づき、複数の番組(動画)から、1つの動画を選択し、MPEGエンコード・デコード部105に供給する。MPEGエンコード・デコード部105は、必要に応じ、HDDインターフェース107を介して、HDD108にチューナ106からのデータを供給したり、HDD108からのデータをHDDインターフェース107を介して、受信したりする。また、その際、必要に応じ、エンコードまたはデコードの処理を実行する。

50

## 【0033】

I/O部109は、起動モード切替部110の状態をCPU101が読みとるために設けられている。以下に説明するソフトウェアは、高速起動イメージを取得するための通常起動モードと、高速起動イメージが取得された後の起動モードとしての高速起動モードを有する。I/O109と起動モード切替部110は、これらの起動モードの切り替えに用いられる。通常起動モードと高速起動モードの切り換えのために、起動モード切替部110をスイッチで構成することが可能である。また、通常起動モードと高速起動モードの切り換えのために、起動モード切替部110を、ブートローダ等からコマンドで切り替える構成とすることも可能である。

## 【0034】

また、一度高速起動のイメージが作成されれば、通常起動モードを不要とすることができます。高速起動モードのみが実装され、通常起動モードと高速起動モードの切り換えを不要とする構成としても良い。そのような構成とした場合、I/O部109と起動モード切替部110を省略した構成とすることも可能である。

## 【0035】

## [MMUについて]

図2は、CPU101が装備するMMU131のモデルを示す図である。図2に示したMMU131は、32bitクラス以上のCPU101が装備するモデルである。MMU131の構成や、物理アドレス、仮想アドレス、各テーブルのインデックスに使用するbit数、テーブルの段数等は、CPU101のメーカーに依存するものであるが、特にメーカーのアーキテクチャに依存はしない。ここでは説明の都合上、32bit等の具体的な数字を例にあげて説明するが、その数値は、本発明の適用範囲の限定を示すものではない。

## 【0036】

MMU131は、最終的な物理ページを指し示すテーブル内エントリの属性にアクセス許可もしくはアクセス許可相当の機能を実装し、不許可の場合にアクセスしたときには、ページフォルトもしくはページフォルト相当の例外処理が発生できる機能を少なくとも有する。

## 【0037】

MMUレジスタ200は、MMU131に装備されるレジスタである。このレジスタにレベル1ディスクリプタテーブル201の先頭アドレスが代入される。レベル1ディスクリプタテーブル201は、メモリ上に置かれたレベル1メモリテーブルである。物理アドレス空間が32bitの場合、1つのアドレスを指し示すのに32bit、即ち4バイトが使用されるため、レベル1ディスクリプタテーブル201のサイズは、12bit空間 = 4KB空間 × 4バイトで16KBのサイズとなる。

## 【0038】

仮想アドレス202は、レベル1メモリテーブルのインデックスとして使われる仮想アドレスの31bitから20bitを示す。VAはVirtual Address(仮想アドレス)を意味する。所定の仮想アドレスにアクセスがあった場合、レベル1ディスクリプタテーブル201の先頭アドレスから仮想アドレスの31bitから20bitがインデックスとされ、レベル1ディスクリプタ203にアクセスがされる。

## 【0039】

物理アドレス空間が32bitのCPU101である場合、1つのアドレスを示すのに32bit、即ち4バイトが使用されるため、レベル1ディスククリプタのアドレスは以下のようになる。

レベル1ディスクリプタ203のアドレス

$$= \text{レベル1ディスクリプタテーブル201の先頭アドレス} \\ + \text{仮想アドレス202(VA[31:20])} \times 4$$

## 【0040】

レベル1ディスクリプタ203は、レベル2ディスクリプタテーブル204の先頭アドレスを指し示すポインタや属性から構成されるディスクリプタである。レベル2ディスク

10

20

30

40

50

リプタテーブル 204 の先頭アドレスから仮想アドレスの 19bit から 12bit がインデックスとされ、レベル 2 ディスクリプタ 206 にアクセスされる。

#### 【0041】

物理アドレス空間が 32bit の CPU101 である場合、1つのアドレスを示すのに 32bit、即ち 4 バイトが使用されるため、レベル 2 ディスクディスクリプタのアドレスは以下のような式になる。

レベル 2 ディスクリプタ 206 のアドレス

$$\begin{aligned} &= \text{レベル 2 ディスクリプタテーブル 204 の先頭アドレス} \\ &\quad + \text{仮想アドレス 205 (VA[19:12])} \times 4 \end{aligned}$$

#### 【0042】

10

レベル 2 ディスクリプタ 206 は、4KB の物理ページ 207 を示すポインタや属性から構成されるディスクリプタである。物理ページ 207 は、最終的に仮想アドレスから物理アドレスに変換された 1 ページの物理メモリである。物理ページ 207 の 4KB 内のアドレスは、仮想アドレス 208 (VA[11:0]) で指定される。

#### 【0043】

図 3 は、レベル 1 ディスクリプタ 203 やレベル 2 ディスクリプタ 206 の一例である。図 3 におけるディスクリプタはあくまでも一例であり、本発明は、このような一例で示した特定の CPU101 やアーキテクチャに依存することを示すものではない。

#### 【0044】

20

ベースアドレス 301 は、次のテーブルや物理ページの先頭アドレスを指すポインタである。属性 302 乃至 304 は、それぞれ、実行可・不可、特権モード・ユーザモードといった属性を示す属性 bit である。アクセス許可 bit 305 は、このディスクリプタが示す物理ページに対してのアクセスが許可されているか否かを示す bit である。このアクセス許可 bit 305 で、アクセスを禁止するように設定されている物理ページにアクセスがあった場合、一般的には、ページフォルトと呼ばれる例外処理、即ち割込み処理が実行され、そのような機構が必要である。よって、CPU101 のアーキテクチャに依存はしないが、ページフォルト、もしくはページフォルト相当の機能は、CPU101 に装備されている必要がある。

#### 【0045】

30

[ 物理ページについて ]

図 4 は、物理ページ 207 が、RAM102 (図 1) 上に並んでいる状態を擬似的に示している。RAM102 には、1 ページ分の物理ページ 207 が、物理ページ 207 - 0 から順に、物理ページ 207 - n まで配列されている。MMU131 搭載の CPU101 上でソフトウェアが動作される場合、1 ページの物理ページ 207 は、このように 4KB 乃至 64KB 単位で 1 ページとして管理されるように構成されていることが多い。

#### 【0046】

40

図 5 は、ソフトウェアが所定の動作状態であるときの物理ページの使用状況について説明するための図である。図 5 中、数字が記載されているページが使用されているページであり、数字が記載されていないページは使用されていないページを示す。ソフトウェアが使うプログラムコードやデータが、図 4 に示したように、全ての領域を使っていたとしても、ソフトウェアの状態をある単位時間でみた場合、図 5 で示すように使われていることが多い。すなわち、使用されているページと使用されていないページとがあり、全てのページが使用されているわけではない。

#### 【0047】

このソフトウェアが、所定の動作状態のときには、物理ページ 207 - 0、物理ページ 207 - 2、物理ページ 207 - 4、物理ページ 207 - 5、物理ページ 207 - 9、物理ページ 207 - 16、および物理ページ 207 - 18 が使用される。すなわち、図 4 に示したように、RAM102 には、1 ページ分の物理ページ 207 が、物理ページ 207 - 0 から順に、物理ページ 207 - n まで配列されているが、そのうち所定のソフトウェアが、所定の動作状態のときには、全てのページが使われるわけではなく、図 5 に示した

50

ように、複数のページのみが使用される。

#### 【0048】

従来のハイバネーション起動による起動の場合、ソフトウェアが動作する前に、図4に示したように、物理ページ207-0から物理ページ207-nまで、順次読み出しが行われてから復帰動作が始まり、所定の動作状態にされる。しかしながら実際に、そのソフトウェアが所定の動作状態になるためには、図5に示したように、所定の複数の物理ページ207が読み出されるだけでよい。そこで、本発明においては、後述するように読み出しを制御することで、図5に示したように、必要とされる物理ページ207のみが読み出されるようにする。

#### 【0049】

従来のハイバネーション起動による起動の場合、図4に示したように物理ページ207-0から順次読み出しが行われるため、換言すれば、必要のない物理ページ207も読み出されるため、読み出しに時間がかかり、結果として、所定のソフトウェア(OSなども含む)の起動が遅くなるということがあった。しかしながら、本発明によれば、図5に示したように、必要とされる物理ページ207のみが読み出されるため、読み出しにかかる時間を短縮することができ、所定のソフトウェア(OSなども含む)の起動を早くすることが可能となる。

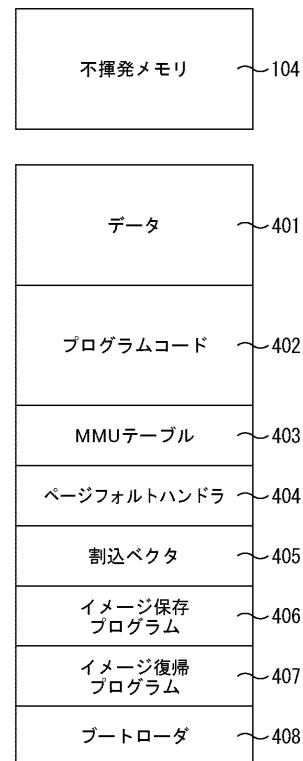

#### 【0050】

図6は、ソフトウェアの物理メモリマップを示す図である。なお、以下に説明する処理は、CPU101やOSに依存するもので、これらの機能が実装されていれば構成やメモリ配置に制限はなく、以下の説明だけに、本発明が適用されることを示すものではない。

#### 【0051】

不揮発メモリ104は、電源を切っても記憶内容が保持されるメモリである。図6に示した例では、不揮発メモリ104としてFLASH ROMをイメージしている。不揮発メモリ104は、メインメモリ上にマッピングされているが、電源を切っても内容が保持され、且つ、RAM102以上の容量を装備している。しかしながら、本発明を適用できる不揮発メモリ104は、I/O経由でのアクセス等、必ずしもメモリマップ上にマッピングされている必要はなく、そのアーキテクチャに制限はない。

#### 【0052】

データ401は、プログラムコード402が使用する読み書きができるデータ領域である。データ401は物理ページ207として、ある特定の大きさに分割されて格納される。データ401は、読み書きできる必要があるのでRAM102上に置かれることが好ましい。

#### 【0053】

プログラムコード402は、起動・実行させる所望のプログラムを示す。一般的なパソコン用コンピュータでWindows(登録商標)やLinuxと言ったOSが搭載され、その上で動作するソフトウェアである場合、プログラムとは、そのOSとソフトウェアを含む。プログラムコード402は、物理ページ207として、ある特定の大きさに分割されて格納される。このプログラムコード402は、RAM102またはROM103上に置かれる。

#### 【0054】

MMUテーブル403は、図2に示したレベル1ディスクリプタテーブル201およびレベル2ディスクリプタテーブル204を示している。ページフォルトハンドラ404は、MMU131のレベル2ディスクリプタ206がアクセス禁止の属性であり、ページフォルトが発生したとき、割込みベクタ経由で例外処理を行うためのプログラムである。ここではプログラムコード402と分けて、ページフォルトハンドラ404を記述しているが、プログラムコード402に含まれる場合もある。

#### 【0055】

割込みベクタ405は、一般的なCPUが持つ割込みベクタである。ページフォルトが発生した場合、この割込みベクタ内のページフォルトにプログラムコードがジャンプし、結果的にページフォルトハンドラ404が呼び出される。

10

20

30

40

50

**【 0 0 5 6 】**

データ 401、プログラムコード 402、MMU テーブル 403、および割込ベクタ 405 の論理アドレスに対する物理アドレスは、任意のアドレスにマッピングできる。

**【 0 0 5 7 】**

イメージ保存プログラム 406 は、所望のプログラムが起動された後、所望の状態でメモリイメージが不揮発メモリ 104 に保存されるようにするためのプログラムである。イメージ保存プログラム 406 の論理アドレスと物理アドレスは、同一アドレスにマッピングされる必要がある。

**【 0 0 5 8 】**

イメージ復帰プログラム 407 は、イメージ保存プログラム 406 の処理により保存された物理メモリイメージを、必要に応じて物理ページ単位に、データ 401 やプログラムコード 402 を、対応する物理ページに、不揮発メモリ 104 から読み込み、復帰させるためのプログラムである。イメージ復帰プログラム 407 の論理アドレスと物理アドレスは、同一アドレスにマッピングされる必要がある。

10

**【 0 0 5 9 】**

ブートローダ 408 は、電源投入もしくはリセット後に最初に起動されるブートローダである。主にブートローダ 408 は、起動に必要な最低限の I/O の初期化を行う。このような構成をソフトウェアは有する。

**【 0 0 6 0 】**

20

**[ ソフトウェアの動作について ]**

次に、本発明を適用したソフトウェアの動作について説明する。まず、概要を説明し、その後詳細を説明する。本発明によれば、ソフトウェアの局所性を利用し、ソフトウェアを高速に起動することができる。ソフトウェアには OS 等も含まれる。例えば、容量 4 GB の RAM を備えるハードウェア上で、所定のソフトウェアを動作させると仮定する。その所定のソフトウェアのプログラムおよびデータの容量の合計が、仮に 4 GB であったとする。一般的にソフトウェアは、様々なモードや機能を有し、所定の単一の機能だけで、全容量の 4 GB を使う可能性は極めて低い。

**【 0 0 6 1 】**

30

例えばソフトウェアが、起動後、特定の状態でユーザからのキー入力を待つとする。一般的にはハードウェアのリセット後、ブートローダが起動され、このソフトウェアが立ち上がってユーザからのキー入力待ちの状態とされる。このソフトウェアを既知の技術であるハイバネーションを適用して高速に起動させた場合、メモリイメージを作成する準備として、ユーザからのキー入力待ちの状態で CPU や各 I/O のレジスタが保存され、プログラムコードやデータの合計 4 GB が、何らかの不揮発メモリに格納されることになる。起動時はこの逆で、通常の起動プロセスは通らず、4 GB のメモリが展開され、CPU や I/O のレジスタが復帰され、キー入力の処理に戻ることになる。

**【 0 0 6 2 】**

40

上記ソフトウェアにおいて、「ユーザからの入力を待つ」という状態を考える。この状態では、キー入力の処理が繰り返されており、このようなキー入力に係わる処理に係わるプログラムコードやデータは比較的小さい。本発明は、この原理を利用して高速起動を実現する。動作は大きく分けると以下のようになる。

**【 0 0 6 3 】**

(A) 通常起動モードで OS や所望のソフトウェアが起動され、そのソフトウェアが所望の状態にされる

(B) イメージ保存プログラムが起動され、その起動されたイメージ保存プログラムにより、MMU 131 の全てのページテーブルに対してのアクセスを禁止するために、アクセス禁止を示す情報に所定の情報が書き換えられた後、上記 (A) の状態のメモリイメージがレジスタに保存されて終了される

(C) 次回以降は、高速起動モードにされることで、(A) の所望の状態で起動される

**【 0 0 6 4 】**

50

このような高速起動を実現するにあたり、基本的な準備として、通常通りにソフトウェアが起動され、そのソフトウェアが所望の状態にされ、その後、メモリイメージやレジスタが保存される。高速起動時は、ハイバネーション起動とは異なり、全てのメモリイメージがメインメモリに展開されるのではなく、実際に使われるメモリ、即ちプログラムコードやデータが、必要に応じて一部分のみ小刻みに展開される。

#### 【0065】

小刻みにプログラムコードやメモリが、メインメモリに展開される方法として、本実施の形態としては C P U が持つMemory Management Unit ( M M U 1 3 1 ) が利用される例をあげて説明している。 O S が、 M M U 1 3 1 を使用する場合もあるが、 O S が利用する前に、本発明が適用されたソフトウェアが元に戻し、 O S は、本発明が適用されたソフトウェアが M M U 1 3 1 を操作したことには関知しない。10

#### 【0066】

具体的には、メモリイメージが保存される前に、 M M U 1 3 1 のテーブルの内容が書き換えられ、全てのページがアクセス禁止に設定される。また、本発明が適用されたソフトウェアは、前記ページをアクセス禁止にしたというマークを付与する機能も有する。

#### 【0067】

仮に、所望のソフトウェアが O S 上で動作し、その O S が M M U 1 3 1 を使用する場合も同じである。高速起動時は、 M M U 1 3 1 のテーブルおよび C P U のレジスタのみ先行で復帰される。そして、メモリイメージが作成された後のアドレスに戻される。 M M U 1 3 1 のテーブルは、全てアクセス禁止に設定されているので、戻りアドレスにジャンプした時にページフォルトが発生する。データアクセス時も同じである。ページフォルトを処理するページフォルトハンドラ 4 0 4 は、ページフォルトが発生したアドレスからページを計算し、且つ、本発明が適用されたソフトウェアが、マークしたマークをチェックし、そのページを不揮発メモリ 1 0 4 からメインメモリ（例えば、 R A M 1 0 2 ）へ読み込み、 M M U 1 3 1 のテーブルを書き換える前の元の通りに書き戻す。20

#### 【0068】

このような処理が繰り返されることで、大容量のメモリイメージであっても、所望の状態に復帰させるには最低限のメモリイメージの読み込みだけで済み、高速に起動することが可能となる。

#### 【0069】

[ 動作の詳細について ]

上記してきたように、本発明によれば、所望のソフトウェアをある状態まで通常の起動と比較して高速に起動することが可能である。その高速起動を行う手順を大きく分けると、簡便に上記したが、( A )、( B )、( C )の3つに分類される。さらに( A )、( B )、( C )を、フローチャートを参照した説明の前に、さらに説明を加える。( A )、( B )の一連の流れは、一度実行されれば、毎回行う必要がない処理である。通常、( C )から実行されるようにすることで、高速起動することが可能となる。30

#### 【0070】

##### ( A ) 通常起動

( A - 1 ) 起動モード切替部 1 1 0 を通常起動モードに設定し、通常の方法により、 O S や所望のプログラムが起動される。40

( A - 2 ) 所望のプログラムが起動された後、ソフトウェアが操作されて、ソフトウェアが所望の状態にされる。高速起動時は、この状態で起動される。

#### 【0071】

##### ( B ) 状態の保存

( B - 1 ) 何らかのキー やコマンドなどによりイメージ保存プログラム 4 0 6 が起動される。この起動に関する起動方法には、特に制限はない。

( B - 2 ) イメージ保存プログラム 4 0 6 は、次回以降に高速に起動したい状態で、メモリイメージとレジスタを保存する。具体的には、イメージ保存プログラム 4 0 6 は、 M M U 1 3 1 のテーブルを全てアクセス禁止状態に設定し、その時点でのデータ 4 0 1 、50

プログラムコード402、MMUテーブル403、ページフォルトハンドラ404、割込ベクタ405、およびレジスタ類を不揮発メモリ104に保存させる。

#### 【0072】

##### (C) 高速起動

(C-1) 起動モード切替部110が、高速起動モードに設定される。ブートローダ408が、起動モードを判断し、高速起動モードの場合は、イメージ復帰プログラム407を呼び出す。イメージ復帰プログラム407は、イメージ保存プログラム406が保存したMMUテーブル403、ページフォルトハンドラ404、割込ベクタ405を復帰させる。

(C-2) B-1の処理でイメージ保存プログラム406が起動された後のアドレスに戻る、即ちジャンプする。MMU131が全てアクセス禁止状態に設定されているので、プログラムコード402やデータ401にアクセスされる毎に、対応するアドレスにてページフォルトが発生し、ページフォルトハンドラ404が呼ばれる。10

(C-3) ページフォルトハンドラ404は、対応する物理ページ207を不揮発メモリ104から1ページ分読み出し、MMU131を元に戻す。

(C-4) ページフォルトが次々に発生し、A-2の状態になるまで、必要なページフォルトが発生し続ける。

(C-5) A-2の状態になるまで物理ページ207が読み込まれる。この処理で読み込まれる物理ページ207は、実行されるソフトウェアや、その状態にも依存するが、極めて少なく、従来のハイバネーション技術で行われていたように、全ての物理ページ207を読み込むと比較して起動時間は著しく短くすることが可能となる。20

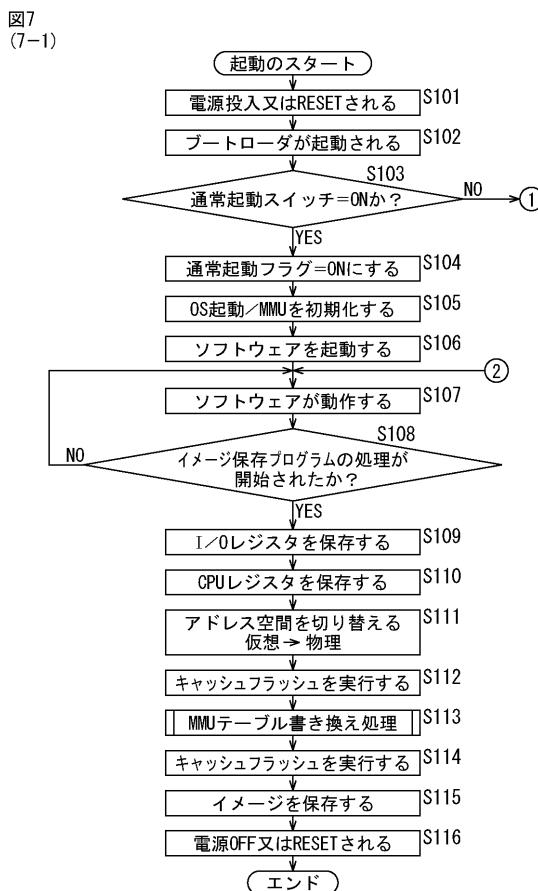

#### 【0073】

図7乃至11のフローチャートを参照し、上記(A)、(B)、(C)の各動作についてさらに説明を加える。

#### 【0074】

図7のフローチャートは、上記(A)、(B)の処理に該当する。すなわち、主に、電源投入からイメージ保存までの処理に係わるフローチャートである。ステップS101において、ハードディスクレコーダ100(図1)の電源が投入、もしくはリセットが発生してシステムが起動される。

#### 【0075】

ステップS102において、ブートローダ408(図6)が起動される。このステップS102で起動されるブートローダ408は、OSや所望のソフトウェアを動作させるために最低限のハードウェアの初期化や、必要に応じてROM103やHDD108に格納されているソフトウェアをRAM102に転送させたりする処理を想定し、そのような処理を実行できるブートローダであればよい。ブートローダ408は、システムに依存するものであり必須のものではない。よって、システムによっては、このステップS102が省略される場合もある。30

#### 【0076】

ステップS103において、起動モード切替部110の状態がチェックされ、通常起動モードか、高速起動モードかの遷移が切り替えられる(通常起動スイッチがONであるか否かが判断される)。起動モード切替部110が通常起動モードの場合、ステップS104に処理が進められ、高速起動モードの場合、ステップS161(図9)に進められる。40

#### 【0077】

ステップS103において、通常起動スイッチがONであると判断されると、通常起動モードで起動するため、通常起動フラグがONに設定される。通常起動フラグがONに設定されると、ステップS105に処理が進められ、OSが搭載されているシステムであれば、OSが起動される。一般的なシステムの場合、OSが起動される時にMMU131が初期化され、図2のMMU131のテーブルが作成される。本発明においては、OSの搭載は必須ではないが、仮にOSを搭載しないシステムの場合、MMU131の初期化を行う必要がある。また、OS搭載の場合であっても、OSの種類等に制限はない。50

**【0078】**

ステップS106において、高速起動させたい所望のソフトウェアが起動される。ステップS107において、起動されたソフトウェアが動作する。この処理は、上記したA-2の処理に該当する。高速起動により起動した状態と同じ状態にソフトウェアを遷移させる。例えば、所望のソフトウェアに複数のモードがあったと仮定し、その中である特定のモードで高速起動させたいのであれば、ソフトウェアを操作し、そのモードにまで遷移させる。例えば、ハードディスクレコーダ100の場合、予約するモード、再生するモード、設定するモードなどがあるが、ユーザが再生するモードをよく利用する場合、再生モードにまで遷移される。

**【0079】**

10

ステップS108において、イメージ保存プログラム406(図6)の処理が開始されたか否かが判断される。この処理は、上記したB-1の処理に該当する。コマンドやキー操作、スイッチ等によってイメージ保存プログラム406による処理が開始される。このイメージ保存プログラム406の実行手段に制限はない。ステップS108において、イメージ保存プログラム406(図6)の処理は開始されていないと判断された場合、ステップS107に処理が戻され、それ以降の処理が繰り返される。すなわちこの場合、ソフトウェアの動作が継続される。

**【0080】**

一方、ステップS107において、イメージ保存プログラム406(図6)の処理が開始されたと判断された場合、換言すれば、ソフトウェアの動作は終了したと判断された場合、ステップS109に処理が進められる。以下のステップS109乃至S116の処理は、上記したB-2の処理に該当する。また、ステップS109乃至S116の処理は、イメージ保存プログラム406が実行する処理である。

20

**【0081】**

ステップS109において、図1に示したI/O部109のレジスタが保存される。基本的には、設定されている値が取得され、保存される。I/Oに関しては、全てのレジスタが読み込める仕様のI/Oとは限らないので、その場合は個別に対応する必要がある。なお、I/Oの種類や仕様は任意であり、特に本発明を適用するうえでの制限はない。

**【0082】**

ステップS110において、CPU101のレジスタが保存される。基本的にはCPU101の全レジスタが保存される。CPU101やレジスタの種類は任意であり、特に本発明を適用するうえでの制限はない。

30

**【0083】**

ステップS111において、アドレス空間の切り換えが行われる。CPU101は、通常、仮想アドレスモードで動作している。このモードが、仮想アドレスモードから物理アドレスモードに遷移される。仮想アドレスモードから物理アドレスモードへの遷移方法は、MMU131のアーキテクチャに依存するため、本発明を適用するうえでの遷移方法に制限はない。また、仮想アドレスモードから物理アドレスモードに遷移させ場合、アドレス空間が変化するため、ステップS111における処理では、論理アドレスと物理アドレスとで同一アドレス空間にマッピングされる必要がある。

40

**【0084】**

ステップS112において、キャッシングフラッシュが実行される。CPU101が、TLB(Translation Look-aside Buffer)、一次キャッシング、二次キャッシングを搭載し、それらが有効だった場合、TLBおよびキャッシングがフラッシュされる必要がある。これは、次のステップS113において、RAM102上に置かれたMMUテーブル403の内容を書き換える必要があり、キャッシングに格納されているデータが、全てRAM102に反映されている必要があるからである。このステップS112におけるキャッシングフラッシュの処理は、必要に応じて行われ、場合によっては省略されても良い処理である。

**【0085】**

ステップS113において、MMU131のMMUテーブル403が、全ての物理ペー

50

ジ 2 0 7 へのアクセスを禁止する情報に書き換えられる。このステップ S 1 1 3 における MMU テーブル書き換え処理については、図 8 のフローチャートを参照して後述する。

#### 【 0 0 8 6 】

ステップ S 1 1 3 において、MMU 1 3 1 の MMU テーブル 4 0 3 が書き換えられると、ステップ S 1 1 4 に処理が進められる。ステップ S 1 1 4 において、キャッシングフラッシュが実行される。CPU 1 0 1 が T L B、一次キャッシング、二次キャッシングを搭載し、それらが有効だった場合、T L B およびキャッシングがフラッシュされる必要がある。これは前段のステップ S 1 1 3 の処理で書き換えた MMU 1 3 1 の MMU テーブル 4 0 3 の内容を、確実に RAM 1 0 2 へ反映させるためである。このステップ S 1 1 4 におけるキャッシングフラッシュの処理は、必要に応じて行われ、場合によっては省略されても良い処理である。10

#### 【 0 0 8 7 】

ステップ S 1 1 5 において、不揮発メモリ 1 0 4 に対して、RAM 1 0 2 の全容量の内容が全て保存される。RAM 1 0 2 のアドレスに対する不揮発メモリ 1 0 4 の相対的なアドレス位置が一致している必要がある。例えば、RAM 1 0 2 の物理アドレスが 0x10000 000 から 0x1fffffff にマッピングされていたとする。この場合、例えば不揮発メモリ 1 0 4 に対しては、0x40000000 から 0x4fffffff のアドレスにより、データが読み込める必要がある。

#### 【 0 0 8 8 】

この例の場合、RAM 1 0 2 のアドレスに対する不揮発メモリ 1 0 4 のオフセットは 0x30000000 となるため、RAM 1 0 2 に対するアドレスであっても、0x30000000 のオフセットを加えるだけで不揮発メモリ 1 0 4 内のアドレスに変換することが可能となる。不揮発メモリ 1 0 4 は、必ずしもメモリマップ上にマッピングされる必要はない。上記オフセットを加えたアドレスをキーにして読み込みができれば良い。また、不揮発メモリ 1 0 4 に対する保存方法は、アーキテクチャに依存するが、本発明の適用するうえで、その保存方法に制限はない。20

#### 【 0 0 8 9 】

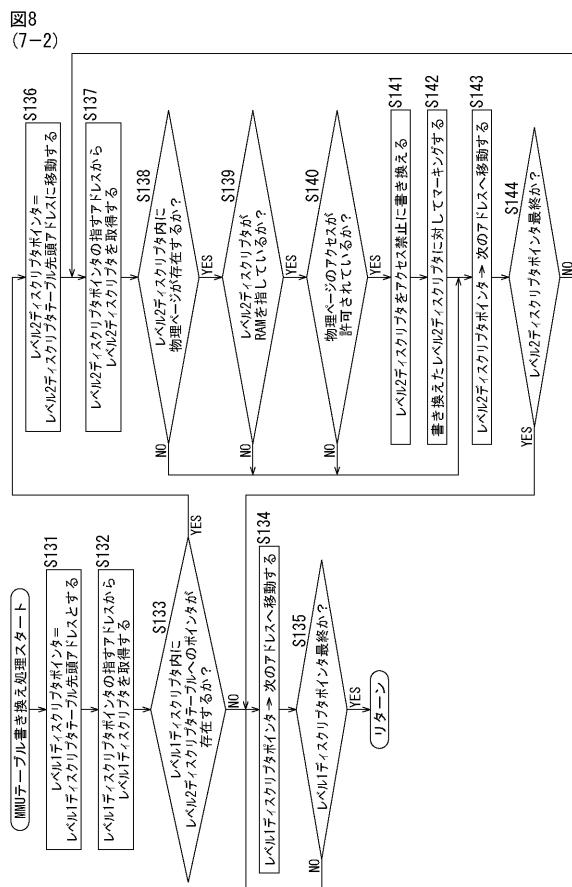

ステップ S 1 1 6 で、イメージ保存プログラム 4 0 6 での処理が終了される。イメージ保存プログラム 4 0 6 での処理が終了されることで、電源が OFF またはリセット(RESET)することができる状態となる。30

#### 【 0 0 9 0 】

図 7 に示したフローチャートにおいて、ステップ S 1 0 3 において、通常起動スイッチが ON ではないと判断されたときの処理と、ステップ S 1 1 3 での MMU テーブル書き換え処理についての詳細な説明が残っているが、まずここでは、図 8 のフローチャートを参照し、ステップ S 1 1 3 での MMU テーブル書き換え処理についての詳細な説明を行う。

#### 【 0 0 9 1 】

図 8 に示したフローチャートに基づく処理は、MMU 1 3 1 の MMU テーブル 4 0 3 が、図 2 で示した構成になっており、この MMU テーブル 4 0 3 を書き換える処理である。

#### 【 0 0 9 2 】

ステップ S 1 3 1 において、MMU 1 3 1 の MMU テーブル 4 0 3 の書き換えが開始されると、まず、変数レベル 1 ディスクリプタポインタに、レベル 1 ディスクリプタテーブル 2 0 1 の先頭アドレスが代入される。ステップ S 1 3 2 において、変数レベル 1 ディスクリプタポインタが指すアドレスからレベル 1 ディスクリプタ 2 0 3 が取得される。40

#### 【 0 0 9 3 】

ステップ S 1 3 3 において、ステップ S 1 3 2 の処理で取得されたレベル 1 ディスクリプタ 2 0 3 内にレベル 2 ディスクリプタテーブル 2 0 4 へのポインタが存在するか否かが判断される。ステップ S 1 3 3 において、レベル 1 ディスクリプタ 2 0 3 内にレベル 2 ディスクリプタテーブル 2 0 4 へのポインタが存在すると判断された場合、ステップ S 1 3 6 に処理が進められ、レベル 1 ディスクリプタ 2 0 3 内にレベル 2 ディスクリプタテーブル 2 0 4 へのポインタが存在しないと判断された場合、ステップ S 1 3 4 に処理が進めら50

れる。

**【0094】**

ステップS134において、変数レベル1ディスクリプタポインタが次のレベル1ディスクリプタポインタのアドレスに移動される。そして、ステップS135に処理が進められ、レベル1ディスクリプタポインタが最終に到達したか否かが判断される。

**【0095】**

ステップS135において、レベル1ディスクリプタポインタが最終に到達したと判断されるまで、ステップS134に処理が戻され、変数レベル1ディスクリプタポインタが次のレベル1ディスクリプタポインタのアドレスに移動されるといった処理が繰り返される。そして、ステップS135において、レベル1ディスクリプタポインタが最終に到達したと判断されると、処理はステップS114(図7)に進められる。すなわち、MMUテーブルの書き換えが終了したと判断され、図7に示したフローチャートの処理に、処理が戻される。

10

**【0096】**

一方、ステップS133において、レベル1ディスクリプタ203内にレベル2ディスクリプタテーブル204へのポインタが存在すると判断された場合、ステップS136に処理が進められる。ステップS136において、変数レベル2ディスクリプタポインタに、レベル2ディスクリプタテーブル204の先頭アドレスが代入される。

**【0097】**

ステップ137において、変数レベル2ディスクリプタポインタが指すアドレスからレベル2ディスクリプタ206が取得される。ステップS138において、ステップS137の処理で取得されたレベル2ディスクリプタ206内に物理ページ207が存在するか否かが判断される。ステップS138において、取得されたレベル2ディスクリプタ206内に物理ページ207が存在すると判断された場合、ステップS139に処理が進められ、取得されたレベル2ディスクリプタ206内に物理ページ207は存在しないと判断された場合、ステップS143に処理が進められる。

20

**【0098】**

ステップS139において、ステップS137の処理で取得されたレベル2ディスクリプタ206内の物理ページ207が、ステップS115(図7)にて保存の対象となるRAM102内のアドレスの範囲内であるか否かが判断される。ステップS139において、レベル2ディスクリプタ206内の物理ページ207が、保存の対象となるRAM102内のアドレスの範囲内であると判断された場合、ステップS140に処理が進められ、保存の対象となるRAM102内のアドレスの範囲内ではないと判断された場合、ステップS143に処理が進められる。

30

**【0099】**

ステップS140において、ステップS137で取得されたレベル2ディスクリプタ206のアクセス許可bit(図3のアクセス許可bit305)がチェックされ、その物理ページ207がアクセス許可にされているか否かが判断される。ステップS140において、物理ページ207へのアクセスが許可されていると判断された場合、ステップS141に処理が進められ、物理ページ207へのアクセスは許可されていないと判断された場合、ステップS143に処理が進められる。

40

**【0100】**

ステップS141において、ステップS137の処理で取得されたレベル2ディスクリプタ206のアクセス許可bit305がアクセス禁止を表すbitに書き換えられる。そして、ステップS142において、書き換えられたレベル2ディスクリプタ206に対してマーキングが実行される。この処理は、ステップS137の処理で取得されたレベル2ディスクリプタ206のアクセス許可bit305が、本発明が適用されたソフトウェアにより書き換えられたのか、他のソフトウェア、例えば、本来のOS等の動作によって書き換えられたのかを識別するための情報を保存する(マーキングする)ために行われる。

**【0101】**

50

ステップS142におけるマーキングの仕方については、アーキテクチャに依存し、本発明を適用するうえでの制限はない。例えば、レベル2ディスクリプタ206に使われていない空きbitが存在するのであれば、その空きbitをマーキングの情報を埋め込むbitとして使用することができる。また、別途テーブルを持たせてマーキングされたところとされていないところとが管理されるようにしても良い。いずれにせよ、仮にOS等が搭載されたシステムで、かつ、OSがこれらのbitを使用していた場合は、共存するような仕組みにすることで、本発明を実施することが可能である。

#### 【0102】

ステップS143において、変数レベル2ディスクリプタポインタが、次のレベル2ディスクリプタ206のポインタのアドレスに移動される。このステップS143への処理には、ステップS138において、レベル2ディスクリプタ206内に物理ページ207が存在しないと判断された場合、ステップS139において、レベル2ディスクリプタ206がRAM102を指していないと判断された場合、または、ステップS140において、物理ページ207へのアクセスは許可されていないと判断された場合にも来る。

10

#### 【0103】

ステップS144において、レベル2ディスクリプタポインタが最終に到達したか否かが判断される。ステップS144において、レベル2ディスクリプタポインタが最終に到達したと判断されるまで、ステップS137に処理が戻され、それ以降の処理が繰り返される。一方、ステップS144において、レベル2ディスクリプタポインタが最終に到達したと判断された場合、ステップS134に処理が進められる。ステップS134以降の処理については既に説明したので、その説明は省略する。

20

#### 【0104】

このようにして、MMU131のMMUテーブル403が書き換えられる。

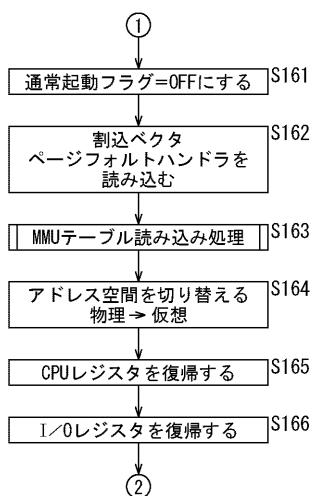

#### 【0105】

次に、高速起動時の処理について説明する。高速起動は、ステップS103において、通常起動スイッチがONになっていないと判断されたとき、すなわち、高速起動にスイッチが切り替えられていると判断されたときに実行される。図9のフローチャートは、ステップS103において、通常起動スイッチがONにはなっていないと判断されたときに処理が進められるフローチャートであり、高速起動時の処理について説明するためのフローチャートである。

30

#### 【0106】

ステップS161において、高速起動モードで起動するため、通常起動フラグがOFF(高速起動フラグがON)に設定される。ステップS162において、必要に応じて、割込ベクタ405、ページフォルトハンドラ404、MMUテーブル403が、イメージが保存された時と同じRAM102のアドレスに読み込まれる。

#### 【0107】

ステップS163において、MMU131のMMUテーブルが読み込まれる。このステップS163において実行されるMMUテーブル読み込み処理については、図10のフローチャートを参照し、後述する。

#### 【0108】

40

MMUテーブルの読み込みが終わると、ステップS164に処理が進められる。ステップS164において、CPU101のアドレス空間が、物理アドレスモードから仮想アドレスモードに遷移される。物理アドレスモードから仮想アドレスモードに遷移させる場合、アドレス空間が変化するため、ステップS164における処理では、論理アドレスと物理アドレスが同一アドレス空間にマッピングされる。

#### 【0109】

ステップS165において、ステップS110(図7)で保存されたCPU101のレジスタの値が不揮発メモリ104から読み出され、CPU101に対して復帰される。CPU101やレジスタの種類は任意であり、本発明を適用する上での制限はない。

#### 【0110】

50

ステップS166において、ステップS109(図7)で保存されたI/Oのレジスタの値が、不揮発メモリ104から読み出され、I/O部109に対して復帰される。I/Oの種類や仕様は任意であり、本発明を適用する上での制限はない。

#### 【0111】

このように、レジスタなどが復帰されると、ステップS107(図7)に処理が進められる。ステップS107において、ソフトウェアが動作する。この場合、ステップS104乃至S106の処理が実行されずに、ステップS107においてソフトウェアが動作開始となる。よって、ステップS104乃至S106の処理が実行される分だけ、少なくともソフトウェアが動作開始できるまでにかかる時間が短縮できることになる。特に、ステップS105におけるOSの起動やMMUの初期化にかかる時間、およびステップS106におけるソフトウェアの起動にかかる時間をなくすことができることで、大幅な時間の短縮を期待することができる。10

#### 【0112】

図9のフローチャートの説明に戻り、ステップS163で実行されるMMUテーブル読み込み処理の詳細について、図10のフローチャートを参照して説明する。

#### 【0113】

ステップS181において、MMUテーブル403の読み出しが開始されると、まずレベル1ディスクリプタテーブル201が読み出される。このレベル1ディスクリプタテーブル201は、ステップS115(図7)の処理で、不揮発メモリ104にRAM102の内容が保存されたが、その不揮発メモリ104に保存されている内容から、レベル1ディスククリプタテーブル201のみが読み出される。20

#### 【0114】

ステップS182において、変数レベル1ディスクリプタポインタに、レベル1ディスクリプタテーブル201の先頭アドレスが代入される。ステップS183において、変数レベル1ディスクリプタポインタが指すアドレスからレベル1ディスクリプタ203が取得される。ステップS184において、ステップS183の処理で取得されたレベル1ディスククリプタ203内にレベル2ディスクリプタテーブル204へのポインタが存在するか否かが判断される。

#### 【0115】

ステップS184において、取得されたレベル1ディスクリプタ203内にレベル2ディスクリプタテーブル204へのポインタが存在すると判断された場合、ステップS187に処理が進められ、取得されたレベル1ディスクリプタ203内にレベル2ディスクリプタテーブル204へのポインタは存在しないと判断された場合、ステップS185に処理が進められる。30

#### 【0116】

ステップS185において、変数レベル1ディスクリプタポインタが、次のレベル1ディスクリプタポインタのアドレスに移動される。そして、ステップS186において、レベル1ディスクリプタポインタが、最終に到達したか否かが判断される。ステップS186において、レベル1ディスクリプタポインタが、最終に到達したと判断された場合、ステップS164(図9)に処理が進められる。すなわちこの場合、MMUテーブル403の読み込みが完了されたため、次の処理へ処理が進められる。40

#### 【0117】

一方、ステップS186において、レベル1ディスクリプタポインタ203は、最終に到達していないと判断された場合、ステップS183に処理が戻され、それ以降の処理が繰り返される。ステップS183乃至S186が繰り返され、ステップS184において、取得されたレベル1ディスクリプタ203内にレベル2ディスクリプタテーブル204へのポインタが存在すると判断されると、ステップS187に処理が進められる。

#### 【0118】

ステップS187において、ステップS183で取得されたレベル1ディスクリプタ203内にある、レベル2ディスクリプタテーブル204へのポインタが、RAM102を50

指しているか否かが判断される。ステップ S 187において、レベル2ディスクリプタテーブル204へのポインタが、RAM102を指していると判断された場合、ステップ S 188に処理が進められ、レベル2ディスクリプタテーブル204へのポインタは、RAM102を指していないと判断された場合、ステップ S 185に処理が進められ、それ以降の処理が繰り返される。

#### 【0119】

ステップ S 188において、レベル2ディスクリプターブルが読み出される。このレベル2ディスクリプターブル204は、ステップ S 115(図7)の処理で、不揮発メモリ104にRAM102の内容として保存され、その不揮発メモリ104に保存されている内容から、レベル2ディスクリプターブル204のみが読み出される。その後、処理は、ステップ S 185に進められ、それ以降の処理が繰り返される。10

#### 【0120】

このようにして、MMUテーブルの読み出しが行われる。

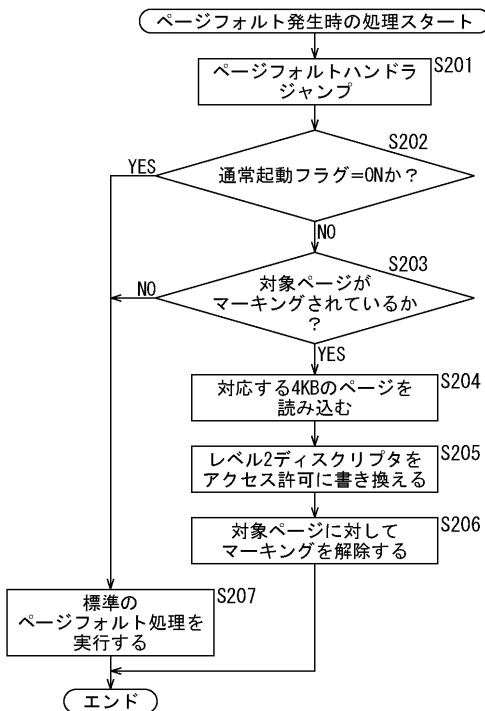

#### 【0121】

次に、図11のフローチャートを参照し、ページフォルトが発生したときに実行される処理について説明を加える。ステップ S 201において、ページフォルトが発生すると、割込ベクタ405にジャンプされる。すなわち、割込ベクタ405から、実際のページフォルト処理を行う割込ハンドラへのジャンプが実行される。

#### 【0122】

一般的なCPU101は、ページフォルトが発生した場合、割込処理として特定の割込ベクタにジャンプし、その割込ハンドラとして処理する。図11に示したページフォルト発生時の処理に係わるフローチャートは、ページフォルトの割込を処理する割込ハンドラを想定しているが、これらはCPU101のアーキテクチャに依存する。なお、本発明の適用は、CPU101のメーカーや型番により、制限が加えられることはない。20

#### 【0123】

ステップ S 202において、通常起動フラグがONであるか否かが判断される。通常起動フラグは、例えば、ステップ S 104(図7)の処理でONに設定される。ステップ S 202において、通常起動フラグがONであると判断された場合、換言すれば、通常起動であると判断された場合、ステップ S 207に処理が進められる。一方、ステップ S 202において、通常起動フラグがONではないと判断された場合、換言すれば、高速起動であると判断された場合、ステップ S 203に処理が進められる。30

#### 【0124】

ステップ S 203において、対象となる物理ページ207、即ちページフォルトが発生したアドレスに対応する物理ページ207が、マーキングされた物理ページ207であるか否かが判断される。マーキングは、ステップ S 142(図8)の処理で実行されたマーキングである。すなわち、マーキングされている物理ページ207は、本発明を適用したソフトウェアにより、アクセス禁止に書き換えられた物理ページ207である。

#### 【0125】

なお、一般的に物理ページ207とアドレスには、以下の計算式が満たされるが、これらはCPU101のアーキテクチャに依存するので、特にこの計算式に本発明の適用範囲が限定されるものではない。40

物理ページ = アドレス / ページサイズ(例えば、上記した例では4KB)

この式が示すように物理ページは、アドレスをページサイズで除算したものとなる。

#### 【0126】

ステップ S 203において、ページフォルトが発生したアドレスに対応する物理ページ207は、マーキングされた物理ページ207であると判断された場合、ステップ S 204に処理が進められ、マーキングされていない物理ページ207であると判断された場合、ステップ S 207に処理が進められる。

#### 【0127】

ステップ S 204において、対象となる物理ページ207、即ちページフォルトが発生

50

したアドレスに対応する物理ページ207が、ステップS115(図7)の処理で不揮発メモリ104に保存されたイメージから4KB分のみ読み出される。

#### 【0128】

ステップS205において、対象となる物理ページ207、即ちページフォルトが発生したアドレスに対応する物理ページ207の、レベル2ディスクリプタ206のアクセス許可bit305がアクセス許可に書き換えられる。ステップS206において、ステップS142(図8)の処理でマーキングした識別情報が解除される。

#### 【0129】

このようにして、ページフォルトが発生されたときの処理が実行されることで、高速起動が実現される。

10

#### 【0130】

一方、ページフォルトが発生したが、ステップS202において、通常起動フラグがONであると判断された場合、または、ステップS203において、対象ページはマーキングされていないと判断された場合、ステップS207に処理が進められる。ステップS207において、標準のページフォルトの処理が実行される。すなわち、通常起動のときや、本発明が適用されたソフトウェア以外のソフトウェア(OSなど)が、アクセスを不許可に設定していたような場合、通常起動や、アクセス不許可時の処理が実行される。

#### 【0131】

本発明を適用したシステムに、OS等が搭載されていた場合、標準的なページフォルトハンドラが通常実装されている。それに対して、上記のようなページフォルト機能がシステムに実装された場合、OS本来が行うページフォルト処理が、改めて実行される必要があるときもある。このステップS207の処理は、OS等のシステムに依存するものであり必須の処理ではないため、本実施の形態として省略することも可能である。

20

#### 【0132】

このようにして、ページフォルトが発生したときの処理が実行されることで、高速起動が実現される。

#### 【0133】

##### 〔効果〕

上記したように、Memory Management Unit(MMU)、もしくは、MMU相当のメモリ管理機能を搭載したコンピュータシステム上で、MMUのテーブルに対し、ソフトウェアの動作に必要なRAMの最小単位、いわゆるページに対して、全てのページにてページフォルトが発生するようにページテーブルエントリを書き換え、起動時は、アクセスするRAMに対して発生したページフォルトに対し、本来OS等が有する既知の技術であるページイン・ページアウトとしての機能だけでなく、発生したページフォルトの機能を保存したメモリイメージのページ単位の読み込みに用いることで、以下のような効果がある。

30

#### 【0134】

まず、必要最小限のメモリイメージの読み込み容量を実現することが可能となる。このことにより、例えば、パーソナルコンピュータの起動時間を短縮することが可能となる。具体的には、従来、数十秒から数分を要していた起動時間を、数秒以内で起動させることができるようになる。

40

#### 【0135】

また、デジタル家電の起動時間を短縮することが可能となる。テレビジョン受像器やハードディスクレコーダなどのデジタル家電(電子機器)には、OS(所定のソフトウェア)を搭載した機種がある。所定のソフトウェアを搭載した機器の場合、起動時間が長くなることがあるが、本発明を適用することで、これらのデジタル家電における起動時間を短縮できるようになる。

#### 【0136】

また、バッテリの寿命を延命化することが可能となる。従来の高速起動を実現させる方法として、CPUやメモリを省電力モードに移行させる方法があった。この方法では、省電力モードとは言え、電力は必要であり、バッテリで動く機器にとってはその消費電力は

50

無視できない。本発明を適用することで、不揮発メモリに起動イメージを保存することが可能となり、電源をRAMに供給したまま停止させる、いわゆるサスPEND（従来の省電力モードに対応）を使う必要がなくなる。よって、結果的に、バッテリ寿命を著しく伸ばすことができる。

#### 【0137】

さらに、家電製品の省エネルギー化を実現することが可能となる。テレビジョン受像器やハードディスクレコーダなどは一般的に起動が遅く、そのために「高速起動モード」なるモードを持つ機種も存在している。しかしながら、この「高速起動モード」は、家電製品を高速に起動させるため、常に電源を投入していることで、高速起動を実現している。そのため電力は電源投入時と同等に消費されている。

10

#### 【0138】

しかしながら、本発明を適用することで、起動時間を短くすることができるため、「高速起動モード」のときにかかる起動時間と同等、またはそれ以上に短い起動時間で起動させることができるようになり、「高速起動モード」を設ける必要がなくなる。したがって、「高速起動モード」のときに、常に電源を投入してなくてはならないといった状態をなくすことが可能となるため、結果として省エネルギー化を実現することが可能となる。

#### 【0139】

上記したコンピュータが実行するプログラムは、本明細書で説明する順序に沿って時系列に処理が行われるプログラムであっても良いし、並列に、あるいは呼び出しが行われたとき等の必要なタイミングで処理が行われるプログラムであっても良い。また、専用のハードウェアで構成することもできる。また、本明細書において、システムとは、複数の装置により構成される装置全体を表すものである。

20

#### 【0140】

なお、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

#### 【符号の説明】

#### 【0141】

100 ハードディスクレコーダ , 101 CPU , 102 RAM , 103

ROM , 104 不揮発メモリ , 105 MPEGエンコード・デコード部 , 10

6 チューナ , 107 HDDインターフェース , 108 HDD , 109 I /

O部 , 110 起動モード切替部

30

【図1】

【図2】

【図3】

図3

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

図9

(7-3)

【図10】

図10

(7-4)

【図11】

図11

---

フロントページの続き

(56)参考文献 国際公開第2006 / 107095 (WO , A1 )

特開2005 - 316809 (JP , A)

特開2007 - 334383 (JP , A)

特開2006 - 202252 (JP , A)

特開2005 - 149225 (JP , A)

高橋 雅彦 , Embedded Optimization (1) Fast Booting , 第6回CELFテクニカルジャンボリー ,

2006年 1月20日 , pp.2-11 , U R L , <http://elinux.org/images/2/2c/Fastbooting-jpn20060120.pdf>

内田 泰 , 機器設計の勘所 デジタル家電の“瞬間起動”技術 Linux搭載機器でハイバネーション , 日経エレクトロニクス , 日経BP社 , 2008年 6月 2日 , 第979号 , pp.128-1

40

(58)調査した分野(Int.Cl. , DB名)

G 06 F 9 / 445

G 06 F 9 / 54

G 06 F 12 / 08 - 12 / 10