**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

**(51) Int. Cl.<sup>6</sup>**

**H01L 45/00**

**(45) 공고일자** 2003년07월16일

**(11) 등록번호** 10-0379322

**(24) 등록일자** 2003년03월27일

|             |                                                                                                                                                        |             |                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|

| (21) 출원번호   | 10-1998-0700584                                                                                                                                        | (65) 공개번호   | 특 1999-0035923 |

| (22) 출원일자   | 1998년01월24일                                                                                                                                            | (43) 공개일자   | 1999년05월25일    |

| 번역문제출일자     | 1998년01월24일                                                                                                                                            |             |                |

| (86) 국제출원번호 | PCT/US1996/12013                                                                                                                                       | (87) 국제공개번호 | WO 1997/05665  |

| (86) 국제출원일자 | 1996년07월19일                                                                                                                                            | (87) 국제공개일자 | 1997년02월13일    |

| (81) 지정국    | 국내특허 : 아일랜드 오스트레일리아 브라질 캐나다 일본 대한민국 멕시코 노르웨이 싱가포르 EA 유라시아특허 : 러시아<br>EP 유럽특허 : 오스트리아 벨기에 스위스 리히텐슈타인 독일 덴마크 스페인 프랑스 영국 그리스 이탈리아 룩셈부르크 모나코 네덜란드 포르투칼 핀란드 |             |                |

(30) 우선권주장 08/506630 1995년07월25일 미국(US)

(73) 특허권자 에너지 컨버전 디바이시즈, 아이엔씨.

미합중국, 48309 미시간, 로체스터 힐스, 워터부 드라이브2956

(72) 발명자 클러시, 패트릭 제이.

미국, 미시간 48360, 레이크 오리온, 766 카밀라 스트랜드, 데이비드 에이.

미국, 미시간 48301, 오클랜드 카운티, 블룸필드 타운십, 5611 프라이어리 레인

오브신스키, 스탠포드 알.

미국, 미시간 48013, 블룸필드 힐즈, 2700 스쿼럴 로드

(74) 대리인 목영동

**심사관 : 김동연**

**(54) 전기적으로 소거 가능하고 직접 오버라이트 가능한 멀티비트 단일셀 메모리 소자 및 이로부터 제조되는 어레이**

**영세서**

**관련 출원 정보**

<1> 본 출원은 1995년 3월 19일자 출원된 미국 특허 출원 제 08/423,484 호의 일부계속 출원으로, 이 출원은 현재 미국 특허 제 5,414,271 호인 1991년 11월 7일자 출원된 미국 특허 출원 제 07/789,234 호의 일부계속출원이며, 이 출원은 현재 미국 특허 제 5,335,219 호인 1991년 9월 30일자 출원된 미국 특허 출원 제 07/768,139 호의 일부계속출원이며, 현재 미국 특허 제 5,296,716 호인 1991년 8월 19일자 출원된 미국 특허 출원 제 07/747,053 호의 일부계속출원으로, 이 출원 각각은 현재 미국 특허 제 5,166,758 호인 1991년 1월 18일자 출원된 미국 특허 출원 제 07/642,984 호의 일부 계속 출원이다.

**기술분야**

**발명의 분야**

<4> 본 발명은 일반적으로 유일하게 설계된 고체, 전기·광학적으로 작동되는, 직접 오버라이트 가능한, 저 에너지, 매우 빠른 스위칭, 불휘발성, 아날로그 및 멀티레벨의 단일 셀 작동 메모리 소자에 관한 것이며, 이 소자들로 부터 제조되는 고밀도의 전기적 메모리 어레이에 관한 것이다. 보다 구체적으로는, 본 발명은 메모리 소자의 구성 요소인 점점 층에 대한 새로운 화학 조성물에 관한 것이다.

**배경기술**

**배경 및 선행 기술**

<5> Ovonic EEPROM은 신규성, 독점성, 고성능성, 불휘발성 있는 박막의 전자 메모리 디바이스이다. 이의 장점은 데이터의 불휘발성 저장 및 고비트 밀도의 가능성을 포함하여, 결과적으로 작은 풋프린트 (footprinting)와 간단한 2 단자 디바이스 구조, 간 프로그래밍 사이클 수명, 낮은 프로그래밍 에너지 및 고 속도로 인해 비용이 낮다. Ovonic EEPROM은 아날로그 및 디지털 형식의 정보 저장이 가능하다. 디지털 저장은 2 진화 ( 메모리 셀당 1 비트 ) 또는 다중 상태 ( 셀당 다중 비트 )일 수 있다. 두 디지털 모두 간의 전환에는 최소의 변경만이 필요하다. 본 발명에 있어서, 용어 "메모리 소자" 및 "제어 소자"는 동의어로 사용될 것이다.

<7> 초기의 전기적 위상 메모리

<8> 전자 메모리에 사용되는 전기적으로 기록 및 소거 가능한 위상 변경 재료 ( 예컨대, 일반적인 비 결정 상태와 결정 상태간에 전기적으로 전환될 수 있는 재료 )를 이용하는 일반적인 개념은 Ovshinsky에게 허여된 1966년 9월 6일자 미국 특허 제 3,271,591호 및 Ovshinsky에게 허여된 1970년 9월 22일자 미국 특허 제 3,530,441호 등에 개시되어 있는 바와같이 당해 기술 분야에 공지되어 있으며, 상기 양 특허는 본 발명과 동일한 양수인에게 양도되고 본원에 참고로 반영되어 있다 ( 이후 "Ovshinsky 특허" 라 칭함 ).

<9> Ovshinsky 특허에 개시된 바와같이, 이와같은 위상 변경 재료는 완전 비결정과 완전 결정 사이의 전체 스펙트럼에 걸쳐 일반적인 비결정과 결정 국부 배열의 구조적 상태간에 또는 국부 배열의 서로다른 검출가능한 상태간에 전기적으로 전환될 수 있다. 즉, Ovshinsky 특허에서는, 상기 재료의 전기적 전환은 완전한 비결정과 완전한 결정 상태간에 발생하는 것을 요하는 것이 아니라 완전한 비결정과 완전한 결정 상태사이의 스펙트럼을 측정하는 국부 배열의 다수 상태로 표시되는 "그레이 스케일 ( gray scale )"을 제공하도록 국부 배열의 변경을 반영하는 증가적 단계에 있을 수 있다는 것이다. Ovshinsky 특허에서 기술된 초기의 재료는 필요한 경우 일반적인 비결정과 결정 국부 배열의 두 구조적 상태사이에서 전환되어 엔코딩된 2진 정보의 단일 비트의 저장 및 검색할 수 있다. 후속적인 전기 고체 메모리 뿐만 아니라 Ovshinsky 특허에서 기술된 전기적으로 소거 가능한 위상 변경 메모리는 많은 한계가 있었다 : ( i ) 비교적 느린 ( 현재 표준을 기준으로 ) 전기적 전환 속도, 특히 보다 큰 국부 배열의 방향으로 ( 결정화를 증가시키는 방향으로 ) 전환되는 경우 ; ( ii ) 국부 배열의 검출가능한 변경을 초기화하는데 필요한 비교적 높은 입력 에너지 요건 ; 및 ( iii ) 저장된 정보의 메모리 단위 당 비교적 높은 비용 ( 특히 현행 하드 디스크 드라이브 매체와 비교하여 ).

<10> 이러한 한계들 중 가장 중요한 것은 국부 배열의 검출가능한 변경을 초기화하기 위해 칼코겐 재료의 화학적 및/또는 전자적 결합 구조의 검출가능한 변경을 얻는데 요구되는 비교적 높은 에너지이다. Ovshinsky 특허에서 기술된 전기 메모리 재료의 전환 시간이 또한 중요했다. 이 재료들은 설정 시간 ( 재료를 비결정으로 부터 결정 상태로 전환시키는데 요구되는 시간 )에 대해 수 밀리 초, 리셋 시간 ( 재료를 결정 상태로 부터 다시 비결정 상태로 전환시키는데 요구되는 시간 )에 대해 대략 마이크로 초의 범위내의 시간을 요했던 것이 전형적이다. 이러한 재료들을 전환시키는데 요구되는 전기 에너지는 대략 마이크로 주울의 범위내에서 측정되었던 것이 전형적이다.

<11> 이러한 에너지의 양은 메모리 셀의 행과 열의 고체 매트릭스내에 있는 메모리 소자 각각에 전달되어야 한다는 것이 주목된다. 이러한 높은 에너지 레벨은 어드레스 라인에 대한 그리고 각 개별 메모리 소자와 연관된 셀 분리/어드레스 디바이스에 대한 고 전류 전달 요구으로 변화된다. 이 에너지 요구를 고려할 때, 당업자의 메모리 셀 분리 소자의 선택은 매우 큰 단일 결정 다이오드 또는 트랜지스터 분리 디바이스로 국한되는데, 이 디바이스는 마이크론 규모의 리소그래피의 사용 결과로 메모리 소자의 고 실장 밀도를 불가능하게 한다. 따라서, 이 재료로 이루어진 매트릭스 어레이의 낮은 비트 밀도는 저장된 정보의 메모리 단위 당 높은 비용을 초래한다.

<12> 아키브 불휘발성 대용량 메모리와 고속 휘발성 시스템 메모리 간의 가격과 성능의 차를 효과적으로 줍힘으로써, 본 발명의 메모리 소자는 신규한 비계층적 " 범용 메모리 시스템 "을 만들어낼 수 있는 능력을 지닌다. 필수적으로 시스템내의 모든 메모리는 낮은 비용, 아키브 및 고속일 수 있다. 본래의 Ovshinsky식 위상 변경 전기 메모리와 비교하여, 본원에서 설명된 메모리 재료는 6배 이상 크기의 고속 프로그래밍 시간 ( 30 나노초 미만 )을 제공하고 입증된 장기간의 안정성과 주기성 (  $10 \times 10^{12}$  주기 이상 )으로 매우 낮은 프로그래밍 에너지 ( 0.1 내지 2 나노 주울 미만 )를 사용한다. 또한, 실험 결과는 소자 크기의 부가적인 감소가 전환 속도와 사이클 수명을 증가시킬 수 있음을 나타낸다.

<13> 최근 개발된 메모리 디바이스는 금속 미결정 실리콘 금속 ( metal - amorphous silicon - metal ; MSM ) 전기 메모리 스위치이다. Journal of Non - Crystalline Solids, 115 ( 1989 ), PP. 168 - 70 Rose 등의 " Amorphous Silicon Analogue Memory Devices " 및 1991년 4월 8일자 Physical Review Letters, Vol66, No.14, PP. 1989 - 21 Hajto 등의 " Quantized Electron Transport in Amorphous - Silicon Memory Structures "를 참조. 이 MSM 스위치는 P형 비결정 실리콘 ( a - si ) 박막의 어느 한 측면상에 특정 선택된 금속 접점을 데포지트하여 제조된다. 금속 접점 재료의 선택의 중요성은 이후에 설명될 것이다. MSM 메모리 스위치는 1 - 5 볼트의 저압 펄스에 대해 비교적 빠른 ( 10 - 100 ns ) 아날로그 스위칭 동작을 보여줌으로써, 저항이 불휘발성 방식으로 설정될 수 있는 대략  $10^3$  내지  $10^6$  오옴의 저항 범위를 제공하는 것으로 설명된다. 당해 기술 분야에서 당업자에 명백한 바와같이, 본 발명의 메모리 소자의 전기적 스위칭 특성과 유사한 전기적 스위칭 특성 ( 예컨대, 에너지 및 결과적인 디바이스 저항 )을 보여주지만, Rose 등과 Hajto 등의 MSM 메모리 스위치는 이들간에 실제 중대한 작동상의 차이점이 존재한다.

<14> 가장 중대한 전기적 스위칭 차이점은 MSM 메모리 스위치가 직접 오버라이트될 수 없는 능력에 있다. 즉, MSM 스위치는 아날로그 저항 범위내의 임의 저항으로 부터 우선적으로 소거되지 않는 ( 특정 개시 저항 또는 " 개시 상태 "로 설정된 ) 상기 범위내의 기타 다른 저항으로 직접 양방향으로 변조될 수 없다. 보다 구체적으로, MSM 스위치는 이 스위치가 아날로그 범위내의 또 다른 저항값으로 설정될 수 있기 전에 고 저항 상태 ( 소거상태 )로 우선적으로 설정되어야 한다. 이와 대조적으로, 본 발명의 메모리 소자는 범위내의 또 다른 저항으로 설정되기 전에 이레이저 ( erasure )를 요하지 않는다 : 예컨대, 상기 소자는 직접 오버라이트 가능하다.

<15> Rose 등과 Hajto 등의 MSM 메모리 스위치와 본 발명의 전기 메모리 소자 사이에 존재하는 전기적 스위칭 특성의 또다른 중대한 차이점은 MSM 스위치의 바이풀라 동작이다. Rose 등이 개시하는 바와같이, MSM 스위치는 기록하는데 사용되는 펄스로부터 반대 극성의 전기 펄스를 사용하여 소거되어야 한다. 중대한 바로는, 이 반대 극성의 인가된 펄스는 본 메모리 소자가 디지털 또는 아날로그 스위칭 어느것에 사용되더라도 본 발명의 메모리 소자에 의해 요구되지 않는다.

&lt;16&gt;

MSM 스위치와 본 발명의 메모리 소자 간의 전기적 스위칭 특성의 이러한 차이점은 소자가 제조되는 재료만의 차이점 이상에 기인한다. 이러한 차이점은 두 디바이스 동작의 물리적 현상을 특징으로 하는 스위칭 기구의 기본적인 차이점을 나타낸다. 위에서 언급되고 전기한 내용에 개시된 바와같이, MSM 메모리 스위치의 전기적 스위칭 특성은 접점이 제조되는 특정 금속(들)에 상당히 좌우된다. 이는, 적어도 하나의 접점으로부터의 금속이 스위치 본체의 구성 부분내로 전달되고 이것으로 형성되는 매우 높은 에너지 "성형" 공정을 MSM 스위치가 요구하기 때문이다. 이 공정에서, 복수개 (Rose 등의 논문의 도 1에서 적어도 15개)의 점진적 상승하는 300 나노초, 5-15 볼트 펄스가 스위치를 형성하도록 사용된다. Rose 등은 "디바이스의 X 선 마이크로분석 연구가 실행되어 왔으며, 상부 전극 재료는 a-Si의 필라멘트 영역내에 삽입되어 있는 것으로 밝혀졌다"고 진술한다. 이것이 제시하는 바는 "상부 금속이 필라멘트내에 분배되고 스위치 메카니즘의 역할을 할 수 있다. …"는 것이다. Rose 등은 유용한 저항의 동적 범위가 상부 전극 접점이 제조되는 금속에 의해 결정된다는 것을 또한 명확히 밝혀냈다. Rose 등이 진술한 바와같이, 범위값은 상부 접점에 완전히 (원문 그대로) 종속적이며, 하부 금속화 (원문 그대로)에 완전히 독립적임이 밝혀졌는, 예컨대 Cr 상부 전극 디바이스는 항상 디지털이고 V 상부 전극 디바이스는 하부 전극에 관계없이 항상 아날로그이다. 전기적 스위칭이 발생하는 곳은 금속 필라멘트 영역내에 있으며; 금속이 a-Si 내로 대량 이동하지 않고서는 스위칭은 존재하지 않는다. - Hajto 등의 논문을 참조. 이와 완전히 대조적으로, 본 발명의 메모리 소자는 고속, 저에너지, 아날로그, 직접적인 오버라이트, 메모리 스위칭을 성취하는데 박막 메모리 소자 내로의 접점 재료의 이동을 요하지 않는다. 사실상, 본 발명의 메모리 소자의 제조에서, 어느 한 전극으로부터 활성 칼코겐 재료내로 금속이 확산되는 것을 방지하는데 상당한 주의가 필요하다.

&lt;17&gt;

MSM 메모리 스위치는 자유 전하 집중 변조기로 간주되지 않는다. 상기 스위치는 변조된 스위치가 전류의 흐름을 제어하는데 사용되는 것과 상당히 동일한 방식으로 저항성의 범위를 얻기위해 비결정성 실리콘 재료를 통한 필라멘트 금속 경로의 형성에 의존한다. 직경이 저항성을 변경시키도록 증가 또는 감소될 수 있는 여과 경로가 설정된다. Fermi 레벨 위치의 어떠한 이동도 스위칭 공정에 포함되지 않는다. 반도체 재료의 활성 변화도 동작을 설명하는데 상기될 필요가 없다. 고립쌍의 비결합 전자의 원자 크기 이동도 존재하지 않는다. 결정체의 크기와 표면 - 부피 비는 중요하지 않다. 그러나 가장 중요한 것은, Rose 등과 Hajto 등이 메모리 재료의 셀내에 저장된 정보를 직접 오버라이트하는 것이 중요하다. MSM 스위치는 새로운 정보가 기록될 수 있기 전에 저장된 정보가 소거되는 것을 요한다.

&lt;18&gt;

본 발명에 앞서 개발된 어떠한 고체 메모리 시스템도 비싸지 않았고; 쉽게 제조가능하고; 불휘발성; 낮은 입력 에너지를 사용하여 전기적으로 기록가능하고 직접 소거가능 (오버라이트가능)하며; 단일 셀내에 다중 비트 저장 가능 (그레이 스케일을 지원)하고; 매우 높은 실장 밀도가 가능하다. 공지된 메모리 시스템의 모든 결함을 해결하기 때문에, 아래에 설명되는 메모리 시스템은 현재 시판중인 모든 유형의 컴퓨터 메모리를 보편적으로 대체하면서 즉시 폭넓게 사용될 것이다. 본 발명의 설계 및 제조에서 중요하게 고려할 것은 금속 전극 재료가 칼코겐 메모리 재료내로 확산 및 전자이동하는 것을 방지하는 것이라는 사실은 초기에 언급하였다. Ovonic EEPROM의 앞선 실시예들은 칼코겐 메모리 재료의 상부 및 하부에 인접 대포지트된 탄소의 두 박막층을 포함하였다. 탄소에 의한 중요한 역할은 이물질이 칼코겐 내로 들어가는 것을 방지하는 확산 장벽의 역할이다. 양호한 확산 장벽의 특성을 갖는 반면, 탄소는 불운하게도 어떠한 반도체 제조 기술에서 재료로 사용되는 경우 몇 가지 문제점들이 존재한다. 예를들면, 스퍼터 데포지션 공정 동안 탄소 타겟을 사용하는 경우, 탄소 미립자는 디바이스 및 장치의 오염원이 될 수 있다. 물론, 탄소가 건식 레지스트스트립 공정을 받는 반도체 디바이스의 일부인 경우, 노출된 탄소층은 포토레지스트 재료를 제거하는데 사용되는 동일한 산소 플라즈마에 의해 제거될 수 있으며, 공정을 부적합하게 만든다. 이와같은 문제들로 인해, 탄소는 디바이스는 제조에 대한 양호한 재료로서 반도체 산업에 그다지 적당하지 않다. 그러므로, 적당한 Ovonic EEPROM 디바이스 동작에 대한 필수적 특징을 지니면서 기술 상태의 반도체 처리 기술과 보다 더 호환될 수 있는 적당한 대체 재료를 모색할 필요성이 있다.

&lt;19&gt;

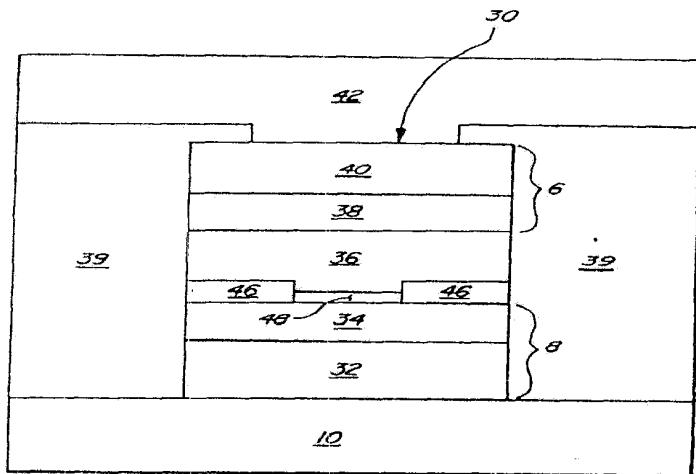

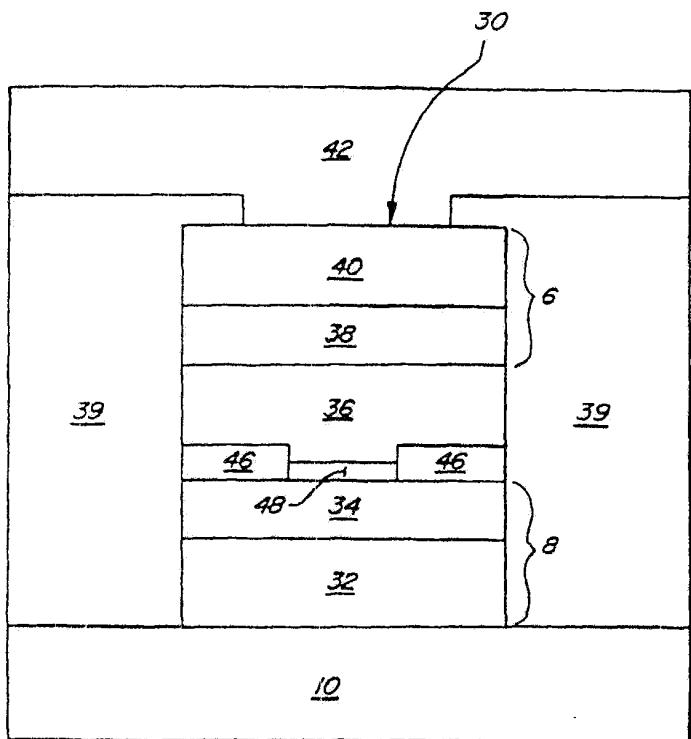

### 발명의 요약

&lt;20&gt;

근복적으로, 새로운 고체, 직접 오버라이트 가능, 전자식, 불휘발성, 고밀도, 낮은 가격, 쉽게 제조가능한 단일 셀 메모리 소자로서, 감소된 스위칭 전류 요건 및 저장된 데이터의 보다 큰 열적 안정성을 지니는 메모리 소자가 본원에 개시되어 있다. 이 메모리 소자는 상당히 감소된 에너지 레벨에서 이전의 칼코겐 메모리 재료보다 더 높은 스위칭 속도를 보여주는 유일한 등급의 칼코겐 메모리 재료를 이용한다. 본 발명의 메모리 소자 및 어레이를 구성하는 신규한 메모리 재료는 가변 펄스 전류, 전압 및 지속기간의 전기적 입력 신호에 의해 선택적·반복적으로 설정될 수 있는 국부 원자 및/또는 전자 배열의 안정하고 불휘발성의 검출가능한 구조를 무엇보다도 특징으로 한다. 따라서, 본 발명의 메모리 디바이스는 적어도 두개의 안정한 세팅에서 제공하도록 서로다른 국부 배열의 원자 및/또는 전자 구조 간에 스위칭 가능하다. 본원에 개시된 메모리 소자에 의해 가능한 스위칭 속도 및 스위칭 에너지에 대한 향상된 정도는 단지 자연적으로 증가되는 것이 아니라, 오히려 가능한 이전의 개념을 넘어 근본적인 향상을 나타낸다.

&lt;21&gt;

본원에 설명된 메모리 재료에 대한 이론들이 현재 조사되고 있지만, 이제껏 제시된 어떠한 이론도 관찰된 모든 특이한 전기적 스위칭 동작을 설명하지 못한다. 구체적으로, 본 반도체 재료는 피코주율 에너지의 입력으로 나노초 시간 주기에서 전기적으로 검출가능한 수많은 상태간에 스위칭될 수 있다. 본 메모리 재료는 실제 불휘발성이며 주기적인 리프레시 신호에 대한 필요성 없이 메모리 셀에 의해 저장되는 정보를 유지하는 동안 거의 무기한적으로 사이클링 (기록 및 재기록)될 수 있다. 본 메모리 재료는 직접 오버라이트가능하여 기타 메모리 소자에 저장된 정보는 주어진 세트의 메모리 소자에 저장된 정보를 변경시키기 위해 (강유전성 및 기타 플래시 저장 시스템에서 요구되는 바와같이) 소거될 필요가 없다.

&lt;22&gt;

본 발명의 한 실시예는 전기적으로 동작되고 직접 오버라이트가능한 다중 비트 단일 셀 메모리 소자를 포함한다. 메모리 소자는 단일 셀의 메모리 소자를 한정하는 메모리 재료의 부피를 포함한다. 메모리 재료는 (1) 전기 저항값의 큰 동적 범위; (2) 상기 단일 셀에 멀티비트 저장 능력을 제공하도록 선택된 전기적 입력 신호에 응답하여 상기 동적 범위내의 복수개의 저항값 중 하나로 설정될 수 있는 능력; 및 (3) 적어도 필라멘트 부분이 재료의 이전 저항값에 관계없이 동적 범위내의 임의 저항값으로 선택된 전기 신호에 의해 설정되도록 하는 능력을 특징으로 한다.

<23> 메모리 소자는 동적 범위내의 선택된 저항값으로 메모리 재료를 설정하도록 전기적 입력 신호를 공급하는 두개의 이격 배치된 전기 접점을 또한 포함한다. 전기 접점총 각각은 메모리 재료에 인접 배치된 박막층을 포함한다. 적어도 하나의 인접 박막층은 B, C, N, O, AISi, P, S 및 훈합물이나 합금으로 이루어진 그룹으로부터 선택된 두개 이상의 원소와 함께 Ti, V, Cr, Zr, Nb, Mo, Hf, Ta, W 및 훈합물이나 합금으로 이루어진 그룹으로부터 선택된 하나 이상의 원소로 구성된다. 바람직하기로는, 적어도 하나의 인접 박막 접점총은 티타늄 카보니트리드 또는 티타늄 실리코니트리드로 구성된다.

<24> 이격 배치된 접점각각은 메모리 재료로 부터 이격 배치된 부가적인 박막층을 포함하는 것이 바람직하다. 이격된 박막층들은 Ti, W, Mo 및 훈합물이나 합금으로 이루어진 그룹으로부터 선택된 하나 이상의 원소로 구성된다. 바람직하기로는, 이격된 박막층 각각은 Ti 및 W로 구성된 합금이다.

<25> 본 발명의 기타 이점 및 뿐만 아니라 기타 실시예 및 특징들은 특히 첨부된 도면과 결부지어 이후에 나오는 본 발명의 상세한 설명으로부터 명백해질 것이다.

### 발명의 상세한 설명

<26> 폭넓은 등급의 칼코겐 재료로 부터 제조된 소거가능한 전기 메모리는 비결정 상태로 부터 결정 상태로 전환되는 재료로 위상 변경되도록 재료내의 어떠한 원자종의 이동에 의해 제공된 구조적 변경을 사용하였다. 예를들면, 황과 비소와 같은 대략 1 내지 2 퍼센트의 소량의 어떠한 기타 원소와 함께 대략 80 내지 85 % 텔루룸과 대략 15 % 게르마늄을 포함하는 것과 같은 텔루룸과 게르마늄으로 형성된 전기적으로 스위칭가능한 칼코겐 합금의 경우에서, 보다더 정렬된 또는 결정 상태는 메모리 재료의 스위칭 가능한 구멍내에 고전도성 결정 Te 필라멘트를 형성하는 것을 특징으로 하는 것이 전형적이다. 이와같은 선행 기술인 재료의 전형적인 조성물은  $Te_{81}Ge_{15}S_2As_2$  또는  $Te_{81}Ge_{15}S_2Sb_2$  등이다. Te가 결정 상태에서 고전도성이기 때문에, 매우 낮은 저항 상태는 보다더 정렬된 또는 결정 상태에서 Te 필라멘트를 통해 설정되었다 ; 이 저항은 덜 정렬된 또는 비결정 상태에서 포어 ( pore )의 저항보다 더 낮은 크기이다.

<27> 그렇지만, 결정 상태에서의 전도성 Te 필라멘트의 형성은 비결정 상태에서의 원자 구조로 부터 결정 Te 필라멘트 상태에서의 새로 국부적으로 집중된 원자 구조로 Te가 이동하는 것을 필요로 했다. 마찬가지로, 칼로겐 필라멘트 재료가 비결정 상태로 다시 스위칭된 경우, 결정 필라멘트로 촉진된 Te는 재료내에서 필라멘트내의 국부 집중된 형태로 부터 비결정 상태의 원자 구조로 다시 이동되도록 요구되었다. 비결정 상태와 결정 상태간의 원자이동, 확산 또는 재배열은 각 경우에서 이동에 적합하도록 충분한 길이의 유지 또는 체류 시간을 필요로 하여 요구되는 스위칭 시간에 에너지를 크게 하였다.

<28> 본 발명자들은 새로운 등급의 칼코겐 반도체 재료에 기초한 전기적으로 소거가능하고 직접 오버라이트 가능한 메모리의 근본적으로 다른 유형에 대한 필요한 스위칭 시간과 에너지 입력 모두의 현저한 감소를 밝혀냈다. 더욱이, 칼코겐 재료는 현저히 빠른 속도에서 현저히 낮은 에너지 입력을 갖는 안정한 상태의 폭넓은 동적 범위내에서 스위칭을 제공하여 이 새로 발견된 등급의 재료는 향상된 전기 메모리 소자를 제조하는데 사용될 수 있다.

<29> 구체적으로, 메모리 재료는 피코주율의 입력으로 나노초 시간 주기 ( 그렇지만 최소 스위칭 속도 및 최소 에너지 요건은 전기 메모리 1 나노초 만큼 짧은 프로그래밍 펄스로 변조 ( 최적화는 아니지만 ) 될 수 있음을 본 출원의 제출에 대한 실험 데이터가 보여주었음을 아직 확증되지 않았다 )에서 가변 저항의 전기적으로 겸출가능한 상태간에 스위칭될 수 있다. 이 메모리 재료는 불휘발성이며 주기적인 리프레시 신호없이 ( 선택된 모차내에 ) 메모리 셀에 의해 저장된 정보를 유지한다. 메모리 용도에 지금까지 상술된 기타 많은 반도체 재료 및 시스템과 대조적으로, 본 발명의 반도체 메모리 재료 및 시스템은 개별의 메모리 소자들이 저장된 정보를 변경하기 위해 소거 ( 명확한 개시점으로 설정 )될 필요가 없도록 직접 오버라이트할 수 있다. 서로 다른 임의의 저항값으로의 상당히 빠르고 낮은 에너지 스위칭은 스위칭 재료의 큰 원자 배열에 대한 필요성 없이 상기 스위칭이 발생한다는 사실에 기인할 수 있다.

<30> 메모리 재료는 복수개의 구성 원자 원소들로 부터 형성되고 이들 각각은 전체의 메모리 부피에 존재한다. 복수개의 구성 원자 원소들은 적어도 칼코겐 원소를 포함하는 것이 바람직하며 적어도 하나의 전이 금속 원소를 포함할 수 있다. 본원에 사용되는 용어 " 전이 금속 "은 원소 ( 21 - 30, 39 - 48, 57 및 72 - 80 )들을 포함한다. 보다 바람직하기로는, 메모리 재료의 부피를 형성하는 복수개의 구성 원자 원소들은 Te, Se, Ge, Sb, Bi, Pb, Sn, As, S, Si, P, O 및 훈합물 또는 합금으로 이루어진 그룹으로부터 선택된 원소들을 포함한다. 보다 바람직하기로는 전이 금속은 Cr, Fe, Ni 및 훈합물 또는 합금을 포함하며 칼코겐 원소는 Te 및 Se를 포함한다. 가장 바람직하기로는 전이 금속은 Ni이다. 이와같은 다원소 시스템의 구체적인 실례들은 Ni 및/또는 Se가 있거나 없는 Te : Ge : Sb에 대하여 이후에 설명된다.

<31> 프로그래밍이 달성되는 방법의 설명에 관계없이, 본 발명은 이전에는 결코 단일 메모리 소자에서 얻을 수 없는 귀중한 전기적 스위칭 특성의 결합을 제공한다.

<32> 메모리 디바이스를 제조하는데 사용되는 특정한 반도체 합금은 " 고립쌍 " 전자의 존재에 특히 주목되는 칼코겐 원소를 포함한다. 따라서 유용한 화학 결합 구조에서 이러한 고립쌍 전자의 효과를 논하는 것은 필수적이다. 간단히 말해서, 고립쌍은 결합에 보통 관계되지 않는 원자의 원자가 겹질내의 원자쌍이다. 이와같은 고립쌍 전자는 구조적 및 화학적으로 모두 중요하다. 이들은 결합 구조에 관계되는 이웃 전자쌍 뿐만 아니라 기타다른 고립쌍에 강한 반발력을 가하여 분자 및 결정 구조의 모양에 영향을 미친다. 고립쌍 전자가 2차 핵에 의해 결합 영역내로 결속되지 않기 때문에, 이들은 영향을 받을 수 있고 낮은 에너지 전자 전이를 초래한다. 우선적으로 Ovshinsky가 지적한 바와같이, 고립쌍은 1과 3 중심 결합을 가질 수 있다 : kastner, Adler 및 Fritsche에 의해 입증된 바와같이, 원자쌍은 원자가 변경 쌍을 갖는다.

<33> 구체적으로, 본원에 설명된 텔루룸 합금은 고립쌍 상태로 이루어진 가전자대를 갖는다. 네개 (4)의 P 셀 전자들이 Te에 존재하고 Te 원자가 P 셀내의 이 결합 전자 중 두개에 의해 화학 결합되기 때문에, 다른 두개의 외각 전자 ( 고립쌍 )는 결합 목적으로 이용되지 않고 따라서 실질적으로 시스템의 원자 에너지를 변경시키지 않는다. 이러한 점에서, 가장 높은 충만된 분자 오비탈은 고립쌍 전자를 포함하

는 오비탈이다. 이는 중요한 것으로, 그 이유는 텔루륨과 게르마늄 원자의 완전한 화학양론적 결정체에서, 결정체가 형성되는 격자내의 일부 내부적 스트레인의 인가시, 가전자대는 확장되고 존재하는 Fermi 레벨의 위치로 상향 이동할 수 있기 때문이다. 그렇지만, TeGe 결정체는 자연적으로 "자기 보상" 되는데, 즉 결정체는 Te가 풍부한 ( 대략 52 % Te 및 48 % Ge ) 조성물을 선택적으로 취한다. 화학양론적 결정체는 면 중심 입방체이다 ; 그렇지만, 최소량의 에너지를 부가하여, 결정체는 Ge 및/또는 Sb 원자가의 수를 증가시켜 능면체 격자를 취할 수 있다. 이것은 TeGe 합금내의 격자 스트레인을 감소시킬 수 있는 결정 격자 구조내의 원자가를 형성하고, 재료의 에너지 상태를 낮추며 가전자대로 Fermi 레벨을 이동시킨다.

<34> 도형을 얻을 목적으로 짧은 범위 국부 배열 모델의 상부에 국부 배열의 비결정 모델을 중첩하는 것이 필수적인 것은 아니고, 원자 행동을 완전히 예측 설명하지는 않지만, 이는 만족할만하다. 재료의 비결정 특성을 고려하면, 가전자대 테일내의 결합 상태의 밀도는 가전자대 에지에 인접한 상태로 가장 큰 반면, 포획된 전하 캐리어에 대한 재결합 중심의 깊이는 가전자대 에지로 부터 보다 이격된 상태로 더 깊다는 쟁이 주목된다. 이러한 깊은 트랩과 테일 상태의 존재는 Fermi 레벨 위치와 가전자대 에지 사이의 순간적 안정한 저항값을 설명할 수 있다. 이론에 관계없이, 완전히 결정체인 경우, 본 발명의 반도체 재료는 금속과 같은 도전성을 보여주는 축퇴된 반도체이다.

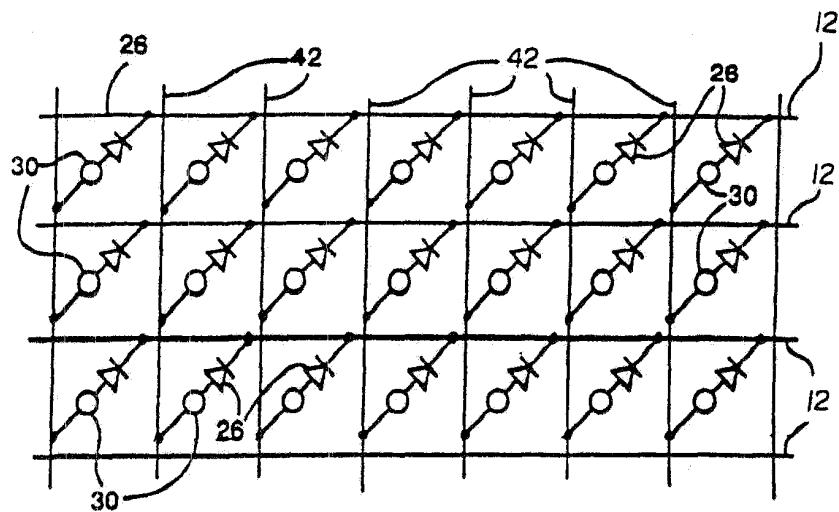

<35> 또한, 반도체 및 메모리 재료의 벌크내에 존재하는 결정의 크기는 비교적 작으며, 바람직하기로는 대략 2000 Å 미만이고 보다 바람직하기로는 대략 50 Å 및 500 Å 사이이며, 가장 바람직하기로는 대략 200 Å 내지 대략 400 Å 정도이라고 생각 된다. 더욱이, 이를 결정은, 상이한 저항 ( 도전율 )으로서 검출될 수 있는, 상기 재료의 여러 페르미 레벨 이치의 신속한 형성과 아울러, 상기 재료가 신뢰성 있고 반복적으로 설정될 수 있는 이와같은 검출가능한 저항값 사이의 전이에 대한 낮은 에너지 요구에 기여할 수 있는 비결정 표피에 의해 예워싸여져 있다고 생각된다.

<36> 또한, 본 발명의 미소결정 재료로 부터 제조되는 2 또는 3단자 반도체 디바이스의 스위칭 특성들의 변조는 반복 및 검출가능한 저항값이 초래될 수 있도록 제어될 수 있는 것으로 발견되어 졌다. 본 발명의 재료가 낮은 에너지 입력 신호에 의해 ( 페르미 레벨 위치에 의해 결정되는 ) 원하는 도전율로 신속히 설정되기 위하여, 단지 상기 재료가 상이한 도전율을 제외하고는 실질적으로 일정한 밴드갭에 의해 특징이 지워지는 최소한 2 개의 상이한 페르미 레벨 위치내에서 안정성 ( 또는 긴 수명의 준안정성 ) 이 있게 존재할 수 있는 것만이 필요한 것으로 발견되어 졌다.

<37> 상기에 주지된 바와같이, 또한 비교적 작은 결정 크기는 검출가능한 저항값들 사이의 신속한 전이에 기여할 수 있다고 생각된다.

<38> 본 발명의 반도체 재료들 중 한가지 특성은 체적당 보다 더 작은 결정의 형성을 향하는 경향이다. 본 발명을 구체화하는 대표적인 재료들의 가장 폭넓은 선호 범위의 결정 크기는 대략 2000 Å 보다 훨씬 좁고, 일반적으로는 선행 기술의 재료의 특성이었던 대략 2000 Å 내지 5000 Å의 범위보다 좁은 것으로 발견되어 졌다. 본원에서의 결정 크기는 결정이 구형이지 않은 부분에서의 직경과 등가인 결정의 직경, 또는 결정의 "특징 치수 ( characteristic dimension ) "의 직경으로서 정해져 있다.

<39> 본 발명의 기준을 만족시키는 TeGeSb 재료의 분류의 높은 저항 상태에서의 조성은 일반적으로 선행 기술의 전기적으로 소거가능한 메모리 재료에 존재하는 것에 비하여 실질적으로 감소된 Te의 농도에 의해 특징이 지워진다고 결정되어 졌다. 실질적으로 개선된 전기적 스위칭 성능 특성을 제공하는 한 조성에 있어서, 데포지트된 상태의 재료에서의 Te의 평균 농도는 70% 미만, 전형적으로는 대략 60% 미만, 일반적으로는 대략 23% 내지 대략 58% 만큼 적은 범위인 Te이었으며 가장 바람직하기로는 대략 40% 내지 58%의 Te이었다. Ge의 농도는 대략 5% 이상이었으며 대체로 50% 미만이 남아 있는 재료에서 평균적으로 대략 8% 내지 대략 30%의 범위에 있었다.

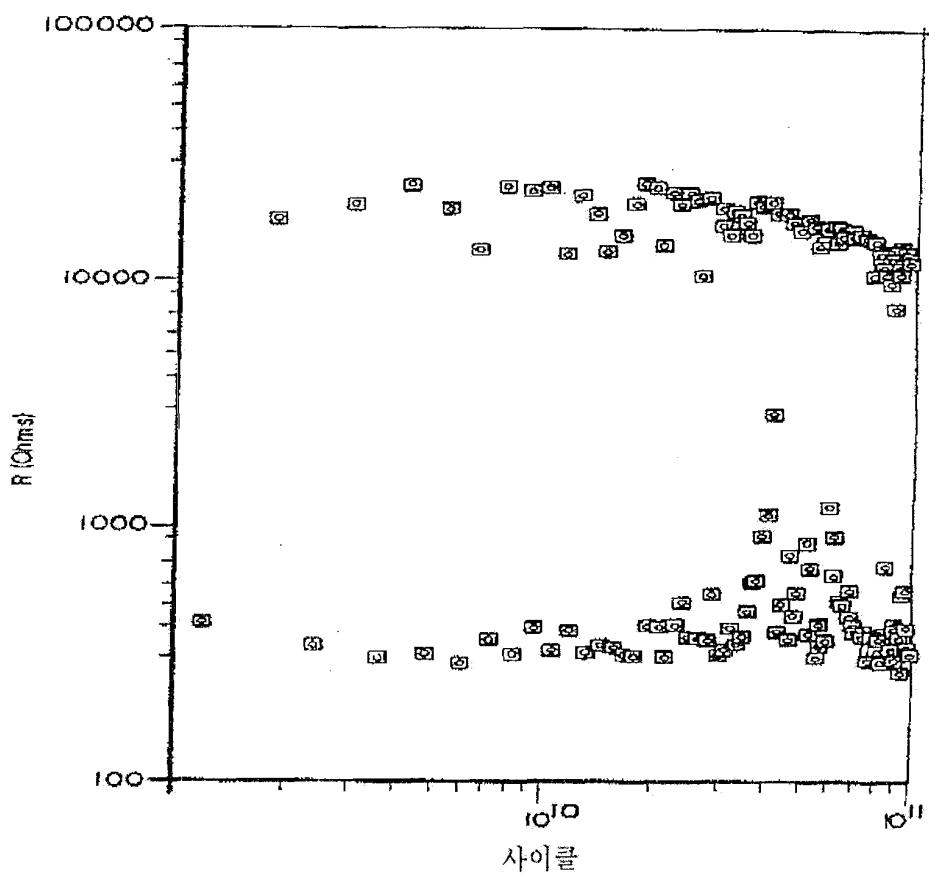

<40> 이러한 조성에서의 주 구성 성분의 잔류 성분은 Sb 이었다. 주어진 퍼센트는, 총합이 구성 성분의 원자의 100%를 이루는 원자 퍼센트이다. 따라서, 이러한 조성은  $Te_aGe_bSb_{100-(a+b)}$ 로서 특징이 지워질 수 있다. 이들의 3원 Te - Ge - Sb 합금은 보다 양호한 전기 특성을 지니는 부가적인 메모리 재료의 개발을 위한 유용한 출발 재료이다.

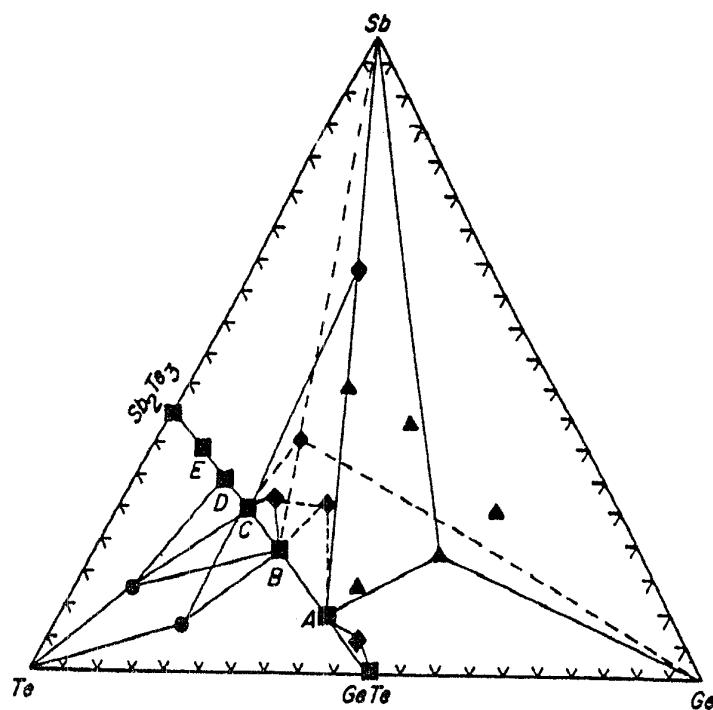

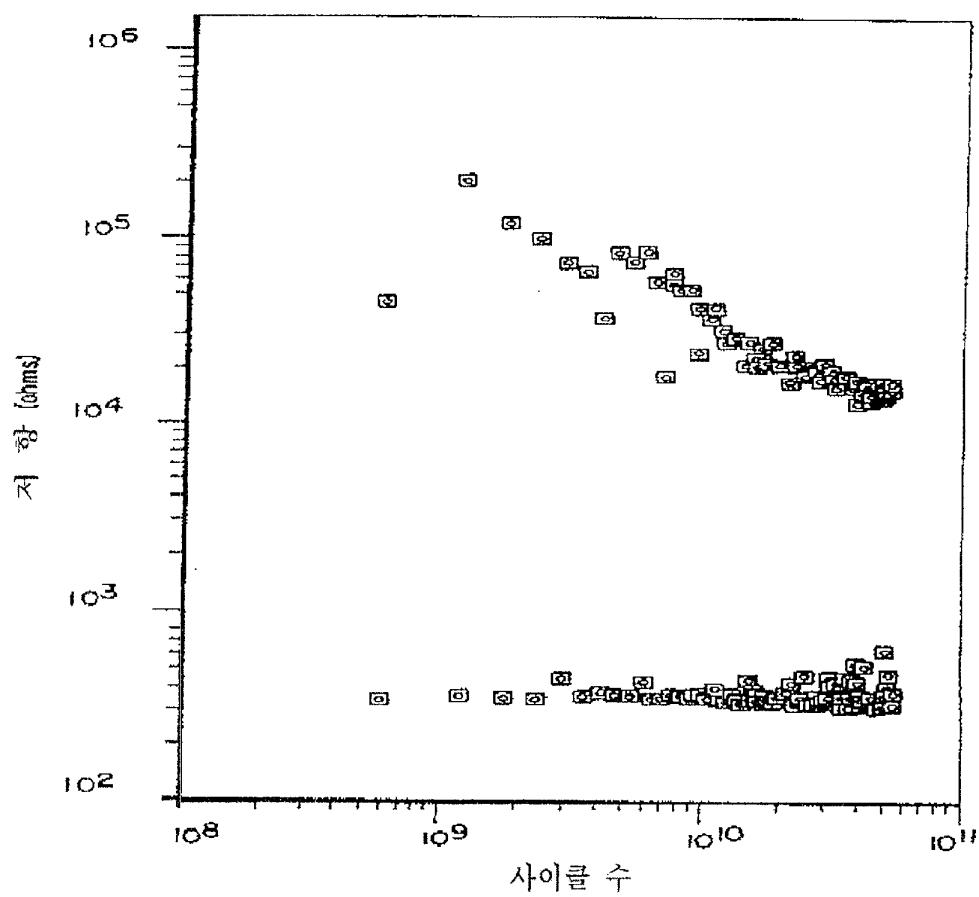

<41> 도 5에는 Te : Ge : Sb 계의 3원 도식이 도시되어 있다. 용해물은 Te, Ge 및 Sb의 여러 혼합물로부터 준비되었는데, 상기 용해물은 급속 응결에 따라 다양으로 분리된다. 이와 같이 급속 응결된 용해물의 분석은 ( 어느 하나의 급속 응결 용해물에 모두 존재하지 않는 ) 10개의 상이한 상들의 존재를 나타내었다. 이들 상은 Ge, Te 및 Sb 원소, GeTe 및  $Sb_2Te_3$  2원 화합물, 및 5 개의 상이한 3원 상이다. 3원상 모두의 원소 조성은 의사 2원 GeTe -  $Sb_2Te_3$  라인상에 위치하여 도 5에 도시된 3원 도식상에서 참조 문자 ( A, B, C, D, E )로 나타나 있다. 이들 5개의 3원상을 이루는 원소의 원자 비는 표 1에 기재되어 있다. 도 5의 보다 구체적인 설명은 이하에 제공되어 있다.

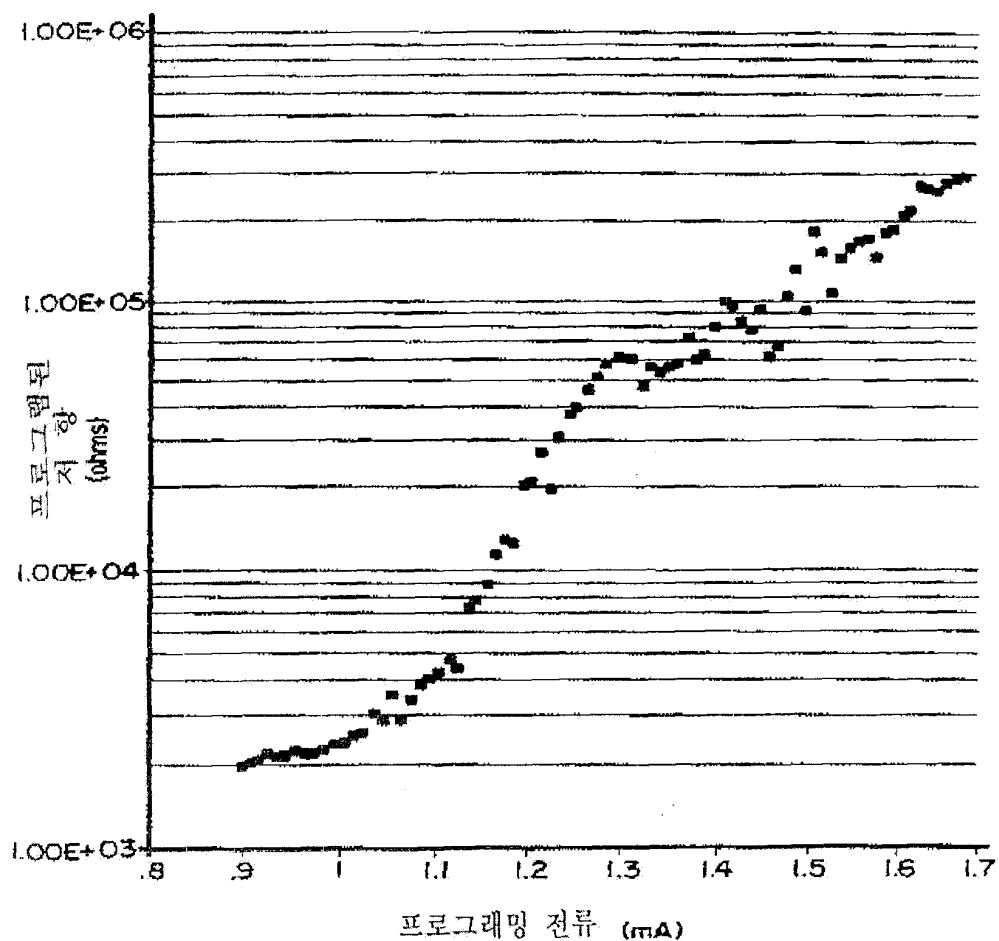

&lt;42&gt;

[표 1]

| TeGeSb 계의 관찰된 3 원 결정상 |         |         |         |

|-----------------------|---------|---------|---------|

| 지정                    | At % Ge | At % Sb | At % Te |

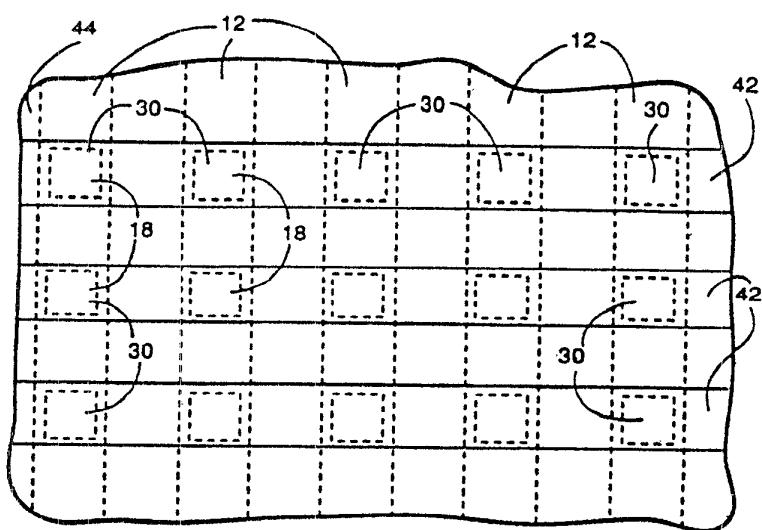

| A                     | 40      | 10      | 50      |

| B                     | 26      | 18      | 56      |

| C                     | 18      | 26      | 56      |

| D                     | 14      | 29      | 57      |

| E                     | 8       | 35      | 56      |

&lt;44&gt;

본 발명의 신규한 메모리 소자는 다양한 메모리 재료를 포함하고, 상기 메모리 재료는 최소한 하나의 칼코겐을 포함하는 것이 바람직스러우며 하나이상의 전이 금속을 포함할 수 있다. 전이 금속을 포함하는 메모리 재료는 Te - Ge - Sb 3 원계에서 원소적으로 변형된 형태의 메모리 재료이다. 즉 변형된 형태의 메모리 재료는 변형된 형태의 Te - Ge - Sb 메모리 합금을 구성한다. 이러한 원소적 변형은 Se와 같은 추가적인 칼코겐 원소를 지니는 이를 지니지 않은, 기초 Te - Ge - Sb 3원계 내로의 전이 금속의 조입에 의해 달성된다. 일반적으로, 원소적으로 변형된 메모리 재료는 2개의 카테고리에 속한다.

&lt;45&gt;

첫 번째 카테고리는, 총합이 구성원소의 100%를 이루는 원자 퍼센트로 첨자가 이루어지고 TM이 하나이상의 전이금속이며 a 및 b가 본원에 기재된 바와같이 기초 Te - Ge - Sb 3원계에 대한 것이고 c가 대략 90 및 대략 99.5% 사이에 있는 경우 비율이  $(Te_a Ge_b Sb_{100-(a+b)})_c$ 를 이루도록 Te, Ge, Sb 및 전이 금속을 포함하는 메모리 재료이다. 상기 전이 금속은 바람직하기로는 Cr, Fe, Ni 및 그들 합금의 혼합물을 포함할 수 있다. 이러한 계에 의해 포함되는 메모리 재료의 특정한 예들은  $(Te_{56} Ge_{22} Sb_{22})_{95}Ni_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}Ni_{10}$ ,  $(Te_{56} Ge_{22} Sb_{22})_{95}Cr_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}Cr_{10}$ ,  $(Te_{56} Ge_{22} Sb_{22})_{95}Fe_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}Fe_{10}$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}Ni_5Cr_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}NiFe_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}Cr_5Fe_5$  등을 포함한다.

&lt;46&gt;

두 번째 카테고리는, 총합이 구성원소의 100%를 이루는 원자 퍼센트로 첨자가 이루어지고 TM이 하나 이상의 전이금속이며, a 및 b가 본원에 기재된 바와 같이 기초 Te-Ge-Sb 3원계에 대한 것이고, c가 대략 80 및 대략 99% 사이에 있고, d는 대략 0.5에서 10% 사이에 있는 경우 비율이  $(Te_a Ge_b Sb_{100-(a+b)})_c$   $TM_c Sb_{100-(a+b)}$ 를 이루도록 Te, Ge, Sb 및 전이금속을 포함하는 메모리 재료이다. 상기 전이 금속은 바람직하기로는 Cr, Fe, Ni 및 그들 합금의 혼합물을 포함할 수 있다. 이러한 계에 의해 포함되는 메모리 재료의 특정한 예들은  $(Te_{56} Ge_{22} Sb_{22})_{90}Ni_5Se_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{80}Ni_{10}Se_{10}$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}Cr_5Se_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{80}Cr_{10}Se_{10}$ ,  $(Te_{56} Ge_{22} Sb_{22})_{90}Fe_5Se_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{80}Fe_{10}Se_{10}$ ,  $(Te_{56} Ge_{22} Sb_{22})_{85}Ni_5Cr_5Se_5$ ,  $(Te_{56} Ge_{22} Sb_{22})_{80}Ni_5Fe_5Se_{10}$ ,  $(Te_{56} Ge_{22} Sb_{22})_{85}Cr_5Fe_5Se_5$ , 등을 포함한다.

&lt;47&gt;

본원발명의 상기 메모리 소자는 상당한 비-휘발성 세트 저항치를 가진다. 그렇지만, 만약 본 메모리 소자의 저항치가 원래의 세트값으로부터 변동(drift)된다면, 이후에 기술될 "조성 변경 (compositional modification)"이 이러한 변동을 제거하기 위해 사용될 수 있다. 본명세서에서, "비-휘발성"이라는 용어는 세트 저항치가 기록상의 주기동안 실질적으로 일정하게 유지되는 조건을 의미한다. 물론, 소프트웨어(이후에 논의될 피드백 시스템을 포함)는 선택된 애러폭외의 "변동"이 절대적으로 일어나지 않도록 보증하기 위하여 사용될 수 있다. 메모리 소자의 저항 수치의 변동은, 방치될 경우, 정보의 그레이 스케일 저장을 방해하므로, 변동을 최소화하는 것이 바람직하다.

&lt;48&gt;

"조성 변경"은 여기서, 메모리 재료 체적의 조성을 변경하여, 실질적으로 안정한 저항치를 내는 모든 수단을 포함하며, 재료의 고유 저항성을 증가시키는 밴드 갭 확장 소자의 첨가를 포함한다. 조성 변경의 한가지 예는 두께에 대한 단계화된 조성 비동질물(graded compositional inhomogeneities)을 포함한다. 예를들면, 메모리 재료의 체적은 제 1 Te-Ge-Sb 합금에서부터 다른 조성의 제 2 Te-Ge-Sb 합금까지 단계화될 수 있다. 조성의 단계화는 세트저항 수치의 변동을 감소시키는 어떠한 형태라도 무방하다. 예를들면, 조성 단계화는 같은 합금 시스템의 제 1 및 제 2 합금에만 한정될 필요는 없다. 또한, 단계화는 2 이상의 합금으로써 실현될 수도 있다. 단계화는 균일하고 연속적일 수도 있고, 또는 불균일하고, 불연속적일 수도 있다. 저항치 변동을 감소시키는 결과를 낳는 조성 단계화의 특이적 예는 일정표면에서의  $Ge_{14}Sb_{29}Te_{57}$ 에서 반대 표면의  $Ge_{22}Sb_{22}Te_{56}$ 로의 균일하고 연속적인 단계화를 포함한다.

&lt;49&gt;

저항 변동을 감소시키는 조성 변경을 사용하는 또 다른 방법은 메모리 재료의 체적을 단층화(layering)하는 것이다. 즉, 메모리 재료의 체적은 서로다른 조성인 다수의 개별적인, 상대적 박막의 형태이다. 예를들면, 메모리 재료의 체적은 하나 또는 그 이상의 쌍을 포함하고, 각각의 층은 서로다른 Te-Ge-Sb 합금으로 형성된다. 역시, 단계화된 조성물의 경우와 마찬가지로, 실질적으로 감소된 저항치 변동을 가져오는 어떠한 단층의 조합도 사용될 수 있다. 상기 단층은 서로 유사한 두께일 수도 있고 다른

두께일 수도 있다. 어떠한 갯수의 단층도 사용될 수 있고, 같은 합금의 다수 단층도 메모리 재료의 체적에, 서로 인접하여 혹은 떨어져서 존재할 수 있다. 단층조성의 특이적 예는  $Ge_{14}Sb_{29}Te_5$  및  $Ge_{22}Sb_{22}Te_{56}$ 의 교대층을 포함하는 메모리 재료의 체적이다.

<50> 저항 변동의 감소를 위한 조성적 비동질성의 또 다른 형태는 조성적 단계화 및 조성별 단층화를 조합시킴으로써 달성된다. 더욱 특이적으로는, 상기한 조성 단계화는 상기한 어떠한 조성별 단층화와도 조합되어 메모리 재료의 안정한 체적을 형성한다. 이러한 조성을 사용하는 메모리 재료의 체적의 예시는 다음과 같다; (1)  $Ge_{22}Sb_{22}Te_{56}$ 에 연이은  $Ge_{14}Sb_{29}Te_{57}$  및  $Ge_{22}Sb_{22}Te_{56}$ 의 단계화된 조성물의 개별적 단층을 포함하는 메모리 재료의 체적 (2)  $Ge_{14}Sb_{29}Te_{57}$  및,  $Ge_{14}Sb_{29}Te_{57}$  및  $Ge_{22}Sb_{22}Te_{56}$ 의 단계화된 조성물의 별개의 단층을 포함하는 메모리 재료의 체적.

<51> 도 1에서는, 단일 결정 실리콘 반도체 웨이퍼(10) 상에 형성된 본 발명의 메모리 소자의 단면도가 도시되어 있다. 메모리 소자(30)는 메모리 재료(36) 및 전기적 입력신호를 메모리 재료에 공급하기 위한, 공간적으로 분리되어 배치된 한쌍의 접촉면(6, 8)을 포함한다.

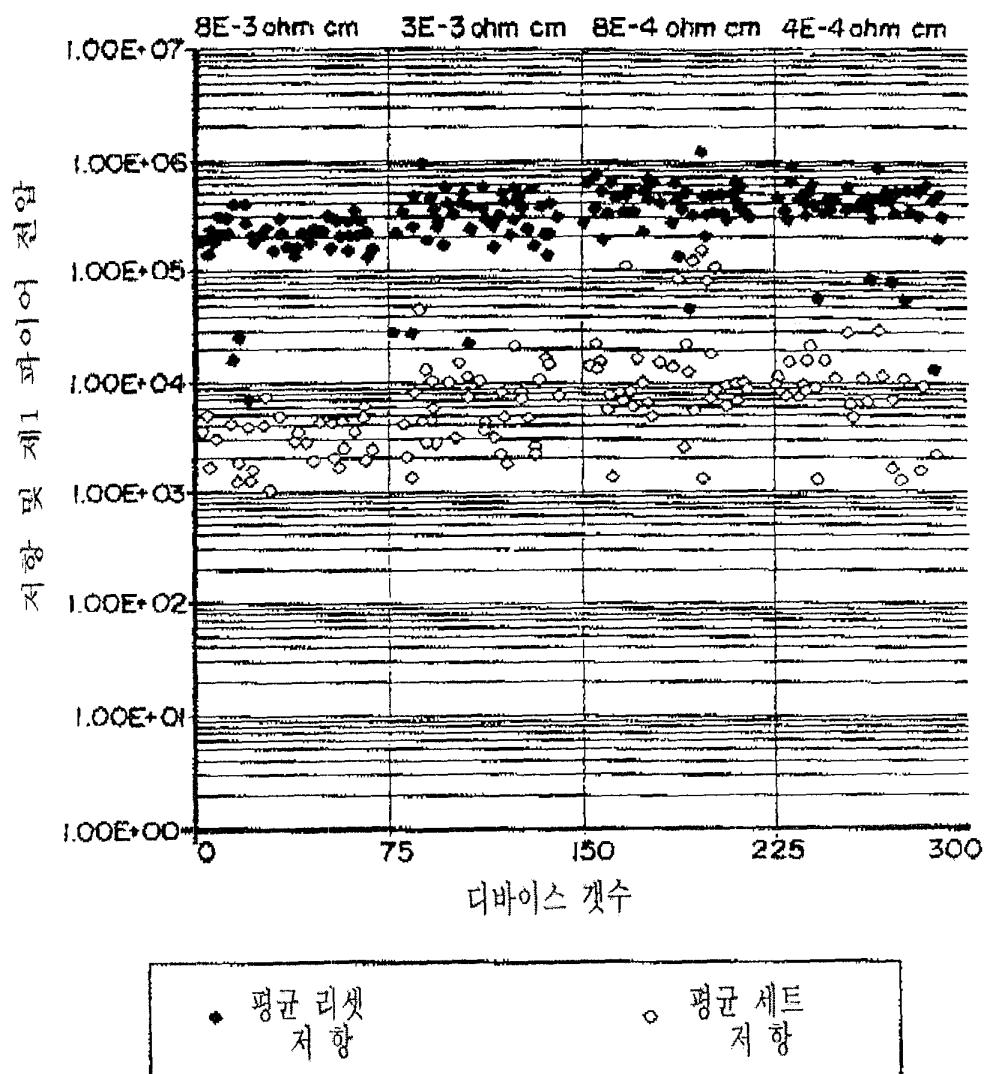

<52> 공간적으로 분리된 각 접촉면은 2개의 박막층을 포함한다. 단층(34, 38)은, 메모리 재료에 인접하여 배치되어, 외부물질이 칼코겐 메모리 재료(36)내로 유입되는 것을 방해하는, 우수한 확산 장벽적 특성을 가진다. 종전에는, Ovonic EEPROM에서, 인접한 박막층(34, 38)은 모두 비결정성 단소, 비결정성 실리콘 또는 이중 비결정성 탄소/비결정성 실리콘 구조로 구성되었다. 본 발명에서는, 인접한 박막층의 최소한 하나가 새로운 재료로 변경되었다. 새로운 재료는 Ti, V, Cr, Zr, Nb, M, Hf, Ta, W로 구성된 그룹에서 선택된 하나의 소자, 및 B, C, N, O, Al, Si, P, S로 구성된 그룹에서 선택된 2개의 소자를 포함하는 화합물로부터 형성된다. 한 실시예에서, 인접한 박막 접촉층의 최소한 하나가 티타늄 카보니트리드로 구성된다. 바람직하게는, 인접한 박막 접촉층의 최소한 하나가, 원자 퍼센트로, 10-60% 티타늄, 5-50% 카본, 10-60% 질소의 조성을 가진 화합물로 구성된다. 추가적으로, 티타늄 카보니트리드는 또한 40%까지의 수소를 포함할 수 있다. 또다른 실시예에서, 인접한 박막 층의 최소한 하나는 티타늄 실리코니트리드로 구성된다. 바람직하게는, 이 실시예에서 인접한 박막층의 최소한 하나가 원자 퍼센트로, 10-60%, 티타늄, 5-50% 실리콘 및 10-60% 질소의 조성물을 가진 화합물로 구성된다. 티타늄 카보니트리드 및 티타늄 실리코니트리드는, 외부물질이 칼코겐 메모리 재료내로의 전기적 유입 및 확산 모두를 방해하는, 우수한 장벽 특성을 가지고 있다.

<53> 티타늄 실리코니트리드 및 티타늄 카보니트리드의 층들은 증기화, 이온 플레이트 뿐아니라 DC 및 RF 스퍼터링 데포지션, 화학적 증착, 및 플라즈마 보조 화학적 증착을 포함하는 물리적 증착과 같은 방법으로 데포지트된다. 사용되는 정확한 방법은 많은 요인에 의존하는데, 그 중의 하나는 칼로겐 타겟 재료의 조성물에 부과된 데포지션 온도 억제이다. 티타늄 카보니트리드 또는 티타늄 실리코니트리드층은 바람직하게는, 100 Å-2000 Å의 두께로 데포지트된다. 이들 층은 바람직하게는, 200-1000 Å의 두께로 데포지트된다.

<54> 공간적으로 분리되어 배치된 접촉층의 쌍(6, 8)은 바람직하게는, 칼코겐 메모리 재료에 대해 떨어져서 데포지트된 추가적 박막층(32, 40)으로 구성된다. 이들 원격 박막층은 각각 Ti, W 및 Mo로 구성된 그룹으로부터의 하나 또는 그 이상의 소자로 구성된다. 한 실시예에서, 각각의 원격 박막층은 Ti 및 W로 구성된다. 바람직하게는, 원격 박막층은, 원자 퍼센트로, 5-30% 티타늄 및 70-95% 텅스텐화합물로 구성된다. Ti-W 합금층(32, 40)은 바람직하게는 DC 스퍼터링 데포지션 공정을 사용하여 데포지트된다. 이들은 바람직하게는, 100 Å-4000 Å의 두께로 데포지트된다. 이들은 더욱 바람직하기로는, 200 Å-2000 Å의 두께로 데포지트된다. Ti-W 합금층(32, 40)은 우수한 음(ohmic) 접촉 특성을 가진다. 더우기, 이들은 외부 전극물질의 칼코겐 메모리 재료내로의 전기적유입 및 확산 모두를 방해하는데 필요한 장벽 특성을 가진다.

<55> 메모리 재료(35)의 층은 여기서 개시된 칼코겐 재료와 같은 다중-소자 반도체 재료로 구성된다. 층(36)은 스퍼터링, 증기화, 또는 RF 글로우 방전과 같은 플라즈마 기술에 의해 측진되는 화학적 증착(CVD)과 같은 방법에 의해 데포지트된다. 본 발명의 칼코겐 메모리 재료는, 가장 바람직하게는, RF 스퍼터링 및 증기화에 의해 제조된다. 칼코겐 층(36)의 RF 스퍼터링 및 증기화에 대한 대표적 데포지션 파라미터는 각각, 아래의 표 2 및 3에서 나타낸다.

&lt;56&gt;

[표 2]

RF 스퍼터링 데포지션 파라미터

| 파라미터           | 대표적 범위                                       |

|----------------|----------------------------------------------|

| 베이스 압력         | $8 \times 10^{-7}$ - $1 \times 10^{-6}$ Torr |

| 스퍼터링 가스(Ar) 압력 | 4 - 8 m Torr                                 |

| 스퍼터링 전력        | 40 - 60 watts                                |

| 진동수            | 13 - 14 MHz                                  |

| 데포지션 속도        | 0.5 - 10 Å/초                                 |

| 데포지션 시간        | 2 - 25 분                                     |

| 필름 두께          | 250 - 1500 Å                                 |

| 기판 온도          | 주변 - 300°C                                   |

&lt;58&gt;

[표 3]

증기화 데포지션 파라미터

| 파라미터    | 대표적 범위                                       |

|---------|----------------------------------------------|

| 베이스 압력  | $1 \times 10^{-6}$ - $5 \times 10^{-6}$ Torr |

| 데포지션 온도 | 450 - 600°C                                  |

| 데포지션 속도 | 2 - 4 Å/초                                    |

| 데포지션 시간 | 2 - 20 분                                     |

| 필름 두께   | 250 - 1500 Å                                 |

| 기판 온도   | 주변 - 300°C                                   |

&lt;60&gt;

가열된 기판에 데포지트된 증기화된 필름은 칼코겐 소자의 배향된 층이 성공적으로 데포지트된 이방성 성장 특성(도 5의 설명 참조)을 나타내는 사실에 주목하는 것이 중요하다. 이것이 전기적 응용에 중요한지의 여부는 아직 증명되지 않았다; 그렇지만, 이런 종류의 필름은 열전기(이를 조성에 대해 이미 측정된 높은 열동력(thermopower), 즉 비스무트 시스템에서 측정된 것보다 큰 4 인자로 인함) 또는 특이적 반도체 및 초전도 응용에 대한 가능성을 보유한다. 메모리 재료(36)층은 바람직하게는, 200 Å - 5000 Å의 두께로, 더욱 바람직하게는 약 250 Å - 2500 Å, 가장 바람직하게는 400 Å - 1,250 Å의 두께로 데포지트된다.

&lt;61&gt;

여기서 사용된 "포어 직경"이라는 용어는 일반적으로 메모리 재료(36) 및 전기적 접촉층(6, 8) 사이의 최소 접촉 지역의 평균 단면을 의미한다. 메모리 재료(36)의 포어 직경은 비록 측면 치수상에 실제적인 제한이 없을 지라도, 약 1에서 2 마이크로미터보다 작거나 그 정도이다. 고전도 재료의 실제 저전도 경로의 직경은 1 마이크로미터보다 실질적으로 작다는 것이 확정적이다. 그러므로, 포어 직경은 리소그래피 해상 제한이 허용하는 만큼 작아질 수 있고, 사실상, 포어가 작으면 작을수록 전기적 스위칭에 대한 에너지 요구량은 낮아진다.

&lt;62&gt;

포어 직경은, 메모리 재료가 높은 저항 상태 또는 낮은 저항상태로 스위치될 때, 그 저항이 실제로 변경되는 메모리 재료의 단면과 실질적으로 일치하도록 선택되는 것이 바람직하다. 메모리 재료(36)의 포어직경은 그러므로, 바람직하게는 약 1 마이크로미터보다 작고, 그리하여, 메모리 재료(36)의 체적은, 리소그래피적으로 가능한 정도까지, 다양한 저항 상태사이에서 실제로 스위치되는 재료(36)의 체적까지 제한된다. 이는 추가로, 저항에 있어서의 검출 가능한 변화를 개시하는데 요구되는 전기적 에너지 및 스위칭시간을 감소시킨다. 이상적으로는, 포어직경은 스위칭 재료가 동적상태에 있을 때 형성된 필라멘트의 직경과 같아야 한다.

&lt;63&gt;

메모리 소자(30)의 포어 영역은, 상하 전극과의 전기적 접촉이 적절한 작동을 위해서 필요한 경우를 제외하고는, 열적으로 분리 되거나/되고 제어되는 것이 더욱 바람직하다. 이는, 저항 전이에 요구되는 전기 에너지 뿐아니라 포어의 스위치된 체적으로부터의 열전이를 제어하고, 제한한다. 이러한 열적 분리는, 절연 재료(39)에 의해서 도 1의 실시예에서 달성되는데, 절연재료는 메모리 소자(30)의 측면 말단을 둘러싼다.

&lt;64&gt;

우리들은 포어 직경에 일반적으로 연관된 메모리 소자의 실행(performance) 경향을 관찰하였다. 장치가 2진 모드로 사용될 경우, 와퍼를 관통하여 기구를 테스트하였을 때 오프-대-온 저항비가 증가하는

것을 관찰하였는 바, 상기의 와퍼에서 포어 직경은 1 미크론으로부터 완전 비 오픈인(not open)인 범위까지 체계적으로 걸쳐있다. 만약, 포어 직경이, 예를 들어, 1 미크론부터 6 미크론까지의 범위내에서 제어되는 경우, 본 장치의 실행능력을 향상시킬 기회가 있다. 전류 밀도 및 에너지 밀도와 같은 인자가 본 장치의 프로그래밍에 중요하기 때문에, 포어 직경의 감소로 인한 장치 체적의 감소는 감도 및 속도의 증가를 낳는다. 에너지/전류/전압 세트를 최소화하기 위하여, 포어직경은 1500 Å 만큼 작은, 또는 심지어 100 Å 만큼 작은 포어 직경이 사용 될 수 있다.

<65> 본 발명에 따른 메모리 소자는 적어도 하나의 이격배치 접촉부와 메모리 재료 부피 사이에서 필라멘트 제한 수단 (48)을 사용함으로써 메모리 소자에 더 우수한 열적 안정성, 더 낮은 세트/리세트 전류 필요량, 더 긴 사이클 수명 및 광범위하고 역동적인 저항의 범위를 주게된다.

<66> 상기 메모리 소자에 있어서, 저항 스위치는 메모리 재료 부피의 필라멘트 부분에서 발생하는 것으로 나타나고 이러한 필라멘트 부분은 필라멘트 한정 수단에 의하여 영향을 받는 것으로 나타난다. 필라멘트 한정 수단은 메모리 소자의 전기 화성 (electrical formation) 동안에 필라멘트 부분의 크기 및 위치를 한정한다. 필라멘트 한정 수단은 또한 메모리 소자를 사용하는 동안 크기를 제한하고 필라멘트 부분의 위치를 한정한다. 그럼으로써 이격 배치 접촉부에 흐르는 매우 낮은 입력 전류에 의존하는 단일의 셀 메모리 소자의 필라멘트 부분 내에 고전류밀도를 제공한다.

<67> 전형적으로 필라멘트 한정 수단은 이격 배치 접촉부의 어느 하나 및 메모리 재료 부피 사이에 배치된 박막층이다. 상기 박막층은 바람직하게는 두께 10 Å 내지 100 Å를 갖는다. 이러한 박막층은 고저항 재료로 만들어지고 적어도 하나의 저저항통로를 구비하고 있어서 그것을 통하여 전기 신호가 전기 접촉부 및 메모리 재료 부피 사이에 통과하게 한다. 고저항 박막층 내의 저저항 통로 영역은 박막층 및 메모리 재료 부피 사이의 총 접촉 영역의 약 2 퍼센트 이하이다. 전형적인 박막층은 실리콘, 질소 및 수소를 포함하는 실리콘 질소화물로 형성된다. 원자 백분율에 있어서, 상기 박막층의 조성율은 바람직하게는 약 30 - 40 % 실리콘, 40 - 50 % 질소 및 30 % 까지의 수소 사이가 된다.

<68> 필라멘트 한정 수단은 메모리 디바이스의 "전기 화성 공정 (electrical formation process)"의 역할을 한다. 전기 화성 공정은 더 높은 전류 전기 필스를 새로 구성된 메모리 소자에 메모리 소자가 그 초기의 매우 높은 "초기" 저항 값에서 낮은 저항값으로 스위치할 때까지 적용하는 단계를 포함한다. 상기 단계가 일어나게 되며, 메모리 소자는 "화성됨 (formed)"으로 불리게 된다. 이제 계속되는 더 낮은 전류 전기 사이클이 준비된 것이다.

<69> 화성 공정은 필라멘트 한정 수단인 실리콘 질소화물 박막층을 "파괴 (break down)" 한다. 즉 실리콘 질소화물 박막층은 고저항이다. 화성 공정 동안 하나 또는 그 이상의 더 높은 전류 필스가 가해지는 동안, 한정층에서 전기적으로 가장 약한 "파괴" 영역은 물리적으로 변호하게 되고 층의 나머지 영역보다 훨씬 고전도체의 성질을 갖게 된다. 계속되는 임의의 메모리 사이클 필스 (즉, 세트 및 리세트 필스)의 전류 모두가 통과하게 되는 것은 상기 영역을 통해서이다. 상기 전류는 메모리 재료 부피의 필라멘트 부분을 저항 스위치하게 되는 크기 및 위치를 한정한다. 파괴 영역은 이동하거나 저전류 메모리 스위칭 동안에 크기가 성장하지 않기 때문에, 그것은 위치를 한정하도록 작용하고, 메모리 소자를 사용하는 동안 필라멘트 부분을 저항 스위치하는 크기를 제한한다.

<70> 매우 낮은 전류가 메모리 소자에 가해질 때에, 모든 전류는 필라멘트 부분을 통과하여 채널된다. 그러므로, 그것의 극도로 작은 크기 때문에 전류 밀도는 메모리 재료의 상기 영역 내에서 매우 높아진다.

## 도면의 간단한 설명

<71> 도 1은 단일 메모리 소자의 단면도 ;

<72> 도 2는 소자들이 한 세트의 X - Y 어드레싱 라인에 연결되는 방법을 보여주는 다중 메모리 소자의 가능한 레이아웃에 대한 상면도 ;

<73> 도 3은 도 2로 부터의 메모리 소자에 대한 개략적인 다이어그램으로, 다이오드와 같은 절연 소자들이 각각의 디바이스를 다른 것들로 부터 전기적으로 절연시키도록 메모리 소자와 직렬 연결되는 방법을 부가적으로 보여주는 도면 ;

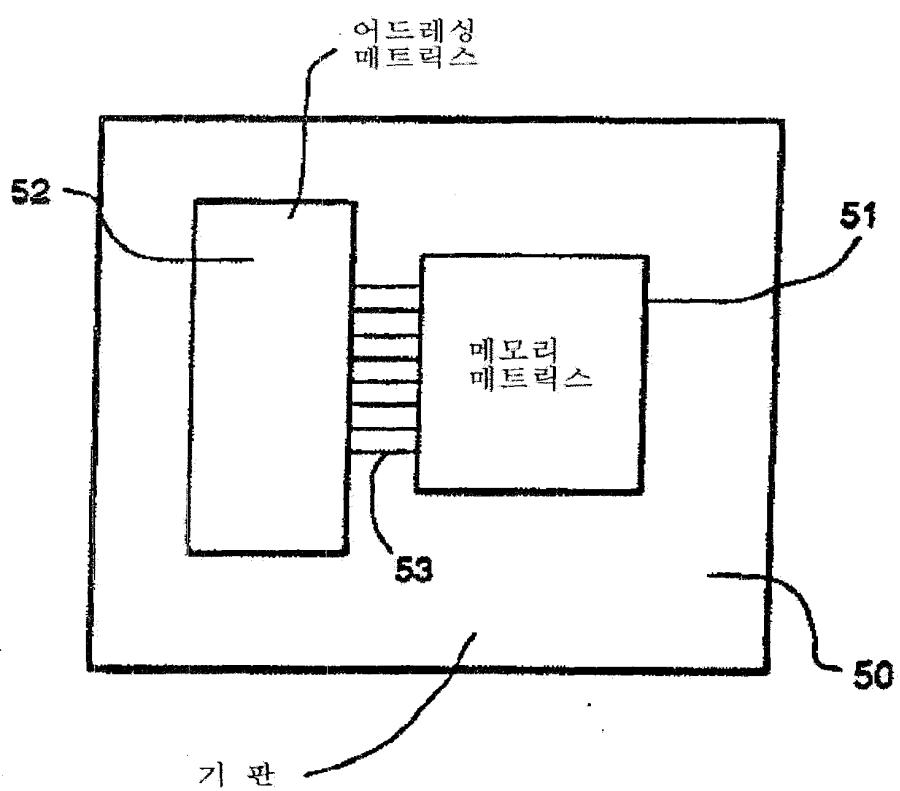

<74> 도 4는 어드레스/드라이버/디코더가 동작적으로 부착된 접적 회로 칩과 전기적으로 연결된 상태로 배치된, 도 1에 도시된 본 발명의 접적된 메모리 매트릭스를 지니는 단일 결정성 반도체 기판을 예시하는 개략적인 대표도 .

<75> 도 5는 본 발명의 메모리 소자가 제조되는 Ge : Sb : Te 합금 시스템의 삼원 상 다이어그램으로, 이 소자들의 여러 혼합물들이 신속한 응고시 분리되는 다중 상의 일부를 보여주는 상 다이어그램 ;

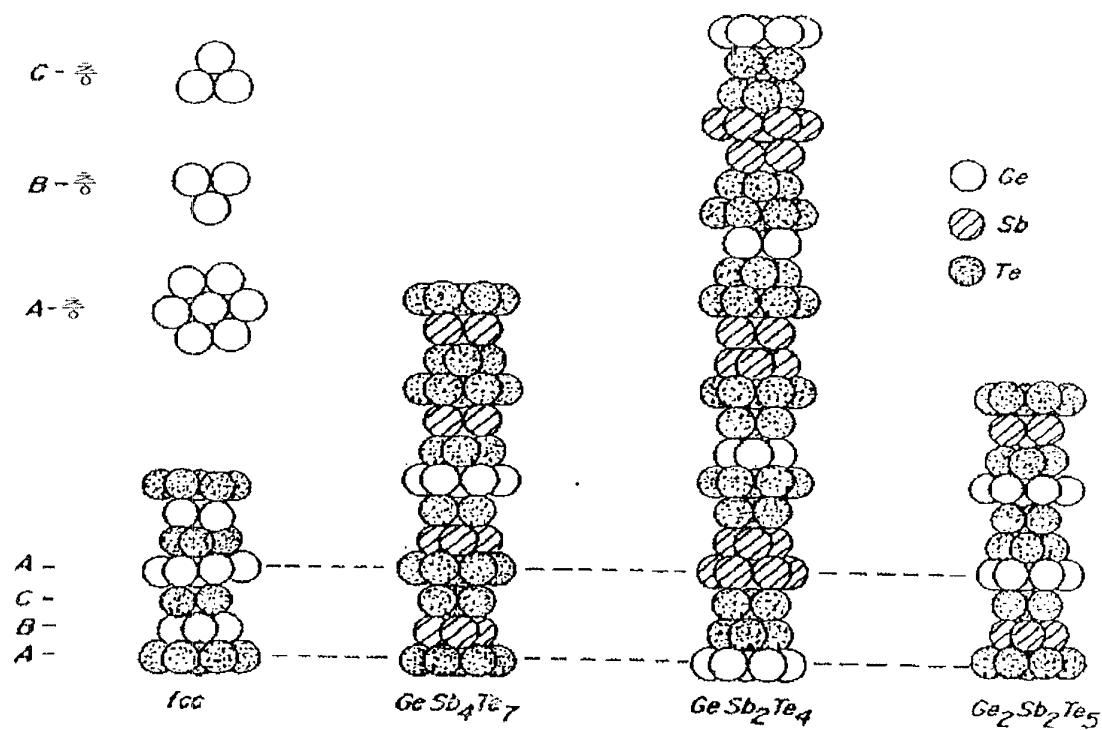

<76> 도 6은 시스템의 이방성 구조를 예시하기 위해 2 원 Ge - Te 의 원주 구조 뿐만 아니라 도 6의 Ge - Sb - Te 시스템의 세 개의 3원 합금에 대한 원자 구조적 층배열을 보여주는 도면 ;

<77> 도 7은 티타늄 카보니트리드로 구성된 상부 인접 접촉층 및 탄소로 구성된 하부 인접 접촉층을 지니는 메모리 소자의 사이클링 특성을 예시하는 데이터의 그래프 ;

<78> 도 8은 티타늄 실리코니트리드로 구성된 상부인접 접점층 및 탄소로 구성된 하부 인접 접점층을 지니는 메모리 소자의 사이클링 특성을 보여주는 데이터의 그래프 ;

<79> 도 9는 티타늄 카보니트리드로 구성된 상부 인접 접점층을 지니는 메모리 소자의 다중 상태 능력 (예컨대, 메모리 소자가 저항의 동적 범위내의 다중 저항 레벨로 설치될 수 있는 능력)을 예시하는 데 이터의 그래프 .

<80> 도 10은 4 개의 서로다른 저항값의 티타늄 카보니트리드로 구성된 두개의 인접 접점층을 지니는 세트 및 리셋 저항값을 예시하는 데이터의 그래프이다.

## 실시예

- <81> 도 1에 도시되어 있는 메모리 소자는 다단계 공정으로 형성될 수 있다. 총 (32), (34) 및 (46)은 맨처음으로 증착되고, 절연층 (46)은 구멍을 형성하도록 예칭된다. 나머지 층 (48), (38), (38) 및 (40)이 증착되고 전체 층 (32), (34), (36), (46), (48), (38) 및 (40)은 선택된 디멘션으로 예칭된다. 전체 구조의 상부상에 증착된 것은  $\text{SiO}_2$  또는  $\text{Si}_3\text{N}_4$ 의 절연물질 (39)이다. 이것이 예칭되고 알루미늄층이 증착되어 제 2 전극 그리드 구조 (42)를 형성하게 되는데, 여기에서 전극 그리드 구조 (42)는 도체(12) 방향으로 수직하게 확장하고 개별적인 메모리 소자에 X - Y 그리드 결합을 완성한다. 완성된 집적 구조 위에  $\text{Si}_3\text{O}_4$ 와 같은 적당한 캡슐봉입제 또는 폴리아미드와 같은 플라스틱 재료의 평면 캡슐 봉입층을 만들어서 성능을 약화 또는 악화시킬 수 있는 습기 및 기타 외부 요소로부터 구조를 밀봉한다.  $\text{Si}_3\text{O}_4$  캡슐봉입제는 예를 들어, 저온 플라스마 증착 공정을 사용하여 증착될 수 있다. 폴리아미드 물질은 회전 증착될 수 있고 공기 기술에 따라서 증착 후 구워지고 캡슐 봉입층을 형성하게 된다.

- <82> 선행 CMOS 기술은 단일 결정 반도체 웨이퍼 벌크 내에서 필요한 반도체 디바이스를 구성하는 것 이기 때문에 상기 타입의 3차원 메모리 어레이를 생산하는 데는 종래의 CMOS 기술을 사용할 수 없고 단지 디바이스의 단일 층을 제조하는데 사용될 수 있을 뿐이다. 게다가 (1) CMOS는 비교적 저비용으로 큰 어레이를 효과적으로 생산하기 위하여 푸트프린트( foot print ) ( 실제 소자 디멘션 ) 만큼 작게 생산할 수 없는 점 및 (2) CMOS 디바이스는 단일 평면 내에 존재하기 때문에 Z 방향을 따라서 결합될 수 없는 점 등이 있다. 따라서, CMOS 디바이스는 보다 진전된 형태의 병렬 처리 컴퓨터용으로 필요한 복잡하고 3 차원 결합을 하는 구조로 제조될 수 없다. 본 발명에 따른 3차원, 박막 메모리 어레이 구조는 다른 한편으로는 종래의 병렬 정보 처리 뿐만 아니라 직렬 정보 처리 모두로서 가능하게 된다.

- <83> 병렬 처리 및 결과적으로 다디멘션 메모리 어레이 구조는 패턴인식, 분류 또는 관련 학습 등과 같은 복잡한 작업을 신속하게 수행하는데 필요하다. 병렬 처리에 대한 다른 용도 및 기술 설명은 본 발명의 양수인에게 양도된 미합중국 특허 제 5,159,661호에 개시되어 있고 그 공개 내용은 본원 명에서에 참고자료로써 함체되어 있다. 그러나, 도 1의 실시예에 도시된 집적 구조에 따르면 완전 수직으로 집적된 메모리구조가 형성되어 있어서 기판상에 차지하고 있는 영역을 최소화하고 있다. 이것은 침내 메모리 소자의 밀도는 단지 리소그래피의 해상 능력에 의하여 기본적으로 제한된다는 것을 의미한다.

- <84> 다 메모리 소자용으로 가능한 배치의 평면도가 도 2에 도시되어 있다. 보는 바와 같이, 디바이스는 메모리 소자의 X - Y 매트릭스를 형성한다. 수평 스트립 (12)은 개별적인 소자를 어드레스 하기 위한 X - Y전극 그리드의 X 세트를 나타낸다. 수직 스트립 (42)은 어드레싱 라인의 Y 세트를 나타낸다.

- <85> 본 발명에 따른 전기적 소거 가능 메모리의 또 다른 회로 배치는 물론 가능하고 실행 가능하다. 특히 유용한 배치의 하나는 3차원, 멀티레벨 어레이로서, 그 내부에는 다수의 메모리 평면 또는 제어 소자 및 각각의 절연 디바이스가 서로 층을 이루고 있다. 각각의 메모리 소자 평면은 다수의 메모리 소자 열과 행으로서 배치되고, X - Y어드레싱을 가능하게 한다. 이러한 평면의 겹침층은 메모리 저장 밀도를 증가시킴과 더불어 결합의 추가적 Z 디멘션을 허용한다. 이러한 배치는 특히 진정한 의미의 인공 지능 컴퓨터용 뉴럴 네트워크를 모방하는데 유용하다.

- <86> 각각의 메모리 소자는 몇 가지 타입의 절연 소자를 사용함으로써 다른 것들과 전기적으로 절연된다. 메모리 디바이스 레이 아웃의 개략적인 다이아그램을 도시하는 도 3은 다이오드를 사용하여 어떻게 전기적인 절연이 달성될 수 있는지를 보여준다. 회로는 절연 다이오드 (26)와 직렬로 전기 접속되는 메모리 소자 (30)를 구비하는 X - Y 그리드를 포함한다. 어드레스 라인 (12) 및 (42)는 본원 발명이 속한 기술적 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있는 방법으로 외부 어드레스 회로에 결합된다. 절연 소자의 목적은 각각의 분리된 메모리 소자로 하여금 매트릭스의 인접 또는 멀리 떨어져 있는 메모리 소자에 정보가 저장되는 것을 방해받지 않고 판독 및 기록될 수 있도록 하기 위함이다.

- <87> 도 4는 기판위에 본 발명에 따라 형성된 메모리 매트릭스(5)를 구비한 단일 결정 반도체 기판 (50)의 일부를 도시한다. 또한 동일한 기판(50) 상에는 집적회로 접속부 (53)에 의하여 메모리 매트릭스 (51)에 적당하게 접속되는 어드레싱 매트릭스(52)가 형성되어 있다. 어드레싱 매트릭스(52)는 메모리 매트릭스 (51)에 가해지는 세팅 및 판독 펄스를 한정하고 제어하는 신호 발생 수단을 포함한다. 물론 어드레싱 매트릭스 (52)는 접속될 수 있고 고체 상태 메모리 매트릭스 (51)와 동시에 형성될 수 있다.

- <88> 종래 기술에 따르면 비교적 고 스위칭 속도 및 저 스위칭 에너지를 갖는 반도체 메모리는 대부분의 적용예에 필수적인 것으로 간주되어 왔는데, 적어도 하나의 트랜지스터 및 전하 측적 소자가 각각의 메모리 소자에 필요하다는 것이다. 집적 회로 형태 내에 그러한 메모리를 형성하는 것은 다른 부가적인 복잡한 구조를 따라서 적어도 3개의 접속부를 필요로 하는데 상기 복잡한 구조는 상기 집적 회로가 어떻게 레이 아웃되었든지 간에 관계없이 임의의 최소 기판 면적을 차지한다. 본 발명에 따른 전기적 소거 가능 메모리의 집적 회로 배치는 각각의 메모리 소자에 단지 2개의 접속부를 필요로 하고, 이러한 것들은 서로 수직 관계로 형성될 수 있다. 게다가 절연 다이오드 및 소자에 대한 한 쌍의 결합부로 완성되는 각각의 메모리 소자는 현저한 고비트밀도가 가능하도록 자체적으로 완전 수직으로 집적된다. 사실 본 발명에 따른 메모리는 고체 상태 다이나믹 램덤 액세스 메모리 ( solid state dynamic random access memories ) ( DRAMs )에서 달성할 수 있는 것보다 양호한 비트 밀도를 제공할 수 있는데, 여기에서 다이나믹 램은 휘발성이어서 결과적으로는 본 발명이 달성할 수 있는 불휘발성이 주는 부가적인 효과가 없는 셈이다.

- <89> 본 발명으로 달성할 수 있는 비트 밀도의 증가는 집적 회로 배치에서 비트당 차지하는 웨이퍼의 면적이 점점 작아지기 때문에 해당하는 만큼 제조 비용이 감소하게 된다. 이것은 본 발명에 따른 메모리로 하여금 전기적 성능 및 메모리 저장 용량의 면에 있어서 뿐만 아니라 비용의 면에 있어서도 기타 다른 더 광범위해지는 응용예를 갖는 구입 가능한 메모리들에 필적하거나 또는 능가하게 한다. 적어도 하나의 트랜지스터 및 각각의 비트에 대한 캐퍼시터로 형성된 종래의 반도체 메모리와 비교해본다면, 도 1에 도시된 바와 같이 본 발명에 따른 집적회로 배치는 동일한 포토 리소그래피 해상도 ( photo lithographic

resolution ) 를 사용한 종래의 배치와 비교하여 훨씬 높은 비트 밀도를 갖는 칩상에 형성될 수 있다. 높은 비트 밀도가 줄 수 있는 비용 효과적인 면에 더하여, 소자들은 더 가깝게 배치되고, 전선 길이, 캐퍼시턴스 및 기타관련 변수들이 소형화함으로써 결과적으로 성능을 향상시킨다.

<90> 실험을 통하여 다음의 요소 즉, 구멍 디멘션 ( 지름, 두께 및 부피 ), 칼코겐 조성물, 열 준비 ( 증착 냉각 후 ), 신호 펄스 지속 기간, 조성물 내에 존재하는 산소와 같은 불순물, 결정화 크기 및 신호 펄스 파형 형태는 저항의 동적 범위의 양, 상기 동적 범위의 절대적 단점 ( end - point ) 및 이러한 저항에서 디바이스를 세트하기 위하여 필요한 전압에 영향을 미치는 것을 보여준다. 예를들면, 비교적 두꺼운 칼코겐 막( 즉, 약 4000 Å )은 결과적으로 더 높은 세트 전압 필요량 ( 그러므로 메모리 재료 부피 내에 더 높은 전류 밀도 )이 되는 반면, 비교적 얇은 칼코겐 층 ( 즉, 약 250 Å )은 결과적으로 더 낮은 세트 전압 필요량( 그리고 전류 밀도 )이 된다. 물론 결정화 크기의 가능한 중요 의미 및 그에 따라서 별크 원자의 수에 비교되는 표면 원자 수의 비는 앞에 상세히 개시되어 있다.

<91> 전기 저항의 동적 범위내에 바람직한 저항 레벨에 메모리 소자를 세트하기 위하여 필요한 신호 펄스 지속 기간은 마찬가지로 신호 전류 레벨 뿐만 아니라 전술한 모든 변수에 의존하게 된다. 통상적으로 신호 펄스 지속 기간은 약 250 나노초 이하이고 바람직하게는 약 50 나노초 이하이다. 강조하고 싶은 것은 우리가 관심을 갖고 있는 짧은 25 나노초 펄스 폭 조차도 사용된 반도체 합금의 두께 및 조성물 뿐만 아니라 구멍의 크기 및 형태에 의존한다는 점이다. 펄스 지속 기간은 메모리 스위치의 작동을 방해하지 않고 현저하게 감소될 수 있다는 점이 인정된다.

<92> 실험은 더 작은 양의 에너지 입력이 소자의 사이클 수명을 증가시키게 된다는 점을 시사한다.

<93> 판독 및 필요시 주어진 메모리 소자의 저항을 조정하는 피드백 루프는 본원 발명의 메모리 시스템 내에 합체될 수 있다. 예를들어, 메모리 소자는 초기에 바람직한 저항값에서 세트될 수 있다 ; 그러나, 어떤 경우에는 소자의 저항은 초기에 세트된 저항값으로부터 약간 변동될 수 있다. 상기 경우에 피드백 루프는 선택된 ( preselected ) 저항값으로 되돌리기 위하여 소자에 필요한 저항 및 지속 기간을 갖는 새로운 신호 펄스를 계산하고 전달하게 된다. 또한 메모리 소자에 전달된 세트 펄스가 결과적으로 바람직한 저항 값에서 소자에 세팅되지 않게 되는 상황이 존재할 수 있다. 상기 경우에 피드백 루프는 바람직한 저항 레벨이 달성될때까지 소자에 추가적인 신호 펄스를 전달하게 된다. 이러한 일련의 세트/조정 사이클의 전체 지속 기간은 약 1000 나노초 이하이고, 바람직하게는 약 500 나노초 이하이다.

<94> 저항 대 디바이스 전류 커브의 선형 부분을 상승 및 하향으로 역방향 이동할 수 있는 능력은 아무리 강조해도 지나치지 않다. 선택된 전류의 펄스는 그전의 세트 조건에 관계없이 바람직한 저항에 메모리 소자를 세트할 수 있다. 커브를 따라서 역방향으로 이동할 수 있는 이러한 능력은 그 전에 저장된 데이터에 직접 오버라이트할 수 있게한다. 그러한 직접 오버라이트 능력은 선행 기술상의 위상 변화 및 MSM ( Si ) 메모리 재료로 가능하지 않다. 중간 저항 값은 역으로 세트하는 능력은 현저하다. 수천의 연속되는 매질 전류 펄스는 단일 매질 전류 펄스에 앞서는 더 높은 전류 펄스 또는 단일 매질 전류 펄스에 앞서는 더 낮은 전류 펄스와 동일한 저항 값을 달성한다.

<95> 저항의 동적 범위는 또한 더 광범한 그레이 스케일 ( gray scale ) 및 멀티레벨 아날로그 메모리 저장을 허용한다. 멀티 레벨 메모리 저장은 넓은 동적 범위를 다수의 서브 - 범위 또는 레벨로 나눔으로써 달성된다. 계속적인 저항 프로그램화 능력은 다중 비트를 단일 메모리 셀에 저장되는 2 진 정보로 되게 한다. 이러한 멀티레벨 저장은 2 진 정보의 다중 비트를 유사 - 아날로그 형태 ( pseudo - analog form )로 모방하여 이 아날로그 정보를 단일 메모리 셀 내에 저장함으로써 달성된다. 따라서, 저항의 동적 범위를  $2^n$  아날로그 레벨로 나눔으로써, 각각의 메모리 셀은 2 진 정보의 n 비트를 저장하게 되는 능력을 갖추게 된다.

<96> 상기한 바와같이 도 5는 Ge-Te-sb 반도체 합금 시스템의 3 차원 다이아그램이다. 2 및 3 위상은 정사각형 ( ■ )으로 표시되어 있다는 앞에 논의한 내용 외에도, 이 다이아그램은 다른 합금의 편석 현상 ( segregation )에 대한 정보를 준다. 이러한 기타 합금은 삼각형 ( ▲ ), 다이아몬드형 ( ◆ ) 및 원 ( ● )으로 표시되어 있고, 합금이 용융에서 신속한 고체화에 의존하여 편석 현상을 일으키는 위상은 거기에서부터 확장하는 선 ( 실선 또는 점선 )으로 표시되어 있다. 두개의 Te - 다량 함유 용융기 시작되는 조성물은 3 차원 다이아그램 상에 원 기호로 표시되어 있다. 신속한 고체화에 의존하여, 이러한 혼합물 위상은 원소 Te 더하기 위상 B, C 및 D에서 편석 현상을 일으킨다.

<97> 유사 2 진 라인의 우측에서 조성물의 용융은 다이아몬드 기호로 표시되고 다이어그램 상에 라인으로 표시된 위상에서 고체화한다. 위상 다이아그램내에서 삼각형으로 표시된 다른 혼합물은 폭 Ge 및 sb 및 위상 A에서 고체화한다. 본 발명에 따른 개선된 메모리 소자에서 용도상 특히 관심을 갖는 합금은  $Ge_{22}Sb_2Te_{56}$  이고, 이것은  $Ge_2Sb_2Te_5$  또는 2-2-5 라 불리기도 한다. 신속한 고체화에 의존하는 상기 2-2-5 합금 위상은 도 5의 위상 다이아그램 내에 표시된 조성물 B (  $Ge_{26}Sb_{18}Te_{5+}$  ) 및 조성물 C (  $Ge_{18}Sb_{26}Te_{56}$  )의 두개의 개별적인 위상의 혼합에서 편석 현상을 일으킨다. 특히 관심을 갖는 또다른 합금은  $Ge_{14}Sb_{29}Te_{57}$  ( 또한  $GeSb_2Te_4$  또는 1-2-4 로 불린다 )로서  $GeTe-Sb_2Te_3$  유사라인 상에 조성물 D이다. 2-2-5 및 1-2-4 합금은 전술한 바와같이 조성물적으로 그레이드되거나 층으로 되거나 또는 그레이드/층 형태의 조합에서 메모리 재료 부피를 형성하는데 관심이 있다.

<98> 도 6은 2 원 합금 Ge - Te의 원자적 구조 뿐만 아니라 3 개의 3 원 합금 Ge - Sb - Te 의 원자적 구조를 도시한다. 3 개의 3 원 합금 중 2 개는 1-2-4 ( 도 5의 3 차원 다이아그램 상의 조성물 D ) 및 상기한 2-2-5 조성물이다. 제 3 원 합금은  $Ge_8Sb_{33}Te_{59}$  로서  $GeSb_4Te_7$  또는 1-4-7 로도 불린다. 상기 1-4-7 합금은 도 5의 3 원 위상 다이아그램 상에서 조성물 E에 대응한다. 상기 합금의 원자적 구조에 대한 설명을 하자면, 속이 빈 원은 Ge 원자를 표시하고, 빛금친 원은 Sb 원자를 표시하고 점무늬 원은 Te 원자를 표시한다. 도 6에 도시된 바와같이 각 합금의 원자적 배치는 면심입방 결정 구조에서 원자의 순서적 반복층을 형성한다. fcc 배치는 도 6에서 A, B 및 C로 라벨되는 세개의 구별되는 타입의 층을 형성한다.

<99> 도 6에 도시되어 있는 1-4-7, 1-2-4 및 2-2-5 합금은 베이스 메모리 재료로서 관심을 끄는 것이

고 본원 발명의 원소적으로 변경된 메모리 재료의 용도를 갖는다. Se가 존재할 때에는 그것을 따라서 전이 금속 ( transition metal )은 Te-Ge-Sb 매트릭스를 통하여 비교적 균일하게 합체되고 스위칭 전류 필요량을 감소시키고 데이터 보유력의 열적 안정성을 증가시키기 위하여 전자/원자 구조를 강화시킨다. 전류 분석은 Se가 구조내에서 Te를 대체하는 것을 보여주는데, 전이 금속의 정확한 위치는 공지되어 있지 않으나, 칼코겐 소자와의 전이 금속 결합이 나타난다.

<100> 마찬가지로, 전술한 바와같이, Ge - Sb - Te 합금이 가열된 기판 상에 증착에 의해서 데포지트될 때, 금속은 이방성 ( anisotropic ) 형태로 데포지트된다. 즉, 이러한 방식으로 데포지트될 Eo, 합금의 결정하는 구성 원자폭의 층이 기판 표면에 실질적으로 평행하게 배열된다. 물론 이것은 이방성 전류 흐름을 초래할 것이다. 그러나, 저저항 방향에서 세트 및 리세트 펄스를 가하기 위하여 금속 원자를 배열하는 가능성을 주는데 긴 기간이 필요하고 결과적으로 아주 낮은 세트 및 리세트 전류, 전압 및/또는 에너지를 달성한다.

<101> 도 7은 티타늄 카보니트리드 ( titanium carbonitride )로 구성된 상부 인접 접촉층이 있는 메모리 소자의 사이클 특성을 도시하는 데이터를 그래프로 도시한다. 디바이스 저항은 세로축에 도시되어 있고 사이클 수는 가로축에 도시되어 있다. 저저항 상태 ( 세트 상태 )로부터 고저항 상태 ( 리세트 상태 )로 가기 위하여 높이 약 2mA 및 폭 약 40 ns의 전기 펄스가 메모리 디바이스에 가해진다. 저저항 상태로 되돌리기 위하여 높이 약 1 mA 및 폭 약 100 ns의 펄스가 디바이스에 가해진다. 그러므로 적당한 높이 및 폭의 일련의 펄스를 가함으로써 디바이스는 도시된 바와같이 사이클된다.

<102> 도 8은 티타늄 실리코니트리드 ( titanium siliconitride )로 구성된 상부 인접 접촉 층의 메모리 소자의 사이클 특성을 도시하는 데이터를 그래프로 도시한다. 저저항 상태 ( 세트상태 )에서 고저항 상태 ( 리세트 상태 )로 가기 위하여 높이 약 2 mA 및 폭 약 40 ns의 전기 펄스가 메모리 디바이스에 가해진다. 저저항 상태로 되돌리기 위하여 높이 약 1 mA 및 폭 약 100 ns 의 펄스가 디바이스에 가해진다.

<103> 도 9는 본원 발명의 메모리 소자에 대한 다중 상태 가능성 ( 즉, 저항의 동적 범위내에서 다수의 저항 레벨 중 어느 하나에 세트되는 메모리 소자의 능력 )을 그래프로 도시한다. 데이터는 티타늄 카보니트리드로 구성되는 상부 인접 접촉 층 (38)을 갖는 메모리 소자에 대한 것이다. 그래프는 저항값을 증가시키도록 메모리 디바이스를 프로그램함으로써 구성된다. 이것은 증가하는 프로그램 전류의 40 ns 전기 펄스를 가함으로써 수행된다.

<104> 도 10은 상부 인접 접촉 층으로서 티타늄 카보니트리드를 갖는 메모리 소자에 대한 평균 세트 및 리세트 저항을 보여주는 데이터를 그래프로 도시한다. 세트 및 리세트 저항은 4 개의 상이한 저항률을 갖는 티타늄 카보니트리드층을 사용하여 결정된다. 저항률은 티타늄 카보니트리드 조성물내의 탄소의 함량을 증가시킴으로써 증가된다. 도시되어 있는 바와같이, 세트 및 리세트 저항의 차이는 티타늄 카보니트리드 저항률을 증가시킴으로써 증가한다.

<105> 오보닉 EEPROM의 프로그래밍과 관련하여 임계 스위칭 전압이 있다. 그러므로 임계 스위치와 마찬가지로 오보닉 EEPROM 프로그래밍 전압은 칼코겐 합금막의 두께에 의존하는 성질을 보여준다. 사실상 오보닉 EEPROM에 있어서, 임계 스위칭 전압은 프로그래밍 사건으로부터 판독 사건을 분리하는 역할을 하고 판독 업세트를 제거하고 데이터 판독 동안에 양호한 동작 마진을 제공한다. 본발명의 디바이스는 가해진 전계가 낮고 이어서 증가하는 전계 저항 내에서 점차적으로 감소할 때에, 선형 저항 특성은 임계 전압까지 상승하는 것을 보여준다. 한번 임계 전압을 넘어서게 되면, 디바이스는 높은 도전 상태, " 다이나믹 온 ( dynamic on ) " 상태로 부저항 전이 ( negative resistance transition )를 보여준다. 가해진 전계가 제거되었을 때에는, 디바이스는 불휘발성 프로그램 저항 상태로 되돌아가게 되고, 디바이스가 다이나믹 온 상태 동안에 " 메모리 평형 시간 ( memory equilibration time ) "을 경험하게되는 전류/에너지 프로파일에 의존하게된다. 비록 임계 전압이 디바이스의 임계 전압에 의존한다 할지라도, 임계 전압에서의 디바이스 전류는 모든 디바이스 저항에 있어서 비교적 일정하다. 두께에 대한 선형 근사인 임계 전압 관계는 1 이하의 비례 인자 ( proportionality factor )를 보여주는데, 이는 동일한 형식상 두께를 갖는 디바이스 내에 광범위한 동작 마진을 준다.

<106> 본원 명세서에 개시된 물질 및 디바이스 배치의 실시를 통하여 전기적으로 소거 가능하고 적절 오버라이트 가능한 메모리 소자가 개발되었는데, 이것은 SRAM 디바이스에 접근하기 위한 빠른 판독 및 기록 속도 ; EEPROM의 불휘발성 및 랜덤 액세스 리프로그래밍 가능성 ; 및 바탕면에서 기타 다른 반도체 메모리에 비하여 메가바이트 당 저장이 현저하게 저렴함 등의 효과를 준다.

<107> 본원 발명의 기술적 사상을 전부 공개하기 위하여 실시예를 상세하게 설명하는 방법으로 본원 명세서를 기술한다. 상기 상세한 설명은 본원 발명의 진정한 의미의 기술적 범위를 제한하는 것은 아니며 첨부하는 청구범위에 한정하여 청구한다.

### (57) 청구의 범위

#### 청구항 1

전기적으로 동작되고 직접 오버라이트 가능한 멀티비트의 단일 셀 메모리 소자에 있어서,

(1) 전기 저항값의 큰 동적 범위, (2) 상기 단일 셀 메모리 소자에 멀티비트 저장 능력을 제공하도록 선택된 전기 입력 신호에 응답하여 메모리 재료의 적어도 필라멘트 부분이 상기 동적 범위내의 복수 개의 저항값 중 하나로 설정될 수 있는 능력, 및 (3) 상기 메모리 재료의 이전 저항값에 관계없이 상기 필라멘트 부분이 상기 동적 범위내의 임의 저항값으로 설정될 수 있는 능력을 특징으로 하는 메모리 재료의 부피, 및

상기 메모리 재료를 상기 동적 범위내의 선택된 저항으로 설정하도록 상기 전기적 입력 신호를 공급하는 한쌍의 이격 배치된 접점

을 포함하고, 개량형은

상기 이격 배치된 접점 각각은 상기 메모리 재료에 인접 배치된 박막 접점층을 포함하고, 상기 인접 박막 접점층 중 적어도 하나는 B, C, N, O, Al, Si, P, S 및 혼합물이나 합금으로 이루어진 그룹으로 부터 선택된 두개 이상의 원소와 함께 Ti, V, Cr, Zr, Nb, Mo, HF, Ta, W 및 그의 혼합물이나 합금으로 이루어진 그룹으로 부터 선택된 하나 이상의 원소를 포함하는 것을 특징으로 하는 메모리 소자.

#### 청구항 2

제 1 항에 있어서, 상기 인접 박막 접점층은 C, N, Al, Si 및 그의 혼합물이나 합금으로 이루어진 그룹으로 부터 선택된 두개 이상의 원소와 Ti를 포함하는 것을 특징으로 하는 메모리 소자.

#### 청구항 3

제 2 항에 있어서, 상기 인접 박막 접점층은 Ti, C, 및 N을 포함하는 것을 특징으로 하는 메모리 소자.

#### 청구항 4

제 3 항에 있어서, 상기 인접 박막 접점층은 40 % 까지의 수소를 포함하는 것을 특징으로 하는 메모리 소자.

#### 청구항 5

제 2 항에 있어서, 상기 인접 박막 접점층은 Ti, Si 및 N을 포함하는 것을 특징으로 하는 메모리 소자.

#### 청구항 6

제 1 항에 있어서, 개량형은

상기 이격 배치된 접점 각각은 상기 메모리 재료에 이격 배치된 박막 접점층을 포함하고, 상기 이격된 박막 접점층은 Ti, W, Mo 및 그의 혼합물이나 합금으로 이루어진 그룹으로 부터 선택된 하나 이상의 원소로 구성되는 것을 특징으로 하는 메모리 소자.

#### 청구항 7

제 1 항에 있어서, 상기 인접 박막 접점층은 Ti 및 W를 포함하는 것을 특징으로 하는 메모리 소자.

#### 요약

전기적으로 동작되는 메모리 소자 (30)는, 전기 저항값의 큰 동적 범위 ; 및 단일 셀에 다비트 저장 능력을 제공하기 위해 재료의 이전 저항값에 관계없이 선택된 전기 신호에 의해 적어도 필라멘트 부분이 동적 범위내의 임의 저항값으로 설정될 수 있는 능력을 특징으로 하는 다량의 메모리 재료 (36)를 포함한다. 메모리 재료 (30)는 1) 박막층 ( 34, 38 ), 바람직하기로는 이율질이 메모리 재료 (36) 내로 들어가는 것을 방지하도록 확산 재료로 사용되는 메모리 재료 (36)에 인접 배치된 티타늄 카보니트리드 또는 티타늄 실리코니트리드, 및 2) 박막층 ( 32, 40 ), 바람직하기로는 장벽에 알루미늄 전자이동과 확산을 제공하고 알루미늄 계면에서 오옴 접점을 제공하는데 사용되는 메모리 재료에 이격 배치된 Ti-W 합금을 포함하는 한쌍의 접점 (6, 8)을 또한 포함한다.

#### 대표도

#### 도면

## 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10