(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3871853号

(P3871853)

(45) 発行日 平成19年1月24日(2007.1.24)

(24) 登録日 平成18年10月27日(2006.10.27)

(51) Int.C1.

F 1

|        |        |           |        |       |      |

|--------|--------|-----------|--------|-------|------|

| G 11 C | 11/406 | (2006.01) | G 11 C | 11/34 | 363K |

| G 11 C | 11/41  | (2006.01) | G 11 C | 11/34 | Z    |

| G 11 C | 11/401 | (2006.01) | G 11 C | 11/34 | 362H |

| G 11 C | 11/407 | (2006.01) | G 11 C | 11/34 | 362S |

| G 11 C | 11/403 | (2006.01) | G 11 C | 11/34 | 363M |

請求項の数 15 (全 27 頁) 最終頁に続く

(21) 出願番号

特願2000-161123 (P2000-161123)

(22) 出願日

平成12年5月26日 (2000.5.26)

(65) 公開番号

特開2001-344967 (P2001-344967A)

(43) 公開日

平成13年12月14日 (2001.12.14)

審査請求日

平成16年3月5日 (2004.3.5)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100089071

弁理士 玉村 静世

(74) 代理人 100075096

弁理士 作田 康夫

(72) 発明者 鮎川 一重

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 三浦 譲士

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体装置及びその動作方法

(57) 【特許請求の範囲】

【請求項 1】

フラッシュメモリが形成された第1半導体チップと、スタティック・ランダム・アクセスメモリコントローラが形成された第2半導体チップと、メモリが形成された第3半導体チップとを内部に含む封止体を有し、

前記封止体は、前記第1から第3チップがその第1正面に搭載された基板を含み、

前記基板は、前記第1正面に設けられ前記第1から第3半導体チップと電気的接続をするための複数の第1電極と、前記複数の第1電極に接続され前記封止体の外部に対して電気的接続をするための複数の第2電極とを有し、

前記メモリは、第1キャパシタと第1MISFETをそれぞれに持つ複数の第1メモリセルを含む第1メモリブロックと、第2キャパシタと第2MISFETをそれぞれに持つ複数の第2メモリセルを含む第2メモリブロックと、前記第1及び第2メモリブロックで共用されるコマンド信号入力のための第1ノード、アドレス信号入力のための第2ノード、及びデータ入出力のための第3ノードとを有し、

前記メモリコントローラは、前記メモリに対するコマンド信号を出力するために設けられ前記メモリの前記第1ノードに結合される第4ノードと、前記メモリに対するアドレスを出力するために設けられ前記第2ノードに結合される第5ノードと、前記第3ノードに結合される第6ノードと、アクセス要求信号を受けるための第7ノードと、アクセスアドレスを受けるための第8ノードとを有し、

前記メモリコントローラは、第1期間において前記第8ノードに第1アクセスアドレス

10

20

が入力された際には前記メモリの前記第1メモリブロックに対するコマンド信号及び第1アドレスを前記第4及び第5ノードから出力するとともに、第2期間において前記第8ノードに前記第1アクセスアドレスが入力された際には前記メモリの前記第2メモリブロックに対するコマンド信号及び前記第1アドレスを前記第4及び第5ノードから出力することを特徴とする半導体装置。

#### 【請求項2】

請求項1において、

前記第1期間において、前記メモリコントローラは、前記第1メモリブロックに対して前記第1アクセスアドレスに対応する第1メモリセルに対する読み出しありまたは書きコマンド信号を前記第4ノードから出力可能とされるとともに、前記第2メモリブロックの前記第2メモリセルに対するリフレッシュを行いうためのリフレッシュコマンド信号を前記第4ノードから出力し、10

前記第2期間において、前記メモリコントローラは、前記第1メモリブロックの前記第1メモリセルに対するリフレッシュを行いうためのリフレッシュコマンド信号を前記第4ノードから出力するとともに、前記第2メモリブロックに対して前記第1アクセスアドレスに対応する第2メモリセルに対する読み出しありまたは書きコマンド信号を前記第4ノードから出力可能とされることを特徴とする半導体装置。

#### 【請求項3】

請求項2において、前記第1メモリブロックと前記第2メモリブロックとは同じ情報を重複して記憶する期間を有することを特徴とする半導体装置。20

#### 【請求項4】

請求項2において、前記第1期間において、前記メモリコントローラは、前記第1メモリブロックにデータ書きが起きた場合には、当該書きデータは所定の手順で前記第2メモリブロックの対応するアドレスの前記第2メモリセルに転写されることを特徴とする半導体装置。20

#### 【請求項5】

請求項2において、

前記メモリコントローラは、前記第1期間と前記第2期間とは交互に時分割で発生することを特徴とする半導体装置。

#### 【請求項6】

請求項1において、

前記半導体装置は、前記第1メモリブロックに対する読み出し／書き込み許容期間であるとともに前記第2メモリブロックに対するリフレッシュ期間となる前記第1期間と、前記第1メモリブロックに対するリフレッシュ期間となるとともに前記第2メモリブロックに対する読み出し／書き込み許容期間である前記第2期間とを交互に繰り返すことを特徴とする半導体装置。30

#### 【請求項7】

請求項1において、

前記メモリコントローラは、書きデータを保持するためのバッファメモリを更に有し、前記第1期間において前記メモリコントローラが第1アクセスアドレスとともにデータ書き込みのアクセス要求信号を受けた場合であって、前記メモリコントローラは第1メモリブロックに対する書きコマンド、前記第1アドレス、及び書きデータを前記第4、第5、および第6ノードから出力し、しかる後に第2メモリブロックに対する書きコマンド、及び前記第1アドレスを前記第4、及び第5ノードから出力する共に、前記バッファメモリに保持された書きデータを前記第6ノードから出力することを特徴とする半導体装置。40

#### 【請求項8】

請求項1において、

前記メモリコントローラの前記第8ノードに入力されるアクセス要求のサイクル時間は、前記メモリコントローラが前記第4ノードから出力するコマンド信号のサイクル時間より長いことを特徴とする半導体装置。50

**【請求項 9】**

請求項 1 において、

前記メモリコントローラは、リフレッシュ制御回路と、アクセス優先判定回路と、書き込みデータを保持するためのバッファメモリとをさらに有し、

前記第 1 期間において、前記アクセス優先判定回路は、前記リフレッシュ制御回路が発生する前記第 2 メモリロックに対するリフレッシュ要求を第 1 優先とし、前記バッファメモリに書き込みデータが保持されている場合に前記バッファメモリの書き込みデータの転写のための前記第 2 メモリロックに対する書き込みコマンドの発行を第 2 優先とすることを特徴とする半導体装置。

**【請求項 10】**

10

請求項 1 において、前記複数の第 2 電極は、前記フラッシュメモリと前記スタティック・ランダム・アクセスメモリに対して共通に設けられた複数のアドレス信号端子と、前記フラッシュメモリのアクセス制御のための複数の第 1 制御信号端子と、前記スタティック・ランダム・アクセスメモリのアクセス制御のための複数の第 2 制御信号端子と、前記第 1 から第 3 半導体チップに対する複数の電源端子とを含み、

前記第 3 半導体チップの前記メモリの第 1 から第 3 ノードは前記第 3 半導体チップ上に設けられるとともに、前記第 2 半導体チップの前記メモリコントローラの第 4 から第 6 ノードは前記第 2 半導体チップ上に設けられ、前記第 1 から第 3 ノードと前記第 4 から第 6 ノードは前記第 1 主面上の前記複数の第 1 電極の所定のものを介して接続されることを特徴とする半導体装置。

20

**【請求項 11】**

請求項 1 において、前記複数の第 2 電極は、前記第 3 半導体チップの前記メモリの機能テストのためのテスト端子を更に含むことを特徴とする半導体装置。

**【請求項 12】**

請求項 1 において、前記半導体装置は、前記複数の第 2 電極から前記第 3 半導体チップの前記メモリに対するリフレッシュ制御コマンドの投入が不要とされることを特徴とする半導体装置。

**【請求項 13】**

請求項 1 において、前記第 3 半導体チップの前記メモリは、複数のメモリバンクを有し、クロックに同期したコマンドにより読み出し / 書込みを行うダイナミック・ランダムアクセス・メモリであることを特徴とする半導体装置。

30

**【請求項 14】**

請求項 1 において、前記第 3 半導体チップの前記メモリは、複数のメモリバンクを有し、クロックに同期したコマンドにより読み出し / 書込みを行うダイナミック・ランダムアクセス・メモリであることを特徴とする半導体装置。

**【請求項 15】**

40

請求項 1 において、前記ダイナミック・ランダムアクセス・メモリチップは、複数のメモリバンクとして 4 個のメモリバンクを有し、2 個の前記メモリバンクが前記第 1 メモリロックに割り当てられるとともに、残る 2 個の前記メモリバンクが前記第 2 メモリロックに割り当てられることを特徴とする半導体装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

この発明は、DRAM を含む複合型メモリ半導体装置に関し、更には DRAM のリフレッシュ方法に関する。

**【0002】****【従来の技術】**

この明細書で参照される文献のリストは以下の通りであり、文献の参照は文献番号をもつてすることとする。[文献 1] : LRS1337 Stacked Chip 32M Flash Memory and 4M SRAM Data Sheet ([平成 12 年 4 月 21 日検索]、インターネット < URL: http://www.sharpsma.co

50

m/index.html > )、[文献2]：特開平11-219984号公報、[文献3]：特開平5-299616号公報（対応欧州特許公開公報566,306号、1993年10月20日）、[文献4]：特開平8-305680号公報、[文献5]：特開平11-204721号公報、[文献6]：特開平10-11348号公報。

#### 【0003】

[文献1]には、フラッシュメモリとSRAMとがスタックチップでBGA型パッケージに一体封止された複合型半導体メモリが記載される。フラッシュメモリとSRAMとはFBGA型パッケージの入出力電極に対してアドレス入力端子とデータ入出力端子が共通化されているが、各々の制御端子はそれぞれ独立とされている。

#### 【0004】

[文献2]には、フラッシュメモリとSRAMとがBGA型パッケージに一体封止された複合型半導体メモリが記載される。フラッシュメモリはBGAパッケージの回路基板に対して半田バンプを介して信号パッドがフェースダウンボンディングされる。フラッシュメモリの上に搭載されたSRAMはワイヤボンディングにより基板に信号パッドが接続される。

#### 【0005】

[文献3]の図17には、フラッシュメモリチップとDRAMチップとがリードフレーム型パッケージに一体封止された複合型半導体メモリが記載される。また、図1にはフラッシュメモリとDRAMとはパッケージの入出力電極に対してアドレス入力端子、データ入出力端子、及び制御端子が共通化されて入出力されるものが記載されている。

#### 【0006】

[文献4]には、ダイパッド上にSRAMチップが搭載され、そのSRAMチップ上にバンプ電極を介して接続されたフラッシュメモリチップとマイコンチップとが搭載され、それらのチップがリード端子型のパッケージに一体封止された半導体装置が記載される。

#### 【0007】

[文献5]の図15には、1つの大型チップの裏面に絶縁プレートを介してそれよりも小型の2個のチップ搭載された、リードフレーム型のパッケージに一体封止された半導体装置が記載されている。搭載しうるチップの組合せとしてフラッシュメモリチップ、DRAMチップ、及びASIC(Application Specific IC)があり、これによりメモリ-ロジック混載LSIが1つのパッケージで実現されると記載される。

#### 【0008】

[文献6]には、2つのDRAMブロックを有し、同じデータを2重化して記憶し、2つのDRAMブロック間でリフレッシュタイミングをずらし、外部からのアクセスとDRAMのリフレッシュの衝突を回避する技術が記載される。この制御はDRAMコントローラによって行われるが、このDRAMコントローラは2つのDRAMブロックに対して物理的に各々独立したアドレス信号や制御信号が発する。

#### 【0009】

##### 【発明が解決しようとする課題】

本願発明者等は、本願に先立って携帯電話及びそれに使用されるフラッシュメモリとSRAMが1パッケージに実装された複合型メモリについて検討を行った。フラッシュメモリには携帯電話システムのOS(オペレーションシステム)の他、通信やアプリケーションのプログラムが格納されている。一方、SRAMには電話番号、住所録、着信音等が記憶されているほか、アプリケーションの実行時に一時的に使用されるワークエリアが確保されている。

#### 【0010】

電話番号や住所録等、記憶しておくべきデータを保持するため、携帯電話の電源がオフになっている場合でもSRAMにはデータを保持するための電源が接続されている。長期にわたってデータを保持するためにはSRAMのデータ保持電流が小さい事が望ましい。しかしながら、アプリケーションが使用するワークエリアは携帯電話に付加される機能（音楽やゲーム等配信等）が増えるにつれて大きくなり、より大きな記憶容量のSRAMが必要となることが予想される。特に最近の携帯電話は高機能化が目覚しく、SRAMの大容量化で対応するこ

10

20

30

40

50

とがしだいに困難になってくることが判明した。即ちSRAMの大容量化には以下のような課題がある。大容量SRAMの課題は、記憶容量の増大分だけ、データ保持電流が増加してしまう他に、ゲートリーアクション電流の増大によるデータ保持電流が増加する点にある。これは大容量SRAMを実現するために微細加工を導入してMOSトランジスタの酸化絶縁膜を薄膜化するとゲートから基盤へトンネル電流が流れてしまいデータ保持電流が増えてしまうという理由による。

#### 【0011】

そこで本願発明の目的の一つは、記憶容量が大きくかつデータ保持電流の少ないメモリを実現にある。

#### 【0012】

10

#### 【課題を解決するための手段】

本発明の代表的な手段を示せば以下の通りである。フラッシュメモリと、スタティック・ランダム・アクセスメモリ(SRAM)と、複数のメモリバンクから構成される、クロックに同期したコマンドにより読み出し/書き込みを行うダイナミック・ランダムアクセス・メモリ(DRAM)を一つの封止体に実装し、封止体に半導体チップとの配線を行うための電極と封止体と封止体外部との接続を行うための電極を設ける。

#### 【0013】

この際に、半導体装置外からDRAMのリフレッシュを隠蔽するために、2つ以上のバンクを1チップに含むDRAMにメモリコントローラを接続してDRAMへのメモリアクセスを制御させる。前記メモリコントローラによって第1の期間にメモリアクセスが行われた場合には第1のバンクへアクセスを行い第2の期間にメモリアクセスが行われた場合には第2のバンクへアクセスを行うとよい。

20

#### 【0014】

更に、複数のメモリバンクから構成される、クロックに同期したコマンドにより読み出し/書き込みを行うダイナミック・ランダムアクセス・メモリ(DRAM)を使用して、複数のメモリバンクを同じメモリ容量を持つ第1メモリブロックと第2メモリブロックとに割り当てて、メモリへのアクセスを第1期間と第2期間が交互に行う。前記第1期間では、前記DRAMに対する読み出し/書き込みコマンドは前記第1メモリブロックに対して実行し、前記第2メモリブロックはリフレッシュを優先して実行する。また、前記第2期間において、前記DRAMに対する読み出し/書き込みコマンドは前記第2メモリブロックに対して実行するとともに、前記第1メモリブロックはリフレッシュを優先して実行すると良い。

30

#### 【0015】

#### 【発明の実施の形態】

以下、本発明の実施例を図面を用いて詳細に説明する。実施例の各ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような1個の半導体基板上に形成される。

#### 【0016】

#### <実施例1>

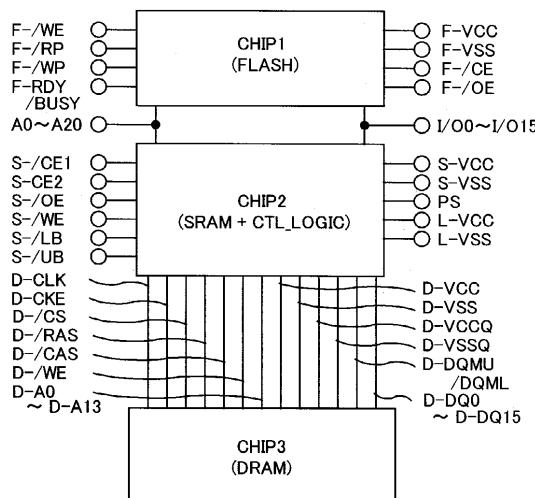

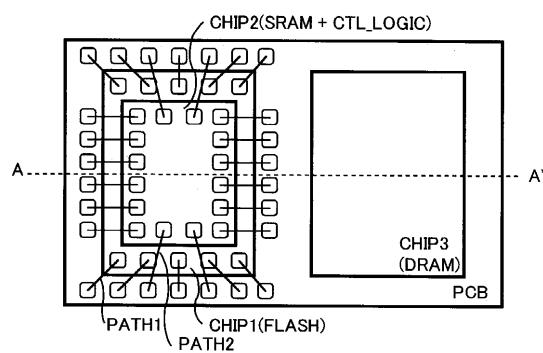

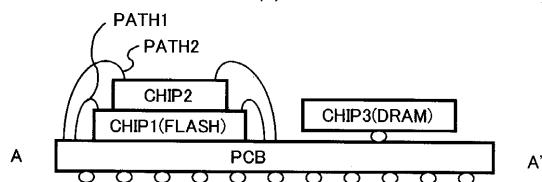

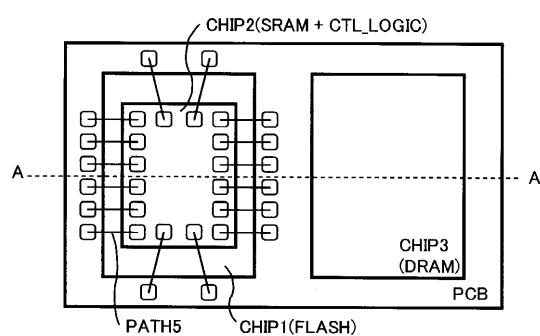

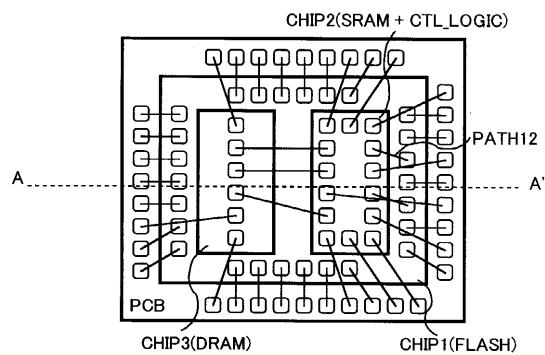

図1は本発明を適用した半導体集積回路装置の一例であるメモリモジュールの第一の実施例を示したものである。本メモリモジュールは3つのチップによって構成されている。以下に夫々のチップについて説明する。

40

#### 【0017】

まず、CHIP1(FLASH)は不揮発性メモリである。不揮発性メモリにはROM(リードオンリーメモリ)、EEPROM(エレクトリカリイレーサブルアンドプログラマブルROM)、フラッシュメモリ等を用いることが出来る。本実施例ではフラッシュメモリを例に説明する。CHIP2(SRAM+CTL\_LOGIC)にはスタティックランダムアクセスメモリ(SRAM)と制御回路(CTL\_LOGIC)が集積されている。制御回路はCHIP2に集積されたSRAMとCHIP3の制御を行う。CHIP3(DRAM)はダイナミックランダムアクセスメモリ(DRAM)である。DRAMは内部構成やインターフェイスの違いからEDO、SDRAM、DDR等様々な種類がある。本メモリモジュールにはいずれのDRA

50

Mでも用いることが出来るが、本実施例ではSDRAMを例に説明する。

#### 【0018】

このメモリモジュールには外部からアドレス(A0～A20)とコマンド信号(S-/CE1, S-CE2, S-/OE, S-/WE, S-/LB, S-/UB, F-/WE, F-/RP, F-/WP, F-RDY/BUSY, F-/CE, F-/OE)が入力される。電源はS-VCC, S-VSS, F-VCC, F-VSS, L-VCC, L-VSSを通して供給され、データの入出力にはI/00～I/015が用いられる。アドレス信号線及びデータ入出力線はCHIP1(FLASH)とCHIP2(SRAM)に共通して接続される。CHIP2はCHIP3の動作に必要となるクロック(D-CLK)、アドレス(D-A0～D-A13)、コマンド(D-CKE, D-/CS, D-/RAS, D-/CAS, D-/WE, D-DQMU/DQML)、DRAM用データ(D-DQ0～D-DQ15)、電源(D-VCC, D-VSS, D-VCCQ, D-VSSQ)を供給する。このメモリモジュールと外部との入手力ノードはDRAMのインターフェースのための信号端子は直接には見えなくしているところが特徴の一つである。従って、後の実施例の図16等で本発明のBGA(ボールグリッドアレイ)型パッケージについて説明するが、このパッケージで外部端子として利用される端子には、DRAMを制御するための信号端子は通常設けられない。これにより、ユーザはDRAMの存在が外部からはリフレッシュ隠蔽され記憶容量の増大のメリットを享受できるようになる。もっとも、BGA型パッケージの信号端子数が非常に多く余裕がある場合には、主に製造業者の製造時のテストの目的のためDRAMの制御端子を並列して外部に引き出すようにしてもよい。こうすることにより、製造業者は不良解析等が迅速に行えるようになる。もちろんこの機能は、通常はユーザには開放されない。

#### 【0019】

ここで各コマンド信号について簡単に説明する。CHIP2に入力されるS-/CE1, S-CE2はチップイネーブル信号、S-/OEはアウトプットイネーブル信号、S-/WEはライトイネーブル信号、S-/LBはロアーバイト選択信号、S-/UBはアッパーべイト選択信号である。CHIP1に入力されるF-/WEはライトイネーブル信号、F-/RPはリセット/ディープパワーダウン信号、F-/WPはライトプロテクト信号、F-RDY/BUSYはレディ/ビジニアウトプット信号、F-/CEチップイネーブル信号、F-/OEはアウトプットイネーブル信号でフラッシュメモリの制御に用いられる。

#### 【0020】

本メモリモジュールは共通したアドレス線(A0～A20)、データ入出力線(I/00～I/015)を用いてフラッシュメモリ、SRAM、DRAMへアクセスすることが出来る。

#### 【0021】

フラッシュメモリ(CHIP1)へアクセスする場合はアドレス線(A0～A20)の他、コマンド信号F-/WE, F-/RP, F-/WP, F-RDY/BUSY, F-/CE, F-/OEのうち必要な信号をアクティブにする。SRAM(CHIP2)又はDRAM(CHIP3)へアクセスする場合はアドレス線(A0～A20)の他、コマンド信号S-/CE1, S-CE2, S-/OE, S-/WE, S-/LB, S-/UBのうち必要な信号をアクティブにする。いずれのアクセスもいわゆるSRAMインターフェイス方式によって行われる。

#### 【0022】

SRAMへのアクセスとDRAMへのアクセスは入力されるアドレスの値によって区別される、入力されたアドレスの値によって制御回路(CTL\_LOGIC)がアクセス先を判定する。SRAMへのアクセスとなるアドレスの範囲とDRAMへのアクセスとなるアドレスの範囲は制御回路(CTL\_LOGIC)に設けられたレジスタにあらかじめ値を設定しておくことによって決められる。

#### 【0023】

DRAMへアクセスする場合にはDRAMへのアクセスに必要なアドレス信号やコマンド信号類を制御回路(CTL\_LOGIC)が生成し、DRAMへのアクセスを行う。リードアクセスの場合にはDRAMからの読み出しデータはDRAM用データI/O(D-DQ0～D-DQ15)から一旦制御回路(CTL\_LOGIC)に読み出され、その後メモリモジュールのデータ入出力線(I/00～I/015)へ出力される。ライトアクセスの場合は書き込みデータはメモリモジュールのデータ入出力線(I/00～I/015)から入力され、その後DRAM用データI/O(D-DQ0～D-DQ15)を通してDRAMに入力される。

#### 【0024】

DRAMへの電源はL-VCC、L-VSSから供給され、制御回路(CTL\_LOGIC)を通してD-VCC, D-VSS, 50

D-VCCQ, D-VSSQへ接続される。DRAMへの電源供給はコマンド信号PSによって制御され、必要に応じて切斷することが出来る。切斷したDRAMの電源を再投入する場合にはDRAMの初期化を行う必要がある。DRAMの初期化に必要な信号生成やタイミング制御は制御回路(CTL\_LOGIC)が行う。

#### 【0025】

また、DRAMのリフレッシュを行う場合には制御回路(CTL\_LOGIC)が定期的にリフレッシュコマンドを投入して行うことが出来る。一般にDRAMのリフレッシュ特性は高温時に悪化するが、制御回路(CTL\_LOGIC)に温度計を設けて高温時にリフレッシュコマンドの投入間隔を狭めることによってDRAMをより広い温度範囲で使用することが出来る。

#### 【0026】

さらに、制御回路(CTL\_LOGIC)によって1つのデータをDRAMの異なった2個所のアドレスに保持させた上で、リフレッシュを行うタイミングを調整することによってメモリモジュール外部からはリフレッシュ動作によってアクセスに制限が生じないようリフレッシュを隠蔽する。

#### 【0027】

以上説明した実施例によれば、SRAMインターフェイス方式を踏襲しながら安価な汎用DRAMを用いた大容量メモリモジュールが実現出来る。本発明によるメモリモジュールではDRAMが使用されているがDRAMに必要なリフレッシュはモジュール内部で実行されるためSRAMと同様にリフレッシュを考慮せずに使用することが出来る。また、モジュール内部で実行されるリフレッシュの間隔を温度によって変えることによってDRAMの使用温度範囲を広げることが可能となり、使用温度範囲の広い大容量メモリモジュールが実現できる。

#### 【0028】

さらに、DRAMにおけるデータ保持の二重化とリフレッシュを行うタイミングを調整することによりDRAMのリフレッシュをメモリモジュール外部から隠蔽することが出来るため、本メモリモジュールにアクセスする場合にリフレッシュを考慮してタイミングを調整する必要は無い。従って従来のSRAMだけを用いたメモリモジュールと同様に使用することが出来るため、従来システムを変更せずに大容量メモリモジュールを使用することが出来る。

#### 【0029】

本発明の別の目的はデータ保持電流の少ないメモリモジュールを実現することである。この目的のためにはDRAMへ供給する電源を切斷し、SRAMに記憶されたデータだけを保持すればよい。保持すべきデータだけをSRAMに記憶して、保持する必要の無いデータが記憶されたメモリへの電源供給を停止することによって最小限のデータ保持電流で必要なデータだけを保持することが可能である。

#### 【0030】

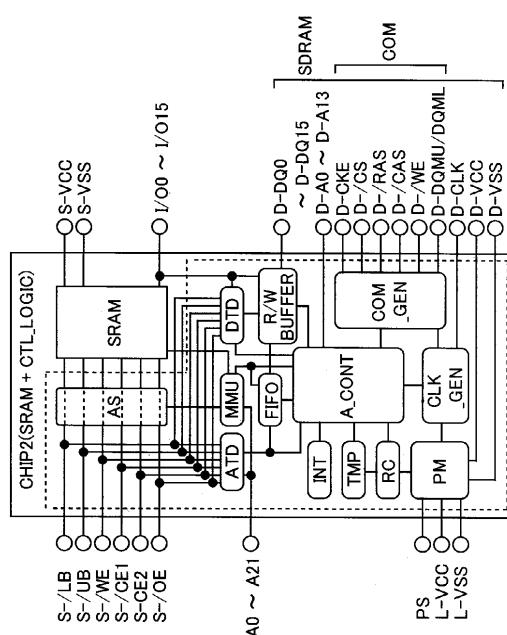

図2はCHIP2(SRAM+CTL\_LOGIC)を示したものである。CHIP2(SRAM+CTL\_LOGIC)はSRAMと制御回路(CTL\_LOGIC)から構成されており、集積されるSRAMは従来より一般的に使用されている非同期SRAMである。制御回路(CTL\_LOGIC)はCHIP2のSRAM以外の部分で、図2では破線に囲まれた領域として示されており、AS、MMU、ATD、DTD、FIFO、R/W BUFFER、A\_CONT、INT、TMP、RC、PM、CLK\_GEN、COM\_GENによって構成される。

#### 【0031】

外部よりアドレスが入力されるとメモリマネージメントユニットMMUは設定された値に従って入力されたアドレスを変換し、アクセスを行うメモリを選択する。SRAMが選択された場合にはアクセススイッチ(AS)によってSRAMへコマンド信号が送られ、SRAMへのアクセスが行われる。アドレストランジションディテクタ回路(ATD)はアドレス信号とコマンド信号の変化を検出してパルスを出力する。データトランジションディテクタ回路(DTD)はデータ信号とコマンド信号の変化を検出してパルスを出力する。R/W BUFFERはDRAMの読み出し、書き込みの為にデータを一時的に保持する。ファーストインファーストアウトメモリ FIFOは先入れ先出しのバッファ回路でDRAMへ書き込みデータとそのアドレスを一時的に保持する。初期化回路INTはDRAMへの電源供給開始時にDRAMの初期化を行う。温度計測モジュール(TMP)は温度を検出し、検出した温度に応じた信号をRCとA\_CONTに出力する。RCはリフ

10

20

30

40

50

レッシュカウンタで、DRAMのリフレッシュ間隔にあわせてリフレッシュを行うアドレスを生成する。また、温度計測モジュール(TMP)の出力信号によって温度に応じたリフレッシュ間隔の変更を行う。パワーモジュール(PM)はCHIP2の制御回路(CTL\_LOGIC)と DRAMへの電源供給及び電源の制御を行う。クロックジェネレータ(CLK\_GEN)はクロックを生成し、DRAMと制御回路(CTL\_LOGIC)へ供給する。コマンドジェネレータ(COM\_GEN)はDRAMへのアクセスに必要なコマンドを生成する。アクセスコントローラ(A\_CONT)はCHIP2 (SRAM+CTL\_LOGIC)全体動作の制御と、DRAMへアクセスを行うためのアドレスを発生する。

#### 【 0 0 3 2 】

CHIP2(SRAM+CTL\_LOGIC)へメモリアクセスを行うには従来より一般に使用されている非同期SRAM方式でインターフェイスする。外部からアドレス(A0～A21)がCHIP2 (SRAM+CTL\_LOGIC)に入力されるとまずMMUによってアドレスの値が変換される。変換のパターンはあらかじめMMU内部のレジスタに入力した値によって決められる。変換されたアドレスによってアクセス先がSRAMなのかDRAMなのかが決定する。10

#### 【 0 0 3 3 】

SRAMへアクセスが行われる場合にはMMUは変換したアドレスをSRAMへ送ると同時に、アドレスアクセススイッチ(AS)にコマンド転送を指示する。アドレスアクセススイッチ(AS)はコマンドをSRAMへ転送し、SRAMへのアクセスが開始される。これ以降の動作はいわゆる非同期SRAMへのアクセスが行われる。

#### 【 0 0 3 4 】

DRAMへリードアクセスを行う場合について制御回路の各ブロックの動作を以下に説明する。まず、外部から入力されてMMUによって変換されたアドレスとATDで検知されたコマンドがA\_CONTに送られる。A\_CONTは送られたアドレスとコマンドからDRAMへのアクセスの実行を判断し、COM\_GENにDRAMへのコマンド発行を指示する。また、A\_CONTはMMUから受け取ったアドレスをDRAM用に変換してDRAMへ出力する。COM\_GENはCLK\_GENが生成したクロックに同期してDRAMにコマンドを発行する。コマンドとアドレスを受け取ったDRAMはデータを出力し、出力されたデータはR/W BUFFERを介してI/00～I/015へ転送されてリードアクセスが終了する。20

#### 【 0 0 3 5 】

DRAMへライトアクセスを行う場合は、外部から入力されMMUによって変換されたアドレスとATDで検知されたコマンド及びDTDで検知されたコマンドとデータがA\_CONTに送られる。A\_CONTは送られたアドレスとコマンドからDRAMへのアクセスの実行を判断し、COM\_GENにDRAMへのコマンド発行を指示する。また、A\_CONTはMMUから受け取ったアドレスをDRAM用に変換してDRAMへ出力する。COM\_GENはCLK\_GENが生成したクロックに同期してDRAMにコマンドを発行する。書き込まれるデータはI/00～I/015から入力されR/W BUFFERに一旦保持された後、DRAMに送られて書き込みが行われる。この他、このように書き込みが行われたデータとアドレスはFIFOにも保持され、後でDRAMの別のバンクにも書き込みが行われる。30

#### 【 0 0 3 6 】

DRAMへ供給される電源はパワーモジュール(PM)によって制御される。メモリモジュールが実装された機器は動作状態に応じて消費電流を削減したい場合がある。そのような場合にはパワーモジュールは、例えばコマンド信号PSに従ってリフレッシュカウンタが行うリフレッシュを停止させてDRAMのリフレッシュに必要な電力を削減することが出来る。さらに消費電力を削減したい場合にはメモリモジュール内部においてDRAMへ供給する電源を切断すればよい。この場合にはパワーモジュールは機器が出力するコマンド信号PSにしたがってDRAMへ供給されるD-VCCへの電力供給を停止する。40

#### 【 0 0 3 7 】

この上、一段と消費電力を削減したい場合はパワーモジュールがコマンド信号PSにしたがってCHIP2(SRAM+CTL\_LOGIC)のうちDRAMへのメモリアクセスに関与する部分への電源供給を停止すれば良い。この状態では例えばCHIP2(SRAM+CTL\_LOGIC)のうちSRAMの他にはMMUとASだけに電源を接続して動作状態とし、SRAMへのアクセスだけを実行するモードとすることが可能である。50

**【 0 0 3 8 】**

さらにコマンドPSによってSRAMのデータ保持だけを行う動作状態とすることも可能である。この様な場合にはSRAMへ接続される電源(S-VCC, S-VSS)以外を切断し、メモリへのアクセスは禁止される。この状態でメモリモジュールはSRAMに記憶されたデータの保持を行う。

**【 0 0 3 9 】**

一旦電源供給を停止して動作を停止したDRAMを再び動作させるためには電源供給の再開の他、DRAMの初期化を行う必要がある。初期化方法は一般的なものだが本メモリモジュールではイニシャル回路(INT)が初期化の手順をアクセスコントローラ(A\_CONT)に指示して初期化が実行される。

10

**【 0 0 4 0 】**

なお、DRAMのリフレッシュを停止した場合にもDRAMを再び動作させるためにはDRAMの初期化が必要であるが、やはりイニシャル回路(INT)が初期化の手順をアクセスコントローラ(A\_CONT)に指示して初期化が実行される

リフレッシュカウンタRCIはDRAMのリフレッシュ間隔に従ってリフレッシュ用アドレスを出力し、アクセスコントローラにリフレッシュの実行を要求する。アクセスコントローラはリフレッシュカウンタの要求に従って、外部から行われるDRAMへのアクセスと調停を取りながらリフレッシュコマンドを発行し、DRAMのリフレッシュを行う。

**【 0 0 4 1 】**

メモリーモジュールを高温で使用する場合にはDRAMのリフレッシュ間隔を短くして頻繁にリフレッシュを行うことが必要となる。この様な場合には温度計測モジュール(TMP)が温度を検出してリフレッシュカウンタとアクセスコントローラに通知する。高温になればリフレッシュカウンタはリフレッシュ間隔を短く変更してリフレッシュ用アドレスを出力する。

20

**【 0 0 4 2 】**

DRAMの動作に必要なクロック(D-CLK)はクロックジェネレータ(CLK\_GEN)で生成される。クロックジェネレータはDRAMの他、制御回路内の各ブロックにクロックを供給する。DRAMがクロックに同期して動作する場合はコマンドジェネレータ(COM\_GEN)のコマンド発行はクロックに同期して行われる。

**【 0 0 4 3 】**

30

DRAMのリフレッシュを停止することによって消費電力を削減することが出来る。DRAMの電源を遮断しSRAMだけにアクセスをおこなった場合には小記憶容量ながらより低電力で動作をおこなうことが可能である。この場合にはさらにDRAMへのアクセスに必要な制御回路への電源供給も停止し、より低電力で動作させることも出来る。さらにSRAMだけに電力を供給してSRAMに記憶されたデータだけを保持することによってより低消費電力なデータ保持モードが実現できる。DRAMに電源を再投入する場合にもDRAMの初期化を制御回路によっておこなえるため、外部からモジュールに対して初期化のための手続きを実行する必要はない。従って簡易に消費電力を削減するメモリモジュールが実現出来る。

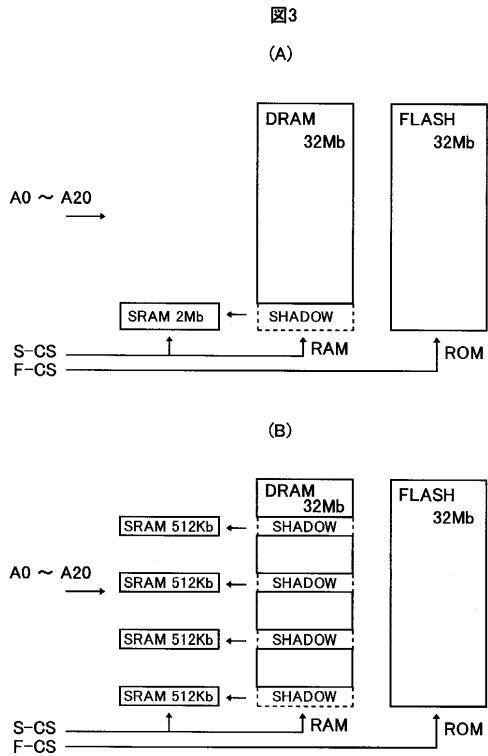

**【 0 0 4 4 】**

図3はMMUによって変換されるメモリマップの一例を示したものである。本実施例では特に限定されないが、不揮発メモリの記憶領域が32Mb、SRAMによるデータ保持領域が2Mb、DRAMの記憶領域が32Mbあるメモリモジュールを例に説明する。外部から入力されたアドレスA0～A20はフラッシュメモリ(CHIP1)とCHIP2で共用されている。アクセス先の選択にはチップ選択のための信号S-CS, F-CSを使用する。F-CSがアクティブとなった場合はCHIP1が選択されてアクセスが行われ、S-CSがアクティブとなった場合はCHIP2が選択されてアクセスが行われる。F-CSはCHIP1のアクセスに使用するコマンド信号F-/WE, F-/RP, F-/WP, F-RDY/BUSY, F-/CE, F-/OEの総称であり、S-CSはCHIP2のアクセスに使用するコマンド信号S-/CE1, S-/CE2, S-/OE, S-/WE, S-/LB, S-/UBの総称である。アクセス先にCHIP2が選択された場合はMMUがアドレスに応じてアクセスするメモリを選択する。

40

**【 0 0 4 5 】**

50

図3(A)に示したメモリマップの例ではアドレス空間の一部に集中してSRAM領域が設定されている。SRAMのアドレス空間はDRAMのアドレス空間に重なっており、重なったアドレス空間へのアクセスはSRAMに対して行われる。同じアドレス空間にあるDRAMはシャドー領域となりアクセスが行われない。

#### 【0046】

これに対して、図3(B)に示したメモリマップの例では複数のアドレス空間に分散してSRAM領域が設定されている。やはりSRAMのアドレス空間はDRAMのアドレス空間に重なっており、重なったアドレス空間へのアクセスはSRAMに対して行われる。この例ではSRAM領域が512kb単位で設定してあるが、これはFLASHメモリの書き込み消去単位に合わせており、アドレス空間の管理単位をFLASHメモリとそろえておくことによってOSやプログラムによって扱いやすくするためである。10

#### 【0047】

このようにMMUは指定したアドレス空間にSRAM領域やDRAM領域をわりあてることが出来る。特にデータ保持電流を少なくしたい場合には保持したいデータを格納するアドレス空間をSRAM領域に割り当て、DRAMへの電源供給を停止すればよい。この方法によってデータ保持電流の少ないメモリモジュールを実現することができる。

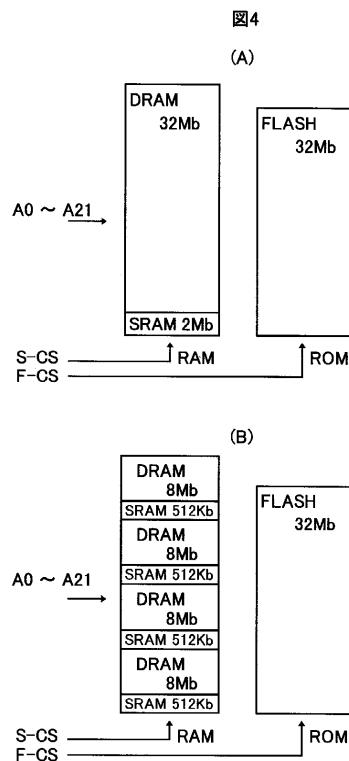

#### 【0048】

図4はMMUによって変換されるメモリマップの別の一例を示したものである。

#### 【0049】

図4(A)に示したメモリマップの例ではアドレス空間の一部に集中してSRAM領域が設定されている。図3(A)に示したメモリマップの例との違いはSRAMのアドレス空間とDRAMのアドレス空間に重なりがないことである。DRAMにシャドー領域が発生しないためDRAMのメモリ空間を有効に利用することが出来る。図4(B)も同様に図3(B)に示したメモリマップの例とはSRAMのアドレス空間とDRAMのアドレス空間に重なりが無い。DRAMにシャドー領域が発生しないためDRAMのメモリ空間を有効に利用することが出来る。図4(A)、図4(B)に示したメモリマップを行うとアドレス空間が2Mbほど増加する。これに対応するにはアドレス線A21を追加すれば良い。このように図4(A)、図4(B)に示したメモリマップではDRAMの記憶領域をより有効に使用することが出来る。20

#### 【0050】

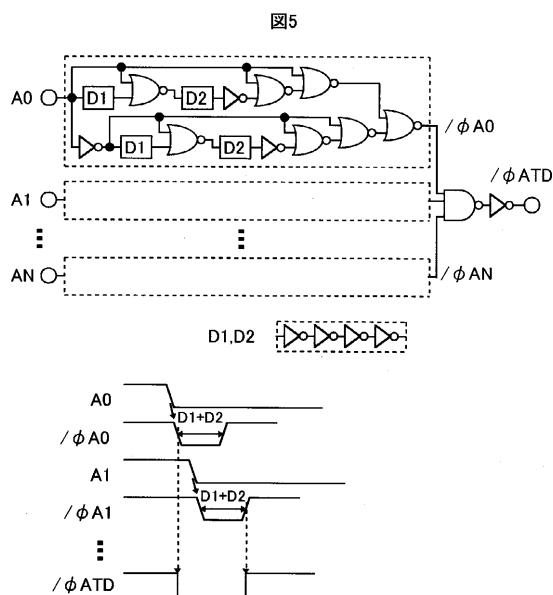

図5はATD回路の構成例と動作波形を示したものである。アドレストランジションディテクション回路(ATD)はアドレス信号線の値が変化したことを検知してパルスを発生するものである。回路図面で使用されているD1、D2の記号はそれぞれ遅延を発生するためのディレイエレメントを表している。ATDはアドレス線(A0～AN)に変化が生じるとディレイエレメントD1とディレイエレメントD2による遅延を足し合わせた幅のパルス(/ A0～/ AN)を出力する。さらに個々のアドレス線の動作ばらつきを勘案し、これらのパルスを足し合わせた信号/ ATDを生成することによってアドレス線に現れるアドレス値が変化したことが検知される。図2に示されているようにATDにはアドレス線だけではなくコマンド信号も接続して新たなコマンドが入力されたことを検出する。データトランジションディテクション回路(DTD)の構成はATDと同様である。DTDはデータ線と書き込みのためのコマンド信号の変化を検出して書き込み用データと書き込みコマンドを認識する。30

#### 【0051】

このようにATDとDTDによって非同期に変化するSRAMインターフェイス信号を検出してメモリモジュールの動作を開始する。これらの回路によって非同期SRAMインターフェイスによって動作するメモリモジュールが実現できる。非同期に変化する信号をパルス化して検知するため、メモリモジュール内部で同期式の動作をするメモリデバイスを使用することも可能である。40

#### 【0052】

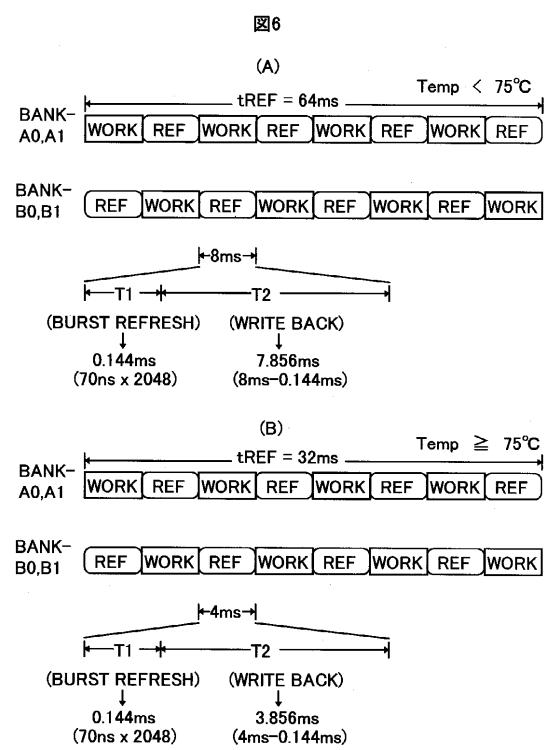

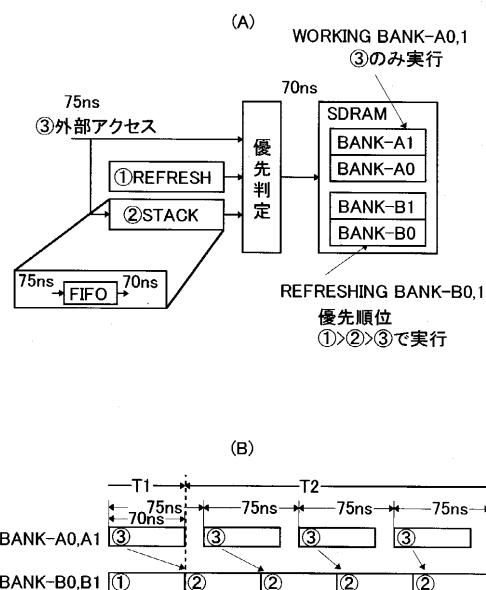

図6はDRAMのリフレッシュを隠蔽することを目的にDRAMを時間分割して動作させる様子を示した。ここでは1チップが4つのバンクで構成されているDRAMを例に説明する。4つのバンクBANK-A0, BANK-A1, BANK-B0, BANK-B1をBANK-A0, BANK-A1とBANK-B0, BANK-B1の2つ50

の組に分けて2つの組は同じアドレス空間にマッピングする。つまり、一つのアドレスで指定されるメモリセルが2つの組に夫々存在し、データが2倍冗長に記憶されている。

#### 【0053】

図6(A)にはDRAMの通常使用温度範囲である75°C以下の動作を示した。通常DRAMのメモリセルは64msに1回リフレッシュを行う必要があるが、その64msを8msづつ8期間に分割してBANK-A0、A1の組とBANK-B0、B1の組で交互に動作させる。図面でWORKと表示されたWORK期間はそのバンクの組が動作する期間を表しており、最初のWORK期間中はBANK-A0、A1の組が動作している。

#### 【0054】

DRAMへのリードアクセスが行われた場合にはWORK期間中であるBANK-A0、A1の組から読み出しが行われる。ライトアクセスが行われた場合はWORK期間中のBANK-A0、A1の組へ書き込みが行われるほか、書き込まれるデータとアドレスがFIFOに一時保管される。保管されたデータは期間T2においてBANK-B0、B1の組へも書き込まれる。期間T2については後述する。BANK-A0、A1がWORK期間中はBANK-B0、B1はREF期間である。REF期間中にBANK-B0、B1の組のバンクの半分の領域にリフレッシュが行われる。REF期間は連続してリフレッシュを行うT1期間とREF期間中に行われた書き込みをFIFOから書き戻すT2期間に分けられる。

10

#### 【0055】

リフレッシュに要する時間を一回あたり70nsとするとリフレッシュに必要な時間は70ns X 2048回で0.144msとなる。従ってT2期間は7.856ms(8ms - 0.144ms)となる。ここで、メモリモジュールには75nsに一回アクセスが行われると仮定する。REF期間中に行われたアクセスが全てライトアクセスだとするとその最大回数は106667回(8ms/75ns)である。これをDRAMに書き込むのに必要な時間は7.47ms(106667回 X 70ns)でありT2期間(7.856ms)以下であるためREF期間中に行われるライトアクセスはT1期間においてリフレッシュを行ってもT2期間内に全て書き戻すことが出来る。

20

#### 【0056】

また、リフレッシュはREF期間中の2つのバンクで同時に実行することも出来る。この場合にはT1期間に1つのバンクで実行されるリフレッシュの回数は半分の1024回になるのでT1期間を半分に短縮出来る。T1期間が短縮されればFIFOの記憶容量を減らすことが出来るほか、外部からアクセスされる間隔をより短くして高速なメモリが実現できる。

#### 【0057】

30

図6(B)はDRAMのリフレッシュ間隔を半分にした場合について示した。一般にDRAMのリフレッシュ特性は高温時に悪化する。従って例えば75°C以上の高温時には図示したようにリフレッシュ間隔を短くすることによってデータを保持することが可能である。本実施例では温度検出回路TMPによって温度を検出し、リフレッシュカウンタとアクセス制御回路(A\_CONT)によってリフレッシュ間隔を変更する。

#### 【0058】

この例では64msのリフレッシュ間隔を半分の32nsに短縮しており、一回のWORK期間とREF期間は夫々4msである。ここでも同様に、REF期間中に行われたアクセスが全てライトアクセスだとするとその最大回数は53334回(4ms/75ns)である。

これをDRAMに書き込むのに必要な時間は3.74ms(53334回 X 70ns)でありT2期間(3.856ms)以下であるためREF期間中に行われるライトアクセスはT1期間においてリフレッシュを行ってもT2期間内に全て書き戻すことが出来る。

40

#### 【0059】

このようにしてDRAMのリフレッシュを隠蔽することが出来る。本実施例により汎用のDRAMを使用しながらそのリフレッシュを隠蔽して非同期SRAMと同様に扱うことが出来るため、非同期SRAMインターフェイスでアクセス出来る大容量メモリモジュールを実現することが出来る。また、高温時にもDRAMを使用する場合にも本実施例のようにリフレッシュ間隔を短縮させるだけで簡単に実現することが出来る。本実施例ではDRAMの動作単位を2バンク毎としたが、メモリモジュールやメモリチップの構成に応じて変更しても良い。また、リフレッシュ間隔である64msを8つの期間に分割してWORK期間とREF期間にしたが、さらに細

50

かく分割すればデータとアドレスを保持するFIFOの記憶容量を少なくすることが出来る。逆に大きく分割すればWORK期間とREF期間の切り換え回数を減らせるため、切り換えに伴う制御回路が簡単に構成出来る。

#### 【0060】

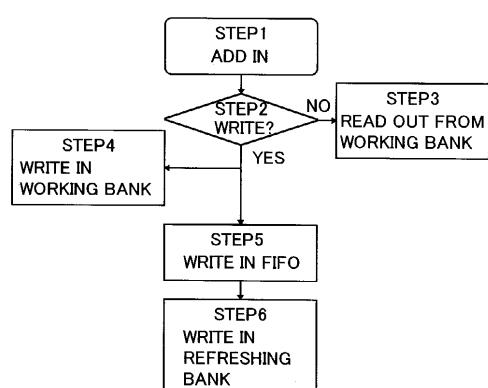

図7はCHIP3(DRAM)へのアクセスを説明するフローチャートである。STEP1ではアドレスが入力されて動作が開始する。STEP2ではコマンドからアクセスの種類が判定される。以降の動作はアクセスの種類によって異なる。アクセスが読み出しの場合はSTEP3に進む。STEP3ではWORK期間中のバンクからデータが読み出されて動作が終了する。アクセスが書き込みの場合はSTEP4及びSTEP5に進む。STEP4ではWORK期間中のバンクに書き込みが行われる。一方STEP5では書き込まれるデータとアドレスがFIFOに保持される。ここでREF期間中のバンクがT1期間からT2期間へ移行したらSTEP6に進みREF期間中のバンクにFIFOに保持されていたデータの書き込みを行う。10

#### 【0061】

この様にしてDRAMへの読み書きを行うことによって、リフレッシュの影響を排除することができるため大容量DRAMを用いて非同期SRAMインターフェイスのメモリモジュールを構成することができる。

#### 【0062】

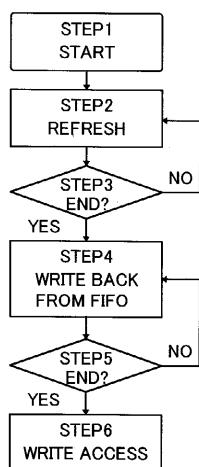

図8はCHIP3(DRAM)のREF期間中のバンクの動作を説明するフローチャートである。STEP1からSTEP3までがT1期間、STEP4からSTEP6まではT2期間である。STEP1でREF期間が開始しSTEP2で集中してリフレッシュが実行される。STEP3ではリフレッシュ回数が管理されており、決められた領域のリフレッシュが終了したらSTEP4に進み、FIFOに蓄積されたデータがバンクに書き込まれる。STEP5でFIFOに保持されたデータの書き込みが終了したと判断された場合はSTEP6に進みライトアクセスを受け付けることも出来る。但し、STEP4の状態のままFIFOへのデータ入力を待ってからライトアクセスを実行してもよい。20

#### 【0063】

以上説明したようにREF期間中のバンクを動作させれば、リフレッシュ動作とライトアクセスの実行をREF期間内に両立させることができる。これによりリフレッシュの影響を排除することができるため大容量DRAMを用いて非同期SRAMインターフェイスのメモリモジュールを構成することができる。

#### 【0064】

図9はDRAMへのアクセスに優先順位を付けた様子を示したものである。本発明にあるDRAMの動作はREF期間中のバンクへのアクセスに優先順位を付けて実行するという考え方で説明出来る。30

#### 【0065】

図9(A)はその優先順位を模式的に表したものである。この図に示したように、WORK期間中のBANK-A0、A1では外部からのアクセス 3 だけが行われる。これはREF期間中のBANK-B0,B1に対して優先的に実行される。一方、REF期間中のBANK-B0,B1ではリフレッシュ 1 、 FIFOに保持されたデータの書き込み 2 、外部からのライトアクセス 3 が行われる。これらの実行にはアクセス制御回路(A\_CONT)によって優先順位が付けられて上記 1 、 2 、 3 の優先順位で実行される。40

#### 【0066】

図9(B)はこれらのアクセスが優先順位に従って実行される様子を示したものである。ここではBANK-A0,A1がWORK期間中になっておりBANK-B0、B1がREF期間中である。BANK-A0,A1では外部アクセス 3 だけが実行されている。一方、BANK-B0、B1はちょうどT1期間からT2期間へ移り変わる所で、T1期間で実行されていたリフレッシュ 1 が終了してT2期間へ移行し、FIFOで保持されていたデータの書き込み 2 が実行されている。また、外部アクセスが75nsで行われるのに対して内部動作は70nsで実行されるのでFIFOで保持されていたデータの処理が外部アクセスより高速に進んでいる。

#### 【0067】

以上説明したようにWORK期間中及びREF期間中のバンクを動作させれば、REF期間中のバン50

クにリフレッシュ動作とFIFOに保持されたデータの書き込みを実行しながらWORK期間中のバンクが外部からのアクセスを実行することができる。この動作方法によってリフレッシュの影響を排除することができるため大容量DRAMを用いて非同期SRAMインターフェイスのメモリモジュールを構成することが出来る。

#### 【0068】

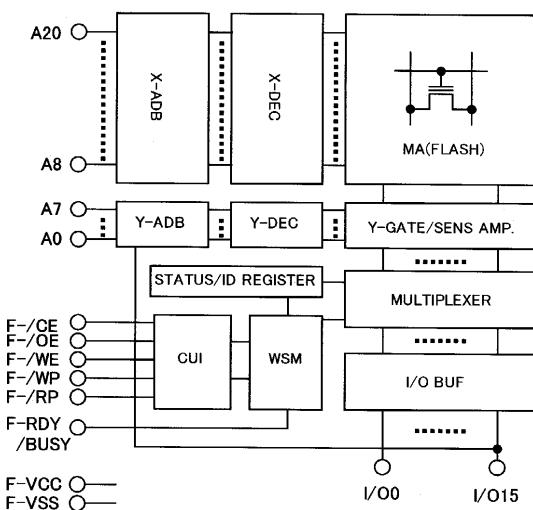

図10は本実施例におけるCHIP1(FLASH)の構成例である。XアドレスバッファX-ADB, XデコーダX-DEC, メモリアレイMA, YアドレスバッファY-ADB, YデコーダY-DEC, Yゲート(カラムスイッチ) & センスアンプ回路Y-GATE/SENS AMP., 状態 / ID 保持レジスタSTAT US / ID REG, マルチプレクサMULTIPLEXER, データ入出力バッファI/O BUF, 書き込み及び消去の制御回路であるライトステートマシンWSM, コマンドのデコード及び実行のためのコマンドユーザインターフェイスCUIより構成されている。CHIP1の動作は従来から一般的に使用されているFLASHメモリと同様である。このCHIP1(FLASH)によって本実施例であるメモリモジュールが構成出来る。

#### 【0069】

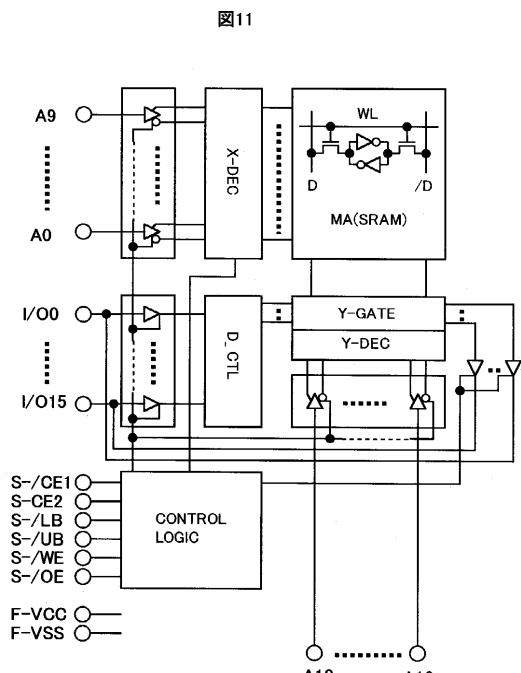

図11は本実施例におけるSRAMの構成例を示したものである。XデコーダX-DEC, メモリアレイMA, YゲートY-GATE, YデコーダY-DEC, 入力データ制御回路D\_CTL, 制御回路CONT ROL LOGICと各信号線の入出力バッファから構成されている。このSRAMは一般的ないわゆる非同期SRAMである。このSRAMによって本実施例であるメモリモジュールが構成出来る。

#### 【0070】

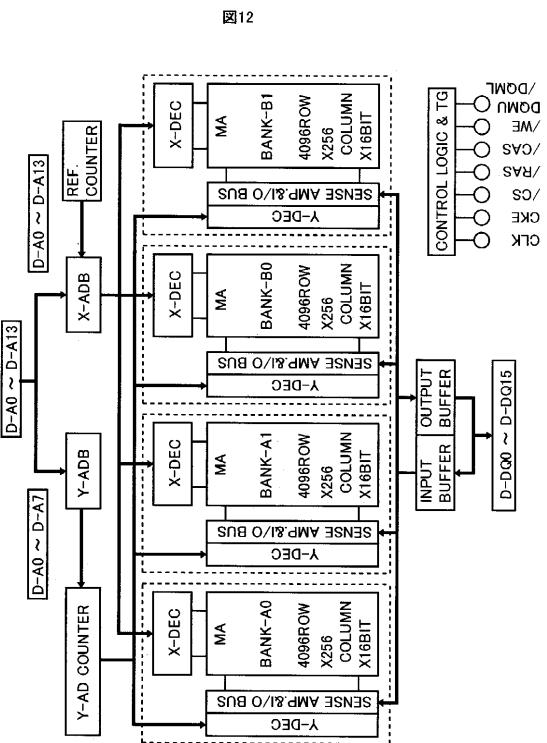

図12は本実施例におけるDRAMの構成例を示したものである。XアドレスバッファX-ADB, リフレッシュカウンタREF. COUNTER, XデコーダX-DEC, メモリアレイMA, YアドレスバッファY-ADB, YアドレスカウンタY-AD COUNTER, YデコーダY-DEC, メモリアレイMA, センスアンプ回路 & Yゲート(カラムスイッチ) SENS AMP.& I/O BUS, 入力データバッファ回路INPUT BUFFER, 出力データバッファ回路OUTPUT BUFFER, 制御回路 & タイミング発生回路CONTROL LOGIC & TGで構成されている。DRAMは従来より用いられている汎用SDRAMである。特に制限されないが具体的には4個の独立動作可能なメモリバンクを含み、それらに対するアドレス入力端子及びデータ入出力端子は共通化されバンク毎に時分割で利用される。このDRAMによって本実施例であるメモリモジュールが構成出来る。

#### 【0071】

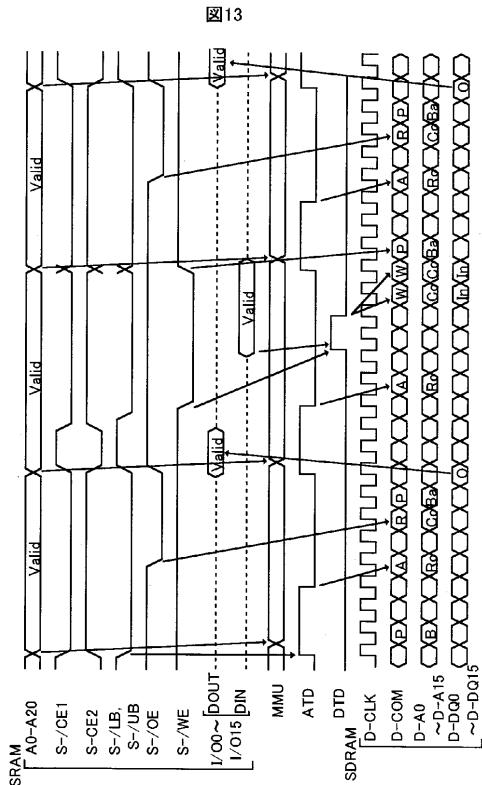

図13は本発明のメモリモジュールの動作波形の一例を示したものである。A0～A20, S-/CE1, S-CE2, S-/LB, S-/UB, S-/OE, S-/WEはメモリモジュールへ入力される信号で、いわゆる非同期SRAMのインターフェイス信号である。データ入出力信号I/00～I/015はデータの入力と出力を分けて夫々DIN、DOUTとして表した。MMU, ATD, DTDは夫々MMU回路、ATD回路、DTD回路の出力信号を表している。D-CLKはDRAMへ供給されるクロック、D-COMはDRAMへ供給されるコマンド信号の総称、D-A0～D-A15はDRAMのアドレス線、D-DQ0～D-DQ15はDRAMのI/O線である。

#### 【0072】

まず、最初に行われているリードアクセスについて説明する。アドレスA0～A20が入力されるとMMU回路は変換したアドレスを出力する。ATD回路はアドレスA0～A20とコマンド類(S-/CE1, S-CE2, S-/LB, S-/UB, S-/OE, S-/WE)の変化を検知し、アドレスとコマンドが確定するとパルスを出力する。このパルスをきっかけにDRAMへバンクアクティブコマンドAが発行され、DRAMはバンクアクティブ状態にされる。次に制御回路はS-/OE信号の立ち下がりをきっかけにリードコマンドRを発行する。DRAMから読み出されたデータはD-DQ0～D-DQ15に出力され、一旦R/W BUFFERを通してからI/00～I/015へ出力される。

#### 【0073】

次のサイクルではライトアクセスの実行例を示した。ライトアクセスの場合もリードアクセスと同様にATD信号の立ち下がりをきっかけにバンクアクティブコマンドAが発行される。その後、DTD回路がI/00～I/015とコマンド類(S-/CE1, S-CE2, S-/LB, S-/UB, S-/OE, S-/WE)の変化を検知してパルスを出力し、このパルスをきっかけにライトコマンドが実行される。書き込まれるデータはライトアクセスの終了を示すS-/WEの立ち上がりで確定す

10

20

30

40

50

るため、ライトコマンドはS-/WEが立ち上がるまで連続して発行される。これはライトサイクル開始後に書込まれるデータが変化した場合にも対応するためである。図13に示した動作例では2回のライトコマンドが連続して発行され、その後S-/WE信号の立ち上がりにしたがってライトが終了し、プリチャージコマンドが発行されている。

#### 【0074】

以上説明した実施例によれば、SRAMインターフェイス方式を踏襲しながら安価な汎用DRAMを用いた大容量メモリモジュールが実現出来る。本発明による制御回路(CTL\_LOGIC)ではDRAMが使用されているがDRAMに必要なリフレッシュは制御回路(CTL\_LOGIC)によって実行されるためSRAMと同様にリフレッシュを考慮せずに使用することが出来る。さらに、DRAMにおけるデータ保持の二重化とリフレッシュを行うタイミングを調整することによりDRAMのリフレッシュをメモリモジュール外部から隠蔽することが出来るため、本メモリモジュールにアクセスする場合にリフレッシュを考慮してタイミングを調整する必要は無い。従つて従来のSRAMだけを用いたメモリモジュールと同様に使用することが出来るため、従来システムを変更せずに大容量メモリモジュールを使用することが出来る。

#### 【0075】

<実施例2>

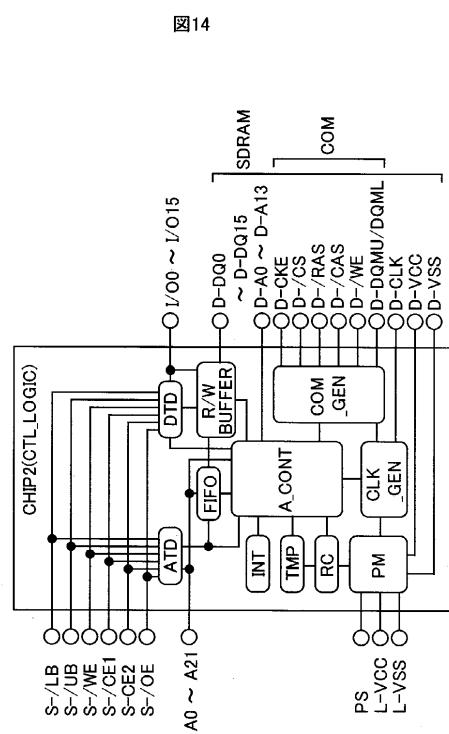

図14は本発明におけるメモリモジュールを構成するCHIP2の別の実施例を示したものである。

#### 【0076】

本実施例におけるCHIP2(CTL\_LOGIC)は制御回路(CTL\_LOGIC)から構成されており、ATD、DTD、FIFO、R/W BUFFER、A\_CONT、INT、TMP、RC、PM、CLK\_GEN、COM\_GENによって構成される。図2に示したCHIP2とはSRAM、アクセススイッチAS、MMUが内蔵されていない点が異なる。したがって、全てのアクセスはDRAMに対して実行される。以下でその動作を説明する。

#### 【0077】

アドレストランジションディテクタ回路(ATD)はアドレス信号とコマンド信号の変化を検出してパルスを出力する。データトランジションディテクタ回路(DTD)はデータ信号とコマンド信号の変化を検出してパルスを出力する。R/W BUFFERはDRAMの読み出し、書き込みの為にデータを一時的に保持する。FIFOは先入れ先出しのバッファ回路でDRAMへ書き込みデータとそのアドレスを一時的に保持する。INTはDRAMへの電源供給開始時にDRAMの初期化を行う。温度計測モジュール(TMP)は温度を検出し、検出した温度に応じた信号をRCとA\_CONTに出力する。RCはリフレッシュカウンタで、DRAMのリフレッシュ間隔にあわせてリフレッシュを行うアドレスを生成する。また、温度計測モジュール(TMP)の出力信号によって温度に応じたリフレッシュ間隔の変更を行う。パワーモジュール(PM)はCHIP2の制御回路(CTL\_LOGIC)とDRAMへの電源供給及び電源の制御を行う。クロックジェネレータ(CLK\_GEN)はクロックを生成し、DRAMと制御回路(CTL\_LOGIC)へ供給する。コマンドジェネレータ(COM\_GEN)はDRAMへのアクセスに必要なコマンドを生成する。アクセスコントローラ(A\_CONT)はCHIP2(CTL\_LOGIC)全体動作の制御と、DRAMへアクセスを行うためのアドレスを発生する。

#### 【0078】

CHIP2(CTL\_LOGIC)には非同期SRAM方式でインターフェイスされる。外部から非同期SRAM方式で信号が送られるとCHIP2はこれを変換してDRAMへアクセスを行う。データ入出力やリフレッシュ動作をCHIP2が制御する。

#### 【0079】

DRAMヘリードアクセスを行う場合について制御回路の各ブロックの動作を以下に説明する。まず、外部から入力されたアドレスとATDで検知されたコマンドがA\_CONTに送られる。A\_CONTは送られたアドレスとコマンドからDRAMへのアクセスの実行を判断し、COM\_GENにDRAMへのコマンド発行を指示する。また、A\_CONTは受け取ったアドレスをDRAM用に変換してDRAMへ出力する。COM\_GENはCLK\_GENが生成したクロックに同期してDRAMにコマンドを発行する。コマンドとアドレスを受け取ったDRAMはデータを出力し、出力されたデータは

10

20

30

40

50

R/W BUFFERを介してI/00～I/015へ転送されてリードアクセスが終了する。

#### 【0080】

DRAMへライトアクセスを行う場合は、外部から入力されたアドレスとATDで検知されたコマンド及びDTDで検知されたコマンドとデータがA\_CONTに送られる。A\_CONTは送られたアドレスとコマンドからDRAMへのアクセスの実行を判断し、COM\_GENにDRAMへのコマンド発行を指示する。やはり、A\_CONTは受け取ったアドレスをDRAM用に変換してDRAMへ出力する。COM\_GENはCLK\_GENが生成したクロックに同期してDRAMにコマンドを発行する。書込まれるデータはI/00～I/015から入力されR/W BUFFERに一旦保持された後、DRAMに送られて書き込みが行われる。この他、書き込みが行われたデータとアドレスはFIFOにも保持され、後でDRAMの別のバンクにも書き込みが行われる。なお、メモリへのアクセス以外の動作は実施例1で説明したものと同様である。10

#### 【0081】

以上説明した実施例によれば、SRAM、アクセススイッチASとMMUを内蔵せずより小さな面積でCHIP2が構成できるため、安価に大容量メモリモジュールを実現することが出来る。また、アクセススイッチASとMMUの動作を介せずDRAMへアクセスを行うことが出来るためより高速な大容量メモリモジュールが実現出来る。なお、本実施例によるその他の効果は実施例1で既に説明したものと同様である。

#### 【0082】

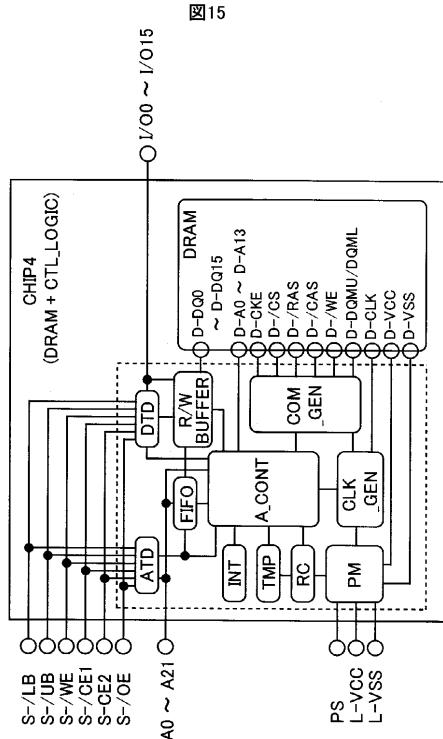

<実施例3>

図15は本発明におけるメモリモジュールを構成するCHIP2及びCHIP3の第三の実施例を示したものである。本実施例におけるCHIP4(DRAM+CTL\_LOGIC)は制御回路(CTL\_LOGIC)とDRAMから構成されており、制御回路を構成するATD、DTD、FIFO、R/W BUFFER、A\_CONT、INT、TMP、RC、PM、CLK\_GEN、COM\_GENとDRAMとが1チップに集積されている。図14に示したCHIP2にDRAMを混載した構成となっている。以下でその動作を説明する。20

#### 【0083】

アドレストランジションディテクタ回路(ATD)はアドレス信号とコマンド信号の変化を検出してパルスを出力する。データトランジションディテクタ回路(DTD)はデータ信号とコマンド信号の変化を検出してパルスを出力する。R/W BUFFERはDRAMの読み出し、書き込みの為にデータを一時的に保持する。FIFOは先入れ先出しのバッファ回路でDRAMへ書き込みデータとそのアドレスを一時的に保持する。イニシャル回路(INT)はDRAMへの電源供給開始時にDRAMの初期化を行う。温度計測モジュール(TMP)は温度を検出し、検出した温度に応じた信号をリフレッシュカウンタ(RC)とアクセスコントローラ(A\_CONT)に出力する。リフレッシュカウンタはDRAMのリフレッシュ間隔にあわせてリフレッシュを行うアドレスを生成する。また、温度計測モジュール(TMP)の出力信号によって温度に応じたリフレッシュ間隔の変更を行う。パワーモジュール(PM)はCHIP4の制御回路(CTL\_LOGIC)とDRAMへの電源供給及び電源の制御を行う。クロックジェネレータ(CLK\_GEN)はクロックを生成し、DRAMと制御回路(CTL\_LOGIC)へ供給する。コマンドジェネレータ(COM\_GEN)はDRAMへのアクセスに必要なコマンドを生成する。アクセスコントローラ(A\_CONT)はCHIP4(DRAM+CTL\_LOGIC)全体動作の制御と、DRAMへアクセスを行うためのアドレスを発生する。CHIP4(DRAM+CTL\_LOGIC)へメモリアクセスを行うにはいわゆる非同期SRAM方式でインターフェイスする。外部から非同期SRAM方式で信号が送られると制御回路はこれを変換してDRAMへアクセスを行う。3040

#### 【0084】

DRAMへリードアクセスを行う場合について制御回路の各ブロックの動作を以下に説明する。まず、外部から入力されたアドレスがA\_CONTに送られる。アドレスの変化とコマンド信号がATDで検知され、ATDはパルスをA\_CONTへ出力する。A\_CONTは送られたアドレスとコマンドからDRAMへのアクセスの実行を判断し、COM\_GENにDRAMへのコマンド発行を指示する。また、A\_CONTは受け取ったアドレスをDRAM用に変換してDRAMへ出力する。COM\_GENはCLK\_GENが生成したクロックに同期してDRAMにコマンドを発行する。コマンドとアドレスを受け取ったDRAMはデータを出力し、出力されたデータはR/W BUFFERを介してI/00～I/01550

へ転送されてリードアクセスが終了する。

#### 【0085】

次にDRAMへライトアクセスを行う場合について説明する。外部から入力されたアドレスとATDで検知されたコマンド及びDTDで検知されたコマンドとデータがA\_CONTに送られる。A\_CONTは送られたアドレスとコマンドからDRAMへのアクセスの実行を判断し、COM\_GENにDRAMへのコマンド発行を指示する。また、A\_CONTは受け取ったアドレスをDRAM用に変換してDRAMへ出力する。COM\_GENはCLK\_GENが生成したクロックに同期してDRAMにコマンドを発行する。書込まれるデータはI/00～I/015から入力されR/W BUFFERに一旦保持された後、DRAMに送られて書き込みが行われる。この他、このように書き込みが行われたデータとアドレスはFIFOにも保持され、後でDRAMの別のバンクにも書き込みが行われる。

10

#### 【0086】

DRAMへ供給される電源はパワーモジュール(PM)によって制御される。メモリモジュールが実装された機器は動作状態に応じて消費電流を削減したい場合がある。そのような場合にはパワーモジュールはコマンド信号PSに従ってリフレッシュカウンタが行うリフレッシュを停止させてDRAMのリフレッシュに必要な電力を削減することが出来る。

#### 【0087】

さらに消費電力を削減したい場合にはCHIP4内部においてDRAMへ供給する電源を切断すればよい。この場合にはパワーモジュールは機器が出力するコマンド信号PSにしたがってDRAMへ供給されるD-VCCへの電力供給を停止する。

#### 【0088】

この上、一段と消費電力を削減したい場合はパワーモジュールがコマンド信号PSにしたがってCHIP4(DRAM+CTL\_LOGIC)のうちDRAMへのメモリアクセスに関する部分への電源供給を停止すれば良い。この状態では例えば、CHIP4(DRAM+CTL\_LOGIC)のうちATDだけに電源を接続して待機状態とすることが可能である。なお、これ以外の動作は実施例1で説明したものと同様である。

20

#### 【0089】

以上説明した実施例によれば、SRAMインターフェイス方式を踏襲しながらDRAMを用いた大容量メモリモジュールが実現出来る。本発明による効果は既に実施例1で説明したものに加えて次のようなものがある。

#### 【0090】

本実施例によれば、メモリモジュールの部品点数を削減してモジュールの組立工程を簡略化しコストを低減することが出来る。さらに、本実施例はメモリモジュールとして用いる他に、単体で大容量SRAMとして使用することも出来る。SRAMインターフェイス方式を踏襲しながら安価なDRAMを用いることによってより小さな面積で大容量SRAM互換チップが実現出来る

30

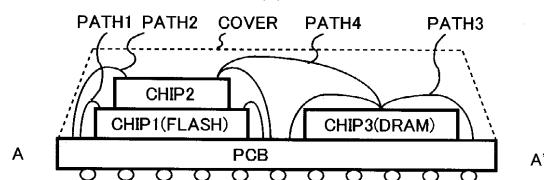

#### <実施例4>

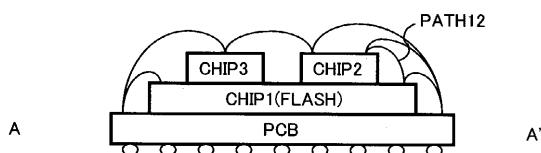

図16は本発明におけるメモリモジュールの第四の実施例を示したものである。図16(A)には上面図、図16(B)には断面図を示した。本メモリモジュールはボールグリッドアレイ(BGA)によって装置に実装する基盤(例えばガラスエポキシ基板でできたプリント回路ボードPCB)上にCHIP1(FLASH)とCHIP3(DRAM)が搭載されている。とくに制限されないが、CHIP3にはいわゆるチップの中央に信号及び電源パッド列が1列に並ぶ汎用DRAMのベアチップが使用されている。CHIP1(FLASH)の上面にはさらにCHIP2(SRAM+CTL\_LOGIC)が搭載されている。CHIP1と基盤上のボンディングパットはボンディングワイヤ(PATH1)で接続され、CHIP2と基盤上のボンディングパットはボンディングワイヤ(PATH2)で接続されている。CHIP3は基盤上のボンディングパッドとボンディングワイヤ(PATH3)で接続される他、CHIP2とボンディングワイヤ(PATH4)でも接続される。チップの搭載された基盤上面は封止物となるレジン樹脂によりモールドが行われて各チップと接続配線を保護する。なお、さらにその上から金属、セラミック、あるいは樹脂のカバー(COVER)を使用しても良い。

40

#### 【0091】

本発明による実施例ではCHIP1上にCHIP2を搭載することができるため実装面積の小さなメ

50

モリモジュールを構成することができる。また、各チップを近接して配置することができるため、チップ間配線長を短くすることができます。チップ間の配線及び各チップと基盤間の配線をボンディングワイヤ方式で統一することによって少ない工程数でメモリモジュールを製造することができる。さらにチップ間をボンディングワイヤで直接配線することによって基盤上のボンディングパット数とボンディングワイヤの本数を削減して少ない工程数でメモリモジュールを製造することができる。大量に量産される汎用DRAMのペアチップを用いることができるため、メモリモジュールを安価に安定供給することができる。樹脂のカバーを使用した場合にはより強靭なメモリモジュールを構成することができる。セラミックや金属のカバーを使用した場合には強度のほか、放熱性やシールド効果に優れたメモリモジュールを構成することができる。

10

#### 【0092】

図17は本発明におけるメモリモジュールの図16の変形例である。図17(A)には上面図、図17(B)には断面図を示した。この例ではCHIP3(DRAM)の基盤への実装及び配線にボールグリッドアレイ(BGA)が用いられている。この半導体チップの回路形成面を下にして半田バンプに代表される金属バンプを介して接続する方法はフェースダウンとも呼ばれる。この実装方法によってCHIP3と基盤間及びCHIP2とのボンディングが不要となりボンディング配線の本数を削減することができるため組立工数を削減出来る上、より信頼性の高いメモリモジュールが実現できる。

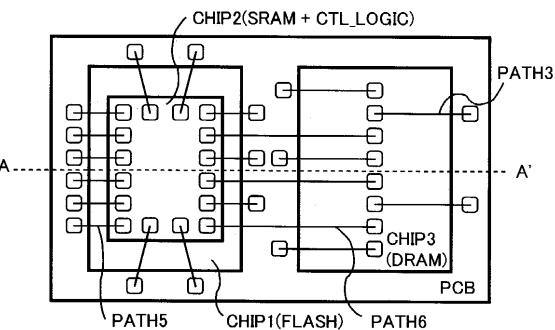

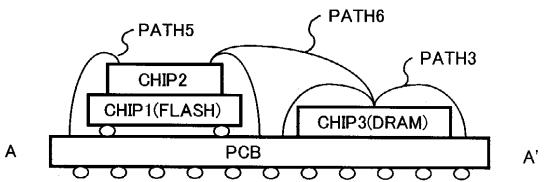

#### 【0093】

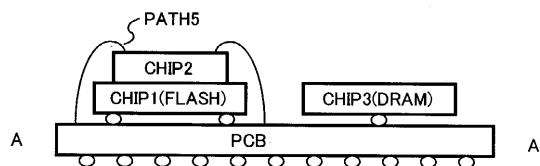

図18は本発明におけるメモリモジュールの図16の変形例である。図18(A)には上面図、図18(B)には断面図を示した。この例ではCHIP1(FLASH)の基盤への実装及び配線にボールグリッドアレイ(BGA)が用いられている。さらにCHIP1上に搭載されたCHIP2と基盤間の配線にはPATH5が用いられ、CHIP2とCHIP3との配線にはPATH6が用いられている。この実装方法によってCHIP1と基盤間のボンディングが不要となり配線本数を削減することができるため組立工数を削減出来る上、より信頼性の高いメモリモジュールが実現できる。また、CHIP1から基盤への配線が無いため高低差の大きなCHIP2から基盤への配線PATH5を低い配線密度で容易に行うことができる。PATH6も同様に配線の密度が下がる他、CHIP3の上面への配線のため高低差が緩和され、ボンディングを容易に行うことができる。

20

#### 【0094】

図19は本発明におけるメモリモジュールの図16変形例である。図19(A)には上面図、図19(B)には断面図を示した。この例ではCHIP1とCHIP3の基盤への実装にボールグリッドアレイが用いられている。ボンディング配線はCHIP2と基盤間だけ行えば良いので配線本数を削減することにより信頼性の高いメモリモジュールが実現できる。また、CHIP1から基盤への配線が無いためCHIP2への配線であるPATH5は配線の密度を下げることが可能となりボンディング工程を容易化することができる。

30

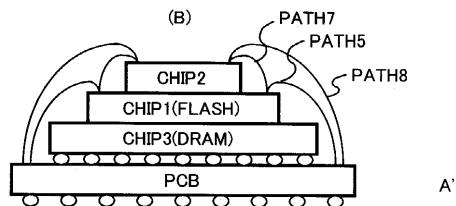

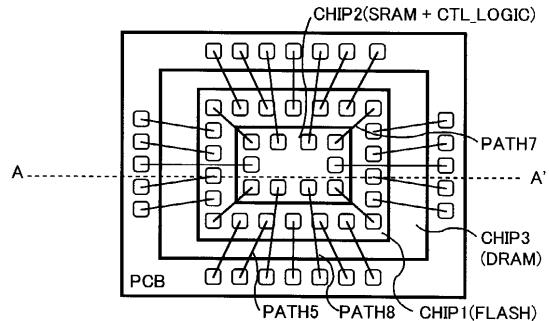

#### 【0095】

図20は本発明におけるメモリモジュールの図16の変形例である。図20(A)には上面図、図20(B)には断面図を示した。この例ではボールグリッドアレイで基盤に実装されたCHIP3の上にCHIP1が搭載され、さらにその上にCHIP2が搭載されている。最上位に搭載されたCHIP2とCHIP1との配線はPATH7によって行われる。またCHIP2と基盤との配線にはPATH8が用いられる。この実装方法によって3チップを積層することができるため、メモリモジュールの実装面積を小さくすることができます。CHIP2と基盤間の接続は配線PATH8を用いるほかに配線PATH5と配線PATH7を用いて信号を中継して接続することも出来る。中継して配線する方法を特にCHIP1とCHIP2に共通に使用される信号の配線に用いた場合には配線本数が削減できるためボンディング工程を簡略化できる。

40

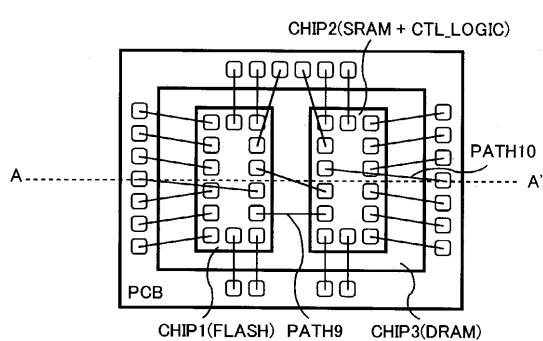

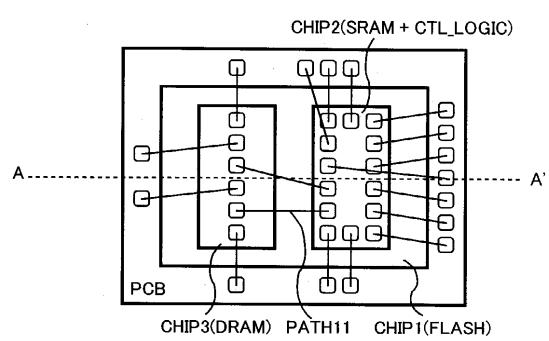

#### 【0096】

図21は本発明におけるメモリモジュールの図16の変形例である。図21(A)には上面図、図21(B)には断面図を示した。この例ではCHIP3がボールグリッドアレイによって基盤上に搭載されて、さらにその上にCHIP1とCHIP2が搭載されている。CHIP1とCHIP2の間の配線にはPATH9が用いられている。また、CHIP1及びCHIP2上にあってモジュールの中心側

50

に配置されたボンディングパットから基盤への配線にはPATH10が用いられている。

#### 【0097】

本実装方法は特にCHIP3の面積が大きい場合にはモジュールの実装面積を小さくする上で有効である。CHIP3をBGAで接続しているためボンディングによる配線の密度を下げられるため配線工程を簡易にすることが出来る。また、同じCHIP3上に搭載されたCHIP1とCHIP2はボンディングパットの高さをそろえやすく、CHIP1とCHIP2の間の配線PATH9は簡易に行えるため配線工程を簡易に行うことが出来る。配線PATH10によってCHIP1及びCHIP2上でモジュールの中心側に配置された配線パットと基盤間の配線を行うことが出来る。また、CHIP3の同一面上にCHIP1とCHIP2を配置することによってモジュールの高さが均一になるためより強固な封止体とすることが出来る。

10

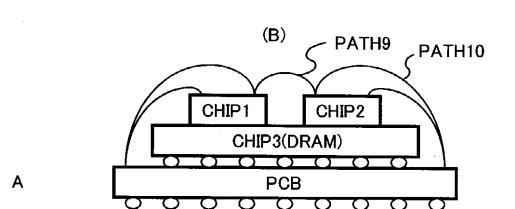

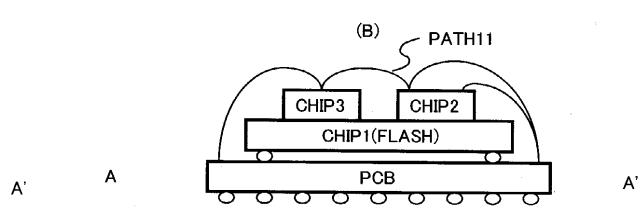

#### 【0098】

図22は本発明におけるメモリモジュールの図16の変形例である。図22(A)には上面図、図22(B)には断面図を示した。この例ではCHIP1がボールグリッドアレイによって基盤上に搭載されて、さらにその上にCHIP2とCHIP3が搭載されている。配線PATH11によってLOC形式のCHIP3とCHIP2の間の配線を行うことが出来る。

#### 【0099】

本実装方法は特にCHIP1の面積が大きい場合にモジュールの実装面積を小さくする上で有効である。CHIP1をBGAで接続しているためボンディングによる配線の密度を下げられるため配線工程を簡易にすることが出来る。また、同じCHIP1上に搭載されたCHIP3とCHIP2はボンディングパットの高さをそろえやすく、LOC形式のCHIP3とCHIP2の間の配線PATH11は簡易に行える。配線PATH11によってCHIP2上でモジュールの中心側に配置された配線パットとCHIP3の間の配線を行うことが出来る。また、CHIP3の同一面上にCHIP1とCHIP2を配置することによってモジュールの高さが均一になるためより強固な封止体とすることが出来る。

20

#### 【0100】

図23は本発明におけるメモリモジュールの第四の実施例を示したものである。図23(A)には上面図、図23(B)には断面図を示した。この例ではまずCHIP1が基盤上に搭載されて、さらにその上にCHIP2とCHIP3が搭載されている。配線PATH12によってCHIP1とCHIP2の間の配線を行うことが出来る。

#### 【0101】

30

本実装方法は特にCHIP1の面積が大きい場合にモジュールの実装面積を小さくする上で有効である。配線はすべてボンディングに統一されており、基盤の製作工程が簡易になる。また、同じCHIP1上に搭載されたCHIP3とCHIP2はボンディングパットの高さをそろえやすく、CHIP3とCHIP2の間の配線は簡易に行える。配線PATH12によってCHIP1とCHIP2の間の配線を行うことが出来る。特にCHIP1とCHIP2に共通に使用される信号の配線に用いた場合にはそれぞれの配線を基盤から接続する場合に比べて配線本数が削減できるためボンディング工程を簡略化できる。また、CHIP3の同一面上にCHIP1とCHIP2を配置することによってモジュールの高さが均一になるためより強固な封止体とすることが出来る。

#### 【0102】

#### 【発明の効果】

40

以上説明したように本発明によって得られる効果は以下の通りである。第一にDRAMへのアクセスをコントローラで制御することによって外部からリフレッシュを行う必要の無い大容量メモリが実現される。第二にデータ保持領域とワークエリアを設定してそれぞれ電源制御を行うことによってデータ保持電流の少ないメモリモジュールが実現される。第三に複数の半導体チップを一つの封止体に実装することによって実装面積の小さなメモリモジュールを提供できる。

#### 【図面の簡単な説明】

【図1】本発明を適用したメモリモジュールの構成図である。

【図2】図1のCHIP2の一例を示すプロック図である。

【図3】本発明を適用したメモリモジュールのアドレスマップの一例を示す説明図である

50

。【図4】本発明を適用したメモリモジュールのアドレスマップの一例を示す説明図である。

。【図5】図2のATD回路又はDTD回路の構成例である。

【図6】DRAMのリフレッシュ方式の一例を示す説明図である。

【図7】DRAMへアクセスを行った場合の処理の流れを示すフローチャートである。

【図8】REF期間中のDRAMのバンクにおける動作の流れを示すフローチャートである。

【図9】DRAMへのアクセスとリフレッシュを両立して行う様子を説明する説明図である。

【図10】フラッシュメモリの一構成例を示すブロック図である。

【図11】SRAMの一構成例を示すブロック図である。

10

【図12】DRAMの一構成例を示すブロック図である。

【図13】本発明を適用したメモリモジュールのタイミングチャートの一例である。

【図14】図1におけるCHIP2の一構成例を示すブロック図である。

【図15】本発明によるDRAMを利用した非同期SRAMインターフェイス方式の大容量メモリの実施例である。

【図16】本発明によるメモリモジュールの実装形態の一例である。

【図17】本発明によるメモリモジュールの実装形態の一例である。

【図18】本発明によるメモリモジュールの実装形態の一例である。

【図19】本発明によるメモリモジュールの実装形態の一例である。

【図20】本発明によるメモリモジュールの実装形態の一例である。

20

【図21】本発明によるメモリモジュールの実装形態の一例である。

【図22】本発明によるメモリモジュールの実装形態の一例である。

【図23】本発明によるメモリモジュールの実装形態の一例である。

#### 【符号の説明】

CHIP1...不揮発性メモリ、 CHIP2...制御回路(CTL\_LOGIC)またはスタティックランダムアクセスメモリ(SRAM)と制御回路(CTL\_LOGIC)が集積された半導体チップ、 CHIP3...ダイナミックランダムアクセスメモリ(DRAM)、 CHIP4...ダイナミックランダムアクセスメモリ(DRAM)と制御回路(CTL\_LOGIC)が集積された半導体チップ、 A0~A20...アドレス信号、 S-/CE1...CHIP2のチップイネーブル信号、 S-CE2...CHIP2のチップイネーブル信号、 S-/E...CHIP2のアウトプットイネーブル信号、 S-/WE...CHIP2のライトイネーブル信号、 S-/LB...CHIP2のロアーバイト選択信号、 S-/UB...CHIP2のアッパー バイト選択信号、 F-/WE...CHIP1のライトイネーブル信号、 F-/RP...CHIP1リセット/ディープパワーダウン信号、 F-/WP...CHIP1ライトプロテクト信号、 F-RDY/BUSY...CHIP1レディ/ビジニアウトプット信号、 F-/CE...CHIP1チップイネーブル信号、 F-/OE...CHIP1アウトプットイネーブル信号、 F-VCC...CHIP1の電源、 F-VSS...CHIP1グラウンド、 S-VCC...CHIP2の電源、 S-VS...CHIP2のグラウンド、 L-VCC...CHIP2の電源、 L-VSS...CHIP2グラウンド、 PS...パワー制御信号、 I/00~I/015...データ入出力、 D-CLK...CHIP3のクロック、 D-A0~D-A13...CHIP3のアドレス信号、 D-CKE...CHIP3のクロックイネーブル信号、 D-/CS...CHIP3のチップセレクト信号、 D-/RAS...CHIP3のロウアドレスストローブ信号、 D-/CAS...CHIP3のカラムアドレスストローブ信号、 D-/WE...CHIP3のライトイネーブル信号、 D-DQMU/D

30

QML...CHIP3のインプット/アウトプットマスク信号、 D-DQ0~D-DQ15...CHIP3のデータ入出力、 D-VCC...CHIP3の電源、 D-VSS...CHIP3のグラウンド、 D-VCCQ...CHIP3のI/O用電源、 D-VSSQ...CHIP3のI/O用グラウンド、 AS...アクセススイッチ回路、 SRAM...スタティックランダムアクセスメモリ、 ATD...アドレストランジションディテクタ、 DTD...データトランジションディテクタ、 MMU...メモリマネージメントユニット、 FIFO...ファーストインファーストアウト(メモリ)、 R/W BUFFER リード/ライトバッファ、 INT...初期化回路、 TMP...温度測定モジュール、 RC...リフレッシュカウンタ、 PM...パワーマネージメントモジュール、 A\_CONTアクセスコントローラ、 CLK\_GEN...クロックジェネレータ、 COM\_GEN...コマンドジェネレータ、 S-CS...SRAM用チップセレクト信号の総称、 F-CS...不揮発メモリ用チップセレクト信号の総称、 SHADOW...シャドウ領域、 /

40

50

A0... ATD回路によるアドレス変化検出信号、 / AN ATD回路によるアドレス変化検出信号、 / ATD... ATD回路出力信号、 D1... ディレイエレメント、 D2... ディレイエレメント、 WORK... ワーク期間、 REF... リフレッシュ期間、 PCB... プリント回路基板、 COVE R... モジュールの封止カバー、 PATH1... PCBとCHIP1を接続するボンディング配線、 PATH2... PCBとCHIP1上に搭載されたCHIP2とを接続するボンディング配線、 PATH3... PCBとCHIP3を接続するボンディング配線、 PATH4... CHIP3とCHIP1上に搭載されたCHIP2とを接続するボンディング配線、 PATH5... PCBとBGAによって配置されたCHIP1上に搭載されたCHIP2とを接続するボンディング配線、 PATH6... CHIP3とBGAによって配置されたCHIP1上に搭載されたCHIP2とを接続するボンディング配線、 PATH7... BGAによって配置されたCHIP3上に搭載されたCHIP1とさらにその上に搭載されたCHIP2とを接続するボンディング配線、 PA10 TH8... BGAによって配置されたCHIP3上に搭載されたCHIP1の上に搭載されたCHIP2とPCBとを接続するボンディング配線、 PATH9... BGAによって配置されたCHIP3上に搭載されたCHIP1と同じくCHIP2とを接続するボンディング配線、 PATH10... BGAによって配置されたCHIP3上に搭載されたCHIP2において、モジュールの中心側に配置されたボンディングパットとPCBとを接続するボンディング配線、 PATH11... BGAによって配置されたCHIP1上に搭載されたCHIP2と同じくCHIP3とを接続するボンディング配線で、 CHIP3がLOC形式のボンディングパット配置のもの、 PATH12... CHIP1とCHIP1上に搭載されたCHIP2を接続するボンディング配線。

【図1】

図1

【図2】

図2

【図3】

【図4】

【図5】

【図6】

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

図15

【図16】

図16

(A)

(B)

【図17】

図17

(A)

(B)

【図18】

図18

(A)

(B)

【図19】

図19

(A)

(B)

【図20】

図20

(A)

【図21】

図21

(A)

(B)

【図22】

図22

(A)

(B)

【図23】

図23

(A)

(B)

---

フロントページの続き

| (51)Int.Cl. |                  | F I                   |

|-------------|------------------|-----------------------|

| G 1 1 C     | 16/04 (2006.01)  | G 1 1 C 11/34 3 7 1 K |

| H 0 1 L     | 25/04 (2006.01)  | G 1 1 C 17/00 6 2 5   |

| H 0 1 L     | 25/18 (2006.01)  | H 0 1 L 25/04 Z       |

| H 0 1 L     | 25/065 (2006.01) | H 0 1 L 25/08 Z       |

| H 0 1 L     | 25/07 (2006.01)  |                       |

(72)発明者 齊藤 良和

東京都小平市上水本町五丁目20番1号

株式会社日立製作半導体グレ - プ内

審査官 須原 宏光

(56)参考文献 特開平10-011348 (JP, A)

特開平11-339469 (JP, A)

特開平11-340421 (JP, A)

特開2001-093277 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/40-409

H01L 27/04

H01L 25/07