(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-122033

(P2007-122033A)

(43) 公開日 平成19年5月17日(2007.5.17)

| (51) Int.C1. |                 | F 1       | テーマコード (参考) |       |

|--------------|-----------------|-----------|-------------|-------|

| <b>G09F</b>  | 9/30 (2006.01)  | G09F 9/30 | 390C        | 3K107 |

| <b>G09G</b>  | 3/30 (2006.01)  | G09G 3/30 | J           | 5C080 |

| <b>G09G</b>  | 3/20 (2006.01)  | G09G 3/20 | 641E        | 5C094 |

| <b>H01L</b>  | 27/32 (2006.01) | G09G 3/20 | 641A        |       |

| <b>H05B</b>  | 33/12 (2006.01) | G09F 9/30 | 365Z        |       |

審査請求 未請求 請求項の数 13 O L (全 82 頁) 最終頁に続く

|              |                              |            |                                                                                                                                                                            |

|--------------|------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-263259 (P2006-263259) | (71) 出願人   | 000153878                                                                                                                                                                  |

| (22) 出願日     | 平成18年9月27日 (2006.9.27)       |            | 株式会社半導体エネルギー研究所                                                                                                                                                            |

| (31) 優先権主張番号 | 特願2005-288373 (P2005-288373) |            | 神奈川県厚木市長谷398番地                                                                                                                                                             |

| (32) 優先日     | 平成17年9月30日 (2005.9.30)       | (72) 発明者   | 木村 肇                                                                                                                                                                       |

| (33) 優先権主張国  | 日本国 (JP)                     |            | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内                                                                                                                                            |

|              |                              | (72) 発明者   | 宮口 厚                                                                                                                                                                       |

|              |                              |            | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内                                                                                                                                            |

|              |                              | F ターム (参考) | 3K107 AA01 BB01 CC07 CC09 EE07<br>EE22 FF13<br>5C080 AA06 BB05 CC03 DD04 EE29<br>EE30 FF11 JJ02 JJ03 JJ04<br>JJ05 JJ06<br>5C094 AA08 BA03 BA27 CA19 CA20<br>CA24 ED03 JA20 |

(54) 【発明の名称】表示装置及び電子機器

## (57) 【要約】

【課題】発光素子を具備する表示装置において、色再現範囲向上させることを課題とする。

【解決手段】複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素に設けられた発光素子と第2の画素に設けられた発光素子、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子、第5の画素に設けられた発光素子と第6の画素に設けられた発光素子は、互いに異なる発光スペクトルを有する構成とする。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

複数の絵素を有する表示領域を有し、

前記絵素は、CIE-X Y色度図で表したときに、前記CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、前記CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、

前記第1の画素に設けられた発光素子と前記第2の画素に設けられた発光素子は互いに異なる発光スペクトルを有し、 10

前記第3の画素に設けられた発光素子と前記第4の画素に設けられた発光素子は互いに異なる発光スペクトルを有し、

前記第5の画素に設けられた発光素子と前記第6の画素に設けられた発光素子は、互いに異なる発光スペクトルを有することを特徴とする表示装置。

**【請求項 2】**

複数の絵素を有する表示領域を有し、

前記絵素は、CIE-X Y色度図で表したときに、前記CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、前記CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、 20

前記第1の画素に設けられた発光素子と前記第2の画素に設けられた発光素子は、前記CIE-X Y色度図において、互いに座標が異なる色で発光し、

前記第3の画素に設けられた発光素子と前記第4の画素に設けられた発光素子は、前記CIE-X Y色度図において、互いに座標が異なる色で発光し、

前記第5の画素に設けられた発光素子と前記第6の画素に設けられた発光素子は、前記CIE-X Y色度図において、互いに座標が異なる色で発光することを特徴とする表示装置。 30

**【請求項 3】**

複数の絵素を有する表示領域を有し、

前記絵素は、CIE-X Y色度図で表したときに、前記CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、前記CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、

前記第1の画素に設けられた発光素子と前記第2の画素に設けられた発光素子は、異なる材料で構成されており、且つ互いに異なる発光スペクトルを有し、 40

前記第3の画素に設けられた発光素子と前記第4の画素に設けられた発光素子は、異なる材料で構成されており、且つ互いに異なる発光スペクトルを有し、

前記第5の画素に設けられた発光素子と前記第6の画素に設けられた発光素子は、異なる材料で構成されており、且つ互いに異なる発光スペクトルを有することを特徴とする表示装置。

**【請求項 4】**

複数の絵素を有する表示領域を有し、

前記絵素は、CIE-X Y色度図で表したときに、前記CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素と、 50

素及び第4の画素と、前記CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、

前記第1の画素に設けられた発光素子と前記第2の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ互いに異なる発光スペクトルを有し、

前記第3の画素に設けられた発光素子と前記第4の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ互いに異なる発光スペクトルを有し、

前記第5の画素に設けられた発光素子と前記第6の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ互いに異なる発光スペクトルを有することを特徴とする表示装置。

10

#### 【請求項5】

複数の絵素を有する表示領域を有し、

前記絵素は、CIE-X Y色度図で表したときに、前記CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、前記CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、

前記第1の画素、前記第2の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ互いに異なる発光スペクトルの光を透過し、

20

前記第3の画素、前記第4の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ互いに異なる発光スペクトルの光を透過し、

前記第5の画素、前記第6の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ互いに異なる発光スペクトルの光を透過することを特徴とする表示装置。

#### 【請求項6】

複数の絵素を有する表示領域を有し、

前記絵素は、CIE-X Y色度図で表したときに、前記CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、前記CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、

30

前記第1の画素に設けられた発光素子と前記第2の画素に設けられた発光素子は、異なる材料で構成されており、且つ前記CIE-X Y色度図において、互いに座標が異なる色で発光し、

前記第3の画素に設けられた発光素子と前記第4の画素に設けられた発光素子は、異なる材料で構成されており、且つ前記CIE-X Y色度図において、互いに座標が異なる色で発光し、

前記第5の画素に設けられた発光素子と前記第6の画素に設けられた発光素子は、異なる材料で構成されており、且つ前記CIE-X Y色度図において、互いに座標が異なる色で発光することを特徴とする表示装置。

40

#### 【請求項7】

複数の絵素を有する表示領域を有し、

前記絵素は、CIE-X Y色度図で表したときに、前記CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、前記CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、

前記第1の画素に設けられた発光素子と前記第2の画素に設けられた発光素子は、互いに

50

に膜厚が異なっており、且つ前記 CIE - XY 色度図において、互いに座標が異なる色で発光し、

前記第3の画素に設けられた発光素子と前記第4の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ前記 CIE - XY 色度図において、互いに座標が異なる色で発光し、

前記第5の画素に設けられた発光素子と前記第6の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ前記 CIE - XY 色度図において、互いに座標が異なる色で発光することを特徴とする表示装置。

#### 【請求項 8】

複数の絵素を有する表示領域を有し、

前記絵素は、CIE - XY 色度図で表したときに、前記 CIE - XY 色度図の x が 0.50 以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、前記 CIE - XY 色度図の y が 0.55 以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、前記 CIE - XY 色度図の x が 0.20 以下、y が 0.25 以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、

前記第1の画素、前記第2の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ当該カラーフィルターを透過した光は、前記 CIE - XY 色度図において互いに座標が異なる色であり、

前記第3の画素、前記第4の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ当該カラーフィルターを透過した光は、前記 CIE - XY 色度図において互いに座標が異なる色であり、

前記第5の画素、前記第6の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ当該カラーフィルターを透過した光は、前記 CIE - XY 色度図において互いに座標が異なる色であることを特徴とする表示装置。

#### 【請求項 9】

請求項 1 乃至 請求項 8 のいずれか一項において、

前記第1の画素が具備する発光素子、前記第2の画素が具備する発光素子のいずれかは、前記 CIE - XY 色度図で表したときに、前記 CIE - XY 色度図の x が 0.6 以上、y が 0.35 以下の領域に座標を有し、

前記第3の画素が具備する発光素子、前記第4の画素が具備する発光素子のいずれかは、前記 CIE - XY 色度図で表したときに、前記 CIE - XY 色度図の x が 0.3 以下、y が 0.6 以上の領域に座標を有し、

前記第5の画素が具備する発光素子、前記第6の画素が具備する発光素子のいずれかは、前記 CIE - XY 色度図で表したときに、前記 CIE - XY 色度図の x が 0.15 以下、y が 0.2 以下の領域に座標を有することを特徴とする表示装置。

#### 【請求項 10】

請求項 1 乃至 請求項 9 のいずれか一項において、

前記絵素は、白色を発光する発光素子を具備することを特徴とする表示装置。

#### 【請求項 11】

請求項 1 乃至 請求項 10 のいずれか一項において、

前記第1の画素及び前記第2の画素、前記第3の画素及び前記第4の画素、並びに前記第5の画素及び前記第6の画素は、互いに異なる面積の発光領域を具備することを特徴とする表示装置。

#### 【請求項 12】

請求項 1 乃至 請求項 11 のいずれか一項において、

前記発光素子は、エレクトロルミネッセンス素子であることを特徴とする表示装置。

#### 【請求項 13】

請求項 1 乃至 請求項 12 のいずれか一項に記載の表示装置を具備することを特徴とする電子機器。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は画素に発光素子や電気光学素子を具備する表示装置に関する。特に発光素子に有機材料や蛍光材料や熒光材料を含む層を具備する表示装置に関する。

## 【背景技術】

## 【0002】

有機材料を含む層を一对の電極間に有し、当該電極間に電流を流すことで発光する発光素子を用いた表示装置の開発が進められている。このような表示装置は薄型軽量化に有利であり、自発光であるため視認性も良く、応答速度も速い。また、消費電力も潜在的には非常に小さくできる可能性があり、次世代の表示装置として盛んに開発が進められ、一部実用化もされている。

## 【0003】

上記の構成の発光素子を用いた表示装置において、高画質、広色域化の向上が望まれている。例えば、印刷業務における編集、芸術・映画等の作品の視聴、遠隔医療における実物の色の正確な把握、等に正確な色の再現・表示が行える表示装置の開発が強く望まれている。そこで人間の眼に視認される色域をよくするため、色純度、広色域化の向上等、構造を最適化する研究がなされている（例えば、特許文献1を参照）。

## 【特許文献1】特表2001-039554号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

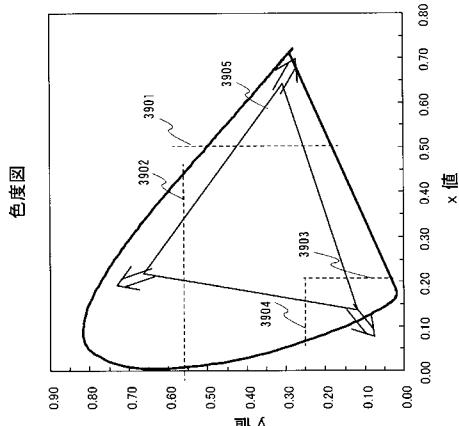

しかしながら、人間の眼に視認される色域にはまだ余剰があり、まだ現状の表示装置での色再現範囲では不十分である。図39は色に関する基準を国際的に管理している国際照明委員会（CIE）が定めたCIE-X Y色度図である。図中の外周において、最右端付近が赤色単色光の発光スペクトル700nm、最上端付近が緑色単色光の発光スペクトル546.1nm、最下端付近が青色単色光の発光スペクトル435.8nmにあたる。この色度図では、グラフ（可視領域）の外周が発光スペクトル上の単色光、内側が単色光を組み合わせてできる混合色に相当するため、内側に進む程、鮮やかさ（彩度）が低下する。加色混合により色を表現する場合、複数の基準色はCIE-X Y色度図で示される点が形成する多角形で囲まれた部分の色のみを再現出来る。

## 【0005】

CIE-X Y色度図で表したときに、赤（R）は、色度図の右側付近の領域（図39において色度図の周囲と点線3901で囲まれた領域）に座標を有する色を人間の眼が赤色として感じることができる。また、緑（G）は、CIE-X Y色度図で表したときに、色度図の上側付近の領域（図39において色度図の周囲と点線3902で囲まれた領域）に座標を有する色を人間の眼が緑色として感じることができる。青（B）は、CIE-X Y色度図を表したときに、色度図の下側付近の領域（図39において、色度図の周囲と点線3903と点線3904とで囲まれた領域）に座標を有する色を人間の眼が青色として感じることができる。具体的な例としては、ハイビジョン（高精細度テレビジョン放送；HDTV）規格の色度座標は、R（x=0.67, y=0.33）、G（x=0.21, y=0.71）、B（x=0.14, y=0.08）が挙げられる（図39における図中の三角形3905）。

## 【0006】

特許文献1に記載された方法によると色純度を高めることによって、図39の矢印方向に色再現範囲が拡大することができ、人間の眼に認識される色の鮮やかさは増加する。しかしながら、人間の眼に認識することができる色域にはまだ余剰があり、これを充足することで、色の再現範囲を広げることが課題となる。

## 【0007】

そこで、本発明は発光素子を具備する表示装置において、上記課題を解決するものであ

10

20

30

40

50

り、色再現範囲を向上させ、人間の眼に視認される色域を広くするものである。

【課題を解決するための手段】

【0008】

本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、CIE-X Y色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、CIE-X Y色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素に設けられた発光素子と第2の画素に設けられた発光素子は互いに異なる発光スペクトルを有し、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子は互いに異なる発光スペクトルを有し、第5の画素に設けられた発光素子と第6の画素に設けられた発光素子は、互いに異なる発光スペクトルを有する構成とする。

【0009】

また別の本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、CIE-X Y色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素に設けられた発光素子と第2の画素に設けられた発光素子は、CIE-X Y色度図において、互いに座標が異なる色で発光し、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子は、CIE-X Y色度図において、互いに座標が異なる色で発光し、第5の画素に設けられた発光素子と第6の画素に設けられた発光素子は、CIE-X Y色度図において、互いに座標が異なる色で発光する構成とする。

【0010】

また別の本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素に設けられた発光素子と第2の画素に設けられた発光素子は、異なる材料で構成されており、且つ互いに異なる発光スペクトルを有し、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子は、異なる材料で構成されており、且つ互いに異なる発光スペクトルを有し、第5の画素に設けられた発光素子と第6の画素に設けられた発光素子は、異なる材料で構成されており、且つ互いに異なる発光スペクトルを有する構成とする。

【0011】

また別の本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素に設けられた発光素子と第2の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ互いに異なる発光スペクトルを有し、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ互いに異なる発光スペクトルを有し、第5の画素に設けられた発光素子と第6の画素に設けられた発光素子は、互いに膜厚が異なっており、且つ互いに異なる発光スペクトルを有する構成とする。

【0012】

10

20

30

40

50

また別の本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素、第2の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ互いに異なる発光スペクトルの光を透過し、第3の画素、第4の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ互いに異なる発光スペクトルの光を透過し、第5の画素、第6の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ互いに異なる発光スペクトルの光を透過する構成とする。

10

## 【0013】

また別の本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素に設けられた発光素子と第2の画素に設けられた発光素子は、異なる材料で構成されており、且つCIE-X Y色度図において、互いに座標が異なる色で発光し、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子は、異なる材料で構成されており、且つCIE-X Y色度図において、互いに座標が異なる色で発光し、第5の画素に設けられた発光素子と第6の画素に設けられた発光素子は、異なる材料で構成されており、且つCIE-X Y色度図において、互いに座標が異なる色で発光する構成とする。

20

## 【0014】

また別の本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素に設けられた発光素子と第2の画素に設けられた発光素子は、互いに膜厚が異なっており、且つCIE-X Y色度図において、互いに座標が異なる色で発光し、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子は、互いに膜厚が異なっており、且つCIE-X Y色度図において、互いに座標が異なる色で発光し、第5の画素に設けられた発光素子と第6の画素に設けられた発光素子は、互いに膜厚が異なっており、且つCIE-X Y色度図において、互いに座標が異なる色で発光する構成とする。

30

## 【0015】

また別の本発明の表示装置の一は、複数の絵素を有する表示領域を有し、絵素は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有する発光素子を具備する第1の画素及び第2の画素と、色度図のyが0.55以上の領域に座標を有する発光素子を具備する第3の画素及び第4の画素と、色度図のxが0.20以下、yが0.25以下の領域に座標を有する発光素子を具備する第5の画素及び第6の画素と、で構成されており、第1の画素、第2の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ当該カラーフィルターを透過した光は、前記CIE-X Y色度図において互いに座標が異なる色であり、第3の画素、第4の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ当該カラーフィルターを透過した光は、前記CIE-X Y色度図において互いに座標が異なる色であり、第5の画素、第6の画素は、互いに透過特性が異なるカラーフィルターを具備し、且つ当該カラーフィルターを透過した光は、前記CIE-X Y色度図において互いに座標が異なる色である構成とする。

40

## 【0016】

50

また、第1の画素が具備する発光素子、第2の画素が具備する発光素子のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.6以上、yが0.35以下の領域に座標を有し、第3の画素が具備する発光素子、第4の画素が具備する発光素子のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.3以下、yが0.6以上の領域に座標を有し、第5の画素が具備する発光素子、第6の画素が具備する発光素子のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.15以下、yが0.2以下の領域に座標を有する構成であってもよい。

## 【0017】

また絵素は、白色を発光する発光素子を具備する構成であってもよい。

## 【0018】

また第1の画素及び第2の画素、第3の画素及び第4の画素、並びに第5の画素及び第6の画素は、互いに異なる面積の発光領域を具備する構成であってもよい。

## 【0019】

また発光素子は、エレクトロルミネッセンス (EL: Electro Luminescence) 素子 (有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子) を用いることができる。

## 【0020】

なお本明細書におけるCIE-X Y色度図における領域とは、CIE-X Y色度図における人間の目が認識することのできる可視光の光を表す領域のことを指すものとする。

## 【0021】

なお、本明細書に示すスイッチは、様々な形態のものを用いることができ、一例として、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トランジスタでもよいし、ダイオード (例えば、PNダイオード、PINダイオード、ショットキーダイオード、ダイオード接続のトランジスタなど) でもよいし、サイリスタでもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性 (導電型) は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているものやマルチゲート構造にしているもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源 (Vss、GND、0Vなど) に近い状態で動作する場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源 (Vddなど) に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとしての動作が容易であるからである。

## 【0022】

なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。CMOS型のスイッチにすると、Pチャネル型かNチャネル型かのどちらかのスイッチが導通すれば電流を流すことができるため、スイッチとして機能しやすくなる。例えば、スイッチへの入力信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることができるので、消費電力を小さくすることも出来る。

## 【0023】

なお、スイッチとしてトランジスタを用いる場合は、入力端子 (ソース端子またはドレイン端子の一方) と、出力端子 (ソース端子またはドレイン端子の他方) と、導通を制御する端子 (ゲート端子) とを有している。一方、スイッチとしてダイオードを用いる場合は、導通を制御する端子を有していない場合がある。そのため、端子を制御するための配線を少なくすることが出来る。

## 【0024】

なお、本明細書において、接続されているとは、電気的に接続されている場合と機能的に

10

20

30

40

50

接続されている場合と直接接続されている場合とを含むものとする。したがって、本明細書が開示する構成において、所定の接続関係以外のものも含むものとする。例えば、ある部分とある部分との間に、電気的な接続を可能とする素子（例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど）が1個以上配置されていてもよい。また、機能的な接続を可能とする回路（例えば、論理回路（インバータやNAND回路やNOR回路など）や信号変換回路（DA変換回路やAD変換回路やガンマ補正回路など）や電位レベル変換回路（昇圧回路や降圧回路などの電源回路やH信号やL信号の電位レベルを変えるレベルシフタ回路など）や電圧源や電流源や切り替え回路や增幅回路（オペアンプや差動增幅回路やソースフォロワ回路やバッファ回路など、信号振幅や電流量などを大きく出来る回路など）や信号生成回路や記憶回路や制御回路など）が間に1個以上配置されていてもよい。あるいは、間に他の素子や他の回路を挟まずに、直接接続されて、配置されていてもよい。

10

#### 【0025】

なお、素子や回路を間に介さずに接続されている場合のみを含む場合は、直接接続されている、と記載するものとする。また、電気的に接続されている、と記載する場合は、電気的に接続されている場合（つまり、間に別の素子を挟んで接続されている場合）と機能的に接続されている場合（つまり、間に別の回路を挟んで接続されている場合）と直接接続されている場合（つまり、間に別の素子や別の回路を挟まずに接続されている場合）とを含むものとする。

20

#### 【0026】

なお、本明細書において、トランジスタは、様々な形態のトランジスタを適用させることが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、例えば、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を有する薄膜トランジスタ（TFT）などを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、低成本で製造できたり、大型基板上に製造できたり、透明基板上に製造できたり、トランジスタで光を透過させたりすることが出来る。また、半導体基板やSOI基板などを用いて形成することが出来る。また、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを適用することが出来る。これらにより、バラツキの少ないトランジスタを製造できたり、電流供給能力の高いトランジスタを製造できたり、サイズの小さいトランジスタを製造できたり、消費電力の少ない回路を構成したりすることが出来る。また、ZnO、a-InGaZnO、SiGe、GaAsなどの化合物半導体を有するトランジスタや、さらに、それらを薄膜化した薄膜トランジスタなどを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、室温で製造できたり、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成したりすることが出来る。また、インクジェットや印刷法を用いて作成したトランジスタなどを適用することが出来る。これらにより、室温で製造したり、真空中の低い状態で製造したり、大型基板で製造したりすることができる。また、マスク（レチクル）を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。また、有機半導体やカーボンナノチューブを有するトランジスタ、その他のトランジスタを適用することができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタが形成されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などに形成することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。配置された別の基板としては、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることができる。これらの基板を用いることにより、特性のよいトランジスタ

30

40

50

を形成したり、消費電力の小さいトランジスタを形成したり、壊れにくい装置にしたり、耐熱性を持たせたりすることが出来る。

【0027】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート電極が2個以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。マルチゲート構造にすることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることなどができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値を大きくしたり、空乏層ができやすくなってS値を小さくすることができる。チャネルの上下にゲート電極が配置されると、複数のトランジスタが並列に接続されたような構成となる。

10

【0028】

また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれているてもよいし、複数の領域に分かれたチャネル領域が、並列に接続されているてもよいし、直列に接続されているてもよい。また、チャネル（もしくはその一部）にソース電極やドレイン電極が重なっているてもよい。チャネル（もしくはその一部）にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD（Lightly Doped Drain）領域があってもよい。LDD領域を設けることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

20

【0029】

なお、本明細書におけるトランジスタは、様々なタイプを用いることができ、様々な基板上に形成させることができる。したがって、回路の全てが、ガラス基板上に形成されてもよいし、プラスチック基板に形成されてもよいし、単結晶基板に形成されてもよいし、SOI基板上に形成されてもよいし、どのような基板上に形成されてもよい。回路の全てが同じ基板上に形成されていることにより、部品点数を減らしてコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすることができる。あるいは、回路の一部が、ある基板に形成されており、回路の別の一部が、別の基板に形成されてもよい。つまり、回路の全てが同じ基板上に形成されていなくてもよい。例えば、回路の一部は、ガラス基板上にトランジスタを用いて形成し、回路の別の一部は、単結晶基板上に形成し、そのICチップをCOG（Chip On Glass）で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB（Tape

30

Automated Bonding）やプリント基板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らしてコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすることができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力の向上を防ぐことができる。

40

【0030】

なお、トランジスタとは、それぞれ、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本発明にお

50

いては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。

【0031】

なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2端子と表記する場合がある。

【0032】

なお、ゲートとは、ゲート電極とゲート配線（ゲート線またはゲート信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域やLDD領域などを形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。ゲート配線とは、各画素のゲート電極の間を接続したり、ゲート電極と別の配線とを接続したりするための配線のことを言う。

10

【0033】

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

20

【0034】

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル領域とオーバーラップしていなかったり、別のゲート電極と接続させる機能を有してなかったりする場合がある。しかし、製造工程などの関係で、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線とつながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んでも良い。

30

【0035】

また、例えば、マルチゲートのトランジスタにおいて、1つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。

30

【0036】

また、例えば、ゲート電極とゲート配線とを接続している部分の導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

40

【0037】

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域について、その一部分のことを言う。

【0038】

なお、ソースとは、ソース領域とソース電極とソース配線（ソース線またはソース信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物（ボロンやガリウムなど）やN型不純物（リンやヒ素など）が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD（Lightly Doped Drain）領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域

50

も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間を接続したり、ソース電極と別の配線とを接続したりするための配線のことを言う。

#### 【0039】

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能していることになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

10

#### 【0040】

また、ソース電極と同じ材料で形成され、ソース電極とつながっている領域や、ソース電極とソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、ソース配線と呼んでも良い。このような領域は、厳密な意味では、別のソース電極と接続させる機能を有していたりすることがない場合がある。しかし、製造工程などの関係で、ソース電極やソース配線と同じ材料で形成され、ソース電極やソース配線とつながっている領域がある。よって、そのような領域もソース電極やソース配線と呼んでも良い。

#### 【0041】

また、例えば、ソース電極とソース配線とを接続している部分の導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

20

#### 【0042】

なお、ソース端子とは、ソース領域の領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。

#### 【0043】

なお、ドレインについては、ソースと同様である。

#### 【0044】

なお、本明細書において、半導体装置とは半導体素子（トランジスタやダイオードなど）を含む回路を有する装置をいう。また、半導体特性を利用することで機能しうる装置全般でもよい。

30

#### 【0045】

また、表示装置とは、表示素子（液晶素子や発光素子など）を有する装置のことを言う。なお、液晶素子やE L素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が同一基板上に形成された表示パネル本体のことでもよい。また、ワイヤボンディングやバンプなどによって基板上に配置された周辺駆動回路、いわゆるチップオングラス（COG）を含んでいても良い。さらに、フレキシブルプリントサーキット（FPC）やプリント配線基盤（PWB）が取り付けられたもの（ICや抵抗素子や容量素子やインダクタやトランジスタなど）も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライトユニット（導光板やプリズムシートや拡散シートや反射シートや光源（LEDや冷陰極管など）を含んでいても良い）を含んでいても良い。また、発光装置とは、特にE L素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。

40

#### 【0046】

なお、表示素子や表示装置や発光素子や発光装置は、様々な形態を用いたり、様々な素子を有したりすることが出来る。例えば、表示素子や表示装置や発光素子や発光装置としては、E L素子（有機E L素子、無機E L素子又は有機物及び無機物を含むE L素子）、電子放出素子、液晶素子、電子インク、グレーティングライトバルブ（GLV）、プラズマディスプレイ（PDP）、デジタルマイクロミラーデバイス（DMD）、圧電セラミック

50

ディスプレイ、カーボンナノチューブ、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いた表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッショナディスプレイ(FED)やSED方式平面型ディスプレイ(SED:Surface-conduction Electron-emitter Display)など、液晶素子を用いた表示装置としては液晶ディスプレイ、透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、電子インクを用いた表示装置としては電子ペーパーがある。

#### 【0047】

なお、本明細書において、ある物の上に形成されている、あるいは、～上に形成されている、というように、～の上に、あるいは、～上に、という記載については、ある物の上に直接接していることに限定されない。直接接してはいない場合、つまり、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上に(もしくは層A上に)、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層Dなど)が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。また、～の上方に、という記載についても同様であり、ある物の上に直接接していることに限定されず、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層Dなど)が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、～の下に、あるいは、～の下方に、の場合についても、同様であり、直接接している場合と、接していない場合とを含むこととする。

#### 【発明の効果】

#### 【0048】

本発明を用いることによって発光素子を用いた表示装置において、CIE-XY色度図上における色再現範囲が向上した表示装置を提供することができる。換言すれば、鮮やかな色彩を表現できる表示装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0049】

以下、本発明の実施の態様、実施例について、図面を参照して説明する。但し、本発明は多くの異なる態様で実施することができる、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

#### 【0050】

##### (実施の形態1)

##### (本実施形態の表示装置の構成)

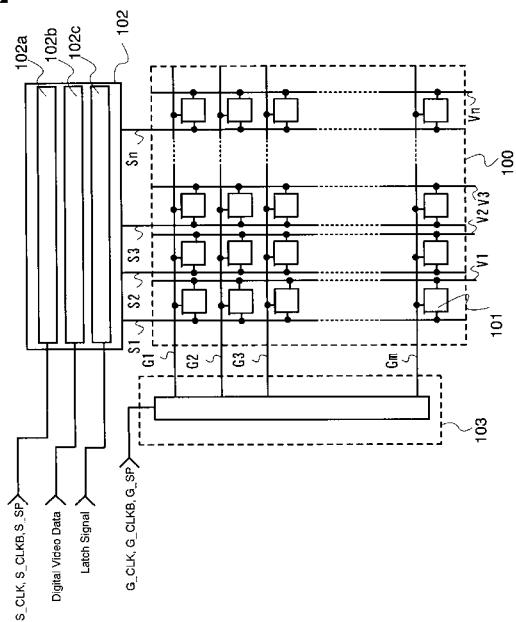

図1に本発明の表示装置の構成の一例を、ブロック図で示す。100は画素部であり、複数の画素101がマトリクス状に配置されており、本構成はアクティブマトリクス方式と呼ばれる。また102は信号線駆動回路、103は走査線駆動回路である。

#### 【0051】

なお図1では信号線駆動回路102と走査線駆動回路103が、画素部100と同じ基板上に形成されているが、本発明はこの構成に限定されない。信号線駆動回路102と走査線駆動回路103とが画素部100と異なる基板上に形成され、FPC(フレキシブルプリント配線板)等のコネクターを介して、画素部100と接続されても良い。なお、FPCを実装する方法は異方導電性材料もしくはメタルバンプを用いた接続方法またはワイヤボンディング方式を採用することができる。また、図1では信号線駆動回路102と走査線駆動回路103は1つずつ設けられているが、本発明はこの構成に限定されない。

10

20

30

40

50

。信号線駆動回路 102 と走査線駆動回路 103 の数は設計者が任意に設定することができる。

【0052】

なお、本明細書においては、画素とは一つの画像を構成する色要素を具備するものであり、発光素子及び発光素子を駆動する素子（例えばトランジスタで構成される回路）を含むものとする。また本明細書においては、絵素とは、一つの最小の画像を表示するための色要素を構成する画素を具備するものであるとする。よって、R（赤）G（緑）B（青）の色要素からなるフルカラー表示装置の場合には、絵素とはRの色要素、Gの色要素、Bの色要素を含む画素から構成されているものとする。また、絵素において、画素を複数有するものについては、第1の画素、第2の画素といった順に呼称するものとする。また、各画素は、その面積の大きさが異なっていてもよい。

【0053】

なお本明細書において接続とは、特に記載のない限り電気的な接続を意味する。逆に切り離すとは、接続していないで電気的に分離している状態を意味する。

【0054】

また図1では、画素部100には信号線S1～Sn、電源線V1～Vn、走査線G1～Gmが設けられている。なお信号線と電源線の数は必ずしも同じであるとは限らない。またこれらの配線を必ず全て有していないとも良く、これらの配線の他に、別の異なる配線が設けられていても良い。

【0055】

信号線駆動回路102は、入力されたビデオ信号を各信号線S1～Snに供給することができる回路であれば良い。具体的に本実施の形態では、一例として、信号線駆動回路102は、シフトレジスタ102aと、第1のラッチ回路102b、第2のラッチ回路102cとを有している。なお、本発明の表示装置の信号線駆動回路102は上述した構成に限定されない。また、デジタルのビデオ信号（デジタルビデオ信号、映像信号ともいう）に対応した信号線駆動回路であってもいいし、D/A（デジタル-アナログ）変換回路を用いてアナログのビデオ信号（アナログビデオ信号）出力する信号線駆動回路であっても良い。また、表示装置の構成によっては、レベルシフタ回路、バッファ回路等を有する構成であってもよい。

【0056】

走査線駆動回路103には、画素部における画素を選択するため各走査線G1～Gmに信号を入力できる回路であればよい。具体的に本実施の形態においては、走査線駆動回路103は、シフトレジスタ回路を有している。また、表示装置の構成によっては、バッファ回路、レベルシフタ回路を有する構成であってもよい。また、ラッチ回路がなく、シフトレジスタとサンプリングスイッチとで構成されていてもよい。

【0057】

また、信号線駆動回路102には、クロック信号（S\_CLK）、クロック反転信号（S\_CLK\_B）、スタートパルス信号（S\_SP）、デジタルビデオ信号（Digital Video Data）、ラッチ信号（Latch Signal）などの信号が入力される。そして、それらの信号にしたがって、各信号線S1～Snへそれぞれ各列の画素に応じたビデオ信号を出力する。なお、なお、アナログビデオ信号が入力されていてもよい。

【0058】

また、走査線駆動回路103には、クロック信号（G\_CLK）、クロック反転信号（G\_CLK\_B）、スタートパルス信号（G\_SP）などの信号が入力される。そして、それらの信号にしたがって、選択する画素行の走査線Gi（第1の走査線G1～Gmのうちいずれか一）に画素を選択する信号を出力する。

【0059】

よって、信号線S1～Snに入力されたビデオ信号は、走査線駆動回路103から走査線Gi（走査線G1～Gmのうちいずれか一）に入力された信号によって選択された画素

10

20

30

40

50

行の各列の画素 101 に書き込まれる。そして、各走査線 G1 ~ Gm により各画素行が選択され、全ての画素に各画素に対応したビデオ信号が書き込まれる。そして、各画素は書き込まれたビデオ信号を一定期間保持する。各画素は、ビデオ信号を一定期間保持することによって、点灯などの状態を維持することができる。

#### 【0060】

図1に示した発光素子を用いた表示装置は、アクティブマトリクス方式による駆動方式について述べたがこれに限定されない。本発明においては単純マトリックス(パッシブ)方式を採用してもよい。図1に示したアクティブマトリクス方式は各画素に数個のスイッチング用の薄膜トランジスタを有する制御回路を備え、各画素の制御回路により各画素の発光非発光を制御する。一方、単純マトリクス方式の表示装置は複数個のカラム信号線と、複数個のロウ信号線とが互いに交差する形で配置され、その交差部において発光素子が挟まれている。よって、選択されたロウ信号線と、出力を行っているカラム信号線とに挟まれた領域に電位差が生じ、電流が流れると発光素子が発光する。

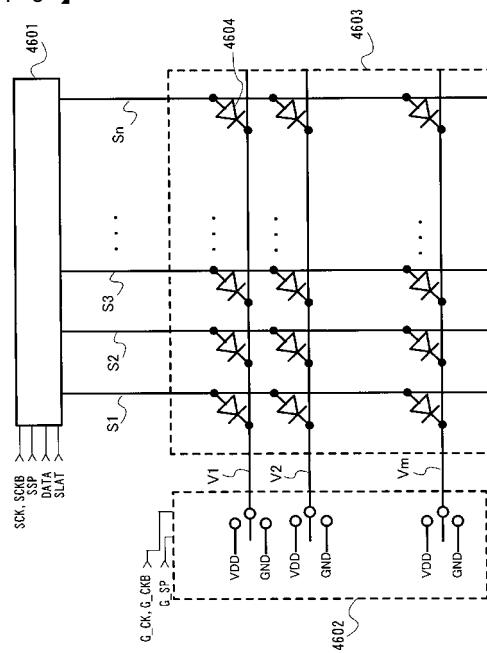

#### 【0061】

図46にパッシブ方式の表示装置の構成について示す。図46は、カラム信号線駆動回路4601、ロウ信号線駆動回路4602、画素部4603を備える。画素部4603はカラム信号線S1 ~ Sn、ロウ信号線V1 ~ Vnが設けられており、カラム信号線とロウ信号線の間には複数の発光素子4604を有する。パッシブ方式を採用する場合、アクティブマトリクス方式を採用する場合に比べ、本発明の構成を簡略化することができ、この点で好適である。

#### 【0062】

以上で述べたような表示装置の構成を、本発明では採用することができる。

#### 【0063】

##### (本実施形態の画素構成)

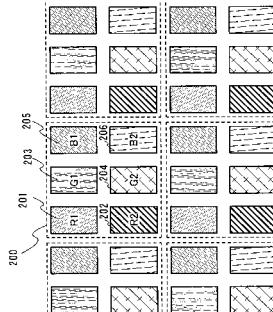

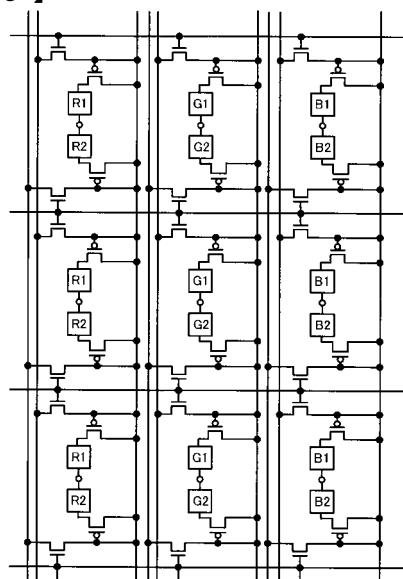

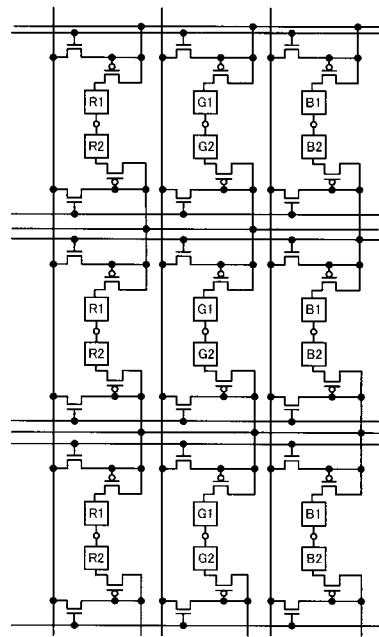

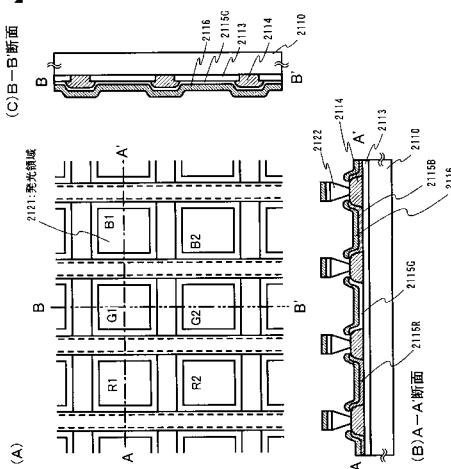

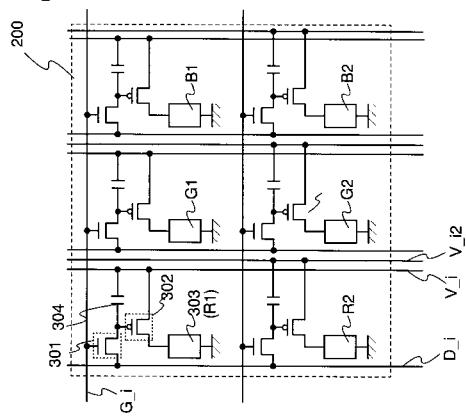

図2に、図1で示した本発明の画素部の構成について詳しい構成を示す。図2において第1の画素201、第2の画素202、第3の画素203、第4の画素204、第5の画素205、第6の画素206がそれぞれ、図1における画素101に対応する。また、第1の画素～第6の画素を併せて一つの最小の画像を表示する絵素200とする。第1の画素201、第2の画素202、第3の画素203、第4の画素204、第5の画素205、第6の画素206にはそれぞれ、発光素子が設けられており、第1の画素には発光素子R1、第2の画素には発光素子R2、第3の画素には発光素子G1、第4の画素には発光素子G2、第5の画素には発光素子B1、第6の画素には発光素子B2がそれぞれ接続されている。

#### 【0064】

ここで本明細書において第1の画素の発光素子R1及び第2の画素の発光素子R2は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有するものとする。また、第3の画素の発光素子G1及び第4の画素の発光素子G2は、CIE-X Y色度図で表したときに、色度図のyが0.55以上の領域に座標を有するものとする。また、第5の画素の発光素子B1及び第6の画素の発光素子B2は、CIE-X Y色度図を表したときに、色度図のxが0.20以下、yが0.35以下の領域に座標を有するものとする。また、より好ましくは、第1の画素の発光素子R1及び第2の画素の発光素子R2のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.6以上、yが0.35以下の領域に座標を有するものとする。またより好ましくは、第3の画素の発光素子G1及び第4の画素の発光素子G2のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.3以下、yが0.6以上の領域に座標を有するものとする。またより好ましくは、第5の画素の発光素子B1及び第6の画素の発光素子B2のいずれかは、CIE-X Y色度図を表したときに、色度図のxが0.15以下、yが0.2以下の領域に座標を有するものとする。

#### 【0065】

なお、本発明においては、発光素子G1とG2とのCIE-X Y色度図の座標の差(x

10

20

30

40

50

、 $y$  の座標の距離) の絶対値  $G_{1,2}$  は、発光素子 R 1 と発光素子 R 2 との CIE-X Y 色度図の座標の差の絶対値  $R_{1,2}$  または発光素子 B 1 と発光素子 B 2 との CIE-X Y 色度図の座標の差の絶対値  $B_{1,2}$  より大きいことが好ましい。 $G_{1,2} > R_{1,2}$  、 $G_{1,2} > B_{1,2}$  を満たすことで、色再現範囲を向上させ、人間の眼に視認される色域を広くすることができ、好適である。

#### 【0066】

なお本明細書における CIE-X Y 色度図における領域とは、CIE-X Y 色度図における人間の目が認識することのできる可視光の光を表す領域のことを指すものとする。すなわち図 3 において示した CIE-X Y 色度図における太線で囲まれた内側の領域に対応する。

10

#### 【0067】

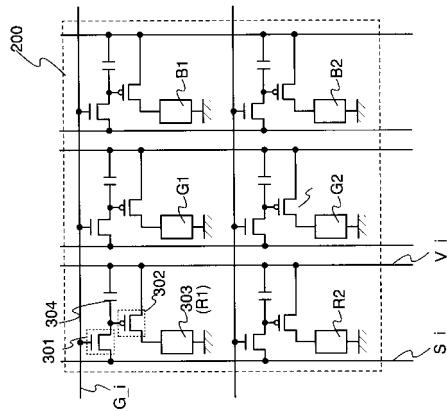

また図 3 に、図 2 で示した本発明の絵素 200 の回路構成を示す。図 2 に示す第 1 の画素 201、第 2 の画素 202、第 3 の画素 203、第 4 の画素 204、第 5 の画素 205、第 6 の画素 206 は、信号線  $S_i$  ( $S_1 \sim S_n$  のうちの 1 つ)、走査線  $G_i$  ( $G_1 \sim G_m$  のうちの 1 つ) 及び電源線  $V_i$  ( $V_1 \sim V_n$  のうちの 1 つ) を有している。また第 1 の画素 201、第 2 の画素 202、第 3 の画素 203、第 4 の画素 204、第 5 の画素 205、第 6 の画素 206 はそれぞれ、映像信号の入力を制御するスイッチング用の第 1 のトランジスタ 301、映像信号によって発光素子の発光・非発光を決定する駆動用の第 2 のトランジスタ 302、発光素子 303 及び保持容量 304 を有している。保持容量 304 は第 2 のトランジスタ 302 のゲートとソースの間の電圧(ゲート電圧)をより確実に保持するために設けられているが、必ずしも設ける必要はない。なお、本明細書において電圧とは、特に記載のない限りグラウンドとの電位差を意味する。また、発光素子 303 は、図 2 における  $R_1, R_2, G_1, G_2, B_1, B_2$  の発光素子が対応し、それぞれは各自を駆動するための回路が接続されている。図 3 に示す構成においては、同じ電源線  $V_i$  で、発光素子 R 1 と発光素子 R 2、発光素子 G 1 と発光素子 G 2、発光素子 B 1 と発光素子 B 2 に電流を供給する電源線を共通化する構成を取りうる。発光素子 R 1 と発光素子 R 2、発光素子 G 1 と発光素子 G 2、発光素子 B 1 と発光素子 B 2 においては色合いがほとんど同じであるため、このように電源線を共通化することができ、その結果、表示装置に配置する電源線の数を減らすことができるため好適である。図 3 においては、発光素子 R 1 と発光素子 R 2、発光素子 G 1 と発光素子 G 2、発光素子 B 1 と発光素子 B 2 にそれぞれに接続される電源線は、別々の配線として記載しているが同じ配線より分岐したものであってもよい。

20

30

40

#### 【0068】

なお、図 3 の示した構成とは別の構成を図 5 2 に示す。図 5 2 において図 3 と同一の機能を有する構成については同一の符号を付す。図 5 2 に示すように、発光素子 R 1 と発光素子 R 2、発光素子 G 1 と発光素子 G 2、発光素子 B 1 と発光素子 B 2 とでそれぞれ異なる第 2 の電源線  $V_{i,2}$  に接続される構成であってもよい。発光素子 R 1 と発光素子 R 2、発光素子 G 1 と発光素子 G 2、発光素子 B 1 と発光素子 B 2 とで電流を供給する電源線を異ならすことによって、それぞれの発光素子について加える電圧を制御することができる輝度を自由に変えることができるため好適である。

#### 【0069】

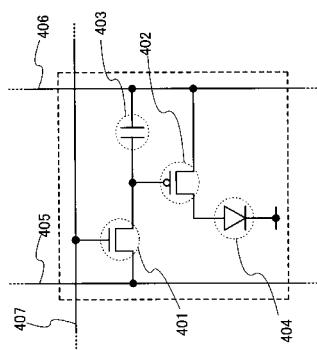

ここで図 4 に、図 3 における発光素子 303 が発光するときの駆動方法について説明する。図 4 において、発光素子 404 に接続している回路は、映像信号の入力を制御するスイッチング用の第 1 のトランジスタ 401 と、映像信号によって前記発光素子の発光強度を決定する駆動用の第 2 のトランジスタ 402 と、信号線 405 と、電源線 406 と、走査線 407 とで構成されている。第 1 のトランジスタ 401 のゲートは、走査線 407 に接続されている。第 1 のトランジスタ 401 の第 1 の端子と第 2 の端子(いずれか一方をソースとし、もう一方をドレインとする)は、一方は信号線 405 に、もう一方は第 2 のトランジスタ 402 のゲートに接続されている。また第 2 のトランジスタ 402 の第 1 の端子と第 2 の端子は、一方は電源線 406 に、もう一方は発光素子 404 が有する画素電

50

極に接続されている。発光素子 404 は陽極と陰極を有しており、本明細書では、陽極を画素電極として用いる場合は陰極を対向電極と呼び、陰極を画素電極として用いる場合は陽極を対向電極と呼ぶ。対向電極の電圧は一定の高さに保たれている場合が多い。また、第1のトランジスタ 401、第2のトランジスタ 402 はnチャネル型トランジスタとpチャネル型トランジスタのどちらでも良い。そして、陽極を画素電極として用い、陰極を対向電極として用いる場合、第2のトランジスタ 402 はpチャネル型トランジスタであるのが望ましい。逆に、陽極を対向電極として用い、陰極を画素電極として用いる場合、第2のトランジスタ 402 はnチャネル型トランジスタであるのが望ましい。

## 【0070】

保持容量 403 が有する2つの電極の一方は、第2のトランジスタのゲートに接続されている。また保持容量 403 が有する2つの電極の他方は、電源線 406 に接続されているがこれに限定されず、別の配線に接続されていてもよい。保持容量 403 は第2のトランジスタ 402 のゲートとソースの間の電圧(ゲート電圧)をより確実に維持するために設けられているが、第2のトランジスタ 402 のゲート容量で代用することにより、必ずしも設ける必要はない。

## 【0071】

図4において、書き込み期間において走査線 407 が選択されると、走査線 407 にゲートが接続されている第1のトランジスタ 401 がオンになる。そして、信号線 405 に入力された映像信号が、第1のトランジスタ 401 を介して第2のトランジスタ 402 のゲートに入力されることによって電源線 406 から発光素子 404 へ電流が流れ、発光素子 404 は発光をする。

## 【0072】

なお、画素構成はこれに限定されない。トランジスタのしきい値電圧のばらつきを補正する方式や、画素に信号電流を入力する方式など様々な画素構成を適用することが可能である。

## 【0073】

以上で述べたような画素構成を、本発明では採用することができる。

## 【0074】

## (本実施形態の動作方法)

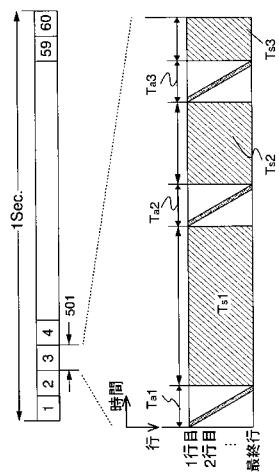

図4に示した回路構成において、表示を行う際の動作タイミングについて、図5を用いて説明する。表示装置においては、表示期間では繰り返し画面の書き換えと表示を行っている。この書き換え回数は、一般的には1秒間に60回程度とすることで、視認者がちらつき(フリッカ)を感じないとされている。ここで、画面の書き換え、表示の一連の動作を1回行う期間、つまり図5中、501で示した期間を、1フレーム期間 501 と表記する。本実施の形態においては、例として、デジタル時間階調方式で3ビットデジタル映像信号を用いた場合を挙げて説明する。デジタル時間階調方式の場合、1フレーム期間 501 を、さらに複数のサブフレーム期間に分割する。ここでは3ビットであるので、3つのサブフレーム期間に分割し、各期間で、各発光色における書き込み、表示を行う。

## 【0075】

各サブフレーム期間は、アドレス(書き込み)期間  $T_{a\#}$ (#は自然数)と、サステイン(発光)期間  $T_{s\#}$ を有する。図5においては、サステイン(発光)期間の長さを、 $T_{s1} : T_{s2} : T_{s3} = 4 : 2 : 1$  とし、各サステイン(発光)期間で、発光もしくは非発光を制御することにより、 $2^3 = 8$  階調を表現する。つまり、サステイン(発光)期間の長さを、 $T_{s1} : T_{s2} : T_{s3} = 2^{(n-1)} : 2^{(n-2)} : \dots : 2^1 : 2^0$  というように、2のべき乗の比とする。例えば、 $T_{s3}$ のみが発光し、 $T_{s1}$ 、 $T_{s2}$ においては非発光である場合、すべてのサステイン(発光)期間のうち、約14%の期間だけ発光していることになる。すなわち、約14%の輝度が表現出来る。 $T_{s1}$ と $T_{s2}$ が発光し、 $T_{s3}$ が非発光である場合には、すべてのサステイン(発光)期間のうち、約86%の期間だけ発光していることになる。すなわち、約86%の輝度が表現出来る。

## 【0076】

10

20

30

40

50

この動作によって、図3における発光素子303であるR1, R2, G1, G2, B1, B2をそれぞれ駆動する。このように、図3の絵素200における各々の画素に設けられた発光素子は、各々の発光素子に接続された回路によって独立に発光時間を制御され、所望の表示色が得られる。ここで、表示色とは、一画素内に含まれる発光色がそれぞれ異なる複数の発光素子から得られる発光が組み合わさり混合された色として、視覚的に認識できる色のことをいう。

【0077】

なお、駆動方法はこれに限定されない。第1のトランジスタのゲートにアナログ信号が入力されて、それに応じて発光素子404の輝度をアナログ的に変化させてもよい。

【0078】

以上で述べたような動作方法を、本発明では採用することができる。

【0079】

(本発明の発光素子の構成)

次に、本発明の表示装置に適用可能な発光素子の例を図6に示す。

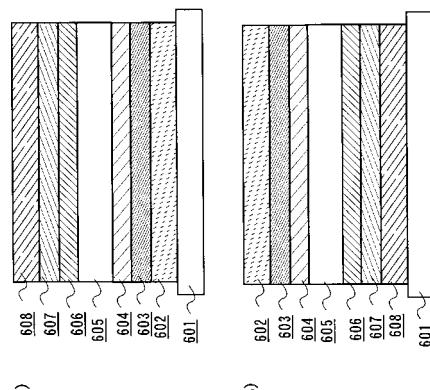

【0080】

図6(a)の発光素子は、基板601の上に陽極602、正孔注入材料からなる正孔注入層603、その上に正孔輸送材料からなる正孔輸送層604、発光層605、電子輸送材料からなる電子輸送層606、電子注入材料からなる電子注入層607、そして陰極608を積層させた素子構造である。ここで、発光層605は、一種類の発光材料のみから形成されることもあるが、2種類以上の材料から形成されてもよい。また本発明の発光素子の構造は、この構造に限定されない。勿論、基板601と陽極602との間にはトランジスタより構成される発光素子を駆動するための回路や配線があつてもよい。

【0081】

また、図6(a)で示した各機能層を積層した積層構造の他、高分子化合物を用いた素子、発光層に三重項励起状態から発光する三重項発光材料を利用した高効率素子など、バリエーションは多岐にわたる。発光素子は、ホールブロック層によってキャリヤの再結合領域を制御し、発光領域を二つの領域にわけることによって得られる白色発光素子などにも応用可能である。

【0082】

図6(a)に示す本発明の素子作製方法は、まず、陽極602(ITO:インジウム錫酸化物)を有する基板601に正孔注入材料、正孔輸送材料、発光材料を順に蒸着する。次に電子輸送材料、電子注入材料を蒸着し、最後に陰極608を蒸着で形成する。

【0083】

なお、正孔注入層に換えて、正孔発生層を設けてもよい。なお、正孔発生層とは、正孔を発生する層であり、正孔輸送性物質の中から選ばれた少なくとも一の物質と、正孔輸送性物質に対して電子受容性を示す物質とを混合することによって形成することができる。ここで、正孔輸送性物質としては、正孔輸送層を形成するのに用いることのできる物質と同様の物質を用いることができる。また、電子受容性を示す物質としては、モリブデン酸化物、バナジウム酸化物、ルテニウム酸化物、レニウム酸化物等の金属酸化物を用いることができる。

【0084】

次に、正孔注入材料、正孔輸送材料、電子輸送材料、電子注入材料、発光材料の材料に好適な材料を以下に列挙する。

【0085】

正孔注入材料としては、フタロシアニン(略称:H2Pc)や銅フタロシアニン(CuPc)等のフタロシアニン系の化合物、或いはポリ(エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)水溶液(PEDOT/PSS)等の高分子等が挙げられる。正孔注入層として用いる材料のイオン化ポテンシャルが、正孔注入層に陽極として機能する電極の反対側に接して形成されている機能層のイオン化ポテンシャルよりも相対的に小さくなるような物質を、正孔輸送性を有する物質の中から選択することによって、正孔注入層

10

20

30

40

50

を形成することができる。

【0086】

正孔輸送材料として最も広く用いられている材料として、4, 4' - ビス [ N - (1-ナフチル) - N - フェニルアミノ ] ビフェニル (略称: NPB)、4, 4' - ビス [ N - (3-メチルフェニル) - N - フェニルアミノ ] ビフェニル (略称: TPD)、4, 4', 4''' - トリス (N, N - ジフェニルアミノ) トリフェニルアミン (略称: TDATA)、4, 4', 4''' - トリス [ N - (3-メチルフェニル) - N - フェニルアミノ ] トリフェニルアミン (略称: MTDATA)、4, 4' - ビス { N - [ 4 - (N, N - ジ-m-トリルアミノ) フェニル ] - N - フェニルアミノ } ビフェニル (略称: DNTPD)、1, 3, 5 - トリス [ N, N - ジ (m - トリル) アミノ ] ベンゼン (略称: m-MTDAB)、4, 4', 4''' - トリス (N - カルバゾリル) トリフェニルアミン (略称: TCTA)、フタロシアニン (略称: H2Pc)、銅フタロシアニン (略称: CuPc)、バナジルフタロシアニン (略称: VOPc) 等が挙げられる。また、正孔輸送層は、以上に述べた物質から成る層を二以上組み合わせて形成した多層構造の層であってもよい。

【0087】

電子輸送材料としては、トリス (8-キノリノラト) アルミニウム (略称: Alq3)、トリス (4-メチル-8-キノリノラト) アルミニウム (略称: Almq3)、ビス (10-ヒドロキシベンゾ [h] - キノリナト) ベリリウム (略称: BeBq2)、ビス (2-メチル-8-キノリノラト) - 4 - フェニルフェノラト - アルミニウム (略称: BAlq)、ビス [ 2 - (2 - ヒドロキシフェニル) ベンゾオキサゾラト ] 亜鉛 (略称: Zn (BOX)2)、ビス [ 2 - (2 - ヒドロキシフェニル) ベンゾチアゾラト ] 亜鉛 (略称: Zn (BTZ)2) 等の他、2 - (4 - ビフェニリル) - 5 - (4 - tert - ブチルフェニル) - 1, 3, 4 - オキサジアゾール (略称: PBD)、1, 3 - ビス [ 5 - (p - tert - ブチルフェニル) - 1, 3, 4 - オキサジアゾール - 2 - イル ] ベンゼン (略称: OXD-7)、3 - (4 - ビフェニリル) - 4 - フェニル - 5 - (4 - tert - ブチルフェニル) - 1, 2, 4 - トリアゾール (略称: TAZ)、3 - (4 - ビフェニリル) - 4 - (4 - エチルフェニル) - 5 - (4 - tert - ブチルフェニル) - 1, 2, 4 - トリアゾール (略称: p-EtTAZ)、パソフェナントロリン (略称: BPhen)、パソキュプロイン (略称: BCP)、2, 2', 2''' - (1, 3, 5 - ベンゼントライル) - トリス (1 - フェニル - 1H - ベンゾイミダゾール) (略称: TPBI)、4, 4 - ビス (5 - メチルベンゾオキサゾル - 2 - イル) スチルベン (略称: BzOs) 等が挙げられる。また、電子輸送層は、以上に述べた物質から成る層を二以上組み合わせて形成した多層構造の層であってもよい。

【0088】

電子注入材料としては、アルカリ金属またはアルカリ土類金属、アルカリ金属のフッ化物、アルカリ土類金属のフッ化物、アルカリ金属の酸化物、アルカリ土類金属の酸化物等の無機物が挙げられる。また、無機物の他、BPhen、BCP、p-EtTAZ、TAZ、BzOs 等の電子輸送層を形成するのに用いることのできる物質も、これらの物質の中から、電子輸送層の形成に用いる物質よりも電子親和力が大きい物質を選択することによって、電子注入層を形成する物質として用いることができる。つまり、電子注入層における電子親和力が電子輸送層における電子親和力よりも相対的に大きくなるような物質を、電子輸送性を有する物質の中から選択することによって、電子注入層を形成することもできる。

【0089】

発光材料を含む層である発光層としては、発光物質について特に限定はなく、発光効率が良好で、所望の発光波長の発光をし得る物質を選択して用いればよい。例えば、赤色系の発光を得たいときには、4 - ジシアノメチレン - 2 - イソプロピル - 6 - [ 2 - (1, 1, 7, 7 - テトラメチルジュロリジン - 9 - イル) エテニル ] - 4H - ピラン (略称: DCJTI)、4 - ジシアノメチレン - 2 - メチル - 6 - [ 2 - (1, 1, 7, 7 - テトラメチルジュロリジン - 9 - イル) エテニル ] - 4H - ピラン (略称: DCJT)、4 -

10

20

30

40

50

ジシアノメチレン - 2 - tert - ブチル - 6 - [ 2 - ( 1 , 1 , 7 , 7 - テトラメチルジュロリジン - 9 - イル ) エテニル ] - 4 H - ピラン ( 略称 : D C J T B ) やペリフランテン、 2 , 5 - ジシアノ - 1 , 4 - ビス [ 2 - ( 10 - メトキシ - 1 , 1 , 7 , 7 - テトラメチルジュロリジン - 9 - イル ) エテニル ] ベンゼン等、 600 nm から 680 nm に発光スペクトルのピークを有する発光を呈する物質を用いることができる。また緑色系の発光を得たいときは、 N , N ' - ジメチルキナクリドン ( 略称 : D M Q d ) 、クマリン 6 やクマリン 545 T 、トリス ( 8 - キノリノラト ) アルミニウム ( 略称 : A l q 3 ) 等、 500 nm から 550 nm に発光スペクトルのピークを有する発光を呈する物質を用いることができる。また、青色系の発光を得たいときは、 9 , 10 - ビス ( 2 - ナフチル ) - tert - ブチルアントラセン ( 略称 : t - B u D N A ) 、 9 , 9 ' - ピアントリル、 9 , 10 - ジフェニルアントラセン ( 略称 : D P A ) や 9 , 10 - ビス ( 2 - ナフチル ) アントラセン ( 略称 : D N A ) 、ビス ( 2 - メチル - 8 - キノリノラト ) - 4 - フェニルフェノラト - ガリウム ( 略称 : B G a q ) 、ビス ( 2 - メチル - 8 - キノリノラト ) - 4 - フェニルフェノラト - アルミニウム ( 略称 : B A l q ) 等、 420 nm から 500 nm に発光スペクトルのピークを有する発光を呈する物質を用いることができる。また、以上に記載した蛍光を発光する物質の他、トリス ( 2 - フェニルピリジン ) イリジウム等の燐光を発光する物質を用いても構わない。

## 【 0090 】

発光物質を分散状態にするために用いる物質 ( ホスト材料とも言われる。 ) について特に限定はなく、 4 , 4 ' - ビス [ N - ( 1 - ナフチル ) - N - フェニルアミノ ] ビフェニル ( 略称 : - N P D ) のようなアリールアミン骨格を有する化合物の他、 4 , 4 ' - ビス ( N - カルバゾリル ) ビフェニル ( 略称 : C B P ) 、 4 , 4 ' , 4 '' - トリス ( N - カルバゾリル ) トリフェニルアミン ( 略称 : T C T A ) 等のカルバゾール誘導体や、 ビス [ 2 - ( 2 - ヒドロキシフェニル ) ピリジナト ] 亜鉛 ( 略称 : Z n p p 2 ) 、 ビス [ 2 - ( 2 - ヒドロキシフェニル ) ベンゾオキサゾラト ] 亜鉛 ( 略称 : Z n ( B O X ) 2 ) 、 トリス ( 8 - キノリノラト ) アルミニウム ( 略称 : A l q 3 ) 等の金属錯体等を用いることができる。

## 【 0091 】

また、図 6 ( b ) に示すように図 6 ( a ) とは逆の順番に層を形成した発光素子を用いることができる。つまり、基板 601 の上に陰極 608 、電子注入材料からなる電子注入層 607 、その上に電子輸送材料からなる電子輸送層 606 、発光層 605 、正孔輸送材料からなる正孔輸送層 604 、正孔注入材料からなる正孔注入層 603 、そして陽極 602 を積層させた素子構造である。

## 【 0092 】

また、発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上に TFT 及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の画素構成はどの射出構造の発光素子にも適用することができる。

## 【 0093 】

以上で述べたような各機能を有する材料を、各々組み合わせ、本発明の発光素子を作製することができる。

## 【 0094 】

( 本実施形態の表示装置における射出構造の構成 )

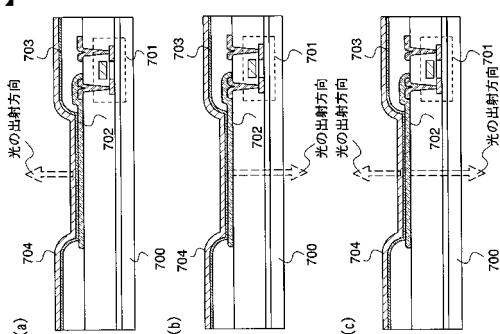

次に、本発明の表示装置に適用可能な発光素子について、上面射出構造、下面射出構造、及び両面射出構造の例を図 7 に示す。

## 【 0095 】

上面射出構造の発光素子について図 7 ( a ) を用いて説明する。

## 【 0096 】

基板 700 上に駆動用 TFT 701 が形成され、駆動用 TFT 701 のソース電極に接し

10

20

30

40

50

て第1の電極702が形成され、その上に発光層703と第2の電極704が形成されている。

【0097】

また、第1の電極702は発光素子の陽極である。そして第2の電極704は発光素子の陰極である。つまり、第1の電極702と第2の電極704とで発光層703が挟まれているところが発光素子となる。

【0098】

また、ここで、陽極として機能する第1の電極702に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、窒化チタン膜、クロム膜、タンゲステン膜、Zn膜、Pt膜などの単層膜の他、窒化チタン膜とアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。光を反射する金属膜を用いることで光を透過させない陽極を形成することができる。

10

【0099】

また、陰極として機能する第2の電極704に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム)からなる金属薄膜と、透明導電膜(ITO(インジウムスズ酸化物)、インジウム亜鉛酸化物IZO)、酸化亜鉛(ZnO)等)との積層を用いるのが良い。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることで光を透過させることができ陰極を形成することができる。

20

【0100】

こうして、図7(a)の矢印に示すように発光素子からの光を上面に取り出すことが可能になる。

【0101】

また、下面射出構造の発光素子について図7(b)を用いて説明する。射出構造以外は図7(a)と同じ構造の発光素子であるため同じ符号を用いて説明する。

30

【0102】

ここで、陽極として機能する第1の電極702に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウムスズ酸化物)膜、インジウム亜鉛酸化物IZO膜などの透明導電膜を用いることができる。透明性を有する透明導電膜を用いることで光を透過させることができ陰極を形成することができる。

【0103】

また、陰極として機能する第2の電極704に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム)からなる金属膜を用いることができる。こうして、光を反射する金属膜を用いることで光が透過しない陰極を形成することができる。

40

【0104】

こうして、図7(b)の矢印に示すように発光素子からの光を下面に取り出すことが可能になる。

【0105】

両面射出構造の発光素子について図7(c)を用いて説明する。射出構造以外は図7(a)と同じ構造の発光素子であるため同じ符号を用いて説明する。

【0106】

ここで、陽極として機能する第1の電極702に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウムスズ酸化物)膜、インジウム亜鉛酸化物IZO膜などの透明導電膜を用いることができる。透明性を有する透明導電膜を用いることで光を透過させることができ陰極を形成することができる。

【0107】

また、陰極として機能する第2の電極704に用いる材料としては、仕事関数の小さい材

50

料 (Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム) からなる金属薄膜と、透明導電膜 (ITO (インジウムスズ酸化物)、酸化インジウム酸化亜鉛合金 (In<sub>2</sub>O<sub>3</sub> ZnO)、酸化亜鉛 (ZnO) 等)との積層を用いるのが良い。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることで光を透過させることができが可能な陰極を形成することができる。

【0108】

こうして、図7(c)の矢印に示すように発光素子からの光を両面に取り出すことが可能になる。

【0109】

以上で述べたような射出構造を本発明の表示装置では採用することができる。

10

【0110】

また、図7で述べた射出構造において、層間膜を増やした別の構成を取りうることもできる。

【0111】

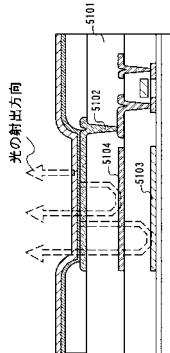

図51に例として上面射出構造の発光素子を具備する構成について述べる。図51において図7(a)と異なる点として、層間絶縁膜5101を一層設け、第1の電極と接続するための配線5102を設ける構成を採用する。層間絶縁膜5101に平坦性を有する膜を採用することで、層間絶縁膜5101の上に設ける第1の電極などにおいて層間膜の段差に起因する配線の断絶等を軽減することができ、好適である。

【0112】

また、発光素子の下部に、ゲート電極と同一の材料よりなる第1の反射電極5103、ソースドレイン電極と同一の材料よりなる第2の反射電極5104を設ける構成を採用するとよい。上面射出構造においては、発光素子下部に射出する光が視認者側に射出されず、光の取り出し効率が悪い。しかし、前記第1の反射電極5103、前記第2の反射電極5104を設ける構成を採用することによって、より発光素子上面に光りを射出することができ好適である。

20

【0113】

以上で述べたような射出構造を本発明の表示装置では採用することができる。

【0114】

(本実施形態の表示装置における発光素子材料の構成)

30

次に、本発明の表示装置に適用可能な発光素子に適用する発光素子材料の具体的な例について説明する。

【0115】

本発明の画素部の構成について、本発明の絵素は、第1の画素、第2の画素、第3の画素、第4の画素、第5の画素、第6の画素を有することについて、図2において説明した。また、第1～6の画素にはそれぞれ、発光素子が設けられており、第1の画素には発光素子R1、第2の画素には発光素子R2、第3の画素には発光素子G1、第4の画素には発光素子G2、第5の画素には発光素子B1、第6の画素には発光素子B2がそれぞれ接続されている。

【0116】

そして本明細書における、本発明の第1の画素の発光素子R1及び第2の画素の発光素子R2は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有するものである。また、本発明の第3の画素の発光素子G1及び第4の画素の発光素子G2は、は、CIE-X Y色度図で表したときに、色度図のyが0.55以上の領域に座標を有するものである。また、本発明の第5の画素の発光素子B1及び第6の画素の発光素子B2は、CIE-X Y色度図を表したときに、色度図のxが0.15以下、yが0.2以下の領域に座標を有するものである。

40

【0117】

なお、前記第1の画素が具備する発光素子、前記第2の画素が具備する発光素子のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.6以上、yが0.35以

50

下の領域に座標を有することであること、前記第3の画素が具備する発光素子、前記第4の画素が具備する発光素子のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.3以下、yが0.6以上の領域に座標を有することであること、前記第5の画素が具備する発光素子、前記第6の画素が具備する発光素子のいずれかは、CIE-X Y色度図で表したときに、色度図のxが0.15以下、yが0.2以下の領域に座標を有するものであることを満たす構成とすることはより好適である。第1の画素に設けられた発光素子と第2の画素に設けられた発光素子、第3の画素に設けられた発光素子と第4の画素に設けられた発光素子、及び第5の画素に設けられた発光素子と第6の画素に設けられた発光素子を、CIE-X Y色度図で表したときにその色座標を異なる領域に配置することによって、CIE-X Y色度図上における色再現範囲がさらに向上した表示装置を得ることができる。

10

### 【0118】

本発明の第1の画素、第2の画素に用いる発光素子R1、発光素子R2の具体的な例について説明する。

### 【0119】

第1の画素に設けられている発光素子R1の具体的な素子構造について述べる。まずITO(110nm)上に、正孔注入層としてCuPcを20nm、次いで正孔輸送層としてNPBを30nm、次いで発光層として、ホスト材料である2,3-ビス(4-ジフェニルアミノフェニル)キノキサリン(略称:TPAQn)と(アセチルアセトナト)ビス[2-(2'-ベンゾチエニル)ピリジナト-N,C3']イリジウム(略称:Ir(btp)2(acac))とを共蒸着した層を30nm、次いで電子輸送層としてBA1qを10nm、さらにA1qを20nm、次いで電子注入層としてフッ化カルシウムを2nm、最後に陰極としてAlを150nm成膜して作製した。なお、発光層におけるTPAQnとIr(btp)2(acac)との割合は、Ir(btp)2(acac)が8wt%となるように調節した。

20

### 【0120】

また、第2の画素に設けられている発光素子R2の具体的な素子構造について述べる。まずITO(110nm)上に、正孔注入層としてCuPcを20nm、次いで正孔輸送層としてNPBを30nm、次いで発光層として、ホスト材料であるTPAQnとルブレンを共蒸着した層を30nm、次いで電子輸送層としてBA1qを10nm、さらにA1qを20nm、次いで電子注入層としてフッ化カルシウムを2nm、最後に陰極としてAlを150nm成膜して作製した。なお、発光層におけるTPAQnとルブレンとの割合はルブレンが10wt%となるように調整した。

30

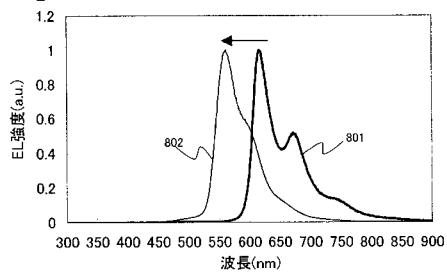

### 【0121】

上記作製された発光素子R1についての発光スペクトル801、発光素子R2についての発光スペクトル802について図8に示す。図8の発光スペクトルは発光素子に25mA/cm<sup>2</sup>の電流密度で電流を流した際の発光スペクトルである。図8において、R1の発光スペクトル801の低波長側にシフトした位置にR2の発光スペクトル802が存在する。このとき、発光素子R1のCIE-X Y色度図における色度座標は、(x, y) = (0.68, 0.32)である。また、発光素子R2のCIE-X Y色度図における色度座標は、(x, y) = (0.47, 0.52)となる。

40

### 【0122】

次に本発明の第3の画素、第4の画素に用いる発光素子G1、発光素子G2の具体的な例について説明する。

### 【0123】

第3の画素に設けられている発光素子G1の具体的な素子構造について述べる。ITO(110nm)上に、正孔注入層としてDNTPDを50nm、次いで正孔輸送層としてNPBを10nm、次いで発光層として、ホスト材料であるAlqとクマリン6とを共蒸着した層を37.5nm、次いで電子輸送層としてAlqを37.5nm、次いで電子注入層としてフッ化カルシウムを2nm、最後に陰極としてAlを150nm成膜して作製

50

した。なお、発光層における Alq とクマリン 6 の割合は、クマリン 6 が 0.3 wt % となるように調節した。

【0124】

また、第 4 の画素に設けられている発光素子 G 2 の具体的な素子構造について述べる。ITO (110 nm) 上に、正孔注入層として DNTPD を 50 nm、次いで正孔輸送層として NPB を 10 nm、次いで発光層として、ホスト材料である Alq と DMQd を共蒸着した層を 37.5 nm、次いで電子輸送層として Alq を 37.5 nm、次いで電子注入層としてフッ化カルシウムを 2 nm、最後に陰極として Al を 150 nm 成膜して作製した。なお、発光層における Alq と DMQd の割合は、DMQd が 0.3 wt % となるように調節した。

10

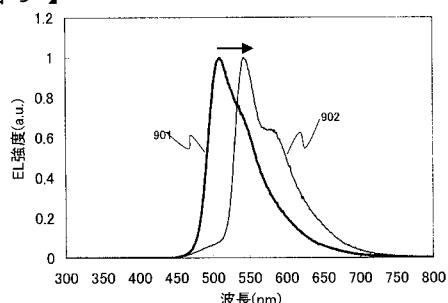

【0125】

上記作製された発光素子 G 1 についての発光スペクトル 901、発光素子 G 2 について発光スペクトル 902 について図 9 に示す。図 9 の発光スペクトルは発光素子に 25 mA / cm<sup>2</sup> の電流密度で電流を流した際の発光スペクトルである。図 9 において、G 1 の発光スペクトル 901 の高波長側にシフトした位置に G 2 の発光スペクトル 902 が存在する。このとき、発光素子 G 1 の CIE-X Y 色度図における色度座標は、(x, y) = (0.28, 0.63) である。また、発光素子 G 2 の CIE-X Y 色度図における色度座標は、(x, y) = (0.43, 0.56) となる。

【0126】

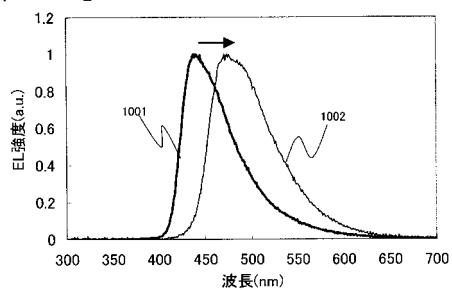

次に本発明の第 5 の画素、第 6 の画素に用いる発光素子 B 1、発光素子 B 2 の具体的な例について説明する。

20

【0127】

第 5 の画素に設けられている発光素子 B 1 の具体的な素子構造について述べる。ITO (110 nm) 上に、正孔注入層として DNTPD を 30 nm、次いで正孔輸送層として NPB を 30 nm、次いで発光層として t-BuDNA を 40 nm、次いで電子輸送層として Alq を 20 nm、次いで電子注入層としてフッ化カルシウムを 2 nm、最後に陰極として Al を 150 nm 成膜して作製した。

【0128】

また、第 6 の画素に設けられている発光素子 B 2 の具体的な素子構造について述べる。ITO (110 nm) 上に、正孔注入層として DNTPD を 30 nm、次いで正孔輸送層として NPB を 30 nm、次いで発光層として t-BuDNA と TPAQn を共蒸着した層を 40 nm、次いで電子輸送層として Alq を 20 nm、次いで電子注入層としてフッ化カルシウムを 2 nm、最後に陰極として Al を 150 nm 成膜して作製した。なお、発光層における t-BuDNA と TPAQn の割合は、TPAQn が 5 wt % となるように調整した。

30

【0129】

上記作製された発光素子 B 1 についての発光スペクトル 1001、発光素子 B 2 について発光スペクトル 1002 について図 10 に示す。図 10 の発光スペクトルは発光素子に 25 mA / cm<sup>2</sup> の電流密度で電流を流した際の発光スペクトルである。図 10 において、B 1 の発光スペクトル 1001 の高波長側にシフトした位置に B 2 の発光スペクトル 1002 が存在する。このとき、発光素子 B 1 の CIE-X Y 色度図における色度座標は、(x, y) = (0.15, 0.11) である。また、発光素子 B 2 の CIE-X Y 色度図における色度座標は、(x, y) = (0.18, 0.32) となる。

40

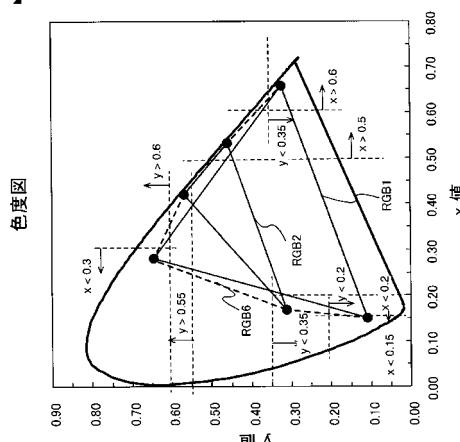

【0130】

図 11 に CIE-X Y 色度図を示し、上記作製した発光素子 R 1、発光素子 R 2、発光素子 G 1、発光素子 G 2、発光素子 B 1、発光素子 B 2 の各色度座標をプロットした図を示す。図 11 において、発光素子 R 1、発光素子 G 1、発光素子 B 1 の色度座標について点を結んだ領域を RGB 1 とし、発光素子 R 2、発光素子 G 2、発光素子 B 2 の色度座標について点を結んだ領域を RGB 2 とする。色の 3 原色である RGB について異なる色合いの発光素子を具備することによって、図 11 に示す RGB 6 で囲まれた領域の各色の色

50

合いを表現することができ、CIE-X Y色度図上における色再現範囲が向上した表示装置を提供することができる。

【0131】

なお、各発光素子において、色純度を高めるため、発光素子の発光領域と反射電極（光を反射する電極）との光学的距離をL、目的とする波長をλとするとき  $L = (2m - 1) / 4$ （但し m は 1 以上の自然数）を満たすようにするいわゆる微小共振器構造（マイクロキヤビティ構造）を採用してもよい。なお、光学的距離は「実際の距離 × 波長 / における屈折率」で算出される。

【0132】

なお、発光素子 R2、G2、B2 の色度座標のいずれかは、発光素子 R1、G1、B1 の色度座標を結んで形成された領域以外の場所に存在すればよい。これは発光素子 R2、G2、B2 の全てが発光素子 R1、G1、B1 の色度座標を結んで形成された領域の中に存在すると、図 11 における RGB1 と RGB2 の色再現範囲が重複するためである。

【0133】

以上、本発明の表示装置は、上述の発光素子の材料を各画素において採用することができる。なお、上記列挙した発光素子の材料は一部に過ぎず、本発明と同様の色度座標を取りうる発光素子であれば、何でもよい。

【0134】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【0135】

（実施の形態 2）

本実施の形態においては上記実施の形態で述べた本発明の表示装置における発光素子の構成とは別の構成について述べる。

【0136】

本発明の画素部の構成について、本発明の絵素は、第 1 の画素、第 2 の画素、第 3 の画素、第 4 の画素、第 5 の画素、第 6 の画素を有することについて、図 2 において説明した。また、第 1 ~ 6 の画素にはそれぞれ、発光素子が設けられており、第 1 の画素には発光素子 R1、第 2 の画素には発光素子 R2、第 3 の画素には発光素子 G1、第 4 の画素には発光素子 G2、第 5 の画素には発光素子 B1、第 6 の画素には発光素子 B2 がそれぞれ接続されている。

【0137】

そして本明細書における、本発明の第 1 の画素の発光素子 R1 及び第 2 の画素の発光素子 R2 は、CIE-X Y 色度図で表したときに、色度図の x が 0.50 以上の領域に座標を有するものとする。また、本発明の第 3 の画素の発光素子 G1 及び第 4 の画素の発光素子 G2 は、は、CIE-X Y 色度図で表したときに、色度図の y が 0.55 以上の領域に座標を有するものとする。また、本発明の第 5 の画素の発光素子 B1 及び第 6 の画素の発光素子 B2 は、CIE-X Y 色度図を表したときに、色度図の x が 0.15 以下、y が 0.2 以下の領域に座標を有するものである。

【0138】

本実施の形態においては、第 1 の画素、第 2 の画素に設けられた発光素子 R1、R2、第 3 の画素、第 4 の画素に設けられた発光素子 G1、G2、第 5 の画素、第 6 の画素に設けられた発光素子 B1、B2 において、それぞれの発光素子の膜厚を異ならせて発光スペクトルを異ならせる。その結果、CIE-X Y 色度図で表したときに、色度図の座標を第 1 の画素、第 2 の画素に設けられた発光素子 R1、R2、第 3 の画素、第 4 の画素に設けられた発光素子 G1、G2、第 5 の画素、第 6 の画素に設けられた発光素子 B1、B2 で異ならせる。以下、その具体例について述べる。

【0139】

本実施の形態においては、第 3 の画素、第 4 の画素に用いる発光素子 G1、発光素子 G2 について、CIE-X Y 色度図で表したときに色度図の座標を異ならせるための具体的

10

20

30

40

50

な例について説明する。

【0140】

第3の画素に設けられている発光素子G1の具体的な構造について述べる。まず、ITO(110nm)上に、ホール注入層としてCuPcを20nm、次いでホール輸送層としてNPBを40nm、次いで発光層として、ホスト材料であるAlqと緑色発光材料であるクマリン6とを共蒸着した層を40nm、次いで電子注入層としてAlqとLiとを共蒸着した層を30nm、最後に陰極としてAlを150nm成膜して作製した。なお、発光層におけるAlqとクマリン6との割合は、クマリン6が0.3wt%となるように調節した。また、電子注入層におけるAlqとLiとの割合は、Liが1wt%となるように調整した。

10

【0141】

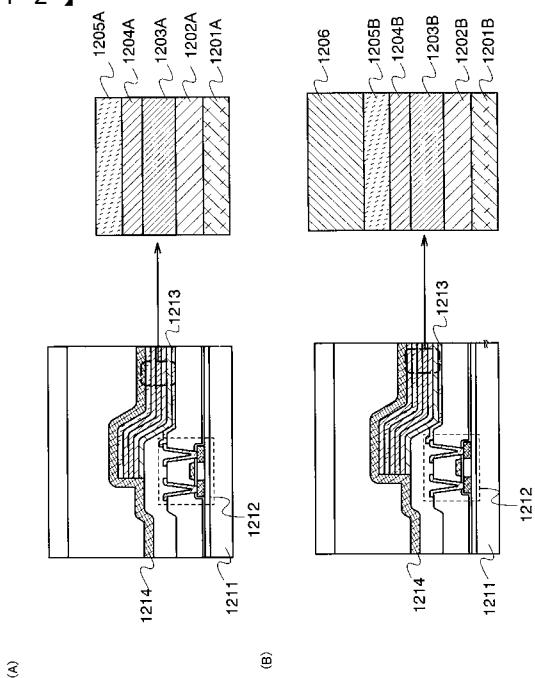

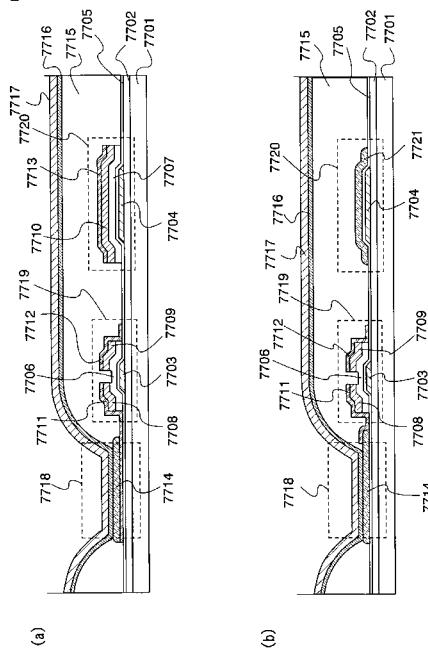

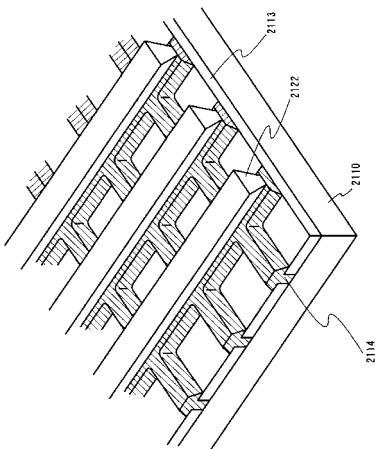

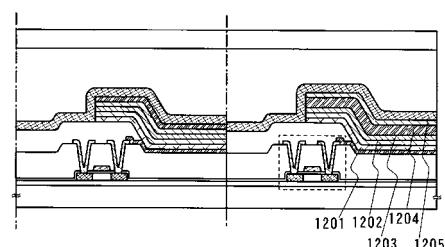

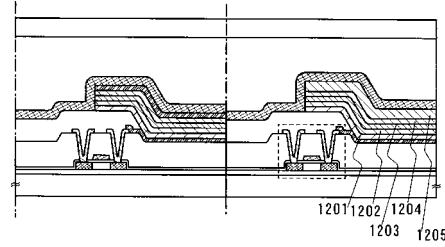

図12(a)に第3の画素に設けられる発光素子G1の積層構造について示す。基板1211の上にトランジスタ1211を介して陽極1213、正孔注入材料からなる正孔注入層1201A、その上に正孔輸送材料からなる正孔輸送層1202A、発光層1203A、電子輸送材料からなる電子輸送層1204A、電子注入材料からなる電子注入層1205A、そして陰極1214を積層させた素子構造である。なお図12(a)の右図における積層構造は、図12(a)における発光素子部の拡大した断面図である。

【0142】

また第4の画素に設けられている発光素子G2の具体的な素子構造について述べる。まず、ITO(110nm)上に、ホール注入層としてCuPcを20nm、次いでホール輸送層としてNPBを40nm、次いで発光層として、ホスト材料であるAlqと緑色発光材料であるクマリン6とを共蒸着した層を40nm、次いで電子注入層としてAlqとLiとを共蒸着した層を30nm、次いでNPBとモリブデン酸化物(VI)との共蒸着層を180nm、最後に陰極としてAlを150nm成膜して作製した。なお、発光層におけるAlqとクマリン6との割合は、クマリン6が0.3wt%となるように調節した。また、電子注入層におけるAlqとLiとの割合は、Liが1wt%となるように調整した。なお、NPBとモリブデン酸化物(VI)との割合は、モリブデン酸化物が20wt%となるように調整した。

20

【0143】

図12(b)に第4の画素に設けられる発光素子G2の積層構造について示す。基板1211の上にトランジスタ1211を介して陽極1213、正孔注入材料からなる正孔注入層1201B、その上に正孔輸送材料からなる正孔輸送層1202B、発光層1203B、電子輸送材料からなる電子輸送層1204B、電子注入材料からなる電子注入層1205B、NPBとモリブデン酸化物(VI)との共蒸着層1206、そして陰極1214を積層させた素子構造である。なお図12(b)の右図における積層構造は、図12(b)における発光素子部の拡大した断面図である。

30

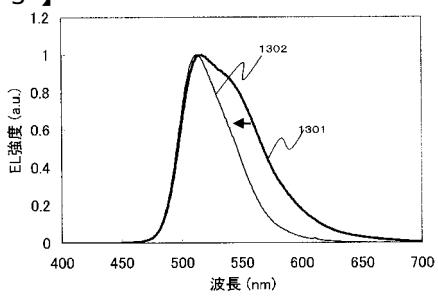

【0144】

また、上記図12(a)の如く積層形成された発光素子G1についての発光スペクトル1301、上記図12(b)の如く積層形成された発光素子G2について発光スペクトル1302について図13に示す。図13の発光スペクトルは発光素子に25mA/cm<sup>2</sup>の電流密度で電流を流した際の発光スペクトルである。図13において、G1の発光スペクトル1301の低波長側にシフトした位置にG2の発光スペクトル1302が存在する。このとき、発光素子G1のCIE-X Y色度図における色度座標は、(x, y) = (0.30, 0.64)である。また、発光素子G2のCIE-X Y色度図における色度座標は、(x, y) = (0.21, 0.69)となる。

40

【0145】

また、同様に第1の画素に設けられた発光素子R1と第2の画素に設けられた発光素子R2、第5の画素に設けられた発光素子B1と第6の画素に設けられた発光素子B2において、それぞれ異なる膜厚を有する発光素子を具備することで、異なる発光スペクトルを有する発光素子を得ることができる。換言すれば第1の画素に設けられた発光素子R1と

50

第2の画素に設けられた発光素子R2、第5の画素に設けられた発光素子B1と第6の画素に設けられた発光素子B2において、異なるCIE-X Y色度図上の色度座標を有する発光素子を得ることができる。

【0146】

本実施の形態に例示した如く、発光素子の膜厚を発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1とB2とで異なる膜厚とすることによって異なるCIE-X Y色度図上の色度座標を有する発光素子を得ることができる。勿論異なる発光素子の材料を用いて、なおかつ発光素子の膜厚を変えることで異なるCIE-X Y色度図上の色度座標を有する発光素子を得てもよい。

【0147】

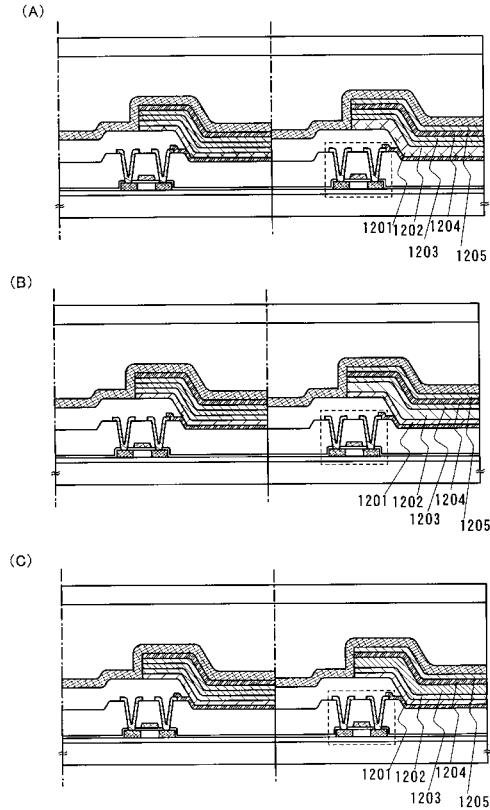

また、発光素子の膜厚を異ならせること（厚膜化）で発光スペクトルを異ならせることは、共蒸着層を形成することで達成することに特に限定されず、例えば図45、図54において示すように、正孔注入層1201、正孔輸送層1202、発光層1203、電子輸送層1204、または電子注入層1205を厚膜化することで達成してもよい。例えば図45(a)に示すように、正孔注入層1201を厚膜化して、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1とB2とで異なる膜厚としてもよい。また、図45(b)に示すように、正孔輸送層1202を厚膜化して、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1とB2とで異なる膜厚としてもよい。また、図45(c)に示すように、発光層1203を厚膜化して、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1とB2とで異なる膜厚としてもよい。また、図54(a)に示すように、電子輸送層1204を厚膜化して、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1とB2とで異なる膜厚としてもよい。また、図54(b)に示すように、電子注入層を厚膜化して、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1とB2とで異なる膜厚としてもよい。勿論、正孔注入層、正孔輸送層、発光層、電子輸送層、または電子注入層のいずれか複数を厚膜化して発光スペクトルを異ならせ、異なるCIE-X Y色度図上の色度座標を有する発光素子を得てもよい。

【0148】

なお、本実施の形態においては、厚膜化の達成のために金属酸化物を含む共蒸着層を用いた。金属酸化物を共蒸着層に用いることによって、膜厚化による駆動電圧の上昇を防止でき、好適である。

【0149】

なお、本発明における本実施の形態は、発光素子の発光領域と反射電極（光を反射する電極）との光学的距離L、目的とする波長をλとすると $L = (2m - 1) / 4$ （但し $m$ は1以上の自然数）を満たすようにするいわゆる微小共振器構造（マイクロキャビティ構造）とは異なる。なお、光学的距離は「実際の距離×波長」における屈折率で算出されるものである。本発明の本実施の形態において発光素子の光学的距離は、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2の発光スペクトルが異なりさえすれば、どのように設計してもよい。例えば、発光素子の膜厚を、発光素子R1、発光素子R2、発光素子G1、発光素子G2、発光素子B1、発光素子B2の順に薄く設計してもよいし、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2の順に薄く設定してもよい。

【0150】

なお、本実施の形態において、発光素子の厚膜化を行うことで、発光素子の第1の電極（陽極）と発光素子の第2の電極（陰極）との距離Dは、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1とB2とでそれぞれ異なる。本明細書において、発光素子の第1の電極（陽極）と発光素子の第2の電極（陰極）との距離Dは、それぞれの電極における発光層側の端面（本実施の形態においては、第1の電極側では正孔注入層との境界、第2の電極側では電子注入層との境界）間の距離とする。

【0151】

10

20

30

40

50

以上、本発明の表示装置は、上述の発光素子の材料を各画素において採用することができる。なお、上記列挙した発光素子の材料は一部に過ぎず、本発明と同様の色度座標を取りうる発光素子であれば、何でもよい。

【0152】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【0153】

(実施の形態3)

本実施の形態においては上記実施の形態で述べた本発明の表示装置における発光素子の構成とは別の構成について述べる。

【0154】

本発明の画素部の構成について、本発明の絵素は、第1の画素、第2の画素、第3の画素、第4の画素、第5の画素、第6の画素を有することについて、図2において説明した。また、第1～6の画素にはそれぞれ、発光素子が設けられており、第1の画素には発光素子R1、第2の画素には発光素子R2、第3の画素には発光素子G1、第4の画素には発光素子G2、第5の画素には発光素子B1、第6の画素には発光素子B2がそれぞれ接続されている。

【0155】

そして本明細書における、本発明の第1の画素の発光素子R1及び第2の画素の発光素子R2は、CIE-X Y色度図で表したときに、色度図のxが0.50以上の領域に座標を有するものである。また、本発明の第3の画素の発光素子G1及び第4の画素の発光素子G2は、は、CIE-X Y色度図で表したときに、色度図のyが0.55以上の領域に座標を有するものである。また、本発明の第5の画素の発光素子B1及び第6の画素の発光素子B2は、CIE-X Y色度図を表したときに、色度図のxが0.15以下、yが0.2以下の領域に座標を有するものである。

【0156】

本実施の形態においては、第1の画素、第2の画素に設けられた発光素子R1、R2、第3の画素、第4の画素に設けられた発光素子G1、G2、第5の画素、第6の画素に設けられた発光素子B1、B2において、発光スペクトルをR1とR2、G1とG2、B1とB2とで概略等しくし、それぞれの発光素子からの光の透過部にカラーフィルターを設ける構成とすることによって発光スペクトルを異ならせる。その結果、CIE-X Y色度図で表したときに、色度図の座標を第1の画素、第2の画素に設けられた発光素子R1、R2、第3の画素、第4の画素に設けられた発光素子G1、G2、第5の画素、第6の画素に設けられた発光素子B1、B2で異ならせる。以下、その具体例について述べる。

【0157】

本実施の形態においては、表示装置の構成について絵素部の断面構造を用いて説明する。

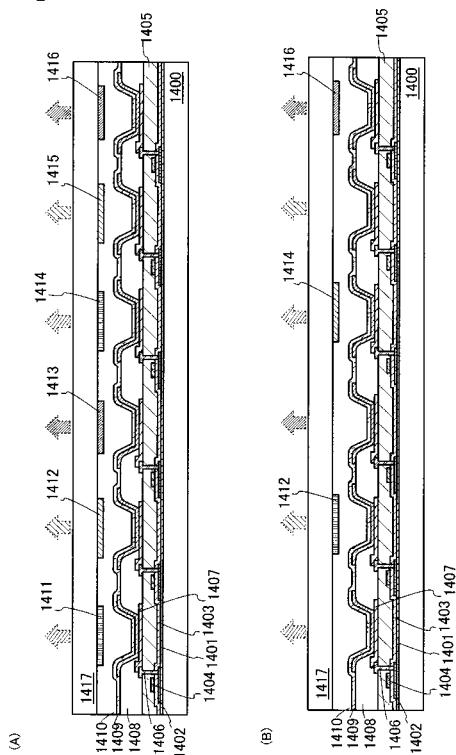

【0158】

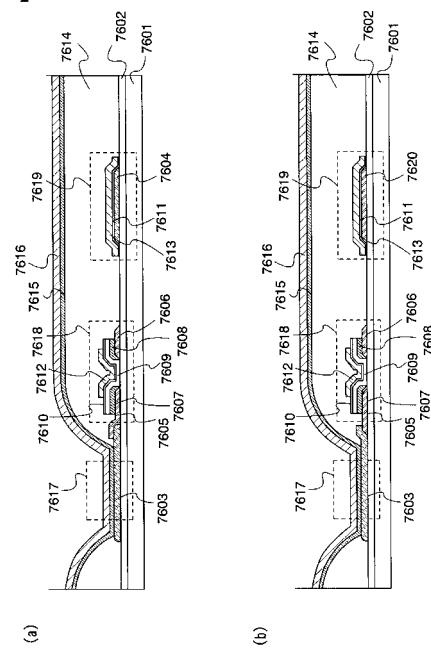

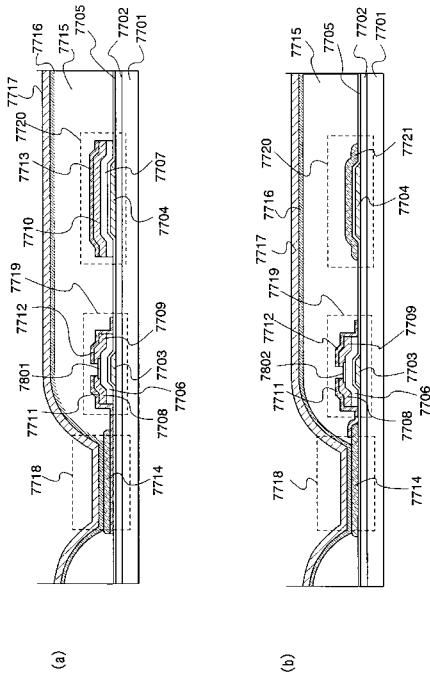

図14は本実施の形態における表示装置の絵素の断面図の一部である。図14(A)に示した本発明の表示装置は基板1400、下地絶縁膜1401、半導体層1402、ゲート絶縁膜1403、ゲート電極1404、層間絶縁膜1405、接続部1406、発光素子の第1の電極1407、隔壁1408、発光層1409、発光素子の第2の電極1410、カラーフィルター(R1)1411、カラーフィルター(R2)1412、カラーフィルター(G1)1413、カラーフィルター(G2)1414、カラーフィルター(B1)1415、カラーフィルター(B2)1416、対向基板1417の構成を含む。

【0159】

発光素子は、発光素子の第1の電極1407と第2の電極1410とに発光層1409が挟まれている部分に形成される。発光素子は第1の電極1407と電気的に接触する接続部1406を介して半導体層1402、ゲート絶縁膜1403、ゲート電極1404よりなる薄膜トランジスタに接続され、発光の制御がなされる。また、本実施の形態においては、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

て、第1の電極1407は反射率の高い材料により形成された反射電極とし、第2の電極1410は透光性を有する導電材料により形成された透明電極とし、第2の電極1410の方向から光を射出する構成となっている。

#### 【0160】

なお、図14(A)における薄膜トランジスタは、左から順に発光素子R1、発光素子G1、発光素子B1、発光素子R2、発光素子G2、発光素子B2を駆動するものとする。なお各画素におけるカラーフィルターを設けない場合の発光素子の発光スペクトルは、R1とR2、G1とG2、B1とB2とで概略等しいものであるとする。なお、図14(A)で表す矢印は、左から順に発光素子R1、発光素子G1、発光素子B1、発光素子R2、発光素子G2、発光素子B2からのカラーフィルターを介した発光を模式的に表したものである。

#### 【0161】

本実施の形態において、第1の画素、第2の画素に設けられた発光素子R1、R2、第3の画素、第4の画素に設けられた発光素子G1、G2、第5の画素、第6の画素に設けられた発光素子B1、B2のそれぞれについて、光が射出される側にはカラーフィルター(R1)1411、カラーフィルター(R2)1412、カラーフィルター(G1)1413、カラーフィルター(G2)1414、カラーフィルター(B1)1415、カラーフィルター(B2)1416が設けられている。本実施の形態においては、カラーフィルター(R1)1411とカラーフィルター(R2)1412、カラーフィルター(G1)1413とカラーフィルター(G2)1414、カラーフィルター(B1)1415とカラーフィルター(B2)1416との光の透過特性を異ならせることによって、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2とで射出される光の発光スペクトルを異ならせることによって、異なるCIE-X Y色度図上の色度座標を有する発光素子を得ることができる。

#### 【0162】

なお、カラーフィルターは顔料分散法、印刷法、電着法、染色法のいずれの方法で作製されたものであってもよい。また、第1の画素、第2の画素に設けられた発光素子R1、R2、第3の画素、第4の画素に設けられた発光素子G1、G2、第5の画素、第6の画素に設けられた発光素子B1、B2のそれぞれには、同じ発光スペクトルを有する発光素子、例えば白色光を射出する発光スペクトルを具備する発光素子であってもよい。同一の発光素子を具備することによって、発光素子作成のプロセスを簡略化することができ、好適である。

#### 【0163】

また、図14(B)は本実施の形態における表示装置の絵素の断面図の一部である。なお、図14(B)に示した本発明の表示装置の各構成は図14(A)に準ずる。

#### 【0164】

図14(A)との違いは、発光素子R1、発光素子G1、発光素子B1から射出される光について、カラーフィルターを介しない点である。このとき各画素におけるカラーフィルターを設けない場合の発光素子の発光スペクトルは、R1とR2、G1とG2、B1とB2とで概略等しいものであるとする。図14(B)においては、発光素子R2、発光素子G2、発光素子B2から射出される光の発光スペクトルをカラーフィルター(R2)1412、カラーフィルター(G2)1414、カラーフィルター(B2)1416の透過特性によって異ならせる。その結果、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2とで射出される光の発光スペクトルを異ならせることによって、異なるCIE-X Y色度図上の色度座標を有する発光素子を得ることができる。

#### 【0165】

なお、同一色の発光素子を全面に配置し、透過特性のそれぞれ異なるカラーフィルタを介して、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2とで射出される光の発光スペクトルを異ならせることによって、異なるCIE

10

20

30

40

50

- X Y 色度図上の色度座標を有する発光素子を得ることを達成してもよい。例えば、同一色の発光素子としては白色の発光素子を配し、図 14 (A) のように、第 1 の画素～第 6 の画素の上部にカラーフィルタを配すればよい。

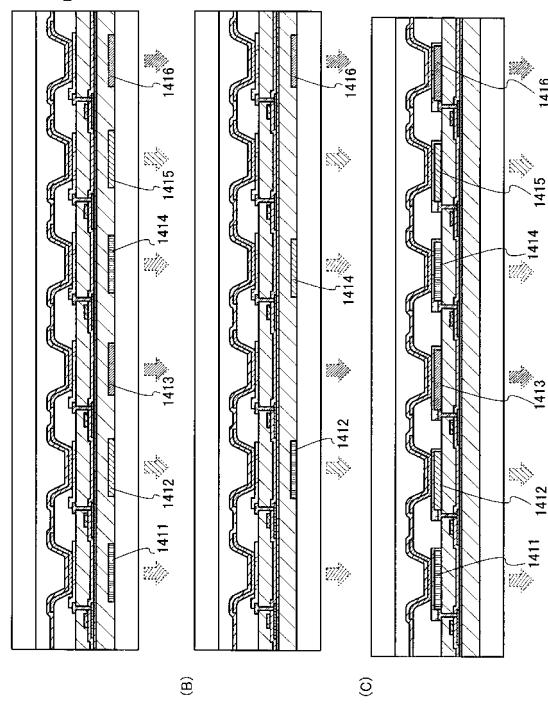

#### 【 0 1 6 6 】

また、図 15 (A) は図 14 (A) と異なる構成を有する本発明の表示装置を表す図である。なお、図 15 (A) に示した本発明の表示装置の各構成は図 14 (A) に準ずる。図 15 (A) では、発光素子の第 1 の電極 1407 側に発光素子が光を射出する構成のボトムエミッション型の表示装置の例を示した。図 15 (B) では第 1 の電極 1407 側から発光を取り出す為、第 1 の電極 1407 は透光性を有する導電材料で形成し、第 2 の電極 1410 を反射電極として反射率の高い導電材料を用いて作製する。

10

#### 【 0 1 6 7 】

本実施の形態において、第 1 の画素、第 2 の画素に設けられた発光素子 R1、R2、第 3 の画素、第 4 の画素に設けられた発光素子 G1、G2、第 5 の画素、第 6 の画素に設けられた発光素子 B1、B2 のそれぞれについて、光が射出される側にはカラーフィルター (R1) 1411、カラーフィルター (R2) 1412、カラーフィルター (G1) 1413、カラーフィルター (G2) 1414、カラーフィルター (B1) 1415、カラーフィルター (B2) 1416 が設けられている。本実施の形態においては、カラーフィルター (R1) 1411 とカラーフィルター (R2) 1412、カラーフィルター (G1) 1413 とカラーフィルター (G2) 1414、カラーフィルター (B1) 1415 とカラーフィルター (B2) 1416 との光の透過特性を異ならせることによって、発光素子 R1 と発光素子 R2、発光素子 G1 と発光素子 G2、発光素子 B1 と発光素子 B2 とで射出される光の発光スペクトルを異ならせることによって、異なる CIE-X Y 色度図上の色度座標を有する発光素子を得ることができる。

20

#### 【 0 1 6 8 】

なお、カラーフィルターは顔料分散法、印刷法、電着法、染色法のいずれの方法で作製されたものであってもよい。また、第 1 の画素、第 2 の画素に設けられた発光素子 R1、R2、第 3 の画素、第 4 の画素に設けられた発光素子 G1、G2、第 5 の画素、第 6 の画素に設けられた発光素子 B1、B2 のそれぞれには、同じ発光スペクトルを有する発光素子、例えば白色光を射出する発光スペクトルを具備する発光素子であってもよい。同一の発光素子を具備することによって、発光素子作成のプロセスを簡略化することができ、好適である。

30

#### 【 0 1 6 9 】

また、図 15 (B) は本実施の形態における表示装置の絵素の断面図の一部である。なお、図 15 (B) に示した本発明の表示装置の各構成は図 15 (A) に準ずる。

#### 【 0 1 7 0 】

図 15 (A) との違いは、発光素子 R1、発光素子 G1、発光素子 B1 から射出される光について、カラーフィルターを介しない点である。このとき各画素におけるカラーフィルターを設けない場合の発光素子の発光スペクトルは、R1 と R2、G1 と G2、B1 と B2 で概略等しいものであるとする。図 15 (B) においては、発光素子 R2、発光素子 G2、発光素子 B2 から射出される光の発光スペクトルをカラーフィルター (R2) 1412、カラーフィルター (G2) 1414、カラーフィルター (B2) 1416 の透過特性によって異ならせる。その結果、発光素子 R1 と発光素子 R2、発光素子 G1 と発光素子 G2、発光素子 B1 と発光素子 B2 とで射出される光の発光スペクトルを異ならせることによって、異なる CIE-X Y 色度図上の色度座標を有する発光素子を得ることができる。

40

#### 【 0 1 7 1 】

なお、同一色の発光素子を全面に配置し、当該発光素子に重畠的に透過特性のそれぞれ異なるカラーフィルターを設け、当該カラーフィルターを介して射出される発光素子 R1 と発光素子 R2、発光素子 G1 と発光素子 G2、発光素子 B1 と発光素子 B2 の発光スペクトルを異ならせることによって、異なる CIE-X Y 色度図上の色度座標を有する発光

50

素子を得ることを達成してもよい。例えば、同一色の発光素子としては白色の発光素子を配し、図15(A)のように、第1の画素～第6の画素の上部にカラーフィルターを配すればよい。

【0172】

また、図15(C)は本実施の形態における表示装置の絵素の断面図の一部である。なお、図15(C)に示した本発明の表示装置の各構成は図14(A)に準ずる。

【0173】

図15(A)、(B)との違いは、カラーフィルター(R1)1411、カラーフィルター(R2)1412、カラーフィルター(G1)1413、カラーフィルター(G2)1414、カラーフィルター(B1)1415、カラーフィルター(B2)1416について、位置を発光素子とトランジスタの間に配置された第1の電極1407の下に配置した点にある。プロセスが簡便になり容易である。その結果、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2とで射出される光の発光スペクトルを異ならせることによって、異なるCIE-X Y色度図上の色度座標を有する発光素子を得ることができる。

【0174】

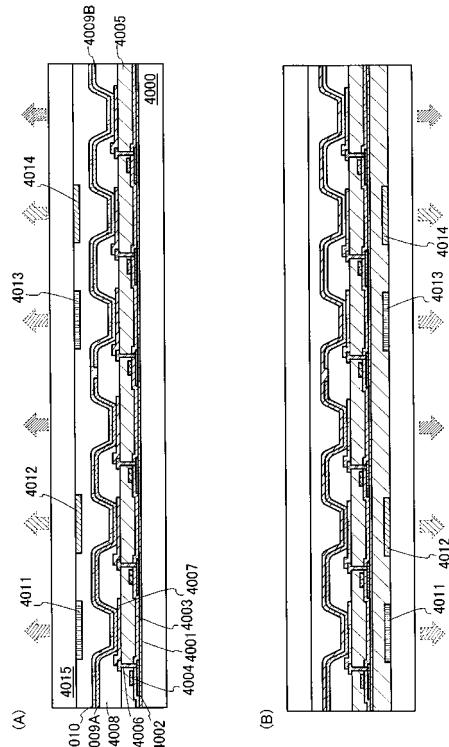

また、波長が短い単色光の発光素子を配置し、色変換層を通して必要な色に変換する方法を用いて、発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2とで射出される光の発光スペクトルを異ならせることによって、異なるCIE-X Y色度図上の色度座標を有する発光素子を得ることを達成してもよい。図40(A)に示した本発明の表示装置は基板4000、下地絶縁膜4001、半導体層4002、ゲート絶縁膜4003、ゲート電極4004、層間絶縁膜4005、接続部4006、発光素子の第1の電極4007、隔壁4008、発光層4009A及び発光層4009B、発光素子の第2の電極4010、色変換層(R1)4011、色変換層(G1)4012、色変換層(R2)4013、色変換層(G2)4014、対向基板4015の構成を含む。

【0175】

例えば、波長が短い単色光の発光層4009A、発光層4009Bとしては発光スペクトルの異なる青色の発光素子B1、B2を配し、図40(A)のように上面発光(トップエミッション)の場合は、第1の画素、第2の画素、第4の画素、第5の画素の上部に色変換層を配すればよい。また、ボトムエミッションを採用する場合には、波長が短い単色光の発光層4009A、4009Bとしては発光スペクトルの異なる青色の発光素子B1、B2を配し、図40(B)のように第1の画素、第2の画素、第4の画素、第5の画素の下部に色変換層を配置すればよい。

【0176】

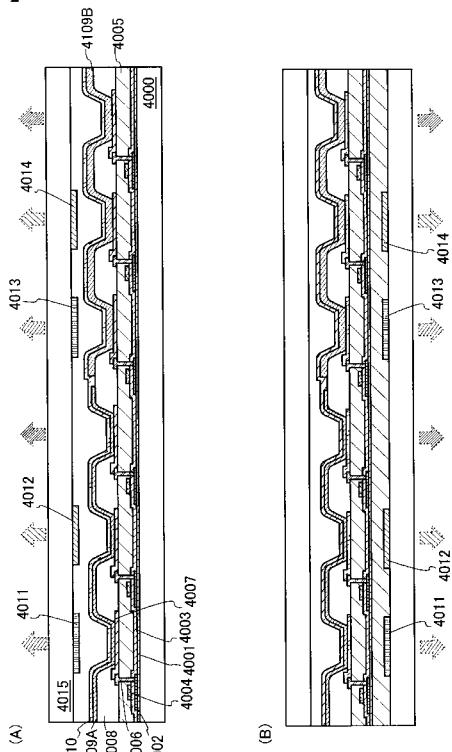

なお、波長が短い単色光の発光素子として発光スペクトルの異なる青色の発光素子B1、B2を配置する場合には、図41の発光層4109A及び発光層4109Bのように青色の発光素子B1とB2の発光素子の膜厚を異ならせ、発光スペクトルを異ならせてもよい。例えば、図41(A)のように上面発光(トップエミッション)の場合は、波長が短い単色光の発光素子として発光スペクトルの異なる青色の発光層4109A、発光層4109Bを配し、第1の画素、第2の画素、第4の画素、第5の画素の上部に色変換層を配すればよい。また、ボトムエミッションを採用する場合には、図41(B)のように青色の発光素子の発光層4109A、発光層4109Bの如く配し、第1の画素、第2の画素、第4の画素、第5の画素の下部に色変換層を配置すればよい。なお、図41に示した本発明の表示装置の各構成は図40に準ずる。

【0177】

色変換層を通して必要な色に変換する色変換法に関しては、発光素子から発する発光色が1色であるため、発光層の塗り分けが必要ないことが大きなメリットであるといえる。また、カラーフィルタ法と比較して、色変換法は色変換層により光の吸収、励起、発光の経過を用いて所望の発光を得るため好適である。

10

20

30

40

50

## 【0178】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

## 【0179】

## (実施の形態4)

本実施の形態においては、上記実施の形態で述べた一絵素内における画素の配置が図2に示したものとは別の構成について述べる。

## 【0180】

なお、本発明の画素部の構成について、本発明の絵素は、第1の画素、第2の画素、第3の画素、第4の画素、第5の画素、第6の画素を有することについて、図2において説明した。また、第1～6の画素にはそれぞれ、発光素子が設けられており、第1の画素には発光素子R1、第2の画素には発光素子R2、第3の画素には発光素子G1、第4の画素には発光素子G2、第5の画素には発光素子B1、第6の画素には発光素子B2がそれぞれ接続されている。

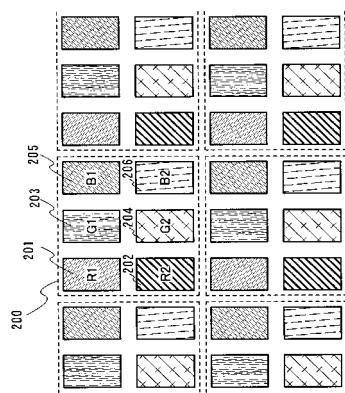

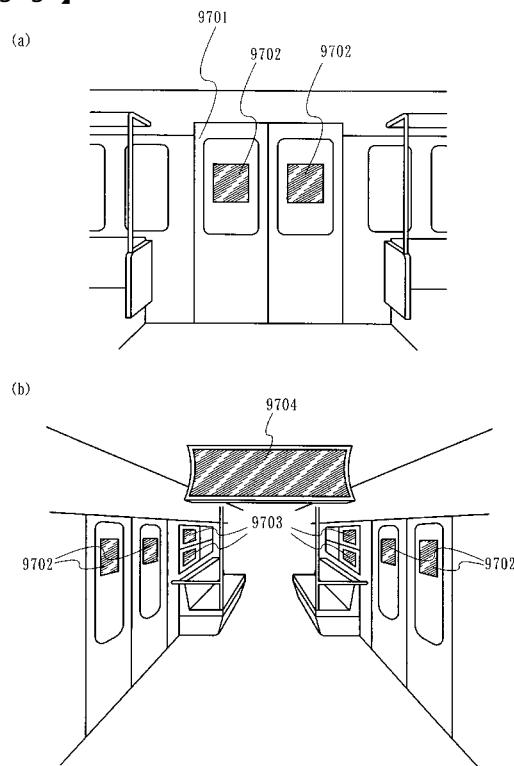

## 【0181】

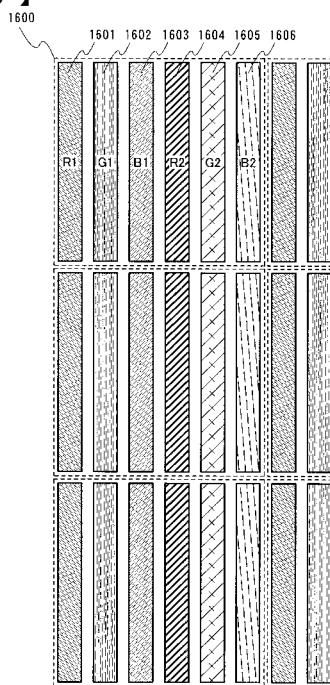

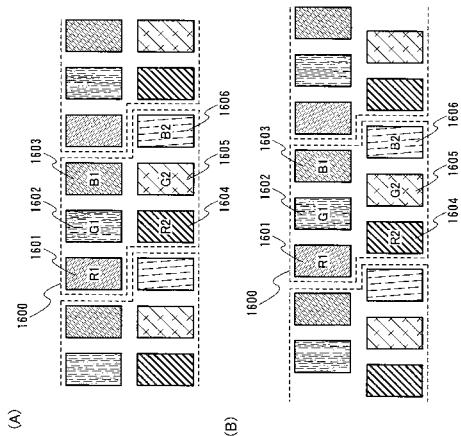

本実施の形態における表示装置の画素の配置は、図16に示すように、絵素1600の中に、第1の画素1601、第2の画素1602、第3の画素1603、第4の画素1604、第5の画素1605、第6の画素1606を有し、各画素がストライプ状に配置されている。

## 【0182】

なお、図16では、各々の第1の画素1601～第6の画素1606は列方向に並んで配置されているが、配置の仕方について特に限定はなく、例えば行方向に並べて配置されても良いし、また、例えば発光素子R1を具備する第1の画素1601と発光素子G2を具備する第5の画素1605が隣接するように配置されていても構わない。また各画素の形状についても、図16に示すような長方形に限らず、例えば正方形やその他の多角形あるいは曲率を有する形状であっても構わない。

## 【0183】

なお、第1の画素1601～第6の画素1606間の幅は、同じ間隔に配置してもよいし、異なる間隔に配置してもよい。

## 【0184】

また、図53(A)では、絵素1600において、第1の画素1601、第2の画素1602、第3の画素1603を並べて配置し、第4の画素1604、第5の画素1605、第6の画素1606を次行に並べて配し、第1の画素1601、第2の画素1602、第3の画素1603と第4の画素1604、第5の画素1605、第6の画素1606を一画素分ずらして配置させてもよい。本実施の形態では、行方向に一画素分ずらして配置したが、特に一画素に限定されない。例えば図53(B)に示すように半画素分ずらして配置させてもよい。このように画素を行毎にずらして配置するような構成を取ることで、特に自然の動画の表示において、なめらかな表示を行うことが可能となる。

## 【0185】

なお、発光素子R1、発光素子R2、発光素子G1、発光素子G2、発光素子B1、発光素子B2において、それぞれの発光効率は、各々の発光色を呈する発光素子ごとに発光効率が異なる。このため、所望の輝度の発光を得るために必要な電流は、発光効率の低い発光素子の方が相対的に多くなる。さらに、人間の眼では発光波長ごとに感度が異なり、一般に、赤や青の発光波長よりも緑の発光波長に対する感度が高い。従って、人間の眼に対し、緑と同等の感度となるように青や赤を発光させるためには、青や赤の輝度を緑の輝度よりも相対的に高くする必要がある。しかし、発光素子の輝度を高くするために発光素子に多くの電流を流すことは、発光素子の劣化を促進し、また表示装置の消費電力の増加を招く。また、発光素子の劣化に起因して発光波長がシフトすると、表示装置の色再現性が低下し画質が低下することもある。

## 【0186】

10

20

30

40

50

そのため、あらかじめ、発光素子R1、発光素子R2、発光素子G1、発光素子G2、発光素子B1、発光素子B2とで発光素子の面積の大きさを異ならせる構成としてもよい。例えば、発光素子R1、発光素子R2、発光素子B1、発光素子B2の面積を2倍にし、発光素子G1、発光素子G2の面積をそのままにする構成としてもよい。このような構成を取ることで、発光素子間の劣化のばらつきを平均化することもできるため、好適である。

#### 【0187】

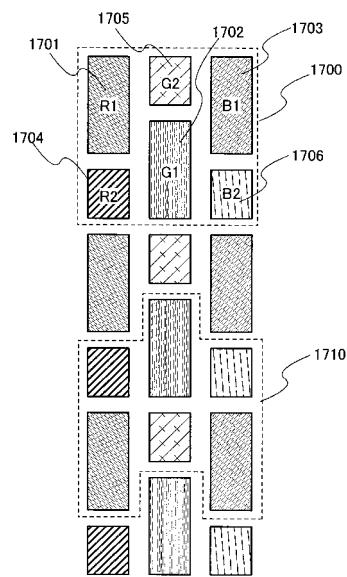

また図16に示した構成とは別に、図17に示す表示装置の画素の配置は絵素1700の中に、第1の画素1701、第2の画素1702、第3の画素1703、第4の画素1704、第5の画素1705、第6の画素1706を有し、第1の画素と第2の画素と第3の画素、第4の画素と第5の画素と第6の画素とがそれぞれデルタ配置して配置されている。

#### 【0188】

図17では第1の画素1701と第4の画素1704、第2の画素1702と第5の画素1705、第3の画素1703と第6の画素1706とで面積を異ならせる構成としたが、これに限定されない。第1の画素1701と第4の画素1704、第2の画素1702と第5の画素1705、第3の画素1703と第6の画素1706と同じ面積にしてもよいし、第1の画素1701～第6の画素1706で全て異なる面積を有する構成としてもよい。また、絵素の取り方においても特に限定されず、絵素1710で画像を形成する構成であってもよい。

#### 【0189】

また、例えば発光素子R1を具備する第1の画素1701と発光素子B1を具備する第3の画素1703が隣接するように配置されていても構わない。また各画素の形状についても、図17に示すような長方形に限らず、例えば正方形やその他の多角形あるいは曲率を有する形状であっても構わない。なお、第1の画素1701～第6の画素1706間の幅は、同じ間隔に配置してもよいし、異なる間隔に配置してもよい。

#### 【0190】

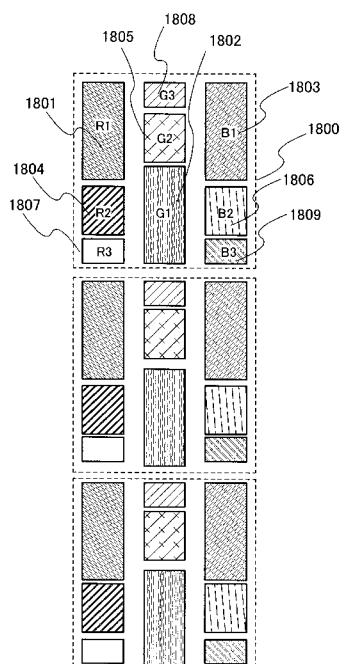

また、本発明の表示装置において、第1の画素～第6の画素に限らず、図18に示すように第1の画素1801、第2の画素1802、第3の画素1803、第4の画素1804、第5の画素1805、第6の画素1806、第7の画素1807、第8の画素1808、第9の画素1809とする構成としてもよい。なお、第7の画素1807は発光素子R3を具備し、第8の画素1808は発光素子G3を具備し、第9の画素1809は発光素子B3を具備する構成とする。

#### 【0191】

図18では第1の画素1801と第4の画素1804と第7の画素1807、第2の画素1802と第5の画素1805と第8の画素1808、第3の画素1803と第6の画素1806と第9の画素1809とで面積を異ならせる構成としたが、これに限定されない。第1の画素1801と第4の画素1804と第7の画素1807、第2の画素1802と第5の画素1805と第8の画素1808、第3の画素1803と第6の画素1806と第9の画素1809と同じ面積にしてもよいし、第1の画素1801～第9の画素1809で全て異なる面積を有する構成としてもよい。

#### 【0192】

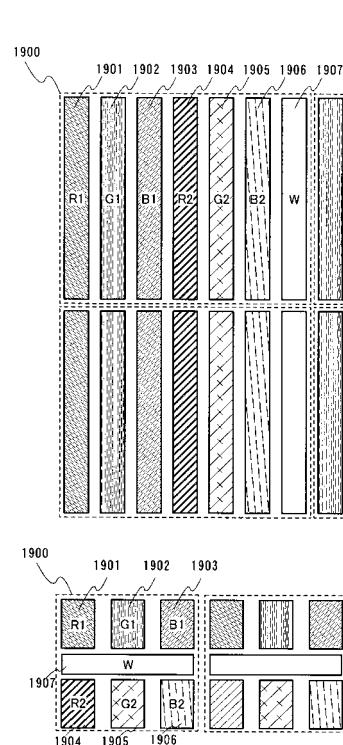

また、本発明の表示装置において、第1の画素～第6の画素に限らず、図19(A)に示すように第1の画素1901、第2の画素1902、第3の画素1903を並べて配置し、第4の画素1904、第5の画素1905、第6の画素1906、第7の画素1907とする構成としてもよい。なお、第7の画素は白色の発光素子Wを具備する構成とする。

#### 【0193】

なお、第7の画素の発光素子Wは、CIE-X Y色度図を表したときに、色度図のxが0.30以上、且つ0.40以下、yが0.30以上、且つ0.40以下の領域に座標を

10

20

30

40

50

有するものとする。また、より好ましくは、第7の画素の発光素子Wは、CIE-X Y色度図で表したときに、色度図のxが0.30以上、且つ0.35以下、yが0.30以上、且つ0.35以下の領域に座標を有するものとする。

【0194】

図19(A)では第1の画素1901と第4の画素1904、第2の画素1902と第5の画素1905、第3の画素1903と第6の画素1906とで面積を同じにする構成としたが、これに限定されない。第1の画素1901と第4の画素1904、第2の画素1902と第5の画素1905、第3の画素1903と第6の画素1906を異なる面積にしてもよいし、第1の画素1901～第6の画素1906で全て異なる面積を有する構成としてもよい。

10

【0195】

また図19(A)とは別の構成について図19(B)に示す。図19(A)との違いは、第1の画素1901、第2の画素1902、第3の画素1903、第4の画素1904、第5の画素1905、第6の画素1906、第7の画素1907の配置の違いである。勿論、各画素の配置についても特にこれに限定されない。また各画素の形状についても、図19に示すような長方形に限らず、例えば正方形やその他の多角形あるいは曲率を有する形状であっても構わない。

【0196】

なお、第7の画素に白色光を発光する発光素子Wを具備することによって、発光素子R1、発光素子R2、発光素子G1、発光素子G2、発光素子B1、発光素子B2の混色で白色を表示するのに対し、発光素子Wだけの発光で表示ができるため、消費電力を低減できるため好適である。また、中間色を表示する際に、白色を交えて加法混色することにより、より消費電力の低減が見込めるため好適である。

20

【0197】

なお、本発明の表示装置においては、絵素において、第7の画素に白色光を発光する発光素子W1を具備し、第8の画素に白色光を発光する発光素子W2を具備する構成としてもよい。上述の発光素子R1と発光素子R2、発光素子G1と発光素子G2、発光素子B1と発光素子B2と同様に、発光素子W1と発光素子W2とで発光スペクトルを異なる。その結果、より鮮やかな色彩を表示し、且つ消費電力が低減した表示装置を提供することが可能となる。

30

【0198】

なお、第7の画素の発光素子W1及び第8の画素の発光素子W2は、CIE-X Y色度図を表したときに、色度図のxが0.30以上、且つ0.40以下、yが0.30以上、且つ0.40以下の領域に座標を有するものとする。また、より好ましくは、第7の画素の発光素子W1及び第8の画素の発光素子W2は、CIE-X Y色度図で表したときに、色度図のxが0.30以上、且つ0.35以下、yが0.30以上、且つ0.35以下の領域に座標を有するものとする。

40

【0199】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【0200】

(実施の形態5)

本実施の形態においては、上記実施の形態で述べた画素の構成、動作方法が図4、図5に示したものとは別の構成について述べる。

【0201】

図4、図5に示す画素構成、動作方法によると、アドレス(書き込み)期間とサステイン(発光)期間とが完全に分離されているため、サステイン(発光)期間の長さを自由に設定出来るといったメリットがあるが、アドレス(書き込み)期間において、ある行で書き込みが行われている間、他の行では書き込みも発光も行われていない。つまり、全体としてデューティー比が低くなってしまう。

50

## 【0202】

そこで、アドレス（書き込み）期間とサステイン（発光）期間とを分離しない動作について説明する。

## 【0203】

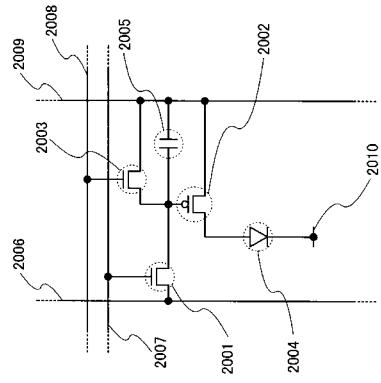

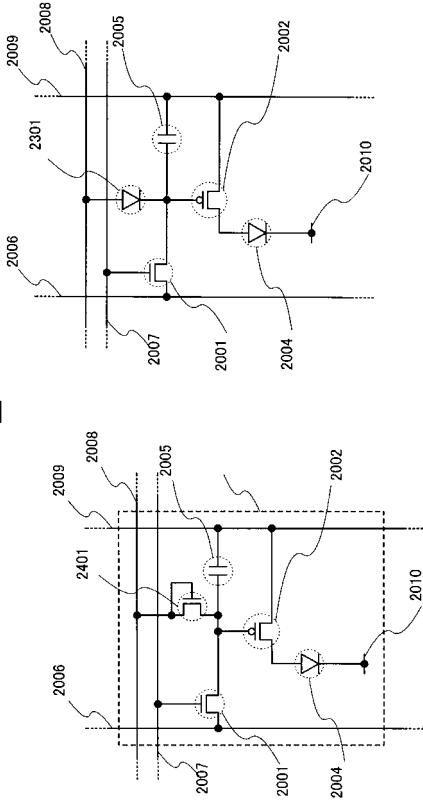

上記動作を達成するための画素構成を図20に示す。図20に示す画素構成は、映像信号の入力を制御するスイッチング用の第1のトランジスタ2001（スイッチングトランジスタともいう）、映像信号によって発光素子の発光・非発光を決定する駆動用の第2のトランジスタ2002（駆動トランジスタともいう）、第2のトランジスタのゲートとソースの間の電圧を消去するための第3のトランジスタ2003（消去トランジスタともいう）、発光素子2004、保持容量2005、信号線2006、第1の走査線2007、第2の走査線2008、電源線2009、及び対向電極2010を有している。保持容量2005は第1のトランジスタ2001及び第2のトランジスタ2002のゲートとソースの間の電圧（ゲート電圧）をより確実に保持するために設けられているが、必ずしも設ける必要はない。なお、本明細書において電圧とは、特に記載のない限りグラウンドとの電位差を意味する。また、発光素子2004は、図2におけるR1, R2, G1, G2, B1, B2の発光素子が対応する。

10

## 【0204】

第1の走査線2007を用いて、第1のトランジスタ2001を制御する。第1のトランジスタ2001がオンすると、信号線2006から、保持容量2005にビデオ信号が入力される。すると、ビデオ信号に応じて、第2のトランジスタ2002がオンオフし、電源線2009から発光素子2004を通って、対向電極2010へ電流が流れる。

20

## 【0205】

信号を消去したい場合は、第2の走査線2008を選択して、第3のトランジスタ2003をオン状態にして、第2のトランジスタ2002がオフ状態になるようにする。すると、電源線2009から発光素子2004を通って、対向電極2010へ電流が流れないようになる。その結果、非点灯期間を作ることができ、点灯期間の長さを自由に制御できるようになる。

20

## 【0206】

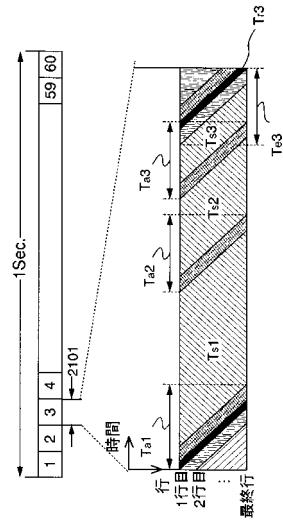

次に、画素の信号を消去する動作を行う場合のタイミングチャートを図21に示す。本実施の形態においては、例として、図5と同様にデジタル時間階調方式で3ビットデジタル映像信号を用いた場合を挙げて説明する。デジタル時間階調方式の場合、1フレーム期間2101を、さらに複数のサブフレーム期間に分割する。ここでは3ビットであるので、3つのサブフレーム期間に分割し、各期間で、各発光色における書き込み、表示を行う。

30

## 【0207】

図21において、各サブフレーム期間は、アドレス（書き込み）期間Ta#（#は自然数）と、サステイン（発光）期間Ts#を有する。図21中、1フレーム期間2101を分割した各サブフレーム期間において、アドレス（書き込み）期間とサステイン（発光）期間とが分離していない様子がわかる。つまり、i行目での書き込みが完了すると、i行目では直ちに発光が始まる。その後、i+1行目での書き込みが行われている時には、すでにi行目はサステイン（発光）期間に入っていることになる。このようなタイミングとすることにより、デューティー比を高くすることが出来る。

40

## 【0208】

ただし、図21のようなタイミングの場合、アドレス（書き込み）期間よりもサステイン（発光）期間が短くなると、あるサブフレーム期間におけるアドレス（書き込み）期間と、次のサブフレーム期間におけるアドレス（書き込み）期間とが重複する期間が生じてしまう。そこで、図20に示したように、第3のトランジスタを用いて、サステイン（発光）期間が終了する時点から、次のアドレス（書き込み）期間が開始されるまでの間、強制的に消去期間Tr3を設けている。この消去期間により、異なるサブフレーム期間におけるアドレス（書き込み）期間同士が重複するのを回避出来る。具体的には、第3のトランジ

50

ンジスタを制御するための、第2の走査線駆動回路を用い、消去用の選択パルスを出力して、1行目から順に、所望のタイミングで第3のトランジスタをONさせる。なお、この第2の走査線駆動回路は、通常の書き込みを行う第1の走査線駆動回路と同じ構成で良い。よって、消去用信号の書き込みを行う期間（以後、リセット期間と表記する）T<sub>e3</sub>は、アドレス（書き込み）期間と長さが等しい。

#### 【0209】

なお、ここでは階調表示ビット数とサブフレーム数が等しい場合を例としたが、さらに多くの期間に分割されていても良い。また、サステイン（発光）期間の長さの比も、必ずしも2のべき乗としなくても、階調表現は可能である。このように図20に示した画素構成を採用することにより、各行において、点灯期間の長さを容易に制御できるようになる。

10

#### 【0210】

図20のような画素構成を取ることで、信号の書き込み動作が遅くても、1フレーム内に複数のサブフレームを配置することが可能となる。また、消去動作を行う場合は、消去用のデータをビデオ信号と同様に取得する必要がないため、ソースドライバの駆動周波数も低減出来る。

#### 【0211】

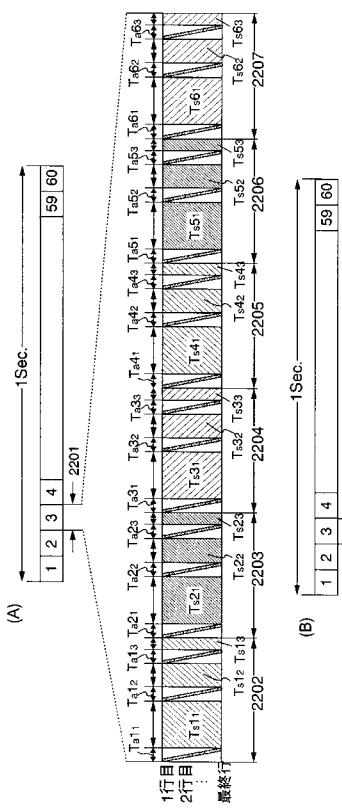

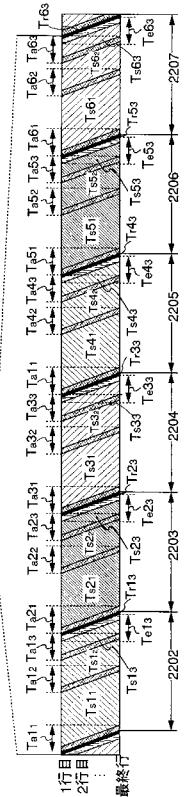

また、図4、図20の画素構成において、フィールドシーケンシャル方式を用いてもよい。図22(A)には、図4の画素構成において、2201で示される1フレーム期間を、2202～2207で示される6つの期間に分割し、各期間で、各発光色における書き込み、表示を行う。また、図22(B)には図20の画素構成において、2201で示される1フレーム期間を、2202～2207で示される6つの期間に分割し、各期間で、各発光色における書き込み、表示を行う。

20

#### 【0212】

なお、図22(A)(B)においては、例として3ビットデジタル映像信号を用いた場合を挙げて説明する。デジタル時間階調方式の場合、フレーム期間2201を、さらに複数のサブフレーム期間に分割する。ここでは3ビットであるので、3つのサブフレーム期間に分割している。

#### 【0213】

なお、図22(A)(B)においては、R1, R2, G1, G2, B1, B2の発光素子に対応する第1の期間2202、第2の期間2203、第3の期間2204、第4の期間2205、第5の期間2206、第6の期間2207で示される6つの期間のうち1つの期間、例えば第1の期間2202の期間について説明する。

30

#### 【0214】

なお、第1の期間2202においては、各サブフレーム期間で、アドレス（書き込み）期間T<sub>a1#</sub>（#は自然数）と、サステイン（発光）期間T<sub>s1#</sub>を有する。また、第2の期間については、アドレス（書き込み）期間T<sub>a2#</sub>（#は自然数）と、サステイン（発光）期間T<sub>s2#</sub>、とし、以下第3の期間～第6の期間も同様の表記をする。

#### 【0215】

図22(A)においては、サステイン（発光）期間の長さを、T<sub>s11</sub> : T<sub>s12</sub> : T<sub>s13</sub> = 4 : 2 : 1とし、各サステイン（発光）期間で、発光もしくは非発光を制御することにより、2<sup>3</sup> = 8階調を表現する。つまり、サステイン（発光）期間の長さを、T<sub>s11</sub> : T<sub>s12</sub> : T<sub>s13</sub> = 2<sup>(n-1)</sup> : 2<sup>(n-2)</sup> : ... : 2<sup>1</sup> : 2<sup>0</sup>というように、2のべき乗の比とする。例えば、T<sub>s13</sub>のみが発光し、T<sub>s11</sub>、T<sub>s12</sub>においては非発光である場合、すべてのサステイン（発光）期間のうち、約14%の期間だけ発光していることになる。すなわち、約14%の輝度が表現出来る。T<sub>s11</sub>とT<sub>s12</sub>が発光し、T<sub>s13</sub>が非発光である場合には、すべてのサステイン（発光）期間のうち、約86%の期間だけ発光していることになる。すなわち、約86%の輝度が表現出来る。

40

#### 【0216】

この動作を図21に示すように、第1～第6の発光色、つまり図2における発光素子R

50

1、発光素子R2、発光素子G1、発光素子G2、発光素子B1、発光素子B2において繰り返すことによって、視認者は残像効果によって多色表現を視認することができる。

【0217】

図20では、第3のトランジスタ2003を用いていたが、別 の方法を用いることも出来る。なぜなら、強制的に非点灯期間をつくればよいので、発光素子2004に電流が供給されないようにすればよいからである。よって、電源線2009から発光素子2004を通って、対向電極2010へ電流が流れる経路のいずれかに、スイッチを配置して、そのスイッチのオンオフを制御して、非点灯期間を作ればよい。あるいは、第2のトランジスタ2002のゲート・ソース間電圧を制御して、第2のトランジスタが強制的にオフになるようにすればよい。

10

【0218】

第2のトランジスタを強制的にオフにする場合の画素構成の例を図23に示す。図20と異なる点は、消去ダイオード2301が第2のトランジスタ2002のゲートと第2の走査線2008との間に接続されている。

【0219】

信号を消去したい場合は、第2の走査線2008を選択（ここでは、高い電位にする）して、消去ダイオード2301がオンして、第2の走査線2008から第2のトランジスタ2002のゲートへ電流が流れるようになる。その結果、第2のトランジスタ2002がオフ状態になる。すると、電源線2009から、発光素子2004を通って、対向電極2010には、電流が流れなくなるようになる。その結果、非点灯期間を作ることができ、点灯期間の長さを自由に制御できるようになる。

20

【0220】

信号を保持しておきたい場合は、第2の走査線2008を非選択（ここでは、低い電位にする）しておく。すると、消去ダイオード2301がオフするので、第2のトランジスタ2002のゲート電位は保持される。

【0221】

なお、消去ダイオード2301は、整流性がある素子であれば、なんでもよい。PN型ダイオードでもよいし、PIN型ダイオードでもよいし、ショットキー型ダイオードでもよいし、ツエナー型ダイオードでもよい。

30

【0222】

また、トランジスタを用いて、ダイオード接続（ゲートとドレインを接続）して、用いても良い。その場合の回路図を図24に示す。消去ダイオード2301として、ダイオード接続したトランジスタ2401を用いている。ここでは、Nチャネル型を用いているが、これに限定されない。Pチャネル型を用いても良い。

【0223】

なお、本実施の形態において示したタイミングチャートや画素構成や駆動方法は、一例であり、これに限定されない。様々なタイミングチャートや画素構成や駆動方法に適用することが可能である。

【0224】

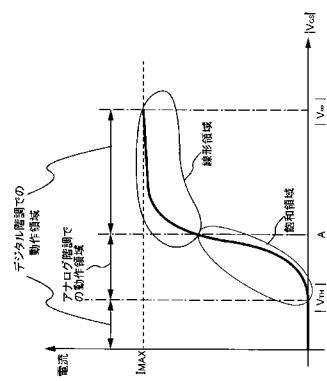

次に、デジタル階調法の場合における、駆動トランジスタの動作領域について述べる。なお図25はトランジスタの動作について、横軸にトランジスタのゲートとソース間にかかる電圧をとり、縦軸にトランジスタのソースとドレインを流れる電流をとった際の特性図である。

40

【0225】

例えば、飽和領域で動作させる場合は、発光素子の電圧電流特性が劣化しても、そこを流れる電流値が変化しない、という利点がある。そのため、表示装置は焼き付きの影響を受けにくい。ただし、駆動トランジスタの電流特性がばらつくと、そこを流れる電流もばらついてしまう。そのため、表示ムラを生じてしまう場合がある。

【0226】

それに対して、線形領域で動作させると、駆動トランジスタの電流特性がばらついても、

50

そこを流れる電流値は影響を受けにくい。そのため、表示ムラが生じにくい。また、駆動トランジスタのゲート・ソース間電圧（の絶対値）が大きくなりすぎないことにより、消費電力も小さくできる。

【0227】

さらに、駆動トランジスタのゲート・ソース間電圧（の絶対値）を大きくすると、駆動トランジスタの電流特性がばらついても、そこを流れる電流値は影響をほとんど受けなくなる。ただし、発光素子の電圧電流特性が劣化すると、そこを流れる電流値が変化してしまう場合がある。そのため、表示装置は焼き付きの影響を受けやすくなる。

【0228】

このように、駆動トランジスタを飽和領域で動作させると、発光素子の特性が変化しても、電流値が変化しない。よって、その場合、駆動トランジスタは、電流源として動作していると見なせる。したがって、このような駆動を定電流駆動と呼ぶことにする。

【0229】

また、駆動トランジスタを線形領域で動作させると、駆動トランジスタの電流特性がばらついても、電流値が変化しない。よって、その場合、駆動トランジスタは、スイッチとして動作していると見なせる。よって、発光素子には、電源線の電圧がそのまま加わっているように見なせる。したがって、このような駆動を定電圧駆動と呼ぶことにする。

【0230】

本発明は定電流駆動、定電圧駆動のいずれも採用することが可能である。したがって、定電流駆動、定電圧駆動のどちらを採用するかは、発光素子、トランジスタのばらつきを考慮して適宜変更すればよい。

【0231】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【0232】

（実施の形態6）

本実施の形態において、本発明における各画素と各配線のレイアウトの他の構成について説明する。

【0233】

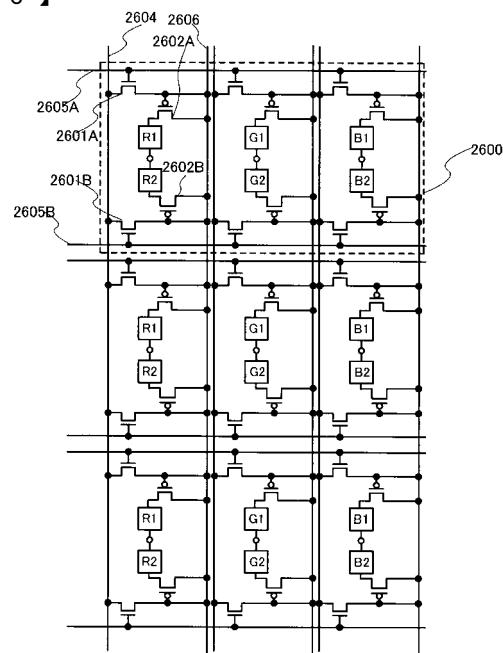

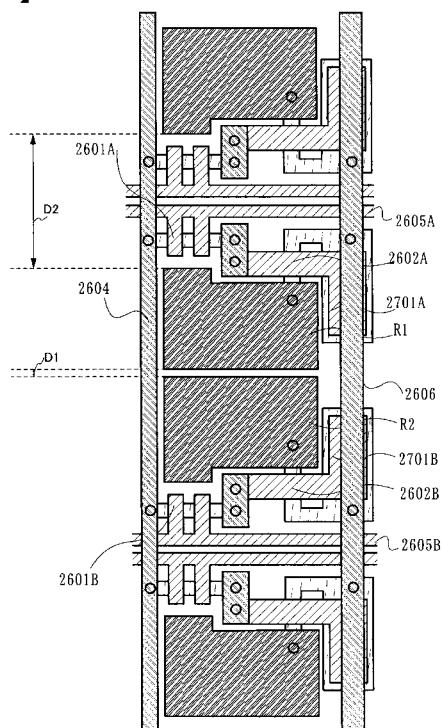

図4に示した回路図について、そのレイアウト図を図26に示す。なお、回路図やレイアウト図は、図4や図26に限定されない。

【0234】

スイッチングトランジスタ2601A、2601B、駆動トランジスタ2602A、2602B、発光素子R1、R2の電極が配置されている。スイッチングトランジスタ2601A、2601Bのソースとドレインは各々、信号線2604と、駆動トランジスタ2602Aか2602Bのゲートとに接続されている。スイッチングトランジスタ2601Aのゲートは、走査線2605Aに接続され、スイッチングトランジスタ2601Bのゲートは、走査線2605Bに接続されている。駆動トランジスタ2602A、2602Bのソースとドレインは各々、電源線2606と、発光素子R1、R2の電極とに接続されている。保持容量は（図示せず）、駆動トランジスタ2602Aか2602Bのゲートと、電源線2606との間に接続されているが、必ずしも設ける必要はない。

【0235】

なお、信号線2604は、駆動トランジスタ2602A、2602Bに対応して複数設ける構成であってもよい。

【0236】

信号線2604、電源線2606は、第2配線によって形成され、走査線2605A、2605Bは、第1配線によって形成されている。

【0237】

図27に図26に対応する画素構成の上面図について示す。図27の各構成に付される符号は、図26に準ずる。

10

20

30

40

50

## 【0238】

図27において、トップゲート構造の場合は、基板、半導体層、ゲート絶縁膜、第1配線、層間絶縁膜、第2配線、の順で膜が構成される。ボトムゲート構造の場合は、基板、第1配線、ゲート絶縁膜、半導体層、層間絶縁膜、第2配線、の順で膜が構成される。また、図27においては、保持容量2701A、2701Bが電源線と第1配線の間に設けられている。

## 【0239】

なお、スイッチングトランジスタ2601A、2601Bのチャネル形成領域が、各々2つ形成されるダブルゲート構造について説明したが、チャネル形成領域が一つ形成されるシングルゲート構造または三つ形成されるトリプルゲート構造であってもよい。あるいは、チャネル形成領域の上下にゲート絶縁膜を介して配置された2つのゲート電極を有するデュアルゲート型やその他の構造としてもよい。

10

## 【0240】

図27において、同じ絵素にある発光素子R1と発光素子R2の距離をD1とすると、発光素子R1と他の行の絵素にある発光素子R2との距離をD2とする。本実施の形態における図27の形態によると、D1 < D2とする構成となり、同じ絵素内にある発光素子R1と発光素子R2の距離を近くすることができる。本発明においては、図27のように列方向(図26における縦方向)に並べて配し、発光素子R1と発光素子R2との間に走査線を配しない構成とすることで発光素子R1と発光素子R2の色の混色がより視認したやすくなるため好適である。勿論発光素子G1と発光素子G2、発光素子B1と発光素子B2も同様の構成とすることで、色の混色が視認しやすくなりより好適である。また、発光素子R1と発光素子R2を行方向(図26における横方向)に並べて配する場合には、電源線を発光素子R1と発光素子R2の間に配しないことによって、発光素子R1と発光素子R2がより隣接した位置に配することとなり、好適である。

20

## 【0241】

図26の画素において、走査線2605Bを他の行の画素の走査線2605Aで代用することができる。つまり、その場合には、図26に示す表示装置の走査線2605Bを省略することができる。一例として、図26の画素の走査線2605Bを省略し、隣の行の画素の走査線2605Aで代用した場合の構成を図28に示す。

30

## 【0242】

図26、図28に示した表示装置の構成は一例であって本発明はこれに限定されない。例えば、電源線は信号線と平行に配置されていなくてもよく、走査線に平行に配置されていてもいいし、電源線のそれぞれが格子状に配置されていてもいい。つまり、図29に示すように、図26の画素における電源線を走査線と平行に配置してもよい。

## 【0243】

上述のように、本発明の表示装置の画素周辺における配線の構成は多岐にわたり、本明細書に列挙した構成に特に限定されないものであることを付記する。

35

## 【0244】

なお、本実施の形態は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。

40

## 【0245】

## (実施の形態7)

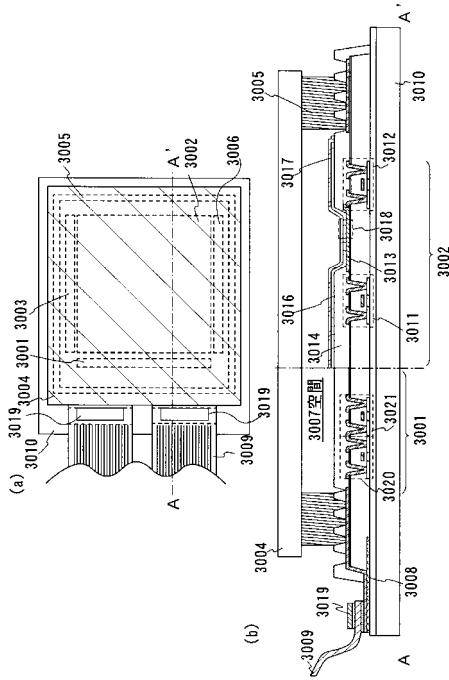

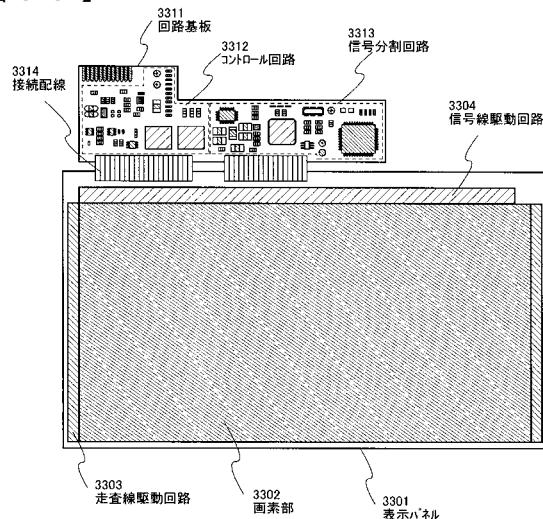

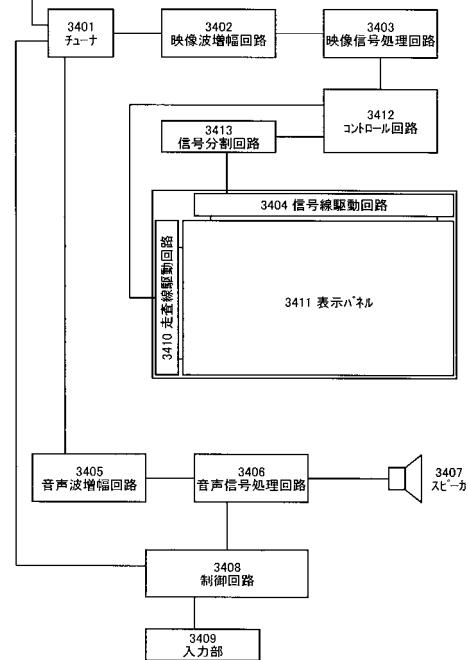

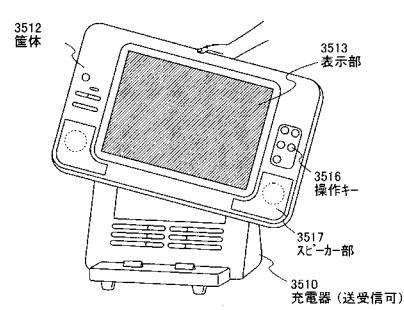

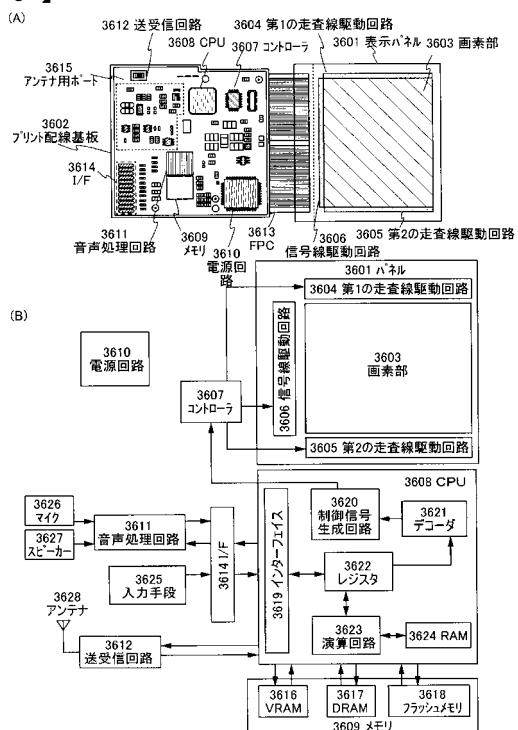

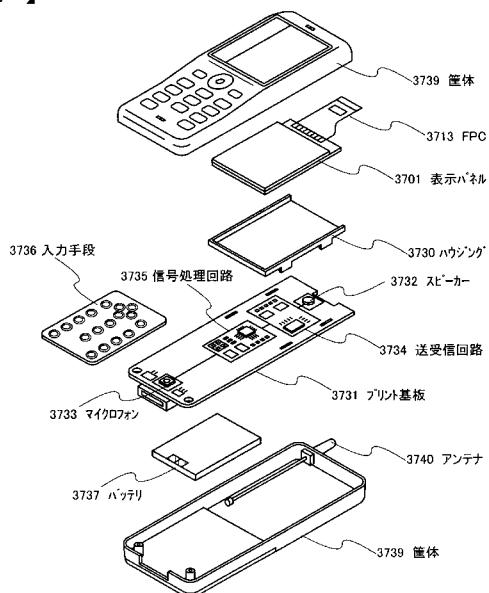

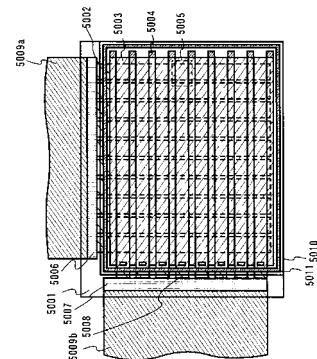

本実施の形態では、上記実施例で示した画素構成を有する表示パネルの構成について図30(a)、(b)を用いて説明する。

## 【0246】

なお、図30(a)は、表示パネルを示す上面図、図30(b)は図30(a)をA-A'で切断した断面図である。表示パネルは、点線で示された信号線駆動回路3001、画素部3002、第1の走査線駆動回路3003、第2の走査線駆動回路3006を有する。また、封止基板3004、シール材3005を有し、シール材3005で囲まれた内側は、空間3007になっている。

50

## 【0247】

なお、配線 3008 は第1の走査線駆動回路 3003、第2の走査線駆動回路 3006 及び信号線駆動回路 3001 に入力される信号を伝送するための配線であり、外部入力端子となる FPC 3009 (フレキシブルプリントサーキット) からビデオ信号、クロック信号、スタート信号等を受け取る。FPC 3009 と表示パネルとの接続部上には I C チップ 3019 (メモリ回路や、バッファ回路などが形成された半導体チップ) が COG (Chip On Glass) 等で実装されている。なお、ここでは FPC しか図示されていないが、この FPC にはプリント配線基盤 (PWB) が取り付けられていても良い。本明細書における表示装置とは、表示パネル本体だけでなく、それに FPC もしくは PWB が取り付けられた状態をも含むものとする。また、I C チップなどが実装されたものを含むものとする。

10

## 【0248】

次に、断面構造について図 30 (b) を用いて説明する。基板 3010 上には画素部 3002 とその周辺駆動回路 (第1の走査線駆動回路 3003、第2の走査線駆動回路 3006 及び信号線駆動回路 3001) が形成されているが、ここでは、信号線駆動回路 3001 と、画素部 3002 が示されている。

## 【0249】

なお、信号線駆動回路 3001 は N チャネル型 TFT 3020 や N チャネル型 TFT 3021 のように单極性のトランジスタで構成されている。なお、画素構成として单極性のトランジスタで画素を構成する場合には、周辺駆動回路を N チャネル型トランジスタで構成することにより单極性表示パネルを作製することができる。もちろん、单極性のトランジスタだけでなく P チャネル型トランジスタも用いて CMOS 回路を形成しても良い。また、本実施の形態では、同一基板上に画素部と周辺駆動回路を形成した表示パネルを示すが、必ずしもその必要はなく、周辺駆動回路の全部若しくは一部を I C チップなどに形成し、COG などで実装しても良い。その場合には駆動回路は单極性にする必要がなく P チャネル型トランジスタを組み合わせて用いることができる。

20

## 【0250】

また、画素部 3002 は TFT 3011 と、TFT 3012 とを有している。なお、TFT 3012 のソース電極は第1の電極 3013 (画素電極) と接続されている。また、第1の電極 3013 の端部を覆って絶縁物 3014 が形成されている。ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。

30

## 【0251】

また、カバレッジを良好なものとするため、絶縁物 3014 の上端部または下端部に曲率を有する曲面が形成されるようにする。例えば、絶縁物 3014 の材料としてポジ型の感光性アクリルを用いた場合、絶縁物 3014 の上端部のみに曲率半径 (0.2 μm ~ 3 μm) を有する曲面を持たせることが好ましい。また、絶縁物 3014 として、光によってエッチャントに不溶解性となるネガ型フォトレジスト、或いは光によってエッチャントに溶解性となるポジ型フォトレジストのいずれも使用することができる。

## 【0252】

第1の電極 3013 上には、発光層 3016、および第2の電極 3017 (対向電極) がそれぞれ形成されている。ここで、陽極として機能する第1の電極 3013 に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO (インジウムスズ酸化物) 膜、インジウム亜鉛酸化物 (IZO) 膜、窒化チタン膜、クロム膜、タンゲステン膜、Zn 膜、Pt 膜などの単層膜の他、窒化チタン膜とアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。

40

## 【0253】

また、発光層 3016 は、蒸着マスクを用いた蒸着法、またはインクジェット法によつて形成される。発光層 3016 には、元素周期表第4族金属錯体をその一部に用いること

50

とし、その他、組み合わせて用いることのできる材料としては、低分子系材料であっても高分子系材料であっても良い。また、発光層に用いる材料としては、通常、有機化合物を単層もしくは積層で用いる場合が多いが、本実施の形態においては、有機化合物からなる膜の一部に無機化合物を用いる構成も含めることとする。さらに、公知の三重項材料を用いることも可能である。

【0254】

さらに、発光層3016上に形成される第2の電極3017に用いる材料としては、仕事関数の小さい材料(A1、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム)を用いればよい。なお、発光層3016で生じた光が第2の電極3017を透過させる場合には、第2の電極3017(陰極)として、膜厚を薄くした金属薄膜と、透明導電膜(ITO(酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金(Indium<sub>2</sub>O<sub>3</sub> ZnO)、酸化亜鉛(ZnO)等)との積層を用いるのが良い。

【0255】

さらにシール材3005で封止基板3004を基板3010と貼り合わせることにより、基板3010、封止基板3004、およびシール材3005で囲まれた空間3007に発光素子3018が備えられた構造になっている。なお、空間3007には、不活性気体(窒素やアルゴン等)が充填される場合の他、シール材3005で充填される構成も含むものとする。

【0256】

なお、シール材3005にはエポキシ系樹脂を用いるのが好ましい。また、これらの材料はできるだけ水分や酸素を透過しない材料であることが望ましい。また、封止基板3004に用いる材料としてガラス基板や石英基板の他、FRP(Fiberglass-Reinforced Plastics)、PVF(ポリビニルフロライド)、マイラー、ポリエスチルまたはアクリル等からなるプラスチック基板を用いることができる。

【0257】

以上のようにして、本発明の画素構成を有する表示パネルを得ることができる。なお、上述した構成は一例であって本発明の表示パネルの構成はこれに限定されない。

【0258】

図30に示すように、信号線駆動回路3001、画素部3002、第1の走査線駆動回路3003及び第2の走査線駆動回路3006を同一基板上に形成することで、表示装置の低コスト化が図れる。また、この場合において、信号線駆動回路3001、画素部3002、第1の走査線駆動回路3003及び第2の走査線駆動回路3006に用いられるトランジスタを単極性とすることで作製工程の簡略化が図れるためさらなる低コスト化が図れる。

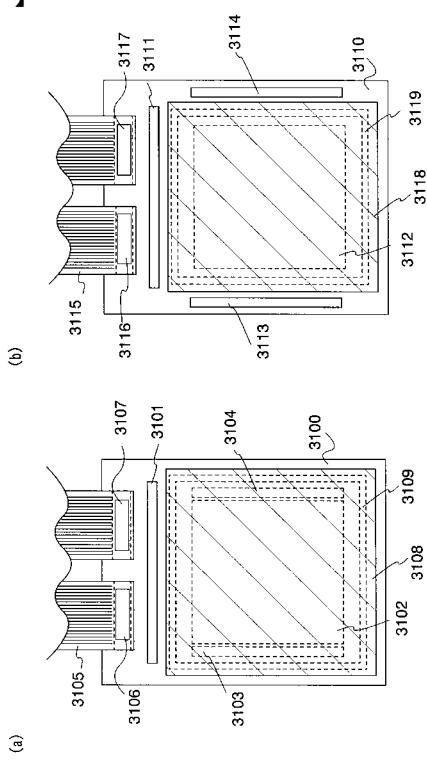

【0259】

なお、表示パネルの構成としては、図30(a)に示したように信号線駆動回路3001、画素部3002、第1の走査線駆動回路3003及び第2の走査線駆動回路3006を同一基板上に形成した構成に限らず、信号線駆動回路3001に相当する図31に示す信号線駆動回路3101をICチップ上に形成して、COG等で表示パネルに実装した構成としても良い。なお、図31(a)の基板3100、画素部3102、第1の走査線駆動回路3103、第2の走査線駆動回路3104、FPC3105、ICチップ3106、ICチップ3107、封止基板3108、シール材3109は図30(a)の基板3010、画素部3002、第1の走査線駆動回路3003、第2の走査線駆動回路3006、FPC3009、ICチップ3019、封止基板3004、シール材3005に相当する。

【0260】

つまり、高速動作が要求される信号線駆動回路のみを、CMOS等を用いてICチップに形成し、低消費電力化を図る。また、ICチップはシリコンウエハ等の半導体チップとすることで、より高速動作且つ低消費電力化を図れる。

10

20

30

40

50

## 【0261】

そして、第1の走査線駆動回路3103や第2の走査線駆動回路3104を画素部3102と同一の基板にすることで、低コスト化が図れる。そして、この第2の走査線駆動回路3103、第2の走査線駆動回路3104及び画素部3102は単極性のトランジスタで構成することでさらなる低コスト化が図れる。画素部3102の有する画素の構成としては実施の形態1、2、3及び4で示した画素を適用することができる。

## 【0262】

こうして、高精細な表示装置の低コスト化が図れる。また、FPC3105と基板3100との接続部において機能回路(メモリやバッファ)が形成されたICチップを実装することで基板面積を有効利用することができる。

10

## 【0263】

また、図30(a)の信号線駆動回路3001、第1の走査線駆動回路3003及び第2の走査線駆動回路3006に相当する図31(b)の信号線駆動回路3111、第1の走査線駆動回路3114及び第2の走査線駆動回路3113をICチップ上に形成して、COG等で表示パネルに実装した構成としても良い。この場合には高精細な表示装置をより低消費電力にすることが可能である。よって、より消費電力が少ない表示装置とするためには、画素部に用いられるトランジスタの半導体層にはポリシリコンを用いることが望ましい。なお、図31(b)の基板3110、画素部3112、FPC3115、ICチップ3116、ICチップ3117、封止基板3118、シール材3119は図30(a)の基板3010、画素部3002、FPC3009、ICチップ3019、封止基板3004、シール材3005に相当する。

20

## 【0264】

また、画素部3112のトランジスタの半導体層にアモルファスシリコンを用いることにより低コスト化を図ることができる。さらに、大型の表示パネルを作製することも可能となる。

## 【0265】

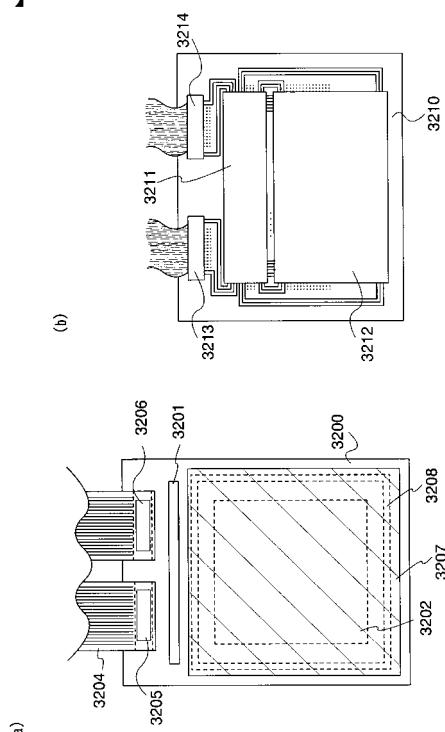

また、画素の行方向及び列方向に第2の走査線駆動回路、第1の走査線駆動回路及び信号線駆動回路を設けなくても良い。例えば、図32(a)に示すようにICチップ上に形成された周辺駆動回路3201が図31(b)に示す、第1の走査線駆動回路3114、第2の走査線駆動回路3113及び信号線駆動回路3111の機能を有するようにしても良い。なお、図32(a)の基板3200、画素部3202、FPC3204、ICチップ3205、ICチップ3206、封止基板3207、シール材3208は図30(a)の基板3010、画素部3002、FPC3009、ICチップ3019、封止基板3004、シール材3005に相当する。

30

## 【0266】

なお、図32(a)の表示装置の配線の接続を説明する模式図を図32(b)に示す。表示装置は、基板3210、周辺駆動回路3211、画素部3212、FPC3213、FPC3214を有する。FPC3213より周辺駆動回路3211に外部からの信号及び電源電位が入力される。そして、周辺駆動回路3211からの出力は、画素部3212の有する画素に接続された行方向及び列方向の配線に入力される。

40

## 【0267】

上述のように、本発明の表示装置における表示パネルの構成は多岐にわたり、本明細書に例挙した構成に特に限定されないものであることを付記する。

## 【0268】

なお、本実施の形態は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。

## 【0269】

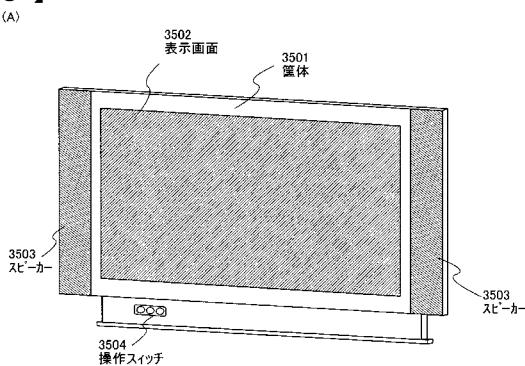

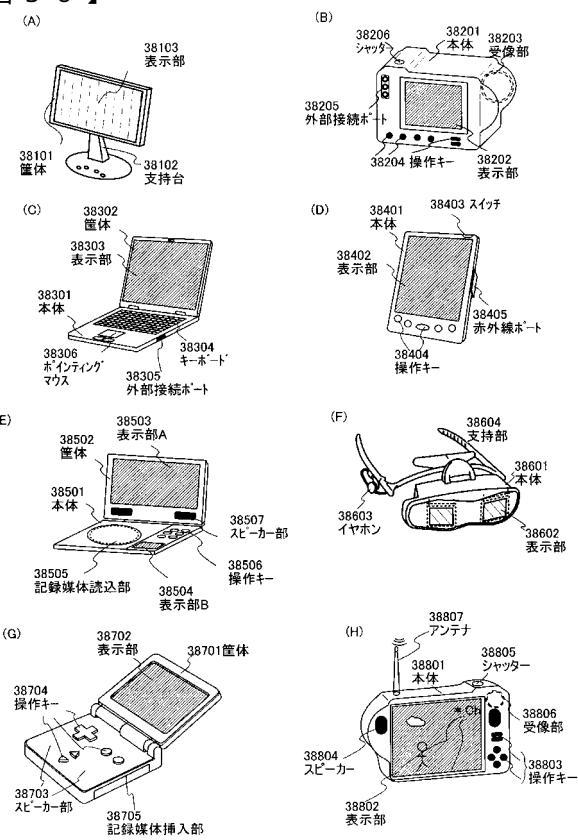

## (実施の形態8)

本実施の形態において、本発明における各画素とトランジスタの断面構造について、他の構成を説明する。

50

## 【0270】

図44に本実施の形態における回路図の一例を示す。なお、回路図は、図44に限定されない。図44に列挙した回路図は、N型のトランジスタを用いて構成された回路図である。N型のトランジスタで画素を構成する回路を構成することで、プロセスが簡易で、大面积の基板に対応することができる表示装置を提供することができる。以下、その具体例について述べる。

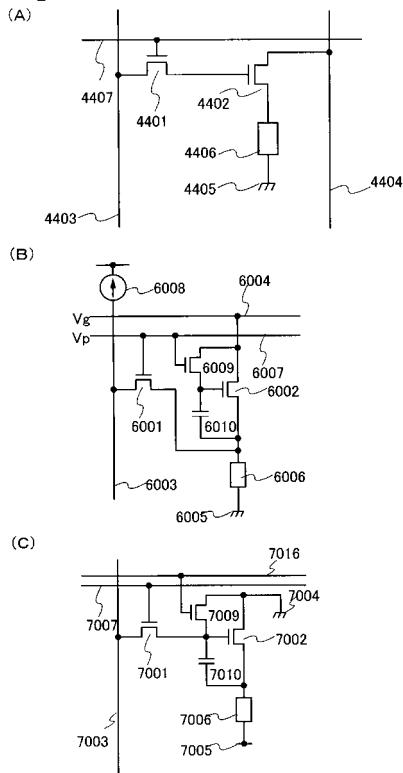

## 【0271】

図44(A)に、回路の構成を示す。画素には、第1のトランジスタ4401、第2のトランジスタ4402、発光素子4406が配置されており、ビデオ信号が入力される信号線4403と第2のトランジスタ4402のゲートとは、第1のトランジスタ4401を介して接続されている。第1のトランジスタ4401のゲートには、走査線4407が接続されている。第1電源供給線4404と第2電源供給線4405との間には、第2のトランジスタ4402と発光素子4406とが接続されている。そして、第1電源供給線4404から第2電源供給線4405の方に電流が流れる。発光素子4406は、そこを流れる電流の大きさに応じて発光する。

## 【0272】

なお、第2のトランジスタ4402のゲートに入力されるビデオ信号を保持するために、保持容量が配置されていてもよい。その場合、第2のトランジスタ4402のゲートと第2のトランジスタ4402のドレインとの間に、保持容量を配置してもよいし、第2のトランジスタ4402のゲートと第2のトランジスタ4402のソースとの間に、保持容量を配置してもよい。あるいは、第2のトランジスタ4402のゲートと別の配線(専用の配線や、前行の画素の走査線など)との間に、保持容量を配置してもよい。あるいは、第2のトランジスタ4402のゲート容量により、保持容量を配置しないことも可能である。なお、第2のトランジスタ4402や第1のトランジスタ4401は、Nチャネル型であるとする。

## 【0273】

また図44(B)に、本実施の形態の別の回路の構成を示す。画素には、第1のトランジスタ6001、第2のトランジスタ6002、第3のトランジスタ6009(保持トランジスタともいう)、保持容量6010、発光素子6006が配置されており、ビデオ信号が入力される信号線6003と第2のトランジスタ6002のソースとは、第1のトランジスタ6001を介して接続されている。第1のトランジスタ6001のゲートには、走査線6007が接続されている。第1電源供給線6004と第2電源供給線6005との間には、第2のトランジスタ6002と発光素子6006とが接続されている。そして、第1電源供給線6004から第2電源供給線6005の方に電流が流れる。発光素子6006は、そこを流れる電流の大きさに応じて発光する。第2のトランジスタ6002のゲート・ソース間には、保持容量6010が配置され、第2のトランジスタ6002のゲート・ドレイン間には、第3のトランジスタ6009が接続されている。第3のトランジスタ6009のゲートには、走査線6007が接続されている。

## 【0274】

信号線駆動回路には、電流源回路6008が配置されている。電流源回路6008は、ビデオ信号に応じた大きさの電流を画素へ供給する。そして、走査線6007が選択されて、ソース信号線6003に供給されたビデオ信号は、第2のトランジスタ6002に入力される。このとき、第1電源供給線6004の電位を変化させているため、第1電源供給線6004と第2電源供給線6005の電位の関係から、発光素子6006には電流が流れない。そして、ビデオ信号の大きさに応じて、必要な大きさの第2のトランジスタ6002のゲート・ソース間電圧が保持容量6010に保持される。その後、走査線6007が非選択状態になり、保持容量6010に蓄積された電荷は保持される。よって、第2のトランジスタ6002のドレイン電位やソース電位が変化しても、第2のトランジスタ6002のゲート・ソース間電圧は変化しない。そして、第1電源供給線6004の電位が元に戻り、第2のトランジスタ6002には、ビデオ信号に応じた大きさの電流が流れ

10

20

30

40

50

、発光素子 7006 にも流れしていく。

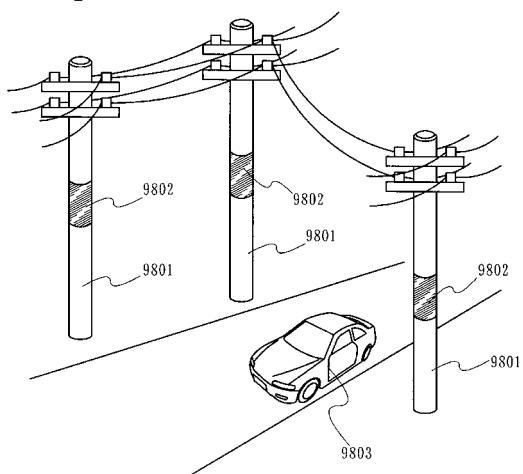

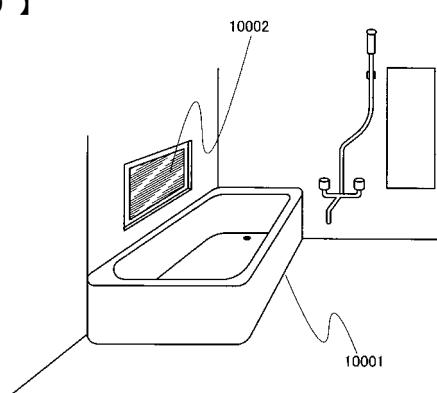

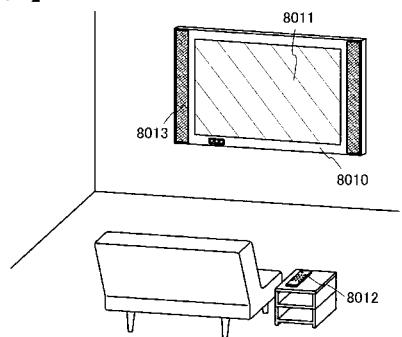

【0275】