(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

7 September 2007 (07.09.2007)

PCT

(10) International Publication Number

WO 2007/100404 A3(51) International Patent Classification:

*HO1L 23/48* (2006.01)

(74) Agents: KING, Robert, L. et al; 7700 W Parmer Lane, MD:PL02, Austin, Texas 78729 (US).

(21) International Application Number:

PCT/US2006/061737

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW

(22) International Filing Date:

7 December 2006 (07.12.2006)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/339,132 25 January 2006 (25.01.2006) US(71) Applicant (for all designated States except US):

**FREESCALE SEMICONDUCTOR INC.** [US/US];

6501 William Cannon Drive West, Austin, Texas 78735 (US).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(72) Inventor; and

Published:

(75) Inventor/Applicant (for US only): **CHATTERJEE, Ritwik** [US/US]; 8707 Bluegrass Drive, Austin, Texas 78759 (US).

— with international search report

(88) Date of publication of the international search report:

9 October 2008

(54) Title: SEMICONDUCTOR INTERCONNECT HAVING ADJACENT RESERVOIR FOR BONDING AND METHOD FOR FORMATION

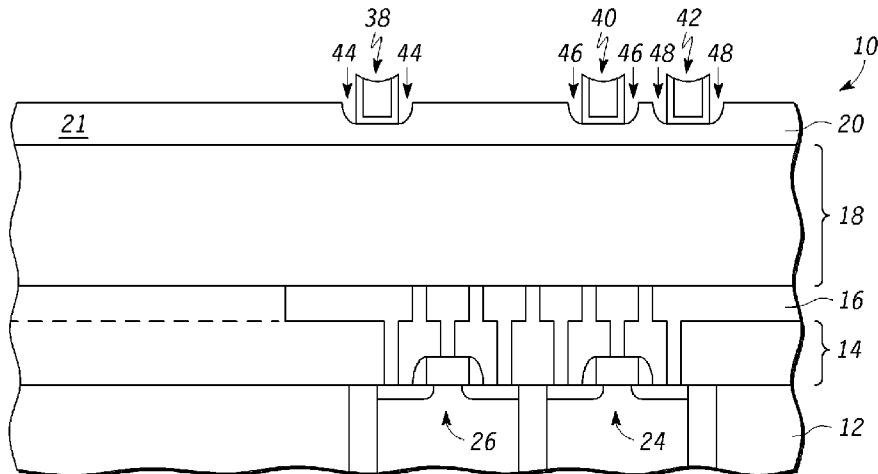

FIG.7

(57) **Abstract:** A semiconductor device (10) and method has interconnects (38, 40, 42) with adjoining reservoir openings (44, 46, 48). A dielectric layer (20) is formed as part of an uppermost of the one or more interconnect layers (18). Openings (30) formed in the dielectric layer result in modified portions (32) of the dielectric layer along portions of sidewalls of the openings. The openings are filled with a conductive material, such as metal. An exposed portion (22) of the dielectric layer (20) is removed to form protruding pads (38, 40, 42) of the conductive material extending above the dielectric layer. Reservoir openings are formed adjacent the protruding pads by removing the modified portions of the dielectric layer. When the semiconductor device is bonded with another device (100), either a wafer or a die, laterally flowing metal collects in the reservoir openings and ensures that a reliable electrical connection is made between the semiconductor device and the other device.

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/US 06/61737

**A. CLASSIFICATION OF SUBJECT MATTER**

IPC(8) - H01 L 23/48 (2008.04)

**USPC - 257/734**

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

USPC - 257/734, 438/667; 438/455; 438/599; 438/675;

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

USPC - 257/734, 438/667; 438/455; 438/599; 438/675;

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

**PubWEST (USPT, PGPB, EPAB, JPAT); DialogPRO (Engineering); Google Scholar**

Search term: **semiconductor device, integrated circuit, IC, device, component, Interconnect\$3 layer, interlevel layer, dielectric layer, pad, opening**

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category*    | Citation of document, with indication, where appropriate, of the relevant passages                       | Relevant to claim No.                       |

|--------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------|

| X<br>--<br>Y | <b>US 6,887,769 B2 (KELLAR et al.) 03 May 2005 (03.05.2005), fig 2-3, col 4 In 24-26, col 5 In 25-29</b> | 1-4,7-10,12,15-20<br>-----<br>5-6, 11,13-14 |

| Y            | <b>US 5,817,572 A (CHIANG et al.) 06 October 1998 (06.10.1998), fig 20, col 17 In 19-30, In 52-68</b>    | 5-6, 11, 14                                 |

| Y            | <b>US 2002/0160596 A1 (WEINRICH et al.) 31 October 2002 (31.10.2002), para [0044]</b>                    | 6                                           |

| Y            | <b>US 6,232,219 B1 (BLALOCK et al.) 15 May 2001 (15.05.2001), abstract</b>                               | 13                                          |

**D** Further documents are listed in the continuation of Box C.

\* Special categories of cited documents:

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier application or patent but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"F" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

|                                                                                                                                                                                 |                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Date of the actual completion of the international search<br><br>08 July 2008 (08.07.2008)                                                                                      | Date of mailing of the international search report<br><br><b>17 JUL 2008</b>                         |

| Name and mailing address of the ISA/US<br>Mail Stop PCT, Attn: ISA/US, Commissioner for Patents<br>P.O. Box 1450, Alexandria, Virginia 22313-1450<br>Facsimile No. 571-273-3201 | Authorized officer:<br><br><b>Lee W. Young</b><br>PCT Halpdøsk: 571-272-4300<br>PCTOSP: 571-272-7774 |