INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |                                                                                                                                                                                            |                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| (51) International Patent Classification <sup>7</sup> :<br><br>G11C 11/15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  | A1                                                                                                                                                                                         | (11) International Publication Number: WO 00/04552<br><br>(43) International Publication Date: 27 January 2000 (27.01.00) |

| (21) International Application Number: PCT/US99/16314<br><br>(22) International Filing Date: 19 July 1999 (19.07.99)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  | (81) Designated States: JP, KP, SG, European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).                                                              |                                                                                                                           |

| (30) Priority Data:<br>09/118,979 20 July 1998 (20.07.98) US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  | Published<br><i>With international search report.<br/>Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.</i> |                                                                                                                           |

| (71) Applicant: MOTOROLA, INC. [US/US]; 1303 East Algonquin Road, Schaumburg, IL 60196 (US).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |                                                                                                                                                                                            |                                                                                                                           |

| (72) Inventors: CHEN, Eugene; 1143 West Sherri Drive, Gilbert, AZ 85233 (US). TEHRANI, Saeid, N.; 1917 E. Palomino Drive, Tempe, AZ 85284 (US).                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |                                                                                                                                                                                            |                                                                                                                           |

| (74) Agents: INGRASSIA, Vincent, B. et al.; Motorola, Inc., Intellectual Property Dept., P.O. Box 10219, Scottsdale, AZ 85271-0219 (US).                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |                                                                                                                                                                                            |                                                                                                                           |

| (54) Title: LOW SWITCHING FIELD MAGNETIC TUNNELING JUNCTION USABLE FOR MULTI-STATE MAGNETIC MEMORY CELL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |                                                                                                                                                                                            |                                                                                                                           |

| (57) Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |                                                                                                                                                                                            |                                                                                                                           |

| <p>A low switching field magnetic tunneling junction memory cell including an antiferromagnetically coupled structure having first and second magnetoresistive layers of different thicknesses and a non-magnetic conducting layer sandwiched therebetween so that the magnetic vectors of the pair of layers are anti-parallel with no applied magnetic field, a magnetoresistive structure having a magnetic vector, and electrically insulating material sandwiched between the antiferromagnetically coupled structure and the magnetoresistive structure to form a magnetic tunneling junction.</p> |  |                                                                                                                                                                                            |                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |                                                                                                                                                                                            |                                                                                                                           |

***FOR THE PURPOSES OF INFORMATION ONLY***

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

|           |                          |           |                                       |           |                                           |           |                          |

|-----------|--------------------------|-----------|---------------------------------------|-----------|-------------------------------------------|-----------|--------------------------|

| <b>AL</b> | Albania                  | <b>ES</b> | Spain                                 | <b>LS</b> | Lesotho                                   | <b>SI</b> | Slovenia                 |

| <b>AM</b> | Armenia                  | <b>FI</b> | Finland                               | <b>LT</b> | Lithuania                                 | <b>SK</b> | Slovakia                 |

| <b>AT</b> | Austria                  | <b>FR</b> | France                                | <b>LU</b> | Luxembourg                                | <b>SN</b> | Senegal                  |

| <b>AU</b> | Australia                | <b>GA</b> | Gabon                                 | <b>LV</b> | Latvia                                    | <b>SZ</b> | Swaziland                |

| <b>AZ</b> | Azerbaijan               | <b>GB</b> | United Kingdom                        | <b>MC</b> | Monaco                                    | <b>TD</b> | Chad                     |

| <b>BA</b> | Bosnia and Herzegovina   | <b>GE</b> | Georgia                               | <b>MD</b> | Republic of Moldova                       | <b>TG</b> | Togo                     |

| <b>BB</b> | Barbados                 | <b>GH</b> | Ghana                                 | <b>MG</b> | Madagascar                                | <b>TJ</b> | Tajikistan               |

| <b>BE</b> | Belgium                  | <b>GN</b> | Guinea                                | <b>MK</b> | The former Yugoslav Republic of Macedonia | <b>TM</b> | Turkmenistan             |

| <b>BF</b> | Burkina Faso             | <b>GR</b> | Greece                                | <b>ML</b> | Mali                                      | <b>TR</b> | Turkey                   |

| <b>BG</b> | Bulgaria                 | <b>HU</b> | Hungary                               | <b>MN</b> | Mongolia                                  | <b>TT</b> | Trinidad and Tobago      |

| <b>BJ</b> | Benin                    | <b>IE</b> | Ireland                               | <b>MR</b> | Mauritania                                | <b>UA</b> | Ukraine                  |

| <b>BR</b> | Brazil                   | <b>IL</b> | Israel                                | <b>MW</b> | Malawi                                    | <b>UG</b> | Uganda                   |

| <b>BY</b> | Belarus                  | <b>IS</b> | Iceland                               | <b>MX</b> | Mexico                                    | <b>US</b> | United States of America |

| <b>CA</b> | Canada                   | <b>IT</b> | Italy                                 | <b>NE</b> | Niger                                     | <b>UZ</b> | Uzbekistan               |

| <b>CF</b> | Central African Republic | <b>JP</b> | Japan                                 | <b>NL</b> | Netherlands                               | <b>VN</b> | Viet Nam                 |

| <b>CG</b> | Congo                    | <b>KE</b> | Kenya                                 | <b>NO</b> | Norway                                    | <b>YU</b> | Yugoslavia               |

| <b>CH</b> | Switzerland              | <b>KG</b> | Kyrgyzstan                            | <b>NZ</b> | New Zealand                               | <b>ZW</b> | Zimbabwe                 |

| <b>CI</b> | Côte d'Ivoire            | <b>KP</b> | Democratic People's Republic of Korea | <b>PL</b> | Poland                                    |           |                          |

| <b>CM</b> | Cameroon                 | <b>KR</b> | Republic of Korea                     | <b>PT</b> | Portugal                                  |           |                          |

| <b>CN</b> | China                    | <b>KZ</b> | Kazakhstan                            | <b>RO</b> | Romania                                   |           |                          |

| <b>CU</b> | Cuba                     | <b>LC</b> | Saint Lucia                           | <b>RU</b> | Russian Federation                        |           |                          |

| <b>CZ</b> | Czech Republic           | <b>LI</b> | Liechtenstein                         | <b>SD</b> | Sudan                                     |           |                          |

| <b>DE</b> | Germany                  | <b>LK</b> | Sri Lanka                             | <b>SE</b> | Sweden                                    |           |                          |

| <b>DK</b> | Denmark                  | <b>LR</b> | Liberia                               | <b>SG</b> | Singapore                                 |           |                          |

| <b>EE</b> | Estonia                  |           |                                       |           |                                           |           |                          |

## LOW SWITCHING FIELD MAGNETIC TUNNELING JUNCTION USABLE FOR MULTI-STATE MAGNETIC MEMORY CELL

Field of the Invention

5        The present invention pertains to magnetic tunneling junctions for memory cells and more specifically to very small magnetic junctions for very high density arrays of memory cells.

10

Background of the Invention

A magnetic random access memory (MRAM) is a non-volatile memory which basically includes a giant magnetoresistive (GMR) material or magnetic tunneling junction (MTJ) structure, a sense line, and a word line. The MRAM employs the magnetic vectors to store memory states. Magnetic vectors in one or all of the layers of GMR material or MTJ are switched very quickly from one direction to an opposite direction when a magnetic field is applied to the magnetic material over a certain threshold or intensity. According to the direction of the magnetic vectors in the GMR material or MTJ, states are stored, for example, one direction can be defined as a logic "0", and another direction can be defined as a logic "1". The GMR material or MTJ maintains these states even without a magnetic field being applied. The states stored in the GMR material or MTJ can be read by passing a sense

stored, for example, one direction can be defined as a logic "0", and another direction can be defined as a logic "1". The GMR material or MTJ maintains these states even without a magnetic field being applied. The states stored 5 in the GMR material or MTJ can be read by passing a sense current through the cell in a sense line because of the difference between the resistances of the two states.

In very high density arrays of magnetic memory cells the size of individual cells becomes very small if the 10 array is constructed small enough to be useful in present day electronic devices. As the size of individual cells becomes smaller the aspect ratio (length/width ratio) generally becomes smaller. In two layer magnetic memory cells, e.g. standard tunneling cells, as the aspect ratio 15 goes below 5, magnetic vectors in the cells are antiparallel in non-energized (zero magnetic field) conditions. In a copending application entitled "Multi-Layer Magnetic Memory Cells with Improved Switching Characteristics", serial number 08/723,159, filed on 25 20 September 1996, and assigned to the same assignee, methods of reading cells with antiparallel magnetic vectors are disclosed. Also, in a copending application entitled "Magnetic Device Having Multi-Layers with Insulating and Conductive Layers", serial number 08/834,968, filed on 7 25 April 1997, and assigned to the same assignees, a dummy magnetic layer is added to a two magnetic layer stack and coupled to one of the two magnetic layers so that the other magnetic layer is a free layer. A drawback of the

dummy magnetic layer approach is that it relies on cancellation of magnetostatic interaction between the two magnetic layers and this magnetostatic interaction strength depends on the geometry of the cell and the 5 interlayer spacing. These parameters change as the critical dimension shrinks.

Also, in two layer magnetic memory cells, e.g. standard tunneling cells, as the aspect ratio goes below 5, the amount of magnetic field required for switching 10 states of the cell increases dramatically. Generally, as the cells are made smaller the layers of the cells are made thinner to reduce the amount of magnetic field required for switching states of the cell, since the magnetic moment (determined by the material) times the 15 thickness of the layer determines the required switching field. Softer magnetic material can also be used to reduce the magnetic moment but the reduction in switching field is limited for ultra small memory cells. Also, as the cells are made smaller they become unstable because, 20 for example, when the size of the memory cell is 10 nm or less, the energy barrier of the magnetization, which is proportional to the cell volume, is decreased due to the decreased volume and is close to the thermal fluctuation energy, which is  $KT$ .

25 Accordingly, it is highly desirable to provide magnetic random access memories and memory cells which are capable of being written (stored states switched) with

less magnetic field and which have a volume sufficient to not be effected by the thermal fluctuation energy.

It is another purpose of the present invention to provide a new and improved multi-state, multi-layer 5 magnetic memory cell with ferromagnetically coupled magnetic layers designed to reduce the required switching field.

It is still another purpose of the present invention to provide a new and improved multi-state, multi-layer 10 magnetic memory cell with ferromagnetically coupled magnetic layers which can be fabricated very small and with an aspect ratio less than 5.

It is a still further purpose of the present invention to provide a new and improved multi-state, 15 multi-layer magnetic memory cell with an increased energy barrier of magnetization.

#### Summary of the Invention

20

The above problems and others are at least partially solved and the above purposes and others are realized in a low switching field magnetoresistive tunneling junction memory cell including a antiferromagnetically coupled 25 multi-layer structure having first and second magnetoresistive layers with a non-magnetic conducting layer situated in parallel juxtaposition between the pair of magnetoresistive layers. The pair of magnetoresistive

layers in the antiferromagnetically coupled multi-layer structure are constructed to switch at different magnetic fields, by having different thicknesses or different magnetic material. Also, the pair of magnetoresistive 5 layers in the antiferromagnetically coupled multi-layer structure each have a magnetic vector which are anti-parallel with no applied magnetic field due to the antiferromagnetic coupling of the pair of layers and the aspect ratio. The cell further includes a 10 magnetoresistive structure having a magnetic vector with a fixed relationship to the vector of the second magnetoresistive layer. Electrically insulating material is situated in parallel juxtaposition between the antiferromagnetic coupled multi-layer structure and the 15 magnetoresistive structure to form a magnetic tunneling junction.

Basically, the magnetic field required to switch states in the cell is dictated by the difference between the two magnetoresistive layers in the 20 antiferromagnetically coupled multi-layer structure. Also, each of the first and second structures have, or can be constructed to have, little net magnetic moment and, hence, the memory cell has little net magnetic moment so that it can be positioned closer to adjacent cells without 25 affecting adjacent cells.

Referring to the drawings:

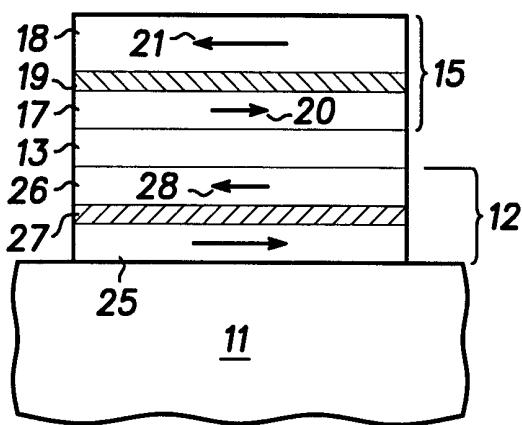

FIG. 1 is a simplified side view of a low switching field magnetic tunneling junction memory cell in accordance with the present invention;

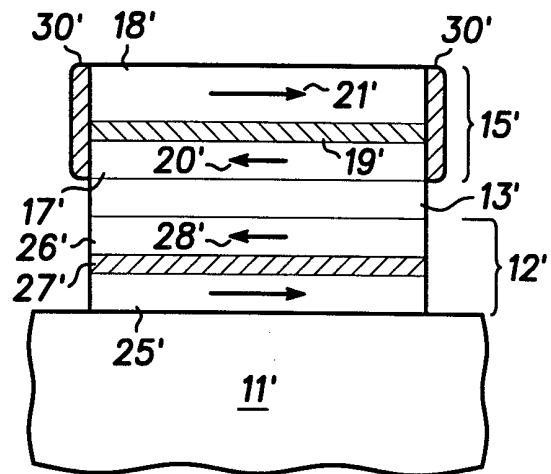

FIG. 2 is a view similar to FIG. 1 illustrating a different mode and a modification;

FIG. 3 through FIG. 9 illustrate steps in switching the low switching field magnetic tunneling junction memory cell from the mode of FIG. 1 to the mode of FIG. 2; and

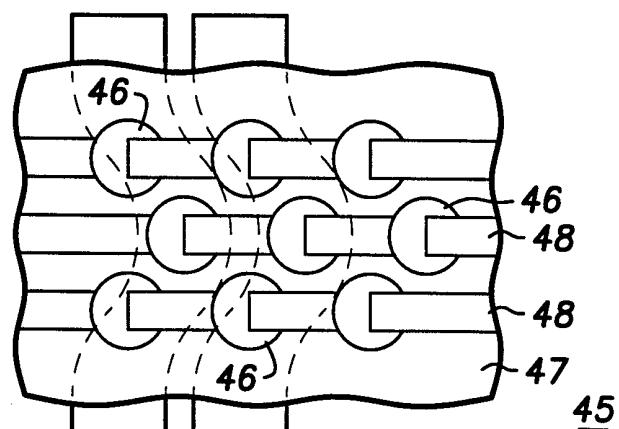

FIG. 10 is a simplified view in top plan of an array of low switching field magnetic tunneling junction memory cell in accordance with the present invention.

15

Description of the Preferred Embodiment

Turning now to the drawings, FIG. 1 illustrates an enlarged, simplified side view of a low switching field magnetic tunneling junction memory cell 10 in accordance with the present invention. Magnetic tunneling junction 10 is generally formed on a supporting substrate 11 and includes a magnetoresistive structure 12 supported on substrate 11, an electrically insulating material layer 13 positioned on structure 12, and a magnetoresistive structure 15 positioned on electrically insulating material layer 13 so as to sandwich layer 13 between

magnetoresistive structures 12 and 15 and form a tunneling junction.

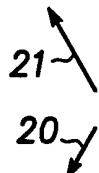

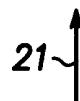

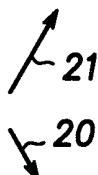

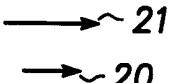

Magnetoresistive structure 15 is comprised of an antiferromagnetically coupled multi-layer structure 5 including magnetoresistive layers 17 and 18 having a non-magnetic conducting layer 19 situated in parallel juxtaposition between magnetoresistive layers 17 and 18. Magnetoresistive layer 17 has a magnetic vector 20 lying along a preferred magnetic axis parallel to the planar 10 surface of substrate 11 and magnetoresistive layer 18 has a magnetic vector 21. Magnetic vectors 20 and 21 are anti-parallel with no magnetic field applied to magnetic tunneling junction 10, due to the antiferromagnetic coupling between magnetoresistive layers 17 and 18 and/or 15 an aspect ratio less than approximately 5. Generally, in cells having a length/width ratio of less than approximately 4 the layers of magnetic material (Layers 17 and 18 in FIG. 1) are antiferromagnetically coupled. Generally, for purposes of this disclosure the term 20 "antiferromagnetically coupled" means that either of the antiparallel states (illustrated in FIGS. 1 and 2) is stable and that the parallel state is unstable and does require a constant magnetic field, since the magnetic vectors always tend to move to an antiparallel state 25 (pointing in opposite directions). Depending upon the construction, shape and size of magnetoresistive structure 15, vectors 20 and 21 can be constrained to lie along the

preferred magnetic axis by either shape or magnetic crystalline anisotropy.

In the case of circularly shaped cells, for example, the preferred magnetization direction can be determined by 5 uniaxial crystal field anisotropy (or magnetic crystalline anisotropy). This preferred magnetization direction is set during film deposition by a bias field or by annealing the film after deposition in a high magnetic field (e.g. several kOe) at elevated temperatures (e.g. 200°C to 10 300°C). In the case of a square or diamond shape, the uniaxial crystal anisotropy can be set along a diagonal direction of the square. In the case of an elliptically or rectangularly shaped cell, the uniaxial crystal anisotropy can be set along the long axis of the cell. A 15 preferred feature here is to minimize the shape effect, which contributes to the rise in required switching fields at narrow cell widths, and to utilize magneto-crystalline anisotropy to set the preferred magnetization direction needed by a memory cell.

20 Also, magnetoresistive layer 17 is constructed to switch direction of magnetic vector 20 at a different magnetic field intensity than the switching of magnetic vector 21 of magnetoresistive layer 18. This feature can be accomplished in several different ways, including by 25 forming layer 17 thinner (with less material) than layer 18, as shown in FIG. 1, by forming layer 17 with different magnetization (e.g. forming layer 17 of softer magnetic

material than layer 18), or some combination of the size and magnetization.

Magnetoresistive layers 17 and 18 each can be single layers of ferromagnetic materials such as a layer of 5 nickel, iron, cobalt, or alloys thereof including alloys having palladium or platinum therein. Alternatively, either of layers 17 and 18 can be a composite ferromagnetic layer, such as a layer of nickel-iron-cobalt covering a layer of cobalt-iron or three layer structures 10 including layers of cobalt-iron and nickel-iron-cobalt and cobalt-iron with cobalt-iron at the interface with adjacent layers. Materials that are suitable for non-magnetic conducting layer 19 include most electrically conductive materials such as copper and the like.

15 Magnetoresistive structure 12, including at least one magnetoresistive layer having a magnetic vector parallel to the preferred magnetic axis, is positioned on substrate 11 with electrically insulating material layer 13 situated in parallel juxtaposition between structures 12 and 15 to 20 form magnetic tunneling junction 10. In FIG. 1, magnetoresistive structure 12 is illustrated as similar to structure 15 and includes magnetoresistive layers 25 and 26 separated by a non-magnetic conducting layer 27. Here it should be noted that only layers 17 and 26, adjacent to 25 electrically insulating material layer 13, contribute to the magnetoresistance or mode changes of magnetic tunneling junction 10. Magnetoresistive layer 26 has a magnetic vector 28 which, generally, in the operation of

magnetic tunneling junction 10, is fixed in one direction along the preferred magnetic axis. Thus, magnetoresistive structure 12 can have substantially any configuration that includes a magnetoresistive layer with a fixed magnetic vector adjacent electrically insulating material layer 13 to produce a magnetic tunneling junction and which, preferably has a substantially zero magnetic moment to produce a minimum effect on adjacent cells.

In a tunneling junction type of magnetic cell, layer 13 is a barrier or tunneling layer, the provision of which between antiferromagnetic layers 17 and 26 produces a tunneling junction that allows a flow of current perpendicularly through layer 13, from layer 17 to layer 26 (or vice versa). Essentially, magnetic tunneling junction 10 appears as a relatively high impedance (referred to herein as a resistance R), which has dependence on the square area of the cell and the dielectric structure, generally several thousand ohms, e.g. 10 to 1000 kohms. When the magnetization vectors in layers 17 and 26 are antiparallel, as illustrated in FIG. 1, the resistance R of magnetic tunneling junction 10 remains very high. When the magnetization vectors in layers 17 and 26 are parallel, as illustrated in FIG. 2, the resistance R of magnetoresistive tunneling junction 10 drops perceptibly.

In a specific example, layer 17 is formed of cobalt (Co) approximately 50 Å thick, layer 13 is formed of aluminum oxide ( $Al_2O_3$ ) approximately 15 Å thick, and layer

26 is formed of nickel iron (NiFe) approximately 50 Å thick. Layer 18, which in this example is thicker than layer 17, is approximately 60 Å thick and layer 25, if present, has a similar thickness. The state of magnetic 5 tunneling junction 10 is relatively easily sensed by passing a sense current therethrough from layer 18 to layer 25 (or vice versa). The change of resistance in magnetic tunneling junction 10 is easily read as a change in voltage drop across magnetic tunneling junction 10 10 which can conveniently be used in conjunction with memory arrays and the like.

Referring specifically to FIG. 2, a structure similar to that of FIG. 1 is illustrated in a different mode, and a slightly different embodiment is illustrated with 15 similar components being designated with similar numbers having a prime added to indicate the different embodiment. In this embodiment, the antiparallel coupling between layers 17' and 18' of structure 15' is reinforced by the addition of flux closure material 30' positioned to 20 enclose exposed edges of layers 17', 18' and 19'. Flux closure material 30' is any soft magnetic material which encloses flux lines, or completes a magnetic circuit, between the various layers. Soft magnetic material 30' simply guides magnetic field lines from layers 17' and 25 18', respectively, into a closed loop to further reduce the end magnetic poles and greatly reduce stray magnetic fields. Similar flux closure material can be used in

conjunction with layers 25', 26', and 27' if the layers are present.

Turning now to FIGS. 3 through 9, several steps are illustrated in switching low switching field magnetic 5 tunneling junction memory cell 10 from the mode of FIG. 1 to the mode of FIG. 2. Specifically, FIG. 3 illustrates vector 20 of magnetoresistive layer 17 and vector 21 of magnetoresistive layer 18 in the antiparallel position of FIG. 1. In this position vector 20 is also antiparallel 10 to vector 28 of magnetoresistive layer 26 so that magnetic tunneling junction memory cell 10 is in the high resistance mode. To switch magnetic tunneling junction memory cell 10 to the low resistance mode (illustrated in FIG. 2), an initial small magnetic field is applied to 15 magnetic tunneling junction memory cell 10 sufficient to switch vector 20 into a parallel position with vector 21, as illustrated in FIG. 4. A larger positive magnetic field is then applied to magnetoresistive tunneling junction memory cell 10, which causes vectors 20 and 21 to 20 rotate in opposite directions 180°, as denoted by the transitional states illustrated in FIGS. 5, 6, and 7, respectively. Finally, vectors 20 and 21 are switched into the opposite direction illustrated in FIG. 8 and, when the magnetic field is removed, vector 20 again 25 assumes an antiparallel state, illustrated in FIG. 9. The antiparallel state illustrated in FIG. 9 is a stable state and, represents the low resistance mode of magnetic tunneling junction memory cell 10.

Because magnetic vectors 20 and 21 of magnetoresistive layers 17 and 18 rotate in opposite directions  $180^\circ$ , the magnetic moments tend to offset each other and a minimum amount of magnetic field is required 5 to perform the switching operation. The amount of switching magnetic field required to perform the switching operation is primarily dependent upon the difference in thickness or material between magnetoresistive layers 17 and 18. That is, because the stable modes for vectors 20 10 and 21 are antiparallel, by forming one of layers 17 and 18 so that it switches at a different magnetic field intensity than the other of layers 17 and 18, the mode switching results in rotation of vectors 20 and 21 in opposite directions with the resulting advantageous 15 offsetting magnetic moments.

Some additional advantages that are realized by the present structure is the fact that the antiparallel vectors 20 and 21 result in very little total magnetic moment for magnetoresistive tunneling junction memory cell 20. This low magnetic moment is further enhanced by the flux closure material 30' illustrated in FIG. 2. Also, when the size of the magnetoresistive tunneling junction memory cell approaches 10 nm, the energy barrier of the magnetization (which is proportional to the volume) is 25 close to the thermal fluctuation energy (KT). This causes the cell to be unstable. In the present invention the switching field can be reduced substantially without reducing the total size to an unstable level. Thus, an

advantage of having two layers switching in opposite directions at the same time is that the switching field is determined by the difference in thickness between the two switching layers or, more accurately, the difference 5 between the product of thickness and magnetization. Thus, both layers can be sufficiently thick so that the energy barrier for the two different magnetic states is higher than the thermal fluctuation energy.

Turning now to FIG. 10, a simplified view in top plan 10 is illustrated of an high density array 45 of low switching field magnetoresistive tunneling junction memory cells 46 in accordance with the present invention. Array 45 is formed on a substrate structure 47 which may include control electronics and other peripheral equipment, if 15 practical. Also, if an antiferromagnetic layer or the like is included as part of substrate structure 47 to pin vector 28 of structure 12 in a fixed position, the layer may be formed as a blanket layer so as to cooperate with each cell 46. Cells 46 lying in a common row, for 20 example, have the top magnetic layer connected to the bottom magnetic layer of the adjacent cell to form a common sense line 48. Further, word lines 49, illustrated in broken lines, are coupled to cells 46 lying in a common column for purposes of writing information into the cells, 25 as described above. Because of the zero, or essentially zero, magnetic moment of cells 10, cells of this type can be positioned very close and the density of an array of these cells can be greatly increased.

Thus, new and improved magnetic random access memories and memory cells which are capable of being written (stored states switched) with less magnetic field have been disclosed. Also, the new and improved multi-state, multi-layer magnetic memory cell with antiferromagnetically coupled magnetic layers is capable of being written (stored states switched) with less magnetic field and has a volume sufficient to not be effected by the thermal fluctuation energy. Further, the new and improved multi-state, multi-layer magnetic memory cell with antiferromagnetically coupled magnetic layers which is disclosed produces less magnetic interaction with adjacent cells in an array and can be fabricated very small and with an aspect ratio less than 5. Further, the new and improved multi-state, multi-layer magnetic memory cell is simpler to manufacture and to use and, because of its size, results in a high density array of cells.

While we have shown and described specific embodiments of the present invention, further modifications and improvements will occur to those skilled in the art. We desire it to be understood, therefore, that this invention is not limited to the particular forms shown and we intend in the appended claims to cover all modifications that do not depart from the spirit and scope of this invention.

What is claimed is:

- 5        1. A low switching field magnetic tunneling junction memory cell comprising:

a first antiferromagnetically coupled multi-layer structure including first and second magnetoresistive layers having a first non-magnetic conducting layer

10      situated in parallel juxtaposition between the first and second magnetoresistive layers, the first magnetoresistive layer having a first magnetic vector and the second magnetoresistive layer having a second magnetic vector with the first and second magnetic vectors being anti-

15      parallel with no applied magnetic field, and the first magnetoresistive layer being constructed to switch direction of the first magnetic vector at a different magnetic field intensity than the second magnetic vector of the second magnetoresistive layer;

- 20        a second structure including at least one magnetoresistive layer having a magnetic vector parallel with one of the first and second magnetic vectors of the first antiferromagnetically coupled multi-layer structure;

and

- 25        electrically insulating material situated in parallel juxtaposition between the first and second structures to form a magnetoresistive tunneling junction.

2. A low switching field magnetic tunneling junction memory cell as claimed in claim 1 wherein the first and second structures have a length/width ratio in a range of 1 to 5.

5

3. A low switching field magnetic tunneling junction as claimed in claim 1 wherein the first and second magnetoresistive layers have different thicknesses for switching at different switching fields.

10

4. A low switching field magnetic tunneling junction memory cell as claimed in claim 1 wherein the first and second magnetoresistive layers have different magnetizations for switching at different switching fields.

15

5. A high density array of low switching field magnetic tunneling junction memory cells comprising:

20 a substrate with a planar surface; and

a plurality of interconnected low switching field magnetoresistive tunneling junction memory cells supported on the planar surface of the substrate and interconnected to form a memory array, each cell of the plurality of cells having an aspect ratio less than 5 and a top plan

25 that is one of circular, diamond-shaped, or elliptical, each cell including

a first antiferromagnetically coupled multi-layer structure including first and second

magnetoresistive layers having a first non-magnetic conducting layer situated in parallel juxtaposition between the first and second magnetoresistive layers, the first magnetoresistive layer having a first magnetic vector and the second magnetoresistive layer having a second magnetic vector with the first and second magnetic vectors being anti-parallel with no applied magnetic field, and the first magnetoresistive layer being constructed to switch direction of the first magnetic vector at a different magnetic field intensity than the second magnetic vector of the second magnetoresistive layer;

15 a second structure including at least one magnetoresistive layer having a magnetic vector parallel with one of the first and second magnetic vectors of the first antiferromagnetically coupled multi-layer structure; and

20 electrically insulating material situated in parallel juxtaposition between the first antiferromagnetically coupled multi-layer structure and

the second structure to form a magnetoresistive tunneling junction.

25 6. A high density array of low switching field magnetic tunneling junction memory cells as claimed in claim 5 wherein the first and second magnetoresistive

layers have different thicknesses for switching at different switching field intensities.

7. A high density array of low switching field

5 magnetic tunneling junction memory cells as claimed in

claim 5 wherein the first and second magnetoresistive

layers have different magnetizations for switching at

different switching field intensities.

10 8. A method of fabricating a low switching field

magnetic tunneling junction memory cell comprising the

steps of:

providing a substrate having a planar surface;

depositing a first magnetoresistive structure on the

15 substrate, the first magnetoresistive structure having a

magnetic vector lying along a preferred magnetic axis

parallel to the planar surface;

depositing a layer of electrically insulating

material on the first magnetoresistive structure; and

20 depositing a second magnetoresistive structure on the

electrically insulating layer including

depositing a first layer of magnetoresistive

material with a first thickness on the electrically

insulating layer and providing the first layer with a

25 magnetic vector lying along the preferred magnetic axis;

depositing a first non-magnetic conducting layer

on the first layer of magnetoresistive material; and

depositing a second layer of magnetoresistive material with a second thickness different than the first thickness on the first non-magnetic conducting layer and providing the second layer with a magnetic vector lying along the preferred magnetic axis parallel to the magnetic axis of the first layer of magnetoresistive material, the first and second layers of magnetoresistive material and the first non-magnetic conducting layer defining an antiferromagnetically coupled multi-layer structure in which the magnetic vector of the second layer is anti-parallel to the magnetic vector of the first layer with no magnetic field applied; and the first magnetoresistive structure, the layer of electrically insulating material, and the second magnetoresistive structure forming a low switching field magnetoresistive tunneling junction memory cell.

9. A method of fabricating a low switching field magnetic tunneling junction memory cell as claimed in claim 8 wherein the steps of depositing first and second magnetoresistive layers include depositing first and second magnetoresistive layers with different thicknesses for switching at different switching fields.

10. A method of fabricating a low switching field magnetic tunneling junction memory cell as claimed in claim 8 wherein the steps of depositing first and second

21

magnetoresistive layers include depositing first and second magnetoresistive layers with different magnetizations for switching at different switching fields.

5

10 FIG. 1

10' FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

# INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 99/16314

**A. CLASSIFICATION OF SUBJECT MATTER**

IPC 7 G11C11/15

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 G11C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                          | Relevant to claim No. |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 5 768 183 A (CHEN EUGENE ET AL)<br>16 June 1998 (1998-06-16)<br>the whole document<br>---                                                                                                                                                                | 1-4, 8-10             |

| Y        | US 5 768 181 A (TEHRANI SAIED N ET AL)<br>16 June 1998 (1998-06-16)<br>column 4, line 50 -column 5, line 15;<br>figure 5<br>---                                                                                                                             | 5-7                   |

| X        | US 5 768 181 A (TEHRANI SAIED N ET AL)<br>16 June 1998 (1998-06-16)<br>column 4, line 50 -column 5, line 15;<br>figure 5<br>---                                                                                                                             | 1                     |

| Y        | PATENT ABSTRACTS OF JAPAN<br>vol. 1998, no. 09,<br>31 July 1998 (1998-07-31)<br>& JP 10 106255 A (TOSHIBA CORP),<br>24 April 1998 (1998-04-24)<br>abstract<br>& US 5 894 447 A (DAISABURO TAKASHIMA)<br>13 April 1999 (1999-04-13)<br>figures 8A, 8B<br>--- | 5-7                   |

|          |                                                                                                                                                                                                                                                             | -/-                   |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

**' Special categories of cited documents :**

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

9 November 1999

17/11/1999

Name and mailing address of the ISA

European Patent Office, P. B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl.

Fax: (+31-70) 340-3016

Authorized officer

Wolff, N

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 99/16314

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                 |                       |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                              | Relevant to claim No. |

| A                                                    | US 5 745 408 A (CHEN EUGENE ET AL)<br>28 April 1998 (1998-04-28)<br>figures 5,11<br>---                                                                                         | 1,5,7                 |

| A                                                    | EP 0 780 912 A (MATSUSHITA ELECTRIC IND CO LTD) 25 June 1997 (1997-06-25)<br>column 1, line 1 -column 3, line 10<br>column 6, line 11 -column 7, line 20;<br>figures 4-6<br>--- | 1                     |

| A                                                    | US 5 691 865 A (DEN BROEDER FRIEDRICH J A ET AL) 25 November 1997 (1997-11-25)<br>figure 6<br>---                                                                               | 1                     |

| A                                                    | US 5 587 943 A (TOROK JAMES ET AL)<br>24 December 1996 (1996-12-24)<br>column 11, line 14 -column 12, line 39;<br>figure 7<br>-----                                             | 5                     |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/US 99/16314

| Patent document cited in search report | Publication date | Patent family member(s)                                                     |  | Publication date                                                   |

|----------------------------------------|------------------|-----------------------------------------------------------------------------|--|--------------------------------------------------------------------|

| US 5768183                             | A 16-06-1998     | NONE                                                                        |  |                                                                    |

| US 5768181                             | A 16-06-1998     | NONE                                                                        |  |                                                                    |

| JP 10106255                            | A 24-04-1998     | US 5894447 A                                                                |  | 13-04-1999                                                         |

| US 5745408                             | A 28-04-1998     | NONE                                                                        |  |                                                                    |

| EP 0780912                             | A 25-06-1997     | JP 9172212 A<br>US 5715121 A                                                |  | 30-06-1997<br>03-02-1998                                           |

| US 5691865                             | A 25-11-1997     | DE 69511017 D<br>EP 0700564 A<br>WO 9522820 A<br>JP 8510095 T<br>SG 52781 A |  | 02-09-1999<br>13-03-1996<br>24-08-1995<br>22-10-1996<br>28-09-1998 |

| US 5587943                             | A 24-12-1996     | CA 2211699 A<br>EP 0809846 A<br>JP 11501438 T<br>WO 9625740 A               |  | 22-08-1996<br>03-12-1997<br>02-02-1999<br>22-08-1996               |