(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7274420号**

**(P7274420)**

(45)発行日 令和5年5月16日(2023.5.16)

(24)登録日 令和5年5月8日(2023.5.8)

(51)国際特許分類

F I

|        |                |        |      |   |

|--------|----------------|--------|------|---|

| H 03 K | 5/08 (2006.01) | H 03 K | 5/08 | E |

| H 03 M | 1/12 (2006.01) | H 03 M | 1/12 | A |

| H 03 K | 5/24 (2006.01) | H 03 K | 5/24 |   |

| H 03 M | 1/06 (2006.01) | H 03 M | 1/06 |   |

請求項の数 12 (全19頁)

(21)出願番号 特願2019-548740(P2019-548740)

(86)(22)出願日 平成30年2月14日(2018.2.14)

(65)公表番号 特表2020-510340(P2020-510340)

A)

(43)公表日 令和2年4月2日(2020.4.2)

(86)国際出願番号 PCT/US2018/018255

(87)国際公開番号 WO2018/164818

(87)国際公開日 平成30年9月13日(2018.9.13)

審査請求日 令和3年2月9日(2021.2.9)

(31)優先権主張番号 15/453,707

(32)優先日 平成29年3月8日(2017.3.8)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 591025439

ザイリンクス インコーポレイテッド

XILINX INCORPORATED

アメリカ合衆国 カリフォルニア州 95

124-3400 サンホセ ロジック

ドライブ 2100

(74)代理人 110001195

弁理士法人深見特許事務所

(72)発明者 ハドナー, ジェイムズ

アメリカ合衆国、95124 カリフォ

ルニア州、サン・ノゼ、ロジック・ドラ

イブ、2100

審査官 及川 尚人

最終頁に続く

(54)【発明の名称】 複数のリセットレベルを有する動的量子化器

**(57)【特許請求の範囲】****【請求項1】**

アナログ信号をデジタル化するための量子化器回路であって、複数の入力電界効果トランジスタを含む入力回路(110)を備え、前記入力回路は、経時変化する第1のクロック信号(c1k)に結合された第1のデバイス(N0)を含み、前記入力回路は、前記量子化器回路の動作のアクティブサイクル中に、入力信号(151、152)に応答して、第1のノードおよび第2のノード(X1、X2)で差動電圧信号を生成するように構成され、前記量子化器回路の前記動作のアクティブサイクルは、前記第1のクロック信号(c1k)に対応しており、前記入力回路(110)は前記入力信号(151、152)を入力電流に変換し、前記入力電流は、前記量子化器回路の前記動作のアクティブサイクルの入力サンプリングフェーズ中に積分され、前記第1のデバイス(N0)は、前記第1のクロック信号(c1k)が前記第1のデバイス(N0)をオフして前記動作のアクティブサイクルが終了すると、前記入力回路(110)が電流を引き込まないように構成され、前記量子化器回路はさらに、

前記入力回路に結合された再生回路(130)を備え、前記再生回路は、前記入力サンプリングフェーズ中に前記入力回路(110)によって生成された前記差動電圧信号を増幅することによって、出力信号(161、162)を生成するように構成され、前記量子化器回路はさらに、

前記入力回路(110)の前記第1のノードおよび前記第2のノード(X1、X2)に結合された第1のリセット回路(P2、P3)と、前記再生回路(130)に結合された

第2のリセット回路( P0、P1 )とを備え、前記動作のアクティブサイクルの終了に応答して、前記第1のリセット回路( P2、P3 )は、前記入力回路( 110 )を第1の電圧( A v c c r s t )の第1の電圧源( 120 )に結合するように構成され、前記第2のリセット回路( 170 )は、前記再生回路( 130 )を第2の電圧( A v c c )の第2の電圧源( 140 )に結合するように構成され、前記第1の電圧は前記第2の電圧とは異なつてあり、前記第1の電圧源( 120 )は、前記第1のクロック信号( c1k )が前記第1のデバイス( N0 )をオンしたときに前記第1のノードおよび前記第2のノード( X1 、 X2 )が初期開始電圧となるように、前記第1のリセット回路( P2、P3 )を介して前記第1のノードおよび前記第2のノード( X1 、 X2 )に電圧供給し、前記第1の電圧( A v c c r s t )は、プロセスに依存する電圧または温度に依存する電圧に応答して調節され、

前記第1の電圧の大きさを増加または減少させるように構成された制御回路をさらに備え、前記制御回路は、前記第1の電圧を表わす基準信号を生成するように構成されたアナログ制御回路( 700, 800 )を含み、前記アナログ制御回路は、プロセスおよび温度に依存する複数の入力信号に応答して前記基準信号を生成する、量子化器回路。

#### 【請求項 2】

前記第1の電圧を前記第2の電圧よりも高くすることによって前記量子化器回路におけるノイズおよび電圧オフセットを減少させるか、または、前記第1の電圧を前記第2の電圧よりも低くすることによって前記量子化器回路のタイミング性能を改善する、請求項1に記載の量子化器回路。

#### 【請求項 3】

前記第1のリセット回路はさらに、経時変化する第2のクロック信号( c1k\_h\_i )を受信するように構成され、

前記第2のクロック信号の大きさは、前記第1の電圧を基準として生成される、請求項1または2に記載の量子化器回路。

#### 【請求項 4】

前記第2のクロック信号は、前記第1のクロック信号( c1k )を示す信号を受信するように構成された調整器から提供される回路によって生成される、請求項3に記載の量子化器回路。

#### 【請求項 5】

前記アナログ制御回路と動作可能に通信する調整器( 710, 814 )をさらに備え、

前記調整器は、前記第1の電圧を表わす前記基準信号に応答して、前記第1の電圧を前記量子化器回路に出力するように構成されている、請求項1に記載の量子化器回路。

#### 【請求項 6】

前記アナログ制御回路は、

複数の入力信号を受信してデジタル入力信号データを生成するように構成された少なくとも1つのアナログ - デジタル変換器( 808 )を含み、前記入力信号は、少なくとも前記プロセスに依存する電圧および前記温度に依存する電圧を示す信号を含み、前記アナログ制御回路はさらに、

前記少なくとも1つのアナログ - デジタル変換器に動作可能に結合されたプログラマブル集積回路( 810 )を含み、前記プログラマブル集積回路は、前記デジタル入力信号データを処理することによって回路構成データを決定し、回路構成データデジタル出力信号を生成するように構成され、前記プログラマブル集積回路は、前記構成データを決定するための実行可能コードでプログラムされており、前記アナログ制御回路はさらに、

前記プログラマブル集積回路に動作可能に結合された少なくとも1つのデジタル - アナログ変換器( 812 )を含み、前記少なくとも1つのデジタル - アナログ変換器は、前記回路構成データデジタル出力信号を、前記第1の電圧を表わす前記基準信号に変換するように構成されている、請求項1～5のいずれか1項に記載の量子化器回路。

#### 【請求項 7】

前記量子化器回路は、バルク接続またはウェル接続を含む、請求項1に記載の量子化器

回路。

**【請求項 8】**

前記複数の入力電界効果トランジスタはN型電界効果トランジスタを含む、請求項1～7のいずれか1項に記載の量子化器回路。

**【請求項 9】**

前記複数の入力電界効果トランジスタはP型電界効果トランジスタを含む、請求項1～8のいずれか1項に記載の量子化器回路。

**【請求項 10】**

前記第1のリセット回路(170)は、前記入力回路(110)を前記第1の電圧源に結合する第1のセットのトランジスタ(172)を含み、

10

前記第2のリセット回路(170)は、前記再生回路(130)を前記第2の電圧源(140)に結合する第2のセットのトランジスタ(174)と、前記量子化器回路の複数の出力ピン(161、162)を互いに結合する第3のトランジスタ(178)とを含む、請求項1～9のいずれか1項に記載の量子化器回路。

**【請求項 11】**

入力段階の利得と再生段階のタイミングとが別々に制御されるように、前記入力回路(110)および前記再生回路(130)の各々は、別々の電流および複数のクロック信号入力を有するように構成および配置されている、請求項1～10のいずれか1項に記載の量子化器回路。

20

**【請求項 12】**

前記第1のクロック信号(c1k)が前記第1のデバイス(N0)をオンしたときに前記第1のノードおよび前記第2のノード(X1、X2)が初期開始電圧となるように前記第1のリセット回路(P2、P3)を介して前記第1のノードおよび前記第2のノード(X1、X2)に電圧供給することは、前記第1のクロック信号(c1k)が前記第1のデバイス(N0)をオンして前記動作のアクティプサイクルが開始される前のリセットフェーズ中に、前記リセット回路(P2、P3)を介して前記第1のノードおよび前記第2のノード(X1、X2)を前記第1の電圧源(120)に結合することを含む、請求項1～11のいずれか1項に記載の量子化器回路。

**【発明の詳細な説明】**

**【技術分野】**

30

**【0001】**

技術分野

本開示は、概して量子化器に関し、より特定的には、複数の電圧源を有する量子化器に関する。

**【背景技術】**

**【0002】**

背景

量子化器回路(「スライサ」と呼ばれることがある)は、一種の高速クロック制御比較器であり、アナログ信号をデジタルビットに量子化するためにS e r D e s (serializer/deserializer)およびアナログ・デジタル変換(「A D C」)回路で使用される。量子化器の性能パラメータのうち最も重要な3つの性能パラメータは、c l o c k - t o - qとして測定されるタイミング、入力換算R M S ノイズ、および入力換算オフセット電圧である。入力換算R M S ノイズ性能および入力換算オフセット電圧性能は、両方とも入力換算であるので、共通のパラメータ(具体的には、順電圧利得)によって関係付けられる。

40

**【0003】**

量子化器は、動的量子化器または静的量子化器に大別することができる。動的量子化器には静的電力損失がないのに対して、静的量子化器タイプ(例えば、電流モード論理(「C M L」)量子化器)には静的電力損失がある。動的量子化器は、さらに2つのグループに細分化することができる。1つ目は、S T R O N G A R M (登録商標)型トポロジーを有するものとして分類されることもあるが、センスアンプと呼ばれる場合もある。他方の

50

グループは、ダブルテールラッチ型トポロジーとして分類されることもあるが、より感度が高く、かつ、与えられたタイミング性能に対して入力換算 RMS ノイズおよび入力換算オフセット電圧がより低いものである。

#### 【 0 0 0 4 】

動的量子化器タイミング性能は、典型的には、トランジスタプロセスコーナーが低速であり、高温であり、かつ電源電圧が最小である場合に最も低い。なぜなら、このようなプロセスコーナーは最小の電流しか供給しないため、内部量子化器ノードの充電速度が最も遅くなるからである。入力換算 RMS ノイズおよび入力換算オフセット電圧は、典型的には、トランジスタプロセスコーナーが高速であり、高温であり、かつ電源電圧が最小である場合に最悪である。なぜなら、このようなプロセスコーナーは電圧利得が最も低いからである。本明細書では、これらのプロセスコーナーをそれぞれ、ワーストケースのタイミングのコーナー、およびワーストケースの RMS ノイズのコーナーと呼ぶ。

#### 【 0 0 0 5 】

STRONGARM (登録商標) 型トポロジーを有する量子化器の入力換算 RMS ノイズおよび入力換算オフセット電圧を改善するための従来の手法として、テール電流を減少させることによって量子化器の電圧利得を増加させるものがある。しかしながら、このようにテール電流を減少させると、量子化器の clock - to - q 時間が増加するため、タイミング性能が悪化する。また別の手法として、テール電流を増加させることによって量子化器の clock - to - q 時間を改善するものがある。しかしながら、この手法では利得が減少するため、入力換算 RMS ノイズおよび入力換算オフセット電圧が悪化する。さらに別の手法としては、テール電流を減少させるのではなく、入力デバイスのサイズを大きくすることによって利得を増加させ、それによって量子化器の入力換算 RMS ノイズおよび入力換算オフセット電圧を改善するものがある。しかしながら、これによって駆動回路への入力キャパシタンスおよび内部寄生キャパシタンスが不必要に増加し、タイミング性能も悪化する。

#### 【 0 0 0 6 】

以下で述べるように、本開示は、上記および他の問題に対処するために、量子化器の構成および動作を改善する。

#### 【 発明の概要 】

#### 【 課題を解決するための手段 】

#### 【 0 0 0 7 】

##### 概要

数多くの実現例が、アナログ信号をデジタル化するための量子化器回路に向けられる。量子化器は、典型的には、入力回路と、再生回路と、リセット回路とを含む。入力回路は、概して複数の入力電界効果トランジスタを含み、第 1 の電圧の入力信号を供給する第 1 の電圧源に結合されている。入力回路は入力信号を入力電流に変換し、この入力電流は、量子化器回路の動作のアクティブサイクルの入力サンプリングフェーズ中に積分される。再生回路は入力回路に結合されており、複数の再生電界効果トランジスタを含む。再生回路は、第 2 の電圧の第 2 の電圧源に接続されている。第 2 の電圧は、典型的には第 1 の電圧とは大きさが異なる。リセット回路はさらに、入力回路および再生回路に結合されている。

#### 【 0 0 0 8 】

いくつかの実現例では、第 1 の電圧および第 2 の電圧は固定されてもよい。必要に応じて、第 1 の電圧は第 2 の電圧に比例してもよく、または第 2 の電圧から導き出されてもよい。第 1 の電圧を第 2 の電圧よりも高くすることによって量子化器回路におけるノイズおよび電圧オフセットを減少させるように構成してもよい。いくつかの実現例では、第 1 の電圧を第 2 の電圧よりも低くすることによって量子化器回路のタイミング性能を改善するように構成してもよい。好ましくは、入力回路は、経時変化する第 1 のクロック信号を受信するように構成され、入力回路は、第 1 のクロック信号が閾値電圧よりも小さい場合は電流を引き込まない。

**【 0 0 0 9 】**

いくつかの実現例では、入力回路はさらに、経時変化する第2のクロック信号を受信するように構成されてもよい。第2のクロック信号の大きさは、第1のクロック信号を基準として生成されてもよい。例えば、第2のクロック信号は、第1のクロック信号を示す信号を受信するように構成された調整器から提供される回路によって生成されてもよい。

**【 0 0 1 0 】**

いくつかの実現例では、第2の電圧を接地とし、かつ、第1の電圧を第2の電圧よりも低くすることによって、量子化器回路におけるノイズおよび電圧オフセットを減少させてもよい。他の実現例では、第2の電圧を接地とし、かつ、第1の電圧を第2の電圧よりも高くすることによって、量子化器回路のタイミング性能を改善してもよい。

10

**【 0 0 1 1 】**

本開示の他の態様によれば、本開示に係る量子化器を動作させるために、第1の電圧の大きさを増加または減少させるように構成された制御回路が設けられる。制御回路は、アナログ部品および／またはデジタル部品を含み得る。いくつかの実現例では、第1の電圧を表わす基準信号を生成するように構成されたアナログ制御回路が設けられる。アナログ制御回路と動作可能に通信する調整器が設けられてもよい。調整器は、第1の電圧を表わす基準信号に応答して、第1の電圧を量子化器回路に出力するように構成されてもよい。必要に応じて、アナログ制御回路は、複数の入力信号に応答して基準信号を生成してもよい。アナログ制御回路への入力信号は、例えば、第2の電圧の大きさ、プロセスに依存する電圧、温度に依存する電圧、および／またはシフト電圧のうちの少なくとも1つを示す信号を含み得る。

20

**【 0 0 1 2 】**

いくつかの実現例では、制御回路は、複数の入力信号を受信してデジタル入力信号データを生成するように構成された少なくとも1つのアナログ - デジタル変換器を含み得る。制御回路はさらに、アナログ - デジタル変換器に動作可能に結合されたプログラマブル集積回路を含み得る。このプログラマブル集積回路は、デジタル入力信号データを処理することによって回路構成データを決定し、回路構成データデジタル出力信号を生成するように構成されてもよい。制御回路はさらに、プロセッサに動作可能に結合された少なくとも1つのデジタル - アナログ変換器を含み得る。上記少なくとも1つのデジタル - アナログ変換器は、回路構成データデジタル出力信号を、第1の電圧を表わす基準信号に変換するように構成されてもよい。入力信号は、第2の電圧の大きさ、プロセスに依存する電圧、コモンモード電圧、温度に依存する電圧、および／またはシフト電圧のうちの少なくとも1つを示す信号を含み得る。制御回路は、上記少なくとも1つのデジタル - アナログ変換器と動作可能に通信する調整器をさらに含んでもよい。調整器は、第1の電圧を表わす基準信号に応答して、第1の電圧を量子化器回路に出力するように構成されてもよい。さまざまな実現例では、プログラマブル集積回路は、構成データを決定するための実行可能コードでプログラムされてもよい。さらに、さまざまな実施形態によれば、量子化器回路は、特に、STRONGARM（登録商標）型量子化器、および「ダブルテール」型量子化器に特有のトポロジーを有してもよい。他の特徴は、以下の詳細な説明および特許請求の範囲を考慮することによって認識されるであろう。

30

**【 0 0 1 3 】**

以下の詳細な説明を検討し、かつ図面を参照すれば、開示された装置および関連する方法のさまざまな態様および特徴が明らかになるであろう。

**【図面の簡単な説明】****【 0 0 1 4 】**

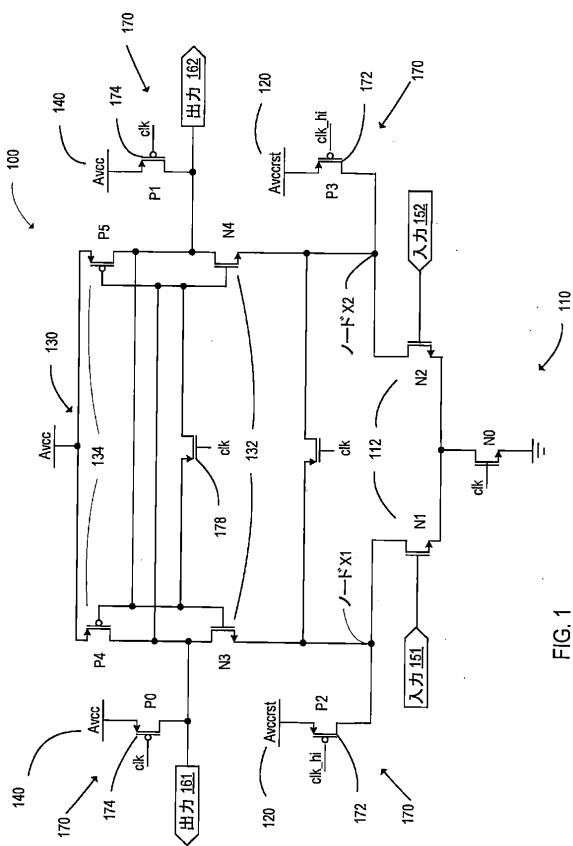

- 【図1】本開示の第1の実現例に係る量子化器を示す図である。

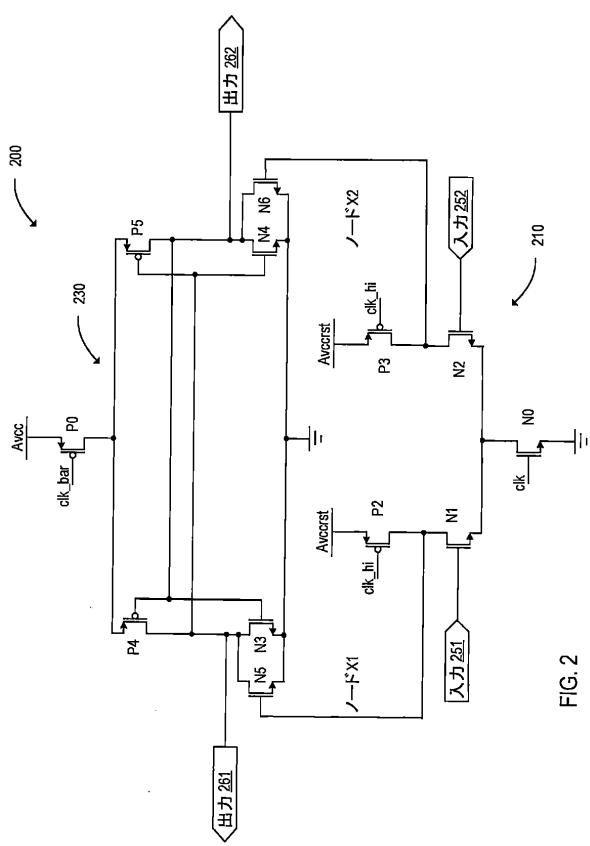

- 【図2】本開示の第2の実現例に係る量子化器を示す図である。

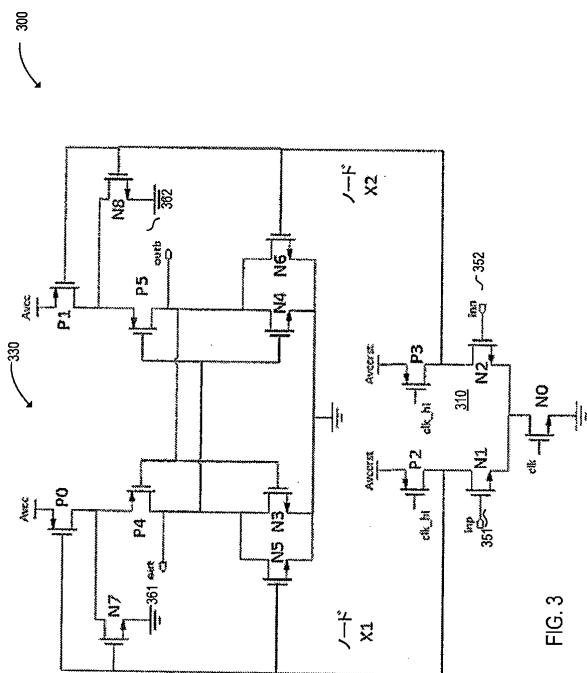

- 【図3】本開示の第3の実現例に係る量子化器を示す図である。

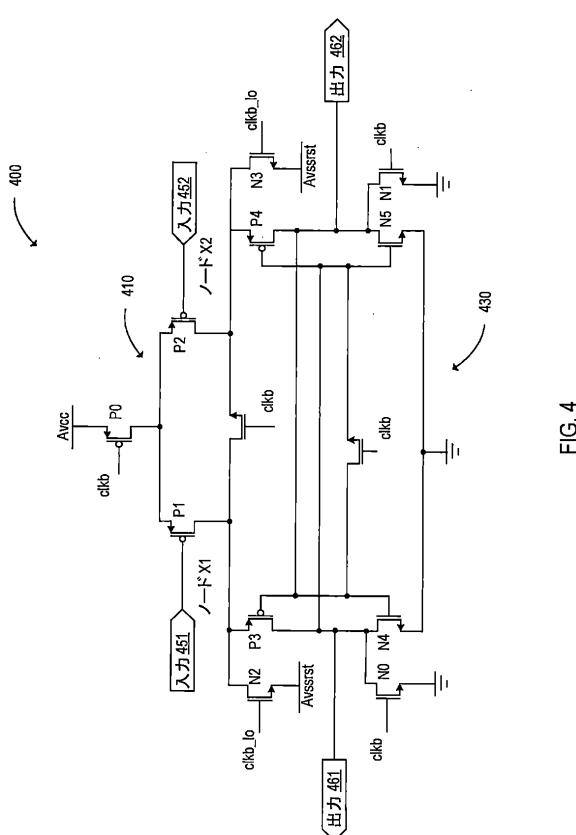

- 【図4】本開示の第4の実現例に係る量子化器を示す図である。

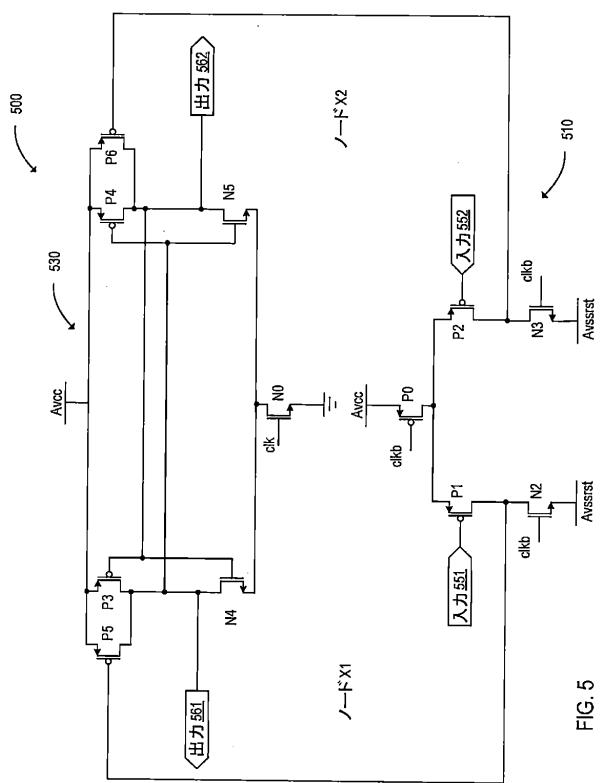

- 【図5】本開示の第5の実現例に係る量子化器を示す図である。

40

50

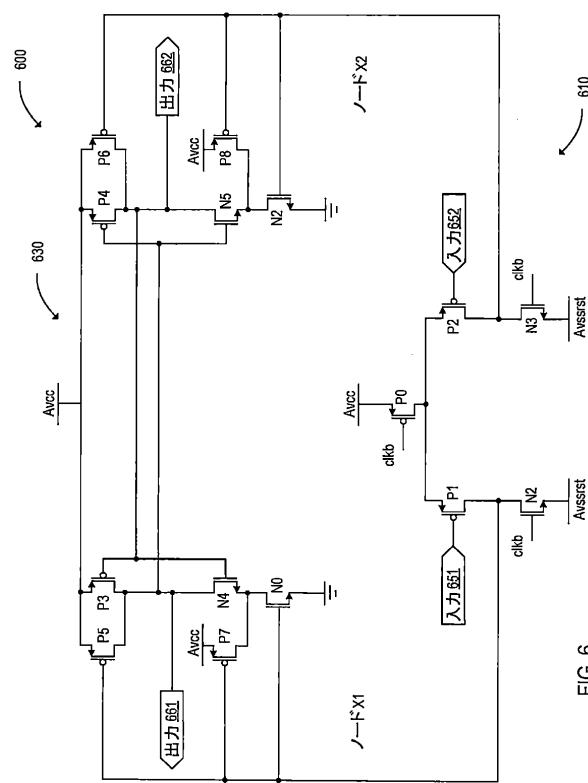

【図 6】本開示の第 6 の実現例に係る量子化器を示す図である。

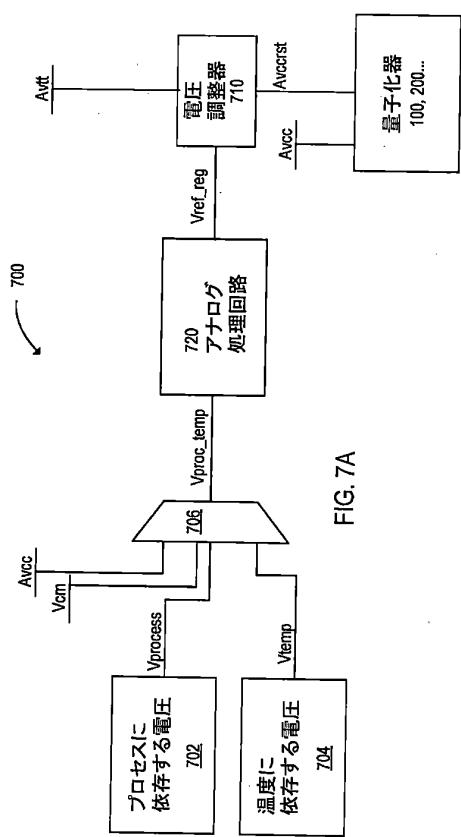

【図 7 A】本開示に係る、量子化器を制御するための制御回路の第 1 の実現例を示す図である。

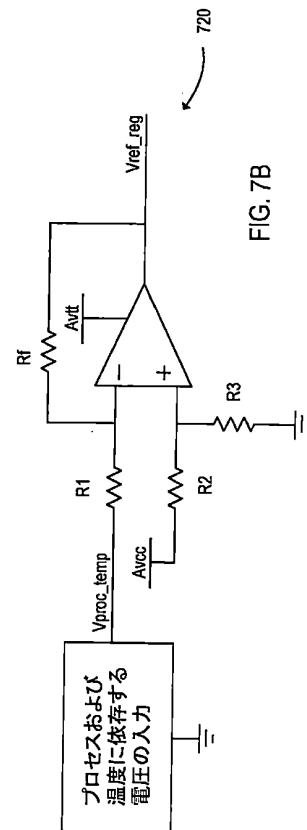

【図 7 B】本開示に係る、図 7 A の制御回路の一部を示す図である。

【図 8】本開示に係る、量子化器を制御するための制御回路の第 2 の実現例を示す図である。

【図 9】本開示に係る、アナログのプロセスおよび温度に依存する電圧を生成するための回路を示す図である。

【図 10】本開示に係る、クロック信号を発生させるクロック発生器を提供する調整器のためのローサイド基準を生成する回路を示す図である。 10

【図 11】開示された回路およびプロセスをその上で実現し得るプログラマブル集積回路（I C）を示す図である。

#### 【発明を実施するための形態】

##### 【0015】

###### 詳細な説明

以下の説明において、本明細書で提示する具体例を説明するために、多くの具体的な詳細を示す。しかしながら、下記の具体的な詳細のうち必ずしもすべてが無くても、1つ以上の他の例および／またはそれらの例の変形例が実施可能であることが、当業者に明らかになるはずである。また、本明細書中の例の説明が不鮮明にならないように、公知の特徴については詳述していない。説明を容易にするために、異なる図中で同じ参照番号を用いて同じ要素または同じ要素の他の例を指すことがある。 20

##### 【0016】

本明細書では、プロセス、電圧、および温度（「P V T」）ならびに入力コモンモード（V cm）の変動に合わせて動的量子化器（またはスライサ）の性能全体を改善するさまざまな実現例を提示する。本明細書で示すように、ある実施形態では、量子化器における他の部分への電圧供給は変更せずに、量子化器の入力デバイスに接続されたリセットデバイスへの電圧供給を分離し、次いで変更することによって、量子化器回路の性能を改善する。いくつかの実現例では、リセットデバイスへの電圧供給を減少させることによって、量子化器のタイミング性能を改善する（clock-to-q を減少させる）ことができる。他の実現例では、リセットデバイスへの電圧供給を増加させることによって、回路の入力換算 RMS ノイズおよび入力換算オフセット電圧を改善する（低減する）ことができる。同様に、リセットデバイスへの電圧供給を増加させることによって、プロセスおよび電圧の規模変更に起因する V cm の増加を緩和することができる。これらの目的および他の目的を達成するために、本明細書では、リセットデバイスへの電圧供給を制御するための制御システムが設けられる。 30

##### 【0017】

開示された実施形態では、必要なタイミング性能を満たすようにテール電流を増加させ、その後、上述の「ワーストケース」の RMS ノイズのプロセスコーナーにおいてリセットデバイスへの電圧供給レベルを増加させることによって、入力換算 RMS ノイズ性能および入力換算オフセット電圧性能を改善することができる。一方、開示された実施形態では、必要な入力換算 RMS ノイズ性能および入力換算オフセット電圧性能を満たすようにテール電流を減少させ、その後、上述の「ワーストケース」のタイミングのプロセスコーナーにおいてリセットデバイスへの電圧供給レベルを減少させることによって、タイミング性能の改善を容易にする。 40

##### 【0018】

したがって、開示された実施形態では、STRONGARM（登録商標）型またはダブルテールラッチ型のトポロジーなど、動的量子化器の設計の自由度を高めることができる。特定の実現例では、これは、入力デバイスに接続されたリセットデバイスへの電源を主電源（本明細書では Avcc または Avss と称する）から切断し、それらのリセットデバイスを別途制御される電源（本明細書では Avccrst または Avssrst と称す 50

る)に接続することによって実現され、その結果、量子化器の性能が改善される。これにより、新たな A v c c r s t / A v s s r s t レベルを容易に増加 / 減少させることができ、その結果、( i ) 量子化器の入力換算 R M S ノイズ性能および入力換算オフセット電圧性能を改善すること、および / または ( i i ) V c m の増大を緩和することができる。また、A v c c r s t / A v s s r s t レベルを容易に減少 / 増加させることができ、その結果、量子化器のタイミング性能を改善することができる。新たな A v c c r s t / A v s s r s t 電源を駆動するために、( i ) プロセスおよび温度 ( P T ) に依存する電源電圧、( i i ) プロセスおよび電圧 ( P V ) に依存する電源電圧、または ( i i i ) プロセス、電圧、および温度 ( P V T ) に依存する電源電圧を生成することによって、上記目的は容易に達成され得る。ここで、「V」は A v c c および V c m の適切な組み合わせで構成されてもよい。

10

#### 【 0 0 1 9 】

補正 P V T を用いて、論理ローの供給により A v c c r s t を基準としたクロックを生成することによって、信頼性の高い動作が可能になるとともに、T D D B、H C I、および B T I の悪化を回避することができる。また、リセットデバイスに対して補正 P V T でのオーバードライブを生じさせるため、リセットデバイスをフルクロックレートで動作させることができる。

#### 【 0 0 2 0 】

本開示の範囲は、S T R O N G A R M (登録商標) 型トポロジーまたはダブルテールラッチ型トポロジーなどの動的量子化器に適用可能である。S T R O N G A R M (登録商標) 型トポロジーを有する量子化器の場合、開示された実施形態によって、タイミング性能の改善と入力換算 R M S ノイズおよび入力換算オフセット電圧の低減とが同時に実現可能である。開示された実施形態は、主にシリアル通信および A D C の分野で使用される動的量子化器に適用可能であるが、その他の検知の分野で使用することも可能であり、信号利得のリセット可能な積分を利用する如何なる回路にも適用可能である。ダブルテールラッチ型の量子化器トポロジーの場合、開示された実施形態を用いることによって、( a ) タイミング性能、ならびに ( b ) 入力換算 R M S ノイズおよび入力換算オフセット電圧の両方を改善することができる。

20

#### 【 0 0 2 1 】

ここで図面を参照すると、限定ではなく例示のために、図 1 は、S T R O N G A R M (登録商標) 型トポロジーを有する、本開示の第 1 の実現例に係る量子化器を示す。図 1 に示すように、アナログ信号をデジタル化するための量子化器回路 1 0 0 が提示されている。量子化器回路 1 0 0 は、入力回路、再生回路、およびリセット回路を含む。入力回路 1 1 0 は、複数の入力電界効果トランジスタ 1 1 2 を含み、第 1 の電圧源 1 2 0 に結合されている。第 1 の電圧源 1 2 0 は、第 1 の電圧の入力信号 (本明細書では A v c c r s t として表わす) を供給する。図示のように、入力回路 1 1 0 は、経時変化する第 1 のクロック信号 ( c l k ) を受信するように構成されている。第 1 のクロック信号が閾値電圧よりも小さく、かつアクティブである場合には、入力回路は電流を引き込まない。第 1 のクロック信号が閾値電圧よりも大きい場合には、入力回路は電流を消費する。

30

#### 【 0 0 2 2 】

再生回路 1 3 0 は、入力回路 1 1 0 に結合されており、複数の再生電界効果トランジスタ 1 3 2、1 3 4 を含む。再生回路は、第 2 の電圧 A v c c の第 2 の電圧源 1 4 0 に接続されている。本明細書に示す所望の性能改善をもたらすように、第 2 の電圧 A v c c は第 1 の電圧 A v c c r s t とは異なる大きさである (必要に応じて、いずれが大きくてよい)。

40

#### 【 0 0 2 3 】

リセット回路 1 7 0 は、入力回路 1 1 0 および再生回路 1 3 0 に結合されている。リセット回路 1 7 0 は、入力回路 1 1 0 を第 1 の電圧源 1 2 0 に結合する第 1 のセットのトランジスタ 1 7 2 と、再生回路 1 3 0 を第 2 の電圧源 1 4 0 に結合する第 2 のセットのトランジスタ 1 7 4 と、出力ピン 1 6 1 を出力ピン 1 6 2 に結合する第 3 のトランジスタ 1 7

50

8とを含む。

#### 【0024】

動作中、入力回路110は、入力ピン151、152からの入力信号を入力電流に変換する。入力電流は、量子化器回路100の動作のアクティブサイクルの入力サンプリングフェーズ中に積分される。前のサイクルのリセットフェーズが終了すると、リセット回路のPMOSのP0、P1、P2、およびP3(172、174)がオフとなるため、入力サンプリングフェーズ中、最初はデバイスN0、N1およびN2(112)のみがオンである。

#### 【0025】

利得を改善することによってノイズ/電圧オフセットを減少させるためには、例えば、

10

入力回路110内のデバイスが飽和状態で動作する時間が、アクティブサイクルのうちで

きるだけ多いことが望ましい(ただしその場合、再生が行われる際には結局すべてのデバ

イスが線形領域に入る(飽和領域から抜け出る)ため、タイミング性能は犠牲になる)。

デバイスN0のドレインの電圧がAvcc-Vth0よりも低下すると、まずデバイスN

0が線形領域に入る。その後、ノードX1およびX2がそれぞれ(Vcm-Vth1)お

よび(Vcm-Vth2)よりも低下すると、デバイスN1およびN2が線形領域に入る

。Vcmは入力151、152におけるコモンモード電圧であり、Vth0、Vth1、

およびVth2は、それぞれデバイスN0、N1およびN2の閾値電圧である。入力サン

プリングフェーズは、N1およびN2が線形領域に入るのとほぼ同時に終了する。

#### 【0026】

入力サンプリングフェーズの終わり頃(N1およびN2が線形領域に入る前)であって

20

、かつノードX1およびX2が(Avcc-Vth34)よりも低下すると(Vth34

はN3およびN4の閾値電圧)、再生デバイスN3およびN4がオンされて2次積分ネット

ワークを形成する。N3およびN4は、この間に飽和となり、これらのデバイスをめぐ

る再生が開始する。N1~N4が飽和状態を維持する間は、量子化器回路100は動作の

第2のフェーズのままである。

#### 【0027】

N3およびN4がオン状態を続けた結果、出力ピン161、162で(Avcc-Vt

h12)未満となるまで放電すると(Vthp12はP1およびP2の閾値電圧)、フル

30

再生が開始する。再生回路130は、入力サンプリングフェーズ中にノードX1および

X2間の入力回路によって(および、出力ピン161、162間のN3/N4によって)

生成される差動電圧を正帰還で増幅することによって、出力ピン161、162のCMOS

レベルに近い大きな信号電圧を生成する。

#### 【0028】

量子化器回路100が動作の第3のフェーズに入ると、P4、P5、N3、およびN4

が再生する。この第3のフェーズは、N1~N4のうちのいずれかが飽和状態でなくなっ

たときに開始する。第3のフェーズにおいてN3およびN4は再生し続け、P4およびP

5は導通し始める。動作の第3のフェーズは、クロック信号の立ち下がりエッジでのリセ

ット時に終了する。

#### 【0029】

本開示に係る利点は、量子化器100に複数の電圧源を設け、いくつかの実施形態では

電圧源同士の相対的な電圧レベルを異ならせることによってもたらされる。

#### 【0030】

入力換算RMSノイズおよび入力換算オフセット電圧はともに、量子化器利得を増加さ

せることによって減少させることができる。なお、本明細書で示す例示的な量子化器では

、オフセット補正を行なっていない。しかしながら、当然理解され得ることであるが、す

べての静的および動的なトポロジーの量子化器では通常、当該技術分野で公知の電流/電

圧または容量の補正に基づく入力換算電圧オフセット補正が行われ得る。

#### 【0031】

量子化器100は上述したようなフェーズの順に動作するので、利得が得られるフェー

50

ズが早いほど、入力換算 RMS ノイズおよび入力換算オフセット電圧の減少幅が大きくなる。したがって、量子化器動作の第 1 のフェーズにおける利得を増加させることによって、入力換算 RMS ノイズおよび入力換算オフセット電圧を減少させることができる。よって、RMS ノイズおよび電圧オフセットを減少させるためには、Avccrst を Avcc よりも高い値に調整するか、または単純に固定すればよい。

#### 【0032】

一方、clock-to-q を減少させてタイミングを改善するためには、Avccrst を Avcc よりも低い値に調整するか、または単純に固定すればよい。他の実現例によれば、Avccrst を、プロセス、電圧、および温度 (PVT) の組み合わせに追従する値に制御してもよい。これにより、量子化器のさまざまな動作条件にわたってタイミングを改善し、RMS ノイズおよび電圧オフセットを減少させることができる。

10

#### 【0033】

本開示の他の態様によれば、量子化器は、最小限の電力増加で入力コモンモード電圧 (Vcm) の増加分を補償することができる。これは、形状寸法に伴って電源電圧を規模縮小する場合に特に好都合である。一般的に、量子化器はアナログ信号処理とデジタル信号処理との境界に配置される。これは通常、その入力が、デジタル電源領域（例えば、Avcc）よりも高いアナログ電源領域から与えられることを意味する。この入力の平均は、コモンモード入力電圧、すなわち Vcm と呼ばれる。Vcm 値が高いと、利得が減少し、RMS ノイズおよびオフセット電圧が増加する。

#### 【0034】

プロセス技術が規模縮小すると、例えば信頼性の問題を緩和し、一定の処理性能に対するデジタル消費電力を低減し、または、一定もしくは低減した消費電力に対するデジタル処理性能を高めるために、デジタル電源も低減させる（例えば、0.85V から 0.75V）。このとき、アナログ電源は低減しないか、またはデジタル電源の低減幅よりも小さい幅だけ低減する。このことは、量子化器の Vcm が、量子化器の新たな低減 Avcc 値に対して実質的に増加したことを意味する。

20

#### 【0035】

このような状況においては、本開示にかかわらず、当業者には、現在のセンスアンプ（例えば、STRONGARM（登録商標）型）量子化器のトポロジーに関して、2つの選択肢しかないだろう。すなわち、利得の低下、ひいては RMS ノイズおよび電圧オフセットの増加を許容するか、または、量子化器利得を維持するために量子化器の電源を規模縮小しないかのいずれかである。しかしながら、後者の選択肢の場合、量子化器の消費電力の増大を許容しなければならず、従前の規模変更されていない Avcc レベルを生成するためには調整器を追加する必要があり、量子化器の出力を Avcc まで低下するようにレベル変更する必要がある。これに対して、本教示を採用することによって、Avccrst は、従前の規模変更されていない Avcc 電源電圧レベル（例えば、0.85V）を維持することができる。これによって利得が維持されるため、RMS ノイズおよびオフセット電圧が改善される。量子化器の残りの部分には、規模変更された Avcc レベル（例えば、0.75V）の電力が供給されることになる。

30

#### 【0036】

本開示によれば、所望の用途に応じて、Avccrst は固定であってもよいし、制御された態様で可変であってもよい。したがって、いくつかの実現例では、第 1 の電圧 (Avccrst) および第 2 の電圧 (Avcc) は互いにに対して相対的に固定されてもよい。必要に応じて、第 1 の電圧 (Avccrst) は第 2 の電圧 (Avcc) に比例してもよく、または第 2 の電圧 (Avcc) から導き出されてもよい。上述のように、第 1 の電圧 (Avccrst) を第 2 の電圧 (Avcc) よりも高くすることによって、量子化器回路におけるノイズおよび電圧オフセットを減少させてもよい。いくつかの実施形態では、上述のように、第 1 の電圧 (Avccrst) を第 2 の電圧 (Avcc) よりも低くすることによって、量子化器回路のタイミング性能を改善してもよい。

40

#### 【0037】

50

図2および図3はそれぞれ、本開示に係る他の実施形態である量子化器200および300を示す。量子化器200および300は「ダブルテール」型であり、それぞれ入力回路210および310を含む。各々の入力回路は、N0、N1、N2、N5、およびN6（N5およびN6は追加の利得を生じさせる）を含み、再生回路230、330は、N3、N4、P4、およびP5（回路300の場合、さらにN7およびN8）を含む。N7およびN8は、P0およびP1（図3）と協働して追加の利得を生じさせるが、簡略化のためにリセット回路の一部とみなすこともできる。

#### 【0038】

回路210、230の各々は別々の電流を有する。この別々の電流により、入力段階の利得と再生段階のタイミングとを別々に最適化することができる。具体的には、入力デバイス（N1、N2、N5、N6）は、再生デバイス（N3、N4、P4、P5）とは別の電流を有する。

10

#### 【0039】

図2の量子化器200が2相クロックを含むのに対して、図3の量子化器は単相クロックを含む。図3の実施形態は、ノードX1、X2からP0、P1、N7、N8を経由してout、outbに至る利得経路を追加的に含む。

#### 【0040】

入力回路210、310は、図1の実施形態と全く同じ方法で、入力を積分してノードX1およびX2に出力する。入力回路210、310は、入力デバイスN1およびN2が飽和している間は、入力251、252（351、352）から利得を生じさせる。しかしながら、Avccrstピンを追加することによって、図1の実施形態と同様に、初期電圧を増加させることができる。このような方法で初期開始電圧を増加させた場合、テール電流を減少させると事実上同じ効果が得られる。なぜなら、入力対N1、N2が飽和状態から抜けるまでにかかる時間が増加するからである。これによって、積分時間が増加するため、利得が増加してRMSノイズおよびオフセット電圧が減少する。

20

#### 【0041】

いくつかの実現例では、第2の電圧を接地とし、かつ、第1の電圧を第2の電圧よりも低くすることによって、量子化器回路におけるノイズおよび電圧オフセットを減少させてもよい。また、例えば、第2の電圧を接地とし、かつ、第1の電圧を第2の電圧よりも高くすることによって、量子化器回路のタイミング性能を改善してもよい。

30

#### 【0042】

限定ではなく例示のために、図4、図5、および図6は、本開示の他の実現例に係る量子化器400、500、600を示す。いくつかの実現例では、アナログ信号がデジタルビットに量子化される箇所で低入力コモンモード電圧（Vcm）を使用すると好都合な場合がある。この場合、量子化器は低入力Vcmとなる。本明細書で上述した量子化器100、200は、高入力Vcmに適したNMOS入力対を有している。上述の量子化器の各々を、高入力Vcm、NMOS入力対の量子化器から低入力Vcm、PMOS入力対の量子化器へ反転させてもよい。このような低入力Vcm回路では、リセット電圧をAvccから接地（Gnd）すなわちAvssに替える。ダブルテールラッチ型トポロジーの場合には、出力リセットを接地（Avss）からAvccに替える。図4、図5、および図6は、このような低入力Vcm、PMOS入力対の量子化器の3つのトポロジーを示す。すなわち、STRONGARM（登録商標）型技術（図4）、ダブルテールラッチ型トポロジー（図5）、および変形されたダブルテールラッチ型トポロジー（図6）である。

40

#### 【0043】

図4～図6の低入力Vcm、PMOS入力対の量子化器はすべて、図1～図3の実施形態と同じ方法で、入力回路（410、510、610）において入力を積分してノードX1およびX2に出力する。これらの実施形態の入力回路は、入力デバイスP1およびP2が飽和している間は、入力から利得を生じさせる。通常、このようなトポロジーでは、ドレインがリセットされてAvssとなり、次いで、コモンモード電流によってAvccの方へ引き上げられる。本開示によれば、ピンの追加によって初期電圧を減少させ、Avs

50

sではなくAvssrstを印加することができる。これにより、初期電圧Avssrstが接地(Avss)よりも低い電圧にまで減少するため、積分時間が増加し、利得が増加するとともに入力換算RMSノイズおよび入力オフセット電圧が減少する。一方、接地よりも高い電圧にまでAvssrstを増加させた場合には、積分時間が減少し、それによってclock-to-qが減少するため、タイミング性能が向上する。上述したのと同様に、Avssrstのレベルは固定してもよいし、または、入力換算RMSノイズおよび入力オフセット電圧の双方、および/またはタイミング性能を改善するように最適化された態様で、PVTに合わせて変動させてよい。

#### 【0044】

本開示の他の態様によれば、本開示に係る量子化器を動作させるために、AvccまたはAvssに対して第1の電圧の大きさを増加または減少させるように構成された制御回路の実施形態が提供される。

#### 【0045】

図7Aおよび図7Bに示すように、制御回路は、第1の電圧を表わす基準信号を生成するように構成されたアナログ制御回路700を含み得る。アナログ制御回路700と動作可能に通信する調整器710が設けられ得る。調整器710は、第1の電圧を表わす基準信号に応答して、量子化器回路に第1の電圧を出力するように構成され得る。アナログ制御回路は、複数の入力信号(702、704、Avcc、Vcm)に応答して基準信号(Vref\_reg)を生成し得る。入力信号は、第2の電圧の大きさ、プロセスに依存する電圧、温度に依存する電圧、またはシフト電圧のうちの少なくとも1つを示す信号を含み得る。図7Bは、図7Aの制御回路で使用される加算器の可能な実現例を示すが、当業者ならば、本開示に従って、電圧加算器および電流加算器の両方について、他のトポロジーの加算器を用いることも可能であろう。当然理解され得ることであるが、プロセスに依存する電圧および温度に依存する電圧の入力がAvcc(またはAvss)と共にプログラマブルスイッチまたは加算器706に与えられ得る。そうすると、その入力が回路720で処理されることによって基準電圧が生成され、この基準電圧は調整器に出力される。

#### 【0046】

処理回路720は演算増幅器を含む。この演算増幅器は、入力されるプロセスおよび温度に依存する電圧に応じて、Avccよりも高い、または低い電圧を出力する。したがって、入力されるプロセスおよび温度に依存する電圧を適切に選択することによって、基準電圧、すなわちAvccrstをAvccよりも高くしたり低くしたりすることができる。同様に、Avssを基準とする場合には、入力されるプロセスおよび温度に依存する電圧を選択することによって、AvssrstをAvssよりも高くしたり低くしたりすることができる。当然理解され得ることであるが、図7Aおよび図7B(本明細書中の他の図面も同様)は、限定ではなく例示を意図するものである。

#### 【0047】

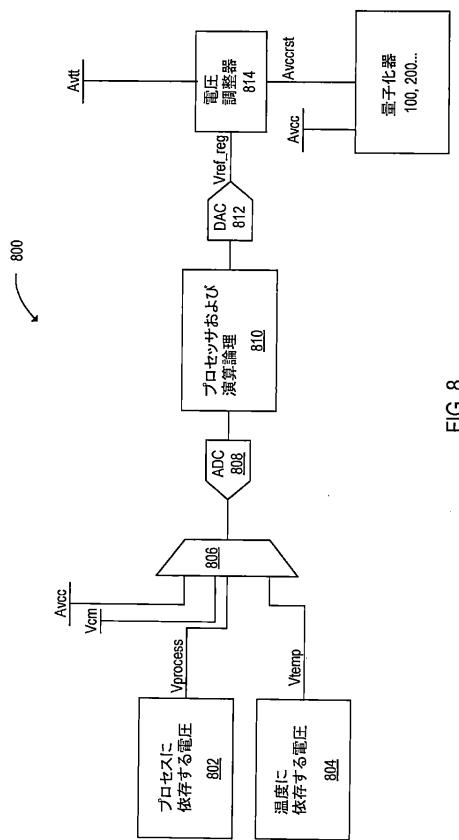

図8に示すように、いくつかの実現例では、制御回路800は、少なくとも1つのアナログ-デジタル変換器808を含み得る。この少なくとも1つのアナログ-デジタル変換器808は、複数の入力信号を受信し、デジタル入力信号データを生成するように構成されている。制御回路800はさらに、上記少なくとも1つのアナログ-デジタル変換器('ADC')808に動作可能に結合されたプログラマブル集積回路(810)を含み得る。このプログラマブル集積回路(810)は、デジタル入力信号データを処理することによって回路構成データを決定し、回路構成データデジタル出力信号を生成するように構成されている。制御回路800はさらに、プロセッサに動作可能に結合された少なくとも1つのデジタル-アナログ変換器(812)を含み得る。この少なくとも1つのデジタル-アナログ変換器は、回路構成データデジタル出力信号を、第1の電圧を表わす基準信号に変換するように構成され得る。

#### 【0048】

入力信号は、第2の電圧の大きさ、コモンモード電圧(Vcm)の大きさ、プロセスに依存する電圧802、温度に依存する電圧804、またはシフト電圧のうちの少なくとも

10

20

30

40

50

1つを示す信号を含み得る。図示のように、1つのA D Cおよびマルチプレクサでこれらの4つのアナログ入力を順次ポーリングし、選択されたアナログ入力信号からデジタルコードを生成してもよい。なお、ハードウェアの観点からコスト増大にはなるが、使用するA D Cの数を増やすこともできる。例えば、入力信号1つにつき1つのA D Cを用いて（例えば、合計4つ）、4つのデジタルコード（各々が入力信号に対応）を並列でプロセッサに送信することも可能である。

#### 【0049】

制御回路（800）は、上記少なくとも1つのデジタル・アナログ変換器（812）と動作可能に通信する調整器（814）をさらに含み得る。この調整器は、第1の電圧を表わす基準信号（Vref\_reg）に応答して、第1の電圧（Avccrst）を量子化器回路に出力するように構成され得る。さまざまな実施形態では、プログラマブル集積回路（810）は、構成データを決定するための実行可能コードでプログラムされてもよい。

10

#### 【0050】

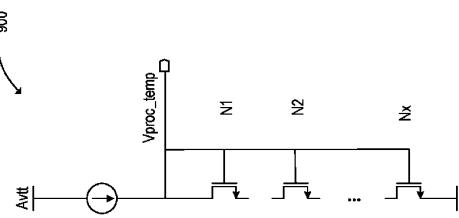

図9は、本開示に係る、アナログのプロセスおよび温度に依存する電圧を生成するための回路900を示す。アナログVref\_reg生成回路には、アナログのプロセスおよび温度に依存する電圧（Vproc\_temp）が必要である。ここでは、アナログのプロセスおよび温度に依存する電圧の生成の一実施形態を示す。図9に示すように、X個のN M O Sデバイスのスタックに電流が流される。デバイスの数Xは、必要なVproc\_tempを設定するように選択される。スタックのうちの一番上のデバイスは、回路（例えば、100）におけるN3/N4に対応し、Vtに追従するように選択され得る。それよりも下のデバイスは、i/pペータ（N1/N2）に対応し、gmに追従するように選択され得る。

20

#### 【0051】

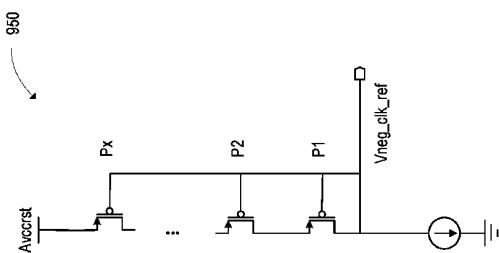

図10は、本開示に係る、クロック信号を発生させるクロック発生器を提供する調整器のためのローサイド基準を生成する回路950を示す。いくつかの実現例では、入力回路（例えば、110）は、経時変化する第2のクロック信号（clk\_hi）をさらに受信するように構成され得る。第2のクロック信号の大きさは、第1のクロック信号を基準として生成され得る。第2のクロック信号（clk\_hi）は、第1のクロック信号を示す信号を受信するように構成された回路によって生成され得る。この回路は、ローサイド基準電圧を受信するように構成された調整器から提供される。

30

#### 【0052】

A v c c r s t > A v c c の場合、量子化器において、PMOSであるリセットデバイスP2、P3は、A v c cではなくA v c c r s tの論理ハイレベルを有するクロック（clk\_hi）を必要とする。量子化器100のためのクロックバッファは、A v c cの論理ハイレベルを有するクロック（clkと呼ぶ）を生成する。clk\_hiは、本文献に記載される高速かつA Cに結合されたクロック発生器を用いて、clkから生成することができる。しかしながら、A v c c r s t > A v c cの場合、このクロックclk\_hiの論理ローレベルは、現代のCMOSプロセスではゼロボルトにはなり得ない。これにより、信頼性の問題が生じ得る。そこで、clk\_hi発生器に新たな論理ローレベルを設ける。本明細書では、これをVneg\_clk\_refと呼ぶ。これは、基準Vneg\_clk\_refを有する調整器によって生成される。しかしながら、A v c c r s t < A v c cを満たし、かつ最小値である場合、Vneg\_clk\_refの値は、A v c c r s tがA v s sに近づくのに伴って下方に変動するはずである。このようにするために、A v c c r s t電源を基準としてVneg\_clk\_refを生成する。この基準は、図10に示すPMOSデバイス（P1...Px）のスタック（量子化器におけるP2、P3に対応）として実現される。

40

#### 【0053】

本開示では、デバイス（100、200...）のバルク接続またはウェル接続についてさらに検討する。一般的に、PMOSデバイスのバルクは最も高い電圧源（通常、本明細書の図面に示すA v c c）に接続される。一般的に、NMOSデバイスのバルクは最も低い

50

電圧源（通常、本明細書の図面に示す  $A_{vss}$ ）に接続される。しかしながら、 $A_{vcrcs}$  および  $A_{vssrs}$  の追加は、必ずしも  $A_{vcrc}$  および  $A_{vss}$  がそれぞれ最も高い電圧源および最も低い電圧源であることを意味するものではない。 $A_{vcrcs}$  または  $A_{vssrs}$  に接続されたリセットデバイスを除いて、本明細書に開示されたすべての PMOS および NMOS のデバイスのバルク接続をそれぞれ  $A_{vcrc}$  および  $A_{vss}$  に保つのが最も簡単である。しかしながら、本開示によれば、すべての PMOS および NMOS のバルクをそれぞれ  $A_{vcrcs}$  または  $A_{vssrs}$  に接続することも可能である。 $A_{vcrcs}$  または  $A_{vssrs}$  から電源供給される PMOS および NMOS のリセットデバイスのバルク接続は、用途によって決まる。

#### 【0054】

10

現代の大容量 CMOS プロセスには、典型的には、電気的に絶縁された N ウェルを有する p 基板が用いられる。PMOS デバイスは N ウェル内にある。これらの N ウェルはさまざまな電位となることができ、1つまたは複数の正の電源電圧に接続される。NMOS デバイスは P ウェル内にあり、それらは p 基板から電気的に絶縁されていない。p 基板は、典型的にはゼロボルトに接続され、通常  $Gnd$  または  $A_{vss}$  として表わされる。

#### 【0055】

(a) 電気的に絶縁された p 基板アイランドを p 基板プロセスに作るための深い N ウェルによって、または (b) 電気的に絶縁された P ウェルを有する n 基板プロセスによって、 $A_{vssrs} < A_{vss}$  の使用が容易になると考えられる。

#### 【0056】

20

すべての PMOS / NMOS デバイスのバルクを  $A_{vcrcs}$  /  $A_{vssrs}$  に接続することが実現可能である。本明細書の例では、高 Vcm、NMOSi / p の量子化器において、すべての PMOS デバイスのバルクを  $A_{vcrcs}$  に接続することができる。また、低 Vcm、PMOSi / p の量子化器において、すべての NMOS デバイスのバルクを  $A_{vssrs}$  に接続することもできる。これにより、すべてのウェルが同電位となって配置密度を高めることができるため、有利な場合がある。しかしながら、上記両方の場合に不利な点は、依然としてソースが  $A_{vcrc}$  または  $A_{vss}$  であるすべての非リセットデバイスで  $Vt$  (ブレーナプロセス) が増加することである。 $A_{vcrcs}$  から電力供給される PMOS リセットデバイスのバルクの接続には、2つの基本的な選択肢がある。1つ目として、バルクを  $A_{vcrcs}$  に接続することが考えられる。2つ目として、バルクを  $A_{vcrc}$  に接続することが考えられる。同様に、NMOS リセットデバイスのバルクを  $A_{vssrs}$  または  $A_{vss}$  に接続することが考えられる。リセットデバイスのバルクを  $A_{vcrcs}$  /  $A_{vssrs}$  に接続した場合、電気的な安全性は向上する傾向にあるが、必要なスペースが増大する場合がある。これは、ソース電圧に対するバルクの値が非ゼロの場合に性能を損なう虞のある非 FinFET プロセスにとって、最善の接続であると考えられる。

30

#### 【0057】

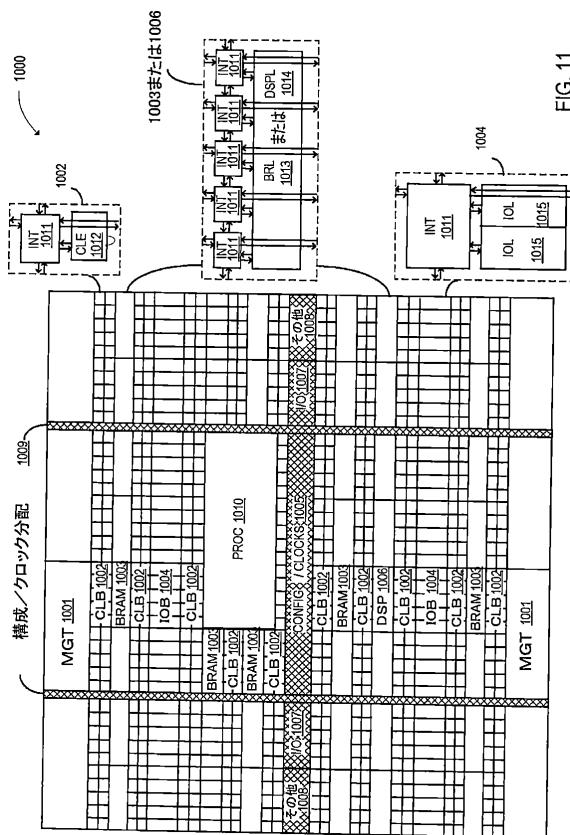

図 11 は、開示された回路およびプロセスをその上で実現し得るプログラマブル集積回路 (IC) 1000 を示す。プログラマブル IC はシステムオンチップ (SOC) と呼ばれる場合もあり、フィールドプログラマブルゲートアレイ論理 (FPGA) を、他のプログラマブルリソースと合わせて含む。FPGA 論理は、いくつかの異なる種類の配列されたプログラマブル論理ブロックを含み得る。例えば、図 11 が示すプログラマブル IC 1000 は、マルチギガビットトランシーバ (MGT) 1001、構成可能論理ブロック (CLB) 1002、ランダムアクセスメモリブロック (BRAM) 1003、入出力ブロック (IOB) 1004、構成およびクロッキング論理 (CONFIG / CLOCKS) 1005、デジタル信号処理ブロック (DSP) 1006、特殊入出力ブロック (I/O) 1007 (例えば、クロックポート)、ならびに、デジタルクロックマネージャ、アナログ - デジタル変換器、およびシステム監視論理などの他のプログラマブル論理 1008 を含む、多数の異なるプログラマブルタイルを含み得る。FPGA 論理を有するプログラマブル IC としては、さらに専用プロセッサブロック (PROC) 1010 ならびに内部

40

50

および外部の再構成ポート（図示せず）を含むものもある。

#### 【0058】

いくつかのFPGA論理において、各プログラマブルタイルはプログラマブルインターフェクト要素（INT）1011を含み、このインターフェクト要素は、隣接する各タイルにおける対応のインターフェクト要素との間の標準接続を有する。したがって、プログラマブルインターフェクト要素は、全体として図示のFPGA論理のプログラマブルインターフェクト構造を実現する。図11の上部に記載された例で示すように、プログラマブルインターフェクト要素INT1011は、同一のタイル内のプログラマブル論理要素との間の接続も有する。

#### 【0059】

例えば、CLB1002は、1つのプログラマブルインターフェクト要素INT1011に加えて、ユーザ論理を実現するようにプログラムされ得る構成可能論理要素CLE1012を含み得る。BRAM1003は、1つ以上のプログラマブルインターフェクト要素に加えてBRAM論理要素（BRL）1013を含み得る。通例、1つのタイルに含まれるインターフェクト要素の数は、タイルの高さによって決まる。図示の実現例では、BRAMタイルの高さはCLB5個分と等しいが、他の数（例えば4個）が用いられてもよい。DSPタイル1006は、適切な数のプログラマブルインターフェクト要素に加えて、DSP論理要素（DSDL）1014を含み得る。IOB1004は、例えば、プログラマブルインターフェクト要素INT1011の1つのインスタンスに加えて、入出力論理要素（IOL）1015の2つのインスタンスを含み得る。当業者には明らかであるが、例えば入出力論理要素1015に接続される実際のI/Oボンドパッドは、図示されたさまざまな論理ブロック上に金属を積層することによって製造され、典型的には入出力論理要素1015の領域にあるとは限らない。

10

#### 【0060】

図示の実現例では、ダイの中心付近の列領域（図11において陰影付きで示す領域）は、構成、クロック、および他の制御論理に用いられる。この列領域から延びる水平領域1009を用いて、プログラマブルICの幅にわたってクロックおよび構成信号を分配する。なお、「列」領域および「水平」領域という呼称は、図面を縦置きして見た向きを基準としている。

20

#### 【0061】

図11に示されるアーキテクチャを使用するプログラマブルICには、当該プログラマブルICの大部分を構成する規則正しい列構造に割って入る追加の論理ブロックが含まれる場合もある。この追加の論理ブロックは、プログラマブルブロックおよび/または専用論理であってもよい。例えば、図11に示されるプロセッサブロックPROC1010は、いくつかのCLBおよびBRAMのいくつかの列にまたがる。

30

#### 【0062】

なお、図11が意図するのは、プログラマブルICのアーキテクチャの一例にすぎない。1列中の論理ブロックの数、列の相対幅、列の数および順番、列に含まれる論理ブロックの種類、論理ブロックの相対サイズ、ならびに、図11の上部に記載されたインターフェクト/論理の実現例は、単なる例として示されている。例えば典型的には、ユーザ論理の効率的な実現を容易にするために、実際のプログラマブルICでは、CLBが現れる場合は必ず2列以上のCLBが隣接して設けられる。

40

#### 【0063】

本明細書で示したさまざまなフロー図に関して、ブロックの特定の順序および関連する機能は、例として提示されたものである。それらの順序は必ずしも限定するためのものではなく、さまざまな実現例に応じて変更可能である。

#### 【0064】

本明細書に開示された機能を実行し得るプロセスおよびデータ構造をホストするためには、さまざまな代替的なコンピューティング配列（プログラムコードを用いて構成される1つ以上のプロセッサおよびメモリの配列を含む）が好適な場合があるということを、当

50

業者ならば理解するであろう。さらに、プロセスは、磁気的もしくは光学的なディスクもしくはテープ、電子記憶装置、またはネットワークを介したアプリケーションサービスなどの、さまざまなコンピュータ可読記憶媒体または配信チャネルを介して提供することが可能である。

【 0 0 6 5 】

態様および特徴が別々の図に記載されている場合があるが、組み合わせが明示的に図示されていないとしても、または、組み合わせとして明示的に説明されていないとしても、ある図中の特徴を別の図中の特徴と組み合わせてもよいことが理解されるであろう。

【 0 0 6 6 】

上述の方法およびシステムは、RAM回路を用いるさまざまなシステムに適用可能であると考えられる。本明細書を考慮することによって、他の態様および特徴が当業者に明らかになるであろう。上述の方法およびシステムの一部は、ソフトウェアを実行するよう構成された1つ以上のプロセッサ、特定用途向け集積回路（ASIC）、またはプログラマブル論理デバイスの論理として実現されてもよい。さらに、本明細書で特定されたさまざまな回路は、共通のコンピュータ処理ユニットまたはデジタル処理ユニットを使用するなど、ハードウェア回路を共有してもよい。本明細書および図面は例示にすぎず、本発明の真の範囲は以下の特許請求の範囲によって示されるということが意図される。

10

20

30

40

50

【図面】

【図 1】

FIG. 1

【図 2】

FIG. 2

【図 3】

FIG. 3

【図 4】

FIG. 4

10

20

30

40

50

【図 5】

【図 6】

【図 7 A】

【図 7 B】

【図 8】

FIG. 8

【図 9】

FIG. 9

10

20

30

40

【図 10】

FIG. 10

【図 11】

FIG. 11

50

---

フロントページの続き

- (56)参考文献

- 特開2011-211371(JP,A)

再公表特許第2007/072588(JP,A1)

特開2000-114970(JP,A)

特開2010-109937(JP,A)

特開2013-187695(JP,A)

米国特許出願公開第2012/0119790(US,A1)

特開2013-183399(JP,A)

特開2012-227588(JP,A)

- (58)調査した分野 (Int.Cl., DB名)

- H03K 5/08

H03M 1/12

H03K 5/24

H03M 1/06