(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년08월23일

(11) 등록번호 10-1770877

(24) 등록일자 2017년08월17일

- (51) 국제특허분류(Int. Cl.)

*H01L 23/48* (2006.01) *H01L 23/522* (2006.01)

*H01L 25/07* (2006.01)

- (21) 출원번호 10-2013-7033346

- (22) 출원일자(국제) 2012년01월16일

심사청구일자 2016년12월15일

- (85) 번역문제출일자 2013년12월16일

- (65) 공개번호 10-2014-0039227

- (43) 공개일자 2014년04월01일

- (86) 국제출원번호 PCT/US2012/021416

- (87) 국제공개번호 WO 2013/002844

국제공개일자 2013년01월03일

- (30) 우선권주장

13/170,020 2011년06월27일 미국(US)

- (56) 선행기술조사문현

US20110073917 A1

JP2009194363 A

JP2004342724 A

- (73) 특허권자

자일링크스 인코포레이티드

미합중국 95124 캘리포니아 산 호세 로직 드라이브 2100

- (72) 발명자

라흐만 아리푸르

미국 캘리포니아 95124 산 호세 로직 드라이브 2100

- (74) 대리인

김태홍

전체 청구항 수 : 총 14 항

심사관 : 정구원

(54) 발명의 명칭 실리콘 관통 비아를 사용한 집적 회로 구조물

**(57) 요약**

집적 회로(IC) 구조물에서, 회로의 물리적 레이아웃과 관련하여 실리콘 관통 비아(TSV)를 배치하는 것이 기술되어 있다. IC 구조물은 복수의 제1 회로 요소(D1, G1, 및 S; 702, 706, 710, 및 714; 또는 702, 706, 704, 및 708); 복수의 제2 회로 요소(D2, G2, 및 S; 704, 708, 712, 및 716; 또는 710, 714, 712, 및 716); 복수의 제1 TSV(410 및 510; 605 내지 620; 또는 720 내지 734); 및 복수의 제2 TSV(415 및 505; 625 내지 640; 또는 736 내지 750)를 포함할 수 있다. 제1 및 제2 회로 요소와 제1 및 제2 TSV는 함께 회로 블록 구성을 구성한다. 회로 블록 구성을 적어도 하나의 대칭축에 대해 대칭이다. 제1 TSV를 중 적어도 하나는 더미 TSV(dummy TSV)이며, 이 더미 TSV가 없으면 회로 블록 구성이 대칭으로 되지 않을 것이다.

**대 표 도** - 도5

## 명세서

### 청구범위

#### 청구항 1

집적 회로(IC: integrated circuit) 구조물로서,

실리콘 웨이퍼;

상기 실리콘 웨이퍼 상에 구현되는 복수의 제1 회로 요소;

상기 실리콘 웨이퍼 상에 구현되는 복수의 제2 회로 요소;

상기 실리콘 웨이퍼의 제1 표면으로부터 상기 실리콘 웨이퍼의 제2 표면으로 연장되는 복수의 제1 실리콘 관통비아(TSV); 및

상기 실리콘 웨이퍼의 상기 제1 표면으로부터 상기 실리콘 웨이퍼의 상기 제2 표면으로 연장되는 복수의 제2 TSV를 포함하고,

상기 제1 및 제2 회로 요소와 상기 제1 및 제2 TSV는 함께 회로 블록 구성을 구성하며;

상기 회로 블록 구성은 적어도 하나의 대칭축에 대해 대칭이고;

상기 제1 TSV들 중 적어도 하나는 더미 TSV(dummy TSV)이며, 상기 더미 TSV가 없으면 상기 회로 블록 구성이 대칭으로 되지 않을 것이며, 상기 더미 TSV 및 상기 복수의 제2 TSV 중 하나는 상기 복수의 제1 회로 요소 중 하나로부터 등거리에 있는 것인, 집적 회로 구조물.

#### 청구항 2

제1항에 있어서, 상기 복수의 제1 회로 요소 및 상기 복수의 제2 회로 요소는 적어도 제1 능동 회로 요소를 포함하고;

상기 더미 TSV와 상기 제1 능동 회로 요소 사이의 거리는, 상기 더미 TSV가 상기 제1 능동 회로 요소의 응력장(stress field)에 기여하도록 결정되는 것인, 집적 회로 구조물.

#### 청구항 3

제1항에 있어서, 상기 회로 블록 구성은 2개의 대칭축에 대해 대칭인 것인, 집적 회로 구조물.

#### 청구항 4

제2항에 있어서, 상기 회로 블록 구성은 2개의 대칭축에 대해 대칭인 것인, 집적 회로 구조물.

#### 청구항 5

제1항에 있어서, 상기 제1 및 제2 복수의 TSV의 중심(centroid)의 위치는 상기 회로 블록 구성의 중심의 위치와 동일한 것인, 집적 회로 구조물.

#### 청구항 6

제2항에 있어서, 상기 제1 및 제2 복수의 TSV의 중심의 위치는 상기 회로 블록 구성의 중심의 위치와 동일한 것인, 집적 회로 구조물.

#### 청구항 7

제3항에 있어서, 상기 제1 및 제2 복수의 TSV의 중심의 위치는 상기 회로 블록 구성의 중심의 위치와 동일한 것인, 집적 회로 구조물.

#### 청구항 8

제4항에 있어서, 상기 제1 및 제2 복수의 TSV의 중심의 위치는 상기 회로 블록 구성의 중심의 위치와 동일한 것인, 접적 회로 구조물.

### 청구항 9

제1항 내지 제8항 중 어느 한 항에 있어서, 상기 IC 구조물은 인터포저(interposer)를 포함하는 것인, 접적 회로 구조물.

### 청구항 10

제1항 내지 제8항 중 어느 한 항에 있어서, 상기 제1 회로 요소는 적어도 제1 능동 회로 요소를 포함하고;

상기 제2 회로 요소는 적어도 제2 능동 회로 요소를 포함하며;

상기 제1 능동 회로 요소가 노출되어 있는 응력장 및 상기 제2 능동 회로 요소가 노출되어 있는 응력장은 상기 더미 TSV의 존재로 인해 동일한 것인, 접적 회로 구조물.

### 청구항 11

제10항에 있어서, 상기 제1 능동 회로 요소 및 상기 제2 능동 회로 요소는 함께 차동 트랜지스터 쌍(differential transistor pair)을 구성하는 것인, 접적 회로 구조물.

### 청구항 12

제10항에 있어서, 상기 제1 능동 회로 요소 및 상기 제2 능동 회로 요소는 클럭 분배 회로망의 상이한 노드에 결합되어 있는 것인, 접적 회로 구조물.

### 청구항 13

제10항에 있어서, 상기 접적 회로 구조물은 인터포저를 포함하는 것인, 접적 회로 구조물.

### 청구항 14

제1항에 있어서, 상기 적어도 하나의 더미 TSV는 접지되거나 전원에 연결되는 것인, 접적 회로 구조물.

### 청구항 15

삭제

## 발명의 설명

### 기술 분야

[0001] 본 명세서에 개시되어 있는 하나 이상의 실시예는 접적 회로(IC)에 관한 것이다. 보다 상세하게는, 하나 이상의 실시예는 실리콘 관통 비아(through silicon via)를 사용하여 IC를 설계하는 것에 관한 것이다.

### 배경 기술

[0002] 접적 회로(IC)는 다수의 다이를 사용하여 구현될 수 있다. 그렇지 않았으면 단일의 보다 큰 다이를 사용하여 구현될 회로 설계가 멀티 다이 IC 구조물(multi-die IC structure)을 사용하여 구현될 수 있다. 멀티 다이 IC 구조물은 통상적으로 서로 결합되어 있고 단일의 IC 패키지 내에 위치되어 있는 2개 이상의 다이를 포함하는 것을 특징으로 한다. 회로 설계는 단일의 보다 큰 다이를 가지는 IC 구조물을 사용하는 것 대신에 다수의 다이에 걸쳐 구현된다.

[0003] 멀티 다이 IC 구조물을 사용하여 회로 설계를 구현하기 위해, 회로 설계는 멀티 다이 IC 구조물의 다이들에 걸쳐 분할되어야만 한다. 분할 프로세스는 회로 설계의 회로 요소들을 멀티 다이 IC 구조물의 다양한 다이들에 할당한다. 분할 프로세스는 필연적으로 하나 이상의 다이간 신호(inter-die signal)를 발생한다. 다이간 신호는 멀티 다이 IC 구조물의 상이한 다이들 간에 교환되는 신호를 말한다.

[0004] 다이들 간의 그리고 다이들로부터 IC 패키지로의 통신을 설정하는 한가지 방식은 "TSV(through silicon via, 실리콘 관통 비아)"라고 하는 구조를 이용하는 것이다. 각각의 TSV는 멀티 다이 IC 구조물의 다이를 통해 뻗어

있는 수직 전도성 경로라고 할 수 있다. 각각의 TSV는 다이(이 다이를 관통하여 TSV가 뻗어 있음)의 상부 표면 상의 노드를 동일한 다이의 하부 표면 상의 상이한 노드와 전기적으로 결합시키기 위해 사용될 수 있다. 예를 들어, TSV는 TSV를 포함하는 제2 다이의 위쪽에 위치해 있는 제1 다이의 노드를 제2 다이의 아래쪽에 위치해 있는 제3 다이의 노드 또는 제2 다이의 아래쪽에 위치해 있는 IC 패키지의 노드와 결합시키기 위해 사용될 수 있다.

### 발명의 내용

[0005]

집적 회로(IC) 구조물에서, 주어진 다이 상의 회로의 물리적 레이아웃과 관련하여 TSV를 배치하는 것은 회로 설계의 회로 블록들의 향상된 동작 특성을 달성할 수 있다. 일 실시예에서, IC 구조물은 복수의 제1 회로 요소; 복수의 제2 회로 요소; 복수의 TSV; 및 복수의 제2 TSV를 포함한다. 제1 및 제2 회로 요소와 제1 및 제2 TSV는 함께 회로 블록 구성을 구성한다. 회로 블록 구성을 적어도 하나의 대칭축에 대해 대칭이다. 제1 TSV를 중 적어도 하나는 더미 TSV(dummy TSV)이며, 이 더미 TSV가 없으면 회로 블록 구성이 대칭으로 되지 않을 것이다.

[0006]

어떤 실시예들에서, 복수의 제1 회로 요소 및 복수의 제2 회로 요소는 적어도 제1 능동 회로 요소를 포함하고; 더미 TSV와 제1 능동 회로 요소 사이의 거리는 더미 TSV가 제1 능동 요소의 응력장(stress field)에 기여할 정도로 충분히 작다.

[0007]

회로 블록 구성을 2개의 대칭축에 대해 대칭일 수 있다. 제1 및 제2 복수의 TSV의 중심(centroid)의 위치는 회로 블록 구성을 중심의 위치와 동일할 수 있다. 제1 능동 회로 요소는 제1 및 제2 복수의 TSV 내의 적어도 하나의 TSV의 종래의 제한 구역(Keep Out Zone) 내에 있을 수 있다. IC 구조물은 인터포저(interposer)를 포함할 수 있다.

[0008]

어떤 실시예들에서, 제1 회로 요소는 적어도 제1 능동 회로 요소를 포함하고; 제2 회로 요소는 적어도 제2 능동 회로 요소를 포함한다. 제1 능동 회로 요소가 노출되어 있는 응력장 및 제2 능동 회로 요소가 노출되어 있는 응력장은 더미 TSV의 존재로 인해 실질적으로 동일하다.

[0009]

제1 능동 회로 요소 및 제2 능동 회로 요소는 함께 차동 트랜지스터 쌍(differential transistor pair)을 구성할 수 있다. 제1 능동 회로 요소 및 제2 능동 회로 요소는 고성능 클럭 분배 회로망의 상이한 노드에 결합되어 있을 수 있다.

[0010]

TSV를 사용하는 집적 회로 설계 방법이 또한 기술되어 있다. 이 방법은, 프로세서를 사용하여, 회로 블록의 제1 능동 회로 요소가 노출되어 있는 응력장과 회로 블록의 제2 능동 회로 요소가 노출되어 있는 응력장이 일치하지 않는 것으로 판정하는 단계를 포함할 수 있다. 이 방법은 TSV에 대한 다이의 레이아웃을 수정함으로써 제1 능동 회로 요소의 응력장과 제2 능동 회로 요소의 응력장 사이의 불일치를 감소시키는 단계를 포함할 수 있다.

[0011]

한 측면에서, 불일치를 감소시키는 단계는 TSV의 위치를 조절하는 단계를 포함할 수 있고, 여기서 TSV는 제1 능동 회로 요소 또는 제2 능동 회로 요소 중 어느 하나의 능동 회로 요소의 응력장에 기여한다. 예를 들어, TSV의 위치를 조절하는 단계는 TSV의 위치를 조절하여 대칭적 TSV 및 회로 블록 구성을 생성하는 단계를 포함할 수 있다.

[0012]

다른 측면에서, 불일치를 감소시키는 단계는 제1 능동 회로 요소로부터 소정의 거리 내에 더미 TSV를 부가하는 단계를 포함할 수 있다. 예를 들어, 더미 TSV를 부가하는 단계는 더미 TSV를 부가하여 대칭적 TSV 및 회로 블록 구성을 생성하는 단계를 포함할 수 있다. 다른 예에서, 더미 TSV를 부가하는 단계는 더미 TSV를 부가하여 제1 능동 회로 요소의 응력장과 중복하는 부가의 응력장을 발생하는 단계를 포함할 수 있다.

[0013]

제1 능동 회로 요소가 노출되어 있는 응력장과 제2 능동 회로 요소가 노출되어 있는 응력장이 일치하지 않는 것으로 판정하는 단계는 TSV에 대한 회로 블록의 대칭에 따라 불일치를 판정하는 단계를 포함할 수 있다. 그에 부가하여 또는 다른 대안으로서, 제1 능동 회로 요소가 노출되어 있는 응력장과 제2 능동 회로 요소가 노출되어 있는 응력장이 일치하지 않는 것으로 판정하는 단계는 TSV와 제1 능동 회로 요소 및 제2 능동 회로 요소 사이의 거리에 따라 불일치를 판정하는 단계를 포함할 수 있다.

[0014]

다른 실시예는 TSV를 사용하는 회로 설계 시스템을 포함할 수 있다. 본 시스템은 프로그램 코드를 가지는 메모리, 및 메모리에 결합되어 있는 프로세서를 포함할 수 있다. 프로세서는, 프로그램 코드를 실행할 시에, 복수의 동작들을 수행하도록 구성되어 있을 수 있다. 이 동작들은 회로 블록의 제1 능동 회로 요소가 노출되어 있는 응력장 및 회로 블록의 제2 능동 회로 요소가 노출되어 있는 응력장이 일치하지 않는 것으로 판정하는 동작, 및 TSV에 대한 다이의 레이아웃을 수정함으로써 제1 능동 회로 요소의 응력장과 제2 능동 회로 요소의 응력장

사이의 불일치를 감소시키는 동작을 포함할 수 있다.

[0015] 불일치를 감소시키는 동작은 TSV의 위치를 조절하는 동작을 포함할 수 있고, 여기서 TSV는 제1 능동 회로 요소 또는 제2 능동 회로 요소 중 어느 하나의 능동 회로 요소의 응력장에 기여한다. 예를 들어, TSV의 위치를 조절하는 동작은 TSV의 위치를 조절하여 대칭적 TSV 및 회로 블록 구성을 생성하는 동작을 포함할 수 있다.

[0016] 그에 부가하여 또는 다른 대안으로서, 불일치를 감소시키는 동작은 제1 능동 회로 요소로부터 소정의 거리 내에 더미 TSV를 부가하는 동작을 포함할 수 있다. 예를 들어, 더미 TSV를 부가하는 동작은 대칭적 TSV 및 회로 블록 구성을 생성하는 더미 TSV를 부가하는 동작을 포함할 수 있다. 다른 예에서, 더미 TSV를 부가하는 동작은 더미 TSV를 부가하여 그에 의해 제1 능동 회로 요소의 응력장과 중복하는 부가의 응력장을 발생하는 동작을 포함할 수 있다.

[0017] 제1 능동 회로 요소가 노출되어 있는 응력장과 제2 능동 회로 요소가 노출되어 있는 응력장이 일치하지 않는 것으로 판정하는 동작은 회로 블록 및 TSV의 대칭에 따라 불일치를 판정하는 동작을 포함할 수 있다. 그에 부가하여 또는 다른 대안으로서, 제1 능동 회로 요소가 노출되어 있는 응력장과 제2 능동 회로 요소가 노출되어 있는 응력장이 일치하지 않는 것으로 판정하는 동작은 TSV와 제1 능동 회로 요소 및 제2 능동 회로 요소 사이의 거리에 따라 불일치를 판정하는 동작을 포함할 수 있다.

[0018] 다른 실시예는 프로세서 및 메모리를 가지는 시스템에 의해 사용가능한 비일시적 데이터 저장 매체를 포함하는 디바이스를 포함할 수 있다. 데이터 저장 매체는, 시스템에 의해 실행될 때, 시스템으로 하여금 동작들을 실행하게 하는 프로그램 코드를 저장할 수 있다. 이 동작들은 회로 블록의 제1 능동 회로 요소가 노출되어 있는 응력장 및 회로 블록의 제2 능동 회로 요소가 노출되어 있는 응력장이 일치하지 않는 것으로 판정하는 동작, 및 TSV에 대한 다이의 레이아웃을 수정함으로써 제1 능동 회로 요소의 응력장과 제2 능동 회로 요소의 응력장 사이의 불일치를 감소시키는 동작을 포함할 수 있다.

[0019] 불일치를 감소시키는 동작은 TSV의 위치를 조절하는 동작을 포함할 수 있고, 여기서 TSV는 제1 능동 회로 요소 또는 제2 능동 회로 요소 중 어느 하나의 능동 회로 요소의 응력장에 기여한다. TSV의 위치를 조절하는 동작은 TSV의 위치를 조절하여 대칭적 TSV 및 회로 블록 구성을 생성하는 동작을 포함할 수 있다. 불일치를 감소시키는 동작은 제1 능동 회로 요소로부터 소정의 거리 내에 더미 TSV를 부가하는 동작을 포함할 수 있다.

### 도면의 간단한 설명

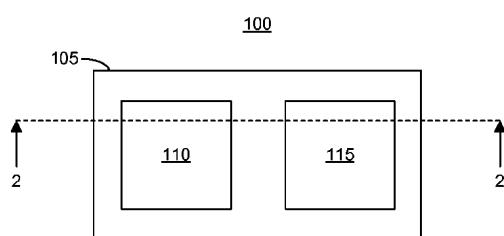

[0020] 도 1은 본 명세서 내에 개시되어 있는 일 실시예에 따른 멀티 다이 집적 회로(IC) 구조물의 토포그래픽 뷰 (topographic view)를 나타낸 제1 블록도.

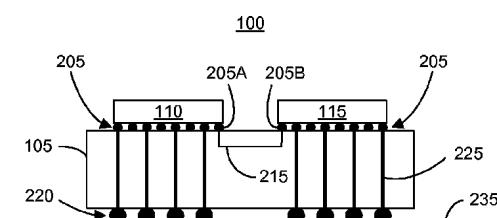

도 2는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 멀티 다이 IC 구조물의 측단면도를 나타낸 제2 블록도.

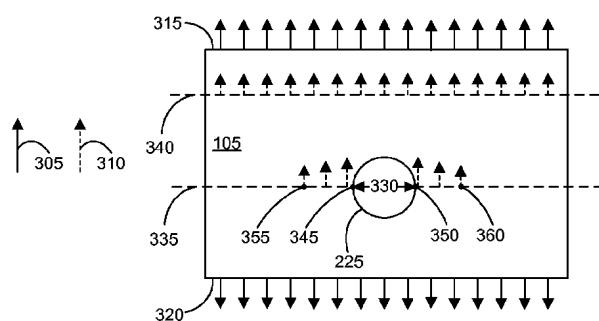

도 3은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 실리콘 관통 비아(TSV)를 둘러싸고 있는 멀티 다이 IC 구조물 내에서의 응력의 예시적인 효과를 나타낸 제3 블록도.

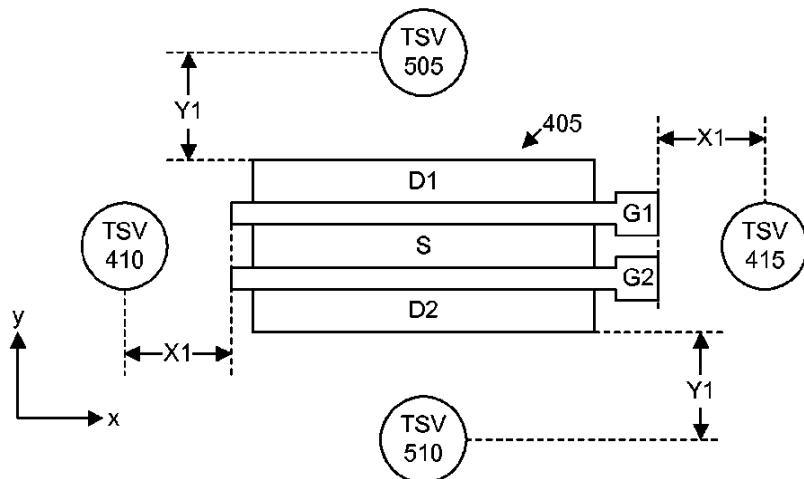

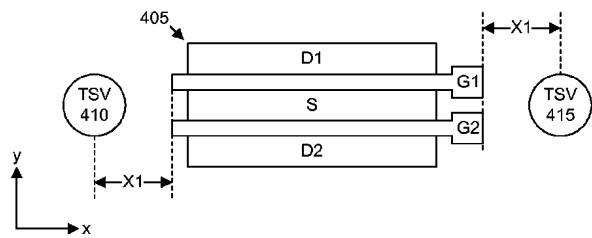

도 4는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 차동 트랜지스터 쌍의 토포그래픽 레이아웃 뷰 (topographical, layout view)를 나타낸 제4 블록도.

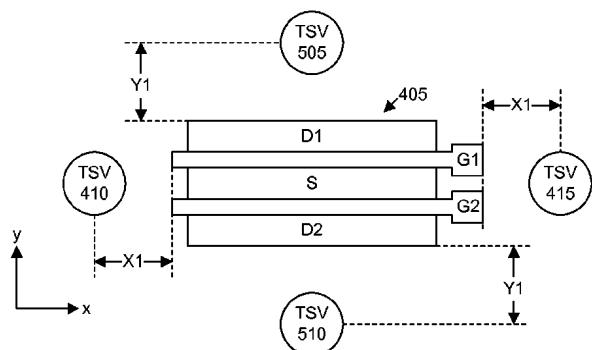

도 5는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 차동 트랜지스터 쌍의 토포그래픽 레이아웃 뷰를 나타낸 제5 블록도.

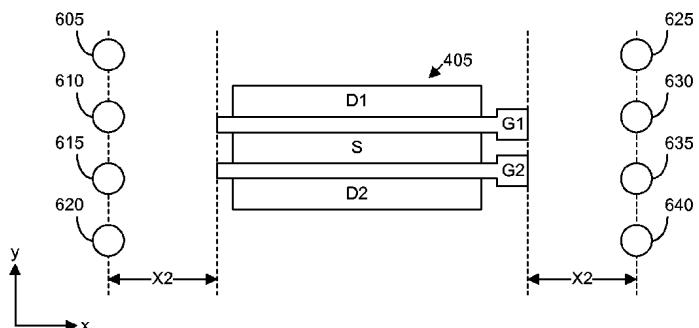

도 6은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 차동 트랜지스터 쌍의 토포그래픽 레이아웃 뷰를 나타낸 제6 블록도.

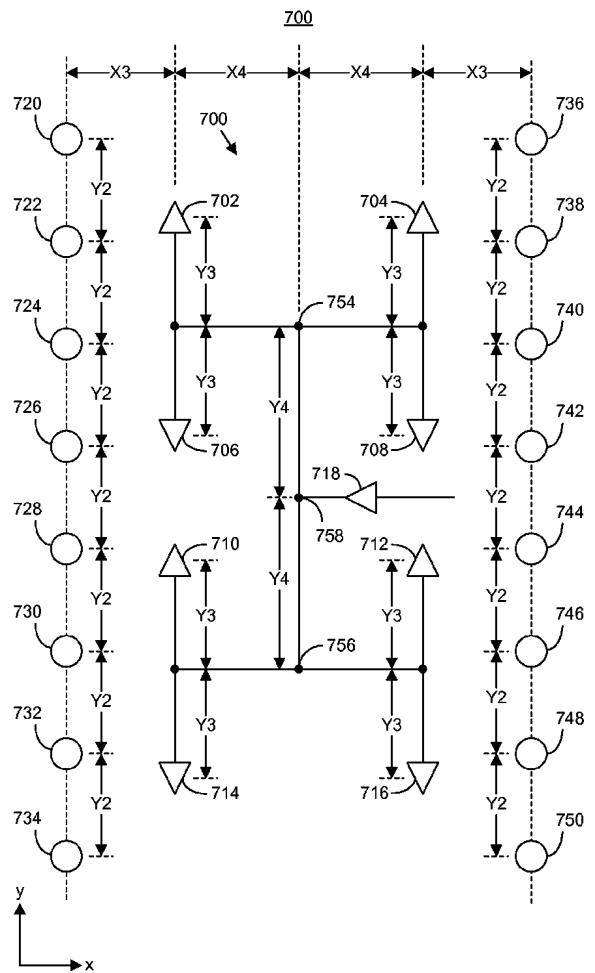

도 7은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 클럭 회로망의 토포그래픽 레이아웃 뷰를 나타낸 제7 블록도.

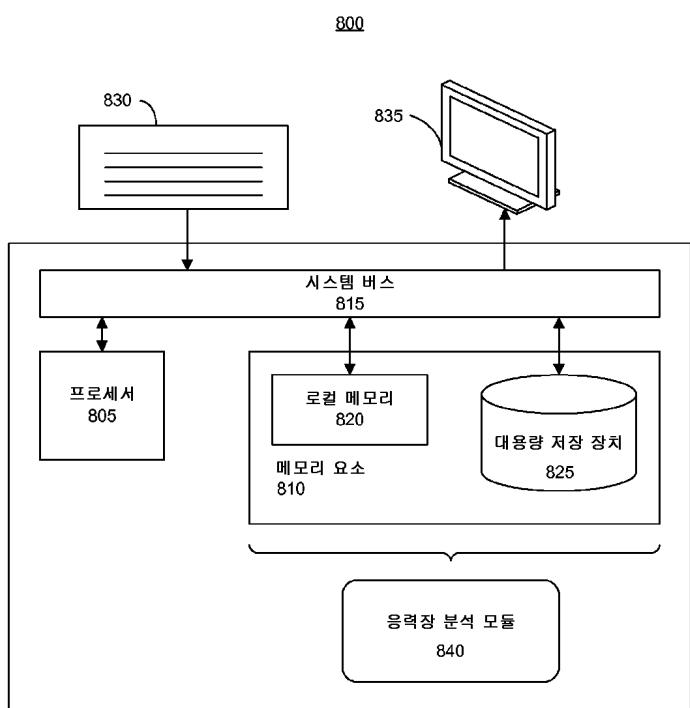

도 8은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 예시적인 컴퓨팅 시스템을 나타낸 제8 블록도.

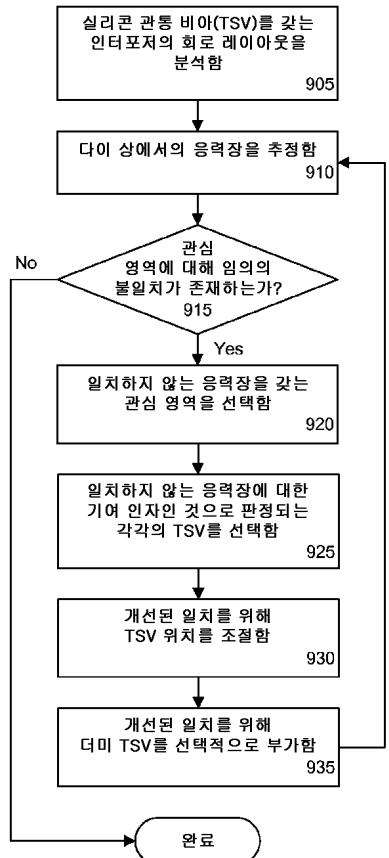

도 9는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 TSV를 사용하여 IC를 설계하는 방법을 나타낸 플로우 차트.

### 발명을 실시하기 위한 구체적인 내용

- [0021] 본 명세서가 신규한 것으로 간주되는 하나 이상의 실시예의 특징들을 한정하는 청구항으로 종결되어 있지만, 도면과 관련한 설명을 고려하면 하나 이상의 실시예가 더 잘 이해될 것으로 생각된다. 필요에 따라, 하나 이상의 상세한 실시예가 본 명세서 내에 개시되어 있다. 그렇지만, 하나 이상의 실시예가 단지 예시적인 것임을 잘 알 것이다. 따라서, 본 명세서 내에 개시되어 있는 구체적인 구조 및 기능 상세가 제한하는 것이 아니라 단지 청구항에 대한 기초로서 그리고 당업자에게 거의 모든 적절히 상세한 구조로 하나 이상의 실시예를 다양하게 이용하도록 가르쳐 주기 위한 대표적인 기초로서 해석되어야 한다. 게다가, 본 명세서에서 사용되는 용어 및 문구가 제한하기 위한 것이 아니라, 오히려 본 명세서에 개시되어 있는 하나 이상의 실시예의 이해가능한 설명을 제공하기 위한 것이다.

- [0022] 본 명세서 내에 개시되어 있는 하나 이상의 실시예는 집적 회로(IC)에 관한 것으로서, 보다 상세하게는, 실리콘 관통 비아(TSV)를 사용하여 IC를 설계하는 것에 관한 것이다. IC 내에 TSV를 사용하거나 포함시키는 것은 그 안에 구현되어 있는 회로의 성능에 영향을 미칠 수 있다. TSV를 포함시키는 것은, 예를 들어, TSV가 구현되어 있는 특정의 다이 내에 응력장을 유발하거나 발생할 수 있다. TSV에 의해 유발되는 응력장은 능동 회로 요소 그리고 따라서, 확장에 의해, 트랜지스터 등의 능동 회로 요소를 사용하여 구성된 보다 복잡한 회로 또는 회로 블록의 성능에 영향을 미칠 수 있다. 예를 들어, 능동 회로 요소에 근접해 있는 TSV에 의해 유발되는 응력장에 의해 영향을 받는 능동 회로 요소의 성능은, TSV가 없는 능동 회로 요소의 성능과 비교하여, 통상적으로 상이하고 열화된다.

- [0023] 본 명세서에 개시되어 있는 하나 이상의 실시예에 따르면, 주어진 다이 상의 회로의 물리적 레이아웃(레이아웃)과 관련하여 하나 이상의 TSV의 배치 또는 위치는 회로 설계의 회로 블록들의 향상된 동작 특성을 달성하도록 결정될 수 있다. 예를 들어, 전자 회로 내의 구성 블록으로서 일상적으로 사용되는 차동 트랜지스터 쌍 등의 회로 블록의 성능은 하나 이상의 TSV의 존재 또는 근접성에 의해 영향을 받을 수 있다. 회로 블록의 각각의 능동 회로 요소의 하나 이상의 선택된 동작 특성이 TSV 또는 TSV들에 의해 유발된 응력장에 의해 균일하게 영향을 받도록 하기 위해, 회로 블록을 둘러싸고 있는 주어진 영역 내에 위치해 있는 하나 이상의 TSV의 배치가 조절될 수 있다.

- [0024] 예를 들어, 회로 블록의 차동 트랜지스터 쌍 유형과 관련한 TSV의 특정의 배치의 결과, 그 회로 블록의 각각의 트랜지스터는 TSV의 응력장에 의해 실질적으로 균일한 방식으로 영향을 받을 수 있다. 이와 같이, 회로 블록의 구동 전류 및 지연 등의 특성은, 경우에 따라, TSV 또는 TSV들의 존재에 의해 대체로 영향을 받지 않은 채로 있을 수 있는데, 그 이유는 회로 블록의 개개의 능동 회로 요소의 동작에 영향을 미칠 수 있는 TSV(들)에 의해 유발된 응력장이 동일하거나 유사한 방식으로 각각의 이러한 능동 회로 요소에 영향을 미치기 때문이다.

- [0025] 도 1은 본 명세서 내에 개시되어 있는 일 실시예에 따른 멀티 다이 IC 구조물(IC 구조물)(100)의 토포그래피 뷰를 나타낸 제1 블록도이다. 한 측면에서, IC 구조물(100)은 단일의 패키지 내에 IC의 다수의 다이를 적층하는 팩킹 방식(packing approach)을 나타내고 있다. IC 구조물(100)은 실리콘 인터포저(인터포저)(105), 다이(110), 및 다이(115)를 포함할 수 있다.

- [0026] 인터포저(105)는 다이들(105 및 110)이 수평으로 적층될 수 있는 평면 표면을 가지는 다이일 수 있다. 도시된 바와 같이, 다이들(105 및 110)이 인터포저(105)의 평면 표면 상에 나란히 위치될 수 있다. 도 1에서 2개의 수평으로 적층된 다이들로 구현되어 있지만, IC 구조물(100)은 또한 3개 이상의 다이들이 수평으로 적층되는 것에 의해 구현될 수 있다. 다른 실시예에서, 다이(115)는 다이(110)의 상부에 수직으로 적층될 수 있다. 또 다른 실시예에서, 인터포저(105)는 2개의 수직으로 적층된 다이들 사이의 중간층으로서 사용될 수 있다. 그 경우에, 인터포저(105)는 멀티 다이 IC 패키지 내에서 수직으로 적층된 다이들을 서로 격리시킬 수 있다.

- [0027] 인터포저(105)는 멀티 다이 IC 구조물의 2개 이상의 다이에 대한 공통의 실장 표면(mounting surface) 및 전기적 결합점(electrical coupling point)을 제공할 수 있다. 인터포저(105)는 다이들 사이의 상호연결 배선(interconnect routing)을 위한 중간층으로서 또는 IC 구조물(100)에 대한 접지 또는 전원 평면으로서 역할할 수 있다. 인터포저(105)는 N형 및/또는 P형 불순물로 도핑되어 있거나 도핑되어 있지 않은 실리콘 웨이퍼 기판으로 구현될 수 있다. 인터포저(105)의 제조는 하나 이상의 금속 상호연결층(들)의 중착을 가능하게 해주는 하나 이상의 부가의 공정 단계를 포함할 수 있다. 이를 금속 상호연결층은 알루미늄, 금, 구리, 니켈, 다양한 실리사이드 등을 포함할 수 있다.

- [0028] 인터포저(105)는, 예를 들어, 이산화 실리콘 등의 하나 이상의 유전체 또는 절연층(들)의 중착을 가능하게 해주는 하나 이상의 부가의 공정 단계를 사용하여 제조될 수 있다. 그에 부가하여, 인터포저(105)는, 예를 들어, 트랜지스터 디바이스 및/또는 다이오드 디바이스 등의 능동 회로 요소의 생성을 가능하게 해주는 하나 이상의

부가의 공정 단계를 사용하여 제조될 수 있다. 언급한 바와 같이, 인터포저(105)는, 일반적으로, 다이이고 하나 이상의 TSV의 존재를 특징으로 하며, 이에 대해서는 본 명세서 내에서 더 상세히 기술할 것이다.

[0029] 도 2는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 멀티 다이 IC 구조물의 측단면도를 나타낸 제2 블록 도이다. 보다 상세하게는, 도 2는 절단선 2-2를 따라 절취한 도 1의 IC 구조물(100)을 나타낸 도면이다. 그에 따라, 본 명세서 전체에 걸쳐 동일한 항목들을 가리키기 위해 유사한 번호들이 사용될 것이다.

[0030] 도 2를 참조하면, 각각의 다이(110 및 115)는 솔더 범프(205)를 통해 인터포저(105)에 전기적으로 결합될 수 있다. 그에 부가하여, 각각의 솔더 범프(205)는 다이(110 및 115)를 인터포저(105)에 물리적으로 부착시키는 역할을 할 수 있다. 예를 들어, 솔더 범프(205)를 통해, 인터포저(105)는 다이(110)에 결합되어 있다. 이와 유사하게, 솔더 범프(205)를 통해, 다이(115)는 인터포저(105)에 결합되어 있다.

[0031] 다이(110 및 115)를 인터포저(105)에 결합시키는 것이 솔더 범프(205)를 통해 달성되지만, 인터포저(105)를 다이(110 및 115)에 결합시키기 위해 각종의 다른 기법들이 사용될 수 있다. 예를 들어, 다이(110 및 115)를 인터포저(105)에 결합시키기 위해 본드 와이어(bond wire) 또는 에지 와이어(edge wire)가 사용될 수 있다. 다른 예에서, 다이(110 및 115)를 인터포저(105)에 물리적으로 부착시키기 위해 접착제가 사용될 수 있다. 그에 따라, 도 2에 예시된 바와 같이, 솔더 범프(205)를 통해 다이(110 및 115)를 인터포저(105)에 결합시키는 것은 예시를 위해 제공되어 있으며, 본 명세서 내에 개시되어 있는 하나 이상의 실시예를 제한하기 위한 것은 아니다.

[0032] 인터포저(105) 내의 상호연결 물질은 다이(110)와 다이(115) 사이에서 다이간 신호를 전달하는 데 사용될 수 있다. 예를 들어, 상호연결부(215)는 다이(110)를 다이(115)에 결합시키기 위해 각각의 솔더 범프(205A 및 205B)에 결합될 수 있고, 그에 의해 다이(110)와 다이(115) 사이에서의 다이간 신호의 교환을 가능하게 해준다. 그에 부가하여, 인터포저(105)는 비아(도시 생략)에 의해 서로 결합될 수 있는 다수의 전도성층으로 구현될 수 있다. 그 경우에, 상호연결부(215)는 인터포저(105) 내의 비아를 사용하여 서로 결합되어 있는 2개 이상의 전도성층으로 구현될 수 있다. 인터포저(105) 내에 상호연결부를 구현하기 위해 다수의 전도성층을 사용하는 것은 인터포저(105) 내에서 보다 많은 수의 신호가 라우팅될 수 있게 해주고 보다 복잡한 신호 라우팅이 달성될 수 있게 해준다.

[0033] 본 명세서 내에서, 단자, 신호 라인, 배선, 및 그의 대응하는 신호를 참조하는 데 동일한 참조 문자가 사용된다. 이와 관련하여, "신호", "와이어", "연결", "단자" 및 "핀"이라는 용어가 본 명세서 내에서 때때로 서로 바꾸어 사용될 수 있다. 또한, "신호", "와이어" 등의 용어가 하나 이상의 신호(예컨대, 단일 와이어를 통한 단일 비트의 전달 또는 다수의 평행한 와이어를 통한 다수의 병렬 비트의 전달)를 나타낼 수 있다는 것을 잘 알 것이다. 게다가, 각각의 와이어 또는 신호는, 경우에 따라, 신호 또는 와이어에 의해 연결되어 있는 2개 이상의 구성요소 사이의 양방향 통신을 나타낼 수 있다.

[0034] 솔더 범프(220)는 인터포저(105)를 표면(235)에 전기적으로 결합시키기 위해 사용될 수 있다. 표면(235)은, 예를 들어, IC 구조물(100)이 구현되어 있는 멀티 다이 IC 패키지를 나타낼 수 있다. 솔더 범프(220)는 또한 IC 구조물(100)을 멀티 다이 IC 패키지의 외부에 있는 노드에 직접 결합시킬 수 있다. 예를 들어, 솔더 범프(220)는 인터포저(105)를 표면(235)에 물리적으로 부착시키기 위해 사용될 수 있다. TSV(225)는, 전도성 물질로 채워질 때, 수직으로 지나가는[예컨대, 인터포저(105)의 전체는 아니지만 상당 부분을 통해 뻗어 있는] 전기적 연결을 형성하는 비아를 나타낸다.

[0035] TSV(225)는 제1 평면 표면[즉, 솔더 범프(205)가 결합되어 있는 표면]으로부터 제2 평면 표면[즉, 솔더 범프(220)가 결합되어 있는 표면]으로 쭉 뻗어 있는 개구부를 인터포저(105) 내에 드릴링 또는 에칭함으로써 구현될 수 있다. 전도성 물질이 이어서 TSV(225) 내에 중착될 수 있다. TSV(225)를 채우는 데 사용될 수 있는 전도성 물질의 예는 구리, 알루미늄, 금, 구리, 니켈, 다양한 실리사이드 등을 포함할 수 있지만, 이들로 제한되지 않는다. 다른 예에서, TSV(225)는 솔더 범프(220)를 상호연결부(215)를 형성하기 위해 사용되는 하나 이상의 금 속층과 결합시키기 위해 실질적으로 인터포저(105)를 관통하여 지나갈 수 있다. 상호연결부(215) 및 하나 이상의 종래의 비아는 이어서 TSV(225)를 솔더 범프(205)에 결합시킬 수 있다.

[0036] TSV(225)는, 솔더 범프(220)와 결합하여, 다이(110)를 표면(235)에 결합시킨다. 언급한 바와 같이, 인터포저(105) 내에 능동 회로 요소를 구현하기 위해 하나 이상의 부가의 공정 단계가 사용될 수 있다. 일반적으로, 멀티 다이 IC 구조물에 의해, 상호연결부 및 TSV를 둘러싸고 있는 부분들을 비롯하여 실리콘 인터포저의 큰 섹션이 사용되지 않은 채로 있다. 본 명세서에 개시되어 있는 하나 이상의 실시예에 따르면, 트랜지스터 및 다이오드 등의 능동 회로 요소가 인터포저(105)의 사용되지 않은 부분 내에 구현될 수 있다.

- [0037] 이와 같이, 도 2에 도시된 바와 같이, 인터포저(105)의 제1 평면 표면은 다이(110 및 115)에 물리적으로 결합될 수 있다. 인터포저(105)의 제2 평면 표면은 표면(235)에 물리적으로 결합될 수 있다. 각각의 다이(110 및 115) 및 표면(235)은 인터포저(105)와 비교하여 상이한 열 팽창 계수를 가질 수 있는 물질을 사용하여 구현될 수 있다. 그 결과, 인터포저(105), 다이(110 및 115) 및 표면(235) 각각은 온도의 변화에 노출될 때 상이한 비율로 팽창할 수 있다.

- [0038] 시스템 내에 구현될 때, 인터포저(105), 다이(110 및 115), 및 표면(235)을 포함하는 IC 패키지는 IC 패키지의 외부의 온도의 변화에 의해 영향을 받을 수 있다. 그에 부가하여, 전원이 켜진 상태에서, IC 구조물(100) 내의 회로 요소는 인터포저(105), 다이(110 및 115), 및 표면(235)의 온도를 변경시킬 수 있는 열을 발생할 수 있다. 온도의 변화의 결과, 인터포저(105), 다이(110 및 115), 및 표면(235) 각각의 연속적인 팽창 및 수축이 일어날 수 있다.

- [0039] 다이(110 및 115) 및 표면(235) 각각이 인터포저(105)와 상이한 열 팽창 계수를 가질 수 있기 때문에, 각각은 인터포저(105)와 상이한 비율로 팽창 및 수축할 수 있다. 다이(110 및 115) 및 표면(235) 각각이 인터포저(105)에 물리적으로 결합되어 있는 경우, 인터포저(105), 다이(110 및 115) 및 표면(235) 사이의 상이한 팽창 및 수축 비율의 결과, 각자의 구성요소에 힘이 가해진다. 이 힘은 TSV(225) 등의 인터포저(105)를 관통하는 개구부를 둘러싸는 영역에서 증가할 수 있는 응력을 인터포저(105) 내에 생성할 수 있다.

- [0040] 그에 부가하여, TSV(225)를 채우는 데 사용되는 전도성 물질은 인터포저(105)와 상이한 열 팽창 계수를 가질 수 있다. 그 경우에, 각각의 TSV(225)를 채우는 데 사용되는 전도성 물질은 인터포저(105)와 상이한 비율로 팽창 및 수축할 수 있다. 그 결과로서, 전도성 물질은 TSV(225)의 내부로부터 인터포저(105)에 부가의 힘을 가할 수 있고, 그에 의해 TSV(225)를 둘러싸는 인터포저(105)의 영역에 가해지는 응력을 추가로 증가시킨다.

- [0041] 도 3은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 TSV를 둘러싸고 있는 멀티 다이 IC 인터포저 내에서의 응력의 예시적인 효과를 나타낸 제3 블록도이다. 보다 상세하게는, 도 3은 인터포저(105) 등의 멀티 다이 IC 인터포저에 힘이 가해지는 결과, 응력이 가해지고 응력장이 발생될 수 있는 방식을 나타낸 것이다. 도 3은 TSV(225) 등의 TSV를 둘러싸는 영역에 응력이 집중되는 방식을 나타낸 것이다.

- [0042] 앞서 기술한 바와 같이, 인터포저(105)를 하나 이상의 다이 및 IC 패키지에 물리적으로 결합시키는 것에 의해, 인터포저(105)에 힘이 가해질 수 있다. TSV(225) 내의 전도성 물질에 의해 또한 인터포저(105)에 힘이 가해질 수 있다. 이 힘은 인터포저(105)를 구현하는 데 사용되는 물질 내에 응력을 생성할 수 있다. 일반적으로, 이 응력은 TSV(225) 등의 인터포저(105)를 관통하는 임의의 개구부를 둘러싸고 있는 인터포저(105)의 영역 내에서 그리고 그 주변에서 증가된다.

- [0043] 어떻게 힘이 인터포저(105) 내에 응력장을 유발하는지를 더 잘 예시하기 위해, 도 3은 단축 힘(uni-axial force)이 인터포저(105)에 가해지는 1차원 경우를 나타낸 것이다. 실제로는, 인터포저(105)의 배치를 정의하는 3개의 직교 축을 따라 또는 이들 사이에 배향되어 있을 수 있는 인터포저(105)에 3차원 힘이 가해질 수 있다. 이와 관련하여, TSV(225)에 의해 유발되는 응력장은 라인(225)을 따라 바깥쪽으로 뻗어 있는 것으로 제한되지 않고 오히려 TSV(225)에 대해 모든 방향으로 바깥쪽으로 뻗어 있을 수 있다. 도 3이 축척대로 그려져 있지 않다는 것을 잘 알 것이다. 도 3은 TSV(225) 등의 TSV 주위에 유발될 수 있는 응력을 보다 명확하게 나타내도록 그려져 있다.

- [0044] 도 3을 참조하면, 가장자리(315 및 320)를 따라 인터포저(105)에 단축 힘이 가해진다. 인터포저(105)에 힘이 인가되는 것은 인터포저(105)를 구현하는 데 사용되는 물질 내에 인장 응력(tensile stress)을 발생한다. 인터포저(105)의 가장자리의 영역에 가해지는 힘은 각각의 화살표(305)로 예시되어 있다. 인터포저(105) 내에 존재하는 인장 응력은 각각의 화살표(310)로 예시되어 있다. 각각의 화살표(305)의 배향 및 길이는, 각각, 인터포저(105)의 가장자리(315 및 320)에 가해지는 힘의 방향 및 크기를 나타낸다. 이와 유사하게, 각각의 화살표(310)의 배향 및 길이는, 각각, 인터포저(105)의 다양한 영역 내에 발생되는 응력의 방향 및 크기를 나타낸다.

- [0045] 인터포저(105)에 힘이 인가될 때, 물질 내의 임의의 불연속부[예컨대, TSV(225)]는 불연속부를 둘러싸는 영역에서의 응력 집중(stress concentration) 또는 응력장에 영향을 미친다. 그 결과로서, TSV(225)는 TSV(225)를 둘러싸는 인터포저(105)의 영역에서의 응력을 증가시킨다. 도 3을 참조하면, TSV(225)는 전도성 물질로 채워지고 직경(330)을 가지는 원형 개구부로서 구현된다.

- [0046] 인터포저(105) 내에 TSV(225)의 존재에 의해 유발되는 응력은 일반적으로 TSV(225)에 대한 개구부의 가장자리에 집중되고 TSV(225)로부터 멀어지는 쪽으로 이동할 때 라인(335)을 따라 감소한다. 환연하면, 인터포저(105)에

가해지는 힘의 방향에 수직인 TSV(225)를 대칭으로 양분하는 축을 따라[즉, 이 경우에, 직경(330)을 따라] 인터포저(105) 내에서 응력이 최대화된다. 일반적으로, 직경(330)에 평행하지만 직경(330)의 아래쪽에 또는 그 위쪽에 있는 인터포저(105)의 영역에서, 응력은 정규화된 방식으로 분포되어 있다. 예를 들어, 인터포저(105) 내에서 라인(340)을 따라 있는 응력의 크기는 정규화되고 균일하게 분포된 응력으로 되돌아간다.

$$\sigma_3 = \sigma_1 \left( 1 + \frac{2b}{a} \right)$$

[0047] 일반적으로, TSV(225)의 가장자리를 따라 있는 점들에서의 인장 응력 집중은 수식  $\frac{2b}{a}$  으로 나타내어질 수 있다.  $\sigma_3$ 에 대한 수식 내에서,  $\sigma_1$ 은, 예를 들어, 라인(340)을 따라 인터포저(105) 내에서의 균일한 또는 평균 인장 응력을 나타낸다. 변수  $a$ 는 힘의 방향에 평행한 TSV(225)의 반경이다. 변수  $b$ 는 힘의 방향에 수직인 TSV(225)의 반경이다. TSV(225) 등의 실질적으로 원형인 TSV의 경우,  $a$ 의 길이는  $b$ 의 길이와 대

략 같다. 이와 같이, 수식  $\frac{2b}{a}$  은 2의 값으로 되고,  $\sigma_3 = 3\sigma_1$ 이다.  $\sigma_3$ 에 대한 수식은 점(345 및 350)에서의 인장 응력 집중(즉,  $\sigma_3$ )이 평균 인장 응력의 대략 3배라는 것을 나타낸다. 일반적으로  $K_t$ 로서 표시되는 "응력 집중 인자(stress concentration factor)"라는 표현은  $K_t = \sigma_3 / \sigma_1 = 3$ 로서 정의된다.

[0048] 인터포저(105) 내에 증가된 응력이 존재한다는 것은 인터포저(105) 내에 구현되는 능동 회로 요소의 성능에 영향을 미칠 수 있다. 예를 들어, 응력은 인터포저(105) 내의 능동 회로 요소 내에 캐리어 이동도(carrier mobility)의 변동을 야기할 수 있다. TSV(225)에 의해 유발된 응력장을 말하는 응력의 집중이 인터포저(105) 내에서 라인(335)을 따라 TSV(225)를 둘러싸는 영역에서 보다 큰 것으로 간주할 때, 라인(335)을 따라 위치해 있는 능동 디바이스의 성능이 TSV(225)에 의해 유발된 증가된 응력 집중의 결과로서 변할 수 있다.

[0049] 살펴본 바와 같이, 도 3은 가장자리(315 및 320)를 따라 인터포저(105)에 가해지는 단축 힘만을 나타내고 있다. 살펴본 바와 같이, TSV(225)에 의해 발생되거나 유발되는 실제의 응력장은 모든 방향에서 바깥쪽으로 뻗어 있다. 응력 집중이 평균 인장 응력 레벨에 도달할 때까지 TSV(225)로부터 멀어지는 쪽으로 이동함에 따라 응력장의 집중이 감소한다. 일반적으로, 응력 집중 또는 레벨은 1/D의 비율로 감소되고, 여기서 "D"는 TSV(225)의 외주(perimeter)로부터의 거리를 나타낸다. 예를 들어, TSV(225)에 의해 유발되는 응력장의 응력 레벨은 TSV(225)로부터 멀어지는 쪽으로 이동하면서 점(355 및 360)에서 정규화된 인장 응력 레벨을 감소시킨다.

[0050] 종래의 설계 기법은 능동 회로 요소에 대한 TSV-유발 응력의 영향을 감소시키기 위해 제한 구역(Keep Out Zone, KOZ)의 개념을 이용한다. 능동 회로 요소에 의한 응력 관련 성능 문제를 피하기 위해 능동 회로 요소가 위치되거나 구현되어서는 안되는, TSV를 둘러싸고 있는 인터포저(105) 등의 다이 내의 특정의 영역을 정의하는 KOZ가 통상적으로 지정된다. 그렇지만, TSV의 수가 증가할 때, 각각의 TSV의 주위에 정의된 많은 KOZ는 능동 회로 요소를 구현하기 위한 다이의 사용가능 영역을 상당히 감소시킬 수 있다. 더욱이, 2개 이상의 TSV로부터의 응력장의 중첩은 TSV-유발 응력을 완전히 제거하는 것의 어려움을 증가시킬 수 있다.

[0051] 어떤 경우에, KOZ는 구동 전류 등과 같은 능동 회로 요소의 하나 이상의 동작 특성의 열화에 따라 정의된다. 이러한 방식으로, KOZ는 외주에서 끝나는 것으로 정의되고, 외주를 벗어나서는 그 위치에 구현되는 능동 회로 요소의 선택된 동작 특성이 (TSV가 존재하지 않는 경우와 비교하여) 소정의 양 또는 퍼센트만큼 열화되거나 전혀 열화되지 않는다. 그렇지만, 능동 회로 요소의 동작 특성의 열화의 척도를 사용하는 것은 여전히 TSV-유발 응력이 회로 블록의 하나의 능동 회로 요소에, 동일한 회로 블록의 다른 능동 회로 요소와 상이한 방식으로, 영향을 미칠 수 있는 상황을 야기할 수 있다.

[0052] 예를 들어, 차동 트랜지스터 쌍의 경우를 생각해보자. 양 트랜지스터가 용인된 공차 범위 내에서 동작함에도 불구하고, 주어진 TSV에 의해, 쌍의 하나의 트랜지스터는 쌍의 다른 트랜지스터와 상이한 방식으로 영향을 받을 수 있다. 이와 유사하게, 통상적으로 입/출력 회로용으로 이용되는 풀업(pull-up) 및/또는 풀다운(pull-down) 회로 내에서 사용되는 트랜지스터는 주어진 TSV에 의해 상이한 방식으로 영향을 받을 수 있다. 다른 예로서, 고성능 클럭 분배 회로망의 상이한 노드들은 하나 이상의 TSV에 의해 상이한 방식으로 영향을 받을 수 있고, 그에 의해 고성능 클럭 분배 회로망의 노드들 간의 성능의 변동이 발생한다. 이를 변동은 회로 설계가 설계 목표를 충족시키지 않는 또는 회로 설계의 실제 성능이, 설계 목표를 충족시킴에도, 예상된 것과 상이하게 동작하는 상황을 야기할 수 있다.

[0053] 예시에서, 회로 설계가 TSV 및 사전 제조된 회로 블록을 포함하는 멀티 다이 IC 구조물 내에 구현되어야 하는

경우를 생각해보자. 사전 제조된 회로 블록을 포함하는 어떤 IC는 지정된 기능을 수행하도록 프로그램될 수 있고, 한 예는 FPGA(field programmable gate array)이다. FPGA는 통상적으로 프로그램가능 타일들의 어레이를 포함한다. 이들 프로그램가능 타일은, 예를 들어, IOB(input/output block), CLB(configurable logic block), BRAM(dedicated random access memory block), 곱셈기, DSP(digital signal processing block), 프로세서, 클록 관리자, DLL(delay lock loop) 등을 포함할 수 있다.

[0054] 각각의 프로그램가능 타일은 통상적으로 프로그램가능 상호연결 회로(programmable interconnect circuitry) 및 프로그램가능 논리 회로(programmable logic circuitry) 둘 다를 포함한다. 프로그램가능 상호연결 회로는 통상적으로 능동 회로 요소를 포함할 수 있는 PIP(programmable interconnect point)에 의해 상호연결된 다양한 길이의 많은 수의 상호연결 라인을 포함한다. 프로그램가능 논리 회로는 역시 능동 회로 요소를 포함할 수 있는, 예를 들어, 함수 발생기, 레지스터, 산술 논리 등을 포함할 수 있는 프로그램가능 요소를 사용하여 사용자 설계의 논리를 구현한다.

[0055] 프로그램가능 상호연결 회로 및 프로그램가능 논리 회로는 통상적으로 프로그램가능 요소가 어떻게 구성되는지를 정의하는 구성 데이터의 스트림을 내부 구성 메모리 셀에 로드함으로써 프로그램된다. 구성 데이터는 외부 장치에 의해 메모리로부터(예를 들어, 외부 PROM으로부터) 판독되거나 FPGA에 기록될 수 있다. 그러면, 개별 메모리 셀의 전체적 상태가 FPGA의 기능을 결정한다.

[0056] FPGA는 한 유형의 프로그램가능 IC에 불과하다. 다른 유형의 프로그램가능 IC는 CPLD(Complex Programmable Logic Device, 복합 프로그램가능 논리 장치)이다. CPLD는 상호연결 스위치 매트릭스에 의해 서로에 또한 입/출력(I/O) 리소스에 연결된 2개 이상의 "기능 블록"을 포함한다. CPLD의 각각의 기능 블록은 PLA(programmable logic array, 프로그램가능 논리 어레이) 및 PAL(programmable array logic, 프로그램가능 어레이 논리) 장치에서 사용되는 것과 유사한 2-레벨 AND/OR 구조를 포함한다. CPLD에서, 구성 데이터는 통상적으로 칩 상의 비휘발성 메모리에 저장된다. 일부 CPLD에서, 구성 데이터는 칩 상의 비휘발성 메모리에 저장되고, 이어서 초기 구성(프로그래밍) 시퀀스의 일부로서 휘발성 메모리에 다운로드된다.

[0057] 이들 프로그램가능 IC 모두에 대해, 그 목적을 위해 장치에 제공된 데이터 비트에 의해 장치의 기능이 제어된다. 데이터 비트는 휘발성 메모리(예를 들어, FPGA 및 일부 CPLD에서와 같이, 정적 메모리 셀)에, 비휘발성 메모리(예를 들어, 일부 CPLD에서와 같이 플래시 메모리)에, 또는 임의의 다른 유형의 메모리 셀에 저장될 수 있다.

[0058] 다른 프로그램가능 IC는 장치 상의 다양한 요소를 프로그램가능하게 상호연결시키는 금속층 등의 처리층을 적용함으로써 프로그램된다. 이들 프로그램가능 IC는 마스크 프로그램가능 장치라고 한다. 프로그램가능 IC는 또한 다른 방식으로, 예컨대, 퓨즈 또는 앤티퓨즈 기술을 사용하여 구현될 수 있다. "프로그램가능 IC"라는 용어는 이들 장치(이들로 제한되지 않음)를 포함할 수 있고, 또한 단지 부분적으로 프로그램가능한 장치를 포함할 수 있다. 예를 들어, 한 유형의 프로그램가능 IC는 하드-코딩된 트랜지스터 논리(hard-coded transistor logic) 및 하드-코딩된 트랜지스터 논리를 프로그램가능하게 상호연결시키는 프로그램가능 스위치 패브릭(programmable switch fabric)의 조합을 포함한다. 다른 유형의 프로그램가능 IC는 프로그램가능 회로를 포함하는 ASIC(application-specific IC)일 수 있다.

[0059] 어쨌든, 프로그램가능 IC 내에 TSV가 존재하는 것이 2개의 동일한 회로 블록으로 하여금, 단지 하나 이상의 TSV와 관련한 각자의 회로 블록 각각의 위치 및 각각의 이러한 TSV에 의해 발생되는 응력장으로 인해, 상이한 방식으로 기능하게 할 수 있다는 것을 잘 알 것이다. 유사하거나 동일한 회로 블록의 이러한 상이한 또는 불균일한 성능은 회로 설계자에 문제가 될 수 있고 멀티 다이 프로그램가능 IC 내에 회로 설계를 신뢰성 있게 구현하는 것을 어렵게 만들 수 있다.

[0060] TSV 또는 2개 이상의 TSV에 의해 유발되는 응력장은 각종의 상이한 기법들 중 임의의 것을 사용하여 결정될 수 있다. 한 측면에서, 주어진 IC 패키지에 대해 힘 및 발생된 응력의 전역적 분석이 수행될 수 있다. 힘은 추정 또는 측정될 수 있고, 발생된 응력장은 수학적으로 전개될 수 있다. 응력장은, 예를 들어, IC 패키지의 단일의 다이 내에서 수학적으로 모델링될 수 있다. 다이에 걸쳐 개별 능동 회로 요소 레벨에서 적용가능한 마이크로 모델(micro model)을 제공하기 위해 IC 패키지에 대해 개발된 매크로 모델(macro model)이 적용되고 세분될 수 있다. 하나 이상의 상이한 능동 회로 요소에 가해지는 개별 TSV로부터의 응력장을 추정하기 위해, 예를 들어, 전체 인터포저에 걸쳐 응력의 국소적 효과가 평가될 수 있다. 한 측면에서, 각각의 능동 회로 요소와 TSV 사이의 거리는, 그 능동 회로 요소가 영향을 받는 TSV에 의해 유발된 응력장을 평가하거나 결정하는 데, 사용될 수 있다.

- [0061] 다른 측면에서, 능동 회로 요소에 대해, TSV 및/또는 능동 회로 요소의 다양한 구성으로 구성되어 있는 테스트 구조물로부터 측정되는 바와 같이 경험적 데이터가 결정될 수 있다. 능동 회로 요소의 포화 전류 등의 능동 회로 요소의 다양한 동작 특성이 측정될 수 있다. 측정된 동작 특성은 능동 회로 요소의 물리적 특성(예를 들어, TSV 위치와 비교한 능동 회로 요소의 배향, 능동 회로 요소의 길이, 능동 회로 요소가 N형 디바이스인지 P형 디바이스인지 등)과 상관될 수 있다. 실제의 실리콘 프로토타입 구조물로부터 측정된 데이터는 IC 설계 시뮬레이션 및/또는 최적화를 위해 사용될 수 있는 모델을 발생하는 데 사용될 수 있다.

- [0062] 도 4는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 차동 트랜지스터 쌍(차동 쌍)의 토포그래픽 레이아웃 뷰를 나타낸 제4 블록도이다. "레이아웃"은 IC 구조물 또는 그의 일부분을 IC의 디바이스들을 구성하는 금속층, 산화물 영역, 확산 영역, 또는 기타 층을 패턴화하는 설계 마스크에 대응하는 평면 기하 형상들로 표현한 것을 말하는 것일 수 있다. 도 4는 차동 쌍(405)을 예시하고 있다. 차동 쌍(405)은 제1 트랜지스터 및 제2 트랜지스터를 포함하고 있다. 제1 트랜지스터는 드레인(D1), 게이트(G1), 및 제2 트랜지스터와 공유되는 소스(S)로 형성되어 있다. 차동 쌍(405)의 제2 트랜지스터는 드레인(D2), 게이트(G2), 및 소스(S)로 형성되어 있다.

- [0063] 차동 쌍(405)은 2개의 TSV(410 및 415) 사이에 위치해 있다. 예시를 위해, TSV(410) 및 TSV(415)는 실질적으로 유사하거나 동일한 형상으로 구현될 수 있고, 실질적으로 동일한 크기로 되어 있을 수 있다. 예를 들어, 원형 TSV로서 구현될 때, TSV(410) 및 TSV(415)는 실질적으로 동등한 직경을 가질 수 있다. 참조를 위해 2차원 좌표계가 예시되어 있다. TSV(410 및 415), 드레인(D1 및 D2), 소스(S), 및 게이트(G1 및 G2) 등의 구성요소는, 예를 들어, 도시된 2차원 좌표계에 대응하는 (x,y) 형태의 좌표를 할당받을 수 있다.

- [0064] 도시된 바와 같이, TSV(410)는 차동 쌍(405)으로부터 X1의 거리에 위치해 있다. TSV(410)가 실질적으로 소스(S)와 정렬되어 있기 때문에[예컨대, y축 상에서 TSV(410)의 중앙이 소스(S)의 중앙과 정렬되어 있음], TSV(410)는 차동 쌍(405)의 제1 및 제2 트랜지스터로부터 같은 거리에 있다. 그에 따라, 차동 쌍(405)의 제1 및 제2 트랜지스터 각각은 TSV(410)에 의해 유발되는 바로 그 응력장에 노출된다. 이와 관련하여, TSV(410)에 의해 유발된 것과 같이, 제1 트랜지스터가 노출되는 응력장이 제2 트랜지스터가 노출되는 응력장과 일치한다.

- [0065] 이와 유사하게, TSV(415)도 차동 쌍(405)으로부터 X1의 거리에 위치해 있다. TSV(415)는 실질적으로 소스(S)와 정렬되어 있고, 따라서 차동 쌍(405)의 제1 트랜지스터 및 제2 트랜지스터로부터 같은 거리에 있다. 그에 따라, 차동 쌍(405)의 제1 및 제2 트랜지스터 각각은 TSV(415)에 의해 유발되는 바로 그 응력장에 노출된다. 이와 관련하여, TSV(415)에 의해 유발된 것과 같이, 제1 트랜지스터가 노출되는 응력장이 제2 트랜지스터가 노출되는 응력장과 일치한다.

- [0066] 차동 쌍(405)의 제1 및 제2 트랜지스터는, 각각의 트랜지스터가 실질적으로 동일한 방식으로 그리고 실질적으로 동일한 양으로 TSV(410 및 415)로부터 유발되는 응력 효과에 의해 열화될 가능성이 있다는 점에서, 정합된 채로 있다. 이와 같이, 제1 트랜지스터 및 제2 트랜지스터가 크기 등의 면에서 일치하는 물리적 특성을 가지는 것으로 가정하면, 각각은, TSV(410 및 415)의 존재에도 불구하고, 동일하거나 유사한 방식으로 동작할 것으로[예컨대, 동일하거나 유사한 동작 특성을 가질 것으로] 예상될 수 있다. 트랜지스터 쌍(405)의 제1 트랜지스터 및 제2 트랜지스터 둘 다는, TSV(410 및 415)의 존재 및/또는 근접에도 불구하고, 계속 정합될 것이다.

- [0067] 일 실시예에서, TSV에 의해 전달되는 특정의 유형의 신호는 그 TSV에 의해 유발되는 응력장의 면에서 무시될 수 있다. 예를 들어, 다시 도 4를 참조하면, TSV(410)는 회로 설계의 신호, 전압원, 또는 접지를 전달하거나 그에 결합될 수 있다. TSV(410)에 의해 유발되는 응력장은, TSV(410)가 신호, 전원, 또는 접지에 결합되어 있는지에 상관없이, 본 명세서 내에서 기술된 바와 같이 결정될 수 있다.

- [0068] 예시를 위해, 각각의 TSV 구조물의 중앙으로부터의 거리가 측정될 수 있다. 거리 측정이 주어진 회로 블록 및 그 회로 블록을 둘러싸고 있는 TSV(들)에 대해 균일한 방식으로 행해지는 한, 바람직한 경우, 각각의 TSV 구조물의 외주(outer perimeter)로부터의 거리도 측정될 수 있다.

- [0069] TSV(410)가 차동 쌍(405)으로부터 TSV(415)와 상이한 거리에 위치해 있을 수 있다는 것을 잘 알 것이다. 각각의 TSV(410 ALC 415)가 차동 쌍(405)의 제1 및 제2 트랜지스터를 일치된 응력장의 영향을 받게 하기 위해, (예컨대, 이 경우, 차동 쌍(405)의 각각의 트랜지스터는 각각의 TSV로부터 동일한 또는 실질적으로 유사한 응력 효과를 경험함), TSV(410 및 415)는 소스(S)를 양분하는 수평선을 따라 위치해 있어야 한다.

- [0070] 도 5는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 차동 트랜지스터 쌍의 토포그래픽 레이아웃 뷰를 나타낸 제5 블록도이다. 보다 상세하게는, 도 5는 차동 쌍(405)을 예시하고 있다. 도시된 바와 같이, 각각의

TSV(410 및 415)는, 도 4를 참조하여 기술한 바와 같이, 차동 쌍(405)으로부터 X의 거리에 위치해 있다.

[0071] 각각의 TSV(505 및 510)의 배치 및 차동 쌍(405)의 배향으로 인해, 각각의 TSV(505 및 510)는 x축에 대해 정렬되어 있을 수 있다(예컨대, 동일한 x 좌표를 가짐). 그에 부가하여, TSV(505)는 차동 쌍(405)의 가장자리로부터 Y1의 거리에 위치해 있다. 이와 유사하게, TSV(510)도 차동 쌍(405)의 가장자리로부터 Y1의 동일한 거리에 위치해 있다. 차동 쌍(405)의 제1 및 제2 트랜지스터를 정합된 능동 회로 요소로서 구현함으로써, TSV(505) 및 TSV(510)가 소스(S)를 실질적으로 양분하는 y 좌표를 갖는 수평선으로부터 같은 거리에 있을 수 있다는 것을 잘 알 것이다. 각각의 TSV(410, 415, 505 및 510)는 실질적으로 동일한 형상으로 되어 있을 수 있고, 실질적으로 동일한 크기로 되어 있을 수 있다.

[0072] TSV(505 및 510)는 차동 쌍(405)을 형성하는 제1 및 제2 트랜지스터의 소스(S)로부터 같은 거리에 있다. 차동 쌍(405)의 배향으로 인해, 차동 쌍(405)으로부터 상이한 거리에 위치해 있을 수 있는 TSV(410 및 415)와 달리, TSV(505) 및 TSV(510)는 차동 쌍(405)의 소스(S)로부터 동일한 거리에 위치해 있어야만 한다. TSV(505)는, TSV(505)가 제1 트랜지스터에 더 근접해 있는 것으로 인해(예컨대, D2보다 D1에 더 근접해 있는 것으로 인해), 제2 트랜지스터에 대해서보다 제1 트랜지스터에 대해 더 큰 응력을 유발할 수 있다. TSV(510)는, TSV(510)가 제2 트랜지스터에 더 근접해 있는 것으로 인해(예컨대, D1보다 D2에 더 근접해 있는 것으로 인해), 제1 트랜지스터에 대해서보다 제2 트랜지스터에 대해 더 큰 응력을 유발할 수 있다. 도시된 바와 같이, TSV(505 및 510)가 차동 쌍(405)의 소스(S)로부터 같은 거리에 있을 때, TSV(505) 및 TSV(510)에 의해 발생된 응력장의 중첩 또는 결합의 결과, 차동 쌍(405)의 제1 트랜지스터 및 제2 트랜지스터 둘 다는 동일한 또는 일치된 응력장에 노출된다. TSV(505)가 차동 쌍(405)으로부터 TSV(510)와 상이한 거리에 위치해 있는 경우, TSV(505) 및 TSV(510)에 의해 유발된 응력장의 결합은 일치된 응력장이 얻어지도록 결합되지 않을 것이다. 제1 트랜지스터는 제2 트랜지스터와 상이한 TSV(505 및 510)로부터의 응력장에 노출될 것이고, 그에 의해 차동 쌍(405)을 형성하는 능동 회로 요소의 동작 특성이 일치되지 않을 것이다.

[0073] 그에 따라, 도 5에 예시되어 있는 TSV 배치를 사용하여, 각각의 TSV(505 및 510)에 의해 유발되는 응력장은 차동 쌍(405)의 제1 및 제2 트랜지스터에 대해 동일한 효과를 가진다. 제1 트랜지스터는 제2 트랜지스터와 동일한 응력장[각각의 TSV(410, 415, 505, 및 510)에 의해 유발됨]의 영향을 받는다. 그에 따라, 도 4에 제시된 예와 같이, 제1 트랜지스터 및 제2 트랜지스터가 일치하는 물리적 특성을 가지는 것으로 가정하면, 각각은, TSV(410, 415, 505, 및 510)의 존재에도 불구하고, 동일하거나 유사한 방식으로 동작할 것으로 예상될 수 있다.

[0074] 도 6은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 차동 트랜지스터 쌍의 토포그래픽 레이아웃 뷰를 나타낸 제6 블록도이다. 보다 상세하게는, 도 6은 제1 열의 TSV(605 내지 620) 및 제2 열의 TSV(625 내지 640) 사이에 배치되어 있는 차동 쌍(405)을 나타낸 것이다. 도 6에 예시된 실시예에서, 각각의 TSV(605 내지 610)는 정렬되어 있고 동일한 y 좌표를 가질 수 있다. 이와 유사하게, 각각의 TSV(625 내지 640)도 정렬되어 있고 동일한 y 좌표를 가질 수 있다. 게다가, 각각의 TSV(605 내지 640)는 실질적으로 동일한 형상으로 되어 있을 수 있고, 실질적으로 동일한 크기로 되어 있을 수 있다.

[0075] 수직축을 따른 간격의 면에서, TSV(610) 및 TSV(615)는 소스(S)를 실질적으로 양분하는 y 좌표를 갖는 수평선으로부터 같은 거리에 있을 수 있다. TSV(605) 및 TSV(620)는 소스(S)를 양분하는 수평선으로부터 같은 거리에 있을 수 있다. TSV(630) 및 TSV(635)는 소스(S)를 양분하는 수평선으로부터 같은 거리에 있을 수 있다. TSV(625) 및 TSV(640)는 소스(S)를 양분하는 수평선으로부터 같은 거리에 있을 수 있다.

[0076] 다른 예에서, TSV(605 내지 620)는 똑같은 간격으로 있을 수 있다. 이와 유사하게, TSV(625 내지 640)도 똑같은 간격으로 있을 수 있다. 그렇지만, 소스(S)를 양분하는 수평선을 참조하여 기술한 바와 같이, TSV 쌍의 등거리 간격이 유지되는 한, 이럴 필요가 없다는 것을 잘 알 것이다. 더욱이, 도시된 바와 같이, TSV(605 내지 620)의 열은 차동 쌍(405)으로부터 X2의 거리에 위치해 있을 수 있다. TSV(625 내지 640)의 열은 요망되는 일치하는 응력장을 유지하면서, 도 4를 참조하여 논의된 바와 같이, 차동 쌍(405)으로부터 X2의 동일한 거리에 또는 상이한 거리에 위치해 있을 수 있다.

[0077] 도시된 정렬 및 배치에 의해, 각각의 TSV(605 내지 640)에 의해 유발되는 얻어진 응력장은 차동 쌍(405)의 제1 트랜지스터 및 제2 트랜지스터에 동일한 방식으로 영향을 미친다. 이와 관련하여, TSV(605 내지 640)에 의해 유발되는, 차동 쌍(405)의 각각의 트랜지스터가 영향을 받는 응력장이 일치된다. 일치하는 물리적 특성을 갖는 제1 트랜지스터 및 제2 트랜지스터가 형성될 때, TSV(605 내지 640)의 존재 시에 일치하는 동작 특성을 유지하기 위해 각각은 동일하거나 유사한 방식으로 열화된다.

- [0078] 도 4 내지 도 6과 관련하여 예시되어 있는 실시예들은 TSV가 회로 블록의 각각의 능동 회로 요소에 동일하거나 실질적으로 유사한 방식으로 영향을 미치도록 배치되어 있는 다양한 예를 나타내고 있다. 이와 관련하여, 하나 이상의 TSV에 의해 유발되는, 회로 블록의 제1 능동 회로 요소가 노출되는 응력장은 회로 블록의 제2 능동 회로 요소가 노출되는 응력장과 동일하거나 일치한다. 그에 따라, 하나 이상의 각자의 TSV에 의해 유발되는 하나 이상의 응력장의 영향에도 불구하고, 제1 및 제2 능동 회로 요소는 정합된 채로 있을 수 있다.

- [0079] 도 4 내지 도 6을 참조하여 예시되어 있는 바와 같이, 능동 회로 요소에 대해 TSV에 의해 유발된 응력장이 일치되는지를 판정하는 대용물로서 거리 및 대칭이 사용될 수 있다. 예를 들어, TSV가 정합되어야 하는 회로 블록의 개별 능동 회로 요소들로부터 동등한 거리에 위치되도록 배치될 수 있다. 다른 예에서, TSV는 회로 블록을 중심으로 대칭이도록 배치될 수 있다. 어떤 경우에, 예를 들어, TSV들의 공통 중심(common centroid)의 위치는 회로 블록의 중심의 위치와 동일할 수 있다. 예를 들어, 도 4 내지 도 6 중 임의의 것을 참조하여, 도 4 내지 도 6의 각자의 도면 각각 내에 예시되어 있는 모든 TSV들이 회로 블록에 대해 대칭이고 및/또는 예시된 회로 블록의 중심과 공통인 중심을 가지도록 TSV들이 배치될 수 있다.

- [0080] "중심"은 회로 블록 등의 주어진 회로 구조 또는 2개 이상의 TSV에 대해 x 축에 평행한 대칭축과 y 축에 평행한 대칭축의 교차점을 말하는 것일 수 있다. 각각의 대칭축은 (예컨대, 회로 블록을 형성하는) 2개 이상의 회로 요소의 능동 표면 영역 또는 표면 영역을 대칭축의 양측에 존재하는 똑같은 대칭의 절반으로 분리시키는 분할선을 나타낼 수 있다.

- [0081] 차동 쌍과 관련하여, 대칭은 회로 블록의 성능에 상당한 영향을 미칠 수 있다. TSV와 트랜지스터 간의 거리는 대칭 판정의 중요한 부분일 수 있다. 주어진 멀티 다이 IC 구조물의 경우, TSV는 일반적으로 고정된 직경을 가진다. TSV의 직경이 고정되어 있는 경우, TSV와 능동 회로 요소 간의 거리를 변화시키고 대칭을 사용하여 회로 블록에 걸쳐 능동 회로 요소의 응력장에의 균일한 노출을 달성하는 것은 IC 설계자의 몫이다.

- [0082] TSV 크기 대 트랜지스터 크기의 상대 비 등의 다른 인자들이 유발되는 응력장 내에서의 응력의 집중에 영향을 미칠 수 있다. 살펴본 바와 같이, TSV에 의해 유발되는 응력은 TSV로부터 멀어지는 쪽으로 이동할 때 대략  $1/D$ 의 비율로 떨어진다. 큰 TSV로부터 작은 거리 D에 위치해 있는 작은 트랜지스터의 경우를 생각해보자. TSV는  $1/D$ 의 응력 감소에도 불구하고 트랜지스터 전체에 걸쳐 대체로 균일한 응력을 유발할 가능성이 있다. 그에 비해, 보다 큰 트랜지스터가 보다 작은 TSV로부터 동일한 거리 D에 위치해 있을 때, TSV는 트랜지스터 전체에 걸쳐 불균일한 응력을 유발할 가능성이 있다.

- [0083] 예를 들어, 도 5를 참조하면, 보다 작은 트랜지스터가 상대적으로 보다 큰 TSV와 함께 이용될 때, 각각의 트랜지스터가 노출되어 있는 응력장을 간에 상당한 불일치를 야기하는 일 없이, 차동 쌍(405)과 TSV(505) 또는 TSV(510) 사이의 Y1으로서 표시되어 있는 수직 간격이 상이할 수 있다. 다른 대안으로서, TSV 직경 대 디바이스 크기(예컨대, 트랜지스터의 채널 길이)의 최소 비에 의해, 반대쪽에 위치해 있는 상쇄용 TSV(counter-balancing TSV)를 필요로 하지 않고, 차동 쌍(405)의 위쪽에 또는 그 아래쪽에 단일의 TSV가 위치될 수 있다. 예를 들어, TSV(505) 또는 TSV(510) 중 한쪽 TSV가 다른쪽 TSV 없이 포함되어 있을 수 있다.

- [0084] 도 7은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 클럭 분배 회로망의 토포그래픽 레이아웃 뷰를 나타낸 제7 블록도이다. 도 7은 "H"자형 패턴으로 배열되어 있는 노드들(702 내지 718)을 포함하고 있는 클럭 분배 회로망(클럭 회로망)(700) 유형의 회로 블록을 나타낸 것이다. 클럭 회로망(700)은 각각의 분기가 클럭 신호 분배의 면에서 일치하는 지연 특성을 가지도록 구성되어 있는 고성능 클럭 회로망으로서 구현될 수 있다. 예를 들어, 노드(718)로부터 각각의 노드(702 내지 716)까지 개별적으로 측정되는 신호 전파 지연은 실질적으로 동등할 수 있다. 예시를 위해, 각각의 노드(702 내지 718)는 하나 이상의 능동 회로 요소를 가지는 베퍼 회로 블록 또는 클럭 신호 구동기 회로 블록을 나타낼 수 있다.

- [0085] 이와 관련하여, 노드(702, 706, 710, 및 714)는 수직으로 열을 이루어 정렬되어 있을 수 있으며, 여기서 각각의 노드(702, 706, 710, 및 714)는 동일한 x 좌표를 가진다. 이와 유사하게, 노드(704, 708, 712, 및 716)도 수직으로 열을 이루어 정렬되어 있을 수 있으며, 여기서 각각의 노드(704, 708, 712, 및 716)는 동일한 x 좌표를 가진다. 노드(702 및 706)는 754로 표시된 점을 통과하는 수평 클럭 회로망 분배 라인으로부터 같은 거리에 있을 수 있다. 각각의 노드(702 및 706)는 점(754)을 통과하는 라인으로부터 Y3의 수직 거리에 위치되어 있는 것으로 도시되어 있다. 노드(704 및 708)는 점(754)을 통과하는 수평 클럭 회로망 분배 라인으로부터 같은 거리에 있을 수 있다. 각각의 노드(704 및 708)는 점(754)을 통과하는 라인으로부터 Y3의 수직 거리에 위치되어 있는 것으로 도시되어 있다.

- [0086] 이와 유사하게, 노드(710 및 714)는 756으로 표시된 점을 통과하는 수평 클럭 회로망 분배 라인으로부터 같은 거리에 있을 수 있다. 각각의 노드(710 및 714)는 점(756)을 통과하는 수평 클럭 회로망 분배 라인으로부터 Y3의 수직 거리에 위치되어 있는 것으로 도시되어 있다. 노드(712 및 716)는 점(756)을 통과하는 수평 클럭 회로망 분배 라인으로부터 같은 거리에 있을 수 있다. 각각의 노드(712 및 716)는 점(756)을 통과하는 수평 클럭 회로망 분배 라인으로부터 Y3의 수직 거리에 위치되어 있는 것으로 도시되어 있다.

- [0087] 점(754 및 756)을 통과하는 각각의 라인은 점(758)을 통과하는 수평 클럭 회로망 분배 라인으로부터 같은 거리에 있을 수 있다. 도시된 바와 같이, 점(754 및 756)을 통과하는 각각의 라인은 점(758)으로부터 Y3의 수직 거리에 위치되어 있는 것으로 도시되어 있다. 노드들(702, 706, 710, 및 714)로 형성되어 있는 노드들의 열은 점들(754, 756, 및 758)에 의해 정의되는 수직축으로부터 X4의 거리에 위치해 있을 수 있다. 이와 유사하게, 노드들(704, 708, 712, 및 716)로 형성되어 있는 노드들의 열은 점들(754, 756, 및 758)에 의해 정의되는 수직축으로부터 X4의 거리에 위치해 있을 수 있다.

- [0088] 이와 관련하여, 제1 열의 TSV(720 내지 734)는 각각의 TSV(720 내지 734)가 동일한 x 좌표를 가지도록 수직으로 정렬되어 있을 수 있다. 제1 열의 TSV(720 내지 734)의 각각의 연속적인 TSV 쌍은 Y2의 수직 거리만큼 분리되어 있을 수 있다. 이와 유사하게, 제2 열의 TSV(736 내지 750)는 각각의 TSV(736 내지 750)가 동일한 x 좌표를 가지도록 수직으로 정렬되어 있을 수 있다. 제2 열의 TSV(736 내지 750)의 각각의 연속적인 TSV 쌍은 동일한 수직 거리 Y2만큼 분리되어 있을 수 있다.

- [0089] 그에 부가하여, TSV(726 및 728)는 점(758)을 통과하는 수평선으로부터 같은 거리에 있도록 배치될 수 있다. 이와 유사하게, 노드(742 및 744)는 점(758)을 통과하는 수평선으로부터 같은 거리에 있을 수 있다. TSV들(720 내지 734)의 열은 노드들(702, 706, 710, 및 714)로 형성되는 노드들의 열로부터 X3의 거리만큼 분리되어 있을 수 있다. TSV들(736 내지 750)의 열은 노드들(704, 708, 712, 및 716)로 형성되는 노드들의 열로부터 X3의 거리만큼 분리되어 있을 수 있다.

- [0090] 그 점에 대해서는, 클럭 분배 회로망(700) 또는 다른 회로 블록에 관해 실질적인 대칭을 유지하는 방식으로 TSV를 배치함으로써, 각각의 TSV(720 내지 750)로부터의 유발된 응력의 효과가 클럭 분배 회로망(700)의 노드들(702 내지 716)에 걸쳐 균일하게 가해질 수 있다. 잘 알 것인 바와 같이, 노드(718)는 TSV들(720 내지 734)의 열에 대해서보다는 TSV들(736 내지 750)의 열에 의해 더 영향을 받는데, 그 이유는 TSV로부터의 응력의 효과가 대략 1/D의 비율로 감소하기 때문이다.

- [0091] 많은 실세계의 경우에, 클럭 분배 회로망은 도 7에 도시된 바와 같은 대칭 형상으로 구현되지 않는다. 예를 들어, 프로그램가능 IC를 비롯한 최근의 IC는 주어진 인터포저 또는 다이의 격자 모양의 레이아웃을 방해하는 프로세서, DSP, 메모리 등과 같은 다양한 회로 블록을 포함할 수 있고, 그에 의해 클럭 분배 회로망이 대칭 패턴으로 구현되지 못하게 한다. 이러한 경우에, 클럭 분배 회로망의 비대칭으로 인해 TSV와 클럭 회로망의 노드들 간의 거리가 상이하게 될 수 있고, 그 결과 노드들에 가해지는 응력장이 상이하게 되고 따라서 응력 레벨이 상이하게 된다. 응력장이 상이한 결과, 클럭 회로망 내의 트랜지스터들의 다양한 성능으로 인해 클럭 회로망 내에서의 지연이 상이하게 될 수 있다.

- [0092] 어떤 경우에, 하나 이상의 부가의 TSV가 다이의 레이아웃에 추가될 수 있다. 능동 회로 요소를 둘러싸고 있는 응력 프로파일을 일치시키기 위해 다이의 레이아웃에 부가되는 TSV는 "더미 TSV"라고 할 수 있다. 더미 TSV는 전원 공급 장치 또는 접지에 결합되어 있는 TSV일 수 있다. 더미 TSV는, 예를 들어, 회로 설계의 신호(예컨대, 데이터)를 전달하는 것이 아니다. 선택된 영역의 TSV의 응력장이 더미 TSV에 의해 유발되는 응력장과 중첩되도록 하나 이상의 더미 TSV가 다이의 레이아웃에 부가되고 그 내에 배치될 수 있다. 더미 TSV 또는 더미 TSV들은, 경우에 따라, 회로 블록 내의 선택된 능동 회로 요소가 동일한(예컨대, 일치하는) 응력장[TSV와 더미 TSV(들)의 중첩된 응력장이라고 함]에 노출되도록, 배치될 수 있다.

- [0093] 도 4 내지 도 7은 다이 또는 인터포저 상에서 회로 블록에 대해 TSV를 배치하는 다양한 기법을 나타낸 것이다. TSV는 능동 회로 요소까지의 거리, 대칭 또는 이 둘의 조합의 면에서 측정되는, 예시되어 있는 다양한 구성을 달성하기 위해 재배치될 수 있다. 게다가, 도시되어 있는 종류의 구성을 달성하기 위해 부가의 더미 TSV들이 부가될 수 있다.

- [0094] 도 8은 본 명세서 내에 개시되어 있는 다른 실시예에 따른 예시적인 컴퓨팅 시스템(시스템)(800)을 나타낸 제8 블록도이다. 시스템(800)은 시스템 버스(815)를 통해 메모리 요소(810)에 결합되어 있는 적어도 하나의 프로세서(805)를 포함할 수 있다. 그에 따라, 시스템(800)은 메모리 요소(810) 내에 프로그램 코드를 저장할 수

있다. 프로세서(805)는 시스템 버스(815)를 통해 메모리 요소(810)로부터 액세스되는 프로그램 코드를 실행할 수 있다. 한 측면에서, 예를 들어, 시스템(800)은 프로그램 코드를 저장 및/또는 실행하기에 적당한 컴퓨터로서 구현될 수 있다. 그렇지만, 시스템(800)이 본 명세서 내에 기술되어 있는 기능들을 수행할 수 있는, 프로세서 및 메모리를 가지는 임의의 시스템의 형태로 구현될 수 있다는 것을 잘 알 것이다.

[0095] 메모리 요소(810)는, 예를 들어, 로컬 메모리(820) 및 하나 이상의 대용량 저장 장치(825) 등의 하나 이상의 물리 메모리 장치를 포함할 수 있다. 로컬 메모리(820)는 프로그램 코드의 실제 실행 동안 일반적으로 사용되는 랜덤 액세스 메모리 또는 다른 비영속적 메모리 장치(들)를 말하는 것일 수 있다. 대용량 저장 장치(들)(825)는 하드 드라이브 또는 다른 영속적 데이터 저장 장치로서 구현될 수 있다. 시스템(800)은 또한, 프로그램 코드가 실행 동안 대용량 저장 장치(825)로부터 검색되어야만 하는 횟수를 감소시키기 위해, 적어도 어떤 프로그램 코드의 일시적 저장을 제공하는 하나 이상의 캐시 메모리(도시 생략)를 포함할 수 있다.

[0096] 키보드(830), 디스플레이(835) 및 포인팅 장치(도시 생략) 등의 입/출력(I/O) 장치가 선택적으로 시스템(800)에 결합될 수 있다. I/O 장치는 직접 또는 중간의 I/O 제어기를 통해 시스템(100)에 결합될 수 있다. 시스템(800)이 중간의 사설 또는 공중 네트워크를 통해 다른 시스템, 컴퓨터 시스템, 원격 프린터, 및/또는 원격 저장 장치에 결합될 수 있게 해주기 위해, 네트워크 어댑터가 또한 시스템(800)에 결합되어 있을 수 있다. 모뎀, 케이블 모뎀, 및 이더넷 카드는 시스템(800)에서 사용될 수 있는 다른 유형의 네트워크 어댑터의 예이다.

[0097] 도 8에 나타낸 바와 같이, 메모리 요소(810)는 응력장 분석 모듈(840)을 저장할 수 있다. 실행가능 프로그램 코드의 형태로 구현되는 응력장 분석 모듈(840)이 시스템(800)에 의해 실행될 수 있다. 응력장 분석 모듈(840)은 주어진 다이 또는 인터포저 내의 개별 능동 디바이스에 가해지는, 다양한 TSV에 의해 유발되는 응력장을 결정할 수 있다. 다른 예에서, 응력장 분석 모듈(840)은 TSV까지의 거리 및 TSV에 의해 발생되는 응력장에 의존하는 능동 회로 요소에 대한 능동 디바이스를 결정하거나 모델링할 수 있다[예컨대, 스파이스 모델(spice model)을 구축함].

[0098] 도 9는 본 명세서 내에 개시되어 있는 다른 실시예에 따른 TSV를 사용하여 IC를 설계하는 방법(900)을 나타낸 플로우차트이다. 방법(900)은 도 1 내지 도 7을 참조하여 기술되어 있는 다양한 규칙 및 기법을 사용하여 도 8에 예시되어 있는 시스템 등의 데이터 처리 시스템에 의해 수행될 수 있다.

[0099] 방법(900)은 이 시스템이 하나 이상의 TSV가 그 안에 구현되어 있는 인터포저(예컨대, 다이)의 회로 레이아웃을 분석할 수 있는 단계(905)에서 시작될 수 있다. 예를 들어, 이 시스템은 능동 회로 요소로부터 TSV[예컨대, 가장 가까운 TSV 또는 각각의 능동 회로 요소로부터 소정의 거리(이 거리 내에서 그 TSV의 응력장이 능동 회로 요소의 성능에 영향을 미치는 것으로 가정됨) 내의 TSV]까지의 거리를 결정할 수 있다. 이 시스템은 또한 정합하는 능동 회로 요소들이 이용되는 차동 쌍, 클럭 분배 회로망, 또는 다른 회로 구조 등의 관심 영역을 식별할 수 있다.

[0100] 단계(910)에서, 이 시스템은 다이 상에서의 응력장을 추정할 수 있다. 이 시스템은 다양한 TSV에 의해 발생되는 응력장을 추정하고 인터포저에 걸친 응력 프로파일을 개발하기 위해 중복하는 응력장들을 중첩할 수 있으며, 그에 의해 응력장을 개별 회로 블록들 및 개별 능동 회로 요소들에 상관시키는 것을 가능하게 해준다.

[0101] 단계(915)에서, 이 시스템은 관심 영역에 대해 임의의 불일치가 존재하는지를 판정할 수 있다. 논의한 바와 같이, 불일치는 정합되도록(예컨대, 서로 물리적으로 실질적으로 동일하거나 똑같은 의도된 기능을 갖도록) 되어 있는 적어도 2개의 능동 회로 요소가 상이한 응력장에 노출되어 있는 상황을 말하는 것이다. 2개의 능동 회로 요소는 통상적으로 동일한 회로 블록 내에 위치해 있고, 따라서 서로 바로 인접해 있지는 않더라도 서로로부터 소정의 거리 내에 있다. 예를 들어, 하나의 회로 요소가 다른 회로 요소가 노출되어 있는 응력 레벨과 최소 응력량 초과만큼 상이한 응력 레벨에 노출되어 있을 때 불일치가 식별되거나 판정될 수 있다.

[0102] 논의한 바와 같이, 응력장의 불일치를 판정하는 다른 기법은, 예를 들어, 회로 블록이 회로 블록의 각각의 능동 회로 요소로부터 소정의 범위 또는 거리 내에 있는 하나 이상의 주변의 TSV 또는 TSV들에 대해 대칭인지를 판정하는 것을 포함할 수 있다. 다른 기법은 TSV와 회로 블록의 능동 회로 요소 사이의 거리를 결정하는 것을 포함할 수 있다. 예를 들어, 이 시스템은 회로 블록으로부터 소정의 거리 내에 있는 하나 이상의 또는 모든 TSV가 각각의 능동 회로 요소로부터 동일한 거리에 위치해 있는지를 판정할 수 있다. 비교 및 응력장이 불일치하는지의 판정을 위해 비대칭의 정도 또는 거리의 크기가 응력장의 크기와 상관되어 있을 수 있다. 살펴본 바와 같이, 예를 들어, 각각의 TSV로부터 응력이 1/D의 비율로 감소한다.

[0103] 단계(920)에서, 이 시스템은 불일치를 갖는 것으로 식별된 관심 영역을 선택할 수 있다. 단계(925)에서, 이 시

스템은 관심 영역의 능동 회로 요소가 노출되어 있는 일치하지 않는 응력장에 대한 기여 인자인 것으로(예컨대, 일치하지 않는 응력장을 적어도 부분적으로 유발하는 것으로) 판정되는 각각의 TSV를 선택할 수 있다.

[0104] 일반적으로, TSV에 대한 다이의 레이아웃을 수정함으로써 응력장들 간의 불일치가 감소될 수 있다. 예를 들어, 단계(930)에서, 이 시스템은 단계(925)에서 선택된 TSV들 중 적어도 하나의 TSV의 위치를 조절할 수 있다. 이 시스템은 일치하지 않는 응력장들 간의 개선된 또는 더 높은 일치를 달성하기 위해 TSV를 재배치할 수 있다. 단계(935)에서, 이 시스템은 선택적으로 더미 TSV를 부가함으로써 레이아웃을 수정할 수 있다. 더미 TSV를 부가하는 것은 일치하지 않는 응력장들 간의 개선된 일치를 달성하기 위해 기존의 응력장에 중첩될 추가의 응력장을 유발할 수 있다. 예를 들어, 소정의 임계값보다 큰[예컨대, 단계(915)에 기술된 응력장 불일치량보다 더 큰] 불일치가 일어날 때, 2개의 응력장 간의 차분이 너무 커서 TSV를 재배치함으로써 극복될 수 없는 것으로 판정될 수 있다. 이러한 경우에, 하나 이상의 더미 TSV가 부가될 수 있다. 살펴본 바와 같이, 더미 TSV(들)는 대칭을 달성하기 위해 부가될 수 있거나, 하나 이상의 선택된 능동 회로 요소에 근접하여 부가되어 이러한 능동 회로 요소가 영향을 받는 응력장에 영향을 줄 수 있다.

[0105] 단계(935) 후에, 방법(900)은 단계(930)에서 조절되는 임의의 위치 변경된 또는 재배치된 TSV 및/또는 단계(940)에서 부가되는 임의의 부가된 더미 TSV에 따라 다이 상에서의 응력장을 추정하기 위해 단계(910)로 루프백 할 수 있다.

[0106] 방법(900)이 예시적인 회로 설계 방법을 나타내고 있다는 것을 잘 알 것이다. 다른 실시예에서, 위치 변경되는 하나 이상의 TSV가 일치하지 않는 응력장들 간의 일치를 최소량만큼 개선시키는 데 실패하는 소정의 반복 횟수 후에만 더미 TSV가 부가될 수 있다. 다른 실시예에서, 조절을 위한 다른 TSV를 선택하기 전에 반복적인 재배치 또는 위치 변경을 위한 하나의 TSV가 선택될 수 있다. 또 다른 실시예에서, 일치하지 않는 응력장들 중 어느 하나에 최대로 기여하는 TSV가 보다 적은 기여를 하는 TSV보다 먼저 선택되도록 위치 변경을 위한 TSV 선택이 수행될 수 있다.

[0107] 한 측면에서, 회로 블록이 회로 블록을 둘러싸고 있는 정의된 영역에 어떤 TSV도 위치해 있지 않은 정규화된 성능 메트릭으로부터의 엘타의 면에서 평가될 수 있다. 이와 같이, 회로 블록의 성능이 메트릭의 소정의 양 내로 개선될 때, 응력장들 간의 임의의 불일치가 원하는 레벨 또는 임계값보다 큰 채로 있는 것에도 불구하고 TSV의 조절이 종료될 수 있다.

[0108] 도면에서의 플로우차트는 본 명세서 내에 개시되어 있는 하나 이상의 실시예에 따른 시스템, 방법 및 컴퓨터 프로그램 제품의 가능한 구현의 아키텍처, 기능 및 동작을 예시하고 있다. 이와 관련하여, 플로우차트에서의 각각의 블록은 명시된 논리적 기능(들)을 구현하는 하나 이상의 실행가능 프로그램 코드 부분을 포함하는 코드 모듈, 코드 세그먼트, 또는 코드 부분을 나타낼 수 있다.

[0109] 어떤 대안의 구현에서, 블록에 나타낸 기능이 도면에 나타낸 순서와 달리 행해질 수 있다는 것을 잘 알 것이다. 예를 들어, 연속하여 도시된 2개의 블록이, 실제로는, 실질적으로 동시에 실행될 수 있거나, 블록들이, 수반되는 기능에 따라, 때때로 정반대 순서로 실행될 수 있다. 또한, 유의할 점은, 플로우차트 예시의 각각의 블록 및 플로우차트 예시에서의 블록들의 조합이 명시된 기능 또는 동작을 수행하는 전용 하드웨어-기반 시스템, 또는 전용 하드웨어와 실행가능 명령어의 조합에 의해 구현될 수 있다는 것이다.

[0110] 하나 이상의 실시예가 하드웨어로 또는 하드웨어와 소프트웨어의 조합으로 실현될 수 있다. 하나 이상의 실시예가 하나의 시스템에서 중앙 집중 방식으로 또는 상이한 구성요소가 몇개의 상호연결된 시스템에 걸쳐 분산되어 있는 분산 방식으로 실현될 수 있다. 본 명세서에 기술된 방법의 적어도 일부분을 수행하도록 구성되어 있는 임의의 종류의 데이터 처리 시스템 또는 다른 장치가 적합하다.

[0111] 하나 이상의 실시예는 또한 본 명세서에 기술되어 있는 방법의 구현을 가능하게 해주는 모든 특징들을 포함하는 컴퓨터 프로그램 제품 등의 디바이스에 내장되어 있을 수 있다. 디바이스는, 메모리 및 프로세서를 포함하는 시스템에 로드되어 실행될 때, 시스템으로 하여금 본 명세서 내에 기술되어 있는 기능들 중 적어도 일부분을 수행하게 하는 프로그램 코드를 저장하는 데이터 저장 매체(예컨대, 비일시적 컴퓨터 사용가능 또는 컴퓨터 판독 가능 매체)를 포함할 수 있다. 데이터 저장 매체의 예는 광 매체, 자기 매체, 광자기 매체, 컴퓨터 메모리(랜덤 액세스 메모리, 대용량 저장 장치, 예컨대, 하드 디스크) 등을 포함할 수 있지만, 이들로 제한되지 않는다.

[0112] "컴퓨터 프로그램", "소프트웨어", "응용 프로그램", "컴퓨터 사용가능 프로그램 코드", "프로그램 코드", "실행가능 코드", 이들의 변형 및/또는 조합과 같은 용어는, 이와 관련하여, 임의의 언어, 코드 또는 표기법으로 되어 있는, 정보 처리 능력을 가지는 시스템으로 하여금 직접 또는 a); 다른 언어, 코드 또는 표기법으로의 변

환; b) 다른 물질 형태로의 재현 중 어느 하나 또는 둘 다 후에 특정의 기능을 수행하게 하도록 되어 있는 명령어 세트의 임의의 표현을 의미한다. 예를 들어, 프로그램 코드는 서브루틴, 함수, 프로시저, 객체 메소드, 객체 구현, 실행가능 응용 프로그램, 애플릿, 서블릿, 소스 코드, 오브젝트 코드, 공유 라이브러리/동적 로드 라이브러리 및/또는 컴퓨터 시스템 상에서 실행되도록 설계되어 있는 다른 명령어 시퀀스를 포함할 수 있지만, 이들로 제한되지 않는다.

[0113] "한" 및 "하나"라는 용어는, 본 명세서에서 사용되는 바와 같이, 하나 또는 2개 이상으로서 정의된다. "복수의"라는 용어는, 본 명세서에서 사용되는 바와 같이, 2개 또는 2개 이상으로서 정의된다. "다른"이라는 용어는, 본 명세서에서 사용되는 바와 같이, 적어도 제2 또는 그 이상으로서 정의된다. "포함하는" 및/또는 "갖는"이라는 용어는, 본 명세서에서 사용되는 바와 같이, 포함하는(comprising)(즉, 개방형)으로서 정의된다. "결합된"이라는 용어는, 본 명세서에서 사용되는 바와 같이, 달리 언급하지 않는 한, 어떤 중간 요소 없이 직접 또는 하나 이상의 중간 요소에 의해 간접적으로 연결된(connected)으로서 정의된다. 2개의 요소가 또한 기계적으로, 전기적으로 결합되어 있거나, 통신 채널, 경로, 네트워크 또는 시스템을 통해 통신 연결될 수 있다.

[0114] 본 명세서 내에 개시되어 있는 하나 이상의 실시예의 사상 또는 본질적인 속성을 벗어나지 않고 다른 형태로 구현될 수 있다. 그에 따라, 하나 이상의 실시예의 범위를 나타내는, 상기 명세서보다는 이하의 특허청 구범위가 참조되어야만 한다.

## 도면

### 도면1

### 도면2

### 도면3

도면4

도면5

도면6

## 도면7

## 도면8

## 도면9

900