(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0098333

(43) 공개일자 2008년11월07일

(51) Int. Cl.

*H01L 23/12* (2006.01) *H01L 23/48* (2006.01)

(21) 출원번호 10-2008-0041968

(22) 출원일자 2008년05월06일

심사청구일자 없음(30) 우선권주장

11/744,657 2007년05월04일 미국(US)

11/768,844 2007년06월26일 미국(US)

(71) 출원인

스테츠 칩팩 엘티디

싱가포르 768442 5 이션 스트리트 23

(72) 발명자

도병태

싱가포르, 싱가포르 596745, 시그네처 파크,

#06-09, 토호 터로드 54

쿠안, 힙 호에

싱가포르, 싱가포르 760210, #10-35, 이션 스트리트 21, 비엘케이210

초우, 생 구안

싱가포르, 싱가포르 760131, #07-243, 이션 스트리트 11, 비엘케이 131

(74) 대리인

이만재

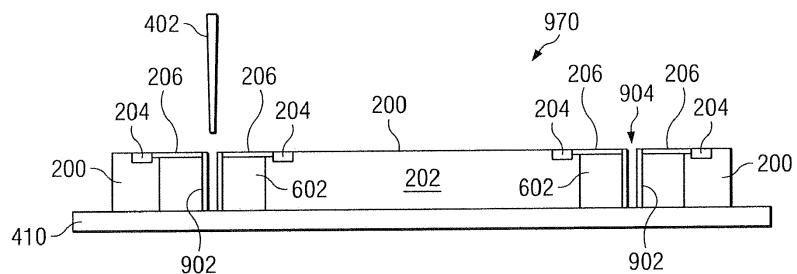

전체 청구항 수 : 총 25 항

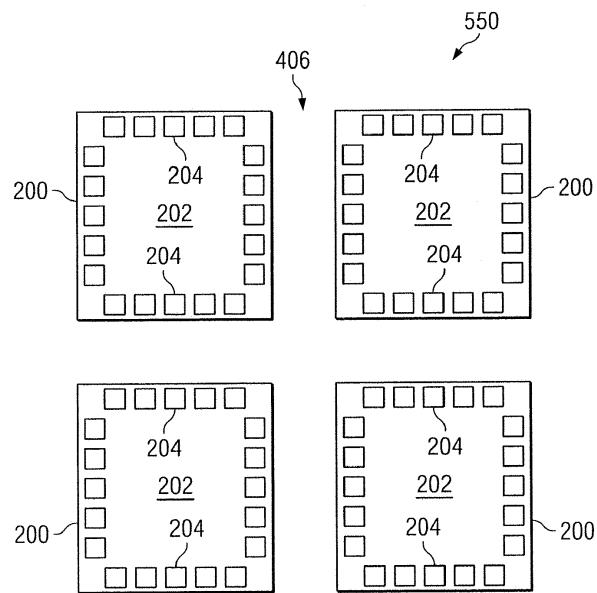

(54) 쏘우 스트리트 상의 관통-홀 비어 다이를 사용하는 패키지-온-패키지

### (57) 요 약

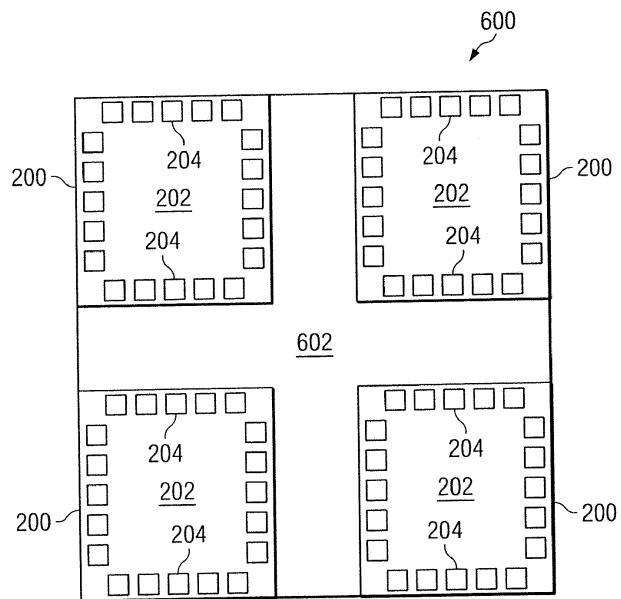

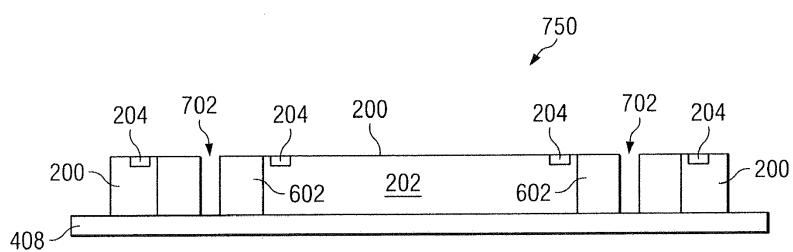

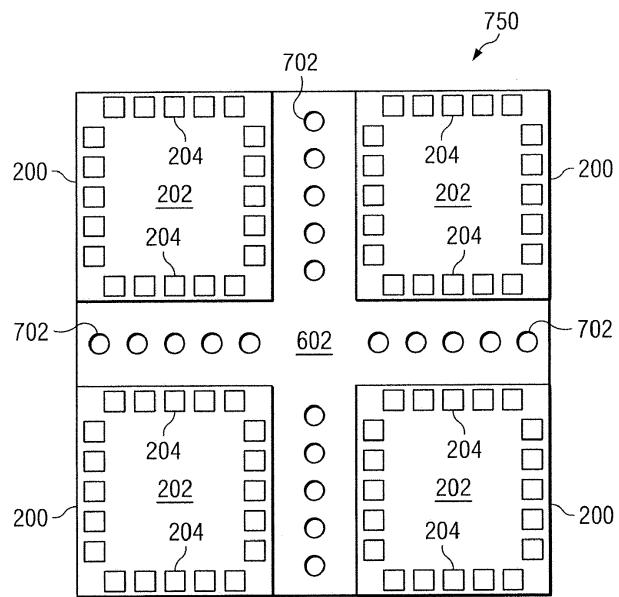

반도체 패키지-온-패키지(PoP) 장치는 제 1다이의 주연면을 따라 위치된 관통-홀 비어(THV)를 포함하는 제 1다이를 포함한다. 상기 제 1다이는 기판 또는 리드프레임 구조체상에 위치된다. 제 1 반도체 패키지는 제 1다이의 THV에 전기적으로 연결되거나 또는 상기 기판 또는 리드프레임 구조체에 전기적으로 연결된다. 캡슐화체가 제 1다이의 일부 또는 제 1반도체 패키기상에 형성된다.

**대 표 도** - 도27a

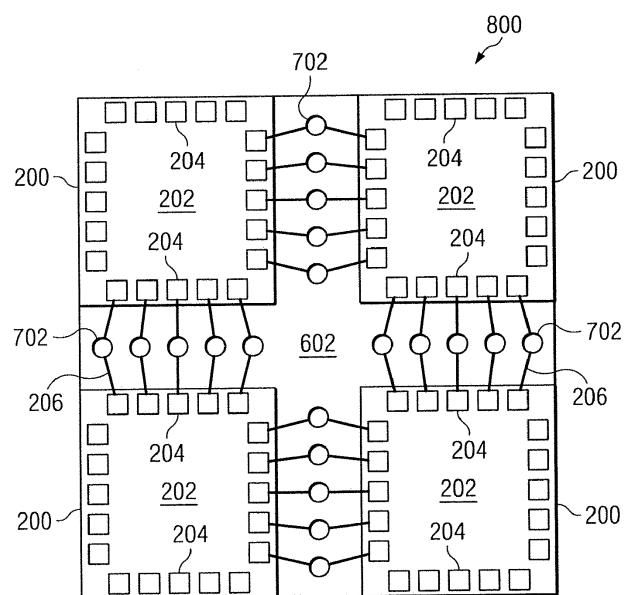

## 특허청구의 범위

### 청구항 1

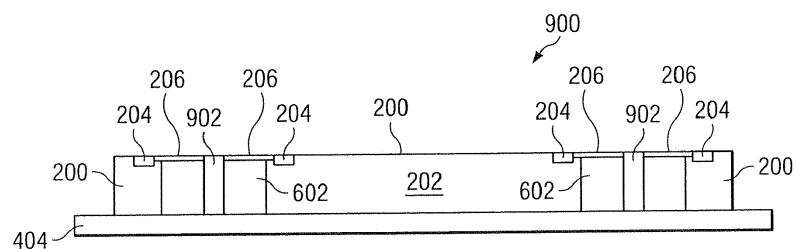

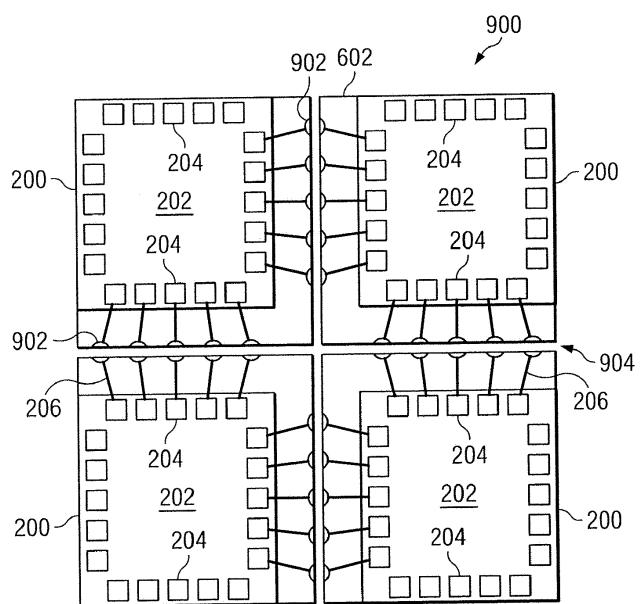

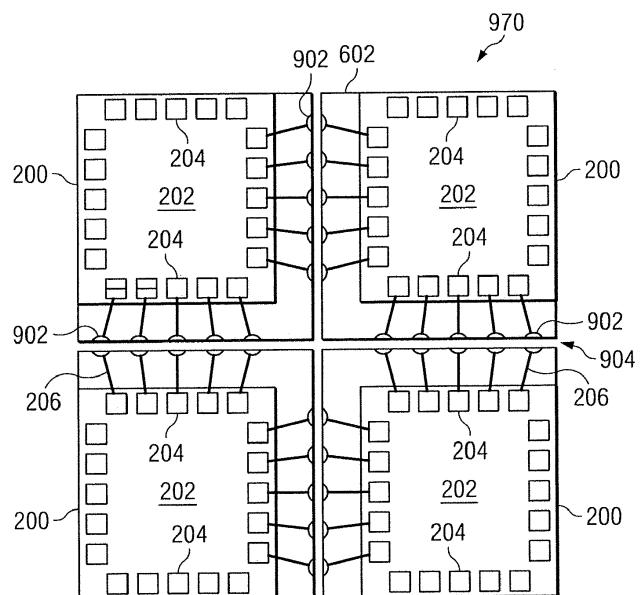

반도체 패키지-온-패키지(PoP) 장치에 있어서,

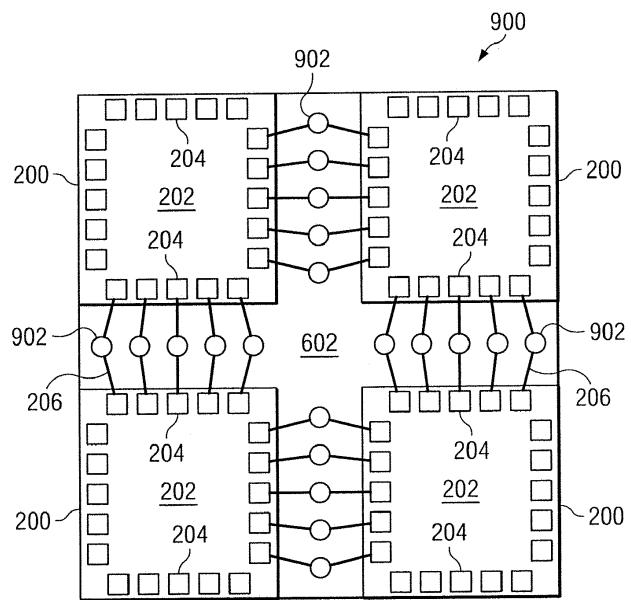

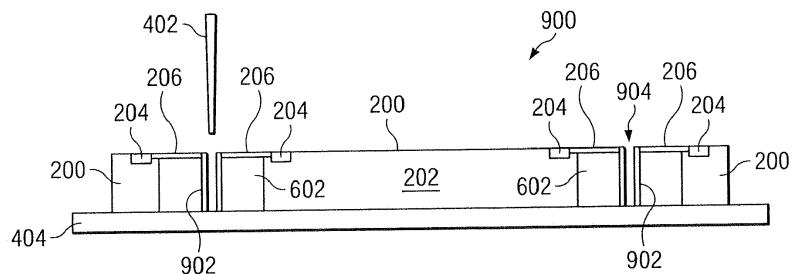

기판 또는 리드프레임 구조체 상에 위치되고, 주연면을 따라 위치된 관통-홀 비어(THV)를 포함하는 제 1다이;

상기 제 1다이의 THV에 전기적으로 연결되거나 또는 상기 기판 또는 리드프레임 구조체에 전기적으로 연결된 제 1반도체 패키지; 그리고

상기 제 1다이 및 제 1반도체 패키지 중의 일부 상에 형성된 캐슬화체;를 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

### 청구항 2

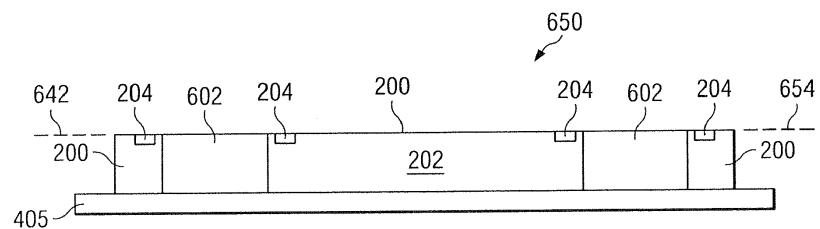

제 1항에 있어서,

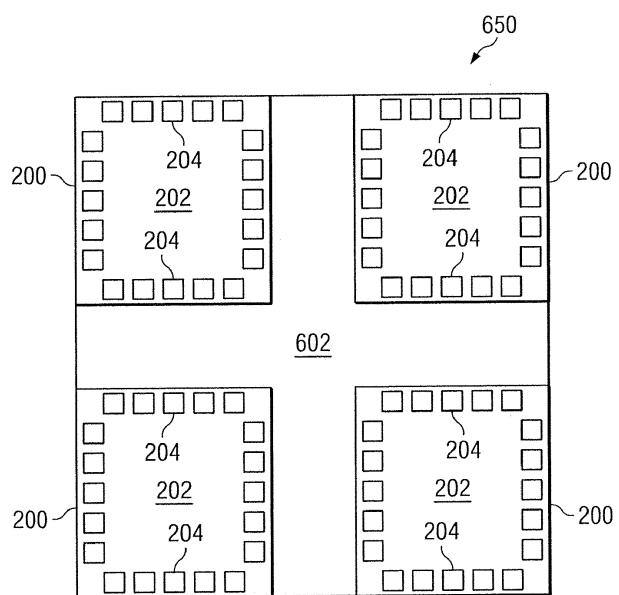

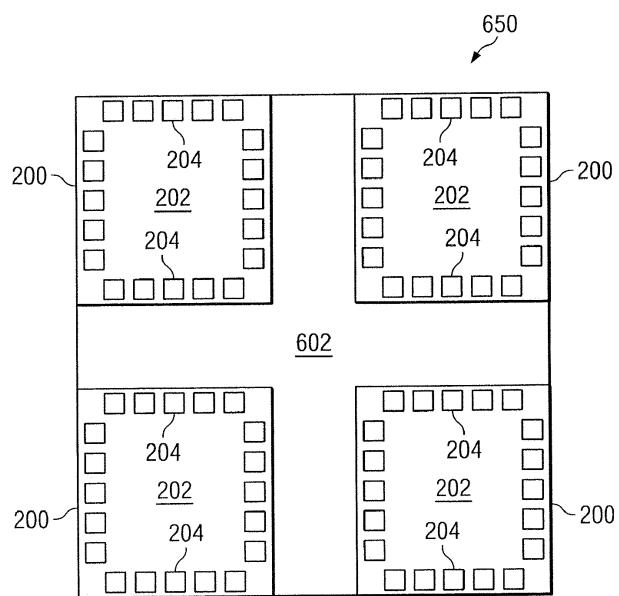

상기 제 1다이에 전기적으로 연결된 제 2다이 또는 제 2반도체 패키지를 또한 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

### 청구항 3

제 2항에 있어서,

상기 제 2다이가 플립 칩 다이를 포함하고, 상기 제 2반도체 패키지가 쿼드 플랫 넌리드(quad flat nonlead)(QFN) 패키지, 스몰 아웃라인 넌리드(small outline nonlead)(SON) 패키지, 쿼드 플랫 패키지(quad flat package)(QFP), 랜드 그리드 어레이(land grid array )(LGA) 장치 또는 볼 그리드 어레이(ball grid array )(BGA) 장치를 또한 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

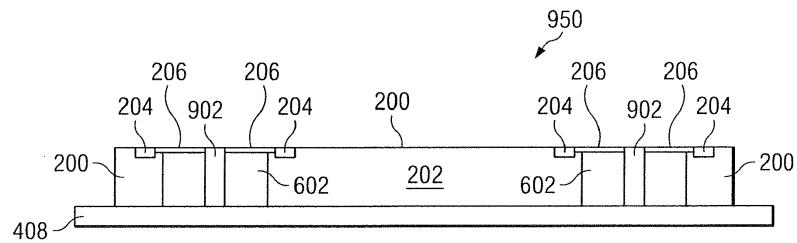

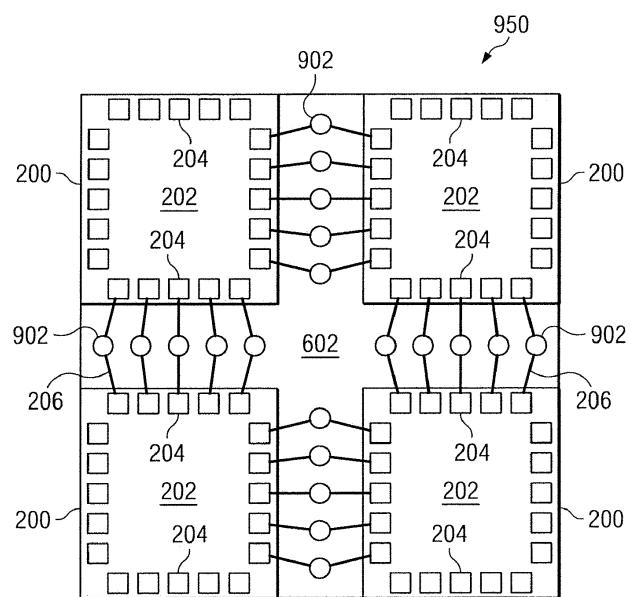

### 청구항 4

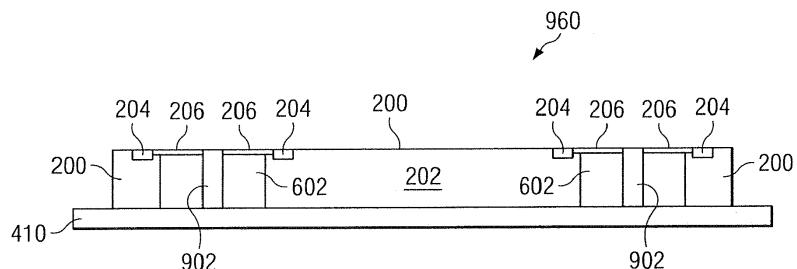

제 1항에 있어서,

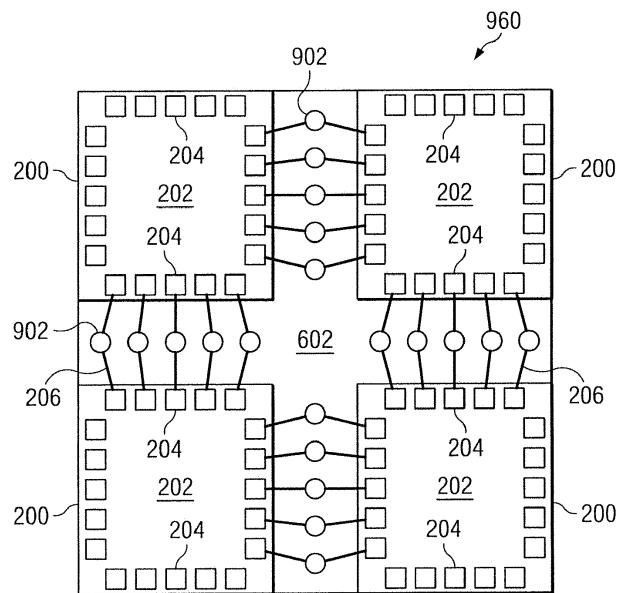

상기 제 1 반도체 패키지가 인버티드 패키지 장치인 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

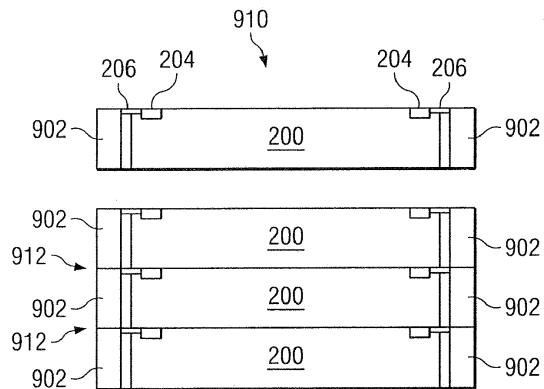

### 청구항 5

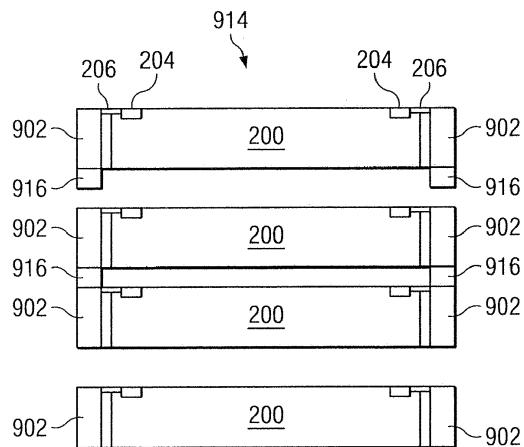

제 4항에 있어서,

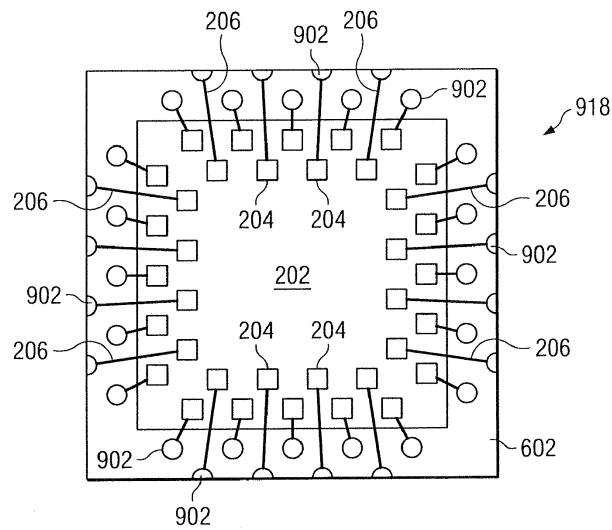

상기 인버티드 패키지가 제 1다이와 상기 기판 또는 리드프레임 구조체 사이에 위치되는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

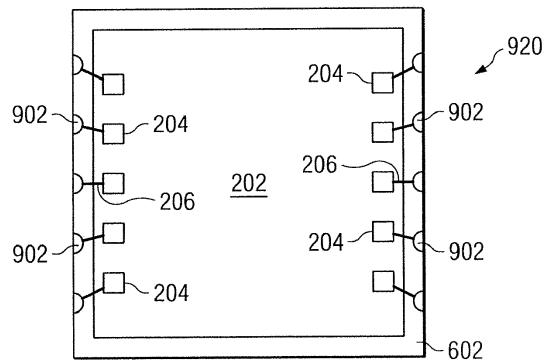

### 청구항 6

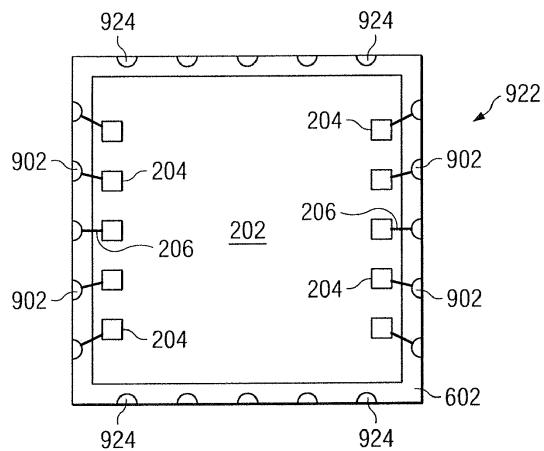

제 1항에 있어서,

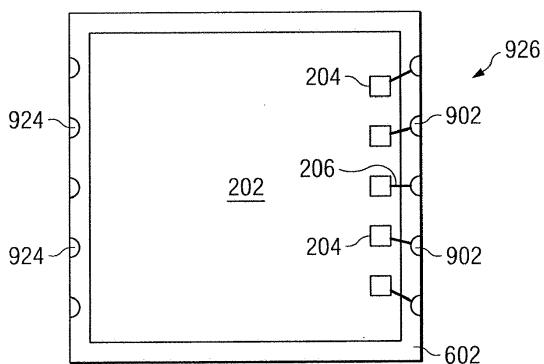

상기 제 1반도체 패키지를 상기 제 1다이에 전기적으로 연결시키기 위해 상기 제 1다이 상에 형성된 인터포저 구조체를 또한 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

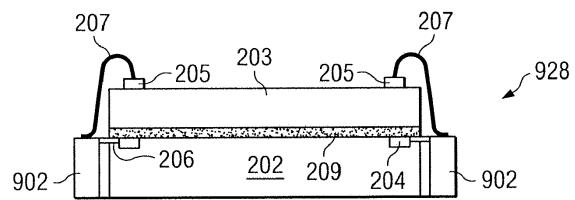

### 청구항 7

제 1항에 있어서,

상기 제 1반도체 패키지가 탑 사이드 업 플립 칩(top side-up flip chip) 다이 구조체를 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

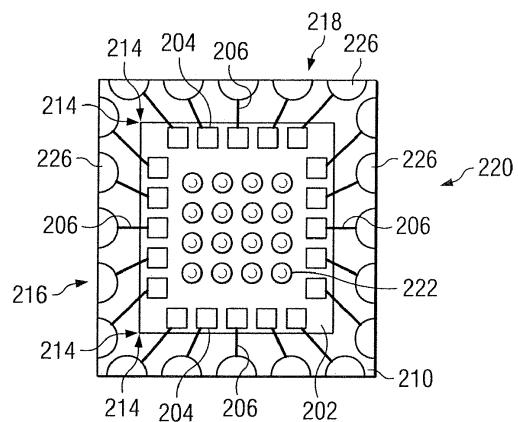

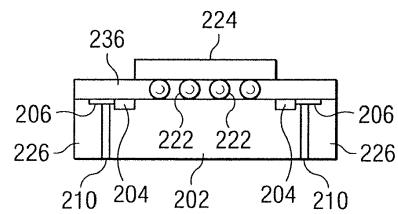

### 청구항 8

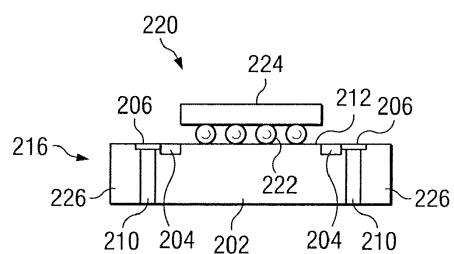

제 1항에 있어서,

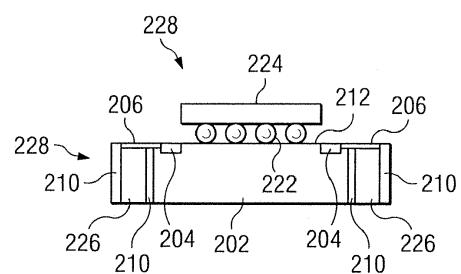

상기 제 1반도체 패키지가 팬-인 패키지-온-패키지(Fi-PoP) 장치를 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

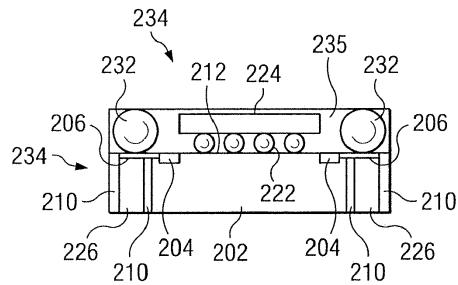

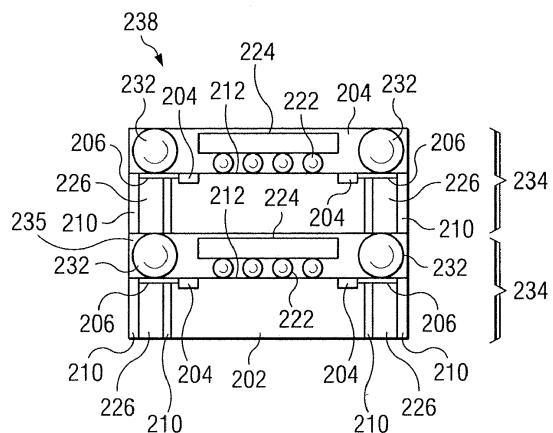

**청구항 9**

제 8항에 있어서,

상기 Fi-PoP 장치에 전기적으로 연결된 제 2다이 또는 제 2반도체 패키지를 또한 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

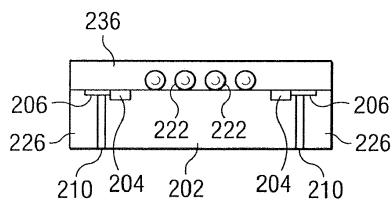

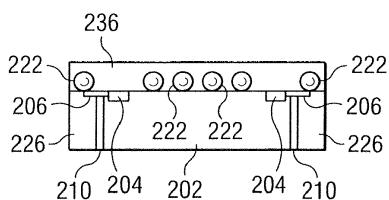

**청구항 10**

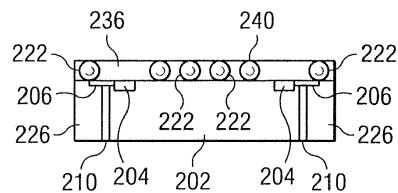

제 9항에 있어서,

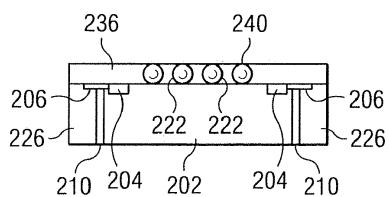

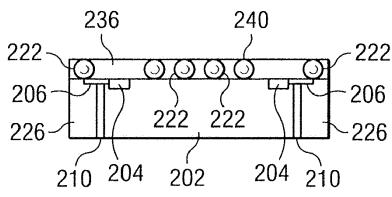

상기 제 2다이가 플립 칩 다이를 포함하고, 상기 제 2반도체 패키지가, 쿼드 플랫 넌리드(quad flat nonlead)(QFN) 패키지, 스몰 아웃라인 넌리드(small outline nonlead)(SON) 패키지, 쿼드 플랫 패키지(quad flat package)(QFP), 랜드 그리드 어레이(land grid array )(LGA) 장치 또는 볼 그리드 어레이(ball grid array )(BGA) 장치를 또한 포함하는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

**청구항 11**

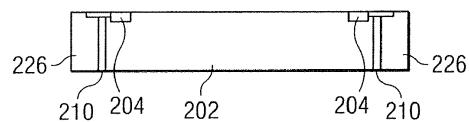

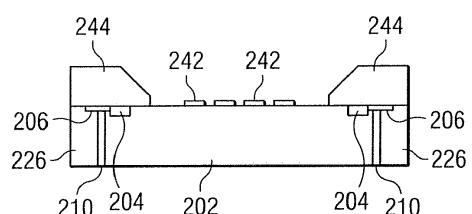

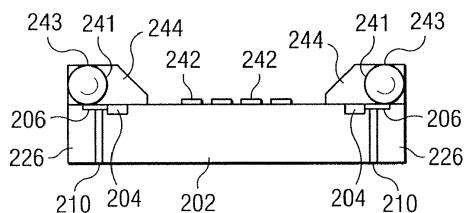

제 3항에 있어서,

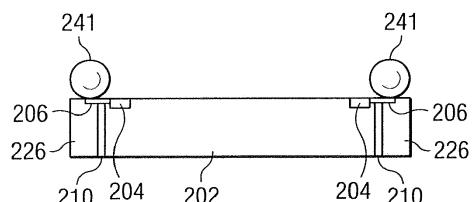

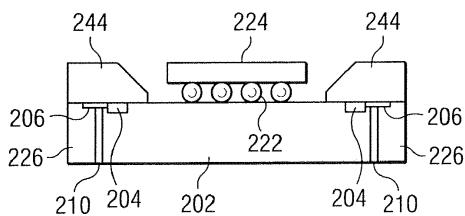

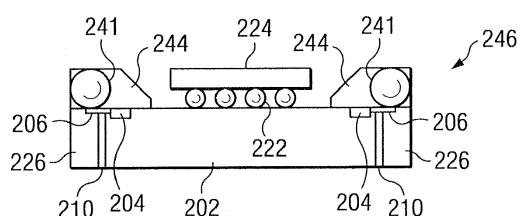

상기 제 2반도체 패키지가 상기 캡슐화체로부터 부분적으로 노출된 범프를 사용하여 상기 제 1다이에 전기적으로 연결되는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

**청구항 12**

제 3항에 있어서,

상기 제 2다이를 수용하기 위한 하나의 캐버티가 상기 기판 또는 리드프래임 구조체중의 일부에 형성되는 것을 특징으로 하는 반도체 패키지-온-패키지 장치.

**청구항 13**

반도체 장치 제조 방법에 있어서,

제 1다이 주연면을 따라 위치된 관통-홀 비어(THV)를 포함하는 제 1다이 상에 위치된 제 2의 범프된(bumped) 다이를 제공하는 단계;

상기 THV 상에 위치된 하나의 범프를 제공하는 단계;

상기 THV 및 범프된 다이의 정상부를 커버하지만 다수의 패키지 중의 제 1패키지를 구성하는 범프의 일부 및 제 1다이의 저부를 노출시키는 캡슐화체를 제공하는 단계; 그리고

상기 제 1패키지의 범프를 제 2패키지의 THV에 연결시킴으로써 다수 패키지 중의 상기 제 1패키지와 제 2패키지를 적층시키는 단계를 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

**청구항 14**

제 13항에 있어서,

상기 범프된 제 2다이가 와이어 본드 다이를 또한 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

**청구항 15**

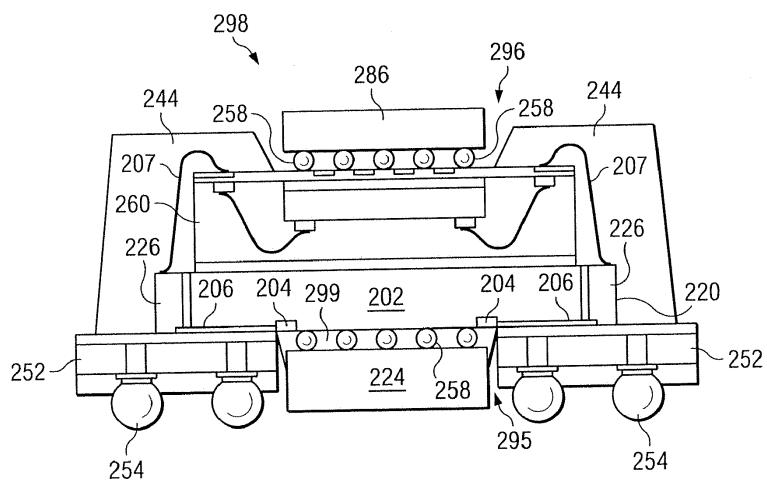

제 14항에 있어서,

상기 제 2의 범프된 다이가, 쿼드 플랫 넌리드(quad flat nonlead)(QFN) 패키지, 스몰 아웃라인 넌리드(small outline nonlead)(SON) 패키지, 쿼드 플랫 패키지(quad flat package)(QFP), 랜드 그리드 어레이(land grid array )(LGA) 장치 또는 볼 그리드 어레이(ball grid array )(BGA) 장치내로 일체화되는 것을 특징으로 하는 반도체 장치 제조 방법.

**청구항 16**

반도체 장치 제조 방법에 있어서,

주연면을 따라 위치된 관통-홀 비어(THV)를 포함하는 제 1다이를 제공하는 단계;

상기 제 1다이 상면상에 위치되거나 또는 THV상에 위치된 하나의 범프를 제공하는 단계;

상기 제 1다이 및 상기 범프중의 일부를 커버하는 캡슐화체를 제공하는 단계;

상기 캡슐화체의 일부를 제거함으로써 상기 범프를 노출시키는 단계; 그리고

제 2다이 또는 제 1 패키지를 상기 노출된 범프상으로 적층시키는 단계를 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

### **청구항 17**

제 16항에 있어서,

상기 펌프된 제 2다이가 와이어 본드 다이를 또한 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

### **청구항 18**

제 16항에 있어서,

상기 제 1패키지가, 쿼드 플랫 넌리드(quad flat nonlead )(QFN) 패키지, 스몰 아웃라인 넌리드(small outline nonlead)(SON) 패키지, 쿼드 플랫 패키지(quad flat package)(QFP), 랜드 그리드 어레이(land grid array )(LGA) 장치 또는 볼 그리드 어레이(ball grid array )(BGA) 장치를 또한 포함하는 것을 특징으로 반도체 장치 제조 방법.

### **청구항 19**

반도체 장치 제조 방법에 있어서,

주연면을 따라 위치되고 금속 트레이스에 의해 본드 패드에 연결된 관통-홀 비어(THV)를 포함하는 제 1다이를 제공하는 단계;

상기 1다이의 정상면에 상호 접속 패드를 위치시키는 단계;

상기 THV, 금속 트레이스 및 본드 패드를 커버하지만 상기 상호 접속 패드와 제 1다이의 저면 중의 일부를 노출시키는 캡슐화체를 제공하는 단계; 그리고

제 2다이 또는 제 1패키지를 상기 상호 접속 패드 상에 적층시키는 단계를 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

### **청구항 20**

제 19항에 있어서,

상기 제 1다이의 정상면 상에 위치되거나 또는 상기 THV 상에 위치되는 하나의 범프를 제공하는 단계를 또한 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

### **청구항 21**

제 19항에 있어서,

상기 제 2다이는 또한 와이어 본드 다이인 것을 특징으로 하는 반도체 장치 제조 방법.

### **청구항 22**

제 19항에 있어서,

상기 제 1패키지가, 쿼드 플랫 넌리드(quad flat nonlead)(QFN) 패키지, 스몰 아웃라인 넌리드(small outline nonlead )(SON) 패키지, 쿼드 플랫 패키지(quad flat package)(QFP), 랜드 그리드 어레이(land grid array )(LGA) 장치 또는 볼 그리드 어레이(ball grid array )(BGA) 장치를 또한 포함하는 것을 특징으로 반도체 장치 제조 방법.

**청구항 23**

제 19항에 있어서,

상기 제 2다이 또는 제 1패키지를 상호 접속 패드상에 적층시키는 단계는 다수 패키지중의 제 1패키지를 나타내는 것을 특징으로 하는 반도체 장치 제조 방법.

**청구항 24**

제 23항에 있어서,

다수 패키지 중의 제 2패키지를 상기 제 1패키지 상에 적층시키는 단계를 또한 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

**청구항 25**

제 24항에 있어서,

상기 범프가 상기 제 1패키지의 THV 정상면을 상기 제 2패키지의 THV 저면에 전기적으로 연결시키는 것을 특징으로 하는 반도체 장치 제조 방법.

**명세서****발명의 상세한 설명****기술 분야**

<1> 본 발명은 2007년 5월 4일 출원되고 발명의 명칭이 "쏘우 스트리트상의 관통-홀 비어"인 미합중국 특허출원 번호 제 11/744,657 호의 일부 계속 출원(CIP)이고, 35 U.S.C. § 120에 따라 전술의 선출원에 대한 우선권을 주장한다.

<2> 본 출원은 이것과 동시에 출원되고 변리사 도킷 번호 제 125155.00022호로서 발명의 명칭이 "쏘우 스트리트상의 관통-홀 비어 다이를 사용하는 패키지-인-패키지"인 동시 계류중인 미합중국 일부 연속 출원 번호 제 (계류중) 호와, 이것과 동시에 출원되고 변리사 도킷 번호 제 125155.00025호로서 발명의 명칭이 "동일한 크기의 관통-홀 비어 다이 적층 패키지"인 동시 계류중인 미합중국 일부 연속 출원 번호 제 (계류중) 호와 관련되어 있다.

<3> 본 발명은 일반적으로 반도체 장치에 관한 것으로, 특히 관통 홀 비어(through-hole via, THV) 적층 반도체 장치에 관한 것이다.

**배경 기술**

<4> 추세적으로, 반도체 제조자들은 반도체 장치용 3차원(3D) 상호접속부 및 패킹을 점진적으로 채용하고 있다. 3차원 상호 접속부는 소형의 짧은 상호 접속 길이 와 각 패키지 안에서 상이한 기능을 갖는 장치들의 집적과 같은 장점을 갖는다.

<5> 3차원 상호 접속부를 구현하는 다양한 방법 중의 하나는 THV 기술의 사용을 포함한다. THV는 반도체 칩, 또는 다이 내에 또는 쏘우 스트리트 안내부를 따르는 다이 외부 중의 하나에 위치될 수 있다.

<6> 그러나, 현재의 THV에는 여러가지 제한이 존재한다. 반도체 칩 내에 위치되는 비어는 칩내에서 추가 회로를 갖는 것에 대한 자유도를 제한한다. 고려할 수 있는 것으로서, THV의 각 위치는 그 위치에 회로 배열을 방해한다. 그 결과, 칩의 기능과 칩을 사용하는 장치가 제한된다.

<7> 반도체 칩 외부(즉, 쏘우 스트리트 안내부를 따르는)에 위치된 비어는 관통-홀의 생성물을 수용하기 위해서 보다 넓은 쏘우 스트리트를 필요로 한다. 그 결과, 수율(즉, 웨이퍼당 칩)이 감소된다.

**발명의 내용****해결 하고자하는 과제**

<8> 전술한 점을 고려하여, 본 발명의 목적은 전술된 수반되는 어떤 제한 없이 THV 적층 반도체 장치를 제공하는 것

이다. 그 장치는 이하에 기술되는 다양한 패키지-온-패키지(package-on-package)(PoP) 구성내에 포함될 수 있다.

### 과제 해결수단

- <9> 따라서, 하나의 실시예에서, 본 발명은 기판 또는 리드프래임 구조체상에 위치된 제 1다이의 주연면을 따라 위치된 관통-홀 비어(THV)를 포함하는 제 1다이, 상기 제 1다이의 THV에 전기적으로 연결되거나 또는 상기 기판 또는 리드프래임 구조체에 전기적으로 연결된 제 1반도체 패키지, 그리고 상기 제 1다이 및 제 1반도체 패키지 중의 일부상에 형성된 캡슐화체를 포함하는 반도체 PoP 장치이다.

- <10> 다른 하나의 실시예에서, 본 발명은, 제 1다이 주연면을 따라 위치된 관통-홀 비어(THV)를 포함하는 제 1다이상에 위치된 제 2의 범프된(bumped) 다이를 제공하는 단계, 상기 THV상에 위치된 하나의 범프를 제공하는 단계, 상기 THV 및 범프된 다이의 정상부를 커버하지만 다수의 패키지중의 제 1패키지를 구성하는 범프의 일부 및 제 1다이의 저부를 노출시키는 캡슐화체를 제공하는 단계, 그리고 상기 제 1패키지의 범프를 제 2패키지의 THV에 연결시킴으로써 다수 패키지중의 제 1패키지와 제 2패키지를 적층시키는 단계를 포함하는 반도체 장치 제조 방법이다.

- <11> 다른 하나의 실시예에서, 본 발명은, 주연면을 따라 위치된 관통-홀 비어(THV)를 포함하는 제 1다이를 제공하는 단계, 상기 제 1다이 상면상에 위치되거나 또는 THV상에 위치된 하나의 범프를 제공하는 단계, 상기 제 1다이 및 상기 범프중의 일부를 커버하는 캡슐화체를 제공하는 단계, 상기 캡슐화체의 일부를 제거함으로써 상기 범프를 노출시키는 단계, 그리고 제 2다이 또는 제 1패키지를 상기 노출된 범프상으로 적층시키는 단계를 포함하는 반도체 장치 제조 방법이다.

- <12> 다른 하나의 실시예에서, 본 발명은, 주연면을 따라 위치되고 금속 트레이스에 의해 본드 패드에 연결된 관통-홀 비어(THV)를 포함하는 제 1다이를 제공하는 단계, 상기 1다이의 정상면에 상호 접속 패드를 위치시키는 단계, 상기 THV, 금속 트레이스 및 본드 패드를 커버하지만 상기 상호 접속 패드와 제 1다이의 저면중의 일부를 노출시키는 캡슐화체를 제공하는 단계, 그리고 제 2다이 또는 제 1패키지를 상기 상호 접속 패드상에 적층시키는 단계를 포함하는 반도체 장치 제조 방법이다.

- 발명의 실시를 위한 구체적인 내용**

- <13> 본 발명이 동일한 번호가 동일 또는 유사 요소를 나타내는 도면을 참조하는 다음의 설명을 통해서 하나 또는 그 이상의 실시예로 기술된다. 본 발명의 목적을 달성하기 위한 최적의 방안에 의해 본 발명이 설명되면서, 후술하는 명세서와 도면에 의해 뒷받침되면서 첨부된 특허청구범위와 특허청구범위의 균등물에 의해 정의되는 발명의 범위와 정신의 안에서 내포 가능한 대안물, 변형물과 균등물을 포함하는 것으로 의도되는 본 발명의 구성요소들의 기능에 의해 본 발명은 해석될 것이다.

- <14> 다음의 설명과 청구범위에서, 용어 "comprise(포함하는)" 와 "include(포함하는)"은 그 파생어들과 함께 서로 각각에 대해서 동의어로서 사용되고 의도될 수 있다. 또한, 다음의 설명 청구범위에서, 용어 "coupled(연결된)" 및 "connected(연결된)"은 그들의 파생어와 함께 사용될 수 있다. "Connected(연결된)"는 두 개 이상의 요소들이 서로 각각 물리적 또는 전기적 접촉을 하고 있음을 표시하는데 사용될 수 있다. "Coupled(연결된)"는 두 개 이상 요소들의 직접적인 물리적 또는 전기적 접촉을 의미할 수 있다. 그러나, "coupled(연결된)"는 또한 두 개 이상의 요소들이 서로 각각 직접적인 접촉은 아니지만, 서로 각각 협동하거나 상호작용하는 것을 의미할 수 있다. 예를 들면, "coupled(연결된)"는 두 개 이상의 요소들이 서로 각각 접촉하지는 않지만, 간접적으로 다른 요소 또는 중간 요소들을 통해서 함께 결합되는 것을 의미할 수 있다. 마지막으로, 용어 "On(상에)", "Overlying(상에)" 및 "Over(상에)"가 다음의 설명 또는 청구범위에 사용될 수 있다. "On(상에)", "Overlying(상에)" 및 "Over(상에)"는 두 개 이상의 요소들이 서로 각각 직접적인 물리적 접촉이 이루어진다는 것을 표시하기 위해 사용될 수 있다. 그러나, "Over(상에)"는 또한 직접적인 접촉이 없다는 것을 의미할 수 있다. 예를 들면, "over(상에)"는 하나의 요소가 다른 하나의 요소 위에 있으나 서로 각각 접촉하지 않고, 그 둘 요소들 사이에 다른 하나의 요소 또는 요소들을 가질 수 있음을 의미한다.

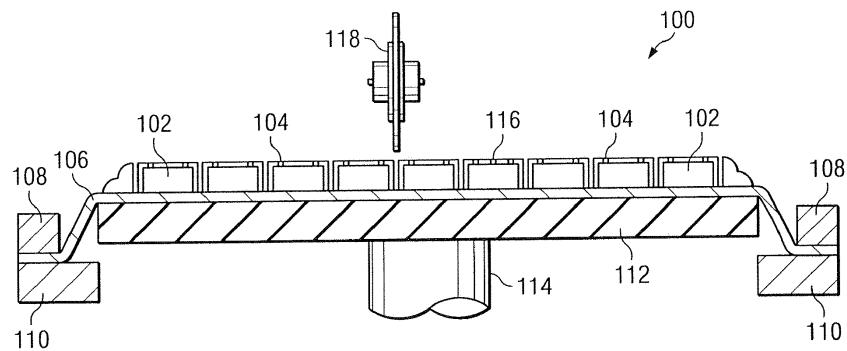

- <15> 도 1은 웨이퍼 레벨 칩 스케일 패키지(wafer level chip scale package)의 종래 제조 방법의 예(100)를 나타내는 도면이다. 다수의 반도체 장치(102)가 웨이퍼로부터 절삭된다. 각 반도체 장치(102)는 반도체 장치(102)의 활성 면에 위치한 돌출 본딩 패드(bonding pad)(104)를 갖는다.

- <16> 다수의 반도체 장치(102)는 신축성 필름(106)의 상면 상에 위치된다. 신축성 필름(106)은 프래임(108)에 의해

고정된다. 프래임(108)은 고정부(fixture)(110)에 의해 고정되고 신축성 필름(106)은 워크 플랫폼(work platform)(112) 상에 위치되고 일정 거리까지 신장된다.

<17> 플랫폼(112)은 고정부(110)에 대응하여 상승 이동할 수 있다. 상기 웨이퍼는 커터(cutter)에 의해 도시된 바와 같은 다수의 반도체 장치(102)로 절삭되고, 상기 칩들은 반도체 패키지 내로 캡슐화(encapsulate)된 후에 커터(118)에 의해 쏘우(saw)된다. 축(114)은 고정부(110)에 대응하여 플랫폼(112)을 들어올리기 위해 상승한다.

<18> 본 발명은, 일부 실시예에서, 특수한 용용 및 실시를 위해서 함께 적층되는 THV 반도체 장치에 대한 종래 제조 방법의 예(100)를 개선하고 있다.

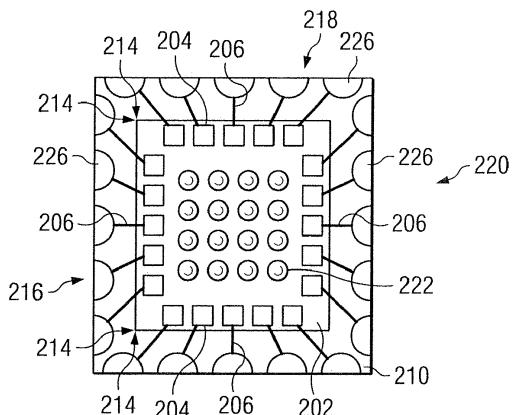

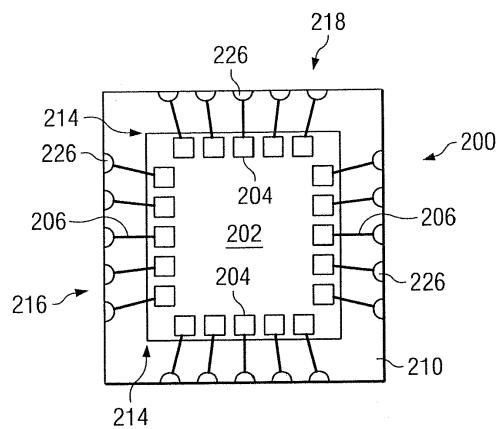

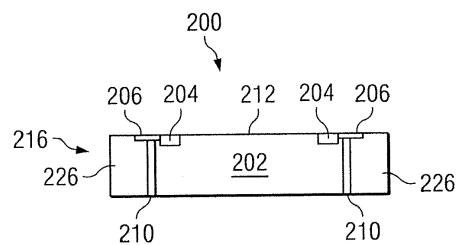

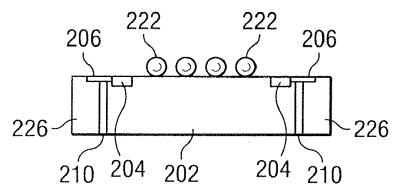

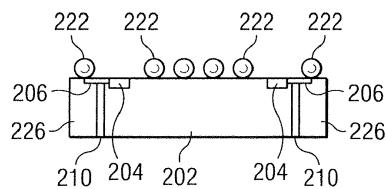

<19> 도 2a 및 도 2b는 각각 THV 적층 반도체 장치(THV stackable semiconductor device)(200)에 따른 제 1실시예를 나타내는 측면도 및 평면도이다. 장치(200)는 구체화된 다이(die)(202)를 구비한다. 장치(200)는 반도체 다이(202)의 활성면 상에 용착(deposited)된 다수의 본드 패드(bond pad)(204)를 포함한다. 본드 패드(204)는 도금 공정 또는 다른 공정에 의해 다이(202)의 전극 단자 상에 용착될 수 있다. 본드 패드(204)의 재료는 알루미늄(A1)과 같은 도전성(conductive) 금속으로 제조될 수 있다. 본드 패드(204)는 솔더링(soldering) 공정에 의해서 기판에 조인될 수 있다.

<20> 일련의 금속 트레이스(metal trace)(206)가 본드 패드(204)를 비어(via)(226)에 전기적으로 접속시킨다. 도 2b에 도시된 바와 같이, 비어(226)는, 다이(202)의 활성 상면(212)과 써라운딩(surrounding) 재료(210)에서 THV 구성과 일치하는 써라운딩 재료(210)와 상기 다이의 저면으로 수직 연장된다.

<21> 본 발명의 목적으로서, 써라운딩 재료(210)는 도시된 바와 같이 다이(202)의 주위면(214) 주위에 용착되는 "유기 재료(organic material)"로서 참조 된다. 유기 재료(210)는 아래에 더 기술되는 바와 같이, 종래 기술에 대한 개선이고 그것으로부터 기초한다. 상기 유기 재료는 벤조싸이클로부텐(benzocyclobutene)(BCB), 폴리이미드(polyimide)(PI) 재료 또는 유사한 재료와 같은 재료를 포함한다. 도시된 바와 같이, 비어(226)는 유기 재료(210)에서 형성되고, 로우(row)에 따라 조직화된다. 본 실시예(200)에서, 비어(226)는 유기 재료(210)의 각 사이드(즉, 사이드(216, 218))에 다이(202)의 주변을 완전히 감싸도록 형성된다. 다수의 본드 패드(204)는 다수 바이어스(226) 각각에 전기적으로 접속된다.

<22> 도시된 바와 같이, THV(226)는, 예를 들면, 멀티플(multiple) 로우를 따라서 다양한 구조로 형성될 수 있다. 또한, 하프-컷(half-cut) 비어(예시적인 도면으로서 도시됨) 또는 완성형 언컷(uncut) 비어(226)가 개개의 구현에 맞추기 위해 다양한 실시예에 형성될 수 있다. 반도체 장치(200)는 다양한 구조에서 추가 다이(202) 상에 적층되거나 연결될 수 있다.

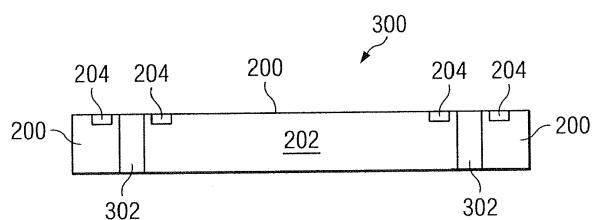

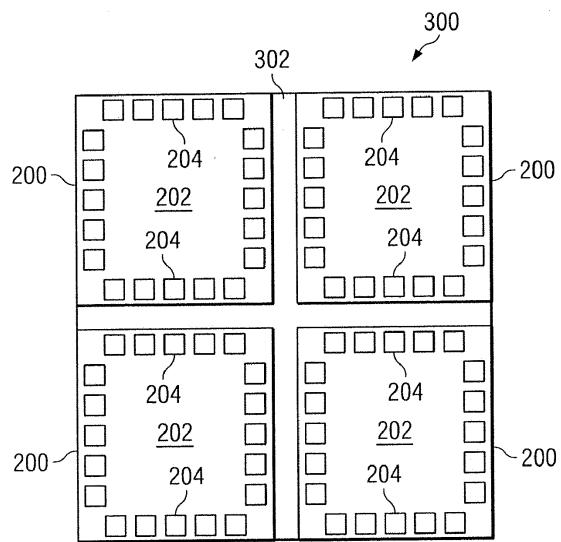

<23> 도 3a 및 도 3b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1단계를 나타내는 측면도 및 평면도이다. 웨이퍼(300)가 제공된다. 일련의 본드 패드(204)가 도시된 바와 같이 상기 웨이퍼의 활성면 상에 형성된다. 상기 웨이퍼는 쏘우 스트리드 안내부(saw street guide)(302)를 구비한다.

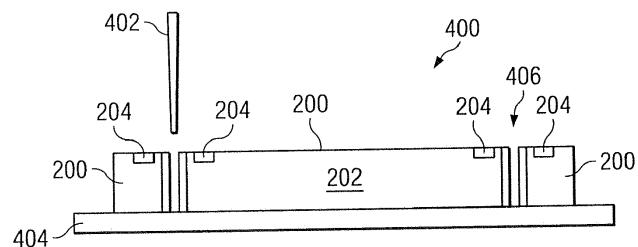

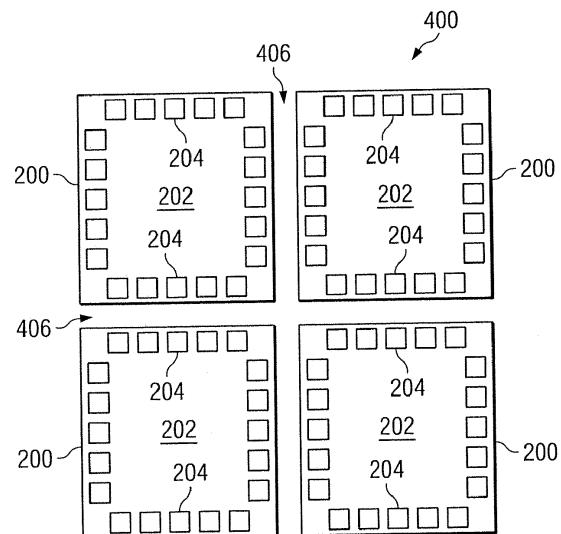

<24> 도 4a 및 도 4b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 2단계를 나타내는 측면도 및 평면도이다. 웨이퍼(300)는 컷팅 쏘스(cutting source)(402)에 의해 제 1단계 동안 표시된 피스(piece)(400)로 싱글레이트(singulated)된다. 컷팅 쏘스(402)는 쏘우 또는 레이저 컷팅 공구를 포함할 수 있다.

<25> 싱글레이션(singulation) 전에, 웨이퍼(300)는 다이싱 테이프(dicing tape)(404) 상에 놓이는데, 상기 다이싱 테이프는 싱글레이션 공정 동안에 다양한 세그먼트(segments)(400)를 정위치에 유지시킨다. 싱글레이션 공정 후에 일련의 갭(gap)(406)이 도시된 바와 같은 각각의 세그먼트 사이에 형성된다.

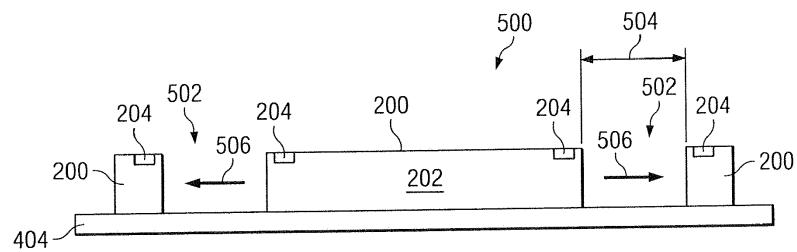

<26> 도 5a 및 도 5b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 3 단계를 나타내는 측면도 및 평면도이다. 도시된 각각의 세그먼트에서, 웨이퍼(300)는 팽창 공정을 겪는다. 다이싱 테이프(404)는 다양한 기술(예, 팽창 테이블)에 의해 신장되어, 소정 거리(504)를 갖는 일련의 갭(502)을 형성한다. 도시된 애로우(arrows)(506)는 웨이퍼 팽창 공정에 의해 거치는 다양한 팽창 방향을 나타낸다.

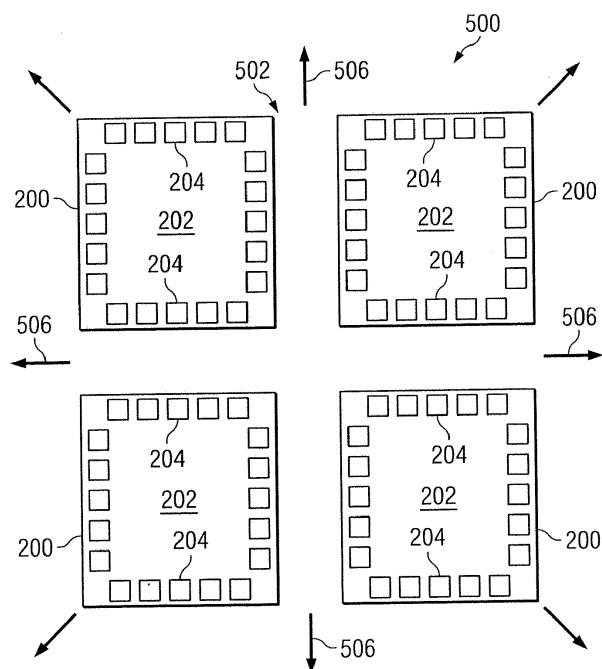

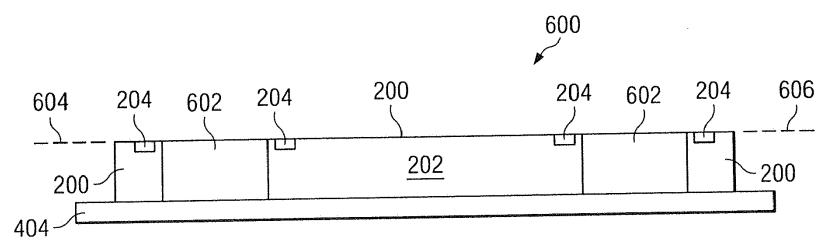

<27> 다음 단계로서, 도 6a 및 도 6b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 4 단계를 나타내는 측면도 및 평면도이다. 도 5a 및 도 5b에 도시된 바와 같은 다양한 갭(gap)(502)은 전술된 유기 재료(602)로 충진(fill)된다. 충진된 세그먼트(600)의 상면에 일치하는 플래인(604)은 유기 재료(602)의 상면과 일치하는 플래인(606)과 같은 평면이다.

<28> 유기 재료(602) 도포(application)는 스픬 코팅, 니들 분배 또는 유사한 용용과 같은 방법에 의해 수행될 수 있

다.

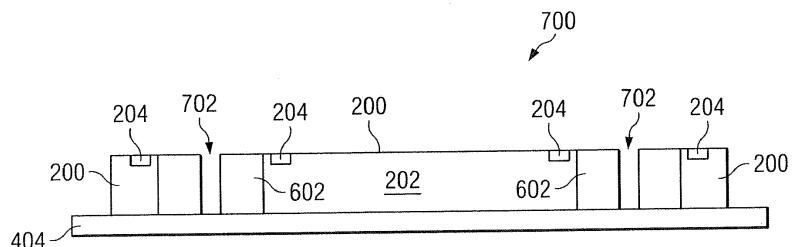

- <29> 도 7a 및 도 7b는 각각 도 2a 및 도 2b에 도시된 바와 같은 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 5 단계를 나타내는 측면도 및 평면도이다. 세그먼트(700)는 도시된 유기 재료(602)에 다수의 비어 홀(via hole)(702)을 형성하기 위한 공정을 거친다. 상기 비어 홀은, 레이저 비어 드릴링(laser via drilling) 공정 또는 에칭(etching) 공정을 포함하는, 다양할 공정에서 형성될 수 있다. 도시된 바와 같이, 각각의 비어 홀은 비어 홀이 관련되는 각각의 펌프 패드(204)와 일치하도록 유기 재료(602)에서 모양이 형성된다.

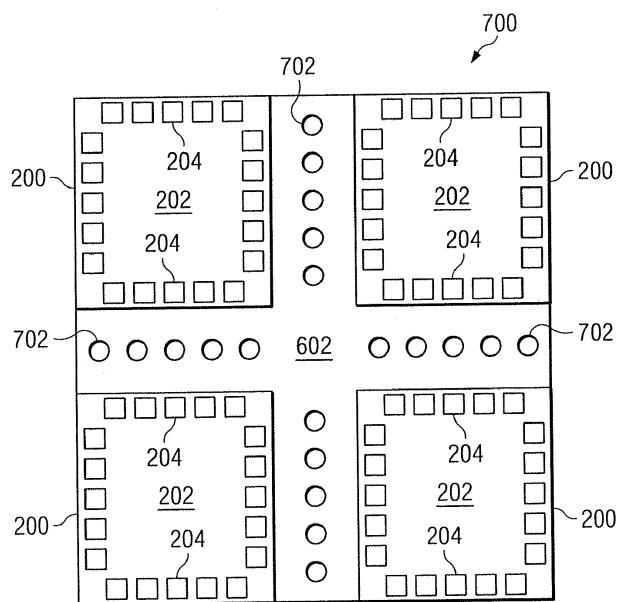

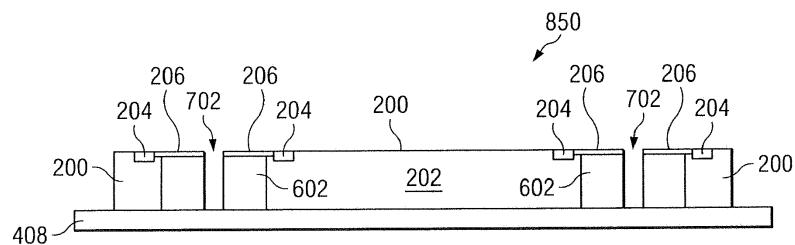

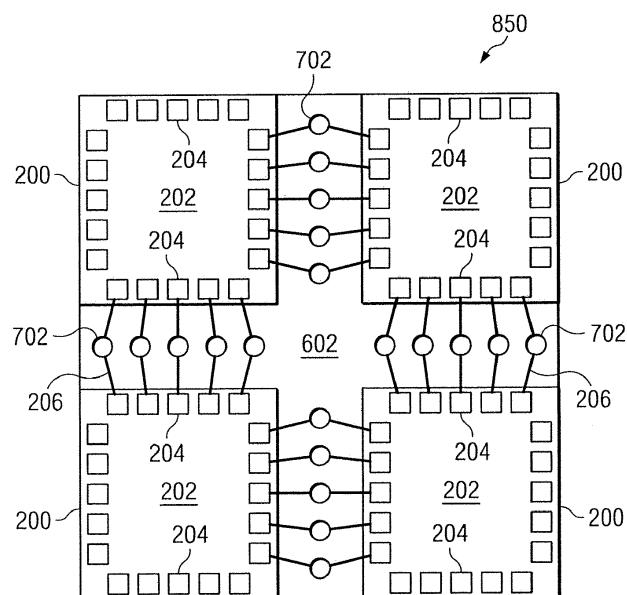

- <30> 다음으로, 도 8a 및 도 8b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 6 단계를 나타내는 측면도 및 평면도이다. 도 8a 및 도 8b는 본드 패드(204)에서 비어 홀(702)까지 일련의 금속 트레이스(metal trace)(206)를 연결시키는 금속 패터닝(metal patterning) 공정을 도시하고 있다. 또한, 금속 트레이스(206)는 도시된 바와 같이 비어 홀(702)의 각각에 상기 본드 패드들을 전기적으로 연결한다.

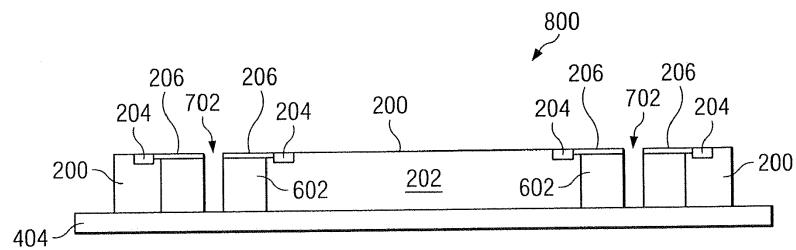

- <31> 도 9a 및 도 9b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 7 단계를 나타내는 도면이다. 비어 홀 금속 용착 공정은, 일련의 금속 비어(902)를 형성하면서, 도전성 재료를 각 비어 홀(702)에 용착하기 위해 어셈블리(assembly)(900)에서 수행된다. 도전성 재료는 알루미늄(Al), 구리(Cu), 텅스텐(W), 또는 다른 도전성 재료 또는 그들의 어떤 조합(alloy)과 같은 재료일 수 있다. 다시, 금속 비어(902)가 유기 재료(602)에 형성된다. 도금 또는 플러깅(plugging) 공정과 같은, 금속 비어 형성을 위한 다양한 방법과 기술이 사용될 수 있다.

- <32> 도 10a 및 도 10b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 8 단계를 나타내는 도면이다. 웨이퍼 어셈블리(300, 900)는 캡(904)을 형성하기 위해 컷팅 소스(402)에 의하는 제 2단계 동안 싱글레이트된다. 당업자가 이해할 수 있는 바와 같이, 도 10a 및 도 10b에 도시된 다양한 다이(202)와, 전술한 예시 형상들은 개개의 웨이퍼(300)에서 산출되는 전체 칩의 작은 부분을 나타낸다. 제 2 싱글레이션 단계 종료에 이어서, 대부분의 다이(202)는 도 2a 및 도 2b에 도시된 실시예와 같이 되는데, 도 2a 및 도 2b에서는 유기 재료(210)가 다이(202)의 주연면을 완전히 감싸고, THV(902)가 전술한 바와 같이 다이 각 측면을 따라서 로우로 배열된다.

- <33> 제 1실시예에서, 도 10a 및 도 10b에 도시된 싱글레이션 단계 후에, 개개의 다이(202)는 다이싱 테이프(404)로부터 각각의 다이(202)를 제거하기 위한 다이 퍽 앤 플레이스(die pick and place) 공정에 의해 제거된다.

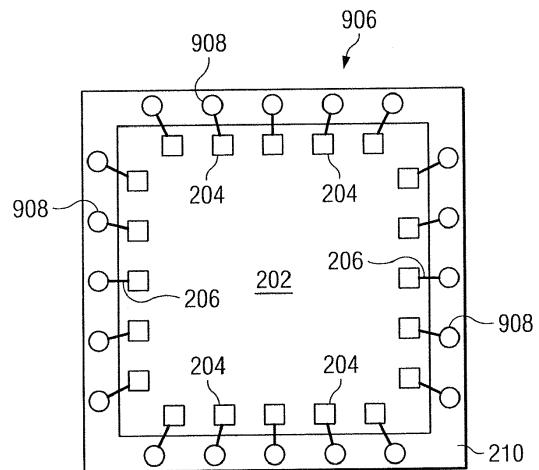

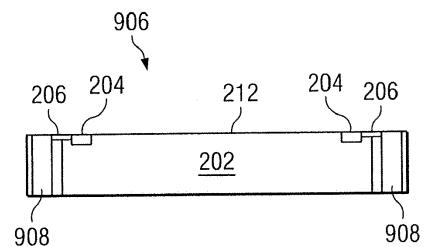

- <34> 도 11a 및 도 11b는 각각 다수의 완성형(complete) THV를 포함하는 관통-홀 적층 반도체 장치(906)에 따른 제 2 실시예를 나타내는 평면도 및 측면도이다. 여기서 다시, 다이(202), 본드 패드(204), 다이(202)의 활성면(212) 상에 형성된 금속 트레이싱을 포함하는 전술한 도면에 도시된 요소들이 도시된다. 본 실시예(906)에서, 각각의 THV(908)은 전술한 실시예에 도시된 하프-컷 대신에 "완성형(complete)"이다. 도시된 완성형 THV(908)는 도 3a 및 도 3b에 도시된 쏘우 스트리트 안내부(302)의 개개의 형상에 의해 형성될 수 있다. 보다 넓은 쏘우 스트리트 안내부(302)는 유기 재료(602)를 도시된 바와 같이 컷트하고, 완성형 비어 홀(908)을 유지시킨다.

- <35> 도 12a 및 도 12b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 3 단계를 나타내는 평면도 및 측면도이다. 기술된 상기 제 2제조 방법은 전술한 제 1실시예의 제 1 두 단계(즉, 웨이퍼를 제공하고 다이싱 테이프(404) 상에 각각 세그먼트로 싱글레이션하는 단계)를 포함한다. 또한, 다양한 요소(즉, 본드 패드 (204))가 구현된다.

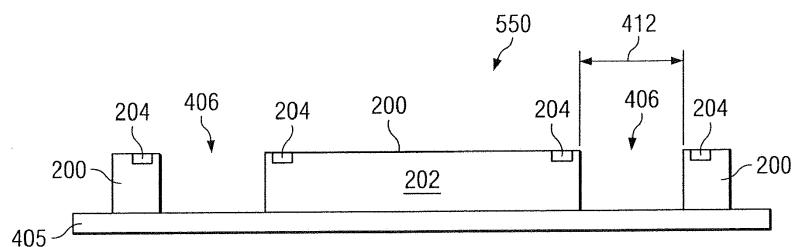

- <36> 다음 단계로서, 웨이퍼 세그먼트(550)가 제 1 다이싱 테이프(404)로부터 퍽킹(picking)되고 도시된 소위 "웨이퍼 지지 시스템" 상에 위치된다. 상기 웨이퍼 지지 시스템은 제 2 다이싱 테이프(405)를 필연적으로 포함한다. 그러나, 상기 웨이퍼 지지 시스템은 또한, 유리, 세라믹, 라미네이트(laminate) 또는 실리콘(Si) 기판과 같은 일시적 웨이퍼 지지 시스템일 수 있다. 일 실시예에서, 절삭된(sawn) 다이(202)는 다이싱 테이프(404)로부터 퍽크(picked)되고 퍽 앤 플레이스 장치를 이용하여 웨이퍼 지지 시스템(405) 상에 위치된다. 퍽 앤 플레이스 공정은 각각의 세그먼트(550) 사이에 소정 폭 또는 거리(412)를 갖는 캡(406)을 형성한다.

- <37> 도 13a 및 도 13b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예 제 4 단계를 나타내는 평면도 및 측면도이다. 유기 재료(602)가 다시 전술한 유사 스판 코팅, 니들 분배 또는 다른 방법으로 세그먼트(650)에 도포(applied)된다. 세그먼트(650)의 플래인(plane)(642)은 유기 재료(602)의 플래인(642)과 실질적으로 같은 평면이다.

- <38> 다음으로, 도 14a 및 도 14b은 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 5 단계를 나타내는 평면도 및 측면도이다. 리코트된(recoated) 웨이퍼(300)가 제 2 웨이퍼 지지 시스템(408)

상에 운송된다. 상기 제 2 웨이퍼 지지 시스템은 다시 유리, 실리콘(Si) 기판 재료, 세라믹 및 라미네이트 재료를 포함할 수 있다.

<39> 도 15a 및 도 15b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 6 단계를 나타내는 평면도 및 측면도이다. 도 7a 및 도 7b에 도시된 것과 유사한 단계(750)에서, 다수 비어 홀(702)이 본드 패드(204)와 부합하기 위해 유기 재료(602)에 형성된다.

<40> 도 16a 및 도 16b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 7 단계(850)를 나타내는 평면도 및 측면도이다. 상기 단계(850)는 다시 본드 패드(204) 위치를 비어(702) 위치에 전기적으로 연결시키는 금속 트레이스(206)의 금속 패터닝에 대해 도 8A 및 도 8B에 도시된 것과 유사하다.

<41> 도 17a 및 도 17b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 8 단계(950)를 나타내는 평면도 및 측면도이다. 비어(702)는 도시된 바와 같이 비어 홀(702)를 충진하고 금속 비어(902)를 형성하기 위해 플러그(plugged)되거나, 도금되거나, 만약 그렇지 않으면 전동성 재료로 용착된다.

<42> 금속 비어(902) 형성 공정 후에, 비어 홀 웨이퍼(960)가 도시된 제 9 단계를 나타내는 도 18a 및 도 18b에 도시된 추가 다이싱 테이프(410) 상으로 운송된다.

<43> 도 19a 및 도 19b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 10 단계를 나타내는 평면도 및 측면도이다. 컷 텅 쏘스(402)는 다시 비어 홀 웨이퍼(960)을 도시된 세그먼트(970)에 싱글레이트하기 위해 사용되고, 그 결과 캡(904)이 형성된다. 마지막 단계로서, 제 2 싱글레이션 공정 후에, 다이 퍼 앤 플레이스 장치가 사용되어 다이싱 테이프(410)으로부터 각 장치(200)을 제거할 수 있다.

<44> 도 20은 다이 대 다이 적층 구성을 이용하는 THV 적층 반도체 장치(910)의 제조 방법에 따른 제 3실시예의 제 8 단계를 나타내는 측면도이다. 일련의 장치(200)가 도시된 바와 같이 적층되어 특수한 응용을 이를 수 있다. 금속 비어(902)의 각각은 직접 비어 금속 본딩 공정을 이용해서 연결(912)될 수 있다. 당업자는 원하는 구현을 실현하기 위해서 도시된 바와같이 적층될 수 있는 장치(200)의 숫자를 가상할 수 있다.

<45> 도 21은 솔더 페이스트(916)를 포함하는 다이 대 다이 적층 구성을 이용하는 THV 적층 반도체 장치(910)의 제조 방법에 따른 제 4실시예를 나타내는 측면도이다. 솔더 페이스트(solder paste)(916)는 작은 솔더 입자와 유제(flux)의 혼합물을 포함한다. 다양한 재료의 다양한 솔더 페이스트가 포함될 수 있다. 솔더 페이스트(916)는 재유동(reflow) 솔더링 방법을 이용해서 도포되어 적층된 장치(914) 각각 사이에서 강한 금속적 본드(metallurgical bond)를 이를 수 있다.

<46> THV 적층 반도체 장치에 따른 제 5실시예가 도 22에 도시되었다. 본 실시예는 평면도에 도시된 바와 같이 금속 트레이싱(206)과 적절하게 연결된 본드 패드(204)의 멀티플 로우와, 비어 홀(902)의 멀티플 로우를 포함한다. 각 비어 홀(902)은 도시된 바와 같이, 유기 재료(602)에 용착된다. 본드 패드(204)의 멀티플 로우와 비어 홀(902)의 멀티플 로우를 갖는 다수의 다이(202) 구성의 구현될 수 있다. 본 실시예(918)에 추가하여, 다른 실시예가 실현될 수 있는데, 그것은 도시된 하프-컷 외측(outer) 비어(902)를 다이(202)의 활성면 상에 위치되지 않지만, 추가 다이(202) 또는 특별한 구현이 요구되는 다른 곳과 같은, 추가적인 표면에 위치되는 본드 패드(204)에 연결한다.

<47> THV 적층 반도체 장치(920)에 따른 제 6실시예가 도 23에 도시되었다. 상기 장치(920)는 본드 패드(204), 트레이스(206), 및 다이(202)의 대향 측에 위치된 일련의 하프-컷 비어(902)를 도시하고 있다. 여기서 다시, 다이(902)는 도시된 다이(202) 각 주연면에 위치한 유기 재료(602)에 형성된다. 도시된 실시예(902)의 변형에서, 한 구성은 완성형 비어(902)를 포함할 수 있다.

<48> THV 적층 반도체 장치(922)에 따른 제 7실시예가 도 24에 도시되었다. 상기 장치(922)는 도시된 다이(202)의 대향측 상에 위치한 소위 일련의 "더미" 비어 홀(924)을 포함한다. 비어(902)는 도시된 좌우 핸드(hand) 사이드 상에 위치된다. 더미 비어 홀(924)은 특수한 적용을 위해서 장치(924)를 통해서 전기적 접속을 제공한다. 더미 비어 홀(924)은 와이어(wire) 본딩 공정을 사용해서 다른 장치(922) 또는 패키지를 연결하는데 사용될 수 있다. 또한, 홀(924)은 입력/출력(I/O) 신호용 그라운드 또는 회로로서 작용할 수 있다.

<49> 더미 홀(924)은 다양한 구현에서 비어(902)와 같은 구성일 수 있다. 예를 들면, 멀티플 로우 또는 완성형 전 또는 하프-컷 홀(924)이 구현될 수 있다. 도 25는 장치(926)의 그러한 실시예를 도시하고 있는데, 다이(202)의 좌측 상에 하프-컷 비어(924)의 로우와, 다이(202)의 우측상에 THV(902)의 로우를 포함하고, 다시 유기 재료(602)에 위치된다.

- <50> 도 26은 상부 다이(203)를 와이어 본딩 공정으로 연결하기 위한 도 24 및 도 25에 도시된 더미 비어 홀(902)을 이용하는 두 개의 적층 다이(202, 203)를 도시하는, THV 적층 반도체 장치(928)에 따른 제 9실시예를 도시하고 있다. 일련의 본드 패드(205)가 다이(203)의 활성면 상에 위치된다. 와이어 본드(207)는 본드 패드(204)를 비어(902)에 연결시킨다. 유전체, 절연체 또는 본딩 재료가 다이(202, 203) 사이에 위치되어 장치/패키지(928)에 대한 구조적 지지를 제공한다.

- <51> 일련의 THV(226, 902)을 포함하는 장치(200)와 같은 반도체 장치는 다양한 적용에서 다양한 기능성과 신축성을 제공할 수 있다. 유기 재료(210)의 사용은 비어(226)를 다이(202) 외측에 위치되게 하고, 다이(202) 내에 추가 회로를 가능하게 하여 장치(200)의 기능성을 향상시킬 수 있다. 또한, 웨이퍼(300) 재료 대신에 유기 재료(210)를 사용함으로써, 웨이퍼당 각 수율이 증가된다. 유기 재료는 어떤 수의 응용에서 다양한 비어(226)을 수용하는데 필요한 두께 정도로 구성될 수 있다.

- <52> THV(226)를 사용하는 장치(200)는 다양한 PoP 구성내에 포함될 수 있다. 그러한 장치는 일체형 THV(226)을 갖는 반도체 다이를 포함할 수 있다. 그러한 반도체 다이는 THV 다이로서 참조될 수 있다. 현재의 패키지-인-패키지(Package-in-Package)(PiP) 패캐이징 기술들은 와이어 및/또는 범프 상호 접속들을 이용하여 다이들, 인터포저들(interposers) 및 패키지들 사이에 전기 신호들을 제공한다. 보다 강하고, 효율적인 공간 절약형 상호 접속부 제공에 대한 욕구가 점증하고 있다. 그러한 상호 접속부를 제공하는 226과 같은 THV 구조체, 따라서 THV 다이의 사용은 보다 강하고, 효율적인 공간 절약형 상호 접속부를 제공할 수 있다.

- <53> 도 27a를 참조하면, THV 적층 반도체 장치(220)의 제 10의 예시적인 실시예가 도시되었다. 장치(220)는 다이(202)를 포함한다. 유기 재료(210)가 다이(202)의 주연면(214)을 중심으로 위치된다. 상기 유기 재료는 예를 들면, 다이(202)의 측부(216, 218)를 따라서 위치된다. 본드 패드(204)가 다이(202)의 상면상에 형성되거나 상면내로 일체화된다. 도전성 재료가 금속 트레이스(metal trace)를 경유하여 위치된 본드 패드(204)는 THV(226)에 연결된다. 일련의 RDL과 상호 접속 패드들이 앞서 도시된 구조체에 위치되거나 또는 다이(202)의 상면내에 일체화된다. 상기 RDL 및 상호 접속 패드들은 THV 다이 장치(220) 상에 적층되는 다이용의 추가적인 전기 접촉 단자들을 제공한다.

- <54> 도 27b는 전술한 THV 다이(220) 상에 적재되는 제 2 반도체 다이(224)를 포함하는 THV 다이 구조체(220)의 측면도를 나타낸다. RDL/상호 접속패드들은 다이(224)를 전기적으로 연결시키기 위한 일련의 범프들(222)에 접속된다. THV 다이(220)는 전술한 THV 구조체(226)를 포함하는데, 그것은 도시된 바와 같이 다이(202)의 주연면을 중심으로 위치된 유기 재료(210)내로 일체화된다. 일련의 본드 패드(204) 및 금속 트레이스(206)가 신호들을 비어(226)를 관통하여 THV 다이(220)의 상면에 보내기 위한 전기적 통로를 제공한다.

- <55> 도 28a는 캡슐화 및 패키지 적층 기술을 도시하기 위한 PoP 반도체 장치 제조에 대한 예시적인 방법의 제 1단계 장치(228)를 도시하고 있다. 그 장치(228)는 유기 재료(210)내로 일체화된 THV(226)를 다시 포함하는 THV 다이(202)를 포함한다. 일련의 범프들(222)이 범프된(bumped) 다이 또는 플립 칩 다이와 같은 제 2다이 또는 패키지(224)를 THV 다이(202)에 전기적으로 연결시킨다. 하나의 실시예에서, 범프들(222)은 도 27a에 도시된 바와 같이, RDL 및 상호 접속 패드들에 연결된다.

- <56> 예시적인 캡슐화 및 패키지 적층 공정에서의 다음 단계 장치(230)가 도 28b에 도시되었다. 다음 단계 장치(234)가 도 28c에 도시되었다. 캡슐화체(235)가 THV 다이(202) 및 다이(204)의 일부상에 위치된다. 범프(232)의 일부가 THV 다이(202)의 저부와 같이 노출된다. THV 다이(202), 범프(232), 다이(224) 및 범프(222)와 같은 다양한 서브 부품들은 도시된 바와 같은 일체형 회로 패키지내에 위치되는 것으로 참조된다.

- <57> 도 28d에 도시된 다음 단계 장치(238)로서, 제 1패키지(234)가 제 2패키지(234)상에 적층된다. 제 2패키지(234)의 노출된 범프(232)의 상면이 제 1패키지, 따라서 제 1패키지의 THV 다이(202)의 THV(226)의 저면에 연결된다. 그와 같이, 여러 패키지(234)의 비어들(226)은 일련의 부분적으로 노출된 범프들(232)을 사용하여 연결될 수 있다. 캡슐화체(235)가 THV 다이(202) 및 다이(204)의 일부상에 위치될 수 있다.

- <58> 도 29a 내지 도 32b는 하나의 노출된 볼(exposed ball) 및 다이 온 패키지(die on package)를 사용하거나 또는 PoP 구성을 사용하는 반도체 장치 제조에 대한 예시적인 방법에서의 일련의 단계를 도시하고 있다. 도 29a, 30a, 31a 및 32a는 예시적인 방법의 제 1선택을 도시하고, 유사하게, 도 29b, 30b, 31b 및 32b는 예시적인 방법의 제 2선택을 도시하고 있다.

- <59> 도 29a는 THV 다이(202) 상에 위치된 일련의 범프들(222)를 제공하는 공정을 도시하고 있다. 하나의 실시예에서, 범프들(222)은 도 27a에 도시된 바와 같이, 다양한 RDL 및 관련된 상호 접속 패드들에 연결될 수

있다. 범프들(222)은 THV 다이(202)와 제 2다이 또는 패키지 사이에 전기 접속 통로를 제공한다. 도 29b는 THV 다이(202)의 비어(226) 상면상의 범프(222) 형성에 대한 추가적인 선택을 도시하고 있다.

<60> 다음 단계로서, 도 30a는 THV 다이(202)의 일부와 범프(222) 상에 캡슐화체(encapsulant)(236)를 형성하는 공정을 도시하고 있다. 유사한 단계에서, 캡슐화체가 도 30b에 도시된 구성의 범프들상에 형성된다.

<61> 캡슐화체의 일부는 이어서 제거되어 제 1선택에 대한 도 31a 및 제 2선택에 대한 도 31b에 화살표(240)로 표시된 바와 같이, 범프들(222)의 일부를 제거시킨다. 그 캡슐화체는 습식 예칭 또는 화학-기계적 폴리싱(CMP) 공정에 의해 제거된다.

<62> 마지막 단계로서, 제 2다이(224) 또는 제 2패키지(224)가 노출된 범프상에 적층되고, 여기서 범프들(222)은 신호들을 THV 다이(202)로 또는 그것으로부터 다이 또는 패키지(224)로 전달시킨다. 도 32a에 도시된 바와 같이, 다이(224)는 주어진 각각의 범프(222) 구성에 적절하게 크기가 결정된다. 유사하게, 도 32b에 도시된 바와 같이, THV 다이(202)의 주연 예지들까지 연장되는 보다 큰 다이 또는 패키지(224)가 사용될 수 있다. 비어(226)들이 그라운드(ground)로서 또는 다이 또는 패키지에 또는 그로부터의 I/O 신호들의 통로로서 사용될 수 있다. 다이 또는 패키지(224), THV 다이(202), 캡슐화체(236) 및 범프들(222)의 조합은 일체형 회로 패키지로 참조되는데, 그것은 특별한 설정에 맞추어 다양한 구성으로 다시 적층될 수 있다.

<63> 도 33a 내지 도 36은 Fi-PoP(fan-in package-on-package) 구현을 포함하는 PoP 구성을 제조하는 다른 예시적인 방법을 도시하고 있다. 도 29a 내지 32b와 유사한 방법에서, 도 33a, 34a 및 35a는 제 1선택을, 반면에 도 33b, 34b, 35b 및 36은 제 2선택을 도시하고 있다.

<64> 도 33a를 참조하면, THV 다이(202)가 제공된다. 선택적인 실시예에서, 일련의 범프들(241)이 도 33b에 도시된 바와 같이, 비어들(226)상에 용착될 수 있다. 도 34a는 도시된 바와 같이 비어들(226), 금속 트레이스들(206) 및 본드 패드들(204) 중의 일부를 커버하는 캡슐을 형성하는 공정들을 도시하고 있다. 캡슐체(244)는 RDL(242) 및/또는 상호 접속 패드(242)를 노출시키기 위해서 THV 다이(202)의 상부를 노출된 상태로 남긴다. 또한, THV 다이(202)의 저면이 노출된 상태로 남는다. 도 34b는 유사한 단계를 도시하고 있는데, 여기서, 캡슐체(244)가 다시 THV 다이의 일부상에 형성되지만, 상호 접속 패드들 및/또는 RDL(242)은 노출된 상태로 남아서, 범프들(241)의 일부에서와 같이, 화살표(243)로 표시된 바와 같은 전기적 연결성을 제공한다.

<65> 도 35a는 다이 또는 패키지(224)를 THV 다이(202) 상에 적층시키는 공정을 도시하는데, 여기서 일련의 범프들(222)은 패키지 또는 다이(224)를 상호 접속 패드 및/또는 RDL을 경유하여 THV 다이(202)에 전기적으로 연결시킨다. 유사한 예에서, 패키지 또는 다이(224)가 도 35b에 도시된 바와 같은 범프를 갖는 실시예상에 부착된다. 범프들(222)은 다이 또는 패키지(224)를 RDL 또는 상호 접속 패드들을 경유하여 THV 다이(202)에 전기적으로 연결시킨다.

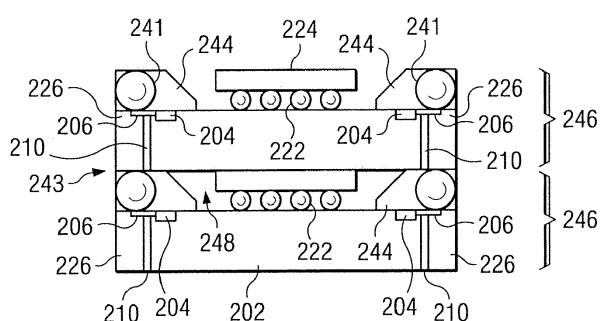

<66> 도 36은 도 33b, 34b 및 35b에 기술된 제 2의 선택적인 방법에서 마지막 단계를 도시하고 있다. 일체형 회로 패키지(246)는 도 35b에 도시된 바와 같이, 추가적인 패키지(246)로 적층되는데, 여기서 비어들(226)은 범프(241)를 사용하여 전기적으로 연결된다. 캡(248)이 두 패키지 사이에 초래될 수 있는데, 그것은 선택적인 언더필 재료의 사용에 의해 감소될 수 있다.

<67> 일부 PoP 배열에서, 상부 및 저부 패키지들은 상부 패키지가 저부 패키지상에 적층된 BGA(ball grid array) 패키지들이다. 상부 패키지는 상부 및 저부 패키지들 사이의 범프들을 경유하여 저부 패키지에 연결된다. 이들 범프들은 저부 패키지의 주연을 중심으로 위치된다.

<68> Fi-PoP는 와이어를 경유하여 베이스 기판에 연결된 260과 같은 인버티드 패키지(inverted package)를 갖는 실시예들로 참조된다. 상기 와이어는 몰딩 재료(molding material)에 의해 캡슐화되고 노출된 중간 캐버티(exposed middle cavity)를 갖는다. 상면 제 2패키지로부터의 전기적 신호가 중앙 캐버티 영역을 경유하여 저면 패키지 내로 전달됨에 따라서, 그 노출된 캐버티 영역은 제 2패키지를 수용할 수 있다. 또한, Fi-PoP는 예비-캡슐화된 패키지를 가질 수 있다. 상기 Fi-PoP는 인터포저(interposer)로 부착된다. 제 2패키지를 수용하기 위해서 와이어들이 부가되고 중간 캐버티를 갖는 캡슐이 노출된다.

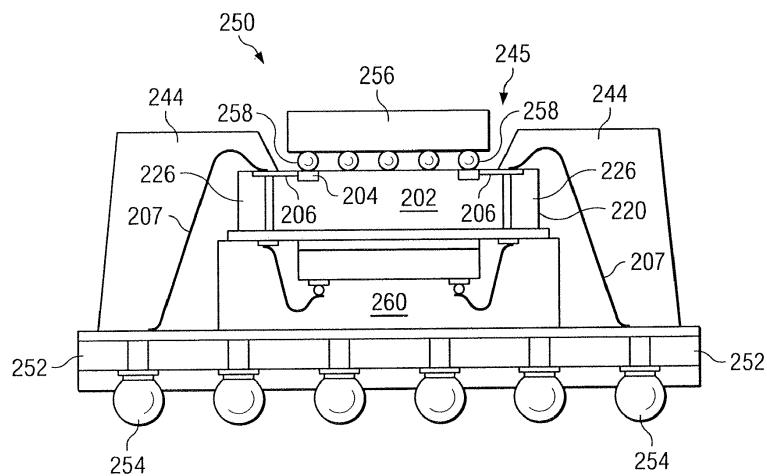

<69> 도 37은 인버티드 패키지(26)상에 위치된 THV 다이(202)를 포함하는 Fi-PoP 구성에 대한 제 1의 예시적인 실시예를 도시하고 있다. THV 다이(202)는 그것의 일체형 회로층들이 상방을 향하도록 정향된다. THV 다이(202)는 회로 캐리어(circuit carrier) 기판(252) 상에 위치되거나, 또는 리드프레임 재료상에 또한 위치될 수 있다. 도시된 실시예에서, 기판(252)은 전기적 접속성을 제공하는 일련의 범프들(254)을 포함한다. 추가적인 다이 또는 패키지(256)가 THV 다이(202)상에 위치되어 전기적으로 연결된다. 캡슐화체(244)가 THV 다이(202), 인버티

드 패키지(260) 그리고 THV 다이(202)를 기판(252)에 연결시키는 와이어 본드(207)의 일부상에 위치된다. 상기 캐슬화체는 비어(226)와 본드 패드(204) 사이, 즉 도시된 금속 트레이스들(206)의 대략 중간에서 종료되도록 형성된다. 비어들(226)은 상면의 일체형 회로 또는 와이어 및/또는 범프 상호 접속체들을 사용하는 패키지(256)에 연결되도록 사용될 수 있다. 도시된 실시예에서, 범프들(258)은 상호 접속을 제공하도록 사용된다.

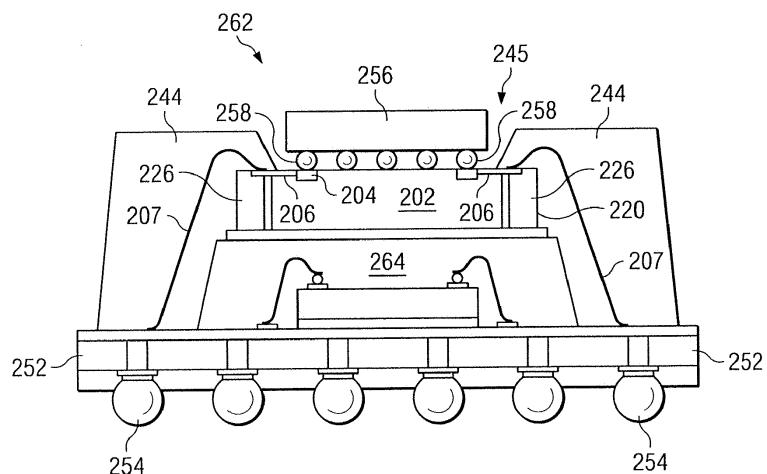

<70> 도 38은 Fi-PoP 구성에 대한 제 2의 예시적인 실시예를 도시하고 있는데, 여기서 THV 다이(202)는 회로 캐리어 기판 또는 리드프래임 패키지(252) 상에 위치되는, 표준 패키지(264)상에 위치된다. THV 다이(202)는 다시 기판(252)에 직접 와이어-본디드(wire-bonded)된다. 추가적인 패키지 또는 다이(256)가 다시 범프들(258)을 경유하여 THV 다이(202)에 전기적으로 연결되는 것으로 도시되었다.

<71> 전체에 걸쳐 많은 Fi-PoP 실시예들에 도시된 바와 같이, 패키지 또는 다이(256)는, 플립 칩 베어 다이(flip chip bare die), 쿼드 플랫 네리드(quad flat nonlead)(QFN) 패키지, 스몰 아웃라인 네리드(small outline nonlead)(SON) 패키지, 쿼드 플랫 패키지(quad flat package)(QFP), 랜드 그리드 어레이(land grid array)(LGA), 볼 그리드 어레이(ball grid array)(BGA)와 같은 장치, 또는 공지된 양호한 다이가 포함되는 유사한 장치 또는 패키징 구성들을 포함한다.

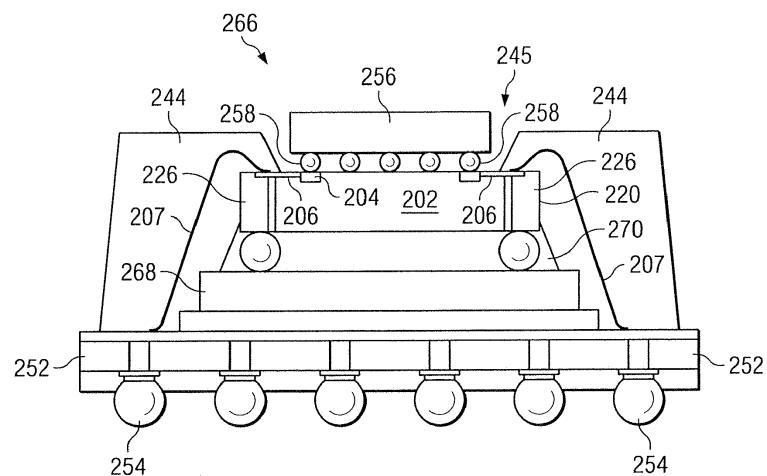

<72> 도 39는 Fi-PoP 구현에 대한 제 3실시예(266)를 도시하고 있는데, 여기서 THV 다이(202)는 탑-사이드 업 플립 칩 다이(top-side up flip chip die)(268)에 포함되고 그 상부에 위치된다. 상면 다이(256) 또는 패키지(256)가 범프들 상호 접속부(258)를 경유하여 THV 다이(202)에 전기적으로 연결된다. THV 다이(202) 아래에 위치되는 언더필 재료(underfill material)는 선택적이다.

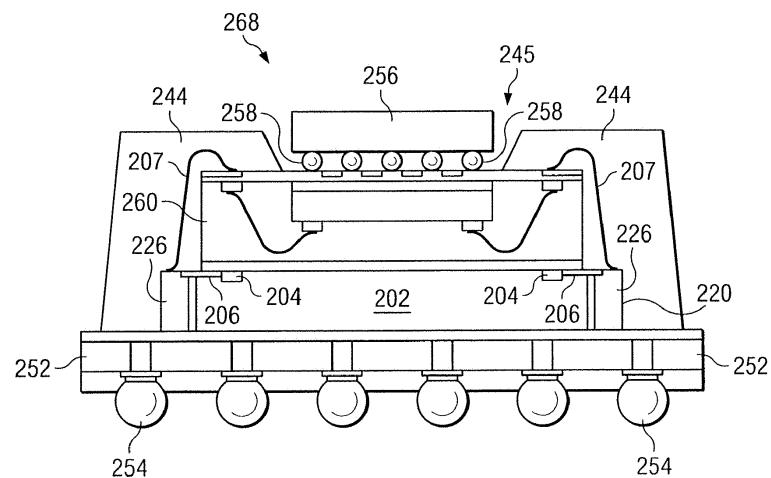

<73> 도 40은 Fi-PoP 구현에 대한 제 4실시예(268)를 도시하는데, 여기서 THV 다이(202)는 도시된 바와 같이 와이어(207)를 이용하여 비어들(226)에 와이어-본디드(wire-bonded)된 인버티드(inverted) 패키지 아래에 위치된다. 도시된 실시예는 또한 THV 다이(202)의 구현에 대한 신축성을 도시하고 있다.

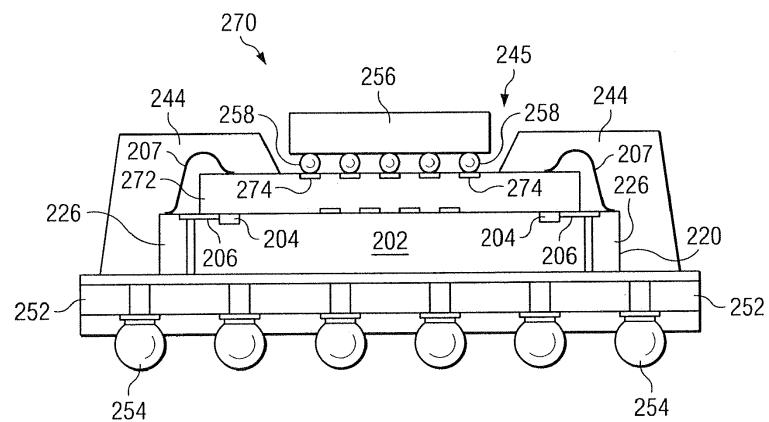

<74> 제 5실시예에서, THV 다이는 도 41에 도시된 바와 같이, 인터포저 장치(interposer device)(272)에 와이어 본디드된다. 그 인터포저는 THV 다이(202)와 상면 다이 또는 패키지(256) 사이에 신호 통로를 제공하는 인터페이스로서 작용한다. 상기 인터포저(272)는 도 40에 도시된 방법과 유사하게 비어들(226)에 와이어-본디드된다.

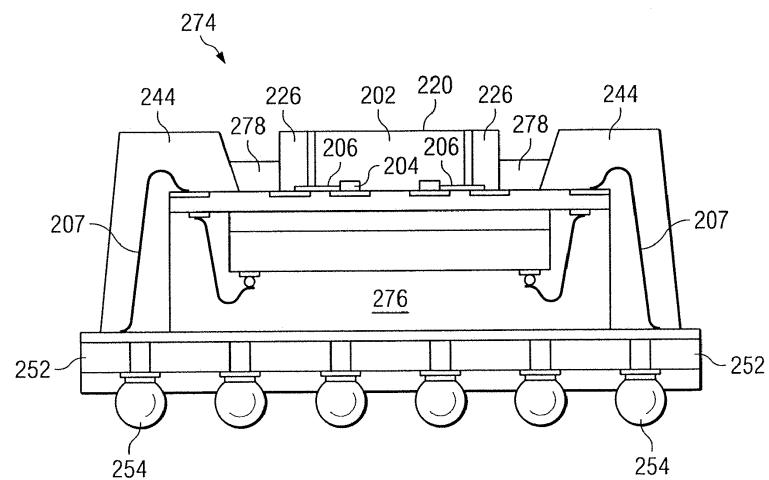

<75> Fi-PoP 구현의 제 6실시예(274)가 도 42에 도시되었는데, 회로 캐리어 기판(252)상에 다시 위치되거나 또는 리드프래임상에 위치될 수 있는 인버티드 장치(276)를 도시하고 있다. 제 2캐슬화체(278)가 선택적으로 THV 다이(202)와 캡슐화체(244) 사이에 형성된 캡 사이에 위치될 수 있다. 도시된 실시예에서, THV 다이는 장치(276)와의 전기적 접촉을 위해서 일체형 회로층이 아래로 접하는 상태를 유지하게 정향된다.

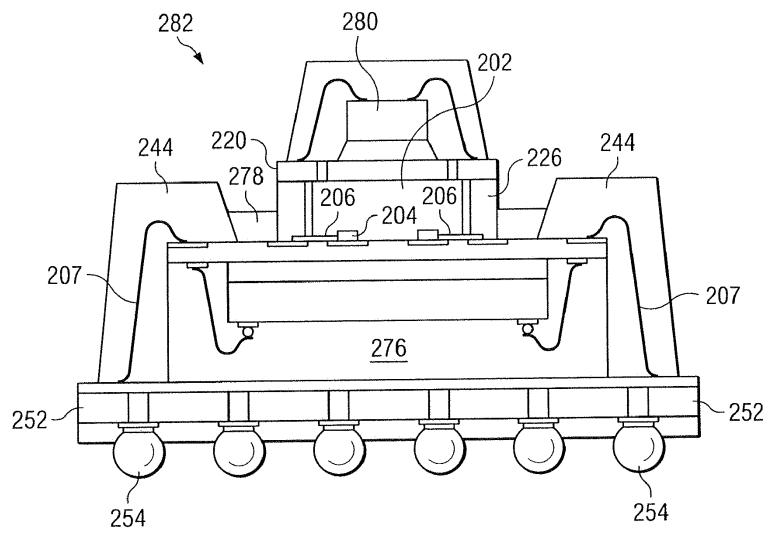

<76> 유사한 실시예(282)가 도 43에 도시되었는데, 여기서 추가적인 패키징(280)이 THV 다이(202)상에 위치된다. 여기서, 패키지(280)의 와이어 본드들이, 패키지(280)를 장치(276)의 상면에 접하는 일체형 회로 층들에 전기적으로 연결시키도록 THV 다이(202)의 비어들(226)를 관통하여 연결된다. 상기 다이(280)는 플립 칩 베어 다이, QFN, QFP, SON, LGA, BGA 또는 공지된 양호한 다이를 포함하는 다른 구현체들을 포함할 수 있다. THV 다이(202)의 신축성은, 특수한 응용에 맞거나, 어떤 성능 사항에 순응하거나, 또는 어떤 치수 요건에 따르도록 THV 다이(202)와 조합하여 구현되어지는 그러한 장치의 다양성을 허용한다.

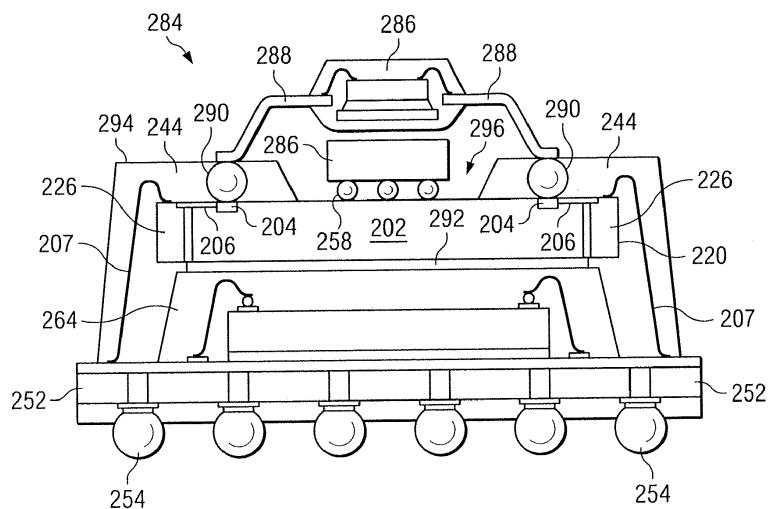

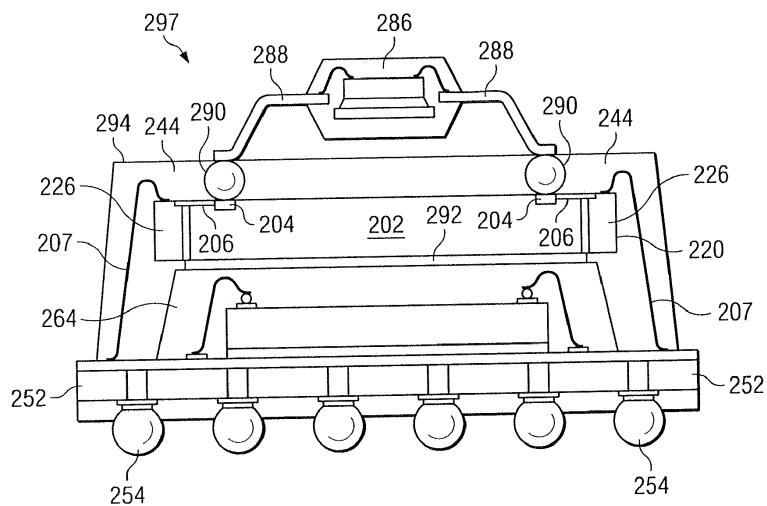

<77> Fi-PoP의 한 실시예(284)는 도시된 한 세트의 노출된 범프들(290)을 사용하는 THV 다이(202)를 도시하고 있다. 범프들(290)은, 장치(280), 즉 BGA, LGA등에 도시된 것과 같은 다양한 장치를 다시 포함할 수 있는, 패키지(286)의 리드프래임(288), 다이(286) 또는 유사한 장치에 연결된다. 도시된 실시예에서, THV 다이(202)는 패키지(264)를 오버행시킨다. 캐슬화체(244)는 THV 다이(202)의 일부와, 패키지(264) 및 범프들(290)를 커버하여 구조적 지지를 제공한다. 도 45에 도시된 유사한 실시예(297)에서, 도 44에 도시된 THV 다이(202)에 직접 장착된 다이(286)가 제거되고, 추가적인 캡슐화체(244)로 대체된다. 도 44 및 도 45 중의 하나에서, THV 다이(202)는 도시된 바와 같이 와이어(207)를 사용하여 비어들(226)로부터 직접 기판(252)에 와이어-본디드된다.

<78> 도 46을 참조하면, THV 다이(202)가, 기판(252)의 일부에 형성된 개방 캐버티(open cavity)(295)를 갖는 기판(252)상에 위치되는 Fi-PoP 구성의 추가적인 실시예(298)가 도시되었다. THV 다이(202)의 일체형 회로 층들은 기판의 개방 캐버티(open cavity)와 접하게 된다. 추가적인 다이(286)가 인버티드된 패키지(260)상에 위치되는데, 여기서 다이(286)는 일련의 범프들(258)을 이용하여 다이(286)를 패키지(260)의 일체형 회로 층에 전기적으로 연결시킨다. 상기 패키지(260)는 다이 어태치(die attach)(D/A) 부착 재료를 이용하여 THV 다이(202)에 연결된다. 유사하게, 추가적인 다이(224)가 THV 다이의 액티브 표면 아래에 위치되고, 그리고 또한 일련의 범프들(258)을 이용하여 THV 다이의 일체형 회로층들에 연결된다. 언더필 재료(underfill material)(299)가 저부 다

이(224) 및 THV 다이(202) 사이에 선택적으로 위치되어 추가적인 구조적 지지를 제공한다.

<79> 도 27 내지 도 46에 다양한 실시예들이 도시된 바와 같이, THV 다이(202)내로 포함된 THV 다이(226)의 사용은 다양한 다이 및 패키지들을 포함하기 위한 신축성있는 다양한 선택을 제공한다. 풋프린트 크기(footprint size) 또는 높이 또는 깊이 요건과 같은 다양한 치수 요건들이 다양한 적층 구성에서 THV 다이(202) 사용을 통해서 만족될 수 있다. 다양한 실시예들에서 THV 다이의 사용은 많은 경우에서 효율적이고 효과적이며 그리고 강한 해법을 제공한다.

<80> 본 발명의 하나 이상의 실시예가 기술되었지만, 당업자는 다음의 첨부된 청구범위에 기술된 바와 같이 본 발명의 범위를 이탈하지 않는 한 그 실시예들의 변형과 변화가 가능함을 이해할 수 있을 것이다.

### 도면의 간단한 설명

<81> 도 1은 웨이퍼 레벨 칩 스케일 패키지(wafer level chip scale package)의 종래 제조 방법의 예(100)를 나타내는 도면이다.

<82> 도 2a 및 도 2b는 각각 THV 적층 반도체 장치(through-hole via stackable semiconductor device)(200)에 따른 제 1실시예를 나타내는 측면도 및 평면도이다.

<83> 도 3a 및 도 3b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 1단계를 나타내는 측면도 및 평면도이다. 웨이퍼(300)가 제공된다.

<84> 도 4a 및 도 4b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 2단계를 나타내는 측면도 및 평면도이다.

<85> 도 5a 및 도 5b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 3 단계를 나타내는 측면도 및 평면도이다.

<86> 도 6a 및 도 6b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 4 단계를 나타내는 측면도 및 평면도이다.

<87> 도 7a 및 도 7b는 각각 도 2a 및 도 2b에 도시된 바와 같은 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 5 단계를 나타내는 측면도 및 평면도이다.

<88> 도 8a 및 도 8b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 6 단계를 나타내는 측면도 및 평면도이다.

<89> 도 9a 및 도 9b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 7 단계를 나타내는 도면이다.

<90> 도 10a 및 도 10b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 1실시예의 제 8 단계를 나타내는 도면이다.

<91> 도 11a 및 도 11b는 각각 다수의 완성형(complete) THV를 포함하는 관통-홀 적층 반도체 장치(906)에 따른 제 2 실시예를 나타내는 평면도 및 측면도이다.

<92> 도 12a 및 도 12b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 3 단계를 나타내는 평면도 및 측면도이다.

<93> 도 13a 및 도 13b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예 제 4 단계를 나타내는 평면도 및 측면도이다.

<94> 도 14a 및 도 14b는 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 5 단계를 나타내는 평면도 및 측면도이다.

<95> 도 15a 및 도 15b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 6 단계를 나타내는 평면도 및 측면도이다.

<96> 도 16a 및 도 16b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 7 단계(850)를 나타내는 평면도 및 측면도이다.

<97> 도 17a 및 도 17b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 8

단계(950)를 나타내는 평면도 및 측면도이다.

<98> 도 18a 및 도 18b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 9 단계를 나타내는 평면도 및 측면도이다.

<99> 도 19a 및 도 19b는 각각 도 2a 및 도 2b에 도시된 THV 적층 반도체 장치 제조 방법에 따른 제 2실시예의 제 10 단계를 나타내는 평면도 및 측면도이다.

<100> 도 20은 다이 대 다이 적층 구성을 이용하는 THV 적층 반도체 장치(910)의 제조 방법에 따른 제 3실시예의 제 8 단계를 나타내는 측면도이다.

<101> 도 21은 솔더 페이스트(916)를 포함하는 다이 대 다이 적층 구성을 이용하는 THV 적층 반도체 장치(910)의 제조 방법에 따른 제 4실시예를 나타내는 측면도이다.

<102> 도 22는 본드 패드의 멀티플 열과 비아 홀의 멀티플 열을 갖는 THV 적층 반도체 장치의 제조 방법에 따른 제 5 실시예를 나타내는 평면도이다.

<103> 도 23은 다이 반대측 상의 본드 패드 로우에 접속된 하프-컷 비어 홀의 로우를 포함하는 THV 적층 반도체 장치의 제 6의 예시적 제조 방법을 도시하는 평면도이다.

<104> 도 24는 반대측 상의 더미 비어 홀을 포함하는 THV 적층 반도체 장치의 제 7의 예시적 제조 방법을 도시하는 평면도이다.

<105> 도 25는 싱글측 상의 더미 비어 홀을 포함하는 THV 적층 반도체 장치의 제 8의 예시적 제조 방법을 도시하는 평면도이다.

<106> 도 26은 상부 다이를 와이어 본딩 공정으로 연결하기 위한 도 24 및 도 25에 도시된 더미 비어 홀을 포함하는 두 적층 다이를 도시하는, THV 적층 반도체 장치의 제 9의 예시적 제조 방법을 도시하는 평면도이다.

<107> 도 27a는 일련의 리디스트리뷰션층(RDL)과 관련된 상호 접속 패드를 포함하는 예시적인 실시예에 대한 정면도;

<108> 27b는 상기 RDL과 상호 접속 패드들에 연결된 부착 다이를 구비한 도 27a에 도시된 THV 다이의 측면도;

<109> 도 28a는 캡슐화체를 포함하는 패키지-온-패키지(PoP) 구성을 만드는 방법과 패키지 적층 기술에 대한 실시예의 제 1단계 장치를 도시하는 도면;

<110> 도 28b는 도 28a로 개시된 예시적인 방법의 제 2단계 장치를 도시하는 도면;

<111> 도 28c는 도 28a로 개시된 예시적인 방법의 제 3단계 장치를 도시하는 도면;

<112> 도 28d는 도 28a로 개시된 예시적인 방법의 제 4단계 장치를 도시하는 도면;

<113> 도 29a 및 도 29b는 각각 제 1및 제 2의 선택적인 실시예에서, 익스포즈드 볼(exposed ball)을 사용한 반도체 장치 제조 방법과, 다이온 패키지(die on package) 기술 또는 패키지 온 패키지 구성에 대한 추가적인 예시적 방법에서 제 1단계를 도시하는 도면;

<114> 도 30a 및 도 30b는 각각 제 1및 제 2의 선택적인 실시예에서, 익스포즈드 볼(exposed ball)을 사용한 반도체 장치 제조 방법과, 다이온 패키지(die on package) 기술 또는 패키지 온 패키지 구성에 대한 추가적인 예시적 방법에서 제 2단계를 도시하는 도면;

<115> 도 31a 및 도 31b는 각각 제 1및 제 2의 선택적인 실시예에서, 익스포즈드 볼(exposed ball)을 사용한 반도체 장치 제조 방법과, 다이온 패키지(die on package) 기술 또는 패키지 온 패키지 구성에 대한 추가적인 예시적 방법에서 제 3단계를 도시하는 도면;

<116> 도 32a 및 도 32b는 각각 제 1및 제 2의 선택적인 실시예에서, 익스포즈드 볼(exposed ball)을 사용한 반도체 장치 제조 방법과, 다이온 패키지(die on package) 기술 또는 패키지 온 패키지 구성에 대한 추가적인 예시적 방법에서 제 4단계를 도시하는 도면;

<117> 도 33a 및 도 33b는 각각 제 1및 제 2의 선택적인 실시예에서, 팬-인 패키지 -온-패키지(Fi-PoP) 구성을 사용하는 반도체 장치 제조에 대한 추가적인 예시적 방법에서 제 1단계를 도시하는 도면;

<118> 도 34a 및 도 34b는 각각 제 1및 제 2의 선택적인 실시예에서, Fi-PoP 구성을 사용하는 반도체 장치 제조에 대

한 추가적인 예시적 방법에서 제 2단계를 도시하는 도면;

<119> 도 35a 및 도 35b는 각각 제 1및 제 2의 선택적인 실시예에서, Fi-PoP 구성을 사용하는 반도체 장치 제조에 대한 추가적인 예시적 방법에서 제 3단계를 도시하는 도면;

<120> 도 36은 Fi-PoP 구성을 사용하는 반도체 장치 제조에 대한 추가적인 예시적 방법에서 제 4단계를 도시하는 도면;

<121> 도 37은 인버티드 패키지 장치상에 위치된 THV 다이를 포함하는 Fi-PoP 구성의 예시적인 실시예를 도시하는 도면;

<122> 도 38은 추가적인 적층을 구비하는 표준 패키지상에 위치된 THV 다이를 포함하는 Fi-PoP 구성에 대한 예시적인 실시예를 도시하는 도면;

<123> 도 39는 탑-사이드 업 플립-칩 다이(top-side up flip-chip die)상에 위치된 THV 다이를 포함하는 Fi-PoP 장치에 대한 예시적인 실시예를 도시하는 도면;

<124> 도 40은 THV 다이상에 위치된 인버티드 패키지 장치를 포함하는 Fi-PoP 장치에 대한 예시적인 실시예를 도시하는 도면;

<125> 도 41은 또 다른 적층을 구비하는 THV 다이상에 위치된 인터포저(interposer) 구조체를 포함하는 Fi-PoP 장치에 대한 예시적인 실시예를 도시하는 도면;

<126> 도 42는 인버티드 패키지상에 위치된 THV 다이를 포함하는 Fi-PoP 패키지에 대한 예시적인 실시예를 도시하는 도면;

<127> 도 43은 또 다른 적층을 구비한 인버티드 패키지상에 위치된 THV 다이를 포함하는 Fi-PoP 패키지에 대한 예시적인 실시예를 도시하는 도면;

<128> 도 44는 익스포즈드 범프를 구비한 THV 다이를 포함하는 Fi-PoP 패키지에 대한 예시적인 실시예를 도시하는 도면;

<129> 도 45는 PoP 구성에서 익스포즈드 범프를 구비한 THV 다이를 포함한 Fi-PoP 패키지에 대한 예시적인 실시예를 도시하는 도면; 그리고

<130> 도 46은 플립 칩 다이를 수용하는 오픈 캐버티(open cavity) 상의 THV 다이를 포함하는 Fi-PoP 패키지에 대한 예시적인 실시예를 도시하는 도면이다.

## 도면

### 도면1

## 도면2a

## 도면2b

## 도면3a

도면3b

도면4a

도면4b

도면5a

도면5b

도면6a

도면6b

도면7a

도면7b

도면8a

도면8b

도면9a

도면9b

도면10a

도면10b

도면11a

도면11b

도면12a

도면12b

도면13a

도면13b

도면14a

도면14b

도면15a

도면15b

도면16a

도면16b

도면17a

도면17b

도면18a

## 도면18b

### 도면19a

도면 19b

도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27a

도면27b

도면28a

도면28b

도면28c

도면28d

도면29a

도면29b

도면30a

도면30b

도면31a

도면31b

도면32a

도면32b

도면33a

도면33b

도면34a

도면34b

도면35a

도면35b

도면36

도면37

도면38

도면39

도면40

도면41

도면42

## 도면43

도면44

도면45

도면46