(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

**(19) World Intellectual Property Organization**

International Bureau

**(43) International Publication Date

15 September 2011 (15.09.2011)**

(10) International Publication Number

**WO 2011/112802 A2**

(51) International Patent Classification:

*H01L 21/3065* (2006.01)

**(21) International Application Number:** PCT/US2011/027881

**(22) International Filing Date:** 10 March 2011 (10.03.2011)

(25) Filing Language: English

(26) Publication Language: English

**(30) Priority Data:** 12/720,942 10 March 2010 (10.03.2010) US

(71) **Applicant (for all designated States except US): APPLIED MATERIALS, INC. [US/US]; 3050 Bowers Av-**

enture, Santa Clara, California 95054 (US).

(73) Inventors/Applicants (for US only): **GANGULY, Udayan** [IN/US]: 470 Boynton Avenue Apt 25 San

**Qayam** [IN/US]; 170 Boynton Avenue, Apt. 25, San Jose, California 95117 (US). **RANISH, Joseph M.** [US/US]; 3751 Woodleaf Court, San Jose, California 95117 (US). **HUNTER, Aaron M.** [US/US]; 430 Eme-line Ave., Santa Cruz, California 95060 (US). **TANG, Jing** [CN/US]; 10405 Wunderlich Dr., Cupertino, California 95014 (US). **OLSEN, Christopher S.** [US/US]; 38642 Moore Drive, Fremont, California 94536 (US). **SCOTNEY-CASTLE, Matthew D.** [GB/US]; 17045 John Telfer Drive, Morgan Hill, California 95037 (US). **NGUYEN, Vicky** [US/US]; 182 Marylinn Drive, Milp-i-

tas, California 95035 (US). **SRINIVASAN, Swaminathan** [US/US]; 1554 Ramblewood Way, Pleasanton, California 94566 (US). **LIU, Wei** [US/US]; 5035 Moorpark Ave., San Jose, California 95129 (US). **SWENBERG, Johanes F.** [US/US]; 128 Mary Way, Los Gatos, California 95032 (US). **SUN, Shiyu** [CN/US]; 4331 Renaissance Dr., Apt. 303, San Jose, California 95134 (US).

**Agent:** SERVILLA, Scott S.; Diehl Servilla LLC, 33 Wood Avenue South, Second Floor, Suite 210, Iselin, New Jersey 08830 (US).

(81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) **Designated States** (*unless otherwise indicated, for every kind of regional protection available*): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK,

[Continued on next page]

**(54) Title:** APPARATUS AND METHODS FOR CYCLICAL OXIDATION AND ETCHING

FIG. 21

**(57) Abstract:** Apparatus and methods for the manufacture of semiconductor devices suitable for narrow pitch applications and methods of fabrication thereof are described herein. Disclosed are various single chambers configured to form and/or shape a material layer by oxidizing a surface of a material layer to form an oxide layer; removing at least some of the oxide layer by an etching process; and cyclically repeating the oxidizing and removing processes until the material layer is formed to a desired shape. In some embodiments, the material layer may be a floating gate of a semiconductor device.

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ,

GW, ML, MR, NE, SN, TD, TG). **Published:**

— *without international search report and to be republished

upon receipt of that report (Rule 48.2(g))*

## APPARATUS AND METHODS FOR CYCLICAL OXIDATION AND ETCHING

## Field

[0001] Embodiments of the present invention generally relate to the field of semiconductor manufacturing processes and devices, and more particularly, to apparatus and methods for the manufacture of devices suitable for use in narrow pitch applications.

## Background

[0002] Scaling semiconductor devices by simply shrinking the device structure often does not produce acceptable results at small dimensions. For example, in NAND flash memory devices, when a floating gate is scaled the capacitive coupling (*e.g.*, sidewall capacitance) of the floating gate is scaled accordingly with the surface area of the floating gate. As such, the smaller the surface area of the floating gate, the smaller the capacitive coupling between the floating gate and, for instance, a control gate. Typically, a trade-off that sacrifices capacitive coupling for scaling is acceptable provided the NAND memory device still functions. Unfortunately, the scaling is limited when the device node becomes sufficiently small such that the capacitive coupling between the floating gate and control gate becomes too small to effectively program the device at permissible operational voltages. Furthermore, parasitic capacitance (*i.e.*, noise) between adjacent floating gates increases beyond the margin for read error of a system controller in a NAND memory device. Thus, a functioning NAND device is not possible under such conditions.

[0003] Methods and apparatus for the manufacture of devices have small surface area, for example, NAND devices and other devices.

## SUMMARY

[0004] Apparatus and methods for manufacturing semiconductor devices suitable for narrow pitch applications are described herein. While the various apparatus and methods described herein are not intended to be limited to the manufacture of a particular type of device, the apparatus and methods described herein are particularly suitable for manufacturing a semiconductor device including a floating gate having a first width proximate a base of the floating gate that is greater than a second width proximate a top of the floating gate. In some embodiments, the width of the floating gate decreases non-linearly from the first width to the second width.

**[0005]** In some embodiments, an apparatus for processing a substrate may include a process chamber having a substrate support disposed therein and configured to support a substrate, the substrate support further having a temperature control system coupled thereto to control the temperature of the substrate support proximate a first temperature; a gas source to provide at least an oxygen-containing gas, an inert gas and an etching gas; a plasma source coupled to the process chamber to provide energy to gases provided by the gas source to form at least one of an oxidizing plasma or an etching plasma; and a heat source coupled to the process chamber to provide energy to the substrate to selectively raise the temperature of the substrate to a second temperature greater than the first temperature. Other and further embodiments of the present invention are described hereinbelow.

**[0006]** According to one or more embodiments, a complete process sequence of an oxidation (and/or nitridation) and an etching step can be completed in the chambers in less than about three minutes. In specific embodiments, a complete process sequence of an oxidation and/or nitridation and an etching step can be completed in the chambers in less than about two minutes, and in more specific embodiments, a complete process sequence of an oxidation and/or nitridation and an etching step can be completed in the chambers in less than about one minute, for example 45 seconds or 30 seconds.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0007]** So that the manner in which the above recited features of the present invention can be understood in detail, a more particular description of the invention, briefly summarized above, may be had by reference to embodiments, some of which are illustrated in the appended drawings. It is to be noted, however, that the appended drawings illustrate only typical embodiments of this invention and are therefore not to be considered limiting of its scope, for the invention may admit to other equally effective embodiments.

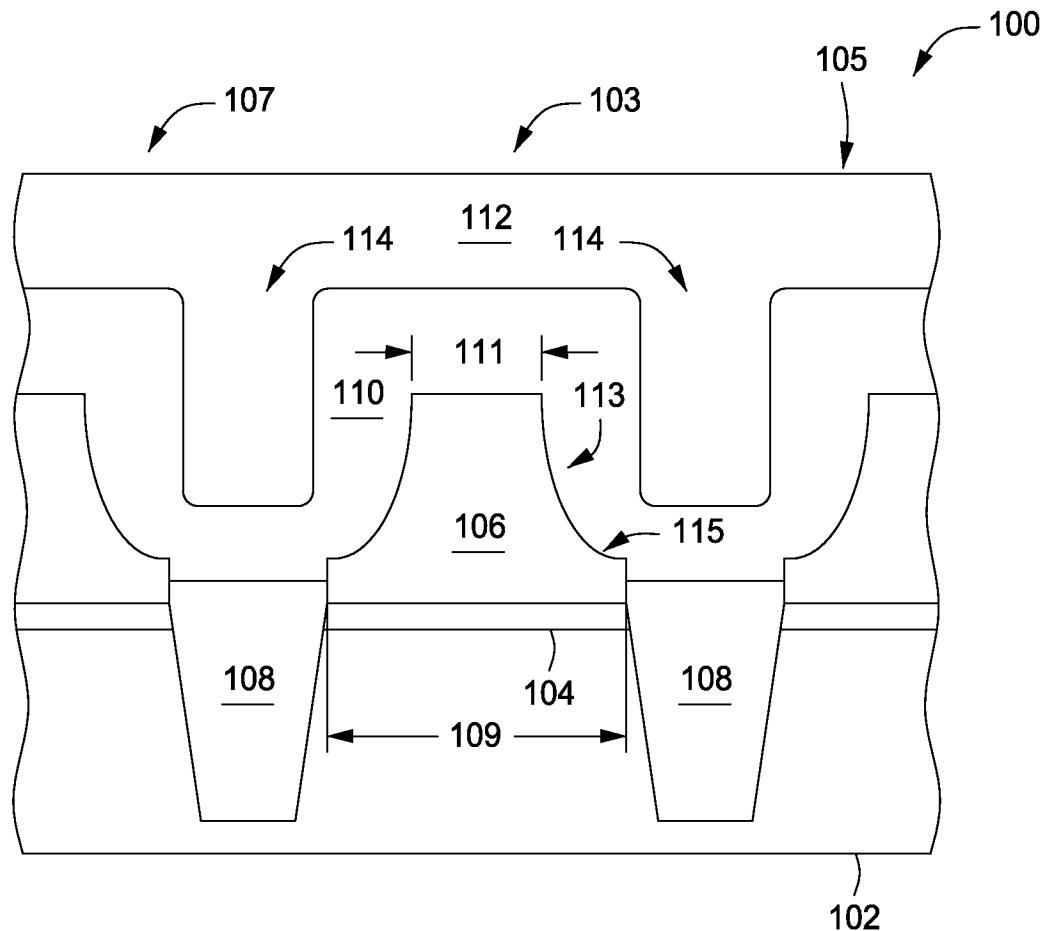

**[0008]** Figure 1 depicts a semiconductor structure having a floating gate made utilizing methods and apparatus in accordance with some embodiments of the present invention;

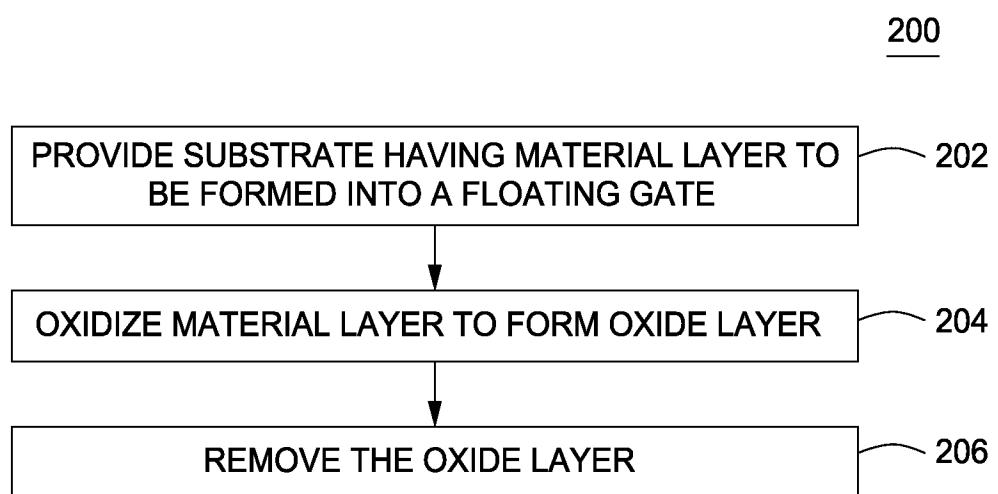

**[0009]** Figure 2 depicts a flow chart for a method of forming a floating gate in accordance with some embodiments of the present invention.

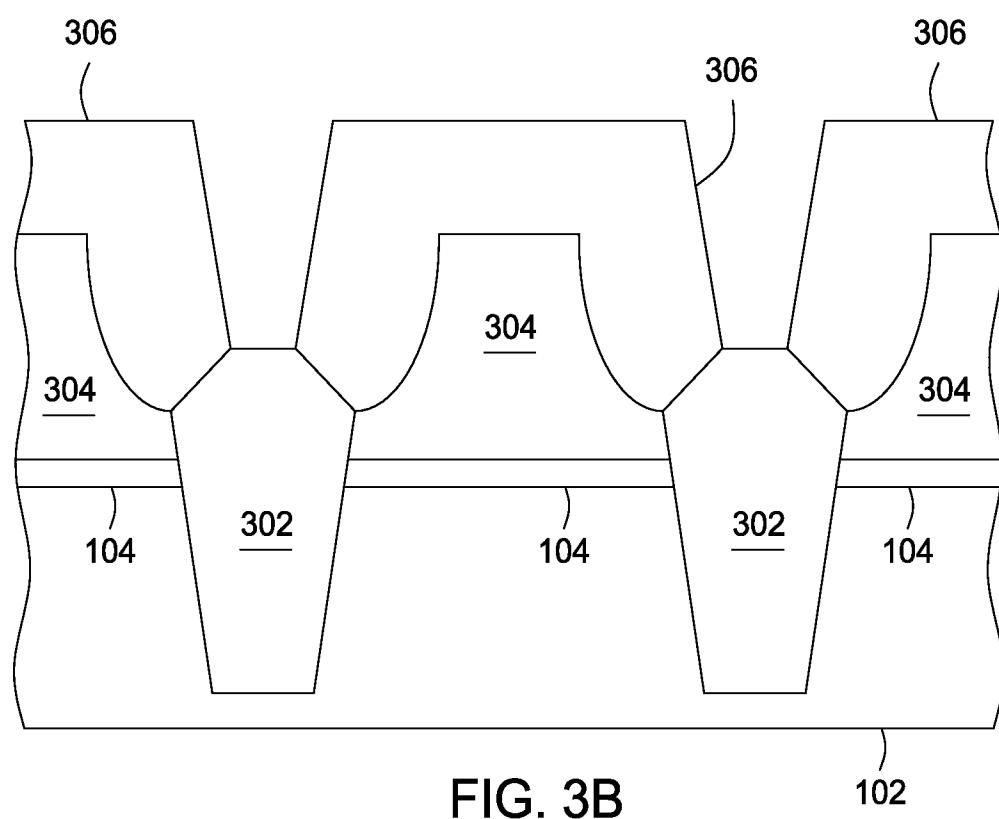

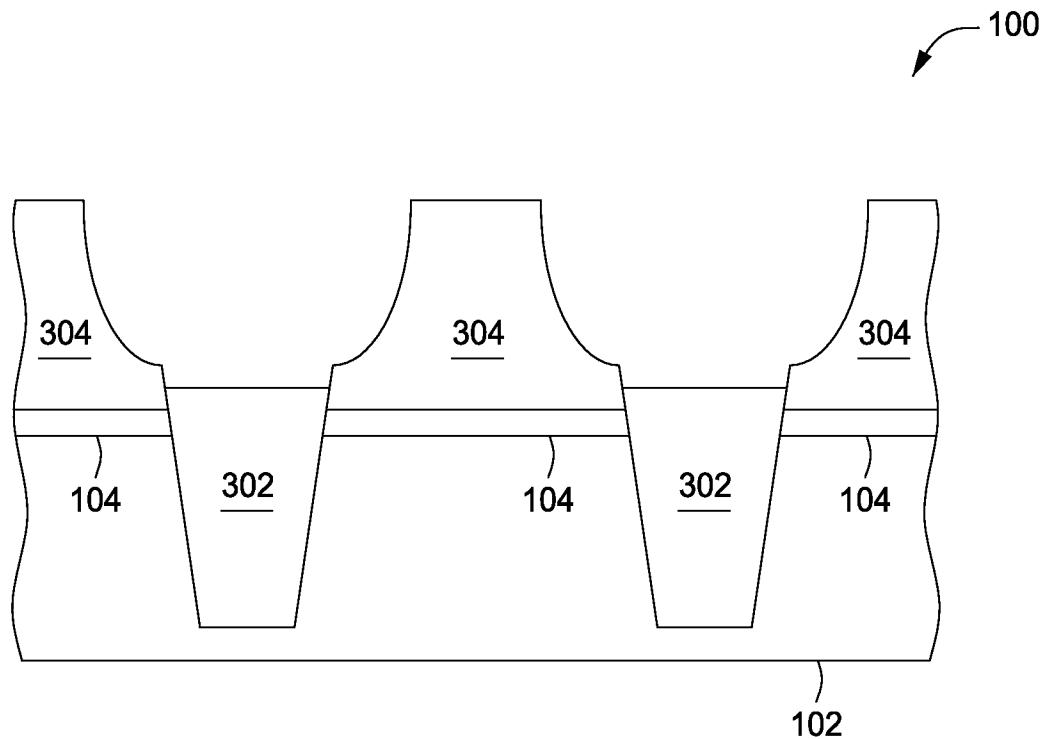

**[0010]** Figures 3A-C depict stages of fabrication of a floating gate in accordance with some embodiments of the method of Figure 2.

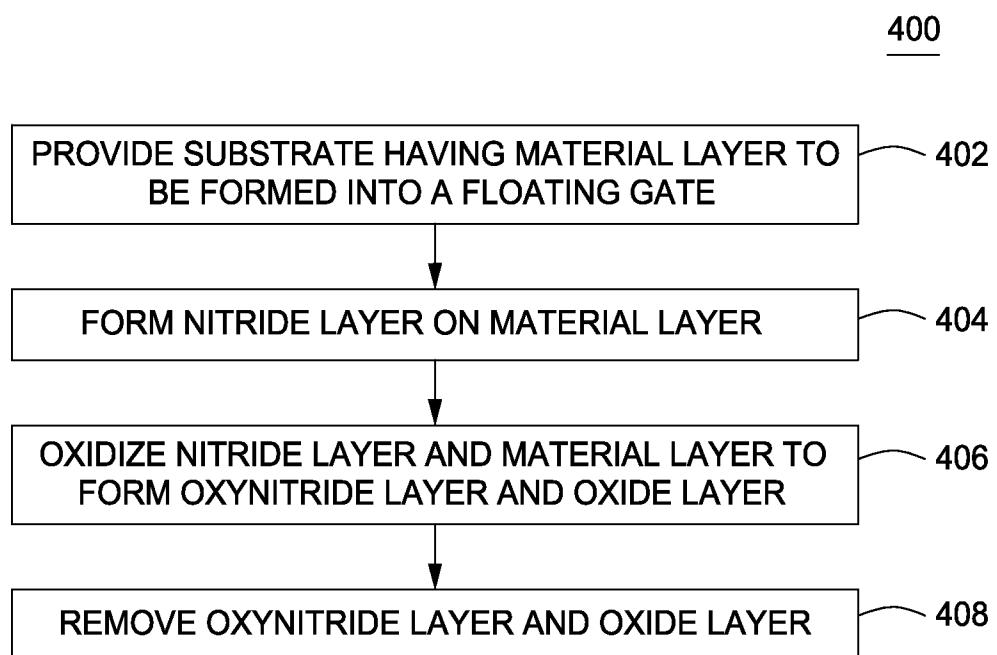

**[0011]** Figure 4 depicts a flow chart for a method of forming a floating gate in accordance with some embodiments of the present invention.

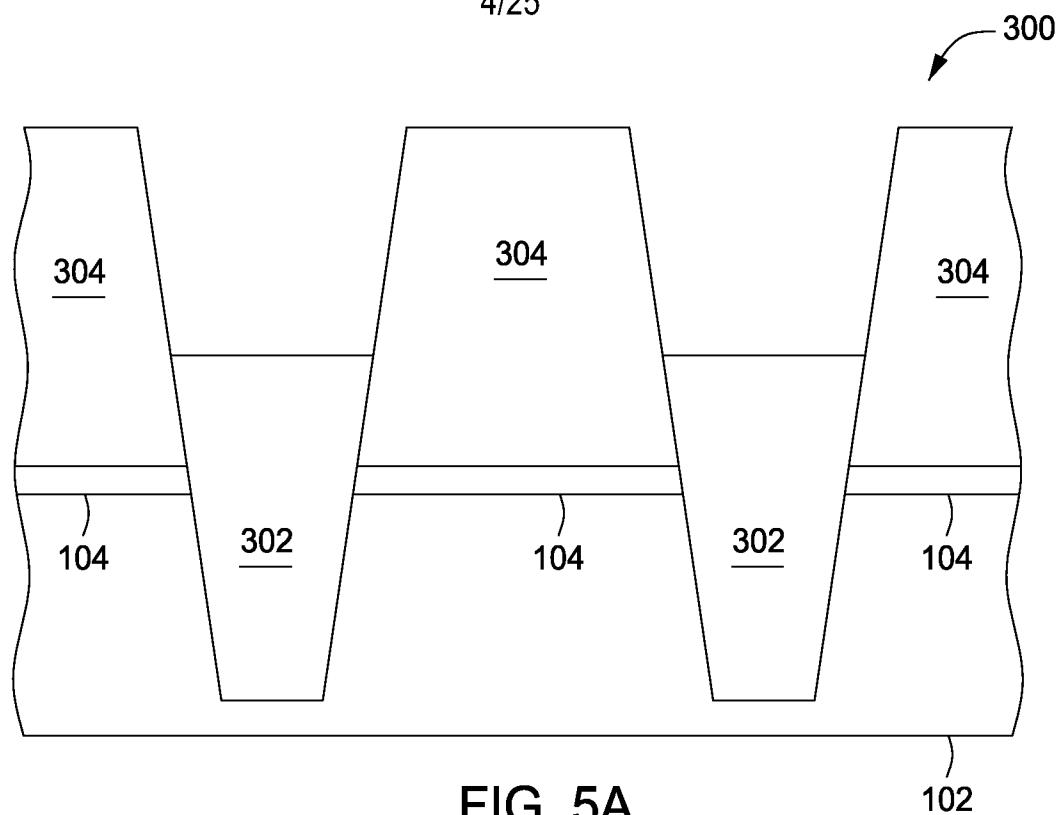

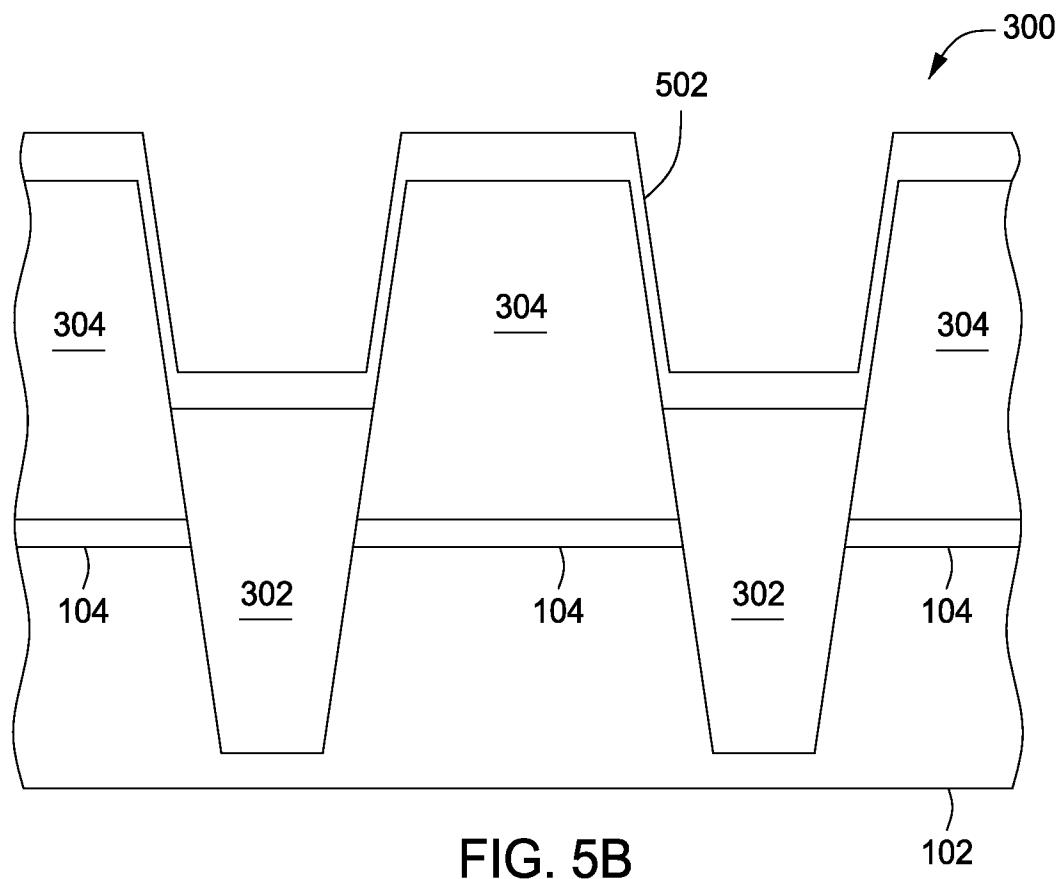

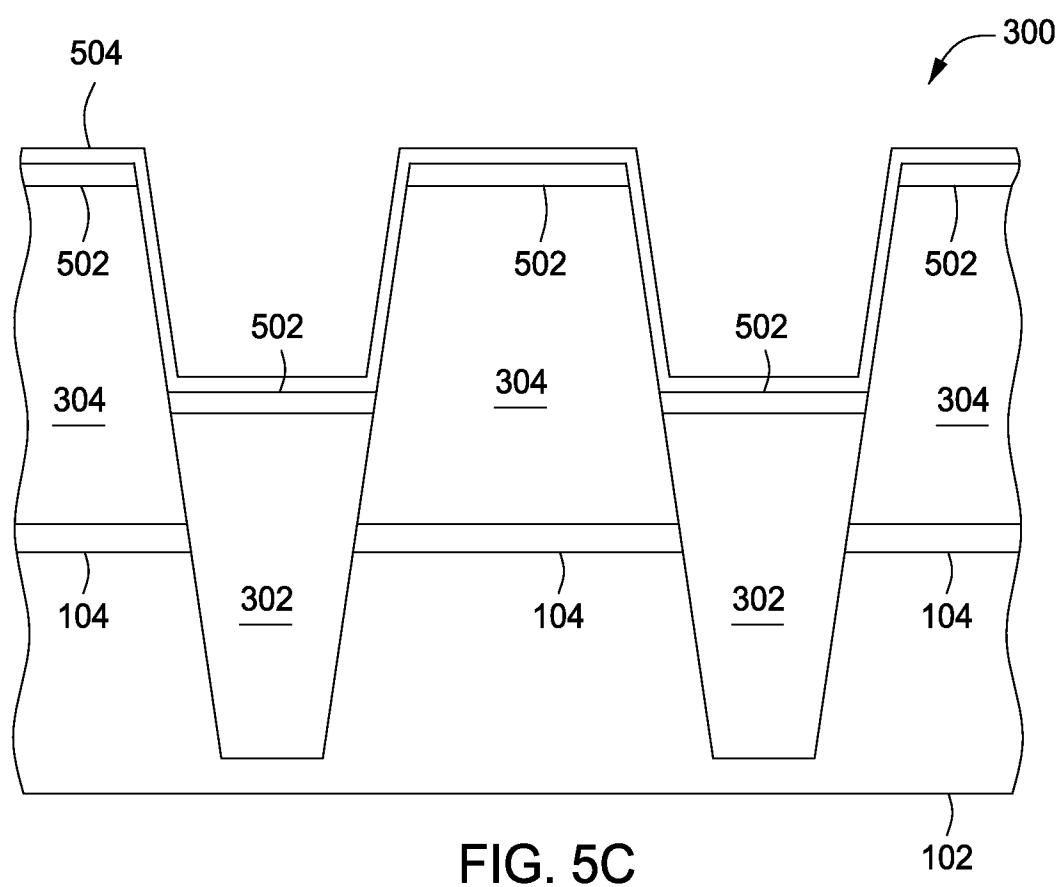

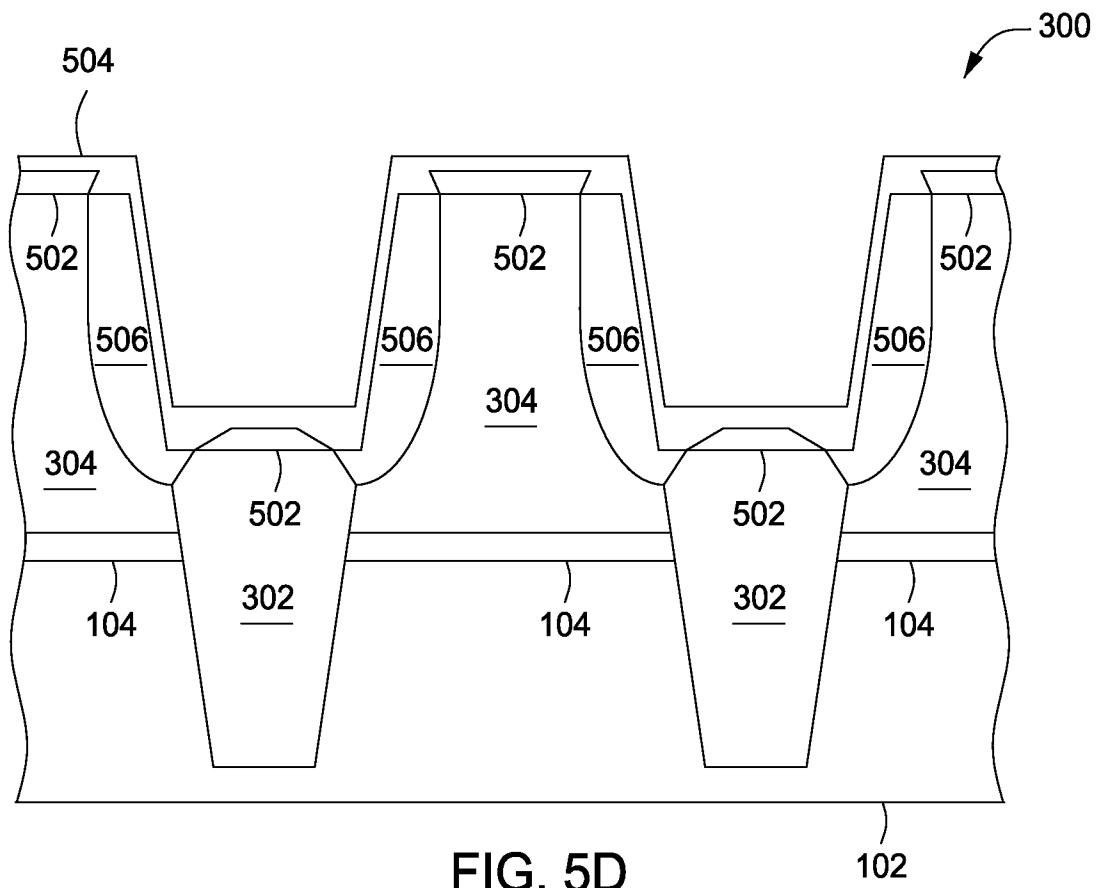

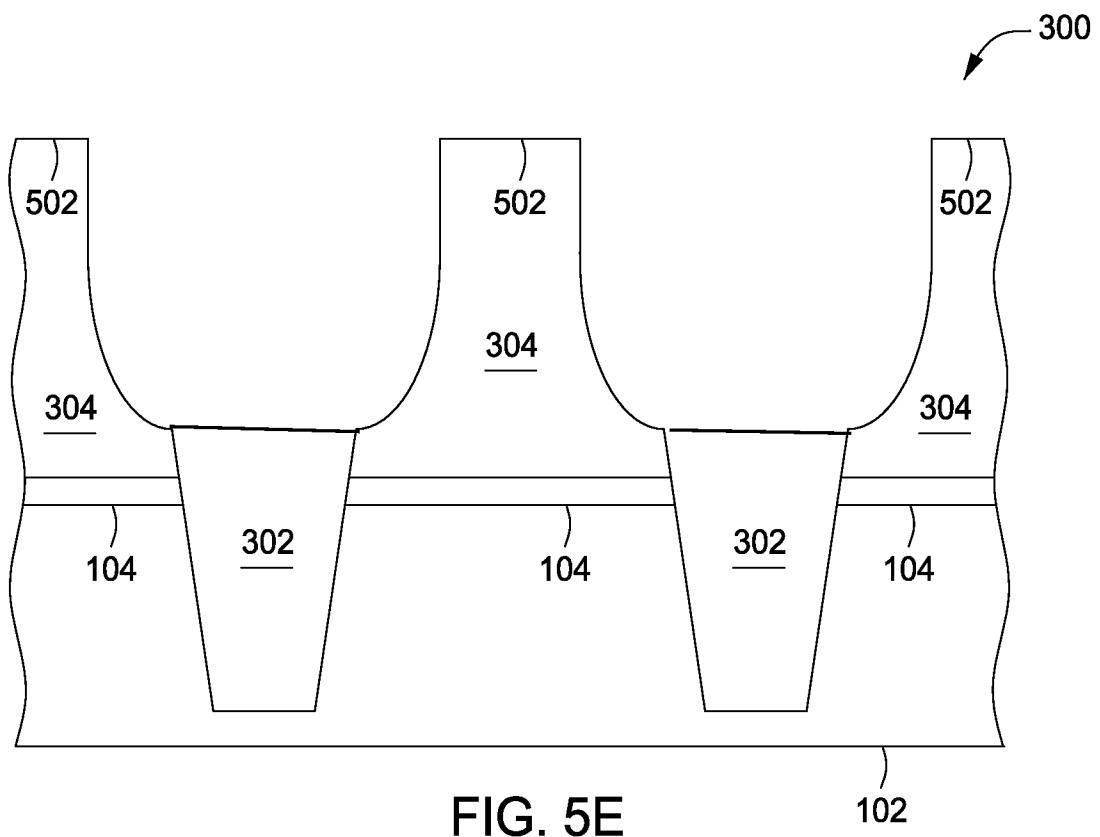

**[0012]** Figures 5A-E depict stages of fabrication of a floating gate in accordance with some embodiments of the method of Figure 4.

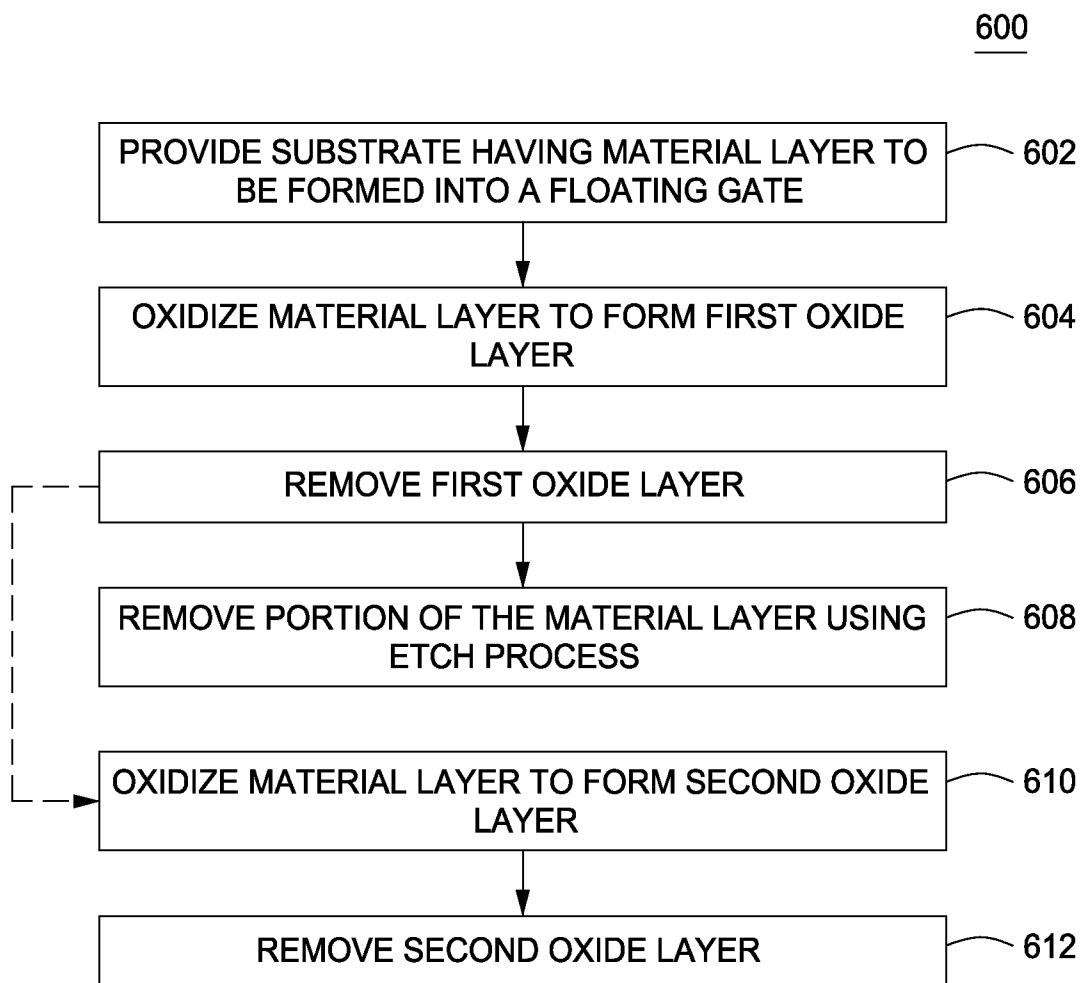

5 **[0013]** Figure 6 depicts a flow chart for a method of forming a floating gate in accordance with some embodiments of the present invention.

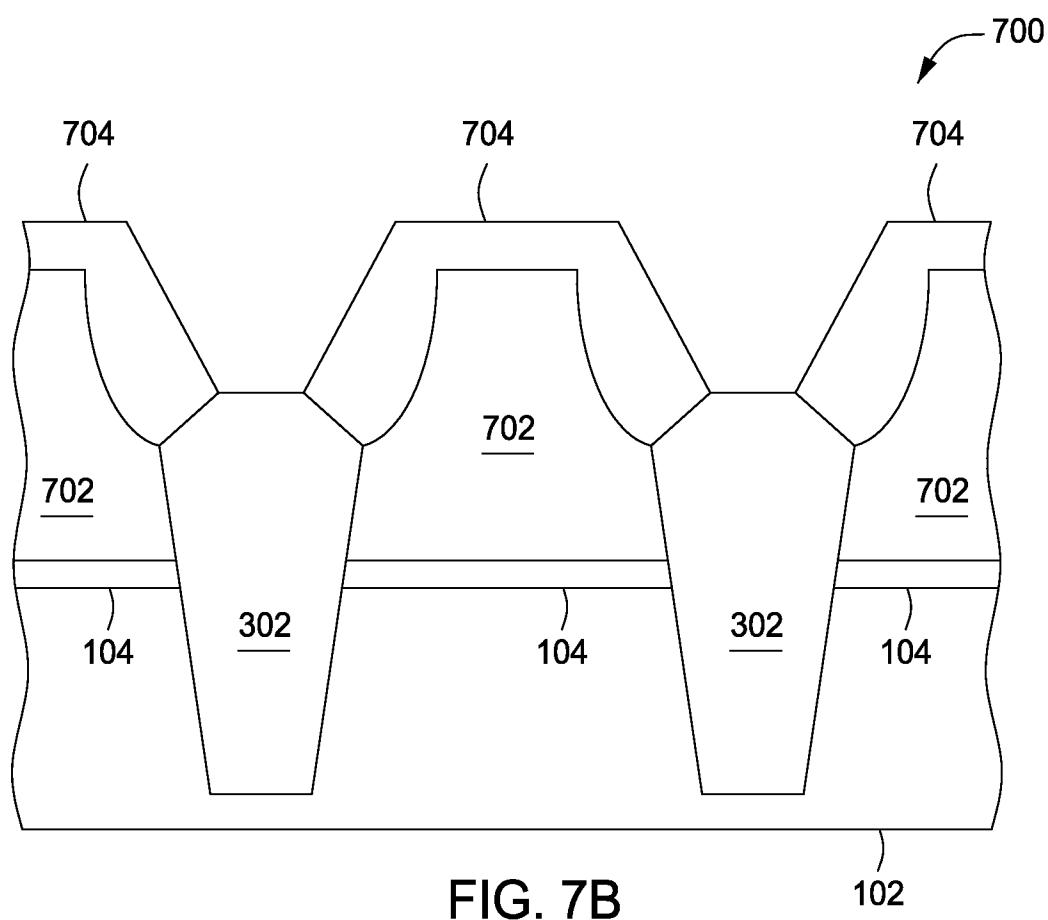

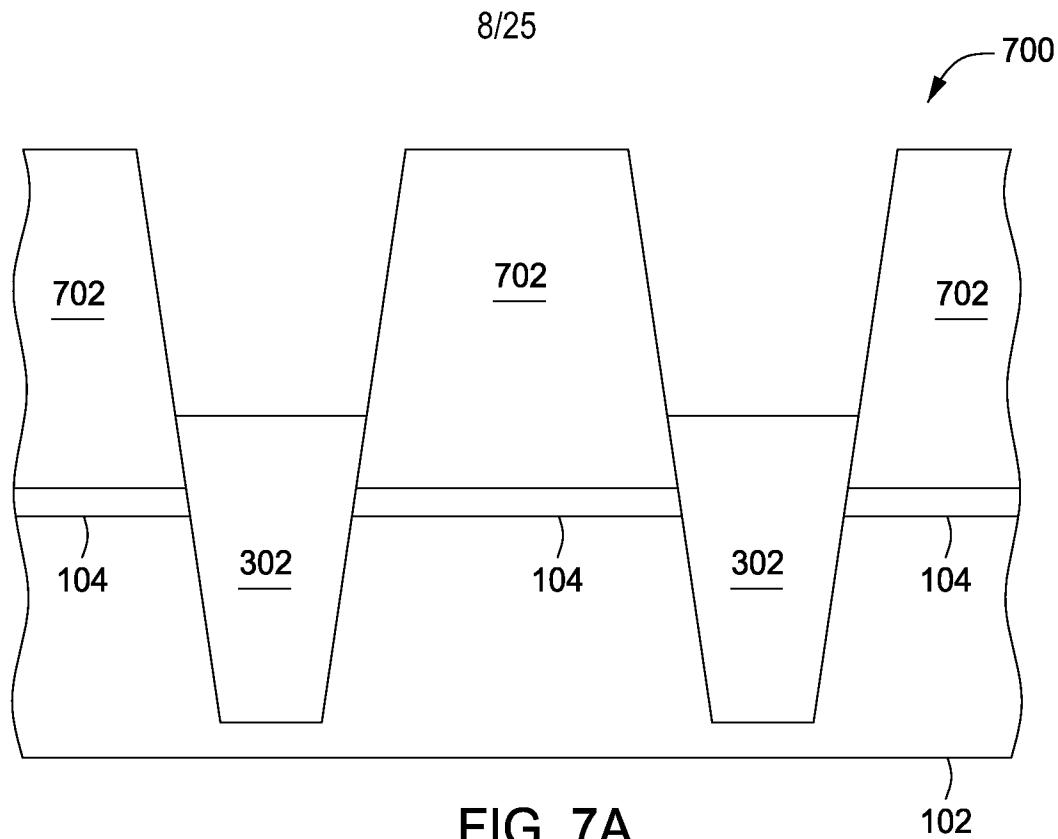

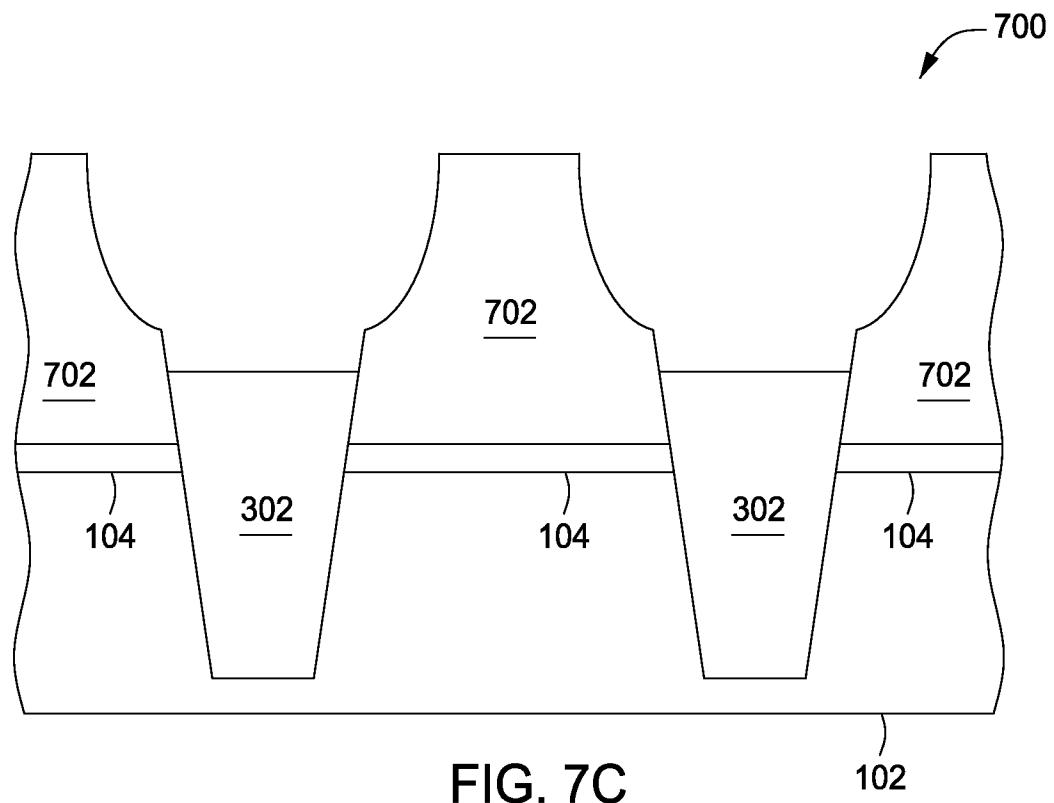

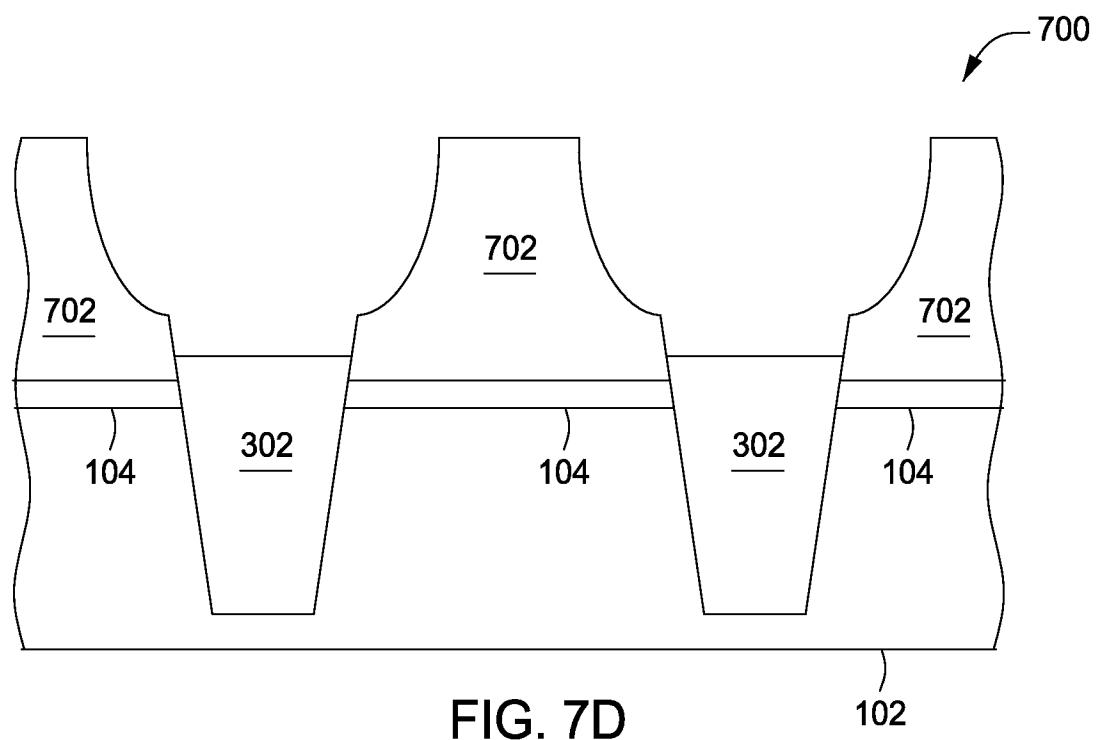

**[0014]** Figures 7A-D depict stages of fabrication of a floating gate in accordance with some embodiments of the method of Figure 6.

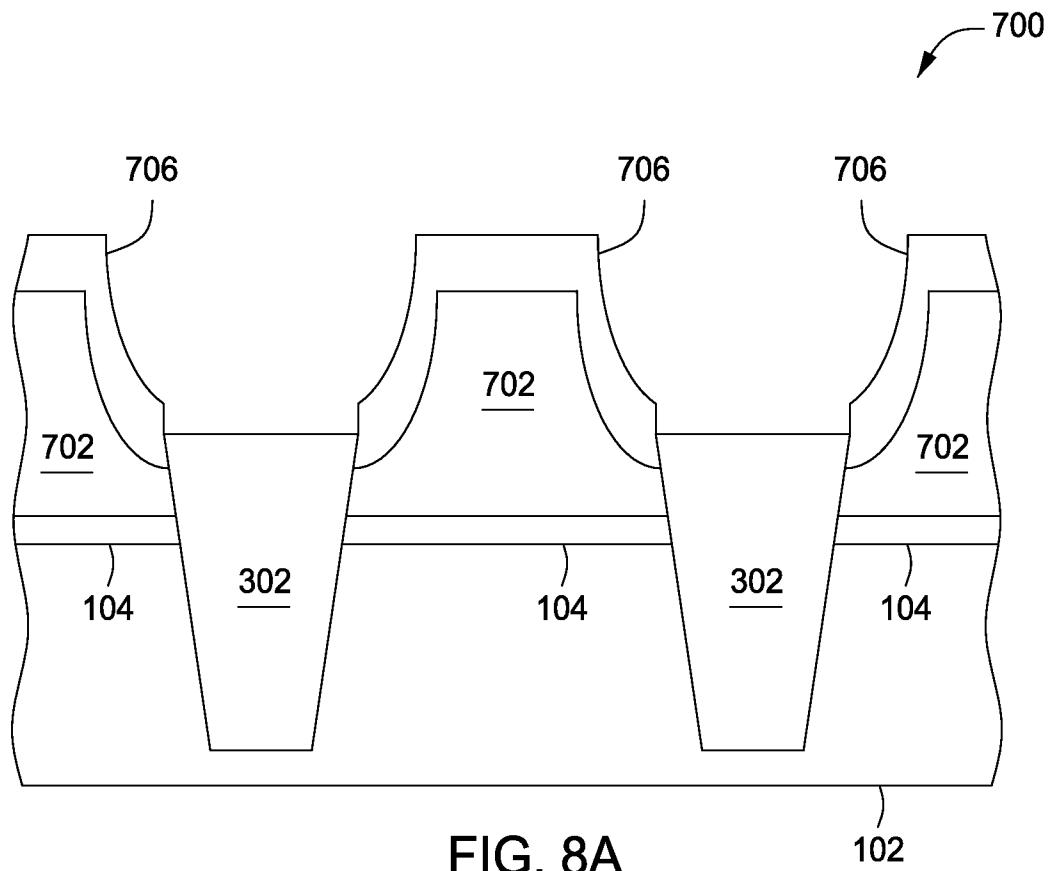

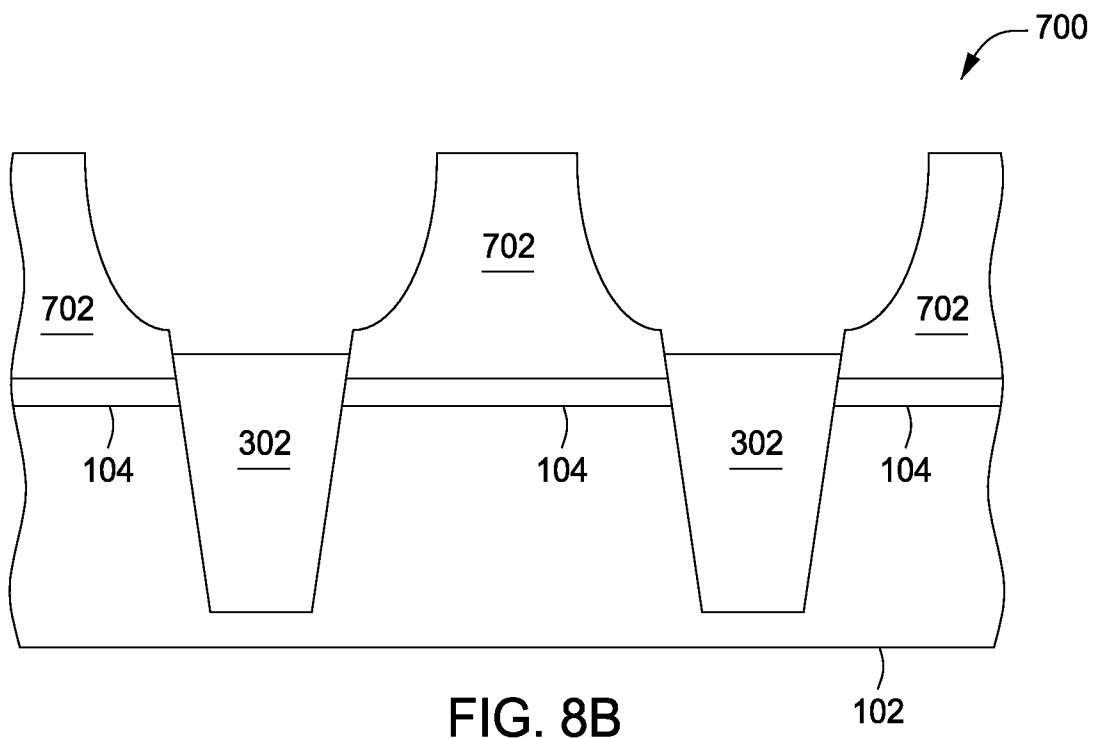

10 **[0015]** Figures 8A-B depict stages of fabrication of a floating gate in accordance with some embodiments of the method of Figure 6.

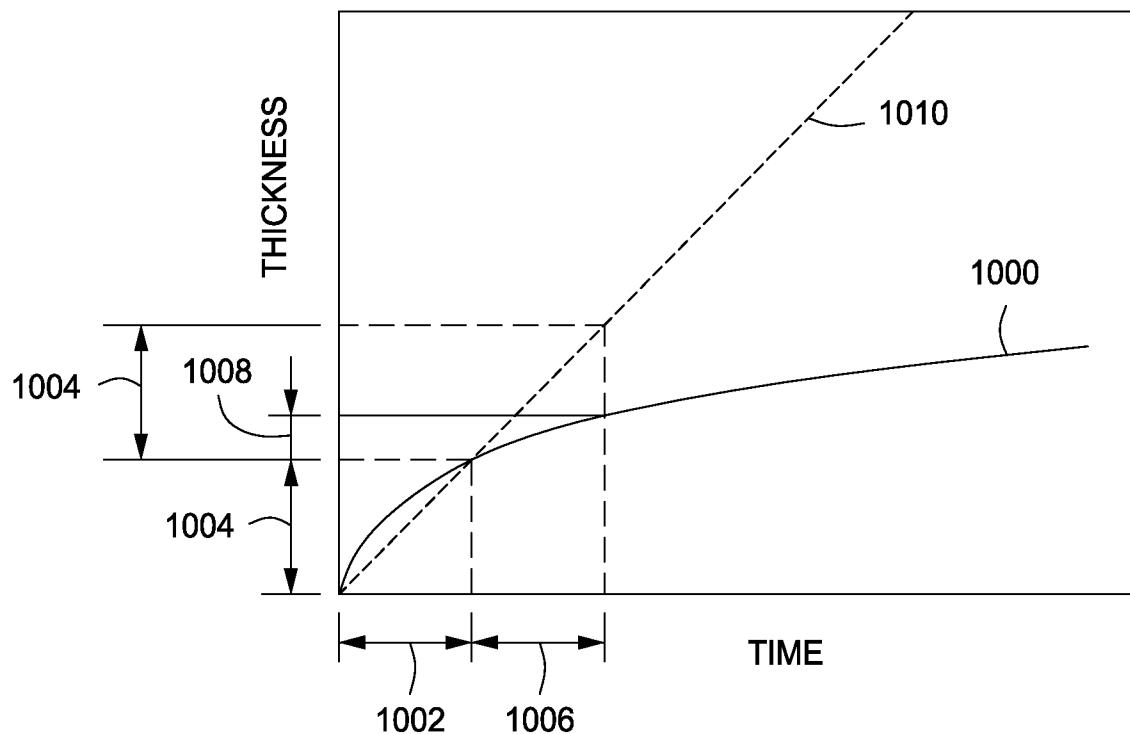

**[0016]** Figure 9 depicts a schematic plot of oxide thickness as a function of time in accordance with some embodiments of the present invention.

**[0017]** Figure 10A-D depicts the stages of fabrication of a floating gate in accordance with some embodiments of the present invention.

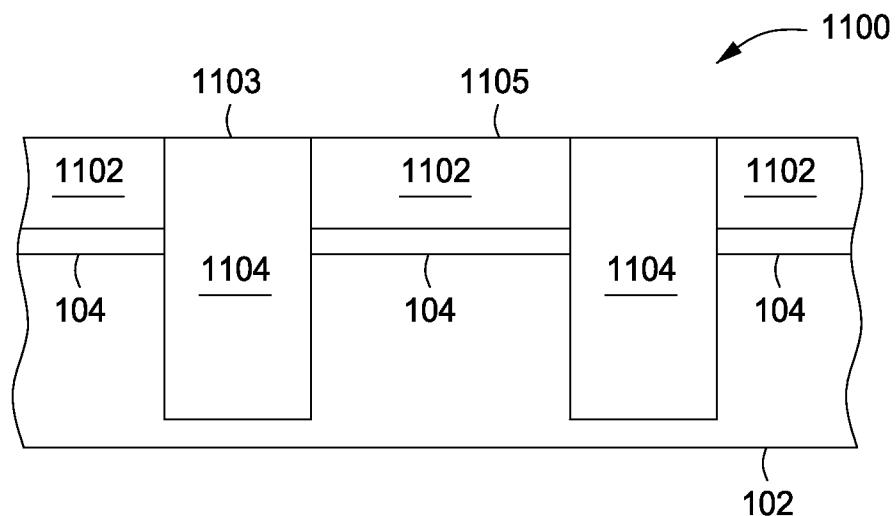

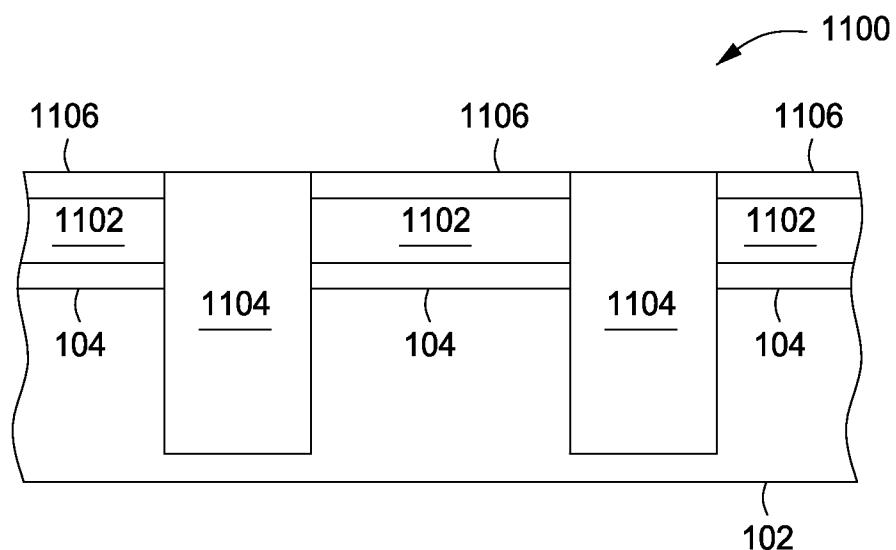

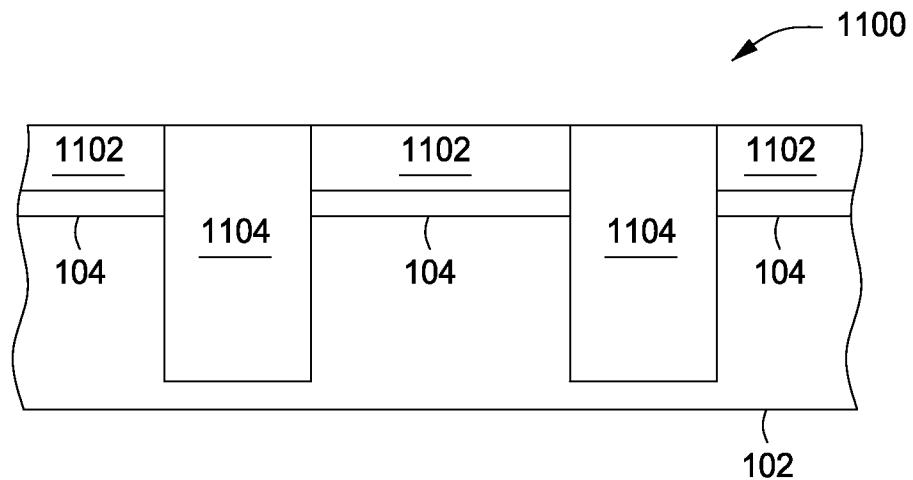

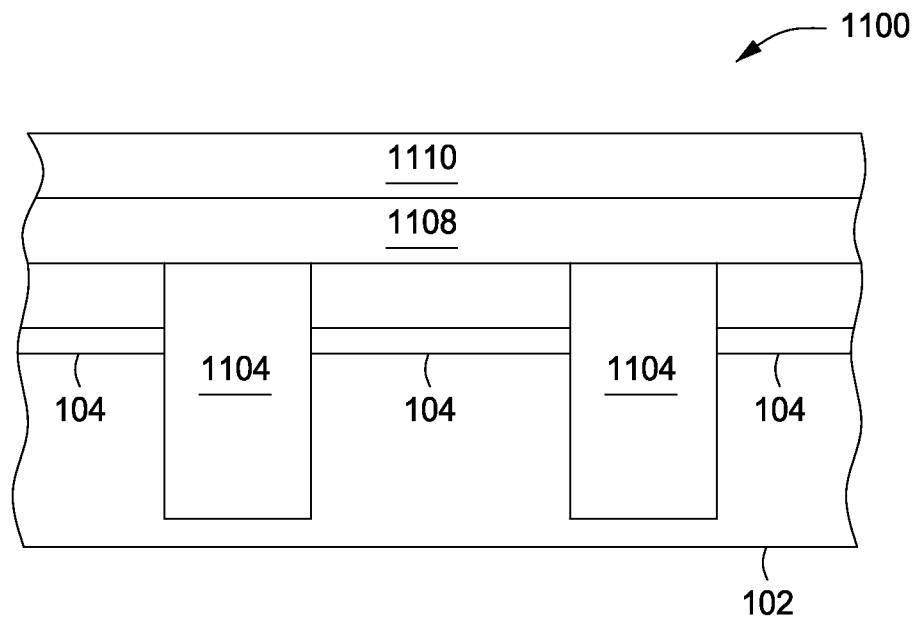

15 **[0018]** Figure 11A-C depicts the stages of fabrication of a structure in accordance with some embodiments of the present invention.

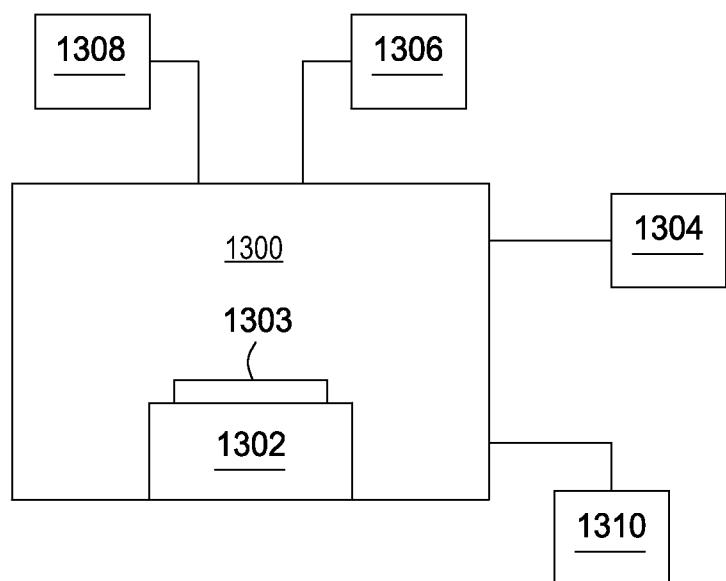

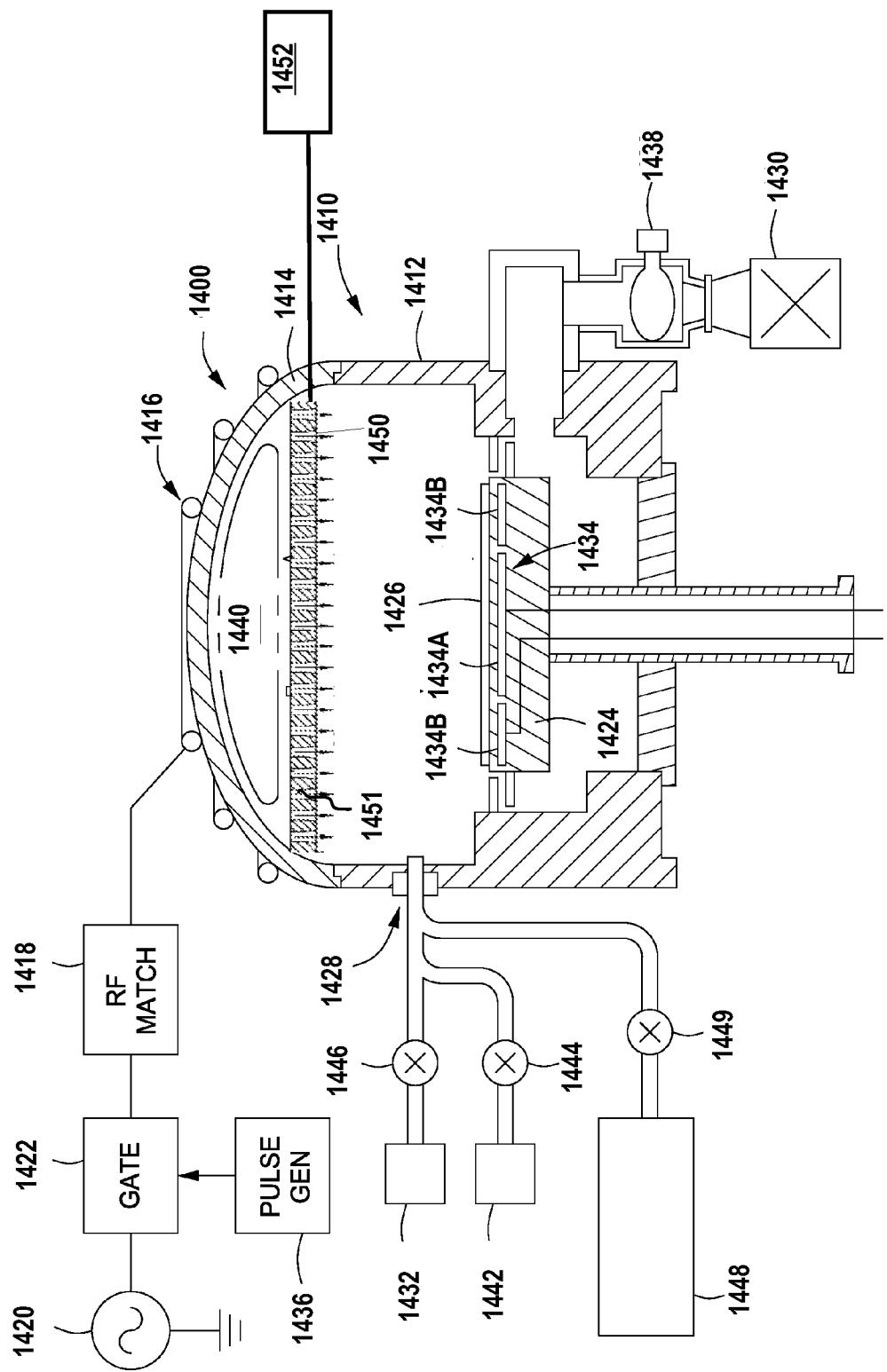

**[0019]** Figure 12 depicts an exemplary process chamber in accordance with some embodiments of the present invention.

20 **[0020]** Figure 13A depicts a first exemplary modified plasma process chamber in accordance with some embodiments of the present invention.

**[0021]** Figure 13B depicts an exemplary embodiment of substrate support cooling system that can be used in chambers according to several embodiments.

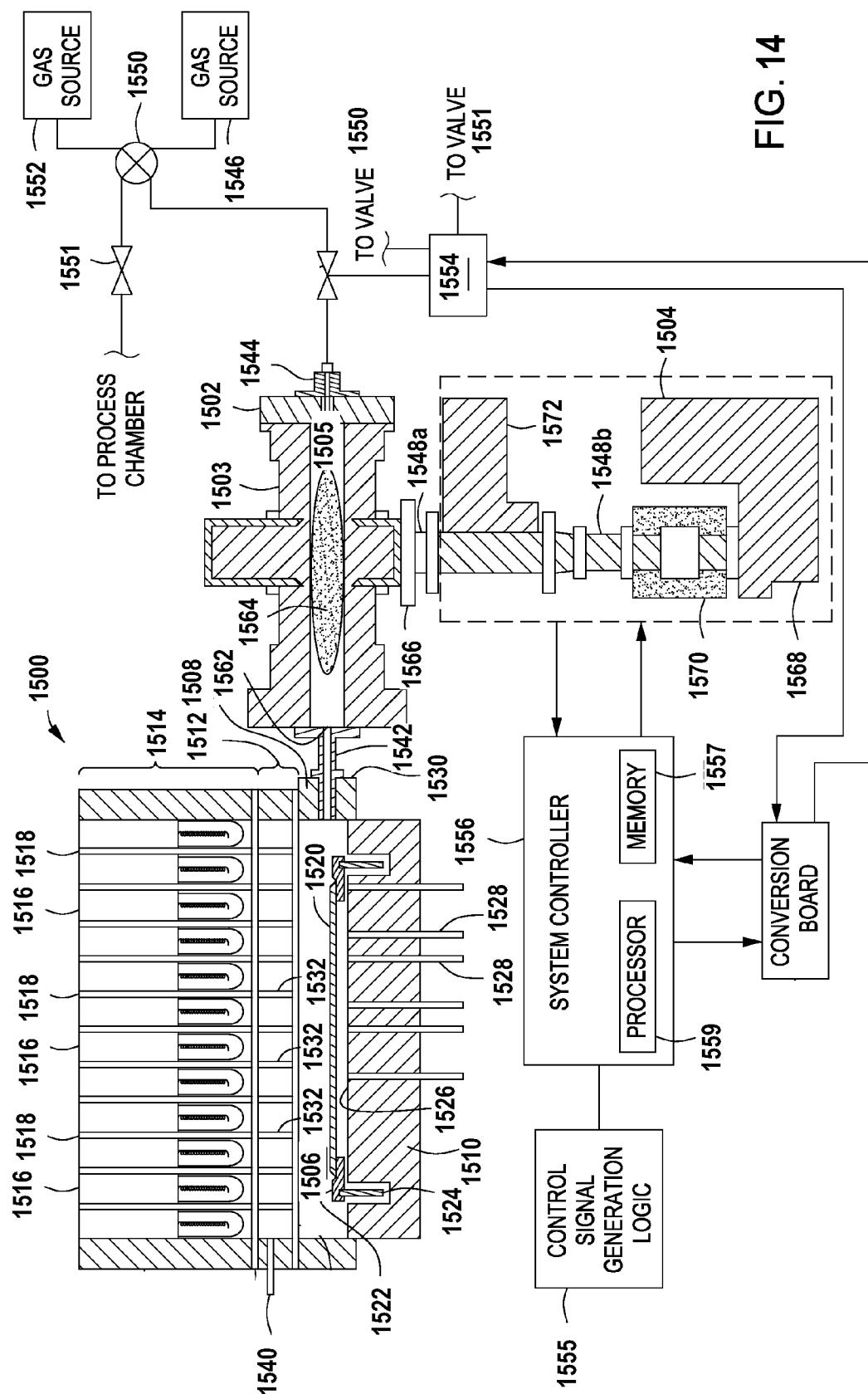

**[0022]** Figure 14 depicts a second exemplary modified plasma process chamber in accordance with some embodiments of the present invention.

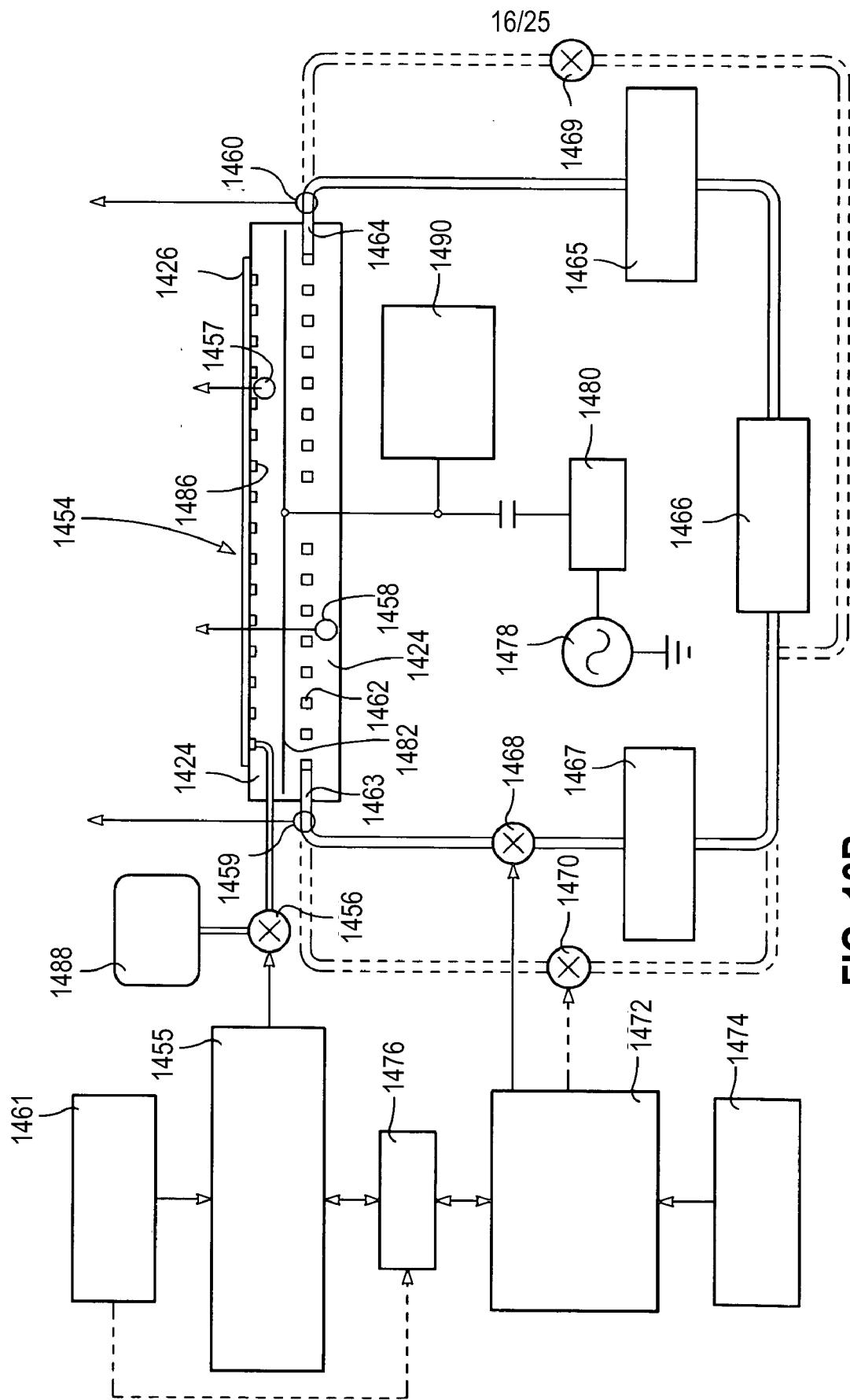

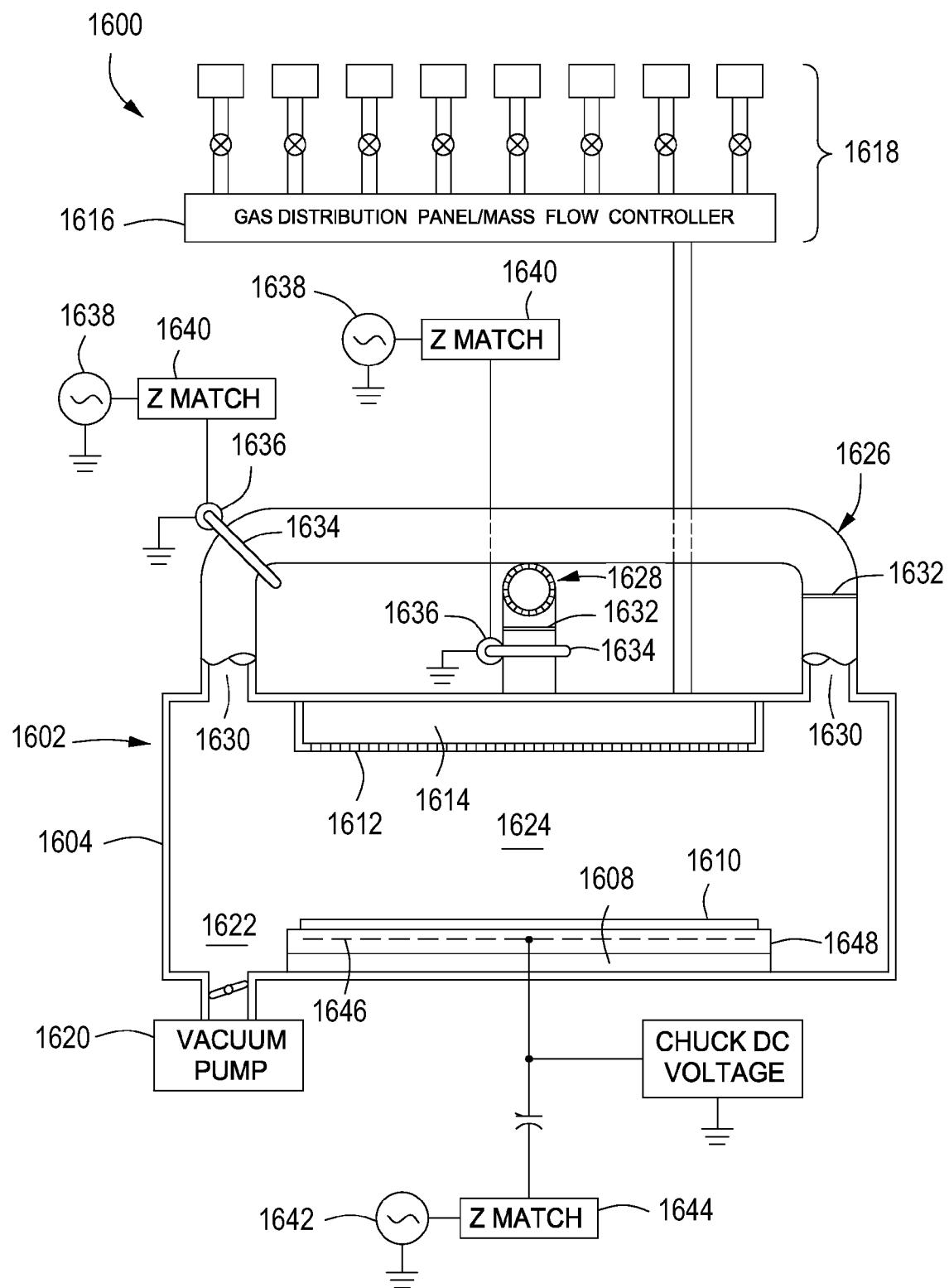

25 **[0023]** Figure 15 depicts a third exemplary modified plasma process chamber in accordance with some embodiments of the present invention.

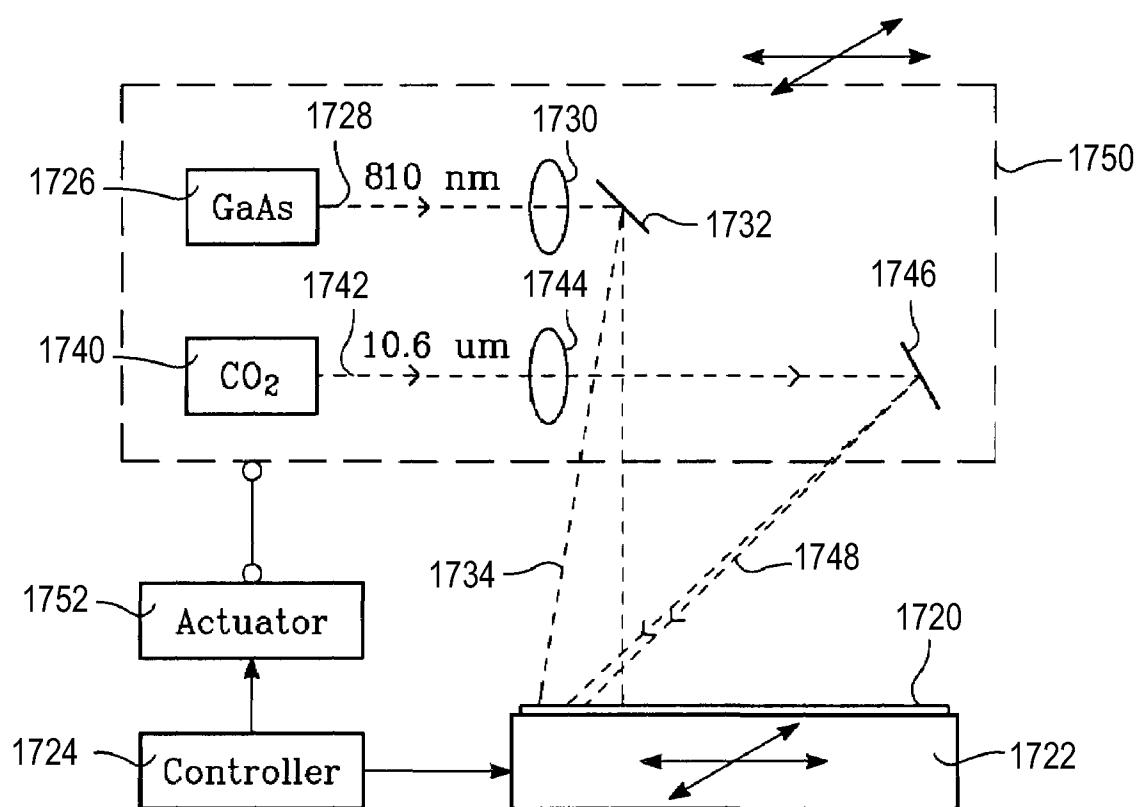

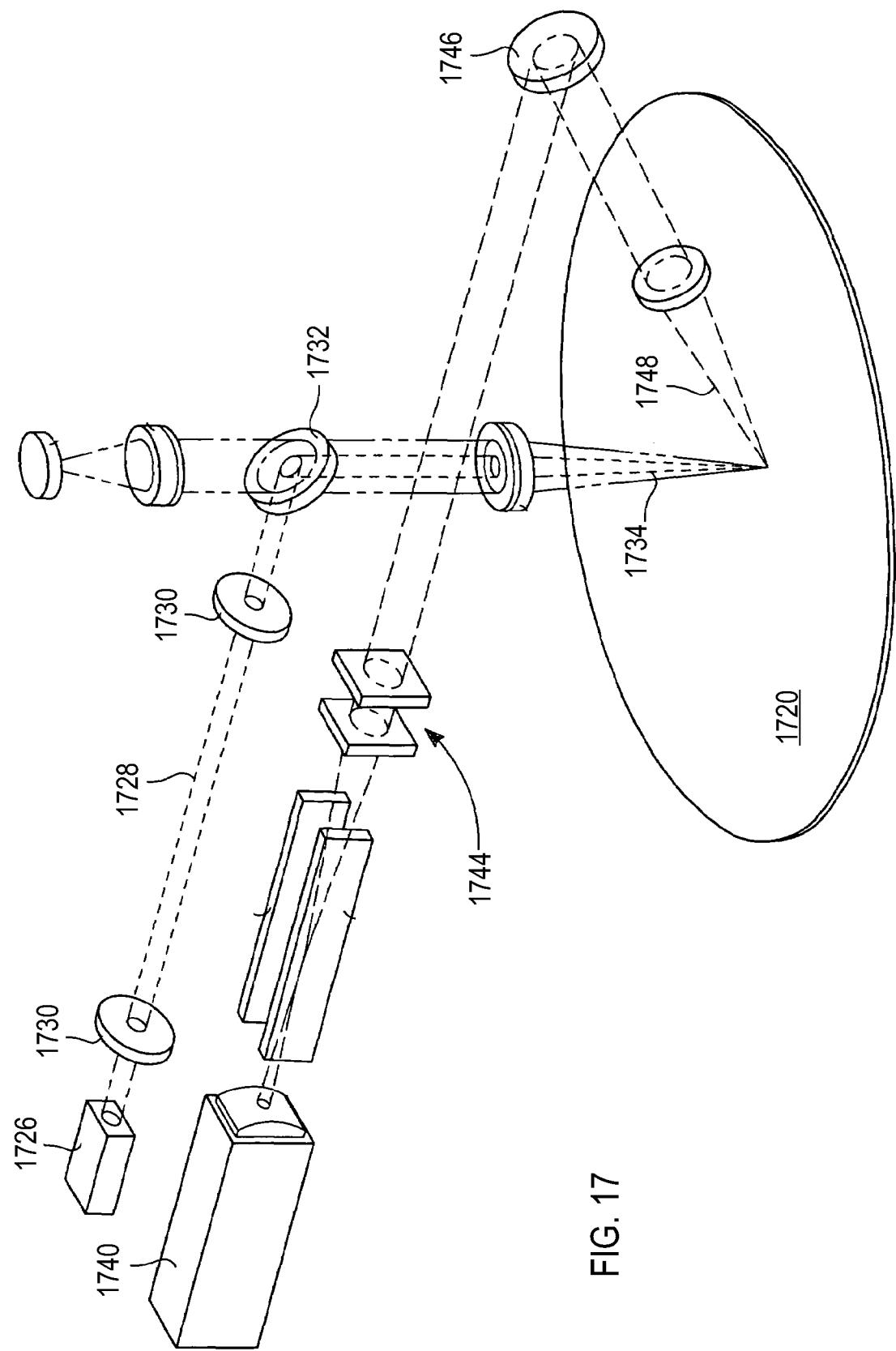

**[0024]** Figure 16 depicts a light source system that can be used for heating a material surface according to chambers of one or more embodiments.

**[0025]** Figure 17 depicts further detail of the light source system of Figure 16 that can be used for heating a material surface according to one or more embodiments

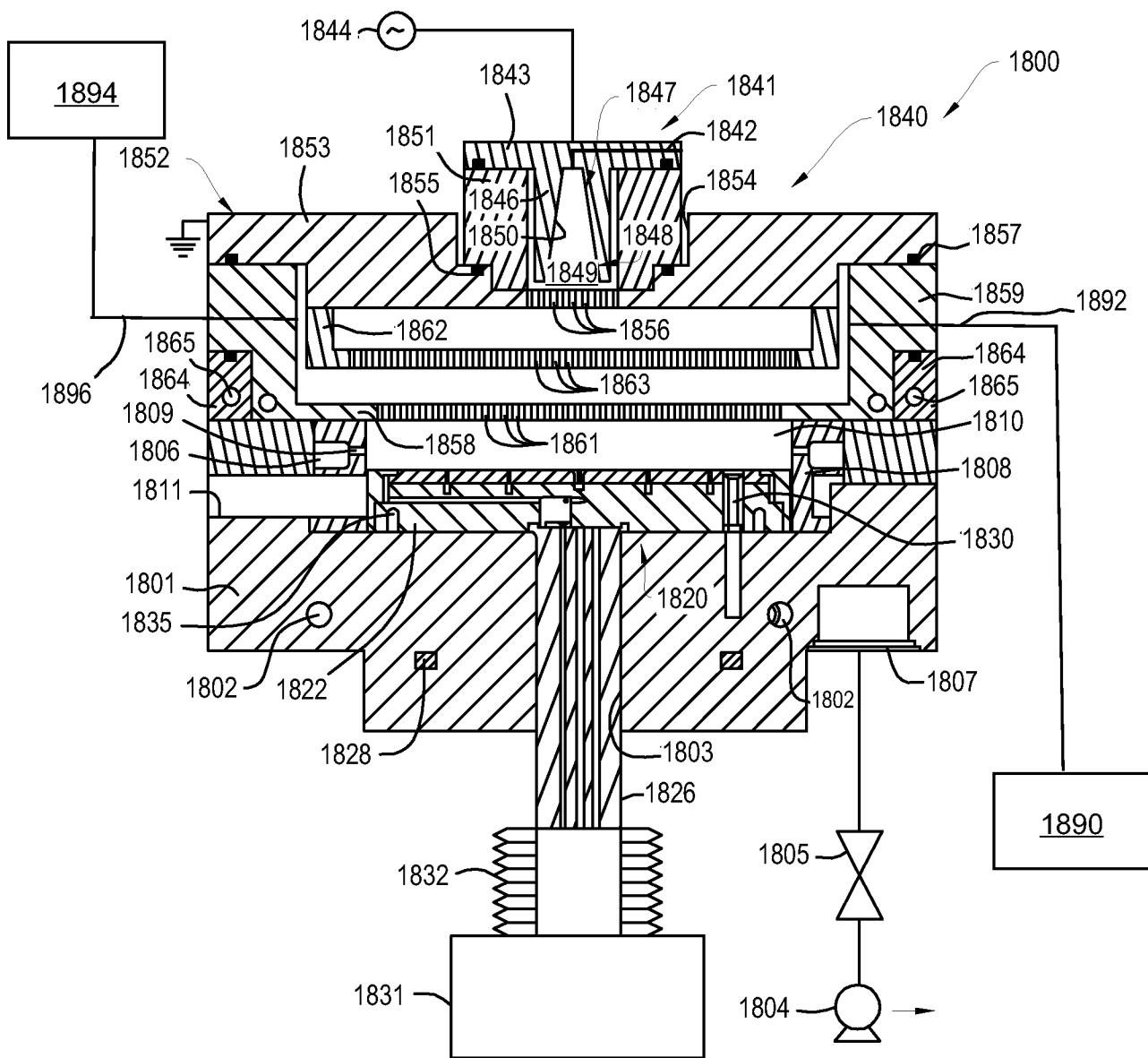

**[0026]** Figure 18 depicts a modified chamber for performing cyclical oxidation and etching according to an embodiment of the invention.

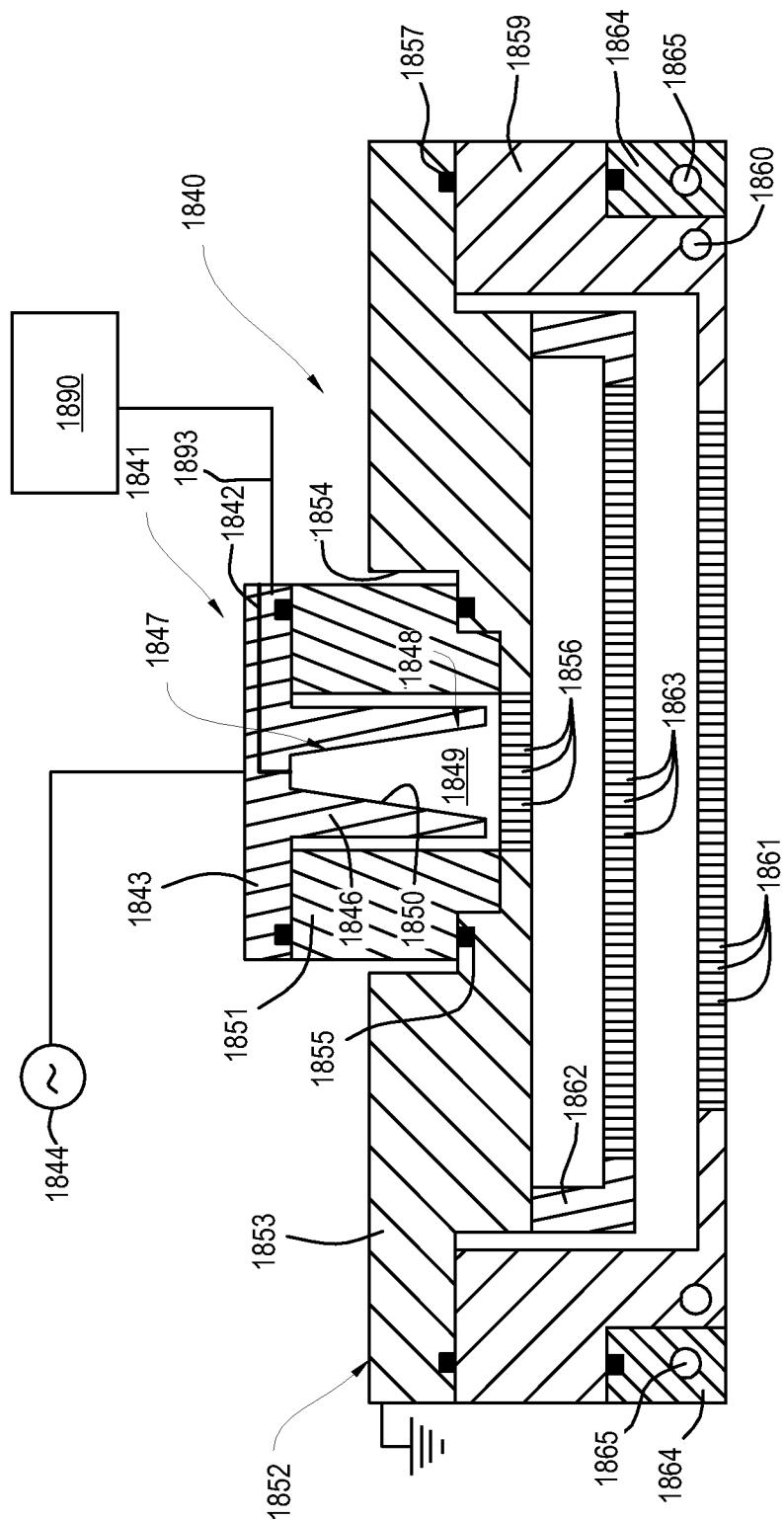

5 **[0027]** Figure 19 depicts a top portion of the chamber of Figure 18.

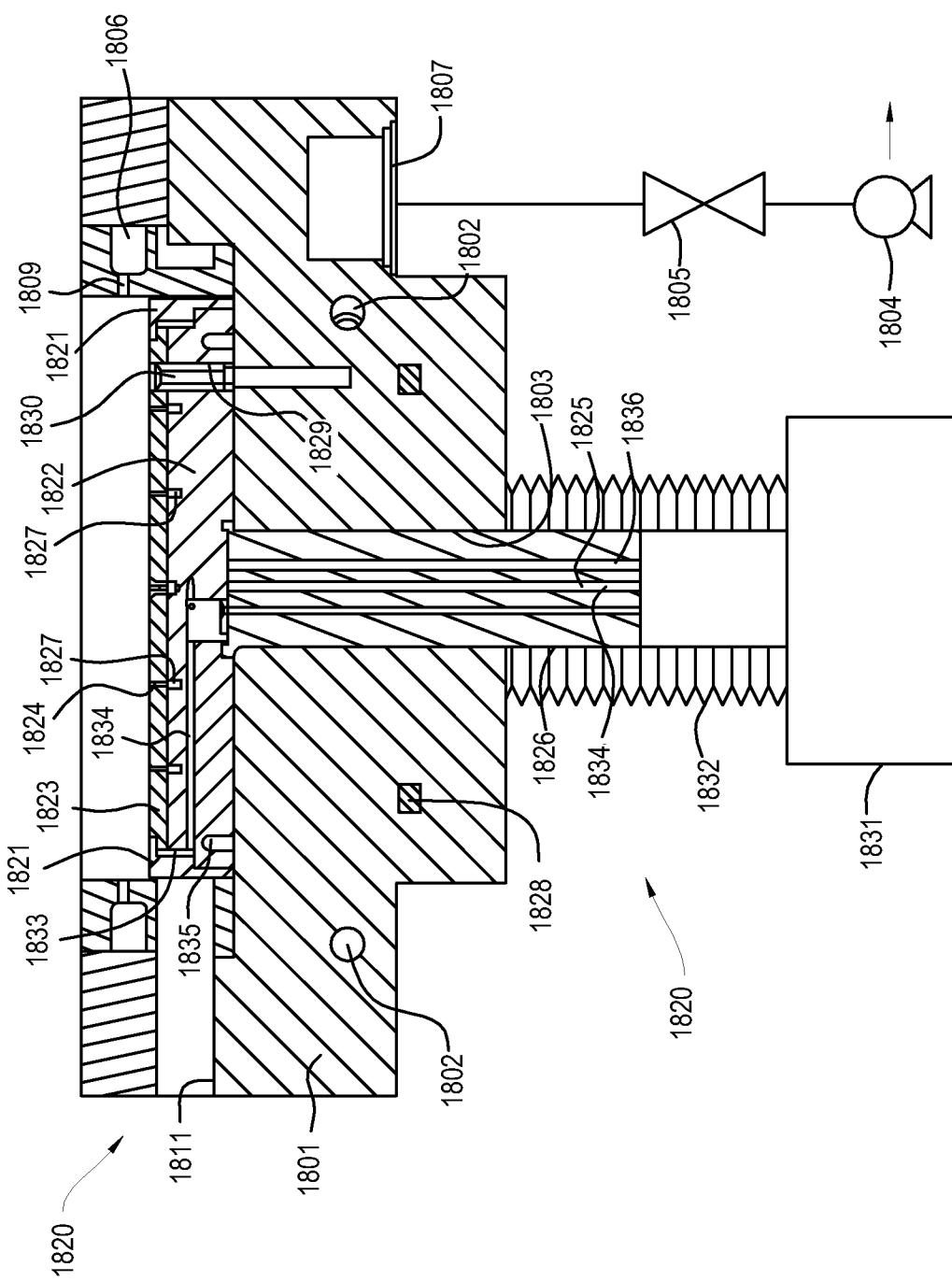

**[0028]** Figure 20 depicts a lower portion of the chamber of Figure 18.

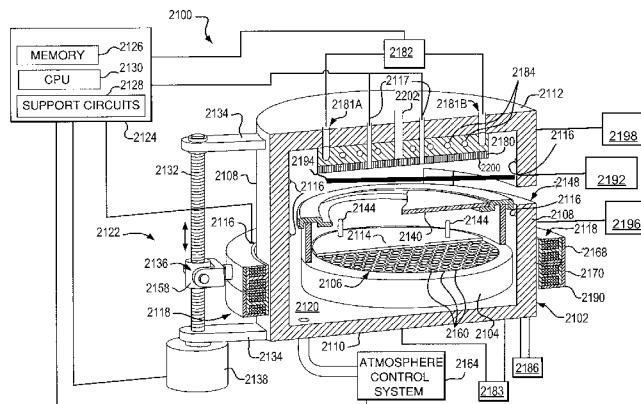

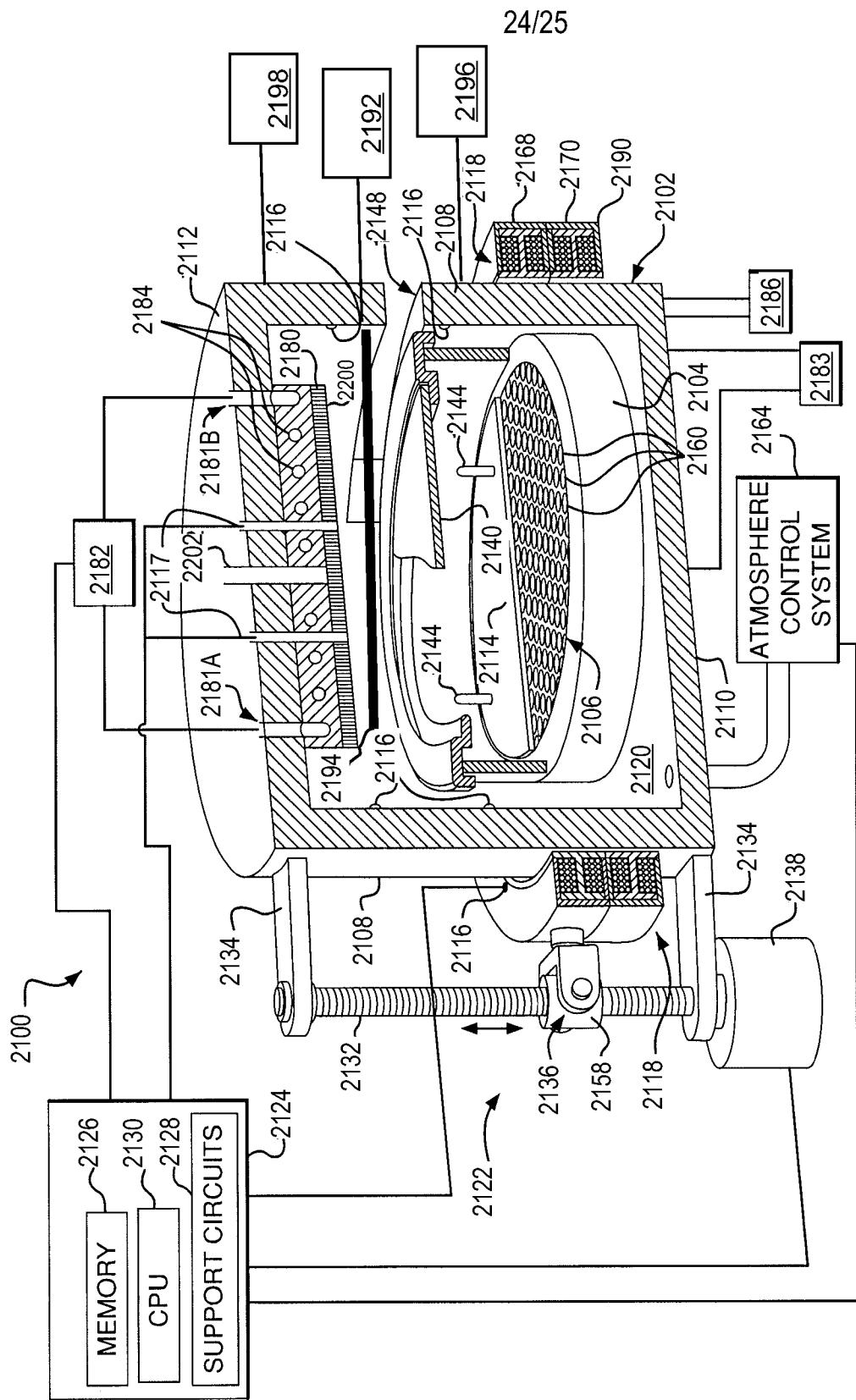

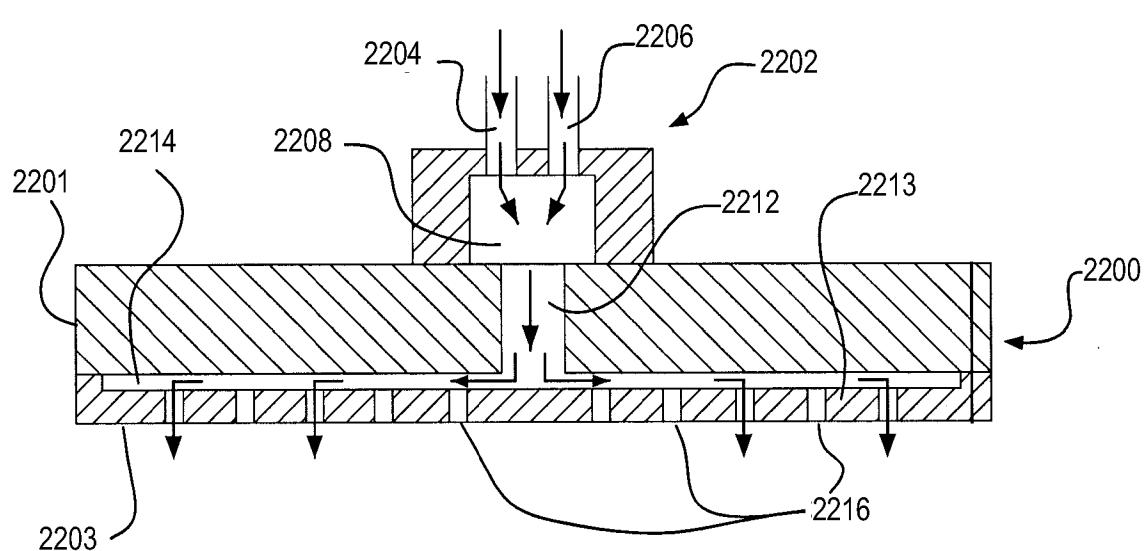

**[0029]** Figure 21 depicts a modified rapid thermal processing chamber according to one or more embodiments.

**[0030]** Figure 22 depicts a gas distribution plate used in the chamber of Figure 21.

10 **[0031]** The drawings have been simplified for clarity and are not drawn to scale. To facilitate understanding, identical reference numerals have been used, wherever possible, to designate identical elements that are common to the figures. It is contemplated that some elements of one embodiment may be beneficially incorporated in other embodiments.

#### DETAILED DESCRIPTION

15 **[0032]** Apparatus and methods for oxidizing a surface of a material layer of a semiconductor device to form an oxide layer and removing at least a portion of the oxide layer by etching in a single chamber. While the present invention is not to be limited to a particular device, the apparatus and methods described can be used for the manufacture of semiconductor devices and structures suitable for narrow pitch applications. As used herein, narrow pitch applications 20 include half-pitches of 32 nm or less (*e.g.*, device nodes of 32 nm or less). The term "pitch" as used herein refers to a measure between the parallel structures or the adjacent structures of the semiconductor device. The pitch may be measured from side to side of the same side of the adjacent or substantially parallel structures. Of course, the semiconductor devices and structures may be utilized in applications having greater pitches as well. The semiconductor 25 devices may be, for example, NAND or NOR flash memory, or other suitable devices. In some embodiments, the semiconductor devices maintain or improve sidewall capacitance between a floating gate and, for example, a control gate of the device, thereby reducing interference (*i.e.*, noise) between adjacent floating gates in adjacent devices. The inventive apparatus and methods disclosed herein advantageously limit undesired effects, such as oxygen 30 diffusion which can, for example, thicken a tunnel oxide layer during processing. Further, the

inventive apparatus and methods can advantageously be applied towards the fabrication of other devices or structures, for example, such as Fin Field Effect Transistors (FinFET) devices, hard mask structures, or other structures, to overcome size limitations in the critical dimension imposed by conventional lithographic patterning. It is contemplated that the specific oxidation and etching apparatus and processes disclosed herein with respect to the formation of one structure may be utilized in the formation of any other structure disclosed herein unless noted to the contrary.

**[0033]** Thus, embodiments of the present invention provide apparatus and methods for performing layer by layer cyclic oxidation and etching in a single chamber or tool, enabling higher throughput than if the processes were performed in separate chambers or tools. When multiple iterations of cyclic oxidation and etching are required to be performed in separate chambers, throughput suffers due to interchamber transfer time. Throughputs can be enhanced if a chamber or tool capable of multiple processes is provided. However, a chamber that can perform multiple etching and oxidation processes that require very disparate temperatures is not believed to be available. According to one or more embodiments, chambers or tools are provided that enable rapid heating and cooling of substrates in a single chamber, thus allowing cyclic oxidation and/or nitridation and etching processes to be performed. In one or more embodiments, the process chambers disclosed herein can perform a single cycle of oxidation and etching as described herein in less than 5 minutes, less than 4 minutes, less than 3 minutes, less than 2 minutes, less than 1 minute, or less than 30 seconds. In one or more embodiments, the oxidation process is performed at temperatures between about 200° C and 800° C, more specifically between about 300° C and 500° C, and a portion of the etching process is performed at a temperature below about 150° C, specifically, below about 120° C, and more specifically at less than or equal to about 100° C. In one or more embodiments, the etching process utilizes a dry etch process using a plasma, for example, a fluorine-containing plasma, and the etching process includes a process that is performed below about 50° C, specifically below about 40° C, and more specifically in the range of about 25° C to 35° C followed by a step performed at a temperature exceeding about 100° C, for example in the range of about 100° C to about 200° C.

**[0034]** An example of a semiconductor device that can be made with and apparatus and/or method embodiment of the present invention is described below with respect to Figure 1 in an illustrative application as a memory device 100. The memory device 100 includes a substrate

102 having a tunnel oxide layer 104 disposed thereon. A floating gate 106 is disposed on the tunnel oxide layer 104. The floating gate 106, the tunnel oxide layer 104, and the underlying portion of the substrate 102 may comprise a cell 103 (or memory unit) of the memory device 100. Each cell of the memory device may be separated. For example, in the memory device 5 100, a shallow trench isolation (STI) region 108 is disposed in the substrate 102 between each cell (for example, adjacent to the tunnel oxide layer 104 and floating gate 106, where the STI region 108 separates the cell 103 from adjacent cells 105 and 107). The memory device 100 further includes an inter-poly dielectric (IPD) layer 110 disposed above the floating gate 106 and a control gate layer 112. The IPD layer 110 separates the floating gate 106 from the 10 control gate layer 112.

**[0035]** The substrate 102 may comprise a suitable material such as crystalline silicon (*e.g.*, Si<100> or Si<111>), silicon oxide, strained silicon, silicon germanium, doped or undoped polysilicon, doped or undoped silicon wafers, patterned or non-patterned wafers, silicon on insulator (SOI), carbon doped silicon oxides, silicon nitride, doped silicon, germanium, gallium 15 arsenide, glass, sapphire, or the like. In some embodiments, the substrate 102 comprises silicon. The tunnel oxide layer 104 may comprise silicon and oxygen, such as silicon oxide (SiO<sub>2</sub>), silicon oxynitride (SiON), or high-k dielectric materials, such as aluminum- (Al), hafnium- (Hf), or lanthanum- (La), zirconium- (Zr) based oxides or oxynitrides, or silicon 20 nitrides (Si<sub>x</sub>N<sub>y</sub>), in single or layered structures (*e.g.*, SiO<sub>2</sub>/high-k/SiO<sub>2</sub>), or the like. The tunnel oxide layer 104 may have any suitable thickness, for example, between about 5 to about 12 nm. The tunnel oxide layer 104 may have a width, within each cell, substantially equivalent to the width of a base of the floating gate 106. The STI region 108 may comprise silicon and oxygen, such as silicon oxide (SiO<sub>2</sub>), silicon oxynitride (SiON), or the like.

**[0036]** The floating gate 106 typically comprises a conductive material, such as polysilicon, 25 metals, or the like. The floating gate 106 has a configuration suitable to facilitate disposing portions of the control gate layer 112 between adjacent cells (*e.g.*, between cells 103, 105, and 107). As such, the floating gate may be formed in an inverted “T” shape. As used herein, the term inverted “T” refers generally to the geometry of the structure wherein an upper portion of the floating gate 106 is relieved with respect to a base of the floating gate 106. Such relief 30 provides room for the IPD layer 110 to be formed over the floating gate 106 without completely filling the gap between adjacent floating gates 106, thereby allowing a portion of the control gate layer 112 to be disposed between adjacent floating gates 106.

**[0037]** For example, as illustrated in Figure 1, the floating gate 106 is generally shown in the shape of an inverted T having a base 115 and a stem 113 (or an upper portion of the floating gate 106). The floating gate 106 may generally have any dimensions as desired for a particular application. In some embodiments, the height of the floating gate 106 may be between about 5 20 to about 100 nm. In some embodiments, the thickness of the base 115 may be less than or equal to about 35 nm.

**[0038]** Due to the relief of the upper portion of the floating gate 106, the floating gate 106 has a first width 109 proximate the base 115 of the floating gate 106 that is greater than a second width 111 proximate the top of the floating gate 106. In some embodiments, a ratio of 10 the first width 109 to the second width 111 is at least about 2:1. In some embodiments, the first width 109 may exceed the second width 111 by about 4 nm or more, or about 6 nm or more, or between about 4 to about 6 nm. The width of the floating gate 106 may vary linearly, non-linearly, continuously, non-continuously, in any fashion, between the base 115 and the top 15 of the floating gate 106. In some embodiments, and as illustrated in Figure 1, the width of the floating gate 106 varies non-linearly between the first width 109 and the second width 111. In some embodiments, the first width may be less than about 35 nm, or between about 20 to about 35 nm. The second width may be between about 5 to about 30 nm, for example, 5 nm, 10 nm, 12 nm, 13 nm, 14 nm, 15 nm, 20 nm, 25, nm or 30 nm.

**[0039]** The stem 113 may have a sidewall portion thereof having a substantially vertical profile, as illustrated in Figure 1. In some embodiments, substantially vertical means less than 20 or equal to about 10 degrees of vertical, or less than or equal to about 5 degrees of vertical, or less than or equal to about 1 degree of vertical. The substantially vertical profile of the sidewall may be up to about 40 percent, or greater than about 40 percent of the total height of 25 the floating gate 106. In some embodiments, the substantially vertical profile is greater than about 40 percent of the height of the floating gate 106. In some embodiments, the substantially vertical profile is between about 20 to about 100 nm.

**[0040]** The IPD layer 110 may comprise any suitable single or multi-layer dielectric materials. A single layer IPD may comprise SiO<sub>2</sub>, SiON, a high-k dielectric material as discussed above with respect to tunnel oxide layer 104, or the like. A non-limiting example of 30 a multi-layer IPD is a multi-layer ONO layer comprising a first oxide layer, a nitride layer, and a second oxide layer. The first and second oxide layers typically comprise silicon and oxygen,

such as silicon oxide ( $\text{SiO}_2$ ), silicon oxynitride ( $\text{SiON}$ ), or the like. The nitride layer typically comprises silicon and nitrogen, such as silicon nitride ( $\text{SiN}$ ), or the like. In some embodiments, a multi-layer IPD layer comprising  $\text{SiO}_2/\text{high-k}/\text{SiO}_2$  (such as,  $\text{SiO}_2/\text{Al}_2\text{O}_3/\text{SiO}_2$ ) can also be used as the IPD layer 110. In some embodiments, the IPD layer 110 is deposited to a thickness of between about 12 to about 15 nm.

5 [0041] Conformal deposition of the IPD layer 110 over the inverted T shape of the floating gate 106 facilitates forming a well 114 in the deposited IPD layer 110. The well 114 is formed between adjacent floating gates. In some embodiments, the well 114 has a width of between about 4 to about 20 nm and a depth of between about 20 to about 90 nm.

10 [0042] Optionally, prior to IPD deposition, the depth level of the IPD penetration between adjacent floating gates may be defined by depositing a layer of material, such as  $\text{SiO}_2$ , to fill the gap between adjacent floating gates, planarizing the layer of material, for example, by chemical mechanical planarization (CMP), to remove excess material down to the top of the floating gate 106. The material remaining in the gap between adjacent floating gates may then 15 be etched to a desired depth to set the level of IPD penetration between the floating gates.

20 [0043] The control gate layer 112 may be deposited atop the IPD layer 110 and in the well 114 to form a control gate. The control gate layer 112 typically comprises a conductive material, such as polysilicon, metal, or the like. The addition of the well 114 provides a larger surface area for the control gate layer 112 proximate a sidewall of the floating gate 106. The increased surface area of the control gate layer 112 facilitated by the well 114 may advantageously improve capacitive coupling between a sidewall of the floating gate 106 and the control gate. Further, the well 114, disposed between adjacent floating gates (for example, those of cells 103 and 105) may reduce parasitic capacitance between adjacent floating gates, floating gate interference, noise, or the like. In addition, the inverted T shape of the floating 25 gate 106 reduces the surface area as compared to an approximate rectangle for the same floating gate height. The reduced cross-section advantageously reduces parasitic capacitance between adjacent floating gates in the bitline direction (*e.g.*, in a different word line and the same bit line of a memory device). Advantageously, the sidewall capacitance between the floating gate and the control gate can be independently controlled (*e.g.*, maintained at a 30 desirable level) by control of the height of the floating gate.

**[0044]** Figure 2 depicts a method 200 of fabricating a semiconductor device having a floating gate geometry in accordance with some embodiments of the present invention. The methods described herein may be performed in any suitable single chamber configured for oxidation and etching with the ability to process at disparate temperatures. In processes that 5 involve cyclic oxidation and etching, according to one or more embodiments, the oxidation is performed at relatively high temperatures, and etching is performed at relatively low temperatures. For example, oxidation may be performed at temperatures of 500° C and above according to one or more embodiments, and alternatively, at temperatures of 500° C and below, more particularly 400° C and below. For example, portions of the etch process may be 10 performed at low temperatures, for example, room temperature, such as 20° C, 25° C or 30° C. It will be understood that the etching process may be performed at higher temperatures such as up to about 75° C. After etching, it may be desirable to raise the temperature to about 100° C to sublimate compounds, which is described in more detail below.

**[0045]** Aspects of the invention pertain to performing an oxidation process, an etching 15 process and sublimation in a single chamber. Oxidation may be achieved by plasma oxidation, rapid thermal oxidation (RTO), radical oxidation, or the like. Suitable oxidation chambers may include plasma chambers such as Plasma Immersion Ion Implantation (P3I), or Decoupled Plasma Oxidation (DPO). Alternatively, thermal oxidation chambers can be used such as RADIANCE®, VANTAGE® RADOX™ chambers available from Applied Materials, Inc. of 20 Santa Clara, California, or a furnace including a remote and/or local plasma source. Exemplary thermal oxidation processes may be performed with various oxidative chemistries include varying reducing gas concentration for reducing gases, such as one or more of hydrogen (H<sub>2</sub>), ammonia (NH<sub>3</sub>) or the like within an oxidative gas mixture include oxidative gases, such as one or more of oxygen(O<sub>2</sub>), nitric oxide (NO), nitrous oxide (N<sub>2</sub>O) or the like, 25 and optionally including inert gases, such as one or more of nitrogen (N<sub>2</sub>), argon (Ar), helium (He), or the like. Exemplary plasma oxidation processes may use any of the oxidative chemistries discussed above for thermal oxidation processes, and may be performed with or without a heating chuck. Photochemical processes, for example, utilizing oxygen species (e.g., O<sub>2</sub>) in the presence of ultraviolet light (UV) to form an oxide layer, or wet chemical oxidation, 30 for example utilizing a chemical solution including nitric acid (HNO<sub>3</sub>) another suitable acid for oxidation, can also be applied. However, these chambers are typically configured to perform oxidation processes only, and are not configured for low temperature processing such as low

temperature etching. Accordingly, modification to the chambers will be necessary to achieve rapid temperature changes required between oxidation and etching. Specific details will be provided below.

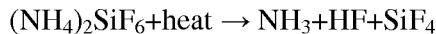

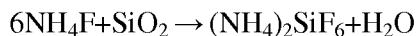

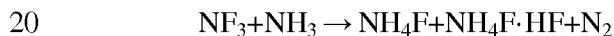

**[0046]** Alternatively, embodiments of methods described herein may be performed in any suitable modified etch chamber configure for wet or dry etch, reactive ion etch (RIE), or the like. Exemplary etch chambers include the SICONI™, Producer®, or Carina™ chambers, also available from Applied Materials, Inc. of Santa Clara, California. One non-limiting, exemplary dry etch process may include ammonia or (NH<sub>3</sub>) or nitrogen trifluoride (NF<sub>3</sub>) gas, or an anhydrous hydrogen fluoride (HF) gas mixture with a remote plasma, which condenses on SiO<sub>2</sub> at low temperatures (*e.g.*, ~30°C) and reacts to form a compound which can be sublimated at moderate temperature (*e.g.*, >100°C) to etch SiO<sub>2</sub>. Such an exemplary etch process can diminish over time and eventually saturate to a point where no further etching occurs unless portions of the compound are removed (for example, by the sublimation process described above). The etch process can be controlled using the above mechanism and/or by a timed etch process (*e.g.*, etching for a predetermined period of time). Exemplary wet etch processes may include hydrogen fluoride (HF) or the like. Exemplary plasma or remote plasma etch processes may include one or more etchants such as carbon tetrafluoride (CF<sub>4</sub>), trifluoromethane (CHF<sub>3</sub>), sulfur hexafluoride (SF<sub>6</sub>), hydrogen (H<sub>2</sub>), or the like, and may be performed with or without a heating chuck. The etch selectivity can be engineered to be between about 1 to about 1000 for different materials combinations, such as heterogeneous surfaces and the like. For example, in some embodiments, the etch selectivity can be about 100 for silicon (Si) in a silicon dioxide (SiO<sub>2</sub>) etch. The etch can be terminated as the etch rate drops to between about 0% to about 90%, or to about 75% of the initial etch rate to provide thickness control of the materials being etched. For example, in some embodiments, terminating the etch process as discussed above may provide thickness control when etching. This control may be particularly advantageous when etching an oxide layer disposed atop heterogeneous materials, for example, including silicon (Si) and silicon dioxide (SiO<sub>2</sub>). Etching chambers such as the SICONI chambers will require modifications to perform oxidation processes in the chamber, which will be described in more detail below.

**[0047]** Thus, method 200, which is understood to be performed in a single chamber, begins at 202, where a substrate having a material layer to be formed into a floating gate may be provided. For example, as shown in Figure 3A, the substrate 102 and material layer 304 may

be part of a partially fabricated memory device 300. The memory device 300 may comprise the substrate 102 having the tunnel oxide layer 104 disposed thereon. The material layer 304 may be deposited atop the tunnel oxide layer 104. A shallow trench isolation (STI) region 302 (similar to STI region 108) may be disposed adjacent to the tunnel oxide layer 104 and the 5 material layer 304. Other fabrication steps to provide the substrate and partially fabricated memory device 300 performed prior to beginning the method 200 include deposition of an isolation material, such as  $\text{SiO}_2$ , in the STI region 302, planarizing the isolation material level with an upper surface of the material layer 304, and etching the isolation material down to a desired level to result in a substrate having the material layer 304 ready to be processed into a 10 floating gate in accordance with the teachings provided herein.

**[0048]** The material layer 304 may comprise a conductive material, such as polysilicon, a metal or the like. The material layer 304 may generally have a slightly trapezoidal or rectangular cross section. The material layer 304 may generally have any suitable starting shape such that when oxidized and/or etched by the methods described herein, the material 15 layer 304 may be formed into a floating gate having an inverted T shape as described above with respect to Figure 1 (for example, the material layer 304 may be patterned and etched to facilitate forming the STI structures 302, and the resultant profile of the material layer 304 may be the starting point for further processing as disclosed herein).

**[0049]** At 204, the material layer 304 is selectively oxidized to form an oxide layer 306 as 20 shown in Figure 3B. The oxide layer 306 is formed on the top and sidewalls of the material layer 304, and may comprise a silicon oxide, metal oxide, or the like. In some embodiments, the oxide layer 306 may consume the material layer 304 to a depth of about 3 to about 15 nm, or about 10 nm. The oxide layer 306 may further consume (or in other encroach or displace) a portion of the STI region 302 as shown in Figure 3B. The oxide layer 306 may be formed 25 using wet or dry oxidation, rapid thermal oxidation (RTO), radical oxidation, plasma oxidation, for example, decoupled plasma oxidation (DPO), or any other oxidation process described herein. In some embodiments, where a low thermal budget and/or reduced diffusion of oxygen are desired, plasma oxidation or radical oxidation may be utilized. A low thermal budget may be required to prevent thickening of the tunnel oxide layer 104 during the oxidation of the 30 material layer 304. As used herein, a low thermal budget means a thermal budget less than a furnace process of tens of minutes at 850 degrees Celsius peak temperature.

**[0050]** Next, at 206, the oxide layer 306 is removed by an etch process, as depicted in Figure 3C in the same chamber that the oxidation step 204 was performed. The remaining portion of the material layer 304 after oxidation of the material layer 304 and removal of the oxide layer 306 may be generally in the shape of an inverted T, for example, similar to the shape of the 5 floating gate 106 depicted in Figure 1. The etch process may use chemicals or gases comprising hydrofluoric acid (HF) hydrochloric acid (HCl), or other etch processes disclosed herein, or the like. The etch process may be selective, for example, selectively removing the oxide layer 306. In one embodiment, the etch process is selective to silicon oxide, and removes the oxide layer 306 comprising silicon oxide relative to the material layer comprising 10 polysilicon. The etch process may further remove a portion of the STI region 302 during removal of the oxide layer 306.

**[0051]** Upon completion of the etch process to form a floating gate having an inverted T shape, the method 200 generally ends. Further processing of the memory device may include the deposition of an IPD layer and a control gate layer, similar to those layers described with 15 respect to Figure 1. In some embodiments, prior to the deposition of an IPD layer, the region between adjacent material layers 304 and above the STI region 302 is filled with a gap fill material, for example,  $\text{SiO}_2$  or the same material that comprises the STI region 302. Next, the top of this filled region can be planarized by chemical mechanical planarization (CMP), or any suitable planarization method, to be substantially even with the top of the material layer 304. 20 The gap fill and CMP are followed by an etch of the gap fill material to set a desired penetration depth for the IPD between the adjacent material layers 204, prior to deposition of the IPD layer.

**[0052]** Alternatively, the floating gate having an inverted T shape may be formed using a method 400, as depicted in Figure 4. The method 400 is illustratively described with reference 25 to Figures 5A-E, which depicts stages of fabrication of the memory device 300 in accordance with the embodiments of the method 400. The method 400 includes the deposition of a sacrificial nitride layer, which may be utilized to limit the diffusion of oxygen during an oxidation process used to oxidize the material layer 304. It may be desired to limit oxygen diffusion to prevent undesirable thickening of the tunnel oxide layer 104 and/or to prevent 30 undesirable removal of portions of the tunnel oxide layer 104 and/or the STI region 302 (or the gap fill material) during the oxide layer removal process as described below.

**[0053]** The method 400 generally begins at 402, where the partially fabricated memory device 300 is provided as illustrated in Figure 5A. The memory device 300 has been described above, and includes the substrate 102 having a tunnel oxide layer 104 disposed thereon and having the material layer 304 disposed above the tunnel oxide layer 104. The memory device 5 300 further includes the STI layer 302 disposed in the substrate 102 and adjacent to the tunnel oxide layer 104 and material layer 304.

**[0054]** At 404, a nitride layer 502 is formed on the exposed surfaces of the material layer 304 and the STI region 202 as illustrated in Figure 5C. The nitride layer 502 may be formed by any suitable nitridation process, for example, plasma nitridation or silicon nitride 10 deposition. The nitride layer 502 may comprise silicon nitride (SiN), silicon oxynitride (SiON), or both. The nitride layer 502 may be formed to a greater thickness on the horizontal surfaces of the material layer 304 and STI region 302 as compared to the sidewall of the material layer 304 (for example, by a directional nitridation process). In some embodiments, a ratio of nitride layer thickness on the horizontal surfaces of the material layer 304 and STI 15 region 302 to that on the sidewall of the material layer 304 is about 2:1 to about 10:1. In some embodiments, the nitride layer 502 has a thickness of about 5 to about 10 nm on the horizontal surfaces of the material layer 304 and the STI region 302. In some embodiments, the nitride layer 502 has a thickness of about 1 nm or less on the sidewalls of the material layer 304.

**[0055]** At 406, the nitride layer 502 and the material layer 304 are selectively oxidized to 20 form an oxynitride layer 504 and an oxide layer 506. The oxidation process is performed in the same chamber as nitridation step 504. The oxidation step 506 may include any suitable oxidation process as discussed above with respect to method 200, and may be performed in a single stage process described with respect to Figures 5C-D. Initially, as depicted in Figure 25 5C, the oxidation process facilitates the formation of an oxynitride layer 504. The oxynitride layer 504 may consume a portion of the nitride layer 502 on the horizontal surface of the material layer 304 and STI region 302, and may consume substantially the entire nitride layer 502 on the sidewall of the material layer 304. The increased thickness of the nitride layer 502 on the horizontal surfaces may limit or prevent oxidation of those underlying surfaces. Upon consumption of the nitride layer 502 on the sidewall of the material layer 304, the oxidation 30 process may consume a portion of the material layer 304. The oxidation of the sidewalls of the material layer may proceed more quickly than on the horizontal surfaces due to the remaining unconsumed nitride layer 502 disposed on those surfaces.

**[0056]** As illustrated in Figure 5D, the oxidation process proceeds at a faster rate on the sidewalls of the material layer 304 forming an oxide layer 506 by generally consuming the material layer 304 from the sidewall inward. The remaining unconsumed portion of the material layer 304 may generally be in the desired shape of an inverted T. Further, and as 5 illustrated in Figure 5D the oxidation process continues to consume a portion of remaining nitride layer 502 and a portion of the STI region 302, albeit at a slower rate than the consumption of the material layer 304 at the sidewall.

**[0057]** At 408, the oxynitride layer 504 and the oxide layer 506 may be removed, resulting in 10 a floating gate having an inverted T shape as depicted in Figure 5E. The layers may be removed by an etch process, for example, a wet or dry chemical etch, reactive ion etch, or the like as discussed above with respect to method 200. The etch process may be selective, for example, selectively removing the oxynitride layer 504 and oxide layer 506. In one embodiment, the etch process is selective to silicon oxide (SiO<sub>2</sub>), silicon oxynitride (SiON), and silicon nitride (SiN), and removes the nitride layer 502 comprising SiN, the oxynitride 15 layer 504 comprising SiON, and the oxide layer 506 comprising SiO<sub>2</sub> selective to the material layer 304 comprising polysilicon. The etch process may further selectively remove a portion of the STI region 302 as illustrated in Figure 5E. In some embodiments, the etch process may be a multi-stage etch process. For example, initially the etch process may be selective to 20 selective to only SiO<sub>2</sub> to remove the oxide layer 506. Next, the etch process may be SiON and SiN to remove the oxynitride layer 504 and the nitride layer 502. Upon completion of the etch process to form a floating gate having an inverted T shape, the memory device 200 may be processed further, for example, by depositing an IPD layer and a control gate layer, similar to those layers described with respect to Figure 1. As discussed above, a gap fill and CMP of the 25 filled region between adjacent material layers 304, followed by an etch of the filled region may be performed prior to deposition of the IPD layer.

**[0058]** As discussed above, a low thermal budget (*e.g.* low diffusion of materials such as one or more of dopants, oxygen (O<sub>2</sub>) or silicon (Si)) may be desired in some embodiments, for example, to limit thickening of the tunnel oxide layer 104 or the STI region 302. However, if possible to limit such undesirable thickening effects, high thermal budget processes (*i.e.*, high 30 oxygen diffusion) may be utilized. For example, high thermal budget processes (*e.g.*, wet, dry, or RTO) can provide conformal oxidation, faster oxidation rates, thicker oxidation (*e.g.*, about 5 to about 15nm thickness) and more efficient sidewall oxidation. In addition, high thermal

budget oxidation processes provide reduced sensitivity to different crystallographic orientation of the material layer used to form a floating gate, thus advantageously generating a smooth surface during oxidation. Reduced sensitivity to crystallographic orientation may be desired, for example, when a material layer comprising a polycrystalline material is used to form a 5 floating gate. Smooth surfaces advantageously improve reliability in the memory device, for example, by reducing junction resistance, or the like.

**[0059]** Thus, in some embodiments, such as described below with respect to Figure 6, a partially fabricated memory device 700 having a material layer 702 may be used to form a floating gate having an inverted T shape. The material layer 702 may be taller, for example, 10 compared to the material layer 304 illustrated in Figures 3A and 5A, respectively. In addition, the height of the STI region 302 may be scaled with the height of the material layer 702 (for example, by depositing and etching back a gap fill material, such as SiO<sub>2</sub>, as discussed above) to provide an increased distance between exposed surfaces thereof and the tunnel oxide layer, thereby facilitating resistance to oxidation diffusion into the tunnel oxide layer during high 15 thermal budget processes. In some embodiments, a gap between the top of the material layer 702 and the top of the STI region 302 may be substantially equivalent in distance to that of similar structures illustrated in Figures 3A and 5A. The increased height of both the material layer 702 and the STI region 302 as compared with similar memory devices in Figures 3A and 5A, may advantageously lengthen the distance oxygen atoms have to travel to reach the tunnel 20 oxide layer 104. The increased height of both structures allows for the use of a higher thermal budget oxidation process, while limiting thickening of the tunnel oxide layer 104. Thus, by increasing the height of the STI region 302 in the memory device 700, high thermal budget oxidation processes may advantageously be used to form a floating gate having an inverted T shape. Following the high thermal budget oxidation process and removal of an oxide layer 25 formed thereby, an etch process and/or a more controllable low thermal budget oxidation process may be used to reduce the thickness at the base of the floating gate. Such a combination of a high thermal budget oxidation process with either an etch process or a low thermal budget oxidation process is described below with respect to Figures 6-8.

**[0060]** For example, Figure 6 depicts a method 600 of fabricating semiconductor device 30 having a floating gate in accordance with some embodiments of the present invention. The method 600 is illustratively described with reference to Figures 7A-D and Figures 8A-B, which

depicts stages of fabrication of a memory device 700 in accordance with embodiments of the method 600.

**[0061]** The method 600 generally begins at 602, where a substrate having a material layer to be formed into a floating gate may be provided. For example, as shown in Figure 7A, the 5 substrate 102 and a material layer 702 may be part of a partially fabricated memory device 700. The memory device 700 may include the substrate 102 having the tunnel oxide layer 104 disposed thereon. The material layer 702 may be deposited atop the tunnel oxide layer 104. Shallow trench isolation (STI) regions 302 may be disposed in the substrate 102, adjacent to the tunnel oxide layer 104 and the material layer 702. The substrate 102, the tunnel oxide layer 10 104 and the STI regions 302 have been discussed above.

**[0062]** The material layer 702 may comprise a conductive material, such as polysilicon, a metal or the like. The material layer 702 may have a starting shape comprising a substantially rectangular or slightly trapezoidal cross section. The material layer 702 may generally have any suitable starting shape such that when oxidized and/or etched by the methods described 15 herein, the material layer 702 may be formed into a floating gate having an inverted T shape. The material layer 702 may have a height of greater than about 30 nm, or up to about 130nm. The material layer 702 may have a ratio of height to width of greater than about 2:1.

**[0063]** Next, at 604, the material layer 702 is selectively oxidized to form a first oxide layer 704 as shown in Figure 7B. The first oxide layer 704 is formed on the top and sidewalls of 20 the material layer 702, and may comprise a silicon oxide, metal oxide, or the like. In some embodiments, the first oxide layer 704 may consume the material layer 702 to a depth of about 5 to about 15 nm, or about 10 nm. The first oxide layer 704 may further thicken a portion of the STI region 302. The formation of the oxide layer may be performed using wet or oxidation, rapid thermal oxidation (RTO), radical oxidation, or plasma oxidation, for example, 25 decoupled plasma oxidation (DPO). In some embodiments, where a low thermal budget and/or reduced diffusion of oxygen are desired, plasma oxidation or radical oxidation may be utilized. A low thermal budget may be required to prevent thickening of the tunnel oxide layer 104 during the oxidation of the material layer 702.

**[0064]** The remaining portion of the material layer 702 after oxidation may be generally in 30 the shape of an inverted T having a greater dimensions than the desired final form (*e.g.*, the height of the base and/or the width of the stem may be greater). At 606, the first oxide layer

704 is removed by an etch process in the same chamber as step 604 resulting in the floating gate having a generally inverted T shape as illustrated by the remaining portion of the material layer 702 depicted in Figure 7C. The etch process may be a wet or dry etch, or a reactive ion etch. The etch process may use chemicals or gases comprising hydrofluoric acid (HF) 5 hydrochloric acid (HCl), or the like. The etch process may be selective, for example, selectively removing the first oxide layer 704. In one embodiment, the etch process is selective to silicon oxide, and removes the first oxide layer 704 comprising silicon oxide relative to the material layer comprising polysilicon. The etch process may further remove a portion of the STI region 302 during removal of the first oxide layer 704.

10 [0065] At 608, an etch process may be used to remove an additional portion of the remaining material layer 702 to form a floating gate having a desired inverted T shape, as depicted in Figure 7D. The etch process may include wet or dry etch, reactive ion etch, or the like. In one embodiment, the etch process is a reactive ion etch. The floating gate formed using method 600 may be similar in dimension to the floating gates formed in methods 200 and 400, as 15 discussed above.

20 [0066] Upon etching the material layer 702 to form a floating gate having an inverted T shape and the dimensions discussed above, the method 600 generally ends and further processing to complete the fabrication of the memory device may be performed. Further processing of the memory device 700 may include the deposition of an IPD layer and a control gate layer as discussed above. Optionally, a gap fill and CMP process, followed by an etch back of the filled region to control the desired depth of the IPD layer in the region between adjacent floating gates may be performed prior to the IPD layer deposition, as discussed above.

25 [0067] Alternatively, in some embodiments, after removal of the first oxide layer 704, the method 600 may proceed from in the same chamber 606 to 610, where the material layer may be selectively oxidized to form a second oxide layer 706. The second oxide layer 706 is formed on the top and sidewalls of the remaining portion of the material layer 702 as depicted in Figure 8A, and may comprise a silicon oxide, metal oxide, or the like. In some embodiments, the second oxide layer 706 may consume the material layer 702 to a depth of about 5 to about 15 nm, or about 10 nm. The formation of the oxide layer may be performed 30 using wet or oxidation, rapid thermal oxidation (RTO), radical oxidation, or plasma oxidation, for example, decoupled plasma oxidation (DPO), and a low thermal budget and/or reduced

diffusion of oxygen are desired, plasma oxidation or radical oxidation may be utilized. In some embodiments, low thermal budget directional oxidation (e.g., plasma oxidation) maybe used where the second oxide layer 706 grows at a higher rate on horizontal surfaces of the material layer 702 than on sidewall surfaces.

5 [0068] The remaining portion of the material layer 702 after selective oxidation to form the second oxide layer 706 may be generally in the shape of an invert T. At 612, the second oxide layer 706 is removed by an etch process to complete the formation of a floating gate having an inverted T as illustrated by the remaining portion of the material layer 702 depicted in Figure 8B. The etch process may be a dry etch, or a reactive ion etch. The etch process may use 10 chemicals or gases comprising hydrofluoric acid (HF) hydrochloric acid (HCl), or the like. The etch process may be selective, for example, selective for removing the second oxide layer 706. In one embodiment, the etch process is selective to silicon oxide, and removes the second oxide layer 706 comprising silicon oxide relative to the material layer 702 comprising polysilicon. The etch process may further remove a portion of the STI region 302 during 15 removal of second oxide layer 706.

20 [0069] Upon etching the remaining portion of material layer 702 to remove the second oxide layer 706 and form a floating gate having a desired inverted T shape the method 600 generally ends. The floating gate formed by the method 600 may have equivalent dimensions to those discussed above at 608. Further processing of the memory device 700 may include the deposition of an IPD layer and a control gate layer as discussed above.

25 [0070] Although high thermal budget processes may be advantageous for some embodiments, as discussed above, the oxidation rate of a material layer, such as material layer 702 above, tends to saturate as higher thermal budgets are applied. For example, this can result in an inability to shape the material layer 702 into a shape having the desired dimensions, thickening of the tunnel oxide layer 104, or both. Further, while the oxidation rate can saturate using any of a broad range of temperatures, for example between about 30 to about 1100 degrees Celsius, the initial oxidation rate is high even at lower temperatures in the range, such as 30 degrees Celsius. This temperature range is valid for all oxidation processes disclosed herein. In addition, plasma oxidation or photochemical (UV or ozone) or dry/wet chemical 30 (e.g. ozone, nitric acid, hydrogen peroxide) based oxidation can occur at room temperature or below. Accordingly, the inventors have developed a method of shaping a material layer, such

as material layer 702, which advantageously utilizes a high initial oxidation rate as discussed below.

[0071] A schematic illustration of saturation in the oxidation rate at high thermal budgets is shown in Figure 9, which generally depicts a plot of an oxide layer thickness as a function of time. An isotherm 1000 is representative of an oxidation process where an oxide layer is continuously grown at a desired arbitrary temperature. Initially, over a first period 1002 of time in the isotherm 1000, the oxidation rate is high as illustrated by a first oxide layer thickness 1004 grown over the first period 1002. As time (and thermal budget) increases, the oxidation rate begins to saturate. For example, over a second period 1006 equivalent in duration to, and immediately following the first period 1002, a second oxide layer thickness 1008 grown during the second period 1006 is less than the first oxide layer thickness 1004 owing to a slower oxidation rate during the second period 1006. The inventors have further discovered that the general shape of the isotherm 1000 is followed at various temperatures.

[0072] Accordingly, to shape the material layer 702 to a desired shape, a high thermal budget may be required to achieve the necessary oxide layer thickness to form the desired dimensions of the floating gate. Unfortunately, during fabrication of some structures, the application of a high thermal budget oxidation process can undesirably cause oxygen (O<sub>2</sub>) to diffuse into exposed oxide layers (such as the tunnel oxide layer 104), causing the oxide layer to undesirably thicken.

[0073] As such, in some embodiments of the method 600, a repetitive oxidation and etch processes may advantageously utilize the high initial oxidation rate applied during the first period 1002, as described in Figure 9 above. For example, in some embodiments, at 604, a surface of a material layer (e.g., material layer 702) may be oxidized to form an oxide layer (e.g., first oxide layer 704) at an initial oxidation rate. The material layer 702 may be oxidized for a first period (e.g., first period 1002) of time where the initial oxidation rate is relatively high. After the oxidation rate decreases to a predetermined amount, for example during the second period 1006, the oxidation process is terminated. In some embodiments, the formation of the first oxide layer 704 may be terminated when the oxidation rate is about 90% or below, or about 75% or below, of the initial oxidation rate. In some embodiments, the formation of the first oxide layer 704 may be terminated when the oxidation rate is between about 0% to about 90%, or about 75%, of the initial rate.

**[0074]** Once the oxidation process has been terminated, at 606, at least some of the first oxide layer 704 is removed by an etching process (as discussed above and as illustrated in Figure 7C). As illustrated in Figure 7C, once the first oxide layer 704 has been removed, the material layer 702 may be at least partially formed into the desired shape as discussed above.

5 The removal of the first oxide layer 704 provides a fresh exposed surface of the material layer 702 which can further be oxidized until the desired shape of the material layer is formed. In some embodiments, the etch process may be a two-stage condensation and sublimation etch process, as described above. In some embodiments, the etch process may be terminated when the etch rate falls to about 0% to about 75%, or to about 90% of the initial etch rate. The 10 decrease in etch rate may be due to material contrast (e.g., Si to SiO<sub>2</sub> selectivity) or diffusion related saturation (e.g., on a homogeneous SiO<sub>2</sub> layer). The time dependency of the etch rate during the etch process may provide a method of additional and independent control of the material removal during the sacrificial oxidation. This provides the capability of layer-by-layer removal on a heterogeneous surface (Si/SiO<sub>2</sub>) as exemplified in Floating Gate formation 15 structures. This may be advantageously used when removing oxidized materials from a heterogeneous substrate to avoid non-uniform material removal.

**[0075]** For example, at 610, the exposed surface of the partially shaped material layer 702 is again oxidized to form another oxide layer (e.g., second oxide layer 706). The oxidation process proceeds at an initial oxidation rate that can be substantially equivalent to the initial 20 oxidation rate discussed above for the first oxidation layer 704 due to the removal of the first oxide layer 704. As above, after the oxidation rate decreases to a predetermined amount, for example during the second period 1006, the oxidation process is terminated. The desired point of termination of the process can be any time similar to discussed above. Oxidation to form the second oxide layer 706 is illustrated in Figure 8A.

25 **[0076]** Once the repeated oxidation process has been terminated, at 612, at least some of the second oxide layer 706 is removed by an etching process (as discussed above and as illustrated in Figure 8B). As illustrated in Figure 8B, once the second oxide layer 706 has been removed, the material layer 702 may be formed into the desired shape, as discussed above. Alternatively, the removal of the second oxide layer 706 again provides a fresh exposed 30 surface of the material layer 702 which can further be oxidized until the desired shape of the material layer is formed. As such, although disclosed as repeating oxidation and etch process

just once, the repetition of these processes may continue as many times as necessary to form the desired shaped of the material layer (*i.e.*, the process can be repeated one or more times).

[0077] Oxidizing in a cyclical process of oxidation and removal of an oxide layer makes it possible to form more oxide at the same thermal budget as compared to an oxidation process 5 performed continuously. Performing the cyclical process of oxidation and removal of an oxide layer in a single chamber can greatly increase process throughput. For example, as shown in Figure 9, a continuously applied oxidation process such as illustrated by the isotherm 1000 applied over the first and second periods 1002, 1006 will form an oxide layer having a thickness which is the sum of the first and second thicknesses 1004, 1008. However, a cyclical 10 oxidation and removal process, for example forming a first oxide layer (*e.g.*, first oxide layer 704) over the first period 1002, removing the first oxide layer, and oxidizing the material layer to form a second oxide layer (*e.g.*, second oxide layer 706) over the second period 1006 can result in a total oxide thickness (*e.g.*, summation of the thicknesses of the first and second 15 oxide layer 704, 706) which is twice the first thickness 1004 using the same thermal budget as a continuous oxidation process.

[0078] An isotherm 1010 which schematically illustrates the cyclical oxidation and removal process is shown in Figure 9. As illustrated, the isotherm 1010 deviates substantially from the isotherm 1000 (representative of a continuous oxidation process) after the first period 1002. The isotherm 1010 is depicted as linear in Figure 10, however, that is merely illustrative. The 20 isotherm 1010 can have any shape based on how the cyclical oxidation and removal process is applied. For example, if each repeat oxidation process is for the same period of time (*e.g.*, the first period 1002), then the isotherm 1010 can have a shape which repeats the shape of the isotherm 1010 during the first period 1002 at each successive step. Alternatively, a successive 25 step in the cyclical oxidation and removal process may be applied for a different duration than the first period (not shown), and the shape of the isotherm 1010 can vary accordingly. However, the total oxide formed during the cyclical oxidation and removal process will be greater than that formed by a continuous oxidation process (*e.g.*, isotherm 1000) using the same thermal budget. In some embodiments, the total oxide formed during the cyclical oxidation and removal process may be up to about 3 times greater than that formed by a 30 continuously oxidation process using the same thermal budget.

**[0079]** The above cyclical oxidation and removal process can be advantageously used to form other structures, including structures having sub-lithographic dimensions. Such structures may include, for example, an ultra thin floating gate, the fin of a finFET device, a patterned hard mask, or the like.

5   **[0080]** For example, in some embodiments, the cyclical oxidation and removal process can be utilized to form an ultra thin floating gate as illustrated in Figures 11A-D. Figures 11A-D depict the stages of fabrication of a floating gate 1102 in accordance with some embodiments of the present invention. The method begins as shown in Figure 11A by providing a partially fabricated memory device 1100. The memory device 1100 is similar in structure and 10 composition to the memory device 100 discussed above. The memory structure 1100 includes the substrate 102 having the tunnel oxide layer 104 disposed thereon. A material layer 1102, similar in composition to any material layer discussed above, is disposed atop the tunnel oxide layer 104. An STI region 1104, similar in composition to the STI regions discussed above, is disposed on either side of the material layer 1102 and adjacent thereto. The STI regions 1104 15 separate the individual memory cells of the device 1100. Generally, a top surface 1103 of the STI region 1104 and a top surface 1105 of the material layer 1102 are substantially planar.

20   **[0081]** Next, the cyclical oxidation and removal process discussed above can be utilized in the same chamber to thin the material layer 1102 to a desired shape (e.g., thickness). The top surface 1105 of the material layer 1102 may be oxidized as discussed above to form an oxide layer 1106 at an initial oxidation rate as illustrated in Figure 11B. The oxidation process is terminated when the oxidation rate falls below a specified percentage of the initial rate as 25 discussed above. The oxide layer 1106 (along with a portion of the oxide in the STI region 1104) is then removed by an etch process as illustrated in Figure 11C. The oxidation and removal processes can be repeated until the material layer 1102 is thinned to a desired shape to form a floating gate.

30   **[0082]** In some embodiments, the desired shape of the material layer 1102 may have a first width at the bottom of the material layer 1102 that is substantially equivalent to a second width at the top of the material layer 1102. Further, the desired shape may include a final thickness of the material layer 1102, for example, of less than about 5 nanometers (although other thicknesses are contemplated, for example, about 1 to about 20 nm, or about 1 to about 10 nm). The cyclical oxidation and removal process advantageously thins the material layer 1102 into

the desired shape of a floating gate without unwanted oxidative thickening of the underlying tunnel oxide layer 104. The inventors have discovered that the oxide present in the STI region 1104 acts as a barrier to prevent the oxidation process from reaching the tunnel oxide layer 104. As illustrated in Figure 10D, an IPD layer 1108 and conductive layer 1110 may be 5 deposited atop the thinned material layer 1102 to form a completed memory device 1100. The IPD layer 1108 and the control gate layer 1100 each may comprise any suitable material or combination of materials for an IPD layer and control gate layer as discussed above.

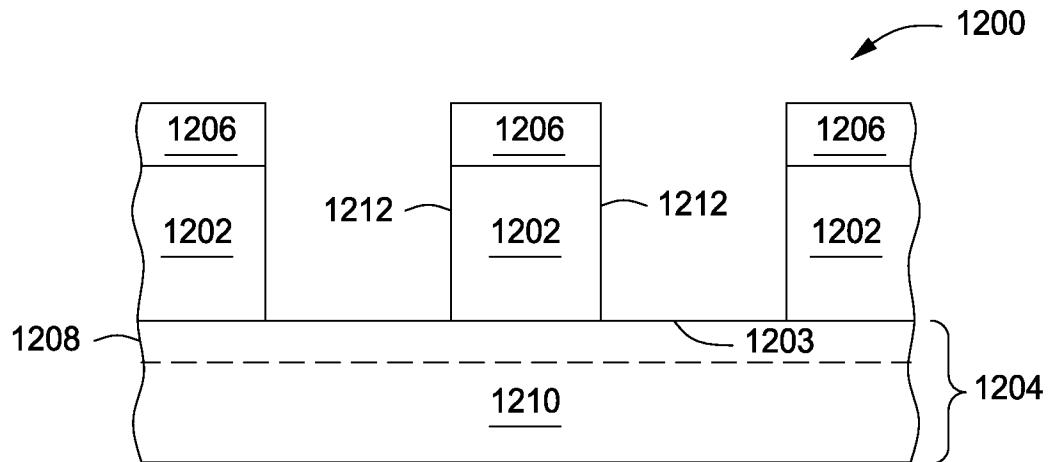

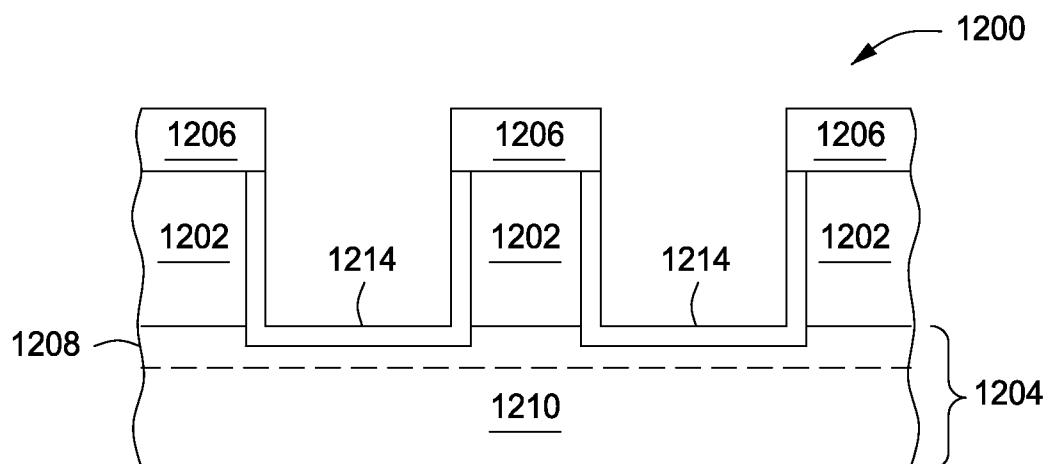

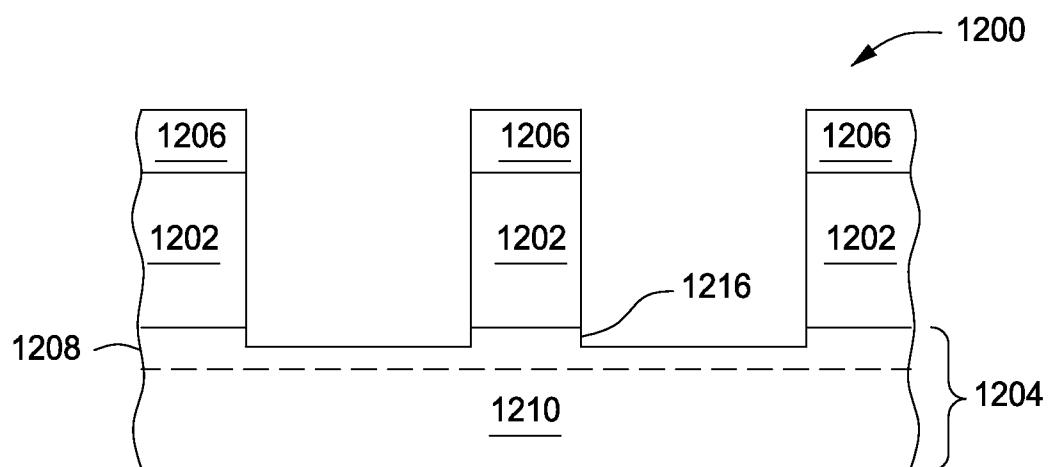

**[0083]** In some embodiments, the cyclical oxidation and removal process can be utilized to form structures to critical dimensions that are smaller than those dimensions accessible by 10 lithographic techniques. For example, Figures 11A-C depicts the stages of utilizing the cyclical oxidation and removal process to trim a lithographically patterned structure 1200 to a sub-lithographic critical dimension. The structure 1200 may be, for example, a partially fabricated logic device, such as a FinFET, or a partially fabricated hard mask structure.

**[0084]** The structure 1200 includes a material layer 1202 deposited atop a substrate 1204. 15 The material layer 1202 may be deposited as illustrated in Figure 11A such that one or more portions of the upper surface 1203 of the substrate 1204 remain exposed. A mask layer 1206 may be deposited atop the material layer 1202. The mask layer 1206, for example, may have been used to pattern the material layer 1202 to a lithographically defined critical dimension.

**[0085]** The substrate 1204 may be any suitable substrate as discussed above. In some 20 embodiments, for example in the fabrication of a logic device the substrate 1204 may comprise silicon (Si) or silicon dioxide (SiO<sub>2</sub>). In some embodiments, for example in the fabrication of a hard mask structure, the substrate 1204 may comprise a layer 1208 (illustrated by dotted line in Figures 11A-C) deposited atop a non-silicon layer 1210 to be patterned by the hard mask. The layer 1208 may function as a second hard mask when etching the non-Si layer 1210. The layer 25 1208 may comprise one or more of silicon dioxide (SiO<sub>2</sub>), silicon nitride (SiN), aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) or other materials deposited at low temperatures, or a buried oxide formed during silicon on insulator (SOI) fabrication. The non-silicon layer 1210 may comprise metals, such as one or more of tungsten (W), titanium nitride (TiN) or the like, and/or a dielectric material, such as SiO<sub>2</sub>, high-k binary oxides, ternary oxides, phase-change materials (such as 30 nickel oxide, germanium antimony telluride, or the like) and/or alternate channel materials in Group IV (e.g., Ge, SiGe), and/or III-V materials (e.g., GaAs, GaN, InP etc) and/or organics

(e.g., pentacene, fullerenes, or the like). Some materials may degrade at temperatures above about 100 degrees Celsius, but can benefit from sub-lithographic patterning made accessible by the inventive methods to enhance device performance.

**[0086]** The mask layer 1206 may be any suitable mask layer such as a hard mask or 5 photoresist layer. The mask layer 1206 may comprise at least one of SiO<sub>2</sub>, SiN, silicides, such as titanium silicide (TiSi), nickel silicide (NiSi) or the like, or silicates, such as aluminum silicate (AlSiO), zirconium silicate (ZrSiO), hafnium silicate (HfSiO), or the like.

**[0087]** The cyclical oxidation and removal process discussed above can be applied to the 10 existing structure 1200 to trim the lithographically patterned material layer 1202 to a sub lithographic critical dimension. As illustrated in Figure 11A, a side wall 1212 of the material layer 1202 and, in some embodiments the exposed upper surface 1203 of the substrate 1204 may be oxidized to form an oxide layer 1214 at an initial oxidation rate as discussed above. The oxidation process may be terminated after a first period of time when the initial oxidation rate falls below a fraction of the initial rate as discussed above.

**[0088]** The oxide layer 1214 is removed, as shown in Figure 11C, using an etch process, 15 which may be any suitable etch process, as discussed above, performed in the same chamber as the oxidation process. The oxidation and removal processes may be repeated as necessary to form the material layer 1202 to a desired shape, for example, having a desired sub-lithographic dimension. In some embodiments where the substrate 1204 (or the oxide layer 1208) is at least 20 partially consumed by the oxidation and/or etch processes, upon completion of the cyclical oxidation and etch process, the material layer 1202 may be disposed on a raised portion 1216 of the substrate 1204 formed by the cyclical process. The raised portion 1216 may have a width that is substantially equivalent to a first width proximate the bottom of the material layer 1202 and a second width proximate the top of the material layer 1202. In some embodiments, 25 the first width and second width of the trimmed material layer 1202 may be between about 1 to about 30 nanometers. In some embodiments, the trimmed material layer 1202 (e.g., the desired shape of the material layer) has an aspect ratio of between about 0.5 to about 20. In some embodiments, the height of the trimmed material layer 1202 is between about 1 to about 30 nanometers. Alternatively, in some embodiments, the substrate may substantially not be 30 consumed by the cyclic process and the raised portion 1216 may not be present. For example, the raised portion maybe avoided if the etch process is selective to the material of the layer

1208, *e.g.*, a layer 1208 comprising SiN may not be etched while etching SiO<sub>2</sub> in some embodiments.

**[0089]** The structure 1200 after trimming the material layer 1202 using the cyclical oxidation and removal process may be further processed. For example, the material layer 1202 may be 5 utilized as a fin in a FinFET device and a gate layer and source/drain regions may be deposited. Alternatively, the trimmed material layer 1202 may itself be utilized to define the critical dimension of a hard mask to be formed from the substrate 1204. Further, the inventive methods may be advantageously utilized for the reduction of line-edge roughness and surface 10 roughness created by lithography and fin etch. The reduction of roughness and variation on FinFET channel shape and sidewall surface may improve device and system performance by reducing noise and variability.

**[0090]** It is further contemplated that parts and/or the whole of the individual methods described above may be used interchangeably where appropriate to form a memory device having a floating gate with an inverted T shape. For example, a nitride layer (as discussed with 15 respect to Figure 4) may be deposited atop the material layer 702 of the partially fabricated memory device 700 (as discussed with respect to Figure 6) to further limit thickening of the tunnel oxide layer. Other combinations and variations of the methods disclosed herein are similarly within the scope of the present invention.

**[0091]** The methods described herein, for example, such as oxidation and etch processes are 20 performed in a single substrate processing chamber configured to provide the respective process gases, plasmas, and the like, necessary to perform the processes discussed above.

**[0092]** Thus, the inventive method is performed in a single reactor or chamber configured to perform oxidation, etch and, optionally, nitridation processes. The process chamber may be 25 configured to perform an oxidation process including one or more of ultraviolet (UV)-, ozone-, thermal-, plasma- based oxidation, or other radical based oxidation schemes (*e.g.*, hot wire). As such, a gas source may be coupled to the chamber to provide one or more oxygen containing gases for the oxidation process. The process chamber may further be configured to perform an etch process including one or more of plasma etching, or a two-stage etch including condensation and sublimation, as discussed above. The two-stage etch process can be 30 activated with a plasma, or may be heat activated with no plasma provided. The process chamber is further configured with a thermal control system for rapidly controlling the

temperature of the substrate to facilitate the two-stage etch process. For example, the process chamber may include a cyclical heating (and cooling) capability for cyclically heating and cooling the substrate. Such heating capability may include flash energy based systems (such as lamps, lasers, or the like), heat sources that provide a large thermal gradient between at least 5 two predetermined substrate processing zones in the chamber (such as suitable to selectively maintain low substrate temperature suitable for condensation and high substrate temperature suitable for sublimation by positioning the substrate in the respective processing zone), or via the use of a combination of a remote plasma source for remote plasma activation of etching gases and a direct plasma source to provide plasma induced heating. The substrate support 10 may be movable to support the substrate in the predetermined processing zones and may further include lift pins or other substrate lifting mechanisms to selectively raise the substrate from the support surface during heating portions of the process and return the substrate to the substrate support surface during cooling portions of the process. The substrate support may also have a cooling (or temperature control) system to maintain the substrate support at a 15 predetermined temperature (such as proximate a condensation temperature for the etch process). For example, in some embodiments, the thermal control system is suitable to rapidly (e.g., in less than about 1 second, or up to about 10 seconds, or up to about 100 seconds) alter the substrate temperature from about 30 degrees Celsius (to facilitate condensation) to at least about 100 degrees Celsius (to facilitate sublimation).

20 [0093] For example, a schematic of a process chamber 1300 having such a configuration is illustrated in Figure 12. The process chamber 1300 includes a substrate support 1302 disposed therein for supporting a substrate 1303 thereon. A gas source 1304 is coupled to the chamber 1300 to provide oxygen-containing gases, etching gases, and optionally inert gases and/or nitrogen-containing gases (for example, any of the gases discussed above). A plasma source 25 1306 may be coupled to the process chamber to provide energy to the gases provided by the gas source to form at least one of an oxidizing plasma or an etching plasma, and, optionally, a nitridizing plasma. A heating source 1308 is coupled to the process chamber to selectively heat the substrate, and, optionally, to provide energy to gases of the gas source to form at least one of an oxidizing or an etching chemistry. A controller 1310 is coupled to the process 30 chamber 1300 for controlling the operation and components thereof. The gas source 1304 may be any suitable gas source, such as a gas panel having multiple gas sources or the like. The gas source 1304 is minimally configured to provide an oxygen-containing gas and an etching gas

to respectively form one or more of, an oxidizing plasma, an etching plasma, an oxidizing chemistry, or a etching chemistry. Optionally, the gas source 1304 may also provide one or more inert gases and/or a nitrogen-containing gas to form a nitridizing plasma.

**[0094]** The plasma source 1306 may be any suitable plasma source or plurality of plasma sources, such as a remote plasma source, inductively coupled source, capacitively coupled source, a first source coupled to an overhead electrode (not shown) and a second source (not shown) coupled to the substrate support, or any other plasma source configurations to form a plasma. In some embodiments, the plasma source 1306 is configured to provide energy to the gases of the gas source 1304 to form the oxidizing plasma, the etching plasma and, optionally, the nitridizing plasma. In some embodiments, the plasma source can supply heat to the wafer for sublimation of reaction byproducts during etching.

**[0095]** The heating source 1308 may be any suitable heating source to heat the substrate and/or to form an oxidizing or etching chemistry from a gas provided by the gas source 1304. For example, the heating source may include one or more lamps configured to heat the substrate or gases provided by the gas source. Alternatively or in combination, the heating source may include a heater, such as a resistive heater or the like, which may for example be disposed in the substrate support 1302 or a gas showerhead for providing the process gases to the process chamber.

**[0096]** In operation, the system controller 1310 enables data collection and feedback from the respective systems such as gas source 1304, plasma source 1306, and heating source 1308 to optimize performance of the tool 1300. The system controller 1310 generally includes a Central Processing Unit (CPU), a memory, and a support circuit. The CPU may be one of any form of a general purpose computer processor that can be used in an industrial setting. The support circuit is conventionally coupled to the CPU and may comprise a cache, clock circuits, input/output subsystems, power supplies, and the like. Software routines, such as one for performing a method of forming a floating gate as described above, when executed by the CPU, transform the CPU into a specific purpose computer (controller) 1310. The software routines may also be stored and/or executed by a second controller (not shown) that is located remotely from the tool 1300. Specific single chamber apparatus for performing processes described above in accordance with one or more embodiments will now be described.