(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7337563号**

**(P7337563)**

(45)発行日 令和5年9月4日(2023.9.4)

(24)登録日 令和5年8月25日(2023.8.25)

(51)国際特許分類

|         |                |     |         |       |

|---------|----------------|-----|---------|-------|

| G 0 6 N | 3/063(2023.01) | F I | G 0 6 N | 3/063 |

| G 0 6 G | 7/60 (2006.01) |     | G 0 6 G | 7/60  |

請求項の数 9 (全104頁)

(21)出願番号 特願2019-118472(P2019-118472)

(22)出願日 令和1年6月26日(2019.6.26)

(65)公開番号 特開2020-9432(P2020-9432A)

(43)公開日 令和2年1月16日(2020.1.16)

審査請求日 令和4年6月13日(2022.6.13)

(31)優先権主張番号 特願2018-124122(P2018-124122)

(32)優先日 平成30年6月29日(2018.6.29)

(33)優先権主張国・地域又は機関

日本国(JP)

|          |                                                |

|----------|------------------------------------------------|

| (73)特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72)発明者  | 木村 肇<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内        |

| (72)発明者  | 黒川 義元<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| 審査官      | 武田 広太郎                                         |

最終頁に続く

(54)【発明の名称】 半導体装置、及び電子機器

**(57)【特許請求の範囲】****【請求項1】**

第1回路を有し、

前記第1回路は、第1入力端子と、第2入力端子と、第1出力端子と、第2出力端子と、第2インバータ回路と、第3インバータ回路と、第4インバータ回路と、第5インバータ回路と、切り替え回路と、を有し、

前記切り替え回路は、第1トランジスタと、第2トランジスタと、第1インバータ回路と、を有し、

前記第1トランジスタは、第1ゲートと、第2ゲートと、を有し、

前記第2トランジスタは、第3ゲートと、第4ゲートと、を有し、

前記切り替え回路は、第3入力端子を有し、

前記第1トランジスタの前記第1ゲートは、前記第3入力端子に電気的に接続され、

前記第2トランジスタの前記第3ゲートは、前記第1インバータ回路の出力端子に電気的に接続され、

前記第1インバータ回路の入力端子は、前記第3入力端子に電気的に接続され、

前記第1入力端子は、前記第2インバータ回路の入力端子に電気的に接続され、

前記第2入力端子は、前記第3インバータ回路の入力端子に電気的に接続され、

前記第1出力端子は、前記第4インバータ回路の出力端子に電気的に接続され、

前記第2出力端子は、前記第5インバータ回路の出力端子に電気的に接続され、

前記切り替え回路は、

10

20

前記第3入力端子に入力された信号に応じて、前記第2インバータ回路の出力端子と、前記第4インバータ回路又は前記第5インバータ回路の一方の入力端子と、の間を導通状態にし、かつ前記第3インバータ回路の出力端子と、前記第4インバータ回路又は前記第5インバータ回路の他方の入力端子と、の間を導通状態にする機能と、

前記第1トランジスタの前記第2ゲートの電位に応じて、前記第2インバータ回路の出力端子から出力された信号が、前記第4インバータ回路の入力端子に入力されるまでの時間を変動させる機能と、

前記第2トランジスタの前記第4ゲートの電位に応じて、前記第3インバータ回路の出力端子から出力された信号が、前記第4インバータ回路の入力端子に入力されるまでの時間を変動させる機能と、を有する、

半導体装置。

#### 【請求項2】

第1回路を有し、

前記第1回路は、第1入力端子と、第2入力端子と、第1出力端子と、第2出力端子と、第2回路と、第3回路と、切り替え回路と、を有し、

前記切り替え回路は、第1トランジスタと、第2トランジスタと、第1インバータ回路と、を有し、

前記第1トランジスタは、第1ゲートと、第2ゲートと、を有し、

前記第2トランジスタは、第3ゲートと、第4ゲートと、を有し、

前記切り替え回路は、第3入力端子を有し、

前記第1トランジスタの前記第1ゲートは、前記第3入力端子に電気的に接続され、

前記第2トランジスタの前記第3ゲートは、前記第1インバータ回路の出力端子に電気的に接続され、

前記第1インバータ回路の入力端子は、前記第3入力端子に電気的に接続され、

前記第1入力端子は、前記第2回路の入力端子に電気的に接続され、

前記第2入力端子は、前記第3回路の入力端子に電気的に接続され、

前記第2回路は、前記第2回路の入力端子に入力された信号を補正して、前記第2回路の出力端子に補正された信号を出力する機能を有し、

前記第3回路は、前記第3回路の入力端子に入力された信号を補正して、前記第3回路の出力端子に補正された信号を出力する機能を有し、

前記切り替え回路は、

前記第3入力端子に入力された信号に応じて、前記第2回路の出力端子と、前記第1出力端子又は前記第2出力端子の一方と、の間を導通状態にし、かつ前記第3回路の出力端子と、前記第1出力端子又は前記第2出力端子の他方と、の間を導通状態にする機能と、

前記第1トランジスタの前記第2ゲートの電位に応じて、前記第2回路の出力端子から出力された信号が、前記第1出力端子に入力されるまでの時間を変動させる機能と、

前記第2トランジスタの前記第4ゲートの電位に応じて、前記第3回路の出力端子から出力された信号が、前記第1出力端子に入力されるまでの時間を変動させる機能と、を有する、

半導体装置。

#### 【請求項3】

請求項1又は請求項2において、

前記切り替え回路は、第1保持部を有し、

前記第1保持部は、前記第1トランジスタの前記第2ゲートの電位、及び前記第2トランジスタの前記第4ゲートの電位を保持する機能を有する、

半導体装置。

#### 【請求項4】

請求項1又は請求項2において、

前記切り替え回路は、第1保持部と、第2保持部と、を有し、

前記第1保持部は、前記第1トランジスタの前記第2ゲートの電位を保持する機能を有

10

20

30

40

50

し、

前記第2保持部は、前記第2トランジスタの前記第4ゲートの電位を保持する機能を有する、

半導体装置。

**【請求項5】**

請求項1又は請求項2において、

前記切り替え回路は、第1保持部と、第2保持部と、第1スイッチと、第2スイッチと、を有し、

前記第1保持部は、前記第1スイッチを介して、前記第1トランジスタの前記第2ゲートと、前記第2トランジスタの前記第4ゲートと、に電気的に接続され、

10

前記第2保持部は、前記第2スイッチを介して、前記第1トランジスタの前記第2ゲートと、前記第2トランジスタの前記第4ゲートと、に電気的に接続され、

前記第1スイッチ、又は第2スイッチの一方をオン状態にし、他方をオフ状態にすることで、前記第1トランジスタの前記第2ゲート及び前記第2トランジスタの前記第4ゲートと、前記第1保持部又は前記第2保持部の一方と、の間を導通状態にする機能を有する、半導体装置。

**【請求項6】**

請求項1乃至請求項5のいずれか一において、

前記第1回路を複数段、有し、

複数の前記第1回路に含まれている前記切り替え回路は、第4入力端子を有し、

20

前段の前記第1回路の第1出力端子は、後段の前記第1回路の第1入力端子に電気的に接続され、

前段の前記第1回路の第2出力端子は、後段の前記第1回路の第2入力端子に電気的に接続され、

全ての前記第1回路の前記第1トランジスタの前記第2ゲート、及び前記第2トランジスタの前記第4ゲートには、それぞれ対応する第1データに応じた電位が保持され、かつ全ての前記切り替え回路の前記第3入力端子には、それぞれ対応する第2データに応じた信号が入力されている場合に、一段目の前記第1回路の前記第1入力端子と前記第2入力端子とにそれぞれ入力信号が入力されることによって、最終段の前記第1回路の第1出力端子と前記第2出力端子とから出力されるそれぞれの出力信号の時間差は、前記第1データと前記第2データの積和に応じた時間となる、

30

半導体装置。

**【請求項7】**

請求項6において、

第4回路を有し、

前記第4回路は、前記最終段の前記第1回路の前記第1出力端子と、前記第2出力端子と、に電気的に接続され、

前記第4回路は、前記出力信号の時間差に応じた信号を生成する機能を有する、

半導体装置。

**【請求項8】**

請求項1乃至請求項7のいずれか一において、

前記第1トランジスタ及び前記第2トランジスタの少なくともいずれか一は、チャネル形成領域に金属酸化物を有する、

半導体装置。

**【請求項9】**

請求項1乃至請求項8のいずれか一の半導体装置と、筐体と、を有し、

前記半導体装置によってニューラルネットワークの演算を行う、

電子機器。

**【発明の詳細な説明】**

**【技術分野】**

40

50

**【0001】**

本発明の一態様は、半導体装置、及び電子機器に関する。

**【0002】**

なお本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の技術分野は、物、方法、又は、製造方法に関するものである。又は、本発明の一態様は、プロセス、マシン、マニュファクチャ、又は、組成物（コンポジション・オブ・マター）に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、蓄電装置、撮像装置、記憶装置、信号処理装置、プロセッサ、電子機器、システム、それらの駆動方法、それらの製造方法、又はそれらの検査方法を一例として挙げることができる。

10

**【背景技術】****【0003】**

現在、人間の脳の仕組みを模した集積回路の開発が盛んに進められている。当該集積回路は、脳の仕組みが電子回路として組み込まれており、人間の脳の「ニューロン」と「シナプス」に相当する回路を有する。そのため、そのような集積回路を、「ニューロモーフィック」や「ブレインモーフィック」と呼ぶこともある。当該集積回路は、非ノイマン型アーキテクチャを有し、処理速度の増加に伴って消費電力が大きくなるノイマン型アーキテクチャと比較して、極めて少ない消費電力で並列処理を行えると期待されている。

**【0004】**

「ニューロン」と「シナプス」とを有する神経回路網を模した情報処理のモデルは、人工ニューラルネットワーク（ANN）と呼ばれる。例えば、特許文献1、特許文献2、非特許文献1、及び非特許文献2には、ReRAM（Resistive Random Access Memory）を用いて、人工ニューラルネットワークを構成した演算装置について開示されている。特に、非特許文献1、及び非特許文献2には、当該演算装置を有する脳の仕組みを模した回路について開示されている。

20

**【先行技術文献】****【特許文献】****【0005】****【文献】特許第5885719号公報**

特開2017-228295号公報

30

**【非特許文献】****【0006】**

**【文献】D. Miyashita et al., IEEE Asian Solid-State Circuits Conference, Nov. 7-9, 2016, S4-2(4077), pp. 25-28.**

D. Miyashita et al., IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 52, NO. 10, Oct. 2017, pp. 2679-2689.

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

人工ニューラルネットワークでは、2つのニューロン同士を結合するシナプスの結合強度（重み係数という場合がある。）と、2つのニューロン間で伝達する信号と、を乗じる計算が行われる。特に、階層型の人工ニューラルネットワークでは、第1層の複数の第1ニューロンと第2層の第2ニューロンとの間のそれぞれのシナプスの結合強度と、第1層の複数の第1ニューロンから第2層の第2ニューロンのーに入力されるそれぞれの信号と、を乗じて足し合わせる必要があり、人工ニューラルネットワークの規模に応じて、当該結合強度の数、及び当該信号を示すパラメータの数が決まる。つまり、人工ニューラルネットワークは、階層の数、ニューロン数などが多くなる程、「ニューロン」及び「シナプス」のそれに相当する回路の数が多くなり、演算量も膨大になることがある。

40

50

**【 0 0 0 8 】**

チップを構成する回路の数が増えると消費電力が高くなり、装置の駆動時の発熱量も大きくなる。特に、発熱量が高くなるほど、チップに含まれている回路素子の特性に影響が出るため、チップを構成する回路は温度による影響を受けにくい回路素子を有することが好ましい。

**【 0 0 0 9 】**

本発明の一態様は、階層型の人工ニューラルネットワークが構築された半導体装置などを提供することを課題の一とする。また、本発明の一態様は、消費電力が低い半導体装置などを提供することを課題の一とする。また、本発明の一態様は、環境の温度の影響を受けにくい半導体装置などを提供することを課題の一とする。また、本発明の一態様は、新規な半導体装置などを提供することを課題の一とする。

10

**【 0 0 1 0 】**

なお、本発明の一態様の課題は、上記列挙した課題に限定されない。上記列挙した課題は、他の課題の存在を妨げるものではない。なお他の課題は、以下の記載で述べる、本項目で言及していない課題である。本項目で言及していない課題は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一態様は、上記列挙した課題、及び他の課題のうち、少なくとも一つの課題を解決するものである。なお、本発明の一態様は、上記列挙した課題、及び他の課題の全てを解決する必要はない。

**【課題を解決するための手段】**

20

**【 0 0 1 1 】****( 1 )**

本発明の一態様は、第1トランジスタと、第2トランジスタと、第3トランジスタと、第4トランジスタと、第1インバータ回路と、を含む回路と、保持部と、を有し、保持部は、第5トランジスタと容量素子と、を有し、第1トランジスタは、第1ゲートと、第2ゲートと、を有し、第2トランジスタは、第3ゲートと、第4ゲートと、を有し、第1トランジスタの第1端子は、第3トランジスタの第1端子に電気的に接続され、第4トランジスタの第1端子は、第2トランジスタの第1端子に電気的に接続され、第1トランジスタの第2端子は、第2トランジスタの第2端子に電気的に接続され、第4トランジスタの第2端子は、第3トランジスタの第2端子に電気的に接続され、第1インバータ回路の入力端子は、第1トランジスタの第1ゲートと、第4トランジスタのゲートと、に電気的に接続され、第1インバータ回路の出力端子は、第2トランジスタの第3ゲートと、第3トランジスタのゲートと、に電気的に接続され、第5トランジスタの第1端子は、第1トランジスタの第2ゲートと、第2トランジスタの第4ゲートと、容量素子と、に電気的に接続されている、半導体装置である。

30

**【 0 0 1 2 】****( 2 )**

また、本発明の一態様は、第1回路を有し、第1回路は、第1入力端子と、第2入力端子と、第1出力端子と、第2出力端子と、第2インバータ回路と、第3インバータ回路と、第4インバータ回路と、第5インバータ回路と、切り替え回路と、を有し、切り替え回路は、第1トランジスタと、第2トランジスタと、第1インバータ回路と、を有し、第1トランジスタは、第1ゲートと、第2ゲートと、を有し、第2トランジスタは、第3ゲートと、第4ゲートと、を有し、切り替え回路は、第3入力端子を有し、第1トランジスタの第1ゲートは、第3入力端子に電気的に接続され、第2トランジスタの第3ゲートは、第1インバータ回路の出力端子に電気的に接続され、第1インバータ回路の入力端子は、第3入力端子に電気的に接続され、第1入力端子は、第2インバータ回路の入力端子に電気的に接続され、第2入力端子は、第3インバータ回路の入力端子に電気的に接続され、第1出力端子は、第4インバータ回路の出力端子に電気的に接続され、第2出力端子は、第5インバータ回路の出力端子に電気的に接続され、切り替え回路は、第3入力端子に入力された信号に応じて、第2インバータ回路の出力端子と、第4インバータ回路又は第5

40

50

インバータ回路の一方の入力端子と、の間を導通状態にし、かつ第3インバータ回路の出力端子と、第4インバータ回路又は第5インバータ回路の他方の入力端子と、の間を導通状態にする機能と、第1トランジスタの第2ゲートの電位に応じて、第2インバータ回路の出力端子から出力された信号が、第4インバータ回路の入力端子に入力されるまでの時間を変動させる機能と、第2トランジスタの第4ゲートの電位に応じて、第3インバータ回路の出力端子から出力された信号が、第4インバータ回路の入力端子に入力されるまでの時間を変動させる機能と、を有する、半導体装置である。

#### 【0013】

(3)

また、本発明の一態様は、第1回路を有し、第1回路は、第1入力端子と、第2入力端子と、第1出力端子と、第2出力端子と、第2回路と、第3回路と、切り替え回路と、を有し、切り替え回路は、第1トランジスタと、第2トランジスタと、第1インバータ回路と、を有し、第1トランジスタは、第1ゲートと、第2ゲートと、を有し、第2トランジスタは、第3ゲートと、第4ゲートと、を有し、切り替え回路は、第3入力端子を有し、第1トランジスタの第1ゲートは、第3入力端子に電気的に接続され、第2トランジスタの第3ゲートは、第1インバータ回路の出力端子に電気的に接続され、第1インバータ回路の入力端子は、第3入力端子に電気的に接続され、第1入力端子は、第2回路の入力端子に電気的に接続され、第2回路は、第2回路の入力端子に入力された信号を補正して、第2回路の出力端子に補正された信号を出力する機能を有し、第3回路は、第3回路の入力端子に入力された信号を補正して、第3回路の出力端子に補正された信号を出力する機能を有し、切り替え回路は、第3入力端子に入力された信号に応じて、第2回路の出力端子と、第1出力端子又は第2出力端子の一方と、の間を導通状態にし、かつ第3回路の出力端子と、第1出力端子又は第2出力端子の他方と、の間を導通状態にする機能と、第1トランジスタの第2ゲートの電位に応じて、第2回路の出力端子から出力された信号が、第1出力端子に入力されるまでの時間を変動させる機能と、第2トランジスタの第4ゲートの電位に応じて、第3回路の出力端子から出力された信号が、第1出力端子に入力されるまでの時間を変動させる機能と、を有する、半導体装置である。

10

20

#### 【0014】

(4)

30

また、本発明の一態様は、上記(2)又は(3)の構成において、切り替え回路は、第1保持部を有し、第1保持部は、第1トランジスタの第2ゲートの電位、及び第2トランジスタの第4ゲートの電位を保持する機能を有する、半導体装置である。

#### 【0015】

(5)

また、本発明の一態様は、上記(2)又は(3)の構成において、切り替え回路は、第1保持部と、第2保持部と、を有し、第1保持部は、第1トランジスタの第2ゲートの電位を保持する機能を有し、第2保持部は、第2トランジスタの第4ゲートの電位を保持する機能を有する、半導体装置である。

#### 【0016】

40

(6)

また、本発明の一態様は、上記(2)又は(3)の構成において、切り替え回路は、第1保持部と、第2保持部と、第1スイッチと、第2スイッチと、を有し、第1保持部は、第1スイッチを介して、第1トランジスタの第2ゲートと、第2トランジスタの第4ゲートと、に電気的に接続され、第2保持部は、第2スイッチを介して、第1トランジスタの第2ゲートと、第2トランジスタの第4ゲートと、に電気的に接続され、第1スイッチ、又は第2スイッチの一方をオン状態にし、他方をオフ状態にすることで、第1トランジスタの第2ゲート及び第2トランジスタの第4ゲートと、第1保持部又は第2保持部の一方と、の間を導通状態にする機能を有する、半導体装置である。

#### 【0017】

50

( 7 )

また、本発明の一態様は、上記(1)乃至(6)のいずれか一の構成において、第1回路を複数段、有し、複数の第1回路に含まれている切り替え回路は、第4入力端子を有し、前段の第1回路の第1出力端子は、後段の第1回路の第1入力端子に電気的に接続され、前段の第1回路の第2出力端子は、後段の第1回路の第2入力端子に電気的に接続され、全ての第1回路の第1トランジスタの第2ゲート、及び第2トランジスタの第4ゲートには、それぞれ対応する第1データに応じた電位が保持され、かつ全ての切り替え回路の第3入力端子には、それぞれ対応する第2データに応じた信号が入力されている場合に、一段目の第1回路の第1入力端子と第2入力端子とにそれぞれ入力信号が入力されることによって、最終段の第1回路の第1出力端子と第2出力端子とから出力されるそれぞれの出力信号の時間差は、第1データと第2データの積和に応じた時間となる、半導体装置である。

【 0 0 1 8 】

( 8 )

また、本発明の一態様は、上記(7)の構成において、第4回路を有し、第4回路は、最終段の第1回路の第1出力端子と、第2出力端子と、に電気的に接続され、第4回路は、出力信号の時間差に応じた信号を生成する機能を有する、半導体装置である。

【 0 0 1 9 】

( 9 )

また、本発明の一態様は、上記(1)乃至(8)のいずれか一の構成において、第1トランジスタ、及び／又は第2トランジスタは、チャネル形成領域に金属酸化物を有する、半導体装置である。

【 0 0 2 0 】

( 1 0 )

また、本発明の一態様は、第1回路を有し、第1回路は、第1入力端子と、第2入力端子と、第1出力端子と、第2出力端子と、第1負荷回路と、第2負荷回路と、第2インバータ回路と、第3インバータ回路と、第4インバータ回路と、第5インバータ回路と、切り替え回路と、を有し、第1入力端子は、第2インバータ回路の入力端子に電気的に接続され、第2入力端子は、第3インバータ回路の入力端子に電気的に接続され、第1出力端子は、第4インバータ回路の出力端子に電気的に接続され、第2出力端子は、第5インバータ回路の出力端子に電気的に接続され、第2インバータ回路の出力端子は、第1負荷回路の第1端子に電気的に接続され、第3インバータ回路の出力端子は、第2負荷回路の第1端子に電気的に接続され、切り替え回路は、第3入力端子を有し、第1負荷回路は、第5入力端子を有し、第1負荷回路は、第5入力端子に入力された信号に応じて、第1負荷回路の第1端子と第2端子との間の抵抗値を変動する機能を有し、切り替え回路は、第3入力端子に入力された信号に応じて、第1負荷回路の第2端子と、第4インバータ回路又は第5インバータ回路の一方の入力端子と、の間を導通状態にし、かつ第2負荷回路の第2端子と、第4インバータ回路又は第5インバータ回路の他方の入力端子と、の間を導通状態にする機能を有する、半導体装置である。

【 0 0 2 1 】

( 1 1 )

また、本発明の一態様は、上記(10)の構成において、第2負荷回路は、第6入力端子を有し、第2負荷回路は、第6入力端子に入力された信号に応じて、第2負荷回路の第1端子と第2端子との間の抵抗値を変動する機能を有する、半導体装置である。

【 0 0 2 2 】

( 1 2 )

また、本発明の一態様は、上記(11)又は(12)の構成において、第1負荷回路は、抵抗变化素子、MTJ素子、相変化メモリのいずれか一を有する、半導体装置である。

【 0 0 2 3 】

( 1 3 )

10

20

30

40

50

また、本発明の一態様は、上記(10)又は(11)の構成において、第1負荷回路は、第1負荷素子と、第2負荷素子と、を有し、第1負荷回路は、第7入力端子を有し、第1負荷回路は、第7入力端子に入力された信号に応じて、第1負荷素子又は第2負荷素子の一方を選択して、選ばれた負荷素子を介して、第1負荷回路の第1端子と第2端子との間を導通状態にする機能を有する、半導体装置である。

**【0024】**

(14)

また、本発明の一態様は、上記(10)乃至(13)のいずれか一の構成において、第1回路を複数段、有し、前段の第1回路の第1出力端子は、後段の第1回路の第1入力端子に電気的に接続され、前段の第1回路の第2出力端子は、後段の第1回路の第2入力端子に電気的に接続され、全ての第1回路の第1負荷回路の第5入力端子には、それぞれ対応する第1データに応じた電位が入力され、かつ全ての切り替え回路の第3入力端子には、それぞれ対応する第2データに応じた信号が入力されている場合に、一段目の第1回路の第1入力端子と第2入力端子とにそれぞれ入力信号が入力されることによって、最終段の第1回路の第1出力端子と第2出力端子とから出力されるそれぞれの出力信号の時間差は、第1データと第2データの積和に応じた時間となる、半導体装置である。

10

**【0025】**

(15)

また、本発明の一態様は、上記(14)の構成において、第4回路を有し、第4回路は、最終段の第1回路の第1出力端子と、第2出力端子と、に電気的に接続され、第4回路は、出力信号の時間差に応じた信号を生成する機能を有する、半導体装置である。

20

**【0026】**

(16)

また、本発明の一態様は、上記(1)乃至(15)のいずれか一の半導体装置と、筐体と、を有し、半導体装置によってニューラルネットワークの演算を行う、電子機器である。

**【0027】**

なお、本明細書等において、半導体装置とは、半導体特性を利用した装置であり、半導体素子(トランジスタ、ダイオード、フォトダイオード等)を含む回路、同回路を有する装置等をいう。また、半導体特性を利用して機能を実現する装置全般をいう。例えば、集積回路、集積回路を備えたチップや、パッケージにチップを収納した電子部品は半導体装置の一例である。また、記憶装置、表示装置、発光装置、照明装置及び電子機器等は、それ自体が半導体装置であり、半導体装置を有している場合がある。

30

**【0028】**

また、本明細書等において、XとYとが接続されていると記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図又は文章に示された接続関係に限定されず、図又は文章に示された接続関係以外のものも、図又は文章に開示されているものとする。X、Yは、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層など)であるとする。

**【0029】**

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など)が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態(オン状態)、又は、非導通状態(オフ状態)になり、電流を流すか流さないかを制御する機能を有している。

40

**【0030】**

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路(例えば、論理回路(インバータ、NAND回路、NOR回路など)、信号変換回路(DA変換回路、AD変換回路、ガンマ補正回路など)、電位レベル変換回路(

50

電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅又は電流量などを大きく出来る回路、オペアンプ、差動増幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。

#### 【0031】

なお、XとYとが電気的に接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟まずに接続されている場合）とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

10

#### 【0032】

また、例えば、「XとYとトランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。又は、「トランジスタのソース（又は第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）はYと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。又は、「Xは、トランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とを介して、Yと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース（又は第1の端子など）と、ドレイン（又は第2の端子など）とを、区別して、技術的範囲を決定することができる。なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

20

#### 【0033】

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、及び電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

30

#### 【0034】

また、本明細書等において、トランジスタは、ゲート、ソース、及びドレインと呼ばれる3つの端子を有する。ゲートは、トランジスタの導通状態を制御する制御端子である。ソース又はドレインとして機能する2つの端子は、トランジスタの入出力端子である。2つの入出力端子は、トランジスタの導電型（nチャネル型、pチャネル型）及びトランジスタの3つの端子に与えられる電位の高低によって、一方がソースとなり他方がドレインとなる。このため、本明細書等においては、ソースやドレインの用語は、言い換えることができるものとする。また、本明細書等では、トランジスタの接続関係を説明する際、「ソース又はドレインの一方」（又は第1電極、又は第1端子）、「ソース又はドレインの他方」（又は第2電極、又は第2端子）と表記を用いる。なお、トランジスタの構造によつては、上述した3つの端子に加えて、バックゲートを有する場合がある。

40

#### 【0035】

50

また、本明細書等において、ノードは、回路構成やデバイス構造等に応じて、端子、配線、電極、導電層、導電体、不純物領域等と言い換えることが可能である。また、端子、配線等をノードと言い換えることが可能である。

#### 【0036】

また、本明細書等において、「電圧」と「電位」は、適宜言い換えることができる。「電圧」は、基準となる電位からの電位差のことであり、例えば基準となる電位をグラウンド電位（接地電位）とすると、「電圧」を「電位」に言い換えることができる。グラウンド電位は必ずしも0Vを意味するとは限らない。また、電位は相対的なものであり、基準となる電位が変わることによって、配線に与えられる電位、回路などに印加される電位、回路などから出力される電位なども変化する。

10

#### 【0037】

「電流」とは、電荷の移動現象（電気伝導）のことであり、例えば、「正の荷電体の電気伝導が起きている」という記載は、「その逆向きに負の荷電体の電気伝導が起きている」と換言することができる。そのため、本明細書等において、「電流」とは、特に断らない限り、キャリアの移動に伴う電荷の移動現象（電気伝導）をいうものとする。ここでいうキャリアとは、電子、正孔、アニオン、カチオン、錯イオン等が挙げられ、電流の流れる系（例えば、半導体、金属、電解液、真空中など）によってキャリアが異なる。また、配線等における「電流の向き」は、正のキャリアが移動する方向とし、正の電流量で記載する。換言すると、負のキャリアが移動する方向は、電流の向きと逆の方向となり、負の電流量で表現される。そのため、本明細書等において、電流の正負（又は電流の向き）について断りがない場合、「素子Aから素子Bに電流が流れる」等の記載は「素子Bから素子Aに電流が流れる」等に言い換えることができるものとする。また、「素子Aに電流が入力される」等の記載は「素子Aから電流が出力される」等に言い換えることができるものとする。

20

#### 【0038】

また、本明細書等において、「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものである。従って、構成要素の数を限定するものではない。また、構成要素の順序を限定するものではない。例えば、本明細書等の実施の形態の一において「第1」に言及された構成要素が、他の実施の形態、あるいは特許請求の範囲において「第2」に言及された構成要素とすることもありうる。また例えば、本明細書等の実施の形態の一において「第1」に言及された構成要素を、他の実施の形態、あるいは特許請求の範囲において省略することもありうる。

30

#### 【0039】

また、本明細書等において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている場合がある。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書等で説明した語句に限定されず、状況に応じて適切に言い換えることができる。例えば、「導電体の上面に位置する絶縁体」の表現では、示している図面の向きを180度回転することによって、「導電体の下面に位置する絶縁体」と言い換えることができる。

#### 【0040】

また、「上」や「下」の用語は、構成要素の位置関係が直上又は直下で、かつ、直接接していることを限定するものではない。例えば、「絶縁層A上の電極B」の表現であれば、絶縁層Aの上に電極Bが直接接して形成されている必要はなく、絶縁層Aと電極Bとの間に他の構成要素を含むものを除外しない。

40

#### 【0041】

また、本明細書等において、「膜」、「層」などの語句は、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。又は、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。又は、場合によっては、又は、状況に応じて、「膜」、「層」などの語句を使わずに、別の用語に入れ替えることが可能である。例

50

えば、「導電層」又は「導電膜」という用語を、「導電体」という用語に変更することが可能な場合がある。又は、例えば、「絶縁層」「絶縁膜」という用語を、「絶縁体」という用語に変更することが可能な場合がある。

#### 【0042】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

#### 【0043】

また、本明細書等において、「配線」、「信号線」、「電源線」などの用語は、場合によっては、又は、状況に応じて、互いに入れ替えることが可能である。例えば、「配線」という用語を、「信号線」という用語に変更することが可能な場合がある。また、例えば、「配線」という用語を、「電源線」などの用語に変更することが可能な場合がある。また、その逆も同様で、「信号線」「電源線」などの用語を、「配線」という用語に変更することが可能な場合がある。「電源線」などの用語は、「信号線」などの用語に変更することが可能な場合がある。また、その逆も同様で「信号線」などの用語は、「電源線」などの用語に変更することが可能な場合がある。また、配線に印加されている「電位」という用語を、場合によっては、又は、状況に応じて、「信号」などという用語に変更することが可能な場合がある。また、その逆も同様で、「信号」などの用語は、「電位」という用語に変更することが可能な場合がある。

10

#### 【0044】

本明細書等において、半導体の不純物とは、例えば、半導体層を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物である。不純物が含まれることにより、例えば、半導体にDOS(Density of States)が形成されることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、主成分以外の遷移金属などがあり、特に、例えば、水素(水にも含まれる)、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコン層である場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

20

#### 【0045】

本明細書等において、スイッチとは、導通状態(オン状態)、又は、非導通状態(オフ状態)になり、電流を流すか流さないかを制御する機能を有するものをいう。又は、スイッチとは、電流を流す経路を選択して切り替える機能を有するものをいう。一例としては、電気的なスイッチ、機械的なスイッチなどを用いることができる。つまり、スイッチは、電流を制御できるものであればよく、特定のものに限定されない。

30

#### 【0046】

電気的なスイッチの一例としては、トランジスタ(例えば、バイポーラトランジスタ、MOSトランジスタなど)、ダイオード(例えば、PNダイオード、PINダイオード、ショットキーダイオード、MIM(Metal Insulator Metal)ダイオード、MIS(Metal Insulator Semiconductor)ダイオード、ダイオード接続のトランジスタなど)、又はこれらを組み合わせた論理回路などがある。なお、スイッチとしてトランジスタを用いる場合、トランジスタの「導通状態」とは、トランジスタのソース電極とドレイン電極が電気的に短絡されているとみなせる状態をいう。また、トランジスタの「非導通状態」とは、トランジスタのソース電極とドレイン電極が電気的に遮断されているとみなせる状態をいう。なおトランジスタを単なるスイッチとして動作させる場合には、トランジスタの極性(導電型)は特に限定されない。

40

#### 【0047】

50

機械的なスイッチの一例としては、MEMS（マイクロ・エレクトロ・メカニカル・システム）技術を用いたスイッチがある。そのスイッチは、機械的に動かすことが可能な電極を有し、その電極が動くことによって、導通と非導通とを制御して動作する。

**【発明の効果】**

**【0048】**

本発明の一態様によって、階層型の人工ニューラルネットワークが構築された半導体装置などを提供することができる。又は、本発明の一態様によって、消費電力が低い半導体装置などを提供することができる。又は、本発明の一態様によって、環境の温度の影響を受けにくい半導体装置などを提供することができる。又は、本発明の一態様によって、新規な半導体装置などを提供することができる。

10

**【0049】**

なお本発明の一態様の効果は、上記列挙した効果に限定されない。上記列挙した効果は、他の効果の存在を妨げるものではない。なお他の効果は、以下の記載で述べる、本項目で言及していない効果である。本項目で言及していない効果は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一態様は、上記列挙した効果、及び他の効果のうち、少なくとも一つの効果を有するものである。従って本発明の一態様は、場合によっては、上記列挙した効果を有さない場合もある。

**【図面の簡単な説明】**

**【0050】**

20

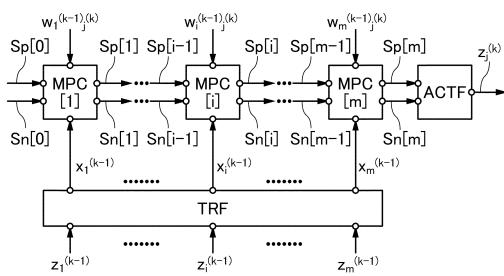

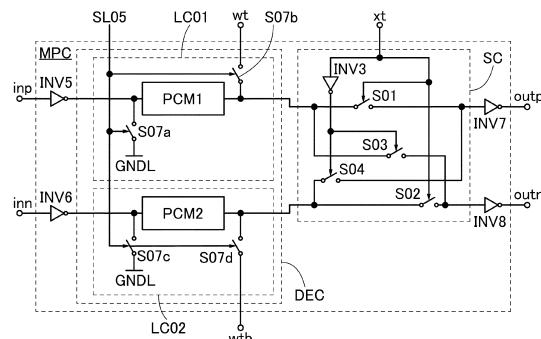

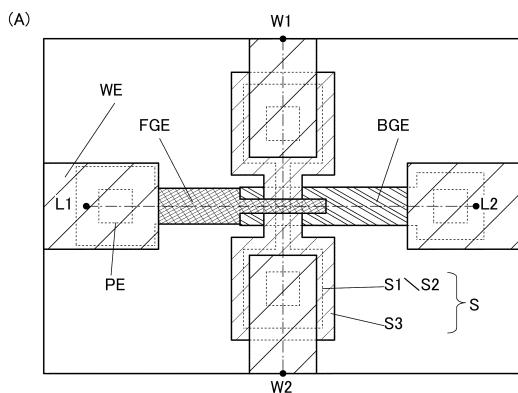

【図1】半導体装置の構成例を示すブロック図。

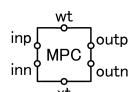

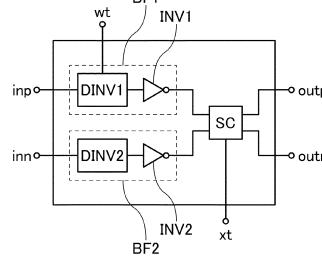

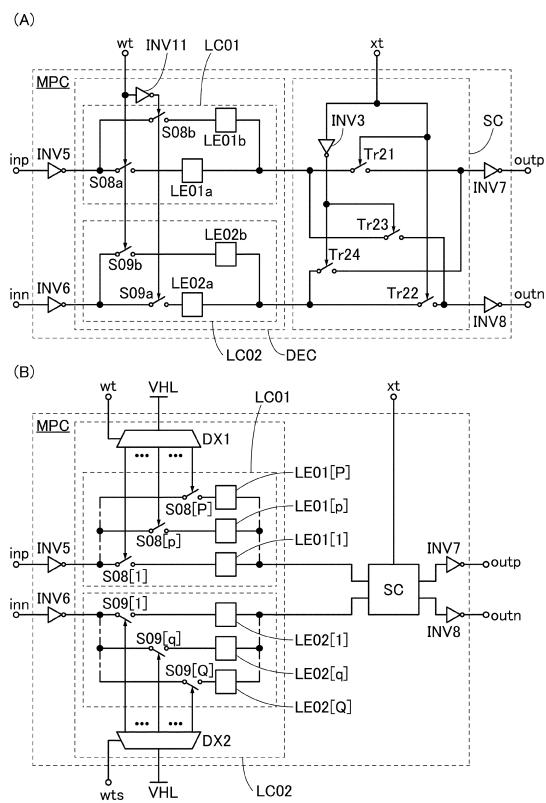

【図2】半導体装置が有する回路の構成例を示すブロック図、及び回路図。

【図3】半導体装置が有する回路の構成例を示す回路図。

【図4】階層型のニューラルネットワークを説明する図。

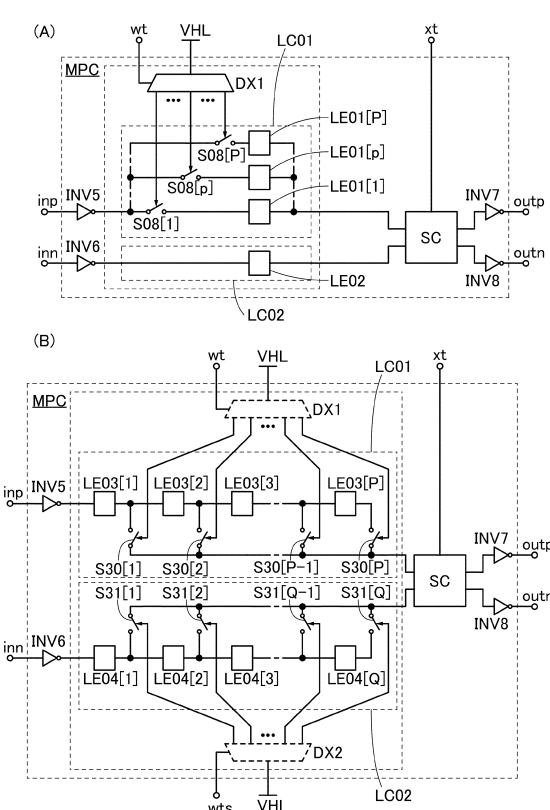

【図5】半導体装置が有する回路の構成例を示すブロック図。

【図6】半導体装置が有する回路の構成例を示す回路図。

【図7】半導体装置が有する回路の動作例を示すタイミングチャート。

【図8】半導体装置が有する回路の構成例を示す回路図。

【図9】半導体装置の構成例を示すブロック図。

【図10】半導体装置が有する回路の構成例を示す回路図。

30

【図11】半導体装置の構成例を示すブロック図。

【図12】半導体装置が有する回路の構成例を示すブロック図。

【図13】半導体装置が有する回路の構成例を示す回路図。

【図14】半導体装置が有する回路の構成例を示す回路図。

【図15】半導体装置が有する回路の構成例を示す回路図。

【図16】半導体装置が有する回路の構成例を示す回路図。

【図17】半導体装置が有する回路の構成例を示す回路図。

【図18】半導体装置が有する回路の構成例を示す回路図。

【図19】半導体装置が有する回路の構成例を示すブロック図。

【図20】半導体装置が有する回路の構成例を示すブロック図。

40

【図21】半導体装置が有する回路の構成例を示す回路図。

【図22】半導体装置が有する回路の構成例を示す回路図。

【図23】半導体装置が有する回路の構成例を示す回路図。

【図24】半導体装置が有する回路の構成例を示すブロック図。

【図25】半導体装置が有する回路の構成例を示すブロック図。

【図26】半導体装置が有する回路の構成例を示すブロック図。

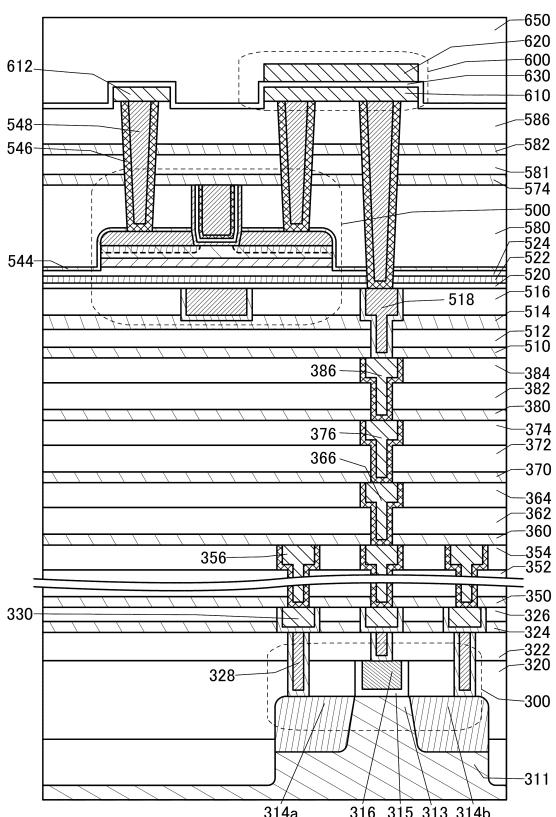

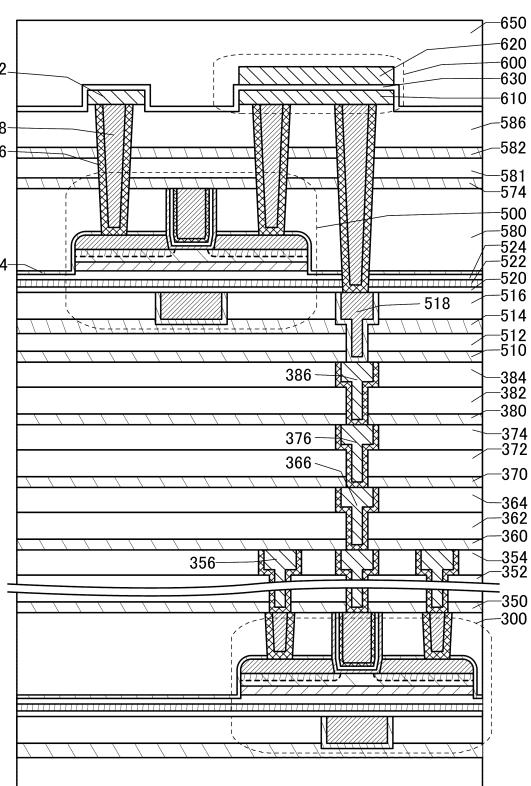

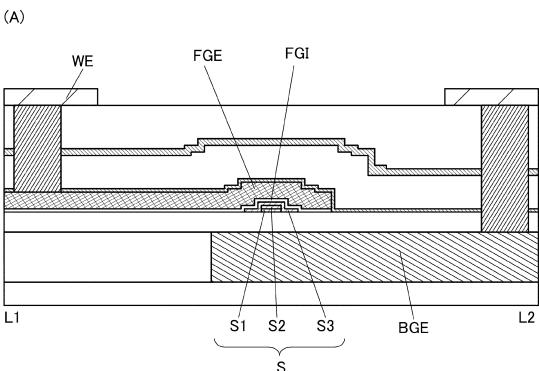

【図27】半導体装置の構成例を示す断面図。

【図28】半導体装置の構成例を示す断面図。

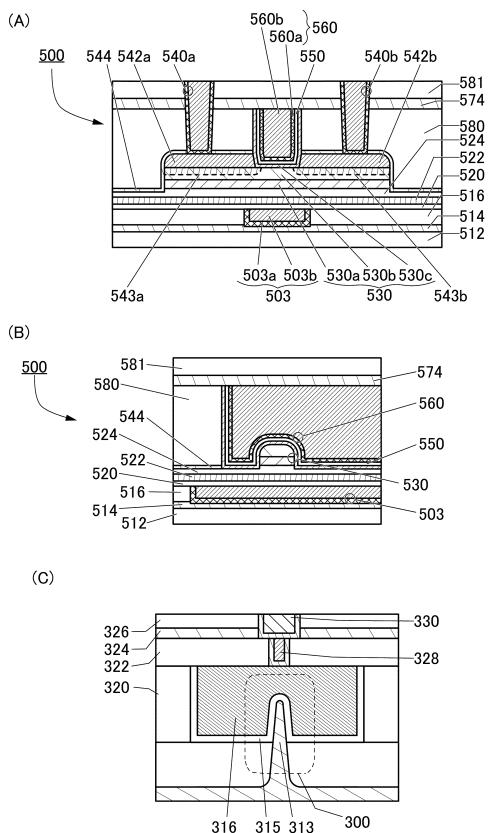

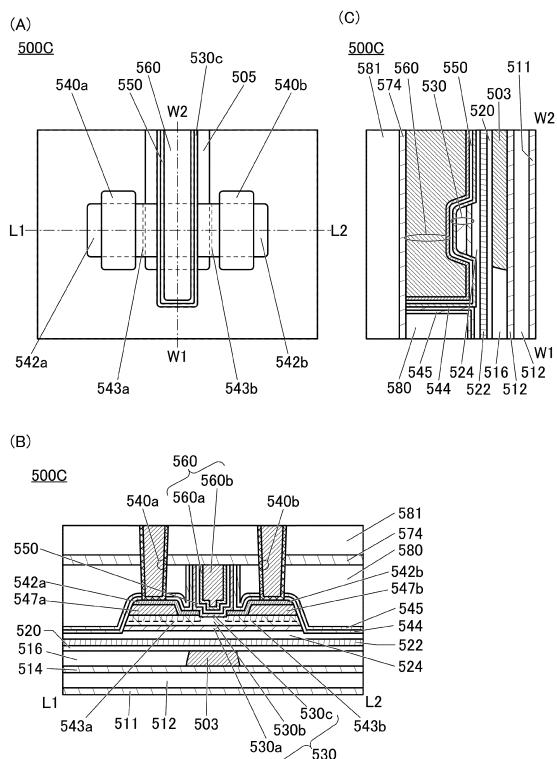

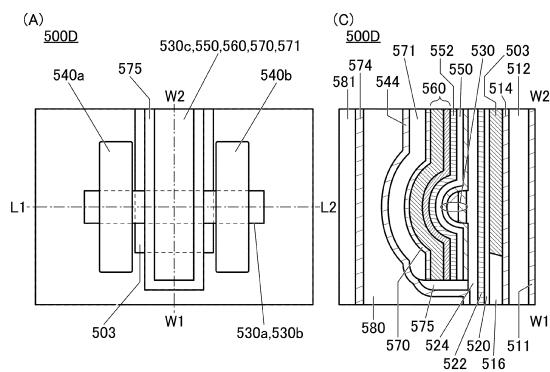

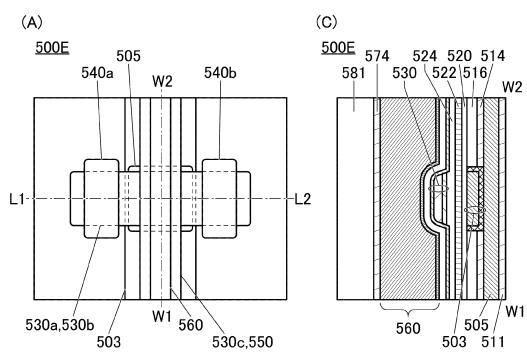

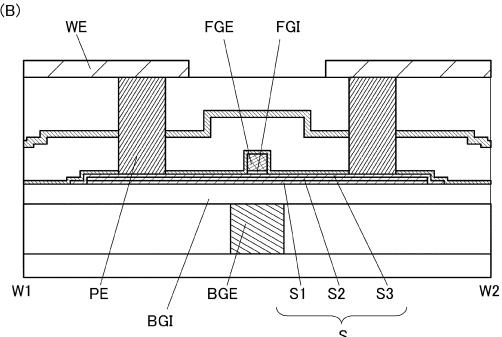

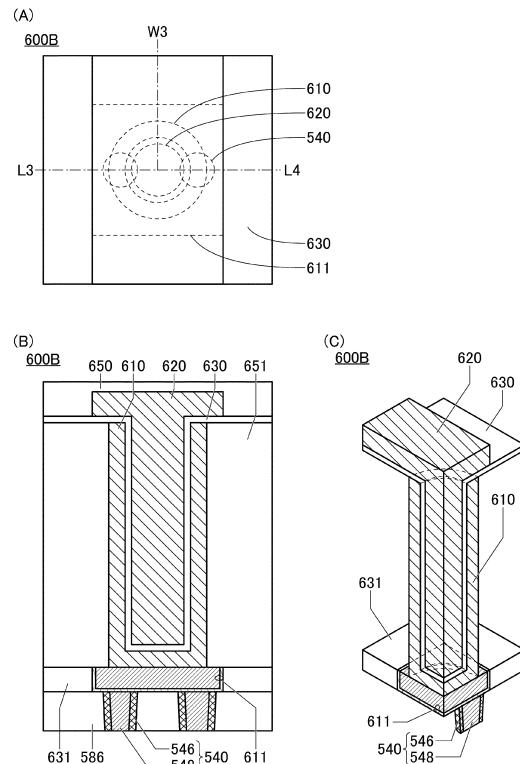

【図29】トランジスタの構造例を示す上面図、及び断面図。

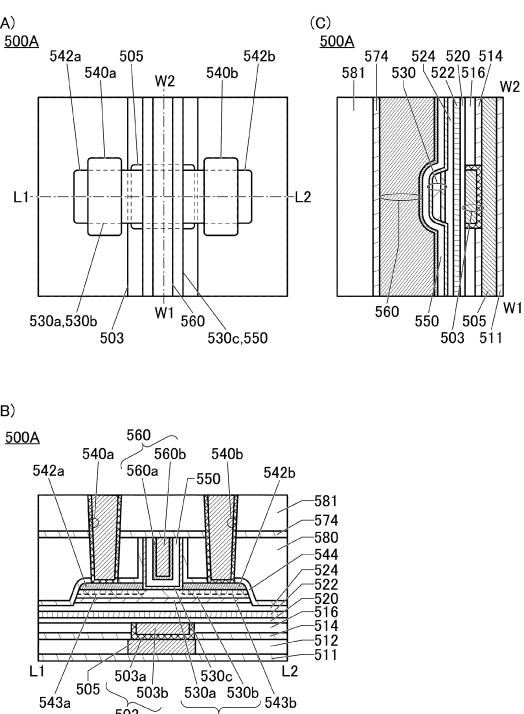

【図30】トランジスタの構造例を示す上面図、及び断面図。

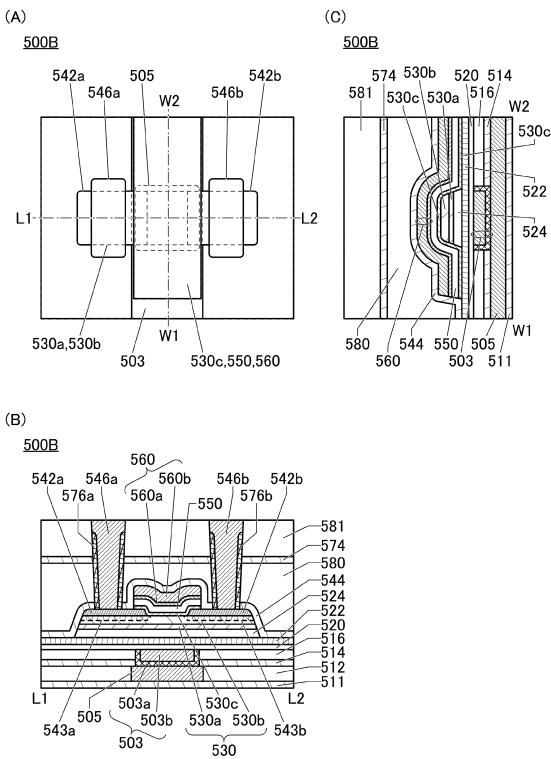

50

- 【図31】トランジスタの構造例を示す上面図、及び断面図。

- 【図32】トランジスタの構造例を示す上面図、及び断面図。

- 【図33】トランジスタの構造例を示す上面図、及び断面図。

- 【図34】トランジスタの構造例を示す上面図、及び断面図。

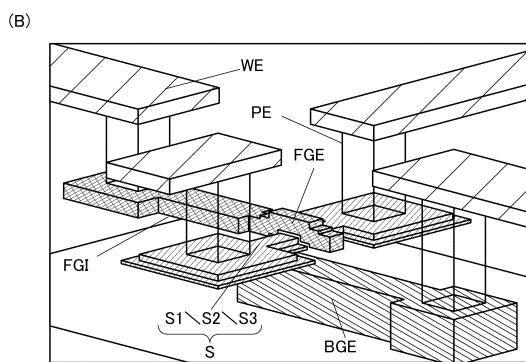

- 【図35】トランジスタの構造例を示す上面図、及び斜視図。

- 【図36】トランジスタの構造例を示す断面図。

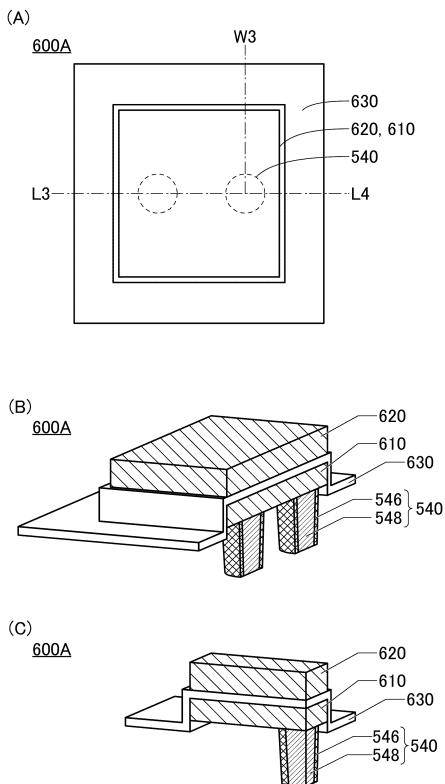

- 【図37】容量素子の構造例を示す上面図、及び斜視図。

- 【図38】容量素子の構造例を示す上面図、及び斜視図。

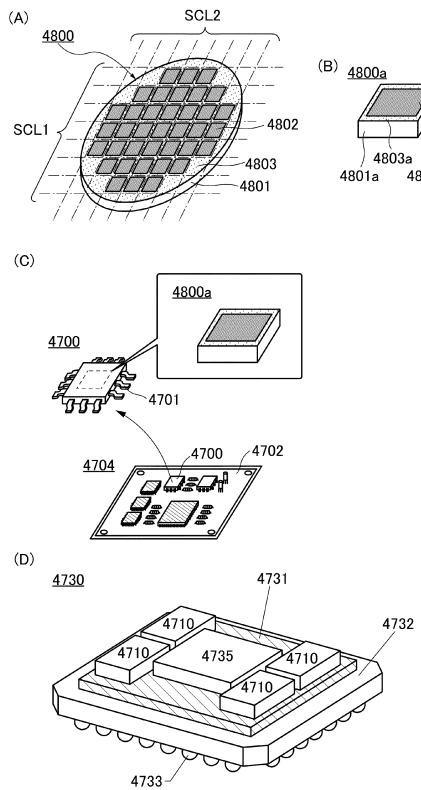

- 【図39】半導体ウェハと電子部品の一例を示す斜視図。

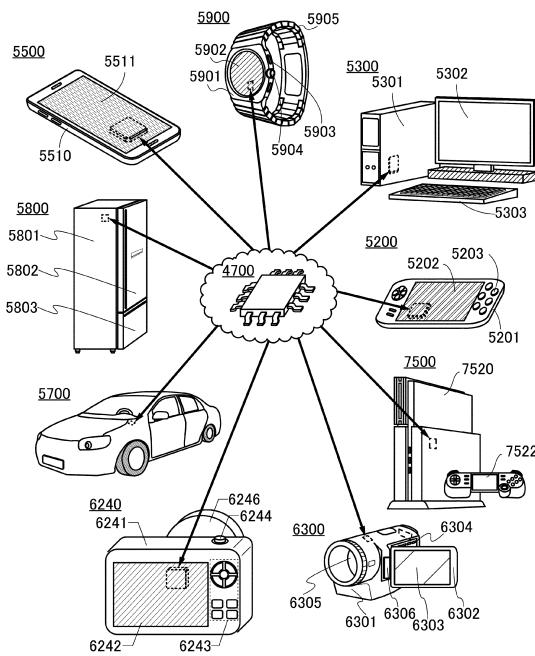

- 【図40】電子機器の一例を示す斜視図。

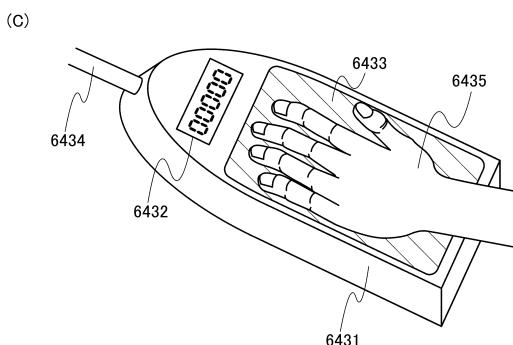

- 【図41】電子機器の一例を示す斜視図。

10

**【発明を実施するための形態】**

**【0051】**

人工ニューラルネットワーク（以後、ニューラルネットワークと呼称する。）において、シナプスの結合強度は、ニューラルネットワークに既存の情報を与えることによって、変化することができる。このように、ニューラルネットワークに既存の情報を与えて、結合強度を決める処理を「学習」と呼ぶ場合がある。

**【0052】**

また、「学習」を行った（結合強度を定めた）ニューラルネットワークに対して、何らかの情報を与えることにより、その結合強度に基づいて新たな情報を出力することができる。このように、ニューラルネットワークにおいて、与えられた情報と結合強度に基づいて新たな情報を出力する処理を「推論」又は「認知」と呼ぶ場合がある。

20

**【0053】**

ニューラルネットワークのモデルとしては、例えば、ホップフィールド型、階層型などが挙げられる。特に、多層構造としたニューラルネットワークを「ディープニューラルネットワーク」（DNN）と呼称し、ディープニューラルネットワークによる機械学習を「ディープラーニング」と呼称する場合がある。

**【0054】**

本明細書等において、金属酸化物（metal oxide）とは、広い意味での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体（透明酸化物導電体を含む）、酸化物半導体（oxide Semiconductor又は単にOSともいう）などに分類される。例えば、トランジスタの活性層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、金属酸化物が增幅作用、整流作用、及びスイッチング作用の少なくとも1つを有するトランジスタのチャネル形成領域を構成し得る場合、当該金属酸化物を、金属酸化物半導体（metal oxide semiconductor）と呼ぶことができる。また、OS FET、又はOSトランジスタと記載する場合においては、金属酸化物又は酸化物半導体を有するトランジスタと換言することができる。

30

**【0055】**

また、本明細書等において、窒素を有する金属酸化物も金属酸化物（metal oxide）と総称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物（metal oxy nitride）と呼称してもよい。

40

**【0056】**

また、本明細書等において、各実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて、本発明の一態様とすることができる。また、1つの実施の形態の中に、複数の構成例が示される場合は、互いに構成例を適宜組み合わせることが可能である。

**【0057】**

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）と、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）との少なくとも一つの内容に対して、適用、組み合わ

50

せ、又は置き換えなどを行うことができる。

**【 0 0 5 8 】**

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。

**【 0 0 5 9 】**

なお、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）と、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）との少なくとも一つの図に対して、組み合わせることにより、さらに多くの図を構成させることができる。

**【 0 0 6 0 】**

本明細書に記載の実施の形態について図面を参照しながら説明している。但し、実施の形態は多くの異なる様で実施することが可能であり、趣旨及びその範囲から逸脱することなく、その形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態の発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。また、斜視図などにおいて、図面の明確性を期すために、一部の構成要素の記載を省略している場合がある。

**【 0 0 6 1 】**

本明細書等において、複数の要素に同じ符号を用いる場合、特に、それらを区別する必要があるときには、符号に“\_1”、“[n]”、“[m, n]”等の識別用の符号を付記して記載する場合がある。

**【 0 0 6 2 】**

また、本明細書の図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

**【 0 0 6 3 】**

(実施の形態 1 )

本実施の形態では、本発明の一態様の半導体装置である、ニューラルネットワークの演算を行う演算回路について説明する。

**【 0 0 6 4 】**

<階層型のニューラルネットワーク>

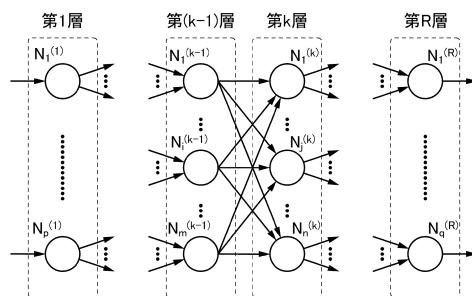

初めに、階層型のニューラルネットワークについて説明する。階層型のニューラルネットワークは、一例としては、一の入力層と、一又は複数の中間層（隠れ層）と、一の出力層と、を有し、合計3以上の層によって構成されている。図4(A)に示す階層型のニューラルネットワーク100はその一例を示しており、ニューラルネットワーク100は、第1層乃至第R層（ここでRは4以上の整数とすることができる。）を有している。特に、第1層は入力層に相当し、第R層は出力層に相当し、それら以外の層は中間層に相当する。なお、図4(A)には、中間層として第(k-1)層、第k層（ここでkは3以上R-1以下の整数とする。）を図示しており、それ以外の中間層については図示を省略している。

**【 0 0 6 5 】**

ニューラルネットワーク100の各層は、一又は複数のニューロンを有する。図4(A)において、第1層はニューロンN<sub>1</sub>(1)乃至ニューロンN<sub>p</sub>(1)（ここでpは1以上の整数である。）を有し、第(k-1)層はニューロンN<sub>1</sub>(k-1)乃至ニューロンN<sub>m</sub>(k-1)（ここでmは1以上の整数である。）を有し、第k層はニューロンN<sub>1</sub>(k)乃至ニューロンN<sub>n</sub>(k)（ここでnは1以上の整数である。）を有し、第R層はニューロンN<sub>1</sub>(R)乃至ニューロンN<sub>q</sub>(R)（ここでqは1以上の整数である。）を有する。

10

20

30

40

50

**【 0 0 6 6 】**

なお、図4(A)には、ニューロン $N_1^{(1)}$ 、ニューロン $N_p^{(1)}$ 、ニューロン $N_1^{(k-1)}$ 、ニューロン $N_m^{(k-1)}$ 、ニューロン $N_1^{(k)}$ 、ニューロン $N_n^{(k)}$ 、ニューロン $N_1^{(R)}$ 、ニューロン $N_q^{(R)}$ に加えて、第 $(k-1)$ 層のニューロン $N_i^{(k-1)}$ (ここでの*i*は1以上m以下の整数である。)、第k層のニューロン $N_j^{(k)}$ (ここでの*j*は1以上n以下の整数である。)も図示しており、それ以外のニューロンについては図示を省略している。

**【 0 0 6 7 】**

次に、前層のニューロンから次層のニューロンへの信号の伝達、及びそれぞれのニューロンにおいて入出力される信号について説明する。なお、本説明では、第k層のニューロン $N_j^{(k)}$ に着目している。10

**【 0 0 6 8 】**

図4(B)は、第k層のニューロン $N_j^{(k)}$ と、ニューロン $N_j^{(k)}$ に入力される信号と、ニューロン $N_j^{(k)}$ から出力される信号と、を示している。

**【 0 0 6 9 】**

具体的には、第 $(k-1)$ 層のニューロン $N_1^{(k-1)}$ 乃至ニューロン $N_m^{(k-1)}$ のそれぞれの出力信号である $z_1^{(k-1)}$ 乃至 $z_m^{(k-1)}$ が、ニューロン $N_j^{(k)}$ に向けて出力されている。そして、ニューロン $N_j^{(k)}$ は、 $z_1^{(k-1)}$ 乃至 $z_m^{(k-1)}$ に応じて $z_j^{(k)}$ を生成して、 $z_j^{(k)}$ を出力信号として第 $(k+1)$ 層(図示しない。)の各ニューロンに向けて出力する。20

**【 0 0 7 0 】**

前層のニューロンから次層のニューロンに入力される信号は、それらのニューロン同士を接続するシナプスの結合強度(以後、重み係数と呼称する。)によって、信号の伝達の度合いが定まる。ニューラルネットワーク100では、前層のニューロンから出力された信号は、対応する重み係数を乗じられて、次層のニューロンに入力される。*i*を1以上m以下の整数として、第 $(k-1)$ 層のニューロン $N_i^{(k-1)}$ と第k層のニューロン $N_j^{(k)}$ との間のシナプスの重み係数を $w_i^{(k-1)} j^{(k)}$ としたとき、第k層のニューロン $N_j^{(k)}$ に入力される信号は、式(1.1)で表すことができる。

**【 0 0 7 1 】****【 数 1 】**

$$w_i^{(k-1)} j^{(k)} \cdot z_i^{(k-1)} \cdots (1.1)$$

30

**【 0 0 7 2 】**

つまり、第 $(k-1)$ 層のニューロン $N_1^{(k-1)}$ 乃至ニューロン $N_m^{(k-1)}$ のそれぞれから第k層のニューロン $N_j^{(k)}$ に信号が伝達するとき、当該信号である $z_1^{(k-1)}$ 乃至 $z_m^{(k-1)}$ には、それぞれの信号に対応する重み係数( $w_1^{(k-1)} j^{(k)}$ 乃至 $w_m^{(k-1)} j^{(k)}$ )が乗じられる。そして、第k層のニューロン $N_j^{(k)}$ には、 $w_1^{(k-1)} j^{(k)} \cdot z_1^{(k-1)}$ 乃至 $w_m^{(k-1)} j^{(k)} \cdot z_m^{(k-1)}$ が入力される。このとき、第k層のニューロン $N_j^{(k)}$ に入力される信号の総和 $u_j^{(k)}$ は、式(1.2)となる。40

**【 0 0 7 3 】****【 数 2 】**

$$u_j^{(k)} = \sum_{i=1}^m w_i^{(k-1)} j^{(k)} \cdot z_i^{(k-1)} \cdots (1.2)$$

**【 0 0 7 4 】**

ニューロン $N_j^{(k)}$ は、 $u_j^{(k)}$ に応じて、出力信号 $z_j^{(k)}$ を生成する。ここで、ニューロン $N_j^{(k)}$ からの出力信号 $z_j^{(k)}$ を次の式で定義する。50

【 0 0 7 5 】

【数3】

$$z_j^{(k)} = f(u_j^{(k)}) \quad \cdots(1.3)$$

【 0 0 7 6 】

関数  $f(u_j^{(k)})$  は、階層型のニューラルネットワークにおける活性化関数であり、ステップ関数、線形ランプ関数、シグモイド関数などを用いることができる。なお、活性化関数は、全てのニューロンにおいて同一でもよいし、又は異なっていてもよい。加えて、ニューロンの活性化関数は、層毎において、同一でもよいし、異なっていてもよい。

10

【 0 0 7 7 】

ところで、各層のニューロンが出力する信号は、アナログ値としてもよいし、2値としてもよい。前者の場合、活性化関数として、線形ランプ関数、シグモイド関数を用いればよい。後者の場合、出力を -1 又は 1 とするステップ関数を用いればよい。

【 0 0 7 8 】

ニューラルネットワーク 100 は、第1層（入力層）に入力信号が入力されることによって、第1層（入力層）から最後の層（出力層）までの各層において順次に、前層から入力された信号を基に、式(1.1)乃至(1.3)を用いて出力信号を生成して、当該出力信号を次層に出力する動作を行う。最後の層（出力層）から出力された信号が、ニューラルネットワーク 100 によって計算された結果に相当する。

20

【 0 0 7 9 】

< 演算回路 >

ここでは、ニューロンの活性化関数を、出力が -1 又は 1 をとるステップ関数としたニューラルネットワーク 100 において、式(1.2)、及び式(1.3)の演算を行うことができる演算回路について説明する。

【 0 0 8 0 】

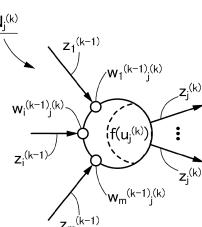

図1(A)に示す演算回路 110 は、回路 MPC[1] 乃至回路 MPC[m] と、回路 ACTF と、変換回路 TRF と、を有する半導体装置である。演算回路 110 は、図4(A)(B)における第 k 層のニューロン  $N_j^{(k)}$  に入力される信号を処理して、ニューロン  $N_j^{(k)}$  から出力される信号  $z_j^{(k)}$  を生成する回路である。なお、本明細書等において、回路 MPC[1] 乃至回路 MPC[m] のそれぞれを区別しない場合は、回路 MPC と記載することとする。

30

【 0 0 8 1 】

<< 回路 MPC >>

図1(B)は、回路 MPC が有する端子を説明する図である。回路 MPC は、一例としては、端子 in p と、端子 in n と、端子 out p と、端子 out n と、端子 wt と、端子 xt と、を有する。

【 0 0 8 2 】

回路 MPC は、端子 in p に入力された信号を端子 out p 又は端子 out n の一方に出力し、端子 in n に入力された信号を端子 out p 又は端子 out n の他方に出力する機能を有する。端子 in p 及び端子 in n に入力された信号の出力先は、一例としては、端子 xt に入力される信号によって定めることができる。

40

【 0 0 8 3 】

また、回路 MPC は、一例としては、信号が端子 in p に入力されてから端子 out p 又は端子 out n の一方から出力するまでにかかる時間を可変する機能を有する。当該時間は、端子 wt に入力される信号によって定めることができる。なお、以後、回路の入力端子に信号が入力されてから、回路の出力端子から信号が出力されるまでにかかる時間を入出力時間と呼称する。

【 0 0 8 4 】

回路 MPC の構成例を図2(A)に示す。図2(A)に示す回路 MPC は、回路 B F 1

50

と、回路 B F 2 と、切り替え回路 S C と、を有する。

【 0 0 8 5 】

回路 B F 1 の入力端子は端子 i n p に電気的に接続され、回路 B F 1 の出力端子は切り替え回路 S C の 2 つの入力端子の一方に電気的に接続されている。回路 B F 2 の入力端子は端子 i n n に電気的に接続され、回路 B F 2 の出力端子は切り替え回路 S C の 2 つの入力端子の他方に電気的に接続されている。切り替え回路 S C の 2 つの出力端子の一方は端子 o u t p に電気的に接続され、切り替え回路 S C の 2 つの出力端子の他方は端子 o u t n に電気的に接続されている。

【 0 0 8 6 】

〔回路 B F 1 〕

10

回路 B F 1 は、回路 B F 1 の入力端子に入力された信号を補正して、回路 B F 1 の出力端子に出力する回路として機能する。回路 B F 1 としては、例えば、インバータ回路を 2 個直列に接続した回路（バッファ回路）などを適用することができる。なお、インバータ回路の数は、2 個に限定されない。ただし、入力と同じ論理値で出力するほうが回路を構成しやすいため、複数個の方が望ましい。インバータ回路の他には、N A N D 回路、N O R 回路などを用いることも出来る。また、回路 B F 1 としては、例えば、論理回路、信号変換回路、電位レベル変換回路などを適用できる場合がある。図 2 ( A ) では、回路 B F 1 は、インバータ回路 D I N V 1 と、インバータ回路 I N V 1 と、を有している構成を示している。

【 0 0 8 7 】

20

インバータ回路 D I N V 1 及びインバータ回路 I N V 1 のそれぞれは、入力された信号の反転信号を出力する機能を有する。特にインバータ回路 D I N V 1 は、端子 w t に電気的に接続されており、端子 w t に入力された信号に応じて、インバータ回路 D I N V 1 の駆動速度を決めることができる。つまり、インバータ回路 D I N V 1 の入出力時間を可変することができる。

【 0 0 8 8 】

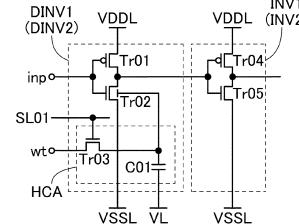

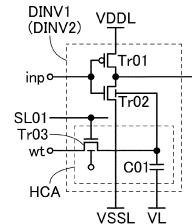

図 2 ( B 1 ) に、回路 B F 1 の具体的な構成例を示す。一例としては、インバータ回路 D I N V 1 は、トランジスタ T r 0 1 乃至トランジスタ T r 0 3 と、容量素子 C 0 1 と、を有し、インバータ回路 I N V 1 は、トランジスタ T r 0 4 、トランジスタ T r 0 5 と、を有する。また、一例としては、トランジスタ T r 0 1 及びトランジスタ T r 0 4 は p チャネル型トランジスタとし、トランジスタ T r 0 2 と、トランジスタ T r 0 3 と、トランジスタ T r 0 5 と、は n チャネル型トランジスタとする。更に、一例としては、トランジスタ T r 0 2 はバックゲートを有する構造のトランジスタとする。同様に、一例としては、トランジスタ T r 0 3 はバックゲートを有する構造のトランジスタとしてもよい。または、一例としては、トランジスタ T r 0 3 は、オフ電流の小さいトランジスタとすることが望ましい。具体例としては、トランジスタ T r 0 3 は、O S トランジスタとすることが望ましい。トランジスタ T r 0 3 以外のトランジスタについても、n チャネル型トランジスタについて、O S トランジスタを採用してもよい。

30

【 0 0 8 9 】

例えば、本明細書等において、トランジスタとして、様々な構造のトランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。トランジスタの一例としては、単結晶シリコンを有するトランジスタ、または、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、ナノクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有するトランジスタなどを用いることが出来る。または、それらの半導体を薄膜化した薄膜トランジスタ（T F T）などを用いることが出来る。T F T を用いる場合、様々なメリットがある。例えば、単結晶シリコンの場合よりも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることが出来る。製造装置を大きくできるため、大型基板上に製造できる。そのため、同時に多くの個数の表示装置を製造できるため、低コストで製造できる。または、製造温度が低いため、耐熱性の弱い基板を用いることができる。そのため、透光性を有する基板上にトラン

40

50

ジスタを製造できる。または、透光性を有する基板上のトランジスタを用いて表示素子での光の透過を制御することが出来る。または、トランジスタの膜厚が薄いため、トランジスタを形成する膜の一部は、光を透過させることが出来る。そのため、開口率が向上させることができる。

#### 【 0 0 9 0 】

なお、トランジスタの一例としては、化合物半導体（例えば、SiGe、GaAsなど）、又は酸化物半導体（例えば、Zn-O、In-Ga-Zn-O、In-Zn-O、In-Sn-O（ITO）、Sn-O、Ti-O、Al-Zn-Sn-O、In-Sn-Zn-Oなど）などを有するトランジスタを用いることが出来る。または、これらの化合物半導体、又は、これらの酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、製造温度を低くできるので、例えば、室温でトランジスタを製造することが可能となる。その結果、耐熱性の低い基板、例えばプラスチック基板又はフィルム基板などに直接トランジスタを形成することが出来る。なお、これらの化合物半導体又は酸化物半導体を、トランジスタのチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、これらの化合物半導体又は酸化物半導体を配線、抵抗素子、画素電極、又は透光性を有する電極などとして用いることができる。それらをトランジスタと同時に成膜又は形成することが可能なため、コストを低減できる。

#### 【 0 0 9 1 】

なお、トランジスタの一例としては、インクジェット法又は印刷法を用いて形成したトランジスタなどを用いることが出来る。これらにより、室温で製造、低真空中で製造、又は大型基板上に製造することができる。よって、マスク（レチカル）を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。または、レジストを用いずに製造することが可能なので、材料費が安くなり、工程数を削減できる。または、必要な部分にのみ膜を付けることが可能なので、全面に成膜した後でエッチングする、という製法よりも、材料が無駄にならず、低コストにできる。

#### 【 0 0 9 2 】

なお、トランジスタの一例としては、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。有機半導体やカーボンナノチューブを有するトランジスタを用いた装置は、衝撃に強くすることができる。

#### 【 0 0 9 3 】

なお、トランジスタとしては、他にも様々な構造のトランジスタを用いることができる。例えば、トランジスタとして、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを用いることが出来る。トランジスタとしてMOS型トランジスタを用いることにより、トランジスタのサイズを小さくすることができる。よって、多数のトランジスタを搭載することができる。トランジスタとしてバイポーラトランジスタを用いることにより、大きな電流を流すことが出来る。よって、高速に回路を動作させることができる。なお、MOS型トランジスタとバイポーラトランジスタとを1つの基板に混在させて形成してもよい。これにより、低消費電力、小型化、高速動作などを実現することができる。

#### 【 0 0 9 4 】

なお、トランジスタの一例としては、チャネルの上下にゲート電極が配置されている構造のトランジスタを適用することができる。チャネルの上下にゲート電極が配置される構造にすることにより、複数のトランジスタが並列に接続されたような回路構成となる。よって、チャネル領域が増えるため、電流値の増加を図ることができる。または、チャネルの上下にゲート電極が配置されている構造にすることにより、空乏層ができやすくなるため、S値の改善を図ることができる。

#### 【 0 0 9 5 】

なお、トランジスタの一例としては、チャネル領域の上にゲート電極が配置されている構造、チャネル領域の下にゲート電極が配置されている構造、正スタガ構造、逆スタガ構

10

20

30

40

50

造、チャネル領域を複数の領域に分けた構造、チャネル領域を並列に接続した構造、又はチャネル領域が直列に接続する構造などのトランジスタを用いることができる。または、トランジスタとして、プレーナ型、F I N型（フィン型）、T R I - G A T E型（トライゲート型）、トップゲート型、ボトムゲート型、ダブルゲート型（チャネルの上下にゲートが配置されている）、など、様々な構成をとることが出来る。

#### 【 0 0 9 6 】

なお、トランジスタの一例としては、チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なっている構造のトランジスタを用いることができる。チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なる構造にすることによって、チャネル領域の一部に電荷が溜まることにより動作が不安定になることを防ぐことができる。

10

#### 【 0 0 9 7 】

なお、トランジスタの一例としては、L D D領域を設けた構造を適用できる。L D D領域を設けることにより、オフ電流の低減、又はトランジスタの耐圧向上（信頼性の向上）を図ることができる。または、L D D領域を設けることにより、飽和領域で動作する時に、ドレインとソースとの間の電圧が変化しても、ドレイン電流があまり変化せず、傾きがフラットな電圧・電流特性を得ることができる。

#### 【 0 0 9 8 】

例えば、本明細書等において、様々な基板を用いて、トランジスタを形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板又はシリコン基板）、S O I基板、ガラス基板、石英基板、プラスチック基板、サファイアガラス基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、繊維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板、貼り合わせフィルム、基材フィルムなどの一例としては、以下のものがあげられる。例えば、ポリエチレンテレフタレート（P E T）、ポリエチレンナフタレート（P E N）、ポリエーテルサルファン（P E S）、ポリテトラフルオロエチレン（P T F E）に代表されるプラスチックがある。または、一例としては、アクリル等の合成樹脂などがある。または、一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。または、一例としては、ポリアミド、ポリイミド、アラミド、エポキシ、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はS O I基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。

20

#### 【 0 0 9 9 】

また、基板として、可撓性基板を用い、可撓性基板上に直接、トランジスタを形成してもよい。または、基板とトランジスタの間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板より分離し、他の基板に転載するためには用いることができる。その際、トランジスタは耐熱性の劣る基板や可撓性の基板にも転載できる。なお、上述の剥離層には、例えば、タングステン膜と酸化シリコン膜との無機膜の積層構造の構成や、基板上にポリイミド等の有機樹脂膜が形成された構成等を用いることができる。

30

#### 【 0 1 0 0 】

つまり、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、アラミドフィルム基板、ポリイミドフィルム基板、石材基板、木材基板、布基板（天然繊維（絹、綿、麻）、合成繊維（ナイロン、ポリウレタン、ポリエステル）若しくは再生繊維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、

40

50

皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

#### 【0101】

なお、所定の機能を実現させるために必要な回路の全てを、同一の基板（例えば、ガラス基板、プラスチック基板、単結晶基板、又はS O I 基板など）に形成することが可能である。こうして、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図ることができる。

#### 【0102】

なお、所定の機能を実現させるために必要な回路の全てを同じ基板に形成しないことが可能である。つまり、所定の機能を実現させるために必要な回路の一部は、ある基板に形成され、所定の機能を実現させるために必要な回路の別の一部は、別の基板に形成されていることが可能である。例えば、所定の機能を実現させるために必要な回路の一部は、ガラス基板に形成され、所定の機能を実現させるために必要な回路の別の一部は、単結晶基板（又はS O I 基板）に形成されることが可能である。そして、所定の機能を実現させるために必要な回路の別の一部が形成される単結晶基板（I C チップともいう）を、C O G（C h i p O n G l a s s）によって、ガラス基板に接続して、ガラス基板にそのI C チップを配置することが可能である。または、I C チップを、T A B（T a p e A u t o m a t e d B o n d i n g）、C O F（C h i p O n F i l m）、S M T（S u r f a c e M o u n t T e c h n o l o g y）、又はプリント基板などを用いてガラス基板と接続することが可能である。このように、回路の一部が画素部と同じ基板に形成されていることにより、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図ることができる。特に、駆動電圧が大きい部分の回路、又は駆動周波数が高い部分の回路などは、消費電力が大きくなってしまう場合が多い。そこで、このような回路を、画素部とは別の基板（例えば単結晶基板）に形成して、I C チップを構成する。このI C チップを用いることによって、消費電力の増加を防ぐことができる。

#### 【0103】

インバータ回路D I N V 1において、トランジスタT r 0 1のゲートとトランジスタT r 0 2のゲートは端子i n pに電気的に接続され、トランジスタT r 0 1の第1端子は配線V D D Lに電気的に接続され、トランジスタT r 0 1の第2端子は、トランジスタT r 0 2の第1端子に電気的に接続されている。トランジスタT r 0 2の第2端子は、配線V S S Lに電気的に接続され、トランジスタT r 0 2のバックゲートは、トランジスタT r 0 3の第1端子と、容量素子C 0 1の第1端子と、に電気的に接続されている。トランジスタT r 0 3の第2端子は、端子w tに電気的に接続され、トランジスタT r 0 3のゲートは、配線S L 0 1に電気的に接続されている。容量素子C 0 1の第2端子は、配線V Lに電気的に接続されている。また、トランジスタT r 0 1の第2端子と、トランジスタT r 0 2の第1端子は、インバータ回路I N V 1の入力端子に電気的に接続されている。

#### 【0104】

インバータ回路I N V 1において、トランジスタT r 0 4のゲートとトランジスタT r 0 5のゲートは、インバータ回路I N V 1の入力端子に電気的に接続され、トランジスタT r 0 4の第1端子は、配線V D D Lに電気的に接続され、トランジスタT r 0 4の第2端子は、トランジスタT r 0 5の第1端子に電気的に接続されている。トランジスタT r 0 5の第2端子は、配線V S S Lに電気的に接続されている。また、トランジスタT r 0 4の第2端子とトランジスタT r 0 5の第1端子は、インバータ回路I N V 1の出力端子に電気的に接続されている。

#### 【0105】

配線V D D Lは、高レベル電位である電圧V D D を供給する電圧線として機能し、配線V S S Lは、低レベル電位である電圧V S S を供給する電圧線として機能する。なお、配線V S S Lには、マイナスの電位が供給されてもよいし、プラスの電位が供給されてもよいし、0 V (G N D) の電位が供給されてもよい。また、配線V Lは、定電圧を供給する

10

20

30

40

50

電圧線として機能し、当該定電圧としては、VDD、VSS、又は接地電位などとすることができる。

#### 【0106】

インバータ回路DINV1において、トランジスタTr03と、容量素子C01とは、保持部HCAに含まれている。保持部HCAは、端子wtから入力された信号に応じた電位を保持する機能を有する。

#### 【0107】

保持部HCAに含まれるトランジスタTr03はスイッチング素子として機能し、配線SL01からトランジスタTr03のゲートに電位を印加することによって、トランジスタTr03をオン状態又はオフ状態にすることができる。

10

#### 【0108】

配線SL01に高レベル電位を与えて、トランジスタTr03をオン状態にすることによって、端子wtと容量素子C01の第1端子との間を導通状態にすることができる。このとき、回路MPCは端子wtから信号を受信することで、当該信号に応じた電位を容量素子C01の第1端子に書き込むことができる。そして、当該電位を容量素子C01の第1端子に書き込んだ後に、配線SL01に低レベル電位を与えて、トランジスタTr03をオフ状態にすることによって、保持部HCAに当該電位を保持することができる。

#### 【0109】

保持部HCAにおいて、容量素子C01の第1端子に書き込んだ電位を長時間保持したい場合、トランジスタTr03は、OSトランジスタであることが好ましい。加えて、トランジスタTr03のチャネル形成領域は、インジウム、元素M（元素Mとしては、アルミニウム、ガリウム、イットリウム、スズなどが挙げられる。）、亜鉛の少なくとも一を含む酸化物であることがより好ましい。トランジスタTr03は、特に実施の形態4に記載するトランジスタの構造であることが更に好ましい。

20

#### 【0110】

OSトランジスタは、チャネル形成領域として機能する金属酸化物のバンドギャップが大きいため、オフ電流が極めて小さいという特性を有する。このため、トランジスタTr03として、OSトランジスタを用いることにより、トランジスタTr03がオフ状態における、容量素子C01の第1端子から端子wtへのリーク電流を非常に小さくすることができる。つまり、容量素子C01の第1端子の電位のリフレッシュ動作を少なくすることができるため、容量素子C01の第1端子の電位を保持するのに必要な消費電力を低減することができる。

30

#### 【0111】

ところで、トランジスタTr02はバックゲートを有しているため、当該バックゲートに電位を与えることによって、トランジスタTr02のしきい値電圧を当該電位に応じて変動することができる。回路MPCでは、トランジスタTr02のバックゲートは、容量素子C01の第1端子に接続されているため、トランジスタTr02のしきい値電圧は、容量素子C01の第1端子の電位に応じて決まる。

#### 【0112】

例えば、容量素子C01の第1端子の電位が高レベル電位である場合、トランジスタTr02のしきい値電圧は、マイナス側に変動するため、トランジスタTr02のソース-ドレイン間に流れる電流量は大きくなる。これにより、インバータ回路DINV1の入力端子に信号が入力されてから、出力端子から信号が出力するまでにかかる入出力時間が短くなる。

40

#### 【0113】

また、例えば、容量素子C01の第1端子の電位が低レベル電位である場合、トランジスタTr02のしきい値電圧は、プラス側に変動するため、トランジスタTr02のソース-ドレイン間に流れる電流量は小さくなる。これにより、インバータ回路DINV1の入力端子に信号が入力されてから、出力端子から信号が出力するまでにかかる入出力時間が長くなる。

50

**【0114】**

具体的には、トランジスタTr02を、トランジスタTr02のゲートに印加する電位の範囲を-0.8V以上2.5V以下として動作させる場合、トランジスタTr02のバックゲートには、例えば、高レベル電位として1.5V以上の電位を与えればよく、低レベル電位として1.5V未満の電位を与えればよい。

**【0115】**

また、トランジスタTr03も、バックゲートを有してもよい。図2(B2)では、図2(B1)のインバータ回路DINV1において、トランジスタTr03がバックゲートを有する場合の回路構成を示している。なお、トランジスタTr03のバックゲートの電気的な接続先としては、例えば、トランジスタTr03のゲートとすることができる。トランジスタTr03のゲートとバックゲートを電気的に接続することによって、トランジスタTr03のオン状態のときに流れる電流を大きくすることができます。また、例えば、トランジスタTr03のバックゲートに、外部回路と電気的に接続するための配線を設けて、当該外部回路によってトランジスタTr03のバックゲートに電位を与えて、しきい値電圧を上げてもよい。このような構成にすることにより、外部回路によってトランジスタTr03のオフ電流を小さくすることができる。

10

**【0116】****[回路BF2]**

図2(A)では、回路BF2は、インバータ回路DINV2と、インバータ回路INV2と、を有している構成を示している。回路BF2は、回路BF1と同様に、回路BF2の入力端子に入力された信号を増幅して、回路BF2の出力端子に出力する増幅回路として機能する。そのため、回路BF2は、図2(B1)に示す回路BF1と同様の構成とすることができる。この場合、インバータ回路DINV2の容量素子C01の第1端子には、高レベル電位と低レベル電位の中間電位を保持するのが好ましい。そして、インバータ回路DINV1の容量素子C01の第1端子の電位を高レベル電位、又は低レベル電位にすることによって、回路BF1の入出力時間を、回路BF2の入出力時間よりも短く、又は長くすることができる。

20

**【0117】**

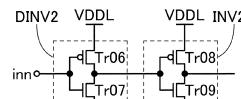

また、回路BF2は、図2(C1)に示す回路構成としてもよい。図2(C1)のインバータ回路DINV2は、トランジスタTr06及びトランジスタTr07を有し、インバータ回路INV2は、トランジスタTr08及びトランジスタTr09を有する。また、トランジスタTr06及びトランジスタTr08はpチャネル型トランジスタとし、トランジスタTr07及びトランジスタTr09はnチャネル型トランジスタとする。

30

**【0118】**

インバータ回路DINV2において、トランジスタTr06のゲートとトランジスタTr07のゲートは端子 $i_{nn}$ に電気的に接続され、トランジスタTr06の第1端子は配線VDDLに電気的に接続され、トランジスタTr06の第2端子は、トランジスタTr07の第1端子に電気的に接続されている。トランジスタTr07の第2端子は、配線VSSLに電気的に接続されている。また、トランジスタTr06の第2端子と、トランジスタTr07の第1端子は、インバータ回路INV2の入力端子に電気的に接続されている。

40

**【0119】**

インバータ回路INV2において、トランジスタTr08のゲートとトランジスタTr09のゲートは、インバータ回路INV2の入力端子に電気的に接続され、トランジスタTr08の第1端子は、配線VDDLに電気的に接続され、トランジスタTr08の第2端子は、トランジスタTr09の第1端子に電気的に接続されている。トランジスタTr09の第2端子は、配線VSSLに電気的に接続されている。また、トランジスタTr08の第2端子とトランジスタTr09の第1端子は、インバータ回路INV2の出力端子に電気的に接続されている。

**【0120】**

50

つまり、インバータ回路DINV2の回路構成は、インバータ回路INV2と同じ回路構成とすることができます。または、トランジスタTr07にバックゲートを設けて、当該バックゲートを配線VSSLに接続してもよい。

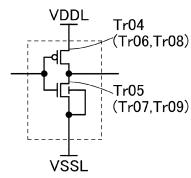

#### 【0121】

また、上述したインバータ回路INV1、インバータ回路INV2、インバータ回路DINV2は、例えば、図2(C2)に示すインバータ回路INV1Aの構成に置き換えてよい。インバータ回路INV1Aは、インバータ回路INV1、インバータ回路INV2、インバータ回路DINV2の回路構成において、トランジスタTr05(トランジスタTr07、トランジスタTr09)がバックゲートを有し、当該バックゲートがトランジスタTr05(トランジスタTr07、トランジスタTr09)の第2端子に電気的に接続されている構成となっている。10

#### 【0122】

##### [切り替え回路SC]

切り替え回路SCは、回路MPCにおける、端子inp又は端子innに入力された信号の出力先を端子outp又は端子outnのどちらか一方に選択する機能を有する。また、切り替え回路SCは、端子xtに電気的に接続され、端子xtに入力される信号(図1(A)における信号x<sub>1</sub>(k-1)乃至x<sub>m</sub>(k-1))に応じて、当該出力先を定めることができる。

#### 【0123】

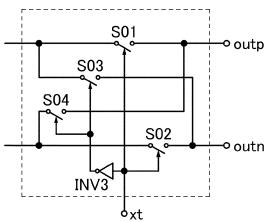

図3(A)に、切り替え回路SCの構成例を示す。切り替え回路SCは、スイッチS01乃至スイッチS04と、インバータ回路INV3と、を有する。20

#### 【0124】

スイッチS01の第1端子は、回路BF1の出力端子と、スイッチS03の第1端子と、に電気的に接続され、スイッチS01の第2端子は、端子outpに電気的に接続されている。スイッチS02の第1端子は、回路BF2の出力端子と、スイッチS04の第1端子と、に電気的に接続され、スイッチS02の第2端子は、端子outnに電気的に接続されている。スイッチS03の第2端子は端子outnに電気的に接続され、スイッチS04の第2端子は端子outpに電気的に接続されている。端子xtは、スイッチS01、スイッチS02のそれぞれの制御端子と、インバータ回路INV3の入力端子と、に電気的に接続され、インバータ回路INV3の出力端子は、スイッチS03、スイッチS04のそれぞれの制御端子と、に電気的に接続されている。30

#### 【0125】

なお、本明細書などにおいて、スイッチS01乃至スイッチS04のそれぞれは、制御端子に高レベル電位が印加されたときにオン状態となり、制御端子に低レベル電位が印加されたときにオフ状態となるものとする。

#### 【0126】

次に、切り替え回路SCの動作について説明する。例えば、端子xtに高レベル電位が印加されることによって、スイッチS01及びスイッチS02はオン状態となり、スイッチS03及びスイッチS04はオフ状態となるため、切り替え回路SCは、回路BF1の出力端子と端子outpとを電気的に接続し、回路BF2の出力端子と端子outnとを電気的に接続するように動作する。また、例えば、端子xtに低レベル電位が印加されることによって、スイッチS03及びスイッチS04はオン状態となり、スイッチS01及びスイッチS02はオフ状態となるため、切り替え回路SCは、回路BF1の出力端子と端子outnとを電気的に接続し、回路BF2の出力端子と端子outpとを電気的に接続するように動作する。40

#### 【0127】

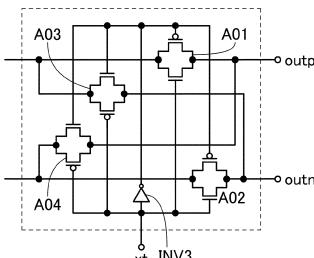

次に、切り替え回路SCの具体的な構成例について説明する。図3(B)は、図3(A)の切り替え回路SCに含まれているスイッチS01乃至スイッチS04をアナログスイッチA01乃至アナログスイッチA04に置き換えた回路構成となっている。

#### 【0128】

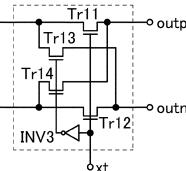

また、図3(B)と異なる、図3(A)の切り替え回路SCの具体的な構成例として、図3(C)に示す回路構成とすることができます。図3(C)の切り替え回路SCは、トランジスタTr11乃至トランジスタTr14と、インバータ回路INV3と、を有する。また、トランジスタTr11乃至トランジスタTr14は、nチャネル型トランジスタとする。なお、スイッチS01乃至スイッチS04の制御端子は、トランジスタTr11乃至トランジスタTr14のゲートに相当する。

#### 【0129】

トランジスタTr11の第1端子は、回路BF1の出力端子と、トランジスタTr13の第1端子と、に電気的に接続され、トランジスタTr11の第2端子は、端子outpに電気的に接続されている。トランジスタTr12の第1端子は、回路BF2の出力端子と、トランジスタTr14の第1端子と、に電気的に接続され、トランジスタTr12の第2端子は、端子outnに電気的に接続されている。トランジスタTr13の第2端子は端子outnに電気的に接続され、トランジスタTr14の第2端子は端子outpに電気的に接続されている。端子xtは、トランジスタTr11乃至トランジスタTr14のそれぞれのゲートに電気的に接続されている。

10

#### 【0130】

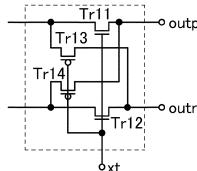

また、図3(B)(C)と異なる、図3(A)の切り替え回路SCの具体的な構成例として、図3(D)に示す回路構成とすることができます。図3(D)の切り替え回路SCは、図3(C)と同様に、トランジスタTr11乃至トランジスタTr14を有する。また、トランジスタTr11及びトランジスタTr12は、nチャネル型トランジスタとし、トランジスタTr13及びトランジスタTr14は、pチャネル型トランジスタとする。なお、スイッチS01乃至スイッチS04の制御端子は、トランジスタTr11乃至トランジスタTr14のゲートに相当する。また、トランジスタTr11及びトランジスタTr12と、トランジスタTr13及びトランジスタTr14と、は極性が異なるため、図3(D)の切り替え回路SCは、インバータ回路INV3を有していない。

20

#### 【0131】

また、切り替え回路SCを図3(A)乃至(D)に示す構成にすることによって、端子xtに入力される信号 $x_1(k-1)$ 乃至 $x_m(k-1)$ のそれぞれは、低レベル電位、又は高レベル電位の信号とすることができます。

30

#### 【0132】

また、回路MPCに適用する切り替え回路SCは、状況に応じて、図3(A)乃至(D)に示したいずれか一から選択することができます。また、回路MPCに適用する切り替え回路SCは、図3(A)乃至(D)に示した切り替え回路SCと異なる回路構成としてもよい。

#### 【0133】

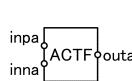

<<回路ACTF>>

図1(C)は、回路ACTFが有する端子を説明する図である。回路ACTFは、端子inpaと、端子innnaと、端子outtaと、を有する。

#### 【0134】

回路ACTFは、端子inpaと端子innnaと、のそれぞれに入力される信号(図1(A)における信号 $S_p[m]$ 、 $S_n[m]$ )の順番及び/又は時間差に応じて信号を生成して、当該信号を端子outtaから出力する機能を有する。なお、当該信号は、図4(B)における $z_j(k)$ に相当する。

40

#### 【0135】

例えば、回路ACTFは、端子inpaに入力される信号が端子innnaに入力される信号よりも遅い場合に、低レベル電位を信号として端子outtaから出力し、端子inpaに入力される信号が端子innnaに入力される信号よりも速い場合に、高レベル電位を信号として端子outtaから出力する構成にすることができます。換言すると、端子inpaに入力される電位の遷移が端子innnaに入力される電位の遷移よりも遅い場合に、低レベル電位を信号として端子outtaから出力し、端子inpaに入力される電位の遷移

50

が端子  $i_{nna}$  に入力される電位の遷移よりも速い場合に、高レベル電位を信号として端子  $o_{uta}$  から出力する構成にすることができる。このとき、低レベル電位を -1、高レベル電位を 1 に対応する信号  $z_j(k)$  とすることで、回路 A C T F は、ステップ関数の演算を行う回路に相当することができる。

#### 【0136】

また、例えば、回路 A C T F は、シグモイド関数、線形ランプ関数などアナログ値を出力する回路としてもよい。または、回路 A C T F は、端子  $i_{npa}$  と端子  $i_{nna}$  とに入力される信号のタイミングのズレに応じて、デジタル値、または、アナログ値を出力する機能を有していてもよい。

#### 【0137】

つまり、回路 A C T F は、ニューラルネットワーク 100において、ニューロンの活性化関数の演算を行う機能を有する。

#### 【0138】

なお、本実施の形態では、以後、回路 A C T F はステップ関数の演算を行う回路として説明する。

#### 【0139】

また、この場合、回路 A C T F は、ステップ関数の演算を行う回路として、フリップフロップ回路を適用することができる。このような場合、回路 A C T F は、端子  $i_{nna}$  に入力される信号が遷移したときに、端子  $i_{npa}$  に入力されている信号を読み出して、端子  $o_{uta}$  に当該信号を出力する動作を行う。

#### 【0140】

<< 変換回路 T R F >>

変換回路 T R F は、ニューラルネットワーク 100において、第  $(k-1)$  層のニューロン  $N_1(k-1)$  乃至ニューロン  $N_m(k-1)$  のそれぞれから出力される信号  $z_1(k-1)$  乃至  $z_m(k-1)$  を適切に変換して、変換したそれぞれの信号を回路 M P C [ 1 ] 乃至回路 M P C [ m ] に送信する機能を有する。

#### 【0141】

図 1 (A) では、信号  $z_1(k-1)$  乃至  $z_m(k-1)$  を信号  $x_1(k-1)$  乃至  $x_m(k-1)$  に変換して、信号  $x_1(k-1)$  乃至  $x_m(k-1)$  をそれぞれ回路 M P C [ 1 ] 乃至回路 M P C [ m ] に送信している様子を図示している。

#### 【0142】

なお、信号  $z_1(k-1)$  乃至  $z_m(k-1)$  のそれぞれは、前述のとおり、-1 又は 1 の値であり、信号  $x_1(k-1)$  乃至  $x_m(k-1)$  は、前述した切り替え回路 S C の説明のとおり、低レベル電位又は高レベル電位の信号とすることができるため、変換回路 T R F は論理回路として構成することができる。

#### 【0143】

なお、変換回路 T R F が行う信号  $z_1(k-1)$  乃至  $z_m(k-1)$  の変換については後述する。

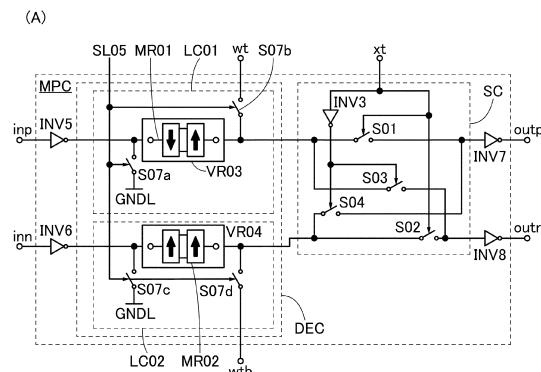

#### 【0144】

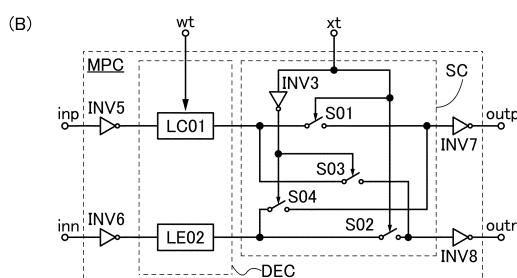

<< 回路 M P C、回路 A C T F、変換回路 T R F 等の変更例 >>

図 1 の演算回路 110 が有する回路 M P C は、上述した回路 M P C の構成に限定されず、状況に応じて、回路 M P C の回路構成が変更されたものとしてもよい。例えば、本発明の一態様の半導体装置として、回路 M P C は、図 5 (A) (B) の構成を適用することができる。図 5 (A) に示す回路 M P C は、図 2 (A) の回路 B F 1 のインバータ回路 D I N V 1 とインバータ回路 I N V 1 との電気的な接続の順序が変更され、かつ図 2 (A) の回路 B F 2 のインバータ回路 D I N V 2 とインバータ回路 I N V 2 との電気的な接続の順序が変更された構成となっている。また、図 5 (B) に示す回路 M P C は、図 2 (A) の回路 B F 1 のインバータ回路 I N V 1 と切り替え回路 S C との電気的な接続の順序が変更され、かつ図 2 (A) のインバータ回路 I N V 2 と切り替え回路 S C との電気的な接続の順序が変更された構成となっている。

10

20

30

40

50

**【0145】**

また、上述した回路MPC、回路ACTF、変換回路TRFなどに含まれるトランジスタは、OSトランジスタであることが好ましい。保持部HCAの説明において、トランジスタTr03として、OSトランジスタを適用するのが好ましいと言及したが、他のトランジスタについても、OSトランジスタを適用するのが好ましい。特に、他のトランジスタとしてOSトランジスタを適用する場合、OSトランジスタは、特に実施の形態4に記載するトランジスタの構造であることがより好ましい。ただし、本発明の一態様は、これに限定されない。

**【0146】**

また、回路MPC、回路ACTF、変換回路TRFなどに含まれるトランジスタは、OSトランジスタではなく、チャネル形成領域にシリコンを含むトランジスタ（以後、Siトランジスタと呼称する。）としてもよい。また、シリコンとしては、例えば、水素化アモルファスシリコン、微結晶シリコン、または多結晶シリコン等を用いることができる。また、OSトランジスタ、Siトランジスタ以外のトランジスタとしては、Geを活性層としたトランジスタ、ZnSe、CdS、GaAs、InP、GaN、SiGeなどの化合物半導体を活性層としたトランジスタ、カーボンナノチューブを活性層としたトランジスタ、有機半導体を活性層としたトランジスタ等を用いることができる。

10

**【0147】**

なお、OSトランジスタの半導体層の金属酸化物において、インジウムを含む金属酸化物（例えば、In酸化物）、あるいは亜鉛を含む金属酸化物（例えば、Zn酸化物）では、n型半導体は作製できているが、p型半導体は移動度及び信頼性の点で作製が難しい。そのため、演算回路110は、回路MPC、回路ACTF、変換回路TRFなどに含まれるnチャネル型トランジスタとしてOSトランジスタを適用し、pチャネル型トランジスタとしてSiトランジスタを適用した構成としてもよい。

20

**【0148】**

## &lt;動作方法&gt;

ここでは、演算回路110の動作方法の一例について説明する。

**【0149】**

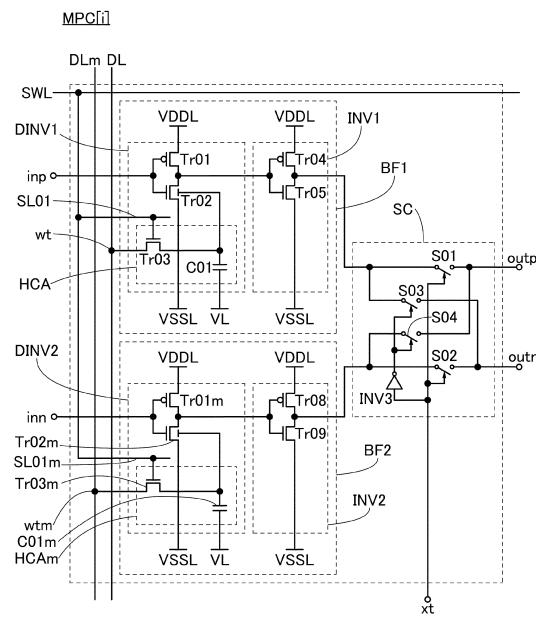

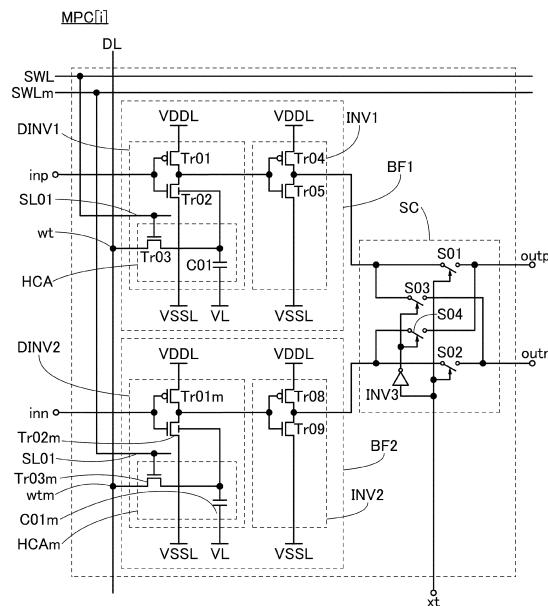

図6は、本動作例で扱う回路MPC[i]の構成例を示している。回路MPC[i]は、回路BF1及び回路BF2として図2(B1)に図示した回路BF1を適用し、切り替え回路SCとして図3(A)に図示した切り替え回路SCを適用している。

30

**【0150】**

なお、図6に示す回路BF2のインバータ回路DINV2が有する回路素子のそれぞれは、回路BF1のインバータ回路DINV1と区別するために、符号の最後に“m”を付記している。そのため、インバータ回路DINV2において、保持部HCAmは、保持部HCAに相当し、トランジスタTr01mはインバータ回路DINV1のトランジスタTr01に相当し、トランジスタTr02mはインバータ回路DINV1のトランジスタTr02に相当し、トランジスタTr03mはインバータ回路DINV1のトランジスタTr03に相当し、容量素子C01mはインバータ回路DINV1の容量素子C01に相当し、配線SL01mはインバータ回路DINV1の配線SL01に相当する。また、端子wtmは、容量素子C01mの第1端子に電位を書き込むための入力端子として機能する。

40

**【0151】**

また、図6に示す回路MPCでは、回路BF1の保持部HCAにおける端子wtは、配線DLに電気的に接続され、回路BF2の保持部HCAmにおける端子wtmは、配線DLmに電気的に接続されている。また、図6に示す回路MPCでは、回路BF1における配線SL01と回路BF2における配線SL01mとは、配線SWLに電気的に接続されている。

**【0152】**

また、本明細書などにおいて、トランジスタTr01乃至トランジスタTr05、トランジスタTr01m乃至トランジスタTr03m、トランジスタTr08、トランジスタ

50

$T_{r09}$ 、トランジスタ  $T_{r11}$  乃至トランジスタ  $T_{r14}$  は、特に断りの無い場合は、オン状態の場合は最終的に線形領域で動作する場合を含むものとする。すなわち、上述したそれぞれのトランジスタのゲート電圧、ソース電圧、及びドレイン電圧は、線形領域で動作する範囲での電圧に適切にバイアスされている場合を含むものとする。

#### 【0153】

また、本明細書などにおいて、「低レベル電位」、「高レベル電位」という用語は、特定の電位を意味するものではなく、配線が異なれば、具体的な電位も異なる場合がある。例えば、回路  $MPC$  に入出力される信号に応じた低レベル電位、高レベル電位のそれぞれは、配線  $SL01$  に印加される低レベル電位、高レベル電位と異なる電位であってもよい。

#### 【0154】

<< 初期動作 >>

初期動作として、端子  $x_t$  には、信号  $x_i(k-1)$  に相当する電位が入力される。これによって、トランジスタ  $T_{r11}$  乃至トランジスタ  $T_{r14}$  のそれぞれは、信号  $x_i(k-1)$  に相当する電位に応じて、オン状態又はオフ状態となる。

#### 【0155】

また、配線  $DL$  には重み係数  $w_i(k-1)_j(k)$  に相当する電位が入力され、配線  $DLm$  には中間電位が入力される。その後、配線  $SWL$  に高レベル電位を印加して、トランジスタ  $T_{r03}$ 、及びトランジスタ  $T_{r03m}$  をオン状態にする。この動作によって、容量素子  $C01$  の第1端子に重み係数  $w_i(k-1)_j(k)$  に相当する電位が書き込まれ、容量素子  $C01m$  の第1端子に中間電位が書き込まれる。このため、トランジスタ  $T_{r02}$  のしきい値電圧は、重み係数  $w_i(k-1)_j(k)$  に応じて変動し、トランジスタ  $T_{r02m}$  のしきい値電圧は、中間電位に応じて変動する。最後に、配線  $SWL$  に低レベル電位を印加して、トランジスタ  $T_{r03}$ 、及びトランジスタ  $T_{r03m}$  をオフ状態にすることによって、容量素子  $C01$  の第1端子及び容量素子  $C01m$  の第1端子のそれぞれの電位を保持することができる。

#### 【0156】

<< 演算動作 >>

初期動作の後に、回路  $MPC[i]$  (ここでの  $i$  は 1 以上  $m$  以下の整数とする。) の端子  $inp$  に信号  $Sp[i-1]$ 、また端子  $inn$  に信号  $Sn[i-1]$  が入力されることで、回路  $MPC[i]$  において演算動作が開始される。特に、 $i$  が 1 である場合、信号  $Sp[0]$ 、 $Sn[0]$  のそれぞれは、時間差がほぼ無く(ほぼ同時に)、回路  $MPC[1]$  の端子  $inp$ 、端子  $inn$  に入力されるものとする。また、 $i$  が 2 以上であるとき、信号  $Sp[i-1]$ 、 $Sn[i-1]$  は、回路  $MPC[i-1]$  から出力されているため、互いに時間差が生じていることがある。なお、演算動作の説明では、便宜的に、信号  $Sp[i-1]$ 、 $Sn[i-1]$  は、時間差がほぼ無く(ほぼ同時に)、回路  $MPC[i]$  の端子  $inp$ 、端子  $inn$  に入力されるものとする。

#### 【0157】

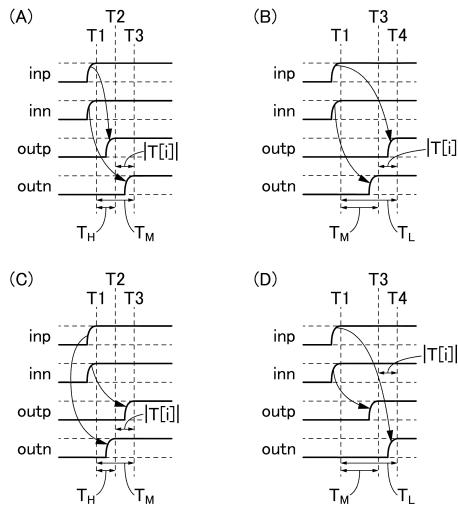

[条件1]

ここで、重み係数  $w_i(k-1)_j(k)$  に相当する電位が高レベル電位であり、かつ信号  $x_i(k-1)$  に相当する電位が高レベル電位である場合を考える。図 7(A) は、その場合における端子  $inp$ 、端子  $inn$ 、端子  $outp$ 、端子  $outn$  の電位の変動を示したタイミングチャートである。初めに、回路  $MPC[i]$  の端子  $inp$ 、端子  $inn$  のそれに信号  $Sp[i-1]$ 、 $Sn[i-1]$  として、高レベル電位が印加される。そして、時刻  $T_1$  のときに、回路  $MPC[i]$  の端子  $inp$ 、端子  $inn$  のそれぞれの電位が高レベル電位に達したとする。

#### 【0158】

このとき、回路  $MPC[i]$  の回路  $BF1$  の入力端子に信号  $Sp[i-1]$  として高レベル電位が印加されるため、回路  $MPC[i]$  の回路  $BF1$  の出力端子から高レベル電位が出力される。同様に、回路  $MPC[i]$  の回路  $BF2$  の入力端子に信号  $Sn[i-1]$  として高レベル電位が印加されるため、回路  $MPC[i]$  の回路  $BF2$  の出力端子から高

10

20

30

40

50

レベル電位が出力される。なお、回路BF1のトランジスタTr02のバックゲートには高レベル電位が印加され、回路BF2のトランジスタTr02mのバックゲートには中間電位が印加されているため、回路BF1は、回路BF2よりも早く動作する。したがって、端子inp及び端子innに同時に信号が入力された場合、回路BF1は、回路BF2よりも先に出力信号を出力する。

#### 【0159】

ところで、切り替え回路SCにおいて、端子xtには高レベル電位が印加されているため、回路BF1の出力端子と端子outpとの間は導通状態となり、回路BF2の出力端子と端子outnとの間は導通状態となる。すなわち、回路BF1からの出力信号は端子outpから出力され、回路BF2からの出力信号は端子outnから出力される。

10

#### 【0160】

回路BF1からの出力信号は、回路BF2からの出力信号よりも早く出力されるため、図7(A)のとおり、時刻T2に端子outpの電位が高レベル電位となり、その後の時刻T3に端子outnの電位が高レベル電位となる。つまり、時刻T2に端子outpから出力信号としてSp[i]が出力され、時刻T3に端子outnから出力信号としてSn[i]が出力される。なお、図7(A)では、端子inpに信号Sp[i-1]が入力されてから、端子outpから信号Sp[i]が出力されるまでの入出力時間をTHと記載し、端子innに信号Sn[i-1]が入力されてから、端子outnから信号Sn[i]が出力されるまでの入出力時間をTMと記載している。

#### 【0161】

20

#### 〔条件2〕

また、重み係数 $w_{i(k-1)}j^{(k)}$ に相当する電位が低レベル電位であり、かつ信号 $x_i(k-1)$ に相当する電位が高レベル電位である場合を考える。図7(B)は、その場合における端子inp、端子inn、端子outp、端子outnの電位の変動を示したタイミングチャートである。図7(A)の場合と同様に、初めに、回路MPC[i]の端子inp、端子innのそれぞれに信号Sp[i-1]、Sn[i-1]として、高レベル電位が印加される。そして、時刻T1のときに、回路MPC[i]の端子inp、端子innのそれぞれの電位が高レベル電位に達したとする。

#### 【0162】

このとき、回路MPC[i]の回路BF1の入力端子に信号Sp[i-1]として高レベル電位が印加されるため、回路MPC[i]の回路BF1の出力端子から高レベル電位が出力される。同様に、回路MPC[i]の回路BF2の入力端子に信号Sn[i-1]として高レベル電位が印加されるため、回路MPC[i]の回路BF2の出力端子から高レベル電位が出力される。なお、回路BF1のトランジスタTr02のバックゲートには低レベル電位が印加され、回路BF2のトランジスタTr02mのバックゲートには中間電位が印加されているため、回路BF1は、回路BF2よりも遅く動作する。したがって、端子inp及び端子innに同時に信号が入力された場合、回路BF1は、回路BF2よりも後に出力信号を出力する。

30

#### 【0163】

ところで、切り替え回路SCにおいて、端子xtには高レベル電位が印加されているため、図7(A)の場合と同様に、回路BF1の出力端子と端子outpとの間は導通状態となり、回路BF2の出力端子と端子outnとの間は導通状態となる。すなわち、回路BF1からの出力信号は端子outpから出力され、回路BF2からの出力信号は端子outnから出力される。

40

#### 【0164】

回路BF1からの出力信号は、回路BF2からの出力信号よりも遅く出力されるため、図7(B)のとおり、時刻T3に端子outnの電位が高レベル電位となり、その後の時刻T4に端子outpの電位が高レベル電位となる。つまり、時刻T3に端子outnから出力信号としてSn[i]が出力され、時刻T4に端子outpから出力信号としてSp[i]が出力される。なお、図7(B)では、端子inpに信号Sp[i-1]が入力

50

されてから、端子  $out_p$  から信号  $S_p[i]$  が出力されるまでの入出力時間を  $T_L$  と記載し、端子  $inn$  に信号  $S_n[i-1]$  が入力されてから、端子  $out_n$  から信号  $S_n[i]$  が出力されるまでの入出力時間を  $T_M$  と記載している。

#### 【0165】

##### 〔条件3〕

また、重み係数  $w_i(k-1)_j(k)$  に相当する電位が高レベル電位であり、かつ信号  $x_i(k-1)$  に相当する電位が低レベル電位である場合を考える。図7(C)は、その場合における端子  $inp$ 、端子  $inn$ 、端子  $out_p$ 、端子  $out_n$  の電位の変動を示したタイミングチャートである。図7(A)の場合と同様に、初めに、回路  $MPC[i]$  の端子  $inp$ 、端子  $inn$  のそれぞれに信号  $S_p[i-1]$ 、 $S_n[i-1]$  として、高レベル電位が印加される。そして、時刻  $T_1$  のときに、回路  $MPC[i]$  の端子  $inp$ 、端子  $inn$  のそれぞれの電位が高レベル電位に達したとする。10

#### 【0166】

このとき、回路  $MPC[i]$  の回路  $BF1$  の入力端子に信号  $S_p[i-1]$  として高レベル電位が印加されるため、回路  $MPC[i]$  の回路  $BF1$  の出力端子から高レベル電位が出力される。同様に、回路  $MPC[i]$  の回路  $BF2$  の入力端子に信号  $S_n[i-1]$  として高レベル電位が印加されるため、回路  $MPC[i]$  の回路  $BF2$  の出力端子から高レベル電位が出力される。なお、回路  $BF1$  のトランジスタ  $Tr02$  のバックゲートには高レベル電位が印加され、回路  $BF2$  のトランジスタ  $Tr02m$  のバックゲートには中間電位が印加されているため、回路  $BF1$  は、回路  $BF2$  よりも速く動作する。したがって、端子  $inp$  及び端子  $inn$  に同時に信号が入力された場合、回路  $BF1$  は、回路  $BF2$  よりも先に出力信号を出力する。20

#### 【0167】

ところで、切り替え回路  $SC$  において、端子  $xt$  には低レベル電位が印加されているため、回路  $BF1$  の出力端子と端子  $out_n$ との間は導通状態となり、回路  $BF2$  の出力端子と端子  $out_p$ との間は導通状態となる。すなわち、回路  $BF1$  からの出力信号は端子  $out_n$  から出力され、回路  $BF2$  からの出力信号は端子  $out_p$  から出力される。

#### 【0168】

回路  $BF1$  からの出力信号は、回路  $BF2$  からの出力信号よりも早く出力されるため、図7(C)のとおり、時刻  $T_2$  に端子  $out_n$  の電位が高レベル電位となり、その後の時刻  $T_3$  に端子  $out_p$  の電位が高レベル電位となる。つまり、時刻  $T_2$  に端子  $out_n$  から出力信号として  $S_n[i]$  が出力され、時刻  $T_3$  に端子  $out_p$  から出力信号として  $S_p[i]$  が出力される。なお、図7(C)では、端子  $inp$  に信号  $S_p[i-1]$  が入力されてから、端子  $out_n$  から信号  $S_n[i]$  が出力されるまでの入出力時間を  $T_H$  と記載し、端子  $inn$  に信号  $S_n[i-1]$  が入力されてから、端子  $out_p$  から信号  $S_p[i]$  が出力されるまでの入出力時間を  $T_M$  と記載している。30

#### 【0169】

##### 〔条件4〕

また、重み係数  $w_i(k-1)_j(k)$  に相当する電位が低レベル電位であり、かつ信号  $x_i(k-1)$  に相当する電位が高レベル電位である場合を考える。図7(D)は、その場合における端子  $inp$ 、端子  $inn$ 、端子  $out_p$ 、端子  $out_n$  の電位の変動を示したタイミングチャートである。図7(A)の場合と同様に、初めに、回路  $MPC[i]$  の端子  $inp$ 、端子  $inn$  のそれぞれに信号  $S_p[i-1]$ 、 $S_n[i-1]$  として、高レベル電位が印加される。そして、時刻  $T_1$  のときに、回路  $MPC[i]$  の端子  $inp$ 、端子  $inn$  のそれぞれの電位が高レベル電位に達したとする。40

#### 【0170】

このとき、回路  $MPC[i]$  の回路  $BF1$  の入力端子に信号  $S_p[i-1]$  として高レベル電位が印加されるため、回路  $MPC[i]$  の回路  $BF1$  の出力端子から高レベル電位が出力される。同様に、回路  $MPC[i]$  の回路  $BF2$  の入力端子に信号  $S_n[i-1]$  として高レベル電位が印加されるため、回路  $MPC[i]$  の回路  $BF2$  の出力端子から高50

レベル電位が出力される。なお、回路BF1のトランジスタTr02のバックゲートには低レベル電位が印加され、回路BF2のトランジスタTr02mのバックゲートには中間電位が印加されているため、回路BF1は、回路BF2よりも遅く動作する。したがって、端子inp及び端子innに同時に信号が入力された場合、回路BF1は、回路BF2よりも後に出力信号を出力する。

#### 【0171】

ところで、切り替え回路SCにおいて、端子xtには低レベル電位が印加されているため、回路BF1の出力端子と端子outnとの間は導通状態となり、回路BF2の出力端子と端子outpとの間は導通状態となる。すなわち、回路BF1からの出力信号は端子outnから出力され、回路BF2からの出力信号は端子outpから出力される。

10

#### 【0172】

回路BF1からの出力信号は、回路BF2からの出力信号よりも遅く出力されるため、図7(D)のとおり、時刻T3に端子outpの電位が高レベル電位となり、その後の時刻T4に端子outnの電位が高レベル電位となる。つまり、時刻T3に端子outpから出力信号としてSp[i]が出力され、時刻T4に端子outnから出力信号としてSn[i]が出力される。なお、図7(D)では、端子inpに信号Sp[i-1]が入力されてから、端子outnから信号Sn[i]が出力されるまでの入出力時間をTLと記載し、端子innに信号Sn[i-1]が入力されてから、端子outpから信号Sp[i]が出力されるまでの入出力時間をTMと記載している。

#### 【0173】

上述の条件1乃至条件4において、端子outnから信号Sn[i]が出力される時間を基準として、端子outpから信号Sp[i]が出力される時間差をTi[i]とする(図7(A)乃至図7(D)では、|Ti[i]|としている)。Ti[i]は、条件1乃至条件4の記載のとおり、重み係数wi(k-1)j(k)に相当する電位と、信号xi(k-1)に相当する電位と、に応じて決まる。

20

#### 【0174】

例えば、信号xi(k-1)に応じた電位が高レベル電位であるときにおいて、重み係数wi(k-1)j(k)が大きいほど(重み係数wi(k-1)j(k)に応じた電位が高いほど)、Ti[i]は小さくなる。そして、端子outnから信号Sn[i]が出力されるよりも早く、端子outpから信号Sp[i]が出力されるため、Ti[i]は負の値をとる。また、重み係数wi(k-1)j(k)が小さいほど(重み係数wi(k-1)j(k)に応じた電位が低いほど)、Ti[i]は大きくなる。そして、端子outnから信号Sn[i]が出力されるよりも遅く、端子outpから信号Sp[i]が出力されるため、Ti[i]は正の値をとる。

30

#### 【0175】

また、例えば、信号xi(k-1)に応じた電位を高レベル電位であるとき、回路BF2に対する回路BF1の入出力時間の差はそのまま出力される。また、例えば、信号xi(k-1)に応じた電位が低レベル電位であるとき、回路MPC[i]は、回路BF2に対する回路BF1の入出力時間の差は-1倍されて出力される。具体的には、条件1(図7(A)のタイミングチャート)において、端子outnから信号Sn[i]が出力された時と、端子outpから信号Sp[i]が出力された時との時間差をTi[i](=TM-TH)としたとき、条件3(図7(C)のタイミングチャート)において、端子outnから信号Sn[i]が出力された時と、端子outpから信号Sp[i]が出力された時との時間差は-Ti[i](=TM-TL)となる。

40

#### 【0176】

ところで、現実的には、切り替え回路SCにおいても、信号が入力されてから出力されるまで遅延が生じるため、端子outnから信号Sn[i]が出力される時間を基準として、端子outpから信号Sp[i]が出力される時間差Ti[i]には、当該遅延の時間が含まれている。なお、本実施の形態では当該遅延を無視して説明するものとする。

#### 【0177】

50

上記のとおり、回路MPC[i]は、回路MPC[i]に信号Sp[i-1]、Sn[i-1]が入力されることで、重み係数 $w_i^{(k-1)} j^{(k)}$ に相当する電位と、信号 $x_i^{(k-1)}$ に相当する電位と、に応じた時間差T[i]を、回路MPC[i]から出力される2つの信号Sp[i]、Sn[i]に付与する。

### 【0178】

<<回路MPCを複数個、接続した場合の演算動作>>

ここで、図1(A)のとおり、回路MPCをm個、接続した場合の演算回路110の動作について説明する。回路MPC[i]は、重み係数 $w_i^{(k-1)} j^{(k)}$ と、信号 $x_i^{(k-1)}$ と、に応じた時間差T[i]を、回路MPC[i]から出力される2つの信号Sp[i]、Sn[i]に付与するため、回路MPC[1]に同時に信号Sp[0]、Sn[0]を与えることで、回路MPC[1]乃至回路MPC[m]の各回路において生じる時間差が累積される。

### 【0179】

回路MPC[i-1]から出力された2つの信号Sp[i-1]、Sn[i-1]の時間差をT[i-1]とし、回路MPC[i]から出力された2つの信号Sp[i]、Sn[i]の時間差をT[i]とすると、T[i]とT[i-1]との関係式は、次の式で表すことができる。

### 【0180】

### 【数4】

$$T[i] = \{T[i-1] + g(w_i^{(k-1)} j^{(k)})\} \cdot x_i^{(k-1)} \quad \dots(1.4)$$

20

### 【0181】

$g(w_i^{(k-1)} j^{(k)})$ は、重み係数を変数として、回路BF1と回路BF2とのそれぞれから出力される信号の時間差を出力する関数である。なお、切り替え回路SCにおける遅延時間を考慮する場合、式(1.4)に当該遅延時間を示す項を加えればよい。

### 【0182】

式(1.4)は、回路MPC[i-1]から出力された2つの信号Sp[i-1]、Sn[i-1]の時間差T[i-1]に対して、回路MPC[i]に保持されている重み係数 $w_i^{(k-1)} j^{(k)}$ に応じた時間差である $g(w_i^{(k-1)} j^{(k)})$ を足して、その値に切り替え回路SCの効果として信号 $x_i^{(k-1)}$ の値を乗じた内容となっている。

30

### 【0183】

なお、T[1]は、次の式で表される。

### 【0184】

### 【数5】

$$T[1] = g(w_1^{(k-1)} j^{(k)}) \cdot x_1^{(k-1)} \quad \dots(1.5)$$

40

### 【0185】

ここで、式(1.4)及び式(1.5)の漸化式を解いてT[m]について求めると、式(1.6)となる。但し、式(1.6)の $\prod$ は、総乗を示す多項演算子である。

### 【0186】

### 【数6】

$$T[m] = \sum_{i=1}^m g(w_i^{(k-1)} j^{(k)}) \cdot \left( \prod_{h=i}^m x_h^{(k-1)} \right) \quad \dots(1.6)$$

### 【0187】

50

ここで、 $x_i^{(k-1)}$ を $z_i^{(k-1)}$ に置き換えることを考える。

### 【0188】

#### 【数7】

$$\prod_{h=i}^m x_h^{(k-1)} = x_i^{(k-1)} \times \cdots \times x_m^{(k-1)} = z_i^{(k-1)} \quad \cdots(1.7)$$

### 【0189】

$x_i^{(k-1)}$ を $z_i^{(k-1)}$ に置き換えることによって、式(1.6)、及び式(1.7)より、T[m]は、重み係数に依る関数 $g(w_i^{(k-1)} j^{(k)})$ と信号 $z_i^{(k-1)}$ との積和で表すことができる。つまり、式(1.2)を演算回路110によって計算することができる。

### 【0190】

次に、 $x_i^{(k-1)}$ を $z_i^{(k-1)}$ に置き換えるための $x_i^{(k-1)}$ と $z_i^{(k-1)}$ との関係式、及び信号 $z_1^{(k-1)}$ 乃至 $z_m^{(k-1)}$ を信号 $x_1^{(k-1)}$ 乃至 $x_m^{(k-1)}$ に変換する変換回路TRFについて説明する。

### 【0191】

初めに、 $z_{i+1}^{(k-1)}$ を考える。 $z_{i+1}^{(k-1)}$ は、式(1.7)を用いることによって次の式に表される(但し、ここでの*i*は1以上m-1以下の整数とする)。

### 【0192】

#### 【数8】

$$x_{i+1}^{(k-1)} \times \cdots \times x_m^{(k-1)} = z_{i+1}^{(k-1)} \quad \cdots(1.8)$$

### 【0193】

次に、式(1.7)と式(1.8)との辺々を割ることによって、次の式が得られる。

### 【0194】

#### 【数9】

$$x_i^{(k-1)} = \frac{z_i^{(k-1)}}{z_{i+1}^{(k-1)}} \quad \cdots(1.9)$$

### 【0195】

また、 $i = m$ のとき、 $x_m^{(k-1)}$ は、式(1.7)より次の式となる。

### 【0196】

#### 【数10】

$$x_m^{(k-1)} = z_m^{(k-1)} \quad \cdots(1.10)$$

### 【0197】

式(1.9)、及び式(1.10)の関係を満たすことによって、式(1.6)において、 $x_i^{(k-1)}$ を $z_i^{(k-1)}$ に置き換えることができる。

### 【0198】

次に、式(1.9)、及び式(1.10)の関係を満たすように、信号 $z_1^{(k-1)}$ 乃至 $z_m^{(k-1)}$ を信号 $x_1^{(k-1)}$ 乃至 $x_m^{(k-1)}$ に変換する変換回路TRFについて説明する。

### 【0199】

式(1.9)に示されている $z_i^{(k-1)}$ 、 $z_{i+1}^{(k-1)}$ は、それぞれ第( $k-1$ )層のニューロン $N_i^{(k-1)}$ 、ニューロン $N_{i+1}^{(k-1)}$ から出力された信号である。演算回路110では、ニューロンの活性化関数を、出力が-1又は1をとるステップ関

10

20

30

40

50

数としているため、信号  $x_i(k-1)$  がとる値も -1 又は 1 となる。そのため、 $x_i(k-1)$  は、 $z_i(k-1)$  と  $z_{i+1}(k-1)$  の排他的論理和の否定をとることによって表現することができる。

#### 【0200】

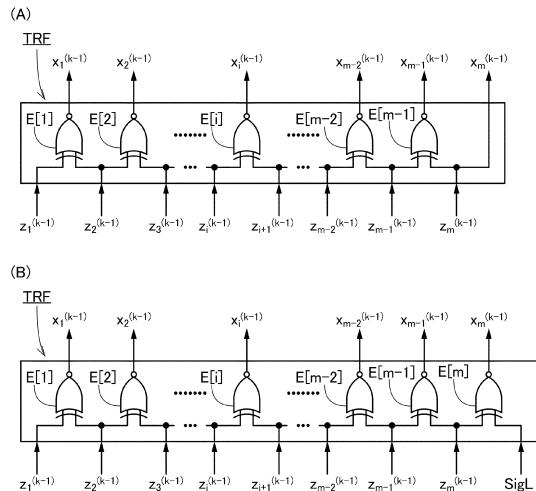

図 8 には、信号  $z_1(k-1)$  乃至  $z_m(k-1)$  を信号  $x_1(k-1)$  乃至  $x_m(k-1)$  に変換する変換回路 TRF の構成例を図示している。

#### 【0201】

図 8 (A) に示す変換回路 TRF は、一致回路（排他的論理和の否定回路）E [1] 乃至一致回路 E [m-1] を有する。なお、図 8 (A) では、一致回路 E [1]、一致回路 E [2]、一致回路 E [i]、一致回路 E [m-2]、一致回路 E [m-1] のみ図示しており、それ以外の一致回路については図示を省略している。10

#### 【0202】

一致回路 E [i] (ここでの i は 1 以上 m-1 以下の整数である。) について説明する。一致回路 E [i] の第 1 端子には信号  $z_i(k-1)$  が入力され、一致回路 E [i] の第 2 端子には信号  $z_{i+1}(k-1)$  が入力される。また、一致回路 E [i] の出力端子から信号  $x_i(k-1)$  が出力される。

#### 【0203】

また、図 8 (A) に示す変換回路 TRF は、信号  $z_m(k-1)$  が入力されることで、信号  $z_m(k-1)$  を信号  $x_m(k-1)$  としてそのまま出力している。

#### 【0204】

図 8 (A) に示す変換回路 TRF を構成することによって、式 (1.9)、式 (1.10) の関係式を満たすように、信号  $z_1(k-1)$  乃至  $z_m(k-1)$  の信号  $x_1(k-1)$  乃至  $x_m(k-1)$  への変換を行うことができる。20

#### 【0205】

なお、演算回路 110 が有する変換回路 TRF は図 8 (A) に示す回路構成に限定されず、状況に応じて、図 8 (A) に示す変換回路 TRF の構成を変更してもよい。

#### 【0206】

例えば、演算回路 110 が有する変換回路 TRF として、図 8 (B) に示す変換回路 TRF を適用してもよい。図 8 (B) の変換回路 TRF は、図 8 (A) の変換回路 TRF に一致回路 E [m] を加えた構成となっている。30

#### 【0207】

具体的には、一致回路 E [m] の第 1 端子には信号  $z_m(k-1)$  が入力され、一致回路 E [m] の第 2 端子には低レベル電位に相当する信号 S i g L が入力される。また、一致回路 E [m] の出力端子から信号  $x_m(k-1)$  が出力される。図 8 (B) の変換回路 TRF を構成することによって、図 8 (A) の変換回路 TRF と同様の動作を行うことができる。

#### 【0208】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【0209】

##### (実施の形態 2)

本実施の形態では、実施の形態 1 で説明した演算回路 110 の別の構成例について説明する。

#### 【0210】

##### < 演算回路 110 の構成例 >

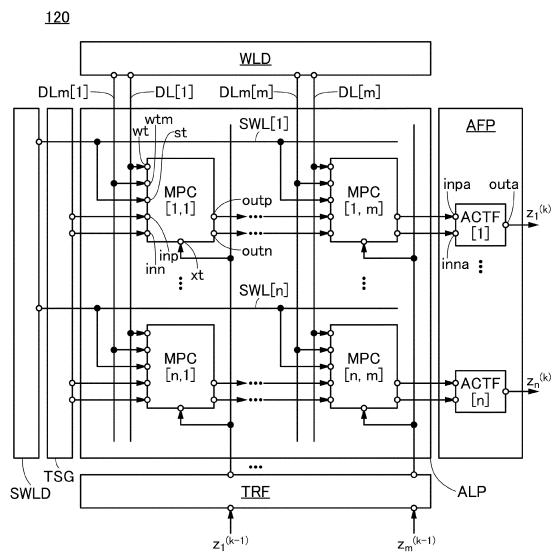

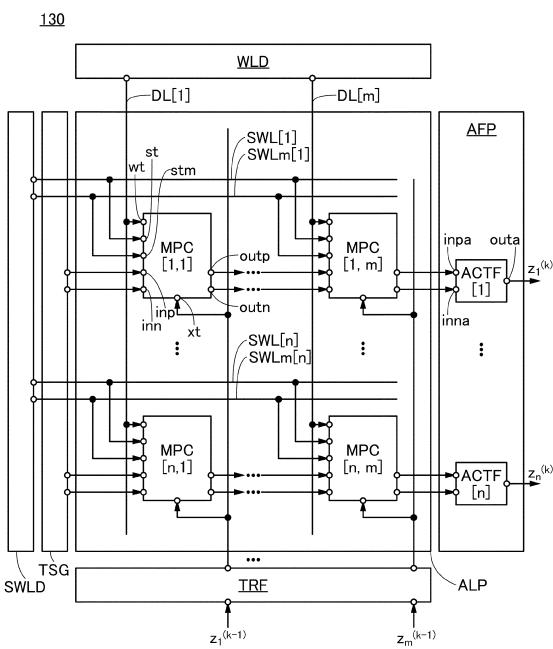

図 1 に示した演算回路 110において、回路 MPC は、例えば、マトリクス状に配置することができる。このような演算回路の構成例を図 9 に示す。

#### 【0211】

演算回路 120 は、回路 MPC がマトリクス状に配置されたアレイ部 ALP と、複数の回路 ACTF を含む回路 AFP と、回路 TSG と、回路 WLD と、回路 SWLD と、変換

10

20

30

40

50

回路 T R F と、を有する。

**【 0 2 1 2 】**

アレイ部 A L P は、 $n \times m$  個の回路 M P C を有し、回路 M P C はアレイ部 A L P において  $n$  行  $m$  列のマトリクス状に配置されている。なお、図 9 では、 $j$  行  $i$  列（ここでの  $j$  は 1 以上  $n$  以下の整数であって、 $i$  は 1 以上  $m$  以下の整数である。）に位置する回路 M P C を、回路 M P C [  $j$ ,  $i$  ] と表記している。但し、図 9 では、回路 M P C [ 1, 1 ]、回路 M P C [ 1,  $m$  ]、回路 M P C [  $n$ , 1 ]、回路 M P C [  $n$ ,  $m$  ] のみ図示しており、それ以外の回路 M P C については図示を省略している。

**【 0 2 1 3 】**

回路 A F P は、 $n$  個の回路 A C T F を有し、それぞれの回路 A C T F は回路 A F P において 1 列に配置されている。なお、図 9 では、 $j$  行に位置する回路 A C T F を、回路 A C T F [  $j$  ] と表記している。但し、図 9 では、回路 A C T F [ 1 ]、回路 A C T F [  $n$  ] のみ図示しており、それ以外の回路 A C T F については図示を省略している。

10

**【 0 2 1 4 】**

アレイ部 A L P 及び回路 A F P において、 $j$  行に着目すると、回路 M P C [  $j$ , 1 ] 乃至回路 M P C [  $j$ ,  $m$  ] は、隣接しあう回路 M P C 同士で、端子 o u t p と端子 i n p とが電気的に接続され、かつ端子 o u t n と端子 i n n とが電気的に接続されている。そして、回路 M P C [  $j$ ,  $m$  ] の端子 o u t p 及び端子 o u t n は、それぞれ回路 A C T F [  $j$  ] の端子 i n p a 及び端子 i n n a に電気的に接続されている。また、回路 M P C [  $j$ , 1 ] 乃至回路 M P C [  $j$ ,  $m$  ] のそれぞれの端子 x t は、変換回路 T R F に電気的に接続されている。

20

**【 0 2 1 5 】**

つまり、演算回路 120 のアレイ部 A L P のある 1 行の回路 M P C と回路 A C T F に着目することで、当該 1 行の回路 M P C と回路 A C T F は、図 1 に示した演算回路 110 とみなすことができる。

**【 0 2 1 6 】**

アレイ部 A L P が有する回路 M P C は、実施の形態 1 で説明した端子 w t 、端子 w t m 、端子 x t 、端子 i n p 、端子 i n n 、端子 o u t p 、端子 o u t n に加え、端子 s t を有する。端子 s t は、実施の形態 1 で説明した配線 S L 0 1 と電気的に接続される端子とする。

30

**【 0 2 1 7 】**

回路 M P C [  $j$ , 1 ] 乃至回路 M P C [  $j$ ,  $m$  ] のそれぞれの端子 s t は、配線 S W L [  $j$  ] に電気的に接続されている。配線 S W L [  $j$  ] は、実施の形態 1 における配線 S W L に相当し、図 9 では、配線 S W L [ 1 ] と配線 S W L [  $n$  ] が図示されている。また、回路 M P C [ 1,  $i$  ] 乃至回路 M P C [  $n$ ,  $i$  ] のそれぞれの端子 w t は、配線 D L [  $i$  ] に電気的に接続されている。配線 D L [  $i$  ] は、実施の形態 1 における配線 D L に相当し、図 9 では、配線 D L [ 1 ] と配線 D L [  $m$  ] が図示されている。更に、回路 M P C [ 1,  $i$  ] 乃至回路 M P C [  $n$ ,  $i$  ] のそれぞれの端子 w t m は、配線 D L m [  $i$  ] に電気的に接続されている。配線 D L m [  $i$  ] は、実施の形態 1 における配線 D L m に相当し、図 9 では、配線 D L m [ 1 ] と配線 D L m [  $m$  ] が図示されている。

40

**【 0 2 1 8 】**

回路 T S G は、回路 M P C [ 1, 1 ] 乃至回路 M P C [  $n$ , 1 ] のそれぞれの端子 i n p 、端子 i n n に入力するための信号を生成する回路である。

**【 0 2 1 9 】**

回路 W L D は、配線 D L [ 1 ] 乃至配線 D L [  $m$  ] に重み係数に応じた電位を与える機能と、配線 D L m [ 1 ] 乃至配線 D L m [  $m$  ] に中間電位を与える機能と、を有する。

**【 0 2 2 0 】**

回路 S W L D は、当該重み係数に応じた電位を保持するための保持部を選択するための回路である。具体的には、回路 S W L D は、配線 S W L [  $j$  ] を介して、回路 M P C [  $j$ , 1 ] 乃至回路 M P C [  $j$ ,  $m$  ] が有する保持部 H C A 及び H C A m のそれぞれのトラン

50

ジスタ Tr 03 及びトランジスタ Tr 03m のゲートに電位を与える機能を有する。

#### 【0221】

例えば、回路 MPC [ j , i ] の保持部 HCA 、保持部 HCAm のそれぞれに電位を保持する場合、回路 WLD によって、配線 DL [ i ] 、配線 DLm [ i ] のそれぞれに保持する電位を印加し、回路 SWLD によって、配線 SWL [ j ] に高レベル電位を印加して、回路 MPC [ j , i ] の保持部 HCA 及び HCAm のそれぞれのトランジスタ Tr 03 及びトランジスタ Tr 03m をオン状態にすることで、容量素子 C01 及び容量素子 C01m の第 1 端子に配線 DL [ i ] 、配線 DLm [ i ] のそれぞれの電位を書き込むことができる。また、容量素子 C01 及び容量素子 C01m の第 1 端子に電位を書き込んだ後は、回路 SWLD によって、配線 SWL [ j ] に低レベル電位を印加して、回路 MPC [ j , i ] の保持部 HCA 及び HCAm のそれぞれのトランジスタ Tr 03 及びトランジスタ Tr 03m をオフ状態にすることで、保持部 HCA 、保持部 HCAm にそれぞれ書き込まれた電位を保持することができる。10

#### 【0222】

変換回路 TRF については、実施の形態 1 で説明した変換回路 TRF の記載を参照する。なお、図 9 では、変換回路 TRF に信号  $z_1(k-1)$  と信号  $z_m(k-1)$  が入力されている様子を示している。また、変換回路 TRF に入力された信号  $z_1(k-1)$  乃至  $z_m(k-1)$  が変換されて出力される信号  $x_1(k-1)$  乃至  $x_m(k-1)$  は、アレイ部 ALP が有する回路 MPC に送られる。特に、信号  $x_i(k-1)$  は、回路 MPC [ 1 , i ] 乃至回路 MPC [ n , i ] の端子 xt に送られる。20

#### 【0223】

図 9 に示す演算回路 120 を構成することによって、複数の演算を同時に行うことができる。実施の形態 1 では、図 1 の演算回路 110 は、図 4 (B) のニューロン  $N_j(k)$  が出力する信号  $z_j(k)$  を求める回路と説明したが、図 9 に示す演算回路 120 を用いることにより、ニューロン  $N_1(k)$  乃至ニューロン  $N_n(k)$  のそれぞれが出力する信号  $z_1(k)$  乃至信号  $z_n(k)$  を同時に求めることができる。

#### 【0224】

詳細に説明すると、第 k 層のニューロン  $N_1(k)$  乃至ニューロン  $N_n(k)$  のそれぞれには、第 (k-1) 層のニューロン  $N_1(k-1)$  乃至ニューロン  $N_m(k-1)$  のそれぞれから出力された信号  $z_1(k-1)$  乃至  $z_m(k-1)$  の全てが入力される。これは、変換回路 TRF から出力された信号  $x_1(k-1)$  乃至  $x_m(k-1)$  が、アレイ部 ALP が有する回路 MPC に送られることに相当する。そして、第 (k-1) 層のニューロン  $N_i(k-1)$  と第 k 層のニューロン  $N_j(k)$  との重み係数に応じた電位を回路 MPC [ j , i ] の保持部 HCA に保持することによって、第 k 層のニューロン  $N_j(k)$  から出力される信号  $z_j(k)$  を、回路 ACTF [ j ] から出力することができる。なお、図 9 では、回路 ACTF [ 1 ] から信号  $z_1(k)$  を出力し、回路 ACTF [ n ] から信号  $z_n(k)$  を出力する様子を図示している。30

#### 【0225】

なお、本発明の一態様の半導体装置は、図 9 に示す演算回路 120 に限定されない。図 9 に示す演算回路 120 は、図 6 に示す回路 MPC [ i ] をマトリクス状に配置した場合の構成であるが、図 10 に示す回路 MPC [ i ] をマトリクス状に配置した場合も演算回路を構成することができる。図 10 の回路 MPC [ i ] は、回路 BF1 の保持部 HCA における端子 wt と、回路 BF2 の保持部 HCAm における端子 wt m と、が配線 DL に電気的に接続されている点と、回路 BF1 における配線 SL01 が配線 SWL に電気的に接続されている点と、回路 BF2 における配線 SL01m が配線 SWLm に電気的に接続されている点で図 6 の回路 MPC [ i ] と異なっている。40

#### 【0226】

図 9 の演算回路 120 と同様に、図 10 の回路 MPC [ i ] を  $n \times m$  個のマトリクス状に配置して演算回路を構成した例を図 11 に示す。図 11 に示す演算回路 130 は、回路 MPC が有する一部の端子、及び当該一部の端子に接続されている配線が、図 9 の演算回

路 1 2 0 と異なっている。

#### 【 0 2 2 7 】

アレイ部 A L P が有する回路 M P C は、図 1 0 に示した端子 w t 、端子 w t m 、端子 x t 、端子 i n p 、端子 i n n 、端子 o u t p 、端子 o u t n に加え、端子 s t と端子 s t m を有する。端子 s t は、回路 B F 1 における配線 S L 0 1 と電気的に接続される端子であり、端子 s t m は、回路 B F 2 における配線 S L 0 1 m と電気的に接続される端子である。なお、端子 w t と端子 w t m は、図 1 0 において、互いに電気的に接続されているため、図 1 1 では端子 w t m の図示を省略し、端子 w t m は端子 w t と同一の端子とみなして説明する。

#### 【 0 2 2 8 】

回路 M P C [ j , 1 ] 乃至回路 M P C [ j , m ] のそれぞれの端子 s t は、配線 S W L [ j ] に電気的に接続されている。配線 S W L [ j ] は、図 1 0 における配線 S W L に相当し、図 1 1 では、配線 S W L [ 1 ] と配線 S W L [ n ] が図示されている。また、回路 M P C [ j , 1 ] 乃至回路 M P C [ j , m ] のそれぞれの端子 s t m は、配線 S W L m [ j ] に電気的に接続されている。配線 S W L m [ j ] は、図 1 0 における配線 S W L m に相当し、図 1 1 では、配線 S W L m [ 1 ] と配線 S W L m [ n ] が図示されている。更に、回路 M P C [ 1 , i ] 乃至回路 M P C [ n , i ] のそれぞれの端子 w t は、配線 D L [ i ] に電気的に接続されている。配線 D L [ i ] は、図 1 0 における配線 D L に相当し、図 1 1 では、配線 D L [ 1 ] と配線 D L [ m ] が図示されている。

#### 【 0 2 2 9 】

つまり、演算回路 1 2 0 は、回路 M P C が有する 2 個の保持部 H C A に保持するための電位を別々の配線で入力し、トランジスタ T r 0 3 及びトランジスタ T r 0 3 m のオン状態とオフ状態の切り替えを 1 本の配線で行う構成であり、演算回路 1 3 0 は、回路 M P C が有する 2 個の保持部 H C A に保持するための電位を 1 本の配線で入力し、トランジスタ T r 0 3 及びトランジスタ T r 0 3 m のオン状態とオフ状態の切り替えを別々の配線で行う構成となっている。

#### 【 0 2 3 0 】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【 0 2 3 1 】

##### ( 実施の形態 3 )

本実施の形態では、実施の形態 1 で説明した回路 M P C の別の構成例について説明する。

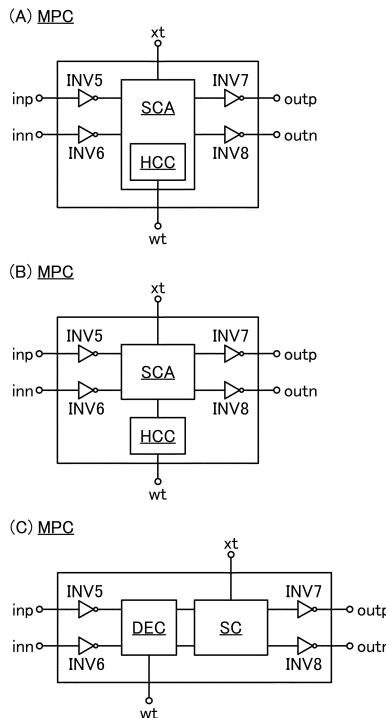

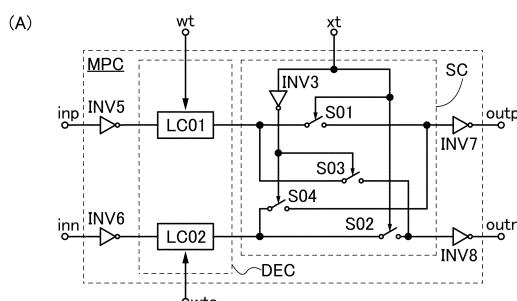

#### 【 0 2 3 2 】

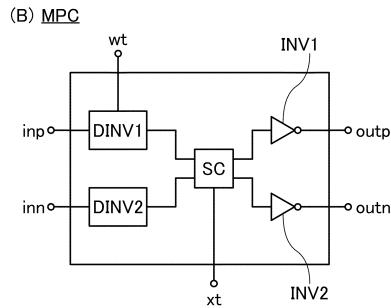

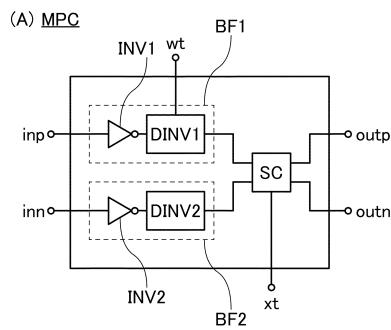

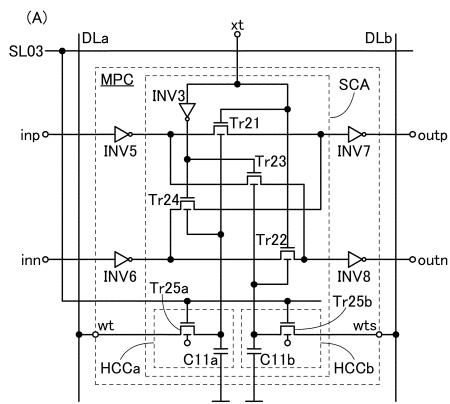

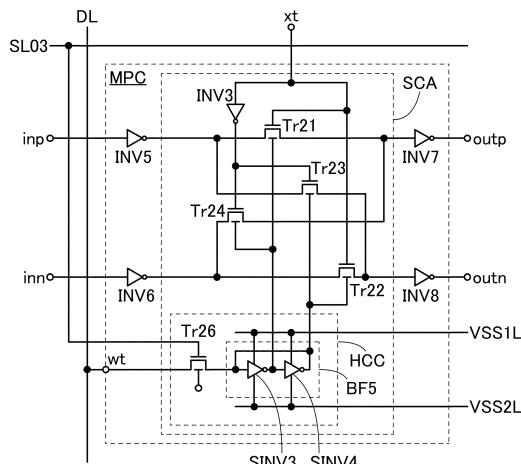

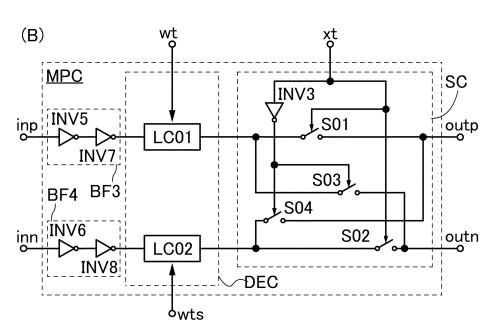

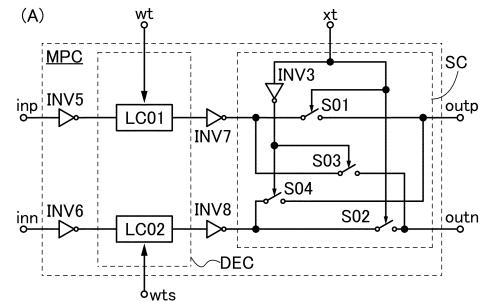

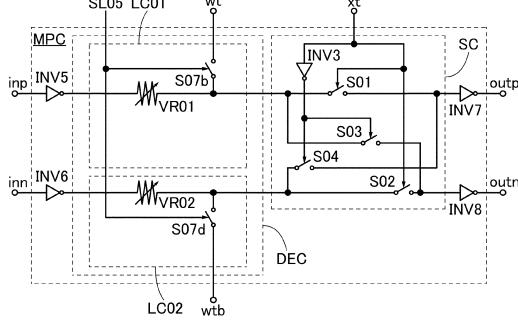

図 1 2 ( A ) に示す回路 M P C は、インバータ回路 I N V 5 乃至インバータ回路 I N V 8 と、切り替え回路 S C A と、を有する。

#### 【 0 2 3 3 】

インバータ回路 I N V 5 の入力端子は端子 i n p に電気的に接続され、インバータ回路 I N V 5 の出力端子は切り替え回路 S C A の 2 つの入力端子の一方へ電気的に接続されている。インバータ回路 I N V 6 の入力端子は端子 i n n に電気的に接続され、インバータ回路 I N V 6 の出力端子は切り替え回路 S C A の 2 つの入力端子の他方に電気的に接続されている。切り替え回路 S C A の 2 つの出力端子の一方はインバータ回路 I N V 7 の入力端子に電気的に接続され、切り替え回路 S C A の 2 つの出力端子の他方はインバータ回路 I N V 8 の入力端子に電気的に接続されている。インバータ回路 I N V 7 の出力端子は端子 o u t p に電気的に接続され、インバータ回路 I N V 8 の出力端子は端子 o u t n に電気的に接続されている。

#### 【 0 2 3 4 】

切り替え回路 S C A は、回路 M P C における、端子 i n p 又は端子 i n n に入力された信号の出力先を端子 o u t p 又は端子 o u t n のどちらか一方に選択する機能を有する。また、切り替え回路 S C A は、端子 x t に電気的に接続され、端子 x t に入力される信号 ( 図 1 ( A ) における信号 x 1 ( k - 1 ) 乃至 x m ( k - 1 ) ) に応じて、当該出力先を定め

10

20

30

40

50

ることができる。

#### 【0235】

また、図12(A)の回路MPCは、信号が端子in pに入力されてから端子out p又は端子out nの一方から出力するまでの入出力時間を可変する機能と、信号が端子innに入力されてから端子out p又は端子out nの他方から出力するまでの入出力時間を可変する機能と、を有する。それぞれの入出力時間は、端子wtに入力される信号(重み係数 $w_1(k-1)_j(k)$ 乃至 $w_m(k-1)_j(k)$ )によって定めることができる。

#### 【0236】

ところで、図12(A)の回路MPCにおいて、切り替え回路SCAは、保持部HCCを有する。保持部HCCは、端子wtから入力された当該信号に応じた電位を保持する機能を有し、回路MPCは、当該電位に応じて上述した入出力時間を可変することができる。

10

#### 【0237】

インバータ回路INV5乃至インバータ回路INV8は、実施の形態1で説明したインバータ回路INV1及びインバータ回路INV2と同様に、入力された信号の反転信号を出力する機能を有する。また、図12(A)の回路MPCでは、インバータ回路INV5と、インバータ回路INV5に切り替え回路SCAを介して電気的に接続されている、インバータ回路INV7又はインバータ回路INV8の一方と、によって第1のバッファ回路が構成され、インバータ回路INV6と、インバータ回路INV6に切り替え回路SCAを介して電気的に接続される、インバータ回路INV7又はインバータ回路INV8の他方と、によって第2のバッファ回路が構成されている。つまり、図12(A)の回路MPCは、端子in pに入力された信号を補正して、端子out p又は端子out nの一方に出力し、端子innに入力された信号を補正して、端子out p又は端子out nの他方に出力する回路としても機能する。なお、インバータ回路の数は、2個に限定されない。ただし、入力と同じ論理値で出力するほうが回路を構成しやすいため、複数個の方が望ましい。

20

#### 【0238】

また、図12(A)の回路MPCは、インバータ回路INV5乃至インバータ回路INV8を用いずに、代わりに論理回路、信号変換回路(アナログデジタル変換回路、デジタルアナログ変換回路など)、電位レベル変換回路などを用いて増幅回路を構成してもよい。

30

#### 【0239】

また、図12(A)の回路MPCは、保持部HCCが切り替え回路SCAに含まれている構成としているが、保持部HCCは、図12(B)に示すとおり、切り替え回路SCAの外部に設けてもよい。

#### 【0240】

また、図12(A)(B)の回路MPCは、端子wtから送られてきた信号に応じた電位を保持部HCCに保持して、当該電位に応じて回路MPCの入出力時間を変動させる構成としているが、回路MPCは、図12(C)に示すとおり、インバータ回路INV5及びインバータ回路INV6と、インバータ回路INV7及びインバータ回路INV8と、の間に、回路DECと、実施の形態1で説明した切り替え回路SCとを設けた構成としてもよい。回路DECは、端子wtから送られてきた信号に応じて、端子in p及び端子innと、端子out p及び端子out nと、の間の信号の伝達速度を変動させる機能を有し、図12(C)の回路MPCは、当該機能によって、回路MPCの入出力時間を変動させる構成となっている。

40

#### 【0241】

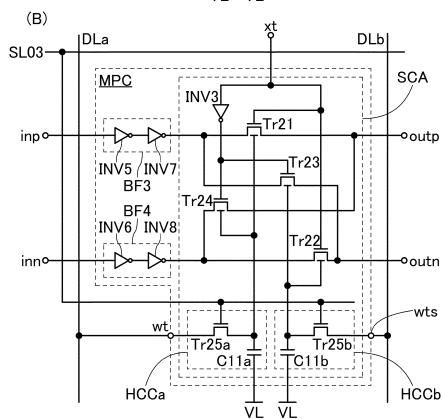

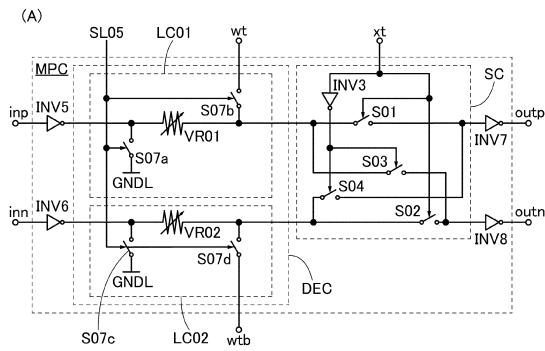

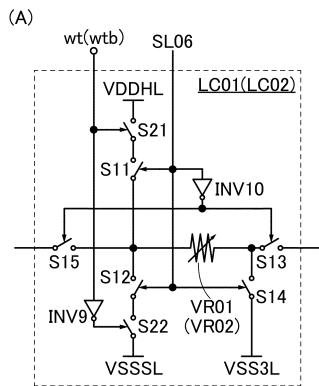

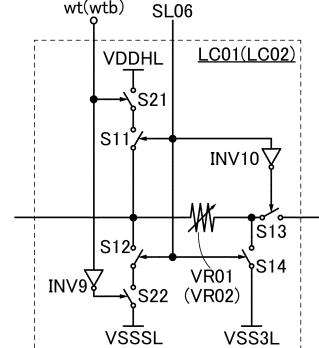

<構成例1>

図12(A)の回路MPCの具体的な構成例を図13(A)に示す。図13(A)に示す回路MPCが有する切り替え回路SCAは、トランジスタTr21乃至トランジスタTr24と、インバータ回路INV3と、を有する。また、図12(A)の切り替え回路SCAが有する保持部HCCは、図13(A)では、保持部HCCaと保持部HCCbとして図示している。保持部HCCaは、トランジスタTr25aと、容量素子C11aと、

50

を有し、保持部 H C C b は、トランジスタ Tr 25b と、容量素子 C 11b と、を有する。

【 0 2 4 2 】

トランジスタ Tr 21 乃至トランジスタ Tr 24 のそれぞれは、バックゲートを有する。また、トランジスタ Tr 21 乃至トランジスタ Tr 24 としては、先の実施の形態で説明した OS トランジスタであることが好ましい。また、トランジスタ Tr 21 乃至トランジスタ Tr 24 のそれぞれは、Si トランジスタとしてもよい。

【 0 2 4 3 】

インバータ回路 IN V 5 の出力端子は、トランジスタ Tr 21 の第 1 端子と、トランジスタ Tr 23 の第 1 端子と、に電気的に接続され、インバータ回路 IN V 6 の出力端子は、トランジスタ Tr 22 の第 1 端子と、トランジスタ Tr 24 の第 1 端子と、に電気的に接続されている。インバータ回路 IN V 7 の入力端子は、トランジスタ Tr 21 の第 2 端子と、トランジスタ Tr 24 の第 2 端子と、に電気的に接続され、インバータ回路 IN V 8 の入力端子は、トランジスタ Tr 22 の第 2 端子と、トランジスタ Tr 23 の第 2 端子と、に電気的に接続されている。端子 x t は、トランジスタ Tr 21 のゲートと、トランジスタ Tr 22 のゲートと、インバータ回路 IN V 3 の入力端子と、に電気的に接続され、インバータ回路 IN V 3 の出力端子は、トランジスタ Tr 23 のゲートと、トランジスタ Tr 24 のゲートと、に電気的に接続されている。

【 0 2 4 4 】

保持部 H C C a において、トランジスタ Tr 25a の第 1 端子は、容量素子 C 11a の第 1 端子と、トランジスタ Tr 21 のバックゲートと、トランジスタ Tr 24 のバックゲートと、に電気的に接続され、トランジスタ Tr 25a の第 2 端子は、端子 w t を介して、配線 D L a に電気的に接続され、トランジスタ Tr 25a のゲートは、配線 S L 03 に電気的に接続されている。容量素子 C 11a の第 2 端子は、配線 V L に電気的に接続されている。

【 0 2 4 5 】

保持部 H C C b において、トランジスタ Tr 25b の第 1 端子は、容量素子 C 11b の第 1 端子と、トランジスタ Tr 22 のバックゲートと、トランジスタ Tr 23 のバックゲートと、に電気的に接続され、トランジスタ Tr 25b の第 2 端子は、端子 w t s を介して、配線 D L b に電気的に接続され、トランジスタ Tr 25b のゲートは、配線 S L 03 に電気的に接続されている。容量素子 C 11b の第 2 端子は、配線 V L に電気的に接続されている。

【 0 2 4 6 】

配線 V L は、実施の形態 1 で説明した配線 V L と同様に、定電圧を供給する電圧線として機能し、当該定電圧としては、V DD、V SS、又は接地電位などとすることができる。

【 0 2 4 7 】

保持部 H C C a は、端子 w t から入力された信号に応じた電位を保持する機能を有し、保持部 H C C b は、端子 w t s から入力された信号に応じた電位を保持する機能を有する。つまり、端子 w t に電気的に接続されている配線 D L a は、保持部 H C C a に保持する電位を供給する信号線として機能し、端子 w t s に電気的に接続されている配線 D L b は、保持部 H C C b に保持する電位を供給する信号線として機能する。

【 0 2 4 8 】

保持部 H C C a に含まれているトランジスタ Tr 25a はスイッチング素子として機能し、配線 S L 03 からトランジスタ Tr 25a のゲートに電位を印加することによって、トランジスタ Tr 25a をオン状態又はオフ状態にすることができる。同様に、保持部 H C C b に含まれているトランジスタ Tr 25b はスイッチング素子として機能し、配線 S L 03 からトランジスタ Tr 25b のゲートに電位を印加することによって、トランジスタ Tr 25b をオン状態又はオフ状態にすることができる。

【 0 2 4 9 】

配線 S L 03 に高レベル電位を与えて、トランジスタ Tr 25a 及びトランジスタ Tr 25b をオン状態にすることによって、端子 w t と容量素子 C 11a の第 1 端子との間は

10

20

30

40

50

導通状態となり、端子 w t s と容量素子 C 1 1 b の第 1 端子との間は導通状態となる。このとき、回路 M P C は端子 w t 及び端子 w t s からそれぞれ信号を受信することで、それぞれの信号に応じた電位を容量素子 C 1 1 a 及び容量素子 C 1 1 b の第 1 端子に書き込むことができる。そして、それぞれの電位を容量素子 C 1 1 a 及び容量素子 C 1 1 b の第 1 端子に書き込んだ後に、配線 S L 0 3 に低レベル電位を与えて、トランジスタ T r 2 5 a 及びトランジスタ T r 2 5 b をオフ状態にすることによって、保持部 H C C a 及び保持部 H C C b にそれぞれ送られた電位を保持することができる。

#### 【 0 2 5 0 】

なお、保持部 H C C a 及び保持部 H C C b に長時間、電位の保持を行う場合、トランジスタ T r 2 5 a、トランジスタ T r 2 5 b は、オフ電流が非常に小さい O S トランジスタを適用するのが好ましい。また、トランジスタ T r 2 5 a 及びトランジスタ T r 2 5 b は、図 1 3 ( A ) に示すとおり、バックゲートを有するトランジスタとしてもよい。図 1 3 ( A ) では、トランジスタ T r 2 5 a 及びトランジスタ T r 2 5 b のバックゲートの詳細な電気的接続を図示していないが、例えば、トランジスタ T r 2 5 a ( トランジスタ T r 2 5 b ) のバックゲートとゲートとを電気的に接続することによって、トランジスタ T r 2 5 a ( トランジスタ T r 2 5 b ) のオン電流を大きくすることができます。また、例えば、トランジスタ T r 2 5 a ( トランジスタ T r 2 5 b ) のバックゲートに、しきい値電圧を高くするような電圧を与える配線を電気的に接続することによって、トランジスタ T r 2 5 a ( トランジスタ T r 2 5 b ) のオフ電流を小さくすることができます。なお、トランジスタ T r 2 5 a 及びトランジスタ T r 2 5 b は、バックゲートを有さなくてもよい。

10

#### 【 0 2 5 1 】

なお、端子 w t には、実施の形態 1 の説明と同様に、重み係数  $w_i(k-1)_j(k)$  に相当する電位が、信号として入力される。当該電位としては、低レベル電位、高レベル電位、又は低レベル電位を超えて高レベル電位未満の電位などとすることができます。一方、端子 w t s には、中間電位が、信号として入力される。当該中間電位としては、低レベル電位を超えて高レベル電位未満の電位とすることができます。つまり、端子 w t s に入力される中間電位は、端子 w t に入力される電位における基準電位として考えることができます。そのため、配線 D L a は、重み係数  $w_i(k-1)_j(k)$  に相当する電位を供給する配線とし、配線 D L b は、中間電位を供給する配線とすればよい。

20

#### 【 0 2 5 2 】

端子 x t には、実施の形態 1 の説明と同様に、信号  $x_i(k-1)$  に相当する電位が、信号として入力される。信号  $x_i(k-1)$  は、低レベル電位、又は高レベル電位の信号とすることができる。

30

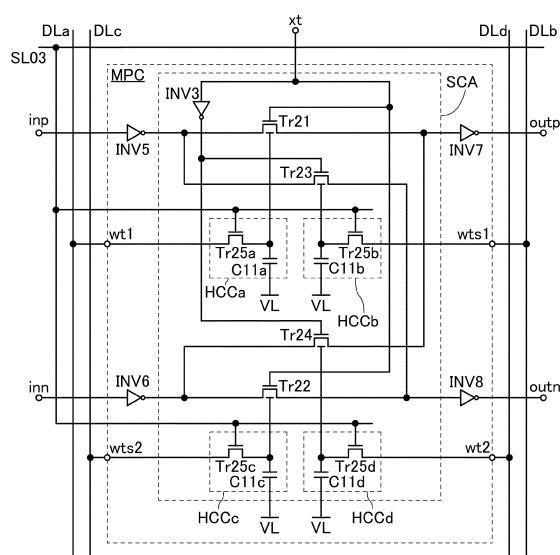

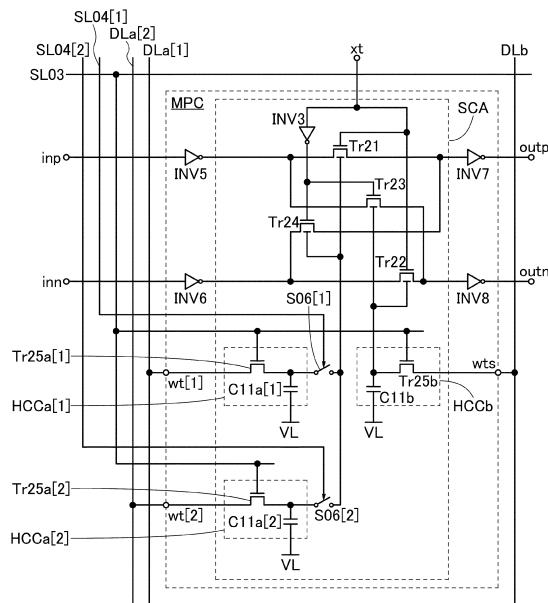

#### 【 0 2 5 3 】

なお、図 1 2 ( A ) の回路 M P C は、図 1 3 ( A ) の回路 M P C の回路構成に限定されず、状況に応じて、図 1 3 ( A ) の回路 M P C の回路構成を変更してもよい。例えば、図 1 3 ( B ) に示すとおり、インバータ回路 I N V 7 及びインバータ回路 I N V 8 を設ける場所を変更してもよい。図 1 3 ( B ) の回路 M P C では、インバータ回路 I N V 7 の入力端子がインバータ回路 I N V 5 の出力端子に電気的に接続され、インバータ回路 I N V 7 の出力端子が切り替え回路 S C A の 2 つある入力端子の一方に電気的に接続され、切り替え回路 S C A の 2 つある出力端子の一方が端子 o u t p に電気的に接続され、インバータ回路 I N V 8 の入力端子がインバータ回路 I N V 6 の出力端子に電気的に接続され、インバータ回路 I N V 8 の出力端子が切り替え回路 S C A の 2 つある入力端子の他方に電気的に接続され、切り替え回路 S C A の 2 つある出力端子の他方が端子 o u t n に電気的に接続されている。また、図 1 3 ( B ) には、インバータ回路 I N V 5 及びインバータ回路 I N V 7 を含む回路として回路 B F 3 と、インバータ回路 I N V 6 及びインバータ回路 I N V 8 を含む回路として回路 B F 4 と、を図示している。回路 B F 3、及び / 又は回路 B F 4 は、図 1 3 ( B ) に示すバッファ回路でなく、代わりに論理回路、信号変換回路 ( アナログデジタル変換回路、デジタルアナログ変換回路など ) 、電位レベル変換回路などを用いた增幅回路としてもよい。

40

50

### 【0254】

なお、図13(B)に示すトランジスタTr25a及びトランジスタTr25bにおいて、バックゲートを図示していないが、図13(A)に示すトランジスタTr25a及びトランジスタTr25bのとおり、バックゲートを有してもよい。また、特に断らない場合に限り、本明細書などに記載されるトランジスタのバックゲートの有無については、限定しないものとする。例えば、図面において、トランジスタにバックゲートが図示されていない場合であっても、当該トランジスタはバックゲートを有する構造とすることができる。

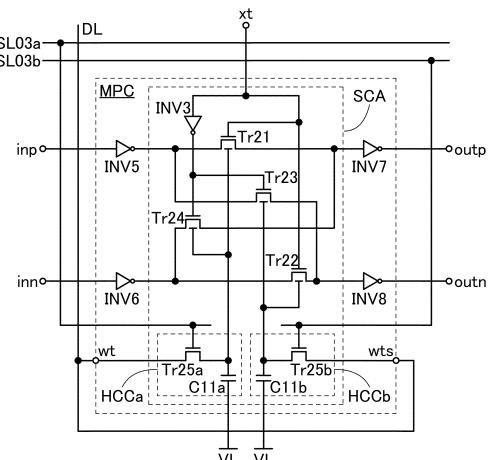

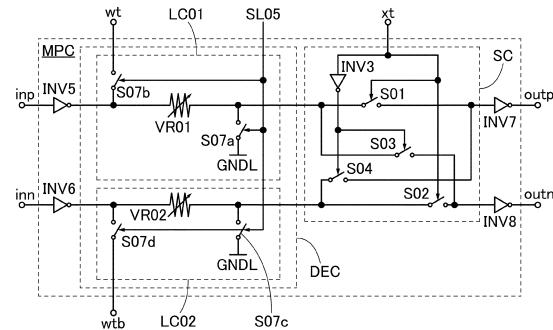

### 【0255】

また、例えば、図13(A)の回路MPCの配線の接続を変更してもよい。図14に示す回路MPCは図13(A)の回路MPCの配線の電気的な接続を変更した構成となっており、保持部HCCaのトランジスタTr25aのゲートには配線SL03aが電気的に接続され、保持部HCCbのトランジスタTr25bのゲートには配線SL03bが電気的に接続され、端子wt及び端子wtsには配線DLが電気的に接続されている。つまり、図14の回路MPCは、図13(A)の回路MPCの配線DLaと配線DLbとを共有し、配線SL03を配線SL03aと配線SL03bとに分けた構成となっている。図14の回路MPCの保持部HCCa、保持部HCCbのそれぞれに異なる電位を書き込む場合、端子wt及び端子wtsには配線DLが電気的に接続されているため、同時に書き込むことはできない。そのため、図14の回路MPCは、配線SL03aと配線SL03bとによって、トランジスタTr25a又はトランジスタTr25bの一方をオン状態にし、他方をオフ状態にして、保持部HCCa又は保持部HCCbの一方に配線DLの電位を書き込む構成となっている。

10

20

### 【0256】

<<演算動作>>

次に、図13(A)の回路MPCを図1の演算回路110に適用した場合の動作例について説明する。本動作例では、図1の演算回路110の回路MPC[i]について着目して説明する。なお、実施の形態1の説明と内容が重複する箇所については、省略する。

### 【0257】

初期動作として、端子xtには、信号xi(k-1)に相当する電位が入力される。これによって、トランジスタTr21乃至トランジスタTr24のそれぞれは、信号xi(k-1)に相当する電位に応じて、オン状態又はオフ状態となる。

30

### 【0258】

また、配線DLaは端子wtに対して重み係数wi(k-1)j(k)に相当する電位を入力し、配線DLbは端子wtsに対して中間電位を入力する。その後、配線SL03に高レベル電位を印加して、トランジスタTr25a、及びトランジスタTr25bをオン状態にする。この動作によって、容量素子C11aの第1端子に重み係数wi(k-1)j(k)に相当する電位が書き込まれ、容量素子C11bの第1端子に中間電位が書き込まれる。このため、トランジスタTr21及びトランジスタTr24のしきい値電圧は、重み係数wi(k-1)j(k)に応じて変動し、トランジスタTr22及びトランジスタTr23のしきい値電圧は、中間電位に応じて変動する。最後に、配線SL03に低レベル電位を印加して、トランジスタTr25a、及びトランジスタTr25bをオフ状態することによって、容量素子C11aの第1端子及び容量素子C11bの第1端子のそれぞれの電位を保持することができる。

40

### 【0259】

初期動作の後に、回路MPC[i](ここでのiは1以上m以下の整数とする。)の端子inpに信号Sp[i-1]、また端子innに信号Sn[i-1]が入力されることで、回路MPC[i]において演算動作が開始される。特に、iが1である場合、信号Sp[0]、Sn[0]のそれぞれは、時間差がほぼ無く(ほぼ同時に)、回路MPC[1]の端子inp、端子innに入力されるものとする。また、iが2以上であるとき、信号Sp[i-1]、Sn[i-1]は、回路MPC[i-1]から出力されているため、

50

互いに時間差が生じていることがある。なお、演算動作の説明では、便宜的に、信号  $S_p[i - 1]$ 、 $S_n[i - 1]$  は、時間差がほぼ無く（ほぼ同時に）、回路  $MPC[i]$  の端子  $i_{np}$ 、端子  $i_{nn}$  に入力されるものとする。

#### 【0260】

##### 〔条件1〕

重み係数  $w_i(k-1)j(k)$  に相当する電位が高レベル電位であり、かつ信号  $x_i(k-1)$  に相当する電位が高レベル電位である場合を考える。

#### 【0261】

このとき、トランジスタ  $T_{r21}$  及びトランジスタ  $T_{r22}$  のそれぞれがオン状態となり、トランジスタ  $T_{r23}$  及びトランジスタ  $T_{r24}$  のそれぞれがオフ状態となるため、インバータ回路  $INV5$  の出力端子とインバータ回路  $INV7$  の入力端子との間が導通状態となり、かつインバータ回路  $INV6$  の出力端子とインバータ回路  $INV8$  の入力端子との間が導通状態となる。10

#### 【0262】

また、トランジスタ  $T_{r21}$  のバックゲートには高レベル電位が印加され、トランジスタ  $T_{r22}$  のバックゲートには中間電位が印加されているため、トランジスタ  $T_{r21}$  のソース - ドレイン間の電流量は、トランジスタ  $T_{r22}$  のソース - ドレイン間の電流量よりも大きくなる。そのため、インバータ回路  $INV5$  の出力端子からインバータ回路  $INV7$  の入力端子への信号の伝達速度は、インバータ回路  $INV6$  の出力端子からインバータ回路  $INV8$  の入力端子への信号の伝達速度よりも速くなる。したがって、端子  $i_{np}$  及び端子  $i_{nn}$  に同時に信号が入力された場合、端子  $i_{np}$  に入力された信号が先に端子  $out_p$  に出力され、端子  $i_{nn}$  に入力された信号はその後に端子  $out_n$  に出力される。20

#### 【0263】

端子  $out_p$  からの出力信号は、端子  $out_n$  からの出力信号よりも早く出力されるため、本条件における回路  $MPC[i]$  のタイミングチャートは図7(A)のタイミングチャートと同様にみなすことができる。時刻  $T_2$  に端子  $out_p$  の電位が高レベル電位となり、その後の時刻  $T_3$  に端子  $out_n$  の電位が高レベル電位となる。つまり、時刻  $T_2$  に端子  $out_p$  から出力信号として  $S_p[i]$  が出力され、時刻  $T_3$  に端子  $out_n$  から出力信号として  $S_n[i]$  が出力される。

#### 【0264】

##### 〔条件2〕

また、重み係数  $w_i(k-1)j(k)$  に相当する電位が低レベル電位であり、かつ信号  $x_i(k-1)$  に相当する電位が高レベル電位である場合を考える。

#### 【0265】

このとき、トランジスタ  $T_{r21}$  及びトランジスタ  $T_{r22}$  のそれぞれがオン状態となり、トランジスタ  $T_{r23}$  及びトランジスタ  $T_{r24}$  のそれぞれがオフ状態となるため、インバータ回路  $INV5$  の出力端子とインバータ回路  $INV7$  の入力端子との間が導通状態となり、かつインバータ回路  $INV6$  の出力端子とインバータ回路  $INV8$  の入力端子との間が導通状態となる。30

#### 【0266】

また、トランジスタ  $T_{r21}$  のバックゲートには低レベル電位が印加され、トランジスタ  $T_{r22}$  のバックゲートには中間電位が印加されているため、トランジスタ  $T_{r21}$  のソース - ドレイン間の電流量は、トランジスタ  $T_{r22}$  のソース - ドレイン間の電流量よりも小さくなる。そのため、インバータ回路  $INV5$  の出力端子からインバータ回路  $INV7$  の入力端子への信号の伝達速度は、インバータ回路  $INV6$  の出力端子からインバータ回路  $INV8$  の入力端子への信号の伝達速度よりも遅くなる。したがって、端子  $i_{np}$  及び端子  $i_{nn}$  に同時に信号が入力された場合、端子  $i_{nn}$  に入力された信号が先に端子  $out_n$  に出力され、端子  $i_{np}$  に入力された信号はその後に端子  $out_p$  に出力される。40

#### 【0267】

端子  $out_p$  からの出力信号は、端子  $out_n$  からの出力信号よりも遅く出力されるた

50

め、本条件における回路MPC[i]のタイミングチャートは図7(B)のタイミングチャートと同様にみなすことができる。時刻T3に端子outnの電位が高レベル電位となり、その後の時刻T4に端子outpの電位が高レベル電位となる。つまり、時刻T3に端子outnから出力信号としてSn[i]が出力され、時刻T4に端子outpから出力信号としてSp[i]が出力される。

#### 【0268】

##### [条件3]

また、重み係数 $w_{i(k-1)}j(k)$ に相当する電位が高レベル電位であり、かつ信号 $x_{i(k-1)}$ に相当する電位が低レベル電位である場合を考える。

#### 【0269】

このとき、トランジスタTr21及びトランジスタTr22のそれぞれがオフ状態となり、トランジスタTr23及びトランジスタTr24のそれぞれがオン状態となるため、インバータ回路INV5の出力端子とインバータ回路INV8の入力端子との間が導通状態となり、かつインバータ回路INV6の出力端子とインバータ回路INV7の入力端子との間が導通状態となる。

#### 【0270】

また、トランジスタTr24のバックゲートには高レベル電位が印加され、トランジスタTr23のバックゲートには中間電位が印加されているため、トランジスタTr24のソース-ドレイン間の電流量は、トランジスタTr23のソース-ドレイン間の電流量よりも大きくなる。そのため、インバータ回路INV6の出力端子からインバータ回路INV7の入力端子への信号の伝達速度は、インバータ回路INV5の出力端子からインバータ回路INV8の入力端子への信号の伝達速度よりも速くなる。したがって、端子inp及び端子innに同時に信号が入力された場合、端子innに入力された信号が先に端子outpに出力され、端子inpに入力された信号はその後に端子outnに出力される。

#### 【0271】

端子outpからの出力信号は、端子outnからの出力信号よりも遅く出力されるため、本条件における回路MPC[i]のタイミングチャートは図7(C)のタイミングチャートと同様にみなすことができる。時刻T2に端子outnの電位が高レベル電位となり、その後の時刻T3に端子outpの電位が高レベル電位となる。つまり、時刻T2に端子outnから出力信号としてSn[i]が出力され、時刻T3に端子outpから出力信号としてSp[i]が出力される。

#### 【0272】

##### [条件4]

また、重み係数 $w_{i(k-1)}j(k)$ に相当する電位が低レベル電位であり、かつ信号 $x_{i(k-1)}$ に相当する電位が低レベル電位である場合を考える。

#### 【0273】

このとき、トランジスタTr21及びトランジスタTr22のそれぞれがオフ状態となり、トランジスタTr23及びトランジスタTr24のそれぞれがオン状態となるため、インバータ回路INV5の出力端子とインバータ回路INV8の入力端子との間が導通状態となり、かつインバータ回路INV6の出力端子とインバータ回路INV7の入力端子との間が導通状態となる。

#### 【0274】

また、トランジスタTr24のバックゲートには低レベル電位が印加され、トランジスタTr23のバックゲートには中間電位が印加されているため、トランジスタTr24のソース-ドレイン間の電流量は、トランジスタTr23のソース-ドレイン間の電流量よりも小さくなる。そのため、インバータ回路INV6の出力端子からインバータ回路INV7の入力端子への信号の伝達速度は、インバータ回路INV5の出力端子からインバータ回路INV8の入力端子への信号の伝達速度よりも遅くなる。したがって、端子inp及び端子innに同時に信号が入力された場合、端子inpに入力された信号が先に端子outnに出力され、端子innに入力された信号はその後に端子outpに出力される。

10

20

30

40

50

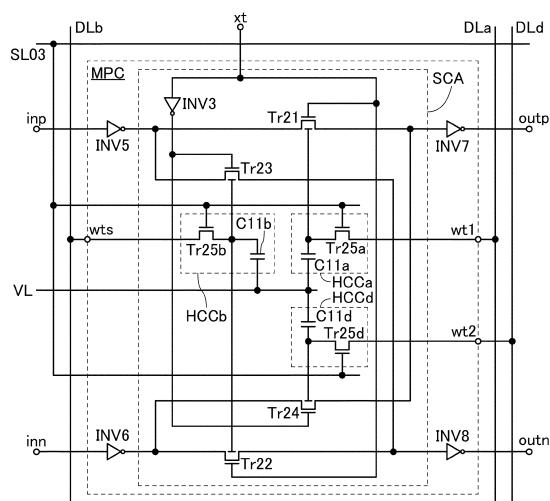

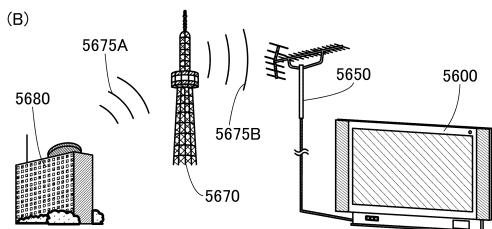

### 【0275】