【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第2区分

【発行日】平成17年9月2日(2005.9.2)

【公開番号】特開2002-215118(P2002-215118A)

【公開日】平成14年7月31日(2002.7.31)

【出願番号】特願2001-296176(P2001-296176)

【国際特許分類第7版】

G 0 9 G 3/36

G 0 2 F 1/133

G 0 2 F 1/1368

G 0 9 G 3/20

G 1 1 C 19/00

H 0 3 K 5/15

H 0 3 K 23/54

【F I】

G 0 9 G 3/36

G 0 2 F 1/133 5 5 0

G 0 2 F 1/1368

G 0 9 G 3/20 6 2 2 E

G 0 9 G 3/20 6 2 3 H

G 1 1 C 19/00 J

H 0 3 K 23/54 B

H 0 3 K 5/15 P

【手続補正書】

【提出日】平成17年3月7日(2005.3.7)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

基板面にシフトレジスタを含む駆動回路を備え、前記シフトレジスタは多結晶シリコンを半導体層とするMIS TFTから構成され、

第1のMIS TFTの第1の端子は入力パルスに接続され、第1のMIS TFTのゲート端子は第1の同期パルスに接続されて、入力部を形成し、

第1のMIS TFTの第2の端子は、第2のMIS TFTのゲート端子及び第4のMIS TFTの第1の端子に接続し、かつ第1の容量素子の第1の端子と接続し、

第1の容量の第2の端子は固定電圧に接続しており、第2のMIS TFTの第1の端子は第1の同期パルスと逆相をなす第2の同期パルスに接続し、

第2のMIS TFTの第2の端子は、第3のMIS TFTの第1の端子及びゲート端子に接続しており、かつ第2の容量の第1の端子と接続し、

第2の容量の第2の端子は、第1のMIS TFTの第2の端子、第2のMISFETのゲート端子及び第4のMIS TFTの第1の端子に接続しており、

第3のMIS TFTの第2の端子は、第5のMIS TFTのゲート端子及び第7のMIS TFTの第1の端子に接続し、かつ第3の容量素子の第1の端子と接続するとともに第1の出力端子を形成し、

第3の容量の第2の端子は固定電圧に接続しており、第5のMIS TFTの第1の端子

は第1の同期パルスに接続し、

第5のMISFTの第2の端子は、第6のMISFTの第1の端子及びゲート端子及び第4のMISFTのゲート端子に接続しており、かつ第4の容量の第1の端子と接続するとともに第2の出力端子を形成し、

第4の容量の第2の端子は第3のMISFTの第2の端子、第5のMISFTのゲート端子及び第7のMISFTの第1の端子に接続しており、

第4のMISFTの第2の端子及び第7のMISFTの第2の端子は固定電源に接続しており、

第7のMISFTのゲート端子には前記第4のMISFTのゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする表示装置。

#### 【請求項2】

第2から第7までのMISFTと第1から第4までの容量から構成される基本回路がn個多段に接続され、

第i番目の基本回路の第2のMISFTに対応するMISFTのゲート端子には、第(i-1)番目の基本回路の第6のMISFTに対応するMISFTの第2の端子に接続され、

第i番目の基本回路の第7のMISFTに対応するMISFTのゲート端子には、第(i+1)番目の第2のMISFTに対応するMISFTの第2の端子に接続され、

第n番目の基本回路の第7のMISFTに対応するMISFTのゲート端子には次段の基本回路の第4のMISFTのゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする請求項1に記載の表示装置。

#### 【請求項3】

第1番目の基本回路に第二のMISFTが、第2番目以降に各基本回路に第一のMISFTおよび第二のMISFTが組み込まれ、

第一のMISFTは、そのゲート端子が入力パルスの入力端子に接続され、第1の端子が第2のMISFTに対応するMISFTのゲート端子に接続され、第2の端子が第1、第2の同期パルスの電圧のうちMISFTのソース電圧となる電圧に等しいか、または少なくとも第4のMISFTのしきい値電圧以上に第1、第2の同期パルスのソース電圧となる電圧と異なることのない固定電源または接地電位に接続され、

第二のMISFTは、そのゲート端子が入力パルスの入力端子に接続され、第1の端子が第5のMISFTあるいはこの第5のMISFTに対応するMISFTのゲート端子に接続され、第2の端子が第1、第2の同期パルスの電圧のうちMISFTのソース電圧となる電圧に等しいか、または少なくとも第4のMISFTのしきい値電圧以上に第1、第2の同期パルスのソース電圧となる電圧と異なることのない固定電源または接地電位に接続されていることを特徴とする請求項2に記載の表示装置。

#### 【請求項4】

基板面にシフトレジスタを含む駆動回路を備え、前記シフトレジスタは多結晶シリコンを半導体層とするMISFTから構成され、

第1のMISFTの第1の端子及びゲート端子は入力パルスに接続されて、入力部を形成し、

第1のMISFTの第2の端子は、第2のMISFTのゲート端子及び第4のMISFTの第1の端子に接続し、かつ第1の容量素子の第1の端子と接続し、

第1の容量の第2の端子は固定電圧に接続しており、第2のMISFTの第1の端子は第1の同期パルスと逆相をなす第2の同期パルスに接続し、

第2のMISFTの第2の端子は、第3のMISFTの第1の端子及びゲート端子に接続しており、

かつ第2の容量の第1の端子と接続し、第2の容量の第2の端子は、第1のMISFT

Tの第2の端子、第2のMISFETのゲート端子及び第4のMISFTの第1の端子に接続しており、

第3のMISFTの第2の端子は、第5のMISFTのゲート端子及び第7のMISFTの第1の端子に接続し、かつ第3の容量素子の第1の端子と接続するとともに第1の出力端子を形成し、

第3の容量の第2の端子は固定電圧に接続しており、第5のMISFTの第1の端子は第1の同期パルスに接続し、

第5のMISFTの第2の端子は、第6のMISFTの第1の端子及びゲート端子及び第4のMISFTのゲート端子に接続しており、かつ第4の容量の第1の端子と接続するとともに第2の出力端子を形成し、

第4の容量の第2の端子は第3のMISFTの第2の端子、第5のMISFTのゲート端子及び第7のMISFTの第1の端子に接続しており、

第4のMISFTの第2の端子及び第7のMISFTの第2の端子は固定電源に接続しており、

第7のMISFTのゲート端子には前記第4のMISFTのゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする表示装置。

#### 【請求項5】

第2から第7までのMISFTと第1から第4までの容量から構成される基本回路がn個多段に接続され、

第i番目の基本回路の第2のMISFTに対応するMISFTのゲート端子には、第(i-1)番目の基本回路の第6のMISFTに対応するMISFTの第2の端子に接続され、

第i番目の基本回路の第7のMISFTに対応するMISFTのゲート端子には、第(i+1)番目の第2のMISFTに対応するMISFTの第2の端子に接続され、

第n番目の基本回路の第7のMISFTに対応するMISFTのゲート端子には次段の基本回路の第4のMISFTのゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする請求項4に記載の表示装置。

#### 【請求項6】

第一番目の基本回路に第二のMISFTが、第二番目以降に各基本回路に第一のMISFTおよび第二のMISFTが組み込まれ、

第一のMISFTは、そのゲート端子が入力パルスの入力端子に接続され、第1の端子が第2のMISFTに対応するMISFTのゲート端子に接続され、第2の端子が第1、第2の同期パルスの電圧のうちMISFTのソース電圧となる電圧に等しいか、または少なくとも第4のMISFTのしきい値電圧以上に第1、第2の同期パルスのソース電圧となる電圧と異なることのない固定電源または接地電位に接続され、

第二のMISFTは、そのゲート端子が入力パルスの入力端子に接続され、第1の端子が第5のMISFTあるいはこの第5のMISFTに対応するMISFTのゲート端子に接続され、第2の端子が第1、第2の同期パルスの電圧のうちMISFTのソース電圧となる電圧に等しいか、または少なくとも第4のMISFTのしきい値電圧以上に第1、第2の同期パルスのソース電圧となる電圧と異なることのない固定電源または接地電位に接続されていることを特徴とする請求項5に記載の表示装置。

#### 【請求項7】

基板面にシフトレジスタを含む駆動回路を備え、前記シフトレジスタは多結晶シリコンを半導体層とするMISFTから構成され、

第1のMISFTの第1の端子及びゲート端子は入力パルスに接続されて、入力部を形成し、

第1のMISFTの第2の端子は、第2のMISFTのゲート端子及び第4のMISFT

S T F T の第 1 の端子に接続し、かつ第 1 の容量を介して、固定電圧に接続しており、

第 2 の M I S T F T の第 1 の端子は、第 1 の同期パルスと逆相をなす第 2 の同期パルスに接続し、

第 2 の M I S T F T の第 2 の端子は、第 3 の M I S T F T の第 1 の端子及びゲート端子に接続しており、かつ第 2 の容量を介して、第 1 の M I S T F T の第 2 の端子、第 2 の M I S T F T のゲート端子及び第 4 の M I S T F T の第 1 の端子に接続しており、

第 3 の M I S T F T の第 2 の端子は、第 5 の M I S T F T のゲート端子及び第 7 の M I S T F T の第 1 の端子に接続し、かつ第 3 の容量素子を介して、固定電圧に接続しており、

第 5 の M I S T F T の第 1 の端子は第 1 の同期パルスに接続し、

第 5 の M I S T F T の第 1 の端子は、第 6 の M I S T F T の第 1 の端子及びゲート端子及び第 4 の M I S T F T のゲート端子に接続しており、かつ第 4 の容量を介して、第 3 の M I S T F T の第 2 の端子、第 5 の M I S T F T のゲート端子及び第 7 の M I S T F T の第 1 の端子に接続しており、

第 4 の M I S T F T の第 2 の端子は固定電源に接続しており、

第 7 の M I S T F T のゲート端子には前記第 4 の M I S T F T のゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする表示装置。

#### 【請求項 8】

第 2 から第 1 1 までの M I S T F T と第 1 、第 2 の容量から構成される基本回路が n 個多段に接続され、

第 i 番目の基本回路の第 2 の M I S T F T に対応する M I S T F T のゲート端子には、第 ( i - 1 ) 番目基本回路の第 1 0 の M I S T F T に対応する M I S T F T の第 2 の端子に接続され、

第 i 番目の基本回路の第 8 の M I S T F T に対応する M I S T F T のゲート端子及び第 7 の M I S T F T に対応する M I S T F T の第 1 の端子に、第 ( i + 1 ) 番目の基本回路の第 6 の M I S T F T に対応する M I S T F T の第 2 の端子に接続され、

第 n 番目の基本回路の第 8 の M I S T F T に対応する M I S T F T のゲート端子及び第 7 の M I S T F T に対応する M I S T F T の第 1 の端子には、前記第 1 4 の M I S T F T のゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする請求項 7 に記載の表示装置。

#### 【請求項 9】

基板面にシフトレジスタを含む駆動回路を備え、前記シフトレジスタは多結晶シリコンを半導体層とする M I S T F T から構成され、

第 1 の M I S T F T の第 1 の端子は入力パルスに接続され、

第 1 の M I S T F T のゲート端子は、第 1 の同期パルスに接続されて、入力部を形成し、

第 1 の M I S T F T の第 2 の端子は、第 4 の M I S T F T のゲート端子及び第 3 の M I S T F T の第 1 の端子に接続し、かつ第 1 の容量の第 1 の端子に接続し、

第 1 の容量の第 2 の端子は第 4 の M I S T F T の第 2 の端子、第 5 の M I S T F T の第 1 の端子及びゲート端子及び第 6 の M I S T F T の第 1 の端子及びゲート端子と接続し、かつ第 7 の M I S T F T のゲート端子と接続しており、

第 2 の M I S T F T のゲート端子は入力パルスに接続され、第 2 の M I S T F T の第 1 の端子は、第 1 1 の M I S T F T の第 2 の端子及び第 3 の M I S T F T のゲート端子に接続し、

第 2 の M I S T F T の第 2 の端子および第 7 の M I S T F T の第 2 の端子は、固定電源に接続しており、

第 3 の M I S T F T の第 2 の端子は、固定電源に接続しており、

第 4 の M I S T F T の第 1 の端子は、第 2 の同期パルスに接続し、

第 5 の M I S T F T の第 2 の端子は第 9 の M I S T F T のゲート端子及び第 8 の M I S

TFT の第 1 の端子に接続し、かつ、第 2 の容量の第 1 の端子に接続し、

第 2 の容量の第 2 の端子は、第 9 の M I S T F T の第 2 の端子及び第 10 の M I S T F T の第 1 の端子及びゲート端子及び第 11 の M I S T F T の第 1 の端子及びゲート端子に接続し、

第 7 の M I S T F T の第 1 の端子は第 8 の M I S T F T のゲート端子に接続し、

第 8 の M I S T F T の第 2 の端子は、固定電源に接続しており、

第 9 の M I S T F T の第 1 の端子は第 1 の同期パルスに接続し、

第 8 の M I S T F T のゲート端子には前記第 3 の M I S T F T のゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする表示装置。

#### 【請求項 10】

第 2、3、4、5、7、8、9、10 の各 M I S T F T と、第 1 および第 2 の容量から構成される基本回路が n 個多段に接続され、

第 i 番目の基本回路の第 10 の M I S T F T に対応する M I S T F T の第 2 の端子が第 (i - 1) 番目の基本回路の第 4 の M I S T F T に対応する M I S T F T のゲート端子に接続され、

第 i 番目の基本回路の第 7 の M I S T F T に対応する M I S T F T の第 2 の端子、第 3 の M I S T F T に対応する M I S T F T のゲート端子が第 (i + 1) 番目の基本回路の第 1 の容量に対応する容量に第 6 の M I S T F T を介して接続され、

該第 6 の M I S T F T の第 2 の端子は M I S T F T の第 2 の端子、第 3 の M I S T F T に対応する M I S T F T のゲート端子に接続され、第 1 の端子及びゲート端子は前記容量に接続されていることを特徴とする請求項 9 に記載の表示装置。

#### 【請求項 11】

第 2 番目からの各基本回路において、第 1 の端子及びゲート端子が入力パルスに接続された第一の M I S T F T の第 2 の端子が第 11 の M I S T F T に対応する M I S T F T の第 2 の端子に接続され、

第 3 番目からの各基本回路において、第 1 の端子及びゲート端子が入力パルスに接続された第二の M I S T F T の第 2 の端子が、該基本回路の前段の基本回路の第 8 の M I S T F T に対応する M I S T F T のゲート端子に接続され、かつ、第 1 の容量に対応する容量の第 2 の端子に M I S T F T を介して接続され、

該 M I S T F T の第 2 の端子は第二の M I S T F T の第 2 の端子に接続され、第 1 の端子及びゲート端子は前記容量に接続されていることを特徴とする請求項 10 に記載の表示装置。

#### 【請求項 12】

基板面にシフトレジスタを含む駆動回路を備え、前記シフトレジスタは多結晶シリコンを半導体層とする M I S T F T から構成され、

第 1 の M I S T F T の第 1 の端子及びゲート端子は入力パルスに接続されて、入力部を形成し、

第 1 の M I S T F T の第 2 の端子は、第 4 の M I S T F T のゲート端子及び第 3 の M I S T F T の第 1 の端子に接続し、かつ第 1 の容量の第 1 の端子に接続し、

第 1 の容量の第 2 の端子は第 4 の M I S T F T の第 2 の端子、第 5 の M I S T F T の第 1 の端子及びゲート端子及び第 6 の M I S T F T の第 1 の端子及びゲート端子と接続し、かつ第 7 の M I S T F T のゲート端子と接続しており、

第 2 の M I S T F T のゲート端子は入力パルスに接続され、

第 2 の M I S T F T の第 1 の端子は、第 11 の M I S T F T の第 2 の端子及び第 3 の M I S T F T のゲート端子に接続し、

第 2 の M I S T F T の第 2 の端子および第 7 の M I S T F T の第 2 の端子は、固定電源に接続しており、

第 3 の M I S T F T の第 2 の端子は、固定電源に接続しており、

第 4 の M I S T F T の第 1 の端子は、第 2 の同期パルスに接続し、

第5のMISFTの第2の端子は第9のMISFTのゲート端子及び第8のMISFTの第1の端子に接続し、かつ、第2の容量の第1の端子に接続し、

第2の容量の第2の端子は、第9のMISFTの第2の端子及び第10のMISFTの第1の端子及びゲート端子及び第11のMISFTの第1の端子及びゲート端子に接続し、

第7のMISFTの第1の端子は第8のMISFTのゲート端子に接続し、

第8のMISFTの第2の端子は、固定電源に接続してあり、

第9のMISFTの第1の端子は第1の同期パルスに接続し、

第8のMISFTのゲート端子には前記第3のMISFTのゲート端子に入力されるパルスに相当するパルスで一クロック分シフトされるパルスが入力されることを特徴とする表示装置。

#### 【請求項13】

第2、3、4、5、7、8、9、10の各MISFTと、第1および第2の容量から構成される基本回路がn個多段に接続され、

第i番目の基本回路の第10のMISFTに対応するMISFTの第2の端子が第(i-1)番目の基本回路の第4のMISFTに対応するMISFTのゲート端子に接続され、

第i番目の基本回路の第7のMISFTに対応するMISFTの第2の端子、第3のMISFTに対応するMISFTのゲート端子が第(i+1)番目の基本回路の第1の容量に対応する容量に第6のMISFTを介して接続され、

該第6のMISFTの第2の端子はMISFTの第2の端子、第3のMISFTに対応するMISFTのゲート端子に接続され、第1の端子及びゲート端子は前記容量に接続されていることを特徴とする請求項12に記載の表示装置。

#### 【請求項14】

第2番目からの各基本回路において、第1の端子及びゲート端子が入力パルスに接続された第一のMISFTの第2の端子が第11のMISFTに対応するMISFTの第2の端子に接続され、

第3番目からの各基本回路において、第1の端子及びゲート端子が入力パルスに接続された第二のMISFTの第2の端子が、該基本回路の前段の基本回路の第8のMISFTに対応するMISFTのゲート端子に接続され、かつ、第1の容量に対応する容量の第2の端子にMISFTを介して接続され、

該MISFTの第2の端子は第二のMISFTの第2の端子に接続され、第1の端子及びゲート端子は前記容量に接続されていることを特徴とする請求項13に記載の表示装置。

#### 【請求項15】

基板面にシフトレジスタを含む表示駆動回路を備え、

前記シフトレジスタは、半導体層を有するトランジスタから構成されているとともに、

前記トランジスタはゲート端子と第1の端子と第2の端子を有し、

前記第1の端子には同期パルスが入力し、

前記ゲート端子の電圧は、ブーストストラップ効果により前記ゲート端子がフローティング状態の場合に、前記同期パルスがロウレベルからハイレベルに変化することに従い上昇し、

前記トランジスタをオン状態とする信号の入力により、前記ゲート端子のブーストストラップ効率を向上させることを特徴とする表示装置。

#### 【請求項16】

基板面にシフトレジスタを含む表示駆動回路を備え、

前記シフトレジスタは、半導体層を有するトランジスタから構成されているとともに、

前記トランジスタはゲート端子と第1の端子と第2の端子を有し、

前記第1の端子には同期パルスが入力し、

前記ゲート端子の電圧は、ブーストストラップ容量により前記ゲート端子がフローティン

グ状態の場合に、前記同期パルスがロウレベルからハイレベルに変化することに従い上昇し、

前記トランジスタをオン状態とする信号の入力により、前記ゲート端子に接続されたポートストラップ容量が増加することを特徴とする表示装置。

【請求項 1 7】

基板面にシフトレジスタを含む表示駆動回路を備え、

前記シフトレジスタは、半導体層を有する第1のトランジスタと第2のトランジスタから構成されているとともに、

前記第1のトランジスタはゲート端子と第1の端子と第2の端子を有し、

前記第1のトランジスタの第1の端子には同期パルスが入力し、

前記第1のトランジスタのゲート端子の電圧は、前記ゲート端子がフローティング状態の場合に、前記同期パルスがロウレベルからハイレベルに変化することに従い上昇し、

前記第2のトランジスタはオン状態で前記第1のトランジスタのゲート端子と電圧線とを接続し、

前記第1のトランジスタをオン状態とする信号の入力により、前記第2のトランジスタはオフ状態となることを特徴とする表示装置。

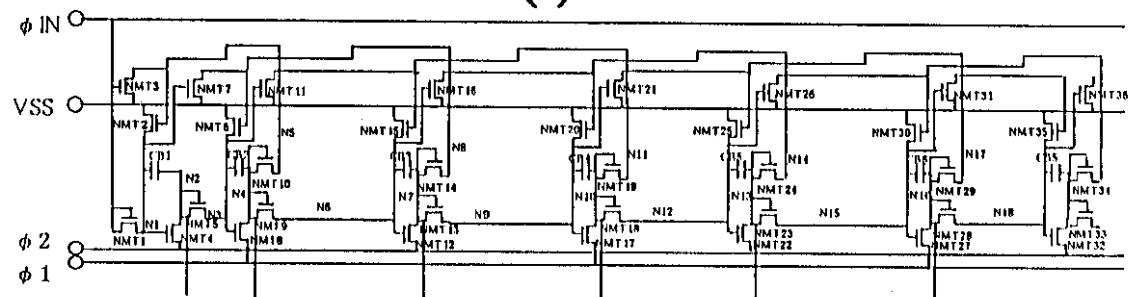

【手続補正 2】

【補正対象書類名】図面

【補正対象項目名】図 1

【補正方法】変更

【補正の内容】

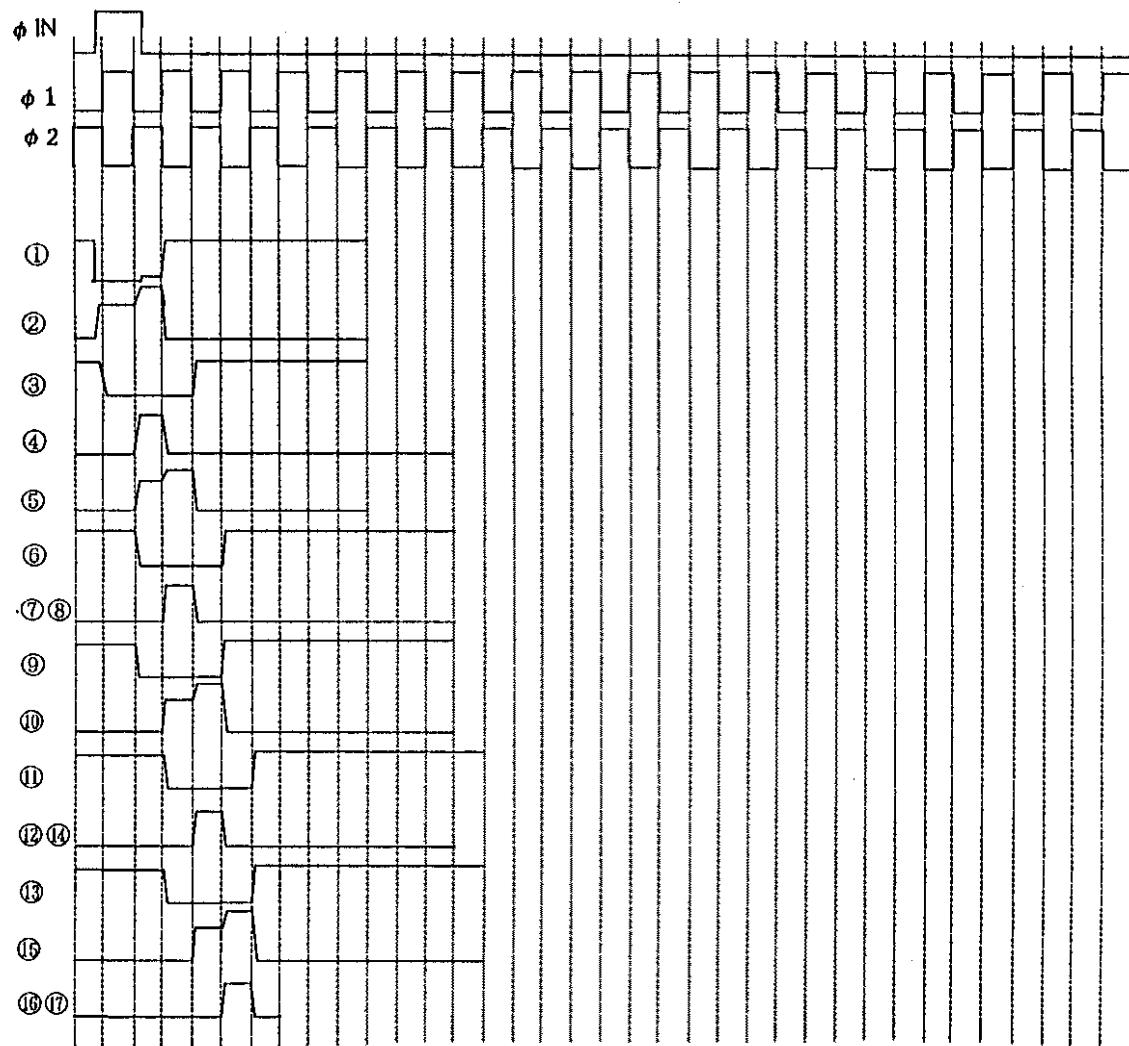

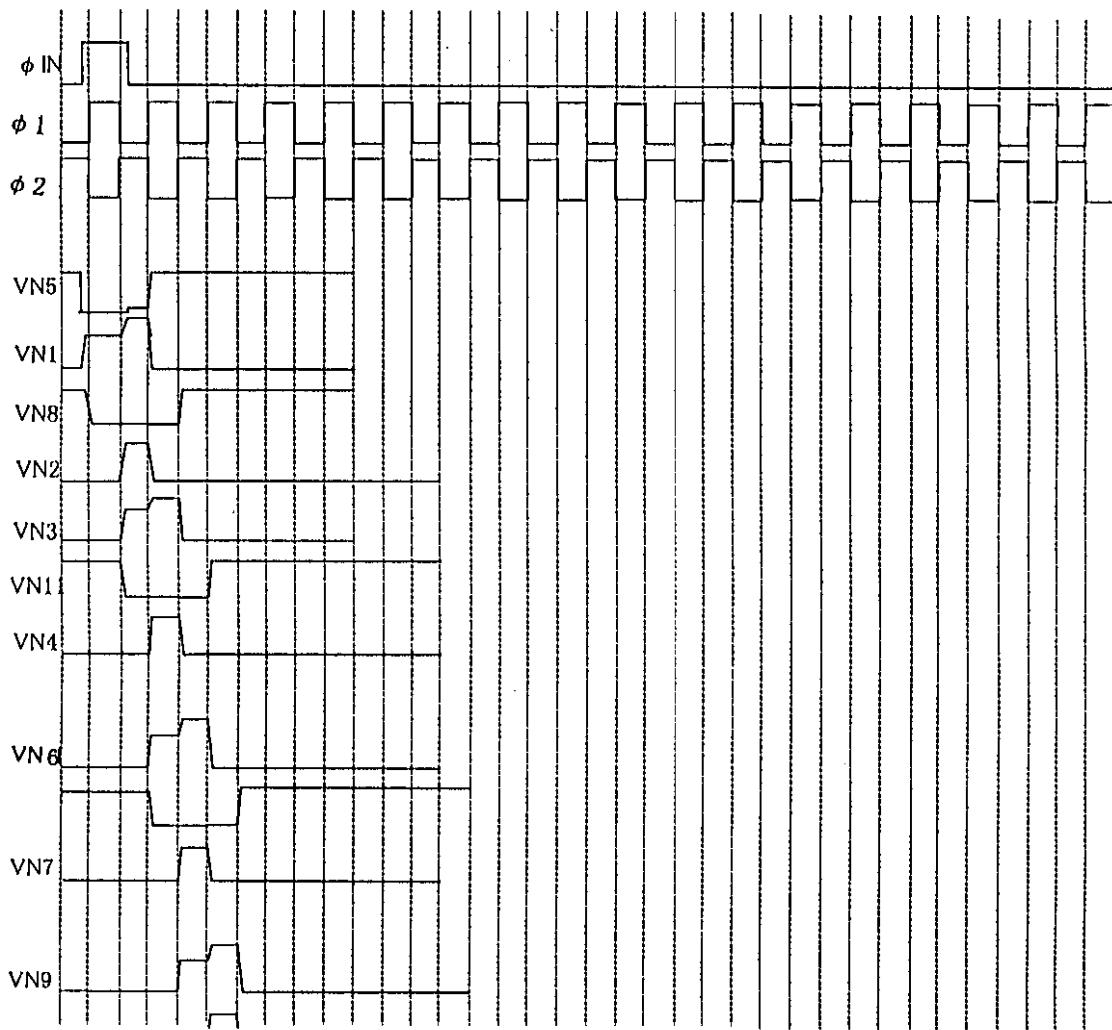

【図1】

## 図1

(a)

(b)

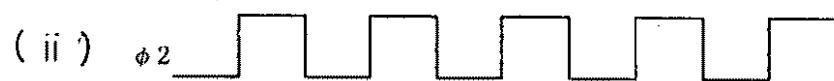

【手続補正3】

【補正対象書類名】図面

【補正対象項目名】図6

【補正方法】変更

【補正の内容】

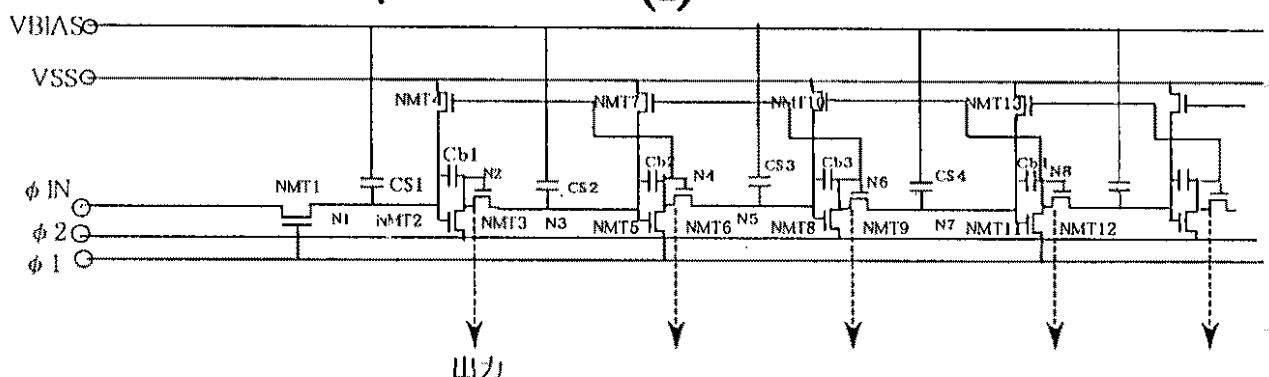

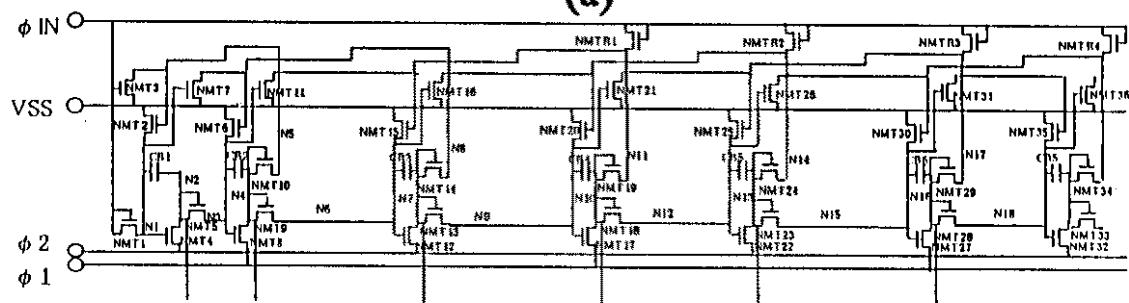

【図6】

図6

(a)

(b)

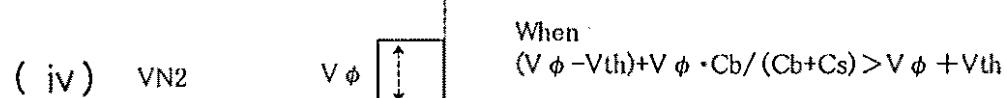

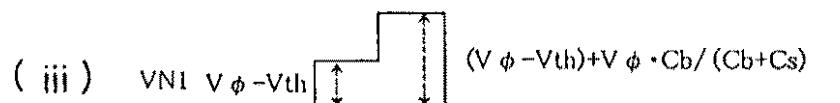

【手続補正4】

【補正対象書類名】図面

【補正対象項目名】図7

【補正方法】変更

【補正の内容】

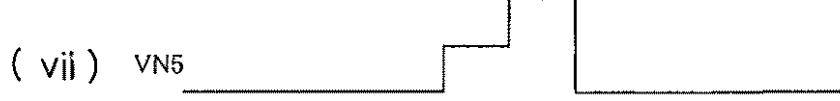

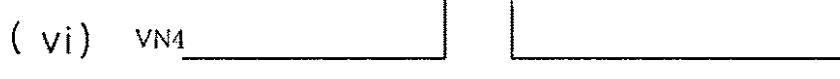

【図7】

☒ 7

(a)

(b)