(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-303032

(P2005-303032A)

(43) 公開日 平成17年10月27日(2005.10.27)

(51) Int.Cl.<sup>7</sup>H01L 29/866

// GO1R 31/26

F 1

H01L 29/90

GO1R 31/26

テーマコード(参考)

2G003

C

審査請求 未請求 請求項の数 5 O L (全 16 頁)

(21) 出願番号

特願2004-117629 (P2004-117629)

(22) 出願日

平成16年4月13日 (2004.4.13)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 清水 和彦

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者 佐藤 隆史

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

F ターム(参考) 2G003 AA05 AB04 AH05

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

**【課題】** ツエナーダイオードにおけるツエナー電圧の測定精製度を向上させることのできる技術を提供する。

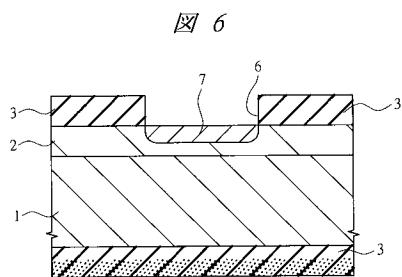

**【解決手段】** フォトレジスト膜をマスクとしたスピニングエッチング法により酸化シリコン膜3をエッチングすることにより、酸化シリコン膜3をn型高濃度基板1の裏面に残しつつn型低濃度層2の表面の酸化シリコン膜3に開口部6を選択的に形成した後、開口部6内を含むn型低濃度層2上にドーピング材料を塗布し、n型高濃度基板1をアニールすることによってp型拡散層7を形成する。その後、不純物を取り込んだn型高濃度基板1の裏面の酸化シリコン膜3を除去する。

【選択図】 図6

図 6

1 : n型高濃度基板(半導体基板)

2 : n型低濃度層(第1半導体層)

3 : 酸化シリコン膜(第1絶縁膜)

6 : 開口部

7 : p型拡散層(第2半導体層)

## 【特許請求の範囲】

## 【請求項 1】

- (a) 第1導電型の半導体基板上に第1導電型の第1半導体層を形成する工程、

(b) 前記第1半導体層の存在下で、前記第1半導体層上および前記半導体基板の裏面に第1絶縁膜を形成する工程、

(c) 前記第1絶縁膜を選択的にエッティングし、前記第1半導体層上の前記第1絶縁膜に前記第1半導体層に達する開口部を形成し、前記半導体基板の前記裏面の前記第1絶縁膜を残す工程、

(d) 前記(c)工程後、前記開口部内を含む前記第1半導体層上の前記第1絶縁膜上に不純物導入材料を配置する工程、

(e) 前記不純物導入材料の存在下で前記半導体基板に熱処理を施すことにより、前記開口部から前記第1半導体層に第2導電型の不純物を導入し、前記開口部の底部にて前記第1半導体層の表面に第2導電型の第2半導体層を形成し、前記半導体基板と前記第1半導体層と前記第2半導体層とを備えた半導体素子を形成する工程、

(f) 前記(e)工程後、前記半導体基板の前記裏面の前記第1絶縁膜を除去する工程、

(g) 前記(f)工程後、前記半導体素子の特性を検査する工程、

を含み、

前記(g)工程において所望の特性が得られなかった場合には、

- (h) 前記半導体基板に熱処理を施した後に前記(g)工程を再度実施する工程、

を前記所望の特性が得られるまで繰り返すことを特徴とする半導体装置の製造方法。

## 【請求項 2】

- (a) 第1導電型の半導体基板上に第1導電型の第1半導体層を形成する工程、

(b) 前記第1半導体層の存在下で、前記第1半導体層上および前記半導体基板の裏面に第1絶縁膜を形成する工程、

(c) 前記第1絶縁膜を選択的にエッティングし、前記第1半導体層上の前記第1絶縁膜に前記第1半導体層に達する開口部を形成し、前記半導体基板の前記裏面の前記第1絶縁膜を残す工程、

(d) 前記(c)工程後、前記開口部内を含む前記第1半導体層上の前記第1絶縁膜上に不純物導入材料を配置する工程、

(e) 前記不純物導入材料の存在下で前記半導体基板に熱処理を施すことにより、前記開口部から前記第1半導体層に第2導電型の不純物を導入し、前記開口部の底部にて前記第1半導体層の表面に第2導電型の第2半導体層を形成し、前記半導体基板と前記第1半導体層と前記第2半導体層とを備えた半導体素子を形成する工程、

(f) 前記(e)工程後、前記半導体基板の前記裏面の前記第1絶縁膜を除去する工程、

(g) 前記(f)工程後、前記半導体素子の特性を検査する工程、

を含み、

前記(g)工程において所望の特性が得られなかった場合には、

- (h) 前記半導体基板に熱処理を施した後に前記(g)工程を再度実施する工程、

を前記所望の特性が得られるまで繰り返し、

前記(c)工程において、前記開口部はスピンドルエッティング法にて形成することを特徴とする半導体装置の製造方法。

## 【請求項 3】

- (a) 第1導電型の半導体基板上に第1導電型の第1半導体層を形成する工程、

(b) 前記第1半導体層の存在下で、前記第1半導体層上および前記半導体基板の裏面に第1絶縁膜を形成する工程、

(c) 前記第1絶縁膜を選択的にエッティングし、前記第1半導体層上の前記第1絶縁膜に前記第1半導体層に達する開口部を形成し、前記半導体基板の前記裏面の前記第1絶縁膜を残す工程、

(d) 前記(c)工程後、前記開口部内を含む前記第1半導体層上の前記第1絶縁膜上に不純物導入材料を配置する工程、

10

20

30

40

50

(e) 前記不純物導入材料の存在下で前記半導体基板に熱処理を施すことにより、前記開口部から前記第1半導体層に第2導電型の不純物を導入し、前記開口部の底部にて前記第1半導体層の表面に第2導電型の第2半導体層を形成し、前記半導体基板と前記第1半導体層と前記第2半導体層とを備えた半導体素子を形成する工程、

(f) 前記(e)工程後、前記半導体基板の前記裏面の前記第1絶縁膜を除去する工程、

(g) 前記(f)工程後、前記半導体素子の特性を検査する工程、

を含み、

前記(g)工程において所望の特性が得られなかった場合には、

(h) 前記半導体基板に熱処理を施した後に前記(g)工程を再度実施する工程、

を前記所望の特性が得られるまで繰り返し、

前記(c)工程において、前記開口部はドライエッティング法にて形成することを特徴とする半導体装置の製造方法。

#### 【請求項4】

(a) 第1導電型の半導体基板上に第1導電型の第1半導体層を形成する工程、

(b) 前記第1半導体層の存在下で、前記第1半導体層上に第1絶縁膜を形成する工程、

(c) 前記第1絶縁膜を選択的にエッティングし、前記第1半導体層上の前記第1絶縁膜に前記第1半導体層に達する開口部を形成する工程、

(d) 前記(c)工程後、前記開口部内を含む前記第1半導体層上の前記第1絶縁膜上に不純物導入材料を配置する工程、

(e) 前記不純物導入材料の存在下で前記半導体基板に熱処理を施すことにより、前記開口部から前記第1半導体層に第2導電型の不純物を導入し、前記開口部の底部にて前記第1半導体層の表面に第2導電型の第2半導体層を形成し、前記半導体基板と前記第1半導体層と前記第2半導体層とを備えた半導体素子を形成する工程、

(f) 前記(e)工程後、前記半導体基板を裏面から第1の厚さだけエッティングする工程、

(g) 前記(f)工程後、前記半導体素子の特性を検査する工程、

を含み、

前記(g)工程において所望の特性が得られなかった場合には、

(h) 前記半導体基板に熱処理を施した後に前記(g)工程を再度実施する工程、

を前記所望の特性が得られるまで繰り返すことを特徴とする半導体装置の製造方法。

#### 【請求項5】

(a) 第1導電型の半導体基板上に第1導電型の第1半導体層を形成する工程、

(b) 前記第1半導体層の存在下で、前記第1半導体層上および前記半導体基板の裏面に第1絶縁膜を形成する工程、

(c) 前記第1半導体層上の前記第1絶縁膜上に第1マスキング層を形成し、前記半導体基板の前記裏面の前記第1絶縁膜上に第2マスキング層を形成する工程、

(d) 前記第1マスキング層および前記第2マスキング層をマスクとして前記第1絶縁膜を選択的にエッティングし、前記第1半導体層上の前記第1絶縁膜に前記第1半導体層に達する開口部を形成し、前記半導体基板の前記裏面の前記第1絶縁膜を残す工程、

(e) 前記(d)工程後、前記第1マスキング層および前記第2マスキング層を除去し、前記開口部内を含む前記第1半導体層上の前記第1絶縁膜上に不純物導入材料を配置する工程、

(f) 前記不純物導入材料の存在下で前記半導体基板に熱処理を施すことにより、前記開口部から前記第1半導体層に第2導電型の不純物を導入し、前記開口部の底部にて前記第1半導体層の表面に第2導電型の第2半導体層を形成し、前記半導体基板と前記第1半導体層と前記第2半導体層とを備えた半導体素子を形成する工程、

(g) 前記(f)工程後、前記半導体基板の前記裏面の前記第1絶縁膜を除去する工程、

(h) 前記(g)工程後、前記半導体素子の特性を検査する工程、

を含み、

前記(h)工程において所望の特性が得られなかった場合には、

10 20 30 40 50

(i) 前記半導体基板に熱処理を施した後に前記(h)工程を再度実施する工程、を前記所望の特性が得られるまで繰り返すことを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、ツェナーダイオードの製造に適用して有効な技術に関するものである。

【背景技術】

【0002】

近年のネットワーク技術の普及により、様々な電子機器がネットワークを介して接続できるようになっている。たとえば、パソコン、プリンタ、ゲーム機器、携帯電話などの電子機器は、他の電子機器との接続用にコネクタが設けられており、このコネクタにケーブルを差込むことにより他の電子機器と接続する構成をしている。このコネクタは、ケーブルと接続していない場合、導電部が剥き出しの状態になっている。そのため、たとえば静電気を帯電した人体が、剥き出しのコネクタに触ると人体に蓄積された静電気（たとえばサージ電圧）による放電が起こり、電子機器内部にあるLSIなどの故障や誤動作を引き起こす虞がある。従って、通常電子機器には、内部のLSIなどを外部からのノイズであるサージ電圧から保護するため、サージ吸収用ツェナーダイオードを使用したサージ保護回路が設けられている。このツェナーダイオードは、コネクタ端子とグランド（接地）との間に設けられており、サージ電圧が外部から印加された場合であっても、内部のLSIなどには、ツェナー電圧以上の電圧が印加されないようになっている。

【0003】

ツェナーダイオードを製造する技術については、たとえば特開2003-209265号公報（特許文献1）に記載されている。

【特許文献1】特開2003-209265号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

たとえば、ツェナー電圧が約6V以上であるツェナーダイオードの主特性（ツェナー電圧）は、半導体基板（半導体ウエハ）に導入した不純物の拡散によって決定している。ツェナー電圧を決定するには、たとえばツェナー電圧を測定する工程と、半導体基板に導入した不純物を拡散する工程とを目標としているツェナー電圧が得られるまで繰り返すことによって行われる。不純物を拡散する際に、複数の半導体基板を一括して処理するバッチ式の装置を用いると、半導体基板の裏面に他の半導体基板上に配置した不純物導入材料から飛び出した不純物が導入され、pn構造であるべき半導体層が、たとえばpnp構造あるいはnpn構造となってしまい、ツェナー電圧の測定値の絶対値にふらつきを生じてしまう原因となる。また、ツェナーダイオードは、主特性であるツェナー電圧の規格幅が非常に狭く、また対象となる品種が多岐に渡ることから、そのようなふらつきが発生した場合には品種毎の特性の制御が困難になってしまう課題が存在する。

【0005】

また、ツェナーダイオードが作り出される半導体基板のロット毎に、先行して1枚の半導体基板に対して上記不純物の拡散工程とツェナー電圧を測定する工程とを行った際に、目標としているツェナー電圧が得られなかった場合でも、その原因が実際にツェナー電圧に起因するものなのか上記ふらつきに起因するものなのかの判別が困難になる。そのため、同じロットの半導体基板から多くの不良品となるツェナーダイオードを作り出してしまう課題が存在する。

【0006】

また、上記のようにpn構造であるべき半導体層がpnp構造あるいはnpn構造となってしまった場合には、半導体基板の抵抗成分が大きくなってしまうことから、ツェナー

10

20

20

30

40

50

電圧を測定する測定機器を検査対象となる半導体基板毎に調整する必要が生じ、ツェナー電圧の測定作業が自動化できなくなってしまう課題が存在する。

#### 【0007】

本発明の目的は、ツェナーダイオードにおけるツェナー電圧の測定精度を向上させることのできる技術を提供することにある。

#### 【0008】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0009】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0010】

本発明による半導体装置の製造方法は、

- (a) 第1導電型の半導体基板上に第1導電型の第1半導体層を形成する工程、

- (b) 前記第1半導体層の存在下で、前記第1半導体層上および前記半導体基板の裏面に第1絶縁膜を形成する工程、

- (c) 前記第1絶縁膜を選択的にエッチングし、前記第1半導体層上の前記第1絶縁膜に前記第1半導体層に達する開口部を形成し、前記半導体基板の前記裏面の前記第1絶縁膜を残す工程、

- (d) 前記(c)工程後、前記開口部内を含む前記第1半導体層上の前記第1絶縁膜上に不純物導入材料を配置する工程、

- (e) 前記不純物導入材料の存在下で前記半導体基板に熱処理を施すことにより、前記開口部から前記第1半導体層に第2導電型の不純物を導入し、前記開口部の底部にて前記第1半導体層の表面に第2導電型の第2半導体層を形成し、前記半導体基板と前記第1半導体層と前記第2半導体層とを備えた半導体素子を形成する工程、

- (f) 前記(e)工程後、前記半導体基板の前記裏面の前記第1絶縁膜を除去する工程、

- (g) 前記(f)工程後、前記半導体素子の特性を検査する工程、

を含み、

前記(g)工程において所望の特性が得られなかった場合には、

- (h) 前記半導体基板に熱処理を施した後に前記(g)工程を再度実施する工程、

を前記所望の特性が得られるまで繰り返すものである。

#### 【発明の効果】

#### 【0011】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

#### 【0012】

すなわち、ツェナーダイオードが形成される半導体基板において、p n p構造あるいはn p n構造が形成されてしまうことを防ぐことができるので、ツェナーダイオードにおけるツェナー電圧の測定精度を向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

#### 【0014】

##### (実施の形態1)

本実施の形態1の半導体装置は、ツェナーダイオードを含むものである。この本実施の形態1の半導体装置の製造工程について図1～図19を用いて説明する。

#### 【0015】

10

20

30

40

50

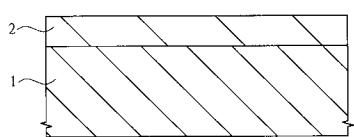

まず、n型（第1導電型）不純物（たとえばSb（アンチモン））が高濃度でドープされたSi（シリコン）からなるウエハ状のn型高濃度基板（半導体基板）1を用意する。このn型高濃度基板1にドープされたn型不純物の濃度は、たとえば $1 \times 10^{19}$ 個/cm<sup>3</sup>～ $1 \times 10^{20}$ 個/cm<sup>3</sup>程度とすることを例示できる。

## 【0016】

続いて、n型高濃度基板1の主面上にn型不純物（たとえばP（リン））がドープされたn型のSi層をエピタキシャル成長させることにより、n型低濃度層（第1半導体層）2を形成する。このn型低濃度層2は、抵抗率が約100Ωcm以上であり、その厚さは、たとえば約15μm程度とし、ドープされたn型不純物の濃度は、 $1 \times 10^{16}$ 個/cm<sup>3</sup>～ $1 \times 10^{19}$ 個/cm<sup>3</sup>程度とすることを例示できる。

10

## 【0017】

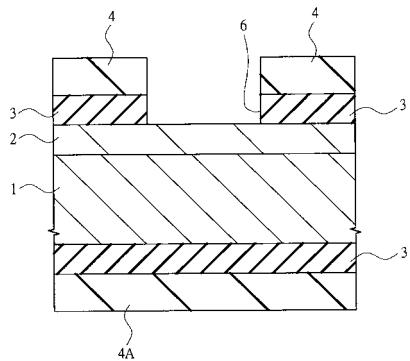

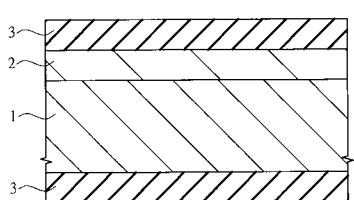

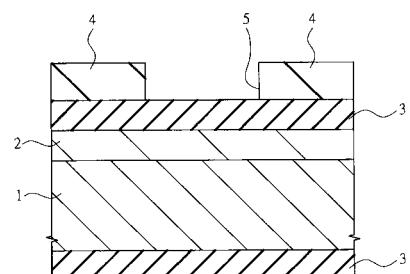

次に、図2に示すように、n型高濃度基板1に熱酸化処理を施し、n型低濃度層2の表面とn型高濃度基板1の裏面とに膜厚0.4μm～1μm程度の酸化シリコン膜（第1絶縁膜）3を形成する。

## 【0018】

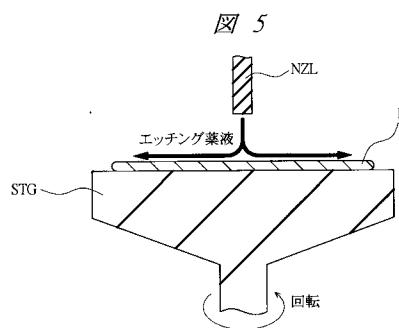

次に、図3に示すように、n型低濃度層2の表面の酸化シリコン膜3上にフォトレジスト膜（第1マスキング層）4を成膜し、このフォトレジスト膜4をフォトリソグラフィ技術によってパターニングし、開口部5を形成する。続いて、図4に示すように、そのフォトレジスト膜4をマスクとして酸化シリコン膜3をエッチングし、n型低濃度層2の表面の酸化シリコン膜3に次の工程において形成するp型拡散層を形成するための開口部6を選択的に形成する。本実施の形態1において、この開口部6を形成する時のエッチングは、スピナエッティング法とすることを例示することができる。すなわち、図5に示すように、n型低濃度層2（図5中の図示は省略）を上側とし、裏面がステージSTGと接するようにn型高濃度基板1をステージSTG上に配置した状態でステージSTGを回転させる。ステージSTGが回転している状況下で、ステージSTG上に配置されたノズルNZよりn型高濃度基板1へエッティング薬液（たとえばフッ酸）を滴下する。n型高濃度基板1へ滴下されたエッティング薬液は、ステージSTGの回転によってn型高濃度基板1の外周へと向かって流れる。それにより、フォトレジスト膜4をマスクとして酸化シリコン膜3をウエットエッティングし、開口部6を形成することができる。このようなスピナエッティング法によって開口部6を形成する場合には、n型高濃度基板1の裏面の酸化シリコン膜3がステージSTGと接することになるので、n型高濃度基板1の裏面の酸化シリコン膜3がエッティング液に曝されることを防ぐことができる。すなわち、開口部6の形成後においても酸化シリコン膜3をn型高濃度基板1の裏面に残すことができる。

20

30

40

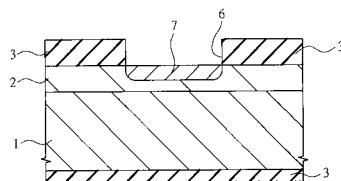

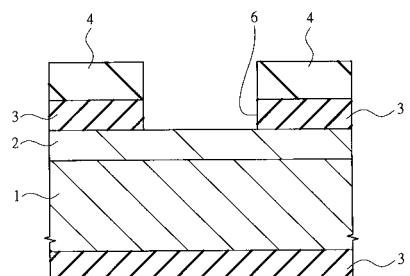

## 【0019】

次に、フォトレジスト膜4を除去した後、図6に示すように、開口部6内を含むn型低濃度層2上に、たとえばPBF（Poly Boron Film）などのドーピング材料を塗布する。続いて、約900°C程度の雰囲気中にてn型高濃度基板1をアニールすることにより、そのn型低濃度層2にp型（第2導電型）不純物であるB（ホウ素）をドーピングし、p型拡散層（第2半導体層）7を形成する。続いて、N<sub>2</sub>（窒素）雰囲気中において、n型高濃度基板1に約1000°C程度の熱処理を施すことにより、p型拡散層7とn型低濃度層2によるpn接合を形成し、ツェナーダイオード素子（半導体素子）を形成することができる。本実施の形態1においては、これらの熱処理は、複数枚のn型高濃度基板1に対して一括して処理を施すことのできるバッチ式の装置を用いて行う。このようなバッチ式の装置を用いた場合には、n型高濃度基板1は正面が他のn型高濃度基板1の裏面と向き合うように装置内に並べて配置される。そのような状況下で熱処理が施されることから、上記ドーピング材料から飛び出した不純物がn型低濃度層2へ導入されるばかりでなく、他のn型高濃度基板1の裏面へも導入されてしまうことになる。ここで、本実施の形態1においては、n型高濃度基板1の裏面には酸化シリコン膜3が形成されていることから、その飛び出した不純物をn型高濃度基板1の裏面の酸化シリコン膜3が取り込むことになる。なお、図6中に示したn型高濃度基板1の裏面の酸化シリコン膜3のうち、その不純物

50

物を取り込んだ部分を梨地模様のハッチングを付して示してある。

【0020】

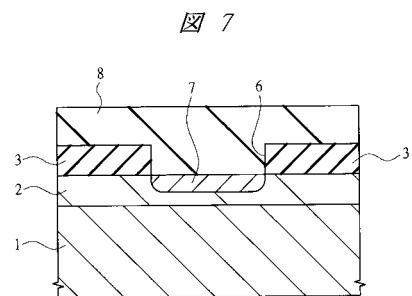

次に、図7に示すように、開口部6内を含むn型低濃度層2の表面の酸化シリコン膜3上にフォトレジスト膜8を成膜し、このフォトレジスト膜8をマスクとしてn型高濃度基板1の裏面の酸化シリコン膜3をフッ酸を用いたウェットエッチングにより除去する。これにより、n型高濃度基板1の裏面の酸化シリコン膜3が取り込んだ上記不純物についても同時に除去することができる。すなわち、p型拡散層7とn型低濃度層2とn型高濃度基板1とによるpn構造がpnp構造となってしまうことを防ぐことができる。

【0021】

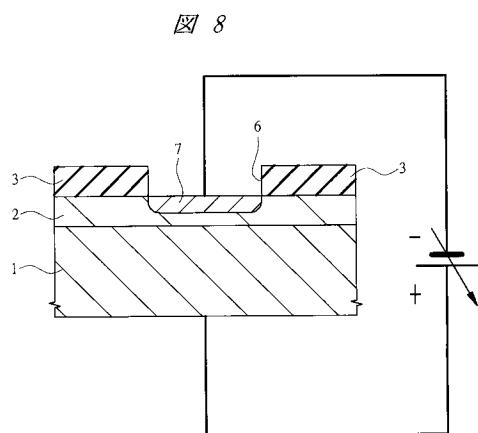

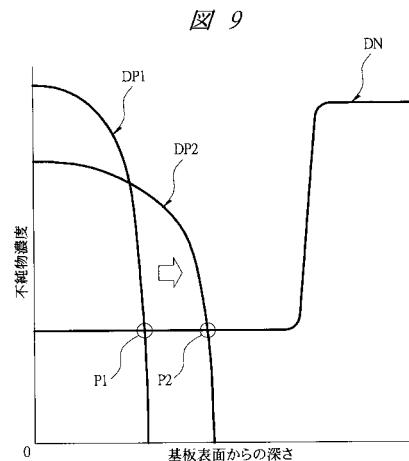

次に、上記フォトレジスト膜8を除去した後、図8に示すように、p型拡散層7とn型低濃度層2とn型高濃度基板1とによるツェナーダイオード素子に逆方向電圧を印加し、そのツェナーダイオード素子のツェナー電圧を測定する。ここで、図9は、本実施の形態1のn型高濃度基板1(n型低濃度層2を含む)の正面からの深さと、n型高濃度基板1に導入された不純物の濃度との関係を示したものであり、曲線DP1、DP2はp型拡散層7を形成するBの濃度を示し、曲線DNはn型高濃度基板1に含まれるSbの濃度を示している。本実施の形態1のツェナーダイオード素子のツェナー電圧は、曲線DP1と曲線DNとの交点P1、あるいは曲線DP2と曲線DNとの交点P2で決定されるものであり、この交点P1、P2の位置がn型高濃度基板1の正面から深くなるほどツェナー電圧は高くなる。本実施の形態1においては、たとえばp型拡散層7を形成するBが曲線DP1で示されるような濃度勾配を有し、交点P1で決定されるツェナー電圧が所望の電圧値より低かった場合には、n型高濃度基板1に1050～1100程度の熱処理を施す。それにより、n型高濃度基板1(n型低濃度層2)に導入されたBがさらにn型高濃度基板1中に拡散することから、Bはピーク濃度が低下する一方で、n型高濃度基板1のより深い位置まで拡散する。すなわち、曲線DP1で示されていたBの濃度勾配は、曲線DP2へと変化する。このような熱処理の後、再びツェナーダイオード素子のツェナー電圧を測定する。このようなツェナー電圧の測定および熱処理を所望のツェナー電圧が得られるまで繰り返す。

【0022】

前述したように、本実施の形態1においては、p型拡散層7とn型低濃度層2とn型高濃度基板1とによるpn構造が、n型高濃度基板1の裏面にp型不純物(B)が導入されてしまうことに起因してpnp構造となってしまうことを防ぐことができるので、ツェナー電圧の測定値の絶対値にふらつきを生じさせてしまうことを防ぐことができる。それにより、主特性であるツェナー電圧の規格幅が非常に狭く、品種が多岐に渡るツェナーダイオードにおいて、品種毎の特性の制御を容易にすることが可能となる。すなわち、ツェナーダイオードにおけるツェナー電圧の測定精度を向上することができる。

【0023】

また、ツェナー電圧の測定値の絶対値にふらつきを生じさせてしまうことを防ぐことができるので、ツェナーダイオードが作り出されるn型高濃度基板1のロット毎に、先行して1枚のn型高濃度基板1に対して上記熱処理およびツェナー電圧の測定を行った際に、所望のツェナー電圧が得られなかった場合には、その原因が実際にツェナー電圧に起因するものであると判断することが可能になる。それにより、同じロットのn型高濃度基板1から多くの不良品となるツェナーダイオードを作り出してしまうことを未然に防ぐことが可能となる。

【0024】

また、p型拡散層7とn型低濃度層2とn型高濃度基板1とによるpn構造となるべきものが、n型高濃度基板1の裏面にp型不純物(B)が導入されてしまうことに起因してpnp構造となってしまった場合には、n型高濃度基板1(p型拡散層7およびn型低濃度層2を含む)の正面と裏面との間での抵抗成分が大きくなってしまうことから、ツェナー電圧を測定する測定機器を検査対象となるn型高濃度基板1毎に調整する必要が生じ、ツェナー電圧の測定作業が自動化できなくなってしまう不具合が懸念される。一方、本実

10

20

30

40

50

施の形態 1 によれば、p n p 構造となってしまうことを防ぐことができるので、そのような不具合が発生することを防ぐことができる。

#### 【0025】

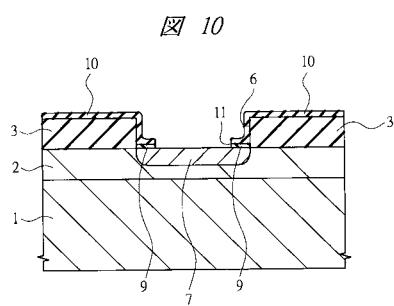

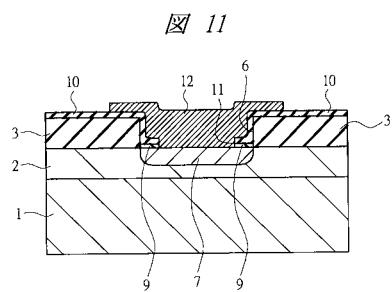

次に、図 10 に示すように、熱酸化法を用いて p 型拡散層 7 の表面に酸化膜 9 を形成する。続いて、開口部 6 内を含む酸化シリコン膜 3 上に酸化シリコン膜および P S G (Phospho Silicate Glass) 膜を順次堆積することにより、酸化シリコン膜と P S G 膜とからなる表面保護膜 10 を形成する。続いて、フォトレジスト膜(図示は省略)をマスクにして酸化膜 9 および表面保護膜 10 をエッティングし、p 型拡散層 7 に達するコンタクトホール 11 を形成する。

#### 【0026】

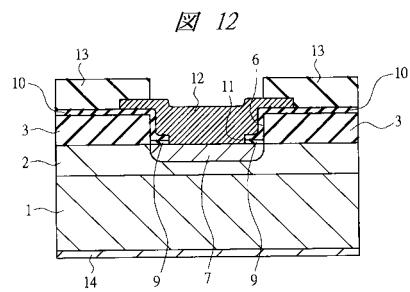

次に、図 11 に示すように、コンタクトホール 11 内を含む表面保護膜 10 上に、たとえばスパッタリング法を用いて Al (アルミニウム) と Si (シリコン) とからなる合金膜を堆積する。続いて、フォトレジスト膜(図示は省略)をマスクにして、その合金膜をエッティングすることにより、表面電極 12 を形成する。

#### 【0027】

次に、図 12 に示すように、n 型高濃度基板 1 上に窒化シリコン膜を堆積する。続いて、その窒化シリコン膜上に酸化シリコン膜を堆積し、酸化シリコン膜と酸化シリコン膜との積層膜からなる表面最終保護膜 13 を形成する。次いで、フォトレジスト膜(図示は省略)をマスクにして表面最終保護膜 13 をエッティングすることにより、表面電極 12 の表面を露出させる。

#### 【0028】

次に、n 型高濃度基板 1 の裏面をグラインディングにより研削し、後述するパッケージ形態に合わせて、n 型高濃度基板 1 を薄くする。続いて、たとえばスピニエッティング装置を用いたウェットエッティング法により、n 型高濃度基板 1 の裏面をエッティングする。

#### 【0029】

次に、n 型高濃度基板 1 を洗浄した後、たとえばスパッタリング法を用いて n 型高濃度基板 1 の裏面に Ag (銀) 膜を堆積する。続いて、たとえばスピニエッティング装置を用いてその Ag 膜をウェットエッティングし、裏面電極 14 を形成する。

#### 【0030】

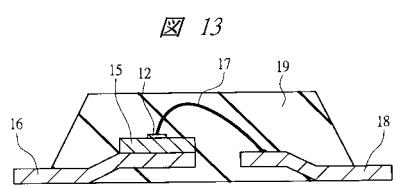

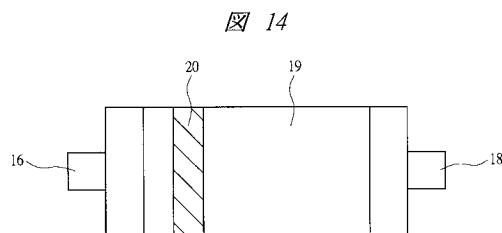

次に、n 型高濃度基板 1 をダイシングにより分割し、単位素子のツェナーダイオードを有するチップ 15 を形成する。続いて、個々のチップ 15 を封止樹脂により封止し、パッケージングする。このパッケージングにおいては、図 13 および図 14 に例示するように、リード 16 にチップ 15 が有する上記裏面電極 14 (図 13 中での図示は省略) を接続する。そして、表面電極 12 を、ボンディングワイヤ 17 を介してリード 18 と電気的に接続する。続いて、リード 16、18 の内端部、チップ 15 およびボンディングワイヤ 17 を封止樹脂 19 により封止することにより、リード 16、18 の外端部を実装用に外部に露出させたパッケージを形成する。この時、封止樹脂 19 の外周面には、カラーバンド等の極性識別マーク 20 が形成される。

#### 【0031】

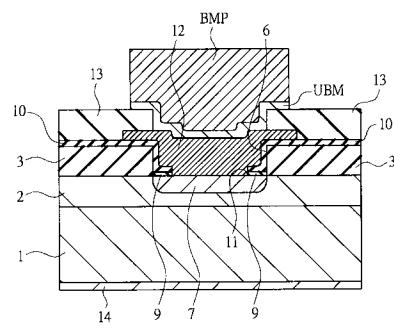

ところで、上記個々のチップ 15 は、ガラス封止体によって封止してもよい。その場合には、上記表面最終保護膜 13 を形成し、表面最終保護膜 13 に表面電極 12 に達する開口部を形成した後、図 15 に示すように、n 型高濃度基板 1 上に、たとえば Ti (チタン) 膜および Ni (ニッケル) 膜を下層から順次蒸着することにより、バンプ電極用下地膜 UBM を形成する。この際、ニッケル膜の代わりに Pd (パラジウム) 膜などを蒸着してもよい。続いて、バンプ電極用下地膜 UBM 上にフォトレジスト膜(図示は省略)を成膜し、そのフォトレジスト膜をフォトリソグラフィ技術によってパターニングすることによって、バンプ電極形成領域に対応する開口部を設ける。続いて、たとえばめっき法により Ni (ニッケル) 膜、Cu (銅) 膜または Ag (銀) 膜などをその開口部に堆積することによって、バンプ電極 B M P を形成する。続いて、バンプ電極 B M P の形成に用いたフォトレジスト膜を除去した後、たとえば水酸化カリウム溶液またはヨウ化アンモニウム溶液

10

20

30

40

50

を用いたウエットエッティングにより、バンプ電極BMPの下部のバンプ電極用下地膜UBMを残し、それ以外のバンプ電極用下地膜UBMを除去する。

#### 【0032】

次に、図12を用いて説明した工程と同様の工程に沿って、n型高濃度基板1の裏面を研削およびエッティングし、裏面電極14を形成し、n型高濃度基板1をダイシングにより分割し、単位素子のツェナーダイオードを有するチップ15を形成する。

#### 【0033】

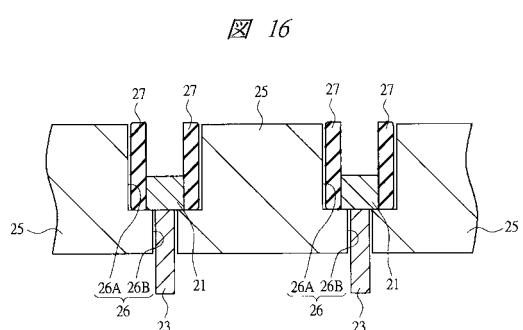

次に、図16に示すように、ジュメット電極形成用の比較的長いジュメット線を用意する。このジュメット線は、たとえばFe(鉄)およびNiを主成分とする合金から形成された円柱状の芯部と、その芯部の外周に形成されたCuを主成分とする被覆層とから形成されている。続いて、そのジュメット線を、たとえばダイヤモンドカッターなどを用いて所定の長さに切断し、ジュメット電極21、22を形成する。なお、ジュメット電極22については、後の工程で用いるため、図16中での図示は省略する。

#### 【0034】

次に、外部リード23をジュメット電極21の端面の中心位置またはその近傍に接続(溶接)し、外部リード24をジュメット電極22の端面の中心位置またはその近傍に接続(溶接)する。この外部リード23とジュメット電極21との接続、および外部リード24とジュメット電極22との接続には、たとえばアーク溶接法またはスポット溶接法などを適用することができる。また、ジュメット電極21、22形成用のジュメット線の断面に外部リード23(外部リード24)を接続(溶接)した後に、ジュメット線を切断して、外部リード23(外部リード24)が接続(溶接)されたジュメット電極21(ジュメット電極22)を形成することもできる。なお、外部リード24およびジュメット電極22については、外部リード23およびジュメット電極21とほぼ同様の構造となるので、図16中での図示は省略する。

#### 【0035】

次に、組立用治具25を用いてガラス封止を行う。組立用治具25の上面には、複数の円形の孔部26が格子状に設けられている。孔部26は、組立用治具25の上面に形成された相対的に大きな直径を有する孔部26Aと、孔部26Aの底部に形成された相対的に小さな直径を有する孔部26Bとからなる。上記のように外部リード23を接続したジュメット電極21を、組立用治具25の各孔部26内に、ジュメット電極21側を上に(外部リード23側を下に)向けて挿入する。孔部26Bの直径をジュメット電極21の直径よりも小さく、外部リード23の直径よりも大きくしておくことで、外部リード23だけが孔部26Bに挿入され、ジュメット電極21は孔部26Aの底部に固定される。

#### 【0036】

次に、ガラス封止体となるガラス管27を組立用治具25の孔部26(孔部26A)内に投入(挿入)して、ガラス管27の孔内にジュメット電極21を嵌め合わせる。あるいは、組立用治具25の孔部26内に先にガラス管27を投入した後に、孔部26(孔部26A)内に外部リード23を接続したジュメット電極21を投入し、ガラス管27の孔内にジュメット電極21を嵌め合わせてもよい。

#### 【0037】

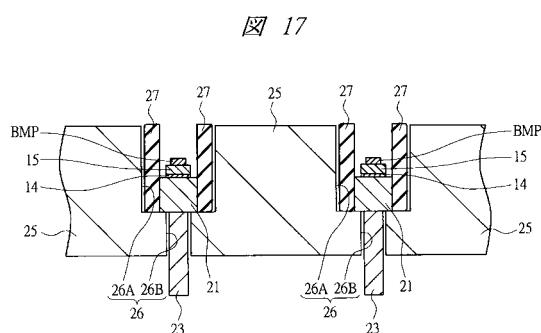

次に、図17に示されるように、組立用治具25の孔部26(孔部26A)内に、チップ15を投入する。これにより、チップ15が、ガラス管27の孔内のジュメット電極21上に配置される。この際、チップ15の正面(バンプ電極BMP形成側の面)または裏面(裏面電極14形成側の面)のいずれが上方を向いていもよい。

#### 【0038】

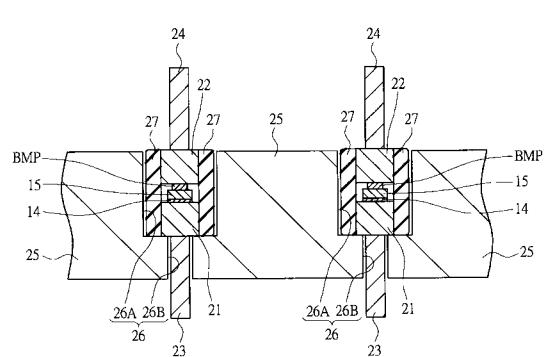

次に、図18に示すように、組立用治具25の孔部26(孔部26A)内に、外部リード24が接続されたジュメット電極22を、ジュメット電極22側を下に(外部リード24側を上に)向けて挿入(投入)する。これにより、ジュメット電極22はガラス管27の孔内に嵌め合わされる。チップ15は、ジュメット電極21、22により挟まれる。そして、必要に応じて加圧器具(図示は省略)を用いてジュメット電極22に対して荷重を

10

20

30

40

50

加えることにより、チップ 15 に対してジュメット電極 21、22 を押圧した状態とする。

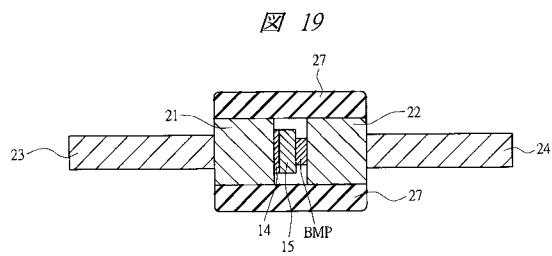

#### 【0039】

次に、ジュメット電極 21、22、チップ 15 およびガラス管 27 がセットされた組立用治具 25 をガラス封止用の加熱装置（図示は省略）に投入し、所定の温度で加熱する。これにより、ガラス管 27 が溶融して、ガラス管 27 がジュメット電極 21、22 の外周面に融着する。加熱の後、冷却されてガラス管 27 が硬化してガラス封止体となる。これにより、各部材が固定され、図 19 に示すようなツェナーダイオードのパッケージが製造される。ガラス封止体とジュメット電極 21、23 の外周とが接着されるので、ジュメット電極 21 とジュメット電極 22 との間に位置するチップ 15 は気密封止される。製造されたパッケージは、組立用治具 25 から取り出され、パッケージの極性を調べるための試験が行われ、パッケージのアノード側とカソード側とが判別され、必要に応じてマーキングが行われる。また、パッケージの配線基板への実装工程では、外部リード 23、24 が配線基板の配線パターンにはんだなどを介して接続される。

#### 【0040】

上記の本実施の形態 1 では、図 4 および図 5 を用いて説明したように、n 型高濃度基板 1 の裏面に酸化シリコン膜 3 を残しつつ、n 型高濃度基板 1 の正面（n 型低濃度層 2 の表面）の酸化シリコン膜 3 に開口部 6 を形成する際には、n 型低濃度層 2 を上側とし、裏面がステージ STG と接するように n 型高濃度基板 1 をステージ STG 上に配置した状況下でスピニエッティングを行うことを説明したが、同様に n 型高濃度基板 1 をステージ上に配置した状況下でドライエッティングを行うことにより、開口部 6 を形成してもよい。この場合には、酸化シリコン膜 3 と n 型低濃度層 2 とのエッティング選択比を十分に取れるようにエッティングガスを選択する。また、このようにドライエッティングによって開口部 6 を形成する手段は、p 型拡散層 7 と n 型低濃度層 2 とによる p-n 接合の位置が n 型高濃度基板 1 の正面（n 型低濃度層 2 の表面）からの深さが所定の深さ以上となる品種についてだけ適用する。これは、ドライエッティングのダメージにより、接合部が破壊もしくは半破壊状態となり、電流のリーク現象等の不具合が発生する可能性が極めて高いからである。

#### 【0041】

##### （実施の形態 2）

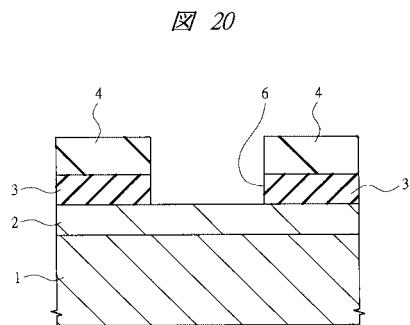

次に、本実施の形態 2 の半導体装置の製造工程について図 20 および図 21 を用いて説明する。

#### 【0042】

本実施の形態 2 の半導体装置の製造工程は、前記実施の形態 1 で図 3 を用いて説明した工程までは同様である。その後、たとえばエッティング薬液（たとえばフッ酸）が入った薬液槽（図示は省略）内へ n 型高濃度基板 1 を浸け込む。それにより、図 20 に示すように、n 型高濃度基板 1 の正面（n 型低濃度層 2 の表面）の酸化シリコン膜 3 にはウエットエッティングにより開口部 6 が形成され、n 型高濃度基板 1 の裏面の酸化シリコン膜 3 は除去される。

#### 【0043】

次に、図 21 に示すように、前記実施の形態 1 で図 6 を用いて説明した工程と同様の工程により p 型の不純物（たとえば B）を n 型低濃度層 2 に導入し、p 型拡散層 7 を形成する。この時、n 型高濃度基板 1 の裏面の酸化シリコン膜 3 は除去されていることから、n 型高濃度基板 1 の裏面にも不純物が導入され、所定の厚さ（第 1 の厚さ）の不純物含有層 1A が形成される。なお、図 21 中において、その不純物含有層 1A は梨地模様のハッチングを付して示してある。

#### 【0044】

続いて、正面をステージ STG へ向けて n 型高濃度基板 1 をステージ STG（図 5 参照）上に配置し、ノズル NZL（図 5 参照）より n 型高濃度基板 1 の裏面へ、たとえばフッ硝酸系のエッティング薬液を滴下しつつステージ STG を回転させる。それにより、不純物含有層 1A を除去することができる。この不純物含有層 1A を除去することにより、p 型

拡散層 7 と n 型低濃度層 2 と n 型高濃度基板 1 による p n 構造が p n p 構造となってしまうことを防ぐことができる。

#### 【0045】

その後、前記実施の形態 1 において図 8 ~ 図 19 を用いて説明した工程と同様の工程を経ることによって本実施の形態 2 の半導体装置を製造する。

#### 【0046】

上記のような本実施の形態 2 によっても、前記実施の形態 1 と同様の効果を得ることができる。

#### 【0047】

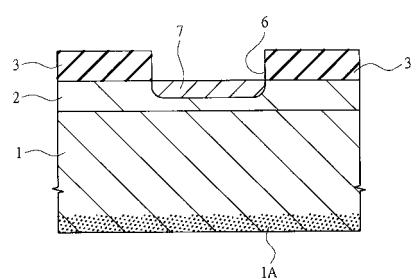

(実施の形態 3)

次に、本実施の形態 3 の半導体装置の製造工程について図 20 および図 22 を用いて説明する。

#### 【0048】

本実施の形態 3 の半導体装置の製造工程は、前記実施の形態 1 で図 3 を用いて説明した工程までは同様である。その後、図 22 に示すように、n 型高濃度基板 1 の裏面の酸化シリコン膜 3 上にフォトレジスト膜(第 2 マスキング層) 4 A を成膜することにより、n 型高濃度基板 1 の裏面の酸化シリコン膜 3 をフォトレジスト膜 4 A で覆う。

#### 【0049】

続いて、たとえばエッチング薬液(たとえばフッ酸)が入った薬液槽(図示は省略)内へ n 型高濃度基板 1 を浸け込む。それにより、酸化シリコン膜 3 を n 型高濃度基板 1 の裏面に残した状態で、n 型高濃度基板 1 の主面(n 型低濃度層 2 の表面)の酸化シリコン膜 3 にはウエットエッチングにより開口部 6 を形成することができる。

#### 【0050】

その後、フォトレジスト膜 4、4 A を除去した後、前記実施の形態 1 において図 6 ~ 図 19 を用いて説明した工程と同様の工程を経ることによって本実施の形態 3 の半導体装置を製造する。

#### 【0051】

上記のような本実施の形態 3 によっても、前記実施の形態 1 と同様の効果を得ることができます。

#### 【0052】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0053】

たとえば、前記実施の形態では、n 型高濃度基板の主面上に n 型低濃度層および p 型拡散層を形成することによって形成された p n 構造を形成する場合について説明したが、B が高濃度に導入された p 型高濃度基板の主面上に B が導入された p 型低濃度層および P が導入された n 型拡散層を形成することによって p n 構造を形成してもよい。この場合には、p 型高濃度基板に n p n 構造が形成されてしまうことを防ぐことができる。

#### 【0054】

また、前記実施の形態においては、ダイオードの裏面電極の材質が A g である場合について説明したが、A u(金)/S b/A u からなる多層膜であってもよい。

#### 【産業上の利用可能性】

#### 【0055】

本発明の半導体装置の製造方法は、たとえばツェナーダイオードを有する半導体装置の製造工程に適用することができる。

#### 【図面の簡単な説明】

#### 【0056】

【図 1】本発明の実施の形態 1 である半導体装置の製造工程を説明する要部断面図である。

10

20

30

40

50

【図2】図1に続く半導体装置の製造工程中の要部断面図である。

【図3】図2に続く半導体装置の製造工程中の要部断面図である。

【図4】図3に続く半導体装置の製造工程中の要部断面図である。

【図5】本発明の実施の形態1である半導体装置の製造工程におけるスピニエッチング工程を示す説明図である。

【図6】図4に続く半導体装置の製造工程中の要部断面図である。

【図7】図6に続く半導体装置の製造工程中の要部断面図である。

【図8】本発明の実施の形態1である半導体装置の製造工程における検査工程の説明図である。

【図9】本発明の実施の形態1である半導体装置が有するツェナーダイオードのツェナー電圧を決定する方法を示す説明図である。 10

【図10】図7に続く半導体装置の製造工程中の要部断面図である。

【図11】図10に続く半導体装置の製造工程中の要部断面図である。

【図12】図11に続く半導体装置の製造工程中の要部断面図である。

【図13】図12に続く半導体装置の製造工程中の要部断面図である。

【図14】本発明の実施の形態1である半導体装置の製造工程中の要部平面図である。

【図15】本発明の実施の形態1である半導体装置の製造工程中の要部断面図である。

【図16】本発明の実施の形態1である半導体装置の製造工程中の要部断面図である。

【図17】図16に続く半導体装置の製造工程中の要部断面図である。

【図18】図17に続く半導体装置の製造工程中の要部断面図である。 20

【図19】本発明の実施の形態1である半導体装置の製造工程中の要部断面図である。

【図20】本発明の実施の形態2である半導体装置の製造方法を説明する要部断面図である。

【図21】図20に続く半導体装置の製造工程中の要部断面図である。

【図22】本発明の実施の形態3である半導体装置の製造方法を説明する要部断面図である。

#### 【符号の説明】

##### 【0057】

- |    |                    |    |

|----|--------------------|----|

| 1  | n型高濃度基板(半導体基板)     |    |

| 1A | 不純物含有層             | 30 |

| 2  | n型低濃度層(第1半導体層)     |    |

| 3  | 酸化シリコン膜(第1絶縁膜)     |    |

| 4  | フォトレジスト膜(第1マスキング層) |    |

| 4A | フォトレジスト膜(第2マスキング層) |    |

| 5  | 開口部                |    |

| 6  | 開口部                |    |

| 7  | p型拡散層(第2半導体層)      |    |

| 8  | フォトレジスト膜           |    |

| 9  | 酸化膜                |    |

| 10 | 表面保護膜              | 40 |

| 11 | コンタクトホール           |    |

| 12 | 表面電極               |    |

| 13 | 表面最終保護膜            |    |

| 14 | 裏面電極               |    |

| 15 | チップ                |    |

| 16 | リード                |    |

| 17 | ボンディングワイヤ          |    |

| 18 | リード                |    |

| 19 | 封止樹脂               |    |

| 20 | 極性識別マーク            |    |

2 1、2 2 ジュメット電極

2 3、2 4 外部リード

2 5 組立用治具

2 6、2 6 A、2 6 B 孔部

2 7 ガラス管

B M P バンプ電極

D N、D P 1、D P 2 曲線

N Z L ノズル

S T G ステージ

U B M バンプ電極用下地膜

10

【図 1】

図 1

【図 2】

図 2

【図 3】

図 3

【図 4】

図 4

【図5】

【図6】

1: n型高濃度基板(半導体基板)

2: n型低濃度層(第1半導体層)

3: 酸化シリコン膜(第1絶縁膜)

6: 開口部

7: p型拡散層(第2半導体層)

【図8】

【図7】

【図9】

【図10】

【図12】

【図13】

【図11】

【図14】

【図16】

【図15】

【図17】

【図18】

【図20】

【図19】

【図21】

図21

【図22】

図22