(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-126255

(P2006-126255A)

(43) 公開日 平成18年5月18日(2006.5.18)

| (51) Int.C1.                 | F 1             | テーマコード (参考) |

|------------------------------|-----------------|-------------|

| <b>GO2F 1/1368 (2006.01)</b> | GO2F 1/1368     | 2H092       |

| <b>GO9F 9/00 (2006.01)</b>   | GO9F 9/00 338   | 5F033       |

| <b>HO1L 29/786 (2006.01)</b> | GO9F 9/00 342Z  | 5F110       |

| <b>HO1L 21/336 (2006.01)</b> | HO1L 29/78 619A | 5G435       |

| <b>HO1L 21/768 (2006.01)</b> | HO1L 29/78 612D |             |

審査請求 未請求 請求項の数 13 O L (全 25 頁) 最終頁に続く

|           |                              |          |                                                           |

|-----------|------------------------------|----------|-----------------------------------------------------------|

| (21) 出願番号 | 特願2004-310677 (P2004-310677) | (71) 出願人 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号                |

| (22) 出願日  | 平成16年10月26日 (2004.10.26)     | (74) 代理人 | 100089233<br>弁理士 吉田 茂明                                    |

|           |                              | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                                    |

|           |                              | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                                    |

|           |                              | (72) 発明者 | 村上 春美<br>熊本県菊池郡西合志町御代志997番地<br>メルコ・ディスプレイ・テクノロジー株式<br>会社内 |

最終頁に続く

(54) 【発明の名称】電気光学装置、液晶表示装置及びそれらの製造方法

## (57) 【要約】 (修正有)

【課題】電気光学装置において、層間絶縁膜のピンホールや欠陥に起因する電極間の短絡不良を防ぐ。

【解決手段】ゲート電極2、保持容量共通電極3、ゲート配線4、ゲート端子5、ソース電極9、ドレイン電極10、ソース配線11及びソース端子12といった第1の電極と、画素電極22、ゲート端子パッド23及びソース端子パッド24といった第2の電極とを絶縁する層間絶縁膜14, 18を、少なくとも二層以上で形成するとともに、この層間絶縁膜14, 18に形成されるコンタクトホールを少なくとも二回以上の工程によって形成する。層間絶縁膜14, 18にピンホールや欠損が発生しても、コンタクトホール以外での電極間の短絡不良を防止でき、歩留りを向上できる。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

下層にある少なくとも 1 種類以上の薄膜状の第 1 の電極と、前記第 1 の電極上に形成されてコンタクトホールが形成された絶縁膜と、前記コンタクトホールが設けられた前記絶縁膜上に薄膜状に形成されて少なくとも 1 種類以上の第 2 の電極とを備え、前記第 2 の電極の少なくとも一部が前記コンタクトホールを介して前記下層にある少なくとも 1 種類以上の前記第 1 の電極と電気的に接続される構造を少なくとも有する電気光学装置を製造する電気光学装置の製造方法であって、

前記絶縁膜を少なくとも二層以上で形成するとともに、前記絶縁膜に形成される前記コンタクトホールを少なくとも二回以上の工程によって形成することを特徴とする電気光学装置の製造方法。

## 【請求項 2】

a ) 絶縁性基板上に第 1 の導電性薄膜を成膜し、第 1 の写真製版工程を用いてゲート配線、ゲート電極、及びゲート端子を少なくとも形成する工程と、

b ) 第 1 の絶縁膜、半導体能動膜及びオーミックコンタクト膜を成膜し、第 2 の写真製版工程を用いて前記半導体能動膜と前記オーミックコンタクト膜をパターニングする工程と、

c ) 第 2 の導電性薄膜を成膜し、第 3 の写真製版工程を用いてソース配線、ソース電極、ソース端子、ドレイン電極を少なくとも形成する工程と、

d ) 第 2 の絶縁膜を成膜し、第 4 の写真製版工程を用いて前記第 2 の絶縁膜に少なくとも前記ソース端子、ドレイン電極に達するコンタクトホールと、前記第 1 の絶縁膜と前記第 2 の絶縁膜に少なくとも前記ゲート端子の表面に達するコンタクトホールとを形成する工程と、

e ) 第 3 の導電性薄膜を成膜し、第 5 の写真製版工程を用いて少なくとも前記ドレイン電極と電気的に接続された画素電極パターンと、前記ゲート端子、ソース端子と電気的に接続された端子パッドパターンを形成する工程とを少なくとも含み、

前記 d ) の工程を少なくとも 2 回以上繰り返すことにより、前記第 2 の絶縁膜の成膜と前記コンタクトホールの形成を、少なくとも二層以上の構造で形成することを特徴とする液晶表示装置の製造方法。

## 【請求項 3】

下層にある少なくとも 1 種類以上の薄膜状の電極と、前記電極上に形成されてコンタクトホールが形成された絶縁膜と、前記コンタクトホールが設けられた前記絶縁膜上に薄膜状に形成された画素電極及び当該画素電極に対向する対向電極とを備え、前記画素電極及び前記対向電極のうちの少なくとも一方が前記コンタクトホールを介して前記下層にある少なくとも 1 種類以上の前記電極と電気的に接続されるとともに、前記画素電極と前記対向電極との間で前記絶縁膜の面と概略平行となる方向に電界が印加される構造を少なくとも有する液晶表示装置を製造する液晶表示装置の製造方法であって、

前記絶縁膜を少なくとも二層以上で形成するとともに、前記絶縁膜に形成される前記コンタクトホールを少なくとも二回以上の工程によって形成することを特徴とする横方向電界方式の液晶表示装置の製造方法。

## 【請求項 4】

a ) 絶縁性基板上に第 1 の導電性薄膜を成膜し、第 1 の写真製版工程を用いてゲート配線、ゲート電極、保持容量共通電極及び第 1 の共通電極を少なくとも形成する工程と、

b ) 第 1 の絶縁膜、半導体能動膜及びオーミックコンタクト膜を成膜し、第 2 の写真製版工程を用いて前記半導体能動膜と前記オーミックコンタクト膜をパターニングする工程と、

c ) 第 2 の導電性薄膜を成膜し、第 3 の写真製版工程を用いてソース配線、ソース電極、ドレイン電極、保持容量コンタクト膜を少なくとも形成する工程と、

d ) 第 2 の絶縁膜を成膜し、第 4 の写真製版工程を用いて前記第 2 の絶縁膜に少なくと

10

20

30

40

50

も前記ドレイン電極、前記保持容量コンタクト膜の表面に達するコンタクトホールと、前記第1の絶縁膜と前記第2の絶縁膜に少なくとも前記保持容量コンタクト膜の表面に達するコンタクトホールとを形成する工程と、

e) 第3の導電性薄膜を成膜し、第5の写真製版工程を用いて前記ドレイン電極と前記保持容量コンタクト膜と電気的に接続された画素電極パターンと、前記画素電極に対向する対向電極として前記保持容量共通電極と電気的に接続された対向電極を形成する工程とを少なくとも含み、

前記d)の工程を少なくとも2回以上繰り返すことにより、前記第2の絶縁膜の成膜と前記コンタクトホールの形成を、少なくとも二層以上の構造で形成することを特徴とする横方向電界方式の液晶表示装置の製造方法。

10

#### 【請求項5】

請求項4に記載の液晶表示装置の製造方法であって、

前記c)の工程で成膜される前記第2の導電性薄膜が、モリブデンを主成分とし、少なくとも10wt%以下のニオブを含むMoNb系合金で形成されることを特徴とする液晶表示装置の製造方法。

#### 【請求項6】

請求項5に記載の液晶表示装置の製造方法であって、

前記e)の工程で成膜される前記第3の導電性薄膜が、モリブデンを主成分とし、少なくとも10wt%以下のニオブを含むMoNb系合金で形成されることを特徴とする液晶表示装置の製造方法。

20

#### 【請求項7】

請求項6に記載の液晶表示装置の製造方法であって、

前記a)の工程で成膜される前記第1の導電性薄膜が、アルミニウムを主成分とし、少なくとも5wt%以下のネオジムを含むAlNd系合金で形成することを特徴とする液晶表示装置の製造方法。

#### 【請求項8】

下層にある少なくとも1種類以上の薄膜状の第1の電極と、

前記第1の電極上に形成されてコンタクトホールが形成された絶縁膜と、

前記コンタクトホールが設けられた前記絶縁膜上に薄膜状に形成された少なくとも1種類以上の第2の電極と

30

を備え、

前記第2の電極の少なくとも一部が前記コンタクトホールを介して前記下層にある少なくとも1種類以上の第1の電極に接続され、

前記絶縁膜が少なくとも二層以上で形成されるとともに、前記二層以上の絶縁膜に形成される前記コンタクトホールの形状が、上層にいくほど面積が大きく、その断面外径が順次広がって階段状または順テープ状に形成されることを特徴とする電気光学装置。

#### 【請求項9】

絶縁性基板上にゲート配線、ゲート電極、ゲート端子及び保持容量共通電極が少なくとも形成され、その上層に、ゲート絶縁膜、薄膜トランジスタの半導体能動膜、ソース電極、ドレイン電極、ソース配線及びソース端子が少なくとも形成され、その上層に、前記ソース端子及び前記ドレイン電極に達するコンタクトホールが形成された層間絶縁膜が形成され、前記ゲート絶縁膜及び前記層間絶縁膜に、前記ゲート端子の表面に達するコンタクトホールが形成され、その上層に、前記ドレイン電極と電気的に接続された画素電極と、前記ゲート端子及びソース端子に電気的にそれぞれ接続された端子パッドが少なくとも形成された液晶表示装置であって、

40

前記層間絶縁膜が少なくとも二層以上の構造で形成されるとともに、前記層間絶縁膜に形成されるコンタクトホールの形状が、上層にいくほど面積が大きくその断面外径が順次広がって階段状または順テープ状に形成されることを特徴とする液晶表示装置。

#### 【請求項10】

下層に少なくとも1種類以上の薄膜状の電極が形成され、前記電極上にコンタクトホー

50

ルが形成された層間絶縁膜が形成され、前記コンタクトホールが形成された前記層間絶縁膜上に薄膜状の画素電極と当該画素電極に対向する対向電極とが形成され、前記画素電極及び前記対向電極の少なくとも一方が前記コンタクトホールを介して前記下層にある少なくとも1種類以上の前記電極と電気的に接続されるとともに、前記画素電極と前記対向電極との間で前記層間絶縁膜の面と概略平行となる方向に電界が印加される液晶表示装置であって、

前記層間絶縁膜が少なくとも二層以上で形成されるとともに前記層間絶縁膜に形成されるコンタクトホールの形状が、上層にいくほど面積が大きく、その断面外径が順次広がっている階段状または順テーパ状に形成されたことを特徴とする横方向電界方式の液晶表示装置。

10

【請求項 1 1】

絶縁性基板上にゲート配線、ゲート電極、保持容量共通電極が少なくとも形成され、その上層に、ゲート絶縁膜、薄膜トランジスタの半導体能動膜及びソース電極、ドレイン電極、ソース配線及び保持容量コンタクト膜が少なくとも形成され、その上層に、前記ドレイン電極及び保持容量コンタクト膜の各表面に達するコンタクトホールがそれぞれ形成された層間絶縁膜が形成され、前記ゲート絶縁膜と前記層間絶縁膜に前記保持容量共通電極の表面に達するコンタクトホールが形成され、その上層に、前記ドレイン電極と前記保持容量コンタクト膜に電気的に接続された画素電極と、前記画素電極に対向して前記保持容量共通電極と電気的に接続された対向電極とが少なくとも形成された液晶表示装置であって、

前記層間絶縁膜が少なくとも二層以上の構造で形成されるとともに、前記二層以上の絶縁膜に形成されるコンタクトホールの形状が、上層にいくほど面積が大きくその断面外径が順次広がって階段状または順テーパ状に形成されたことを特徴とする横方向電界方式の液晶表示装置。

20

【請求項 1 2】

請求項 8 に記載の電気光学装置であって、

二層以上で形成される前記絶縁膜の膜厚が、上層にいくほど薄くなっていることを特徴とする電気光学装置。

【請求項 1 3】

請求項 9 から請求項 1 1 のいずれかに記載の液晶表示装置であって、

30

二層以上で形成される前記層間絶縁膜の膜厚が、上層にいくほど薄くなっていることを特徴とする液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、絶縁膜をはさんだ配線の層間短縮による不良防止と歩留まりを向上させることができる電気光学装置、横方向電界方式等の液晶表示装置及びそれらの製造方法に関する。

【背景技術】

【0 0 0 2】

近年、特許文献 1 に開示されているように、アクティブマトリックス型の液晶表示装置において、液晶に印加する電界の方向を基板に対して平行な方向とする横方向電界方式が、主に超広視野角を得る手法として用いられている。この方式を採用すると、視角方向を変化させた際のコントラストの変化や階調レベルの反転がほとんど無くなることが明らかにされている。

40

【0 0 0 3】

特許文献 1 においては、一対の対向電極が下層のソース配線を挟んで互いに分離して配置されている。このため、ソース配線に電圧が印加された状態においては、その電圧によって電界が発生し、TFTアレイ基板とカラーフィルタ基板との間に設けられた液晶の配向状態を変えてしまう。このため、一対の対向電極同士の形成幅が広く必要であり、光の

50

透過が制限されるため、パネル表示部の開口率が低くなるという問題があった。

#### 【0004】

このような問題点を解決するための横方向電界方式のデバイス構造が、例えば特許文献2に開示されている。この特許文献2では、対向電極がソース配線を覆い、両者が重なり合うように配置されている。このような構成によれば、ソース配線から発生する電界が対向電極によって遮られるため、この電界が液晶まで及ばず、液晶の配向状態の変化を低減することができる。このため、光の透過を制限する幅を短くでき、開口率を高くすることができます。

#### 【0005】

上記のように開口率を高くするために、ソース配線と上部の電極とを重畳させる技術に10

関しては、横方向電界方式以外の方式においても同様であり、例えば特許文献3にも開示

されている。

#### 【0006】

【特許文献1】特開平8-254712号公報

【特許文献2】特開2003-307748号公報

【特許文献3】特開平9-325358号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

しかしながら、特許文献2の場合には、層間絶縁膜を介して上層の対向電極が下層のソース配線を覆い、両者が重なり合うように配置されているために、この重なり合う領域の層間絶縁膜にピンホールや欠損等があると、上層の対向電極と下層のソース配線が電気的に短絡して表示不良となり、歩留まりの低下や信頼性を低下させる等の問題を招いていた。

20

#### 【0008】

さらに、特許文献3の場合においては、ゲート絶縁膜を介して上層の画素電極が下層のソース配線と一部重畳しているため、上記と同様の問題を招いていた。

#### 【0009】

上記層間絶縁膜のピンホールや欠損等の欠陥は例えば、パターニング加工を行う為のレジストパターン形成時にレジスト中の気泡や、レジスト現像時の現像液中に含まれる気泡が原因で発生したり、層間絶縁膜の成膜時に発生した膜中の異物が原因で発生し、実質的にこれらの欠陥発生をゼロにすることは難しい。

30

#### 【0010】

そこで、本発明の課題は、層間絶縁膜のピンホールや欠陥に起因する電極間の短絡不良を防止して、高歩留り、高信頼性を有する電気光学装置の実現とその製造方法を得ることにある。

#### 【0011】

また本発明は、超広視野角を有する横方向電界方式においてパネル表示部開口率を高くすることができるとともに、層間絶縁膜のピンホールや欠損に起因する電極間の短絡不良を防止して、高歩留り、高信頼性を同時に得ることができる液晶表示装置の実現とその製造方法を提供することにある。

40

#### 【課題を解決するための手段】

#### 【0012】

上記課題を解決すべく、この発明は、下層にある少なくとも1種類以上の薄膜状の第1の電極と、前記第1の電極上に形成されてコンタクトホールが形成された絶縁膜と、前記コンタクトホールが設けられた前記絶縁膜上に薄膜状に形成されて少なくとも1種類以上の第2の電極とを備え、前記第2の電極の少なくとも一部が前記コンタクトホールを介して前記下層にある少なくとも1種類以上の前記第1の電極と電気的に接続される構造を少なくとも有する電気光学装置を製造するにあたって、前記絶縁膜を少なくとも二層以上で形成するとともに、前記絶縁膜に形成される前記コンタクトホールを少なくとも二回以上

50

の工程によって形成するものである。

【発明の効果】

【0013】

請求項1に記載の発明では、下層にある少なくとも1種類以上の導電性薄膜からなる第1の電極と、この第1の電極上に形成されてコンタクトホールが形成された層間絶縁膜と、この層間絶縁膜上に導電性薄膜からなる少なくとも1種類以上の第2の電極とを備え、この第2の電極の少なくとも一部がコンタクトホールを介して下層にある少なくとも1種類以上の第1の電極と電気的に接続され、層間絶縁膜を少なくとも二層以上で形成するとともに、この層間絶縁膜に形成されるコンタクトホールを少なくとも二回以上の工程によって形成するので、層間絶縁膜にピンホールや欠損が発生しても、コンタクトホール以外での電極間の短絡不良を防止することができ、信頼性の高い電気光学装置を高い歩留りで製造することが可能となる。

【発明を実施するための最良の形態】

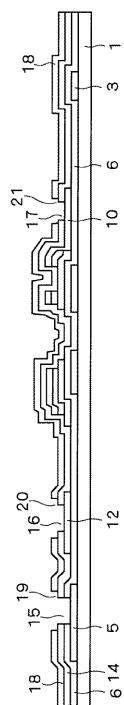

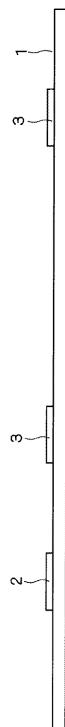

【0014】

{実施の形態1}

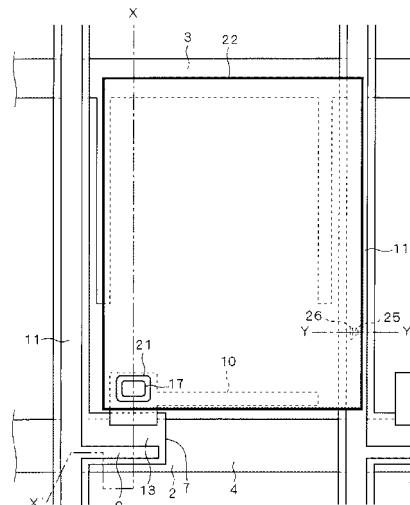

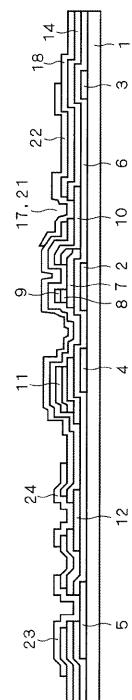

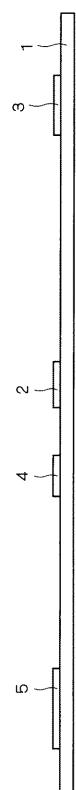

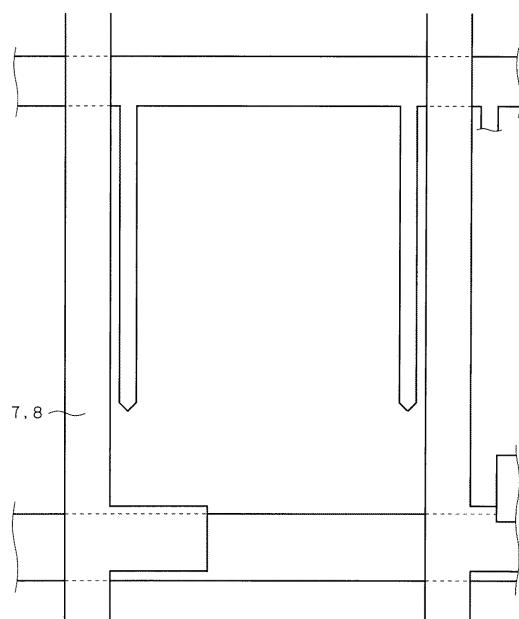

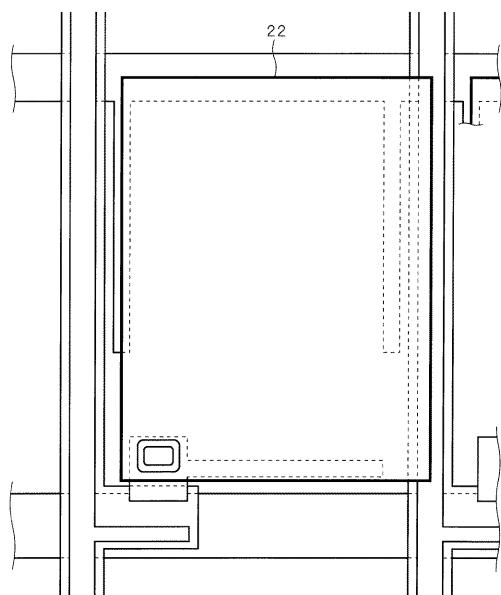

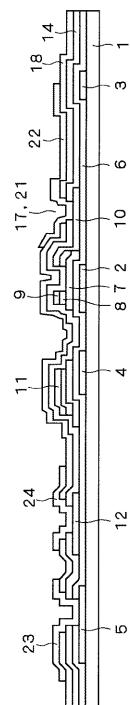

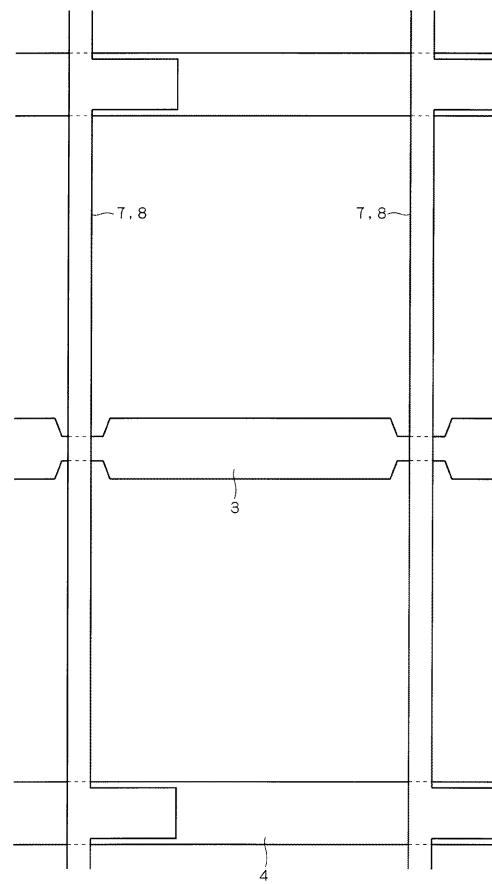

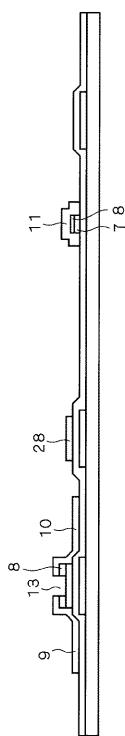

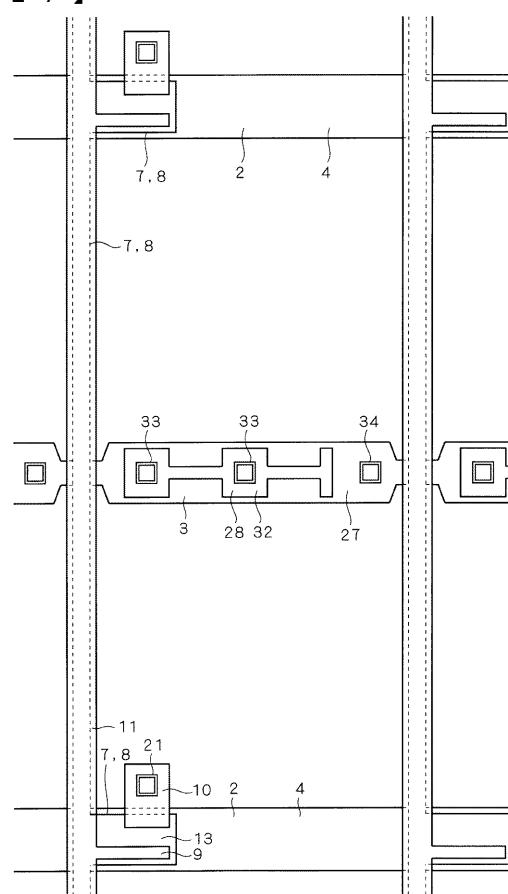

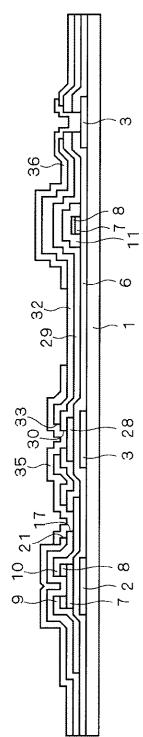

本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の平面図を図1に、同じくその断面図を図2にそれぞれ示す。尚、図2の断面図は、図1におけるX-X'部の断面に加え、ゲート端子部とソース端子部の断面構造を示している。

【0015】

この液晶表示装置用TFTアレイ基板は、ガラス基板などの透明絶縁性基板1上に少なくとも1種類以上の導電性薄膜を成膜することにより形成される最下層の金属層、即ち、ゲート電極2と、保持容量共通電極3と、ゲート配線4と、ゲート端子5と、当該最下層の金属層の一部または全部を覆うゲート絶縁膜6と、当該ゲート絶縁膜6上に形成されて少なくとも1種類以上の導電性薄膜からなる第1の電極10, 11, 12と、この第1の電極10, 11, 12上に形成された層間絶縁膜14, 18と、この層間絶縁膜14, 18に設けられたコンタクトホール16, 17(図10及び図12参照), 19, 20, 21(図12参照)と、層間絶縁膜14, 18とゲート絶縁膜6とに設けられたコンタクトホール15(図10参照)と、層間絶縁膜18上に、少なくとも1種類以上の導電性薄膜によって形成され、前記層間絶縁膜14, 18及びコンタクトホール15, 16, 17の少なくとも一部を覆うように配置された第2の電極22, 23, 24とからなり、第2の電極22, 23, 24の少なくとも一部がコンタクトホール15, 16, 17(図10及び図12参照), 19, 20, 21(図12参照)を介して下層にある少なくとも1種類以上の第1の電極5, 10, 12と電気的に接続され、且つ当該第2の電極22は、層間絶縁膜14, 18の少なくとも一方によって該第1の電極10と電気的に絶縁されている構造を有している。

【0016】

層間絶縁膜14, 18という少なくとも二層からなる積層構造を前記第1の電極5, 10, 12と前記第2の電極22, 23, 24との間に形成するとともに、この層間絶縁膜14, 18に形成されるコンタクトホールを少なくとも二回以上の工程によって形成している。

【0017】

この液晶表示装置用TFTアレイ基板の製造方法を図2及び図3～図14を参考にして説明する。

【0018】

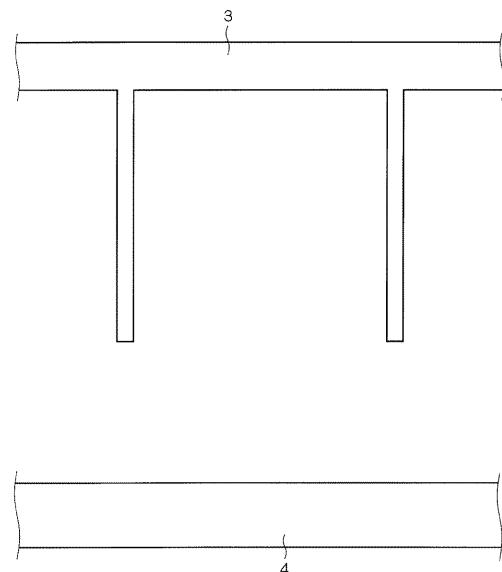

(A) 第1の工程

まず、ガラス基板などの透明絶縁性基板1上に第1の金属薄膜を成膜した後に、第1回目のフォトリソグラフィプロセス(写真製版工程)により第1の金属薄膜をパターニングして、図2、図3及び図4の如く、少なくともゲート電極2、保持容量共通電極3、ゲート配線4及びゲート端子5を形成する。これらの第1の金属薄膜としては、電気的比抵抗値の低いAl(アルミニウム)またはMo(モリブデン)や、これらを主成分とする合金

を用いることが好ましい。

【0019】

好適な実施例として、ここではまず、透明絶縁性基板1上に、公知のArガスを用いたスパッタリング法でAl膜を200nmの厚さで成膜する。スパッタリング条件はDCマグネットロンスパッタリング方式で、成膜パワー密度3W/cm<sup>2</sup>、Arガス流量40sccmとする。

【0020】

続けて、公知のArガスにN<sub>2</sub>ガスを混合したガスを用いた反応性スパッタリング法により窒素(N)原子を添加したAlN合金を50nmの厚さで成膜する。このスパッタリング条件は、成膜パワー密度3W/cm<sup>2</sup>、Arガス流量40sccm、N<sub>2</sub>ガス流量20sccmとする。以上により第1の金属薄膜として200nm厚のAl膜とその上層に50nm厚のAlN膜を有する2層膜を形成する。尚、このときの上層AlN膜のN元素組成は例えば約18wt%とされる。

【0021】

その後、レジストパターンを形成し、公知のリン酸+硝酸を含む溶液を用いて2層膜をエッチングした後にレジストパターンを除去して、図2、図3及び図4の如く、ゲート電極2、保持容量共通電極3、ゲート配線4及びゲート端子5のそれぞれのパターンを形成する。

【0022】

ここで、前記ゲート端子5はゲート配線4の延長上にあり、また前記保持容量共通電極3は、前記ゲート配線4や前記ゲート端子5と電気的に接続されていないという関係を有する。

【0023】

(B) 第2の工程

次に、図2、図5及び図6の如く、第1の絶縁膜(ゲート絶縁膜)6と、シリコン等からなる半導体能動膜7と、不純物原子を添加したシリコン等からなるオーミックコンタクト膜8とを順次成膜した後に、第2回目のフォトリソグラフィプロセス(写真製版工程)で、半導体膜(半導体能動膜)7とオーミックコンタクト膜8とをパターン形成する。この際、半導体能動膜7及びオーミックコンタクト膜8の形状は、薄膜トランジスタ(TFT)を形成する領域を含むとともに、後述の第3の工程で形成されるソース電極9及びソース配線11のパターンを包括するように、大きくかつ連続した形状に設定される。

【0024】

この第2の工程の好適な実施例として、化学的気相成膜(CVD)法を用い、第1の絶縁膜(ゲート絶縁膜)6として窒化シリコン(SiNx:xは正数)膜を400nm、半導体能動膜7としてアモルファスシリコン(a-Si)膜を150nm、オーミックコンタクト膜8としてリン(P)を不純物原子として添加したn+型のアモルファスシリコン(n+a-Si)膜を30nmの厚さで順次成膜した後に、レジストパターンを形成し、公知の弗素系ガスを用いたドライエッチング法でアモルファスシリコン膜及びオーミックコンタクト膜8をエッチングした後に、レジストパターンを除去して半導体膜7,8を形成する。

【0025】

(C) 第3の工程

次に、第2の金属薄膜を成膜した後に、第3回目のフォトリソグラフィプロセス(写真製版工程)によりパターンングし、図2、図7及び図8の如く、ソース電極9、ドレイン電極10(画素ドレイン)、ソース配線11及びソース端子12を形成する。

【0026】

これらの第2の金属薄膜としては、電気的比抵抗値が低いこと、オーミックコンタクト膜8との良好なコンタクト特性をもつこと、及びこのあとのプロセスで形成される画素電極22とのコンタクト特性に優れる等の利点を有する材料を用いることが好ましい。このような特性をもつ材料として例えばモリブデン(Mo)を基としてこれにニオブ(Nb)

10

20

30

40

50

やタンゲステン (W) 等を添加した合金を選ぶことが可能である。

【0027】

この第3の工程の好適な実施例として、Moに10wt%以下、例えば5wt%のNbを添加したMoNb合金を、公知のArガスを用いたスパッタリング法で200nmの厚さで成膜した後に、レジストパターンを形成し、公知のリン酸+硝酸を含む溶液を用いてエッチングし、さらに続けて公知の弗素系ガスを用いたドライエッチング法で少なくともソース電極9とドレイン電極10との間のオーミックコンタクト膜8を除去した後に、レジストパターンを除去してソース電極9、ドレイン電極10、ソース配線11及びソース端子12を形成する。また、この際、TFTのチャネル部13が形成される。

【0028】

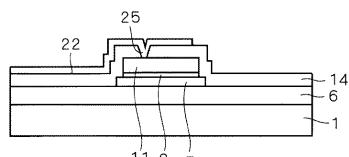

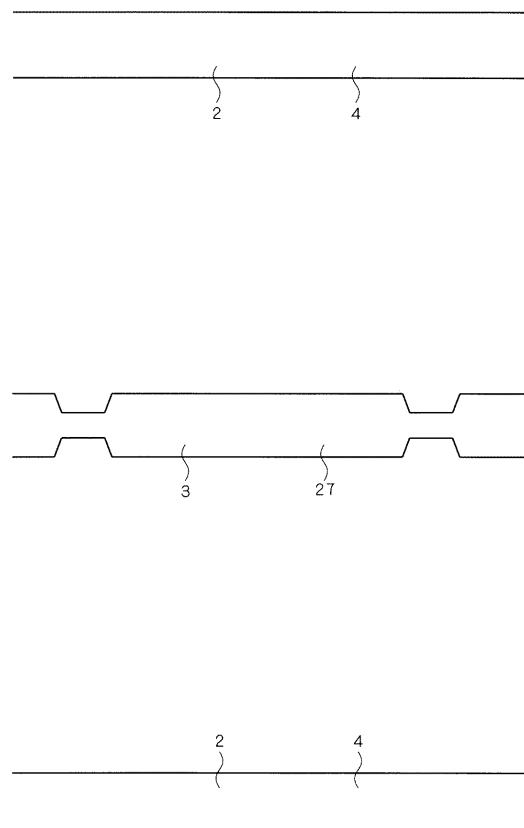

(D) 第4の工程

次に、図2、図9及び図10の如く、第2の絶縁膜を第1の層間絶縁膜14として成膜した後に、第4回目のフォトリソグラフィプロセス(写真製版工程)によりパターニングし、少なくとも第1の金属薄膜としてのゲート端子5の表面まで貫通するコンタクトホール15と、第2の金属薄膜のうちソース端子12の表面まで貫通するコンタクトホール16と、ドレイン電極10の表面まで貫通するコンタクトホール17とを同時に形成する。

【0029】

この第4の工程の好適な実施例として、第1の層間絶縁膜14としてCVD法を用いて窒化シリコン(SiNx)膜を200nmの厚さで成膜した後にレジストパターンを形成し、公知の弗素系ガスを用いたドライエッチング法で前記窒化シリコン膜をエッチングした後にレジストパターンを除去してゲート端子5用のコンタクトホール15、ソース端子12用のコンタクトホール16及びドレイン電極10(画素ドレイン)用のコンタクトホール17を形成する。

【0030】

この場合、レジストパターンにおいて泡などにより生じた欠陥部が存在すると、ドライエッチングにより、その欠陥部直下の窒化シリコン膜(第1の層間絶縁膜)14はエッチングされてしまうためピンホール25が形成されてしまう。

【0031】

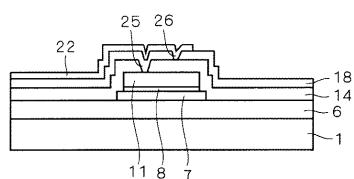

(E) 第5の工程

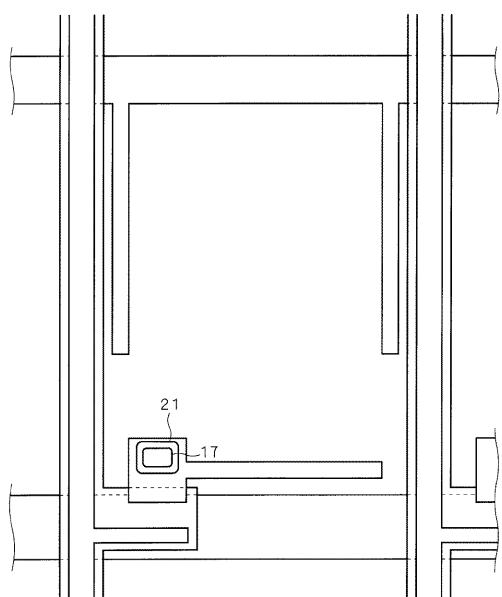

次に、再度(D)の第4の工程と同様の工程を第5の工程として繰り返す。即ち、図2、図11及び図12の如く、第3の絶縁膜を第2の層間絶縁膜18として成膜した後に、第5回目のフォトリソグラフィプロセス(写真製版工程)によりパターニングし、第4の工程(D)と同様にゲート端子5用のコンタクトホール19、ソース端子12用のコンタクトホール20、及びドレイン電極10(画素ドレイン)用のコンタクトホール21を形成する。

【0032】

このとき、コンタクトホール19, 20, 21は、それに対応する第4の工程(D)で形成されたコンタクトホール15, 16, 17の外径寸法よりも大きく、その断面形状が階段状になるようにしておくことが好ましい。

【0033】

また、第2の層間絶縁膜18の膜厚は、第1の層間絶縁膜14の膜厚よりも薄く形成しておくことが好ましい。

【0034】

この第5の工程の好適な実施例として、第2の層間絶縁膜18としてCVD法により窒化シリコン(SiNx)膜を100nmの厚さで成膜した後にレジストパターンを形成し、公知の弗素系ガスを用いたドライエッチング法で前記窒化シリコン膜をエッチングした後にレジストパターンを除去して、ゲート端子5用のコンタクトホール19、ソース端子12用のコンタクトホール20及びドレイン電極10(画素ドレイン)用のコンタクトホール21を形成する。

【0035】

10

20

30

40

50

この場合、レジストパターンにおいて泡などにより生じた欠陥部が存在すると、ドライエッチングにより、その欠陥部直下の窒化シリコン膜（第2の層間絶縁膜）18はエッチングされてしまうためピンホール26が形成されてしまう。

【0036】

（F）第6の工程

最後に、図2、図13及び図14の如く、透明導電性薄膜を成膜した後に、第6回目のフォトリソグラフィプロセス（写真製版工程）により、この透明導電性薄膜を用いて、コンタクトホール17, 21を介して下層のドレイン電極10と電気的に接続される画素電極22と、コンタクトホール15, 19を介して下層のゲート端子5と電気的に接続されるゲート端子パッド23と、コンタクトホール16, 20を介して下層のソース端子12と電気的に接続されるソース端子パッド24とをそれぞれパターン形成し、この実施の形態1に係る電気光学表示装置用TFTアレイ基板が完成する。

10

【0037】

第6の工程の好適な実施例として、透明導電性膜として酸化インジウム（In<sub>2</sub>O<sub>3</sub>）と酸化スズ（SnO<sub>2</sub>）とを混合したITO膜を公知のArガスを用いたスパッタリング法で100nmの厚さで成膜した後に、レジストパターンを形成し、公知の塩酸+硝酸を含む溶液を用いてエッチングした後にレジストパターンを除去して光を透過させる画素電極22、ゲート端子パッド23、及びソース端子パッド24を形成する。

20

【0038】

このようにして完成させたTFTアレイ基板においては、層間絶縁膜14と層間絶縁膜18とからなる少なくとも二層からなる積層構造が、下層と上層の配線や電極等（ゲート電極2、保持容量共通電極3、ゲート配線4、ゲート端子5、ドレイン電極10、ソース配線11及びソース端子12といった第1の電極と、画素電極22、ゲート端子パッド23、及びソース端子パッド24といった第2の電極）を、電気的に絶縁しているので、一層の層間絶縁膜しか設けていない例に比べて、下層と上層の配線や電極の電気的短絡や電気的短絡による表示不良を効果的に防止することが可能である。

20

【0039】

図15に、上層である画素電極29と下層であるソース電極11との重疊部の断面を示す。図15は、図1のY-Y'部で示す箇所の断面を示している。また、層間絶縁膜14と層間絶縁膜18において、膜欠損や、コンタクトホール等のパターンを形成する時のレジストパターンに気泡等の欠陥が生じることによるピンホール欠陥25, 26が発生した場合における比較のため、図16として、層間絶縁膜が一層しかない場合の断面図を示す。図16では、層間絶縁膜14が一層あるだけであり、ピンホール欠陥25によりソース配線11の表面が露出されてしまうため、透明導電性薄膜を成膜した時に画素電極22との電気的短絡が発生してしまう。一方、本実施の形態1を示した図15においては、ピンホール欠陥25とピンホール欠陥26とが別の位置で発生しているため、ソース配線11が露出せず、したがって画素電極22との電気的短絡も発生しない。もちろん、図15において、ピンホール欠陥25とピンホール欠陥26とが同じ位置で発生した場合は、電気的短絡が発生してしまうが、層間絶縁膜14でのピンホール欠陥25と層間絶縁膜18でのピンホール欠陥26とが全く同じ位置で発生して重なる確率は著しく低いと考えられるため、本実施の形態1に係る発明により電気的短絡や電気的短絡による表示不良を効果的に防止することができる。

30

【0040】

さらに、この実施の形態1においては、特に第2の層間絶縁膜18に形成する複数のコンタクトホール19, 20, 21の外径寸法を、図1及び図2の如く、それぞれに対応する第1の層間絶縁膜14のコンタクトホール15, 16, 17の外径寸法よりも大きく設定しているので、上層電極膜22, 23, 24のコンタクトホール段差部における断線不良を防止する効果を得ることができる。

40

【0041】

また、第2の層間絶縁膜18の膜厚を、第1の層間絶縁膜14の膜厚よりも薄く形成し

50

ておくことにより、レジストパターンに気泡等の欠陥が生じることによるピンホール欠陥 25、26等が発生した場合でも、第2の層間絶縁膜18のみを貫通させる為の公知の弗素系ガスを用いたドライエッティング法でエッティングすればよい。したがって、エッティング及びCVD法を用いて形成した窒化シリコン(SiNx)膜の面内均一性を考慮した場合に、エッティング時間を最小時間にでき、より信頼性が高く、歩留りを向上させる効果を得ることができる。

【0042】

したがって、この実施の形態1によるTFTアレイ基板と、共通電極及びカラーフィルタ等を有する対向基板とを貼り合わせ、これらの間に電気光学材料として液晶を挟持して製造される電気光学表示装置は、液晶表示装置として、歩留りを向上させ生産能力を向上させることができるので生産コストを低減して安価で供給されることが可能となる。 10

【0043】

また、液晶表示装置に限らず、この実施の形態1によるTFTアレイ基板の画素電極22上にエレクトロルミネセンス(EL)等の発光型の電気光学材料をパターン形成し、このELパターンを密閉封止するようにこの実施の形態1によるTFTアレイ基板と対向電極等を有する対向基板とを貼り合わせることにより、EL型の表示装置を歩留りよく製造することができる。

【0044】

尚、この実施の形態1では、層間絶縁膜14と層間絶縁膜18との二層からなる積層構造を形成していたが、これに限らず、例えばさらに第3の層間絶縁膜等を形成した三層以上の構造としてもよい。このように、多層構造になればなるほど、各層で発生する膜の欠損やピンホール不良の補完を確実にすることができる。ただし、実際上では二層構造とすることで膜の欠損やピンホールをほぼ補完することができる、及び工程の複雑化を避けるため二層または多くても三層構造までで充分である。 20

【0045】

以上のように、層間絶縁膜14と層間絶縁膜18との二層からなる積層構造を形成するとともに、この層間絶縁膜14,18に形成されるコンタクトホールを少なくとも二回以上の工程によって形成しているので、層間絶縁膜14,18にピンホールや欠損が発生しても、コンタクトホール以外での電極間の短絡不良を防止することができ、信頼性の高い電気光学装置を高い歩留りで製造することができる。 30

【0046】

{実施の形態2}

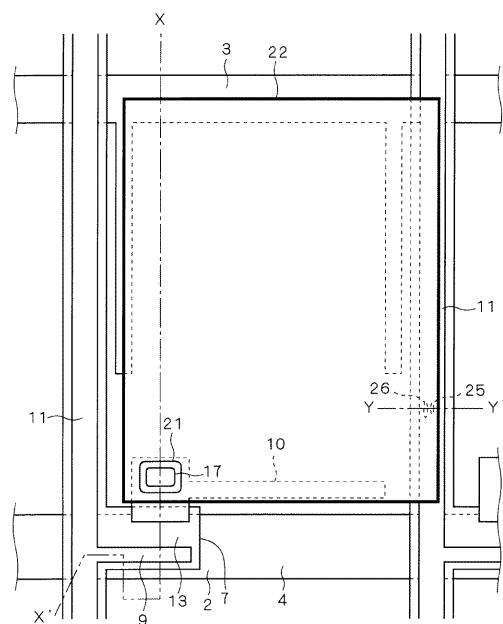

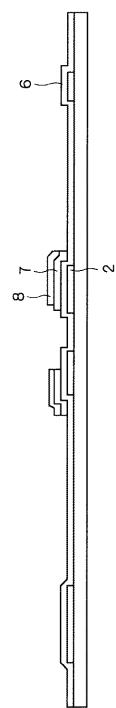

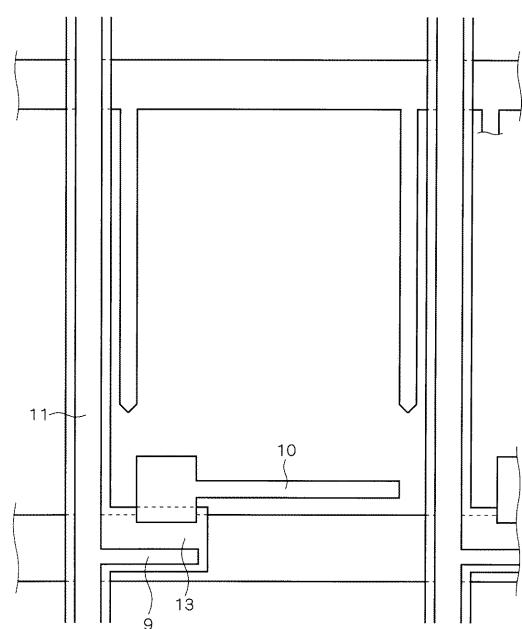

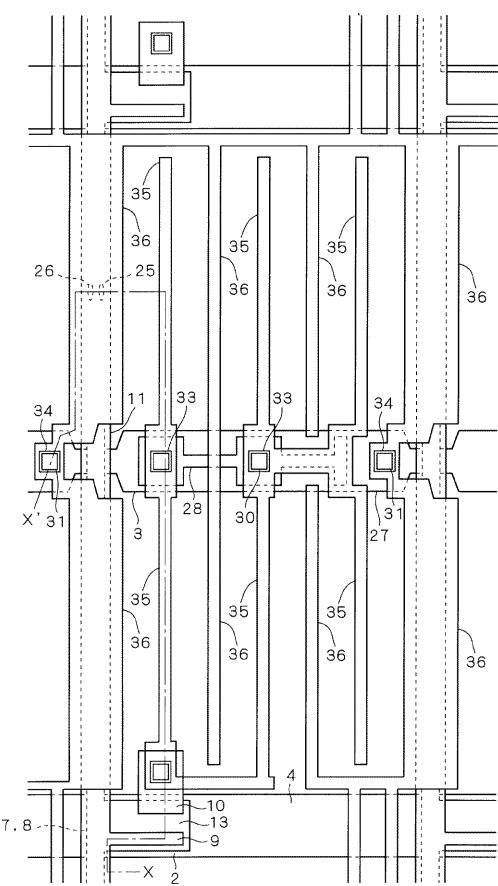

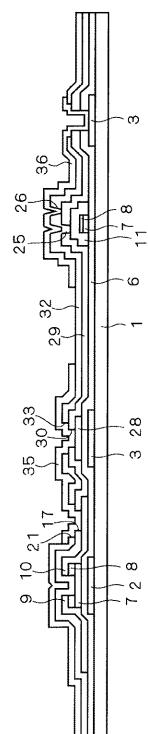

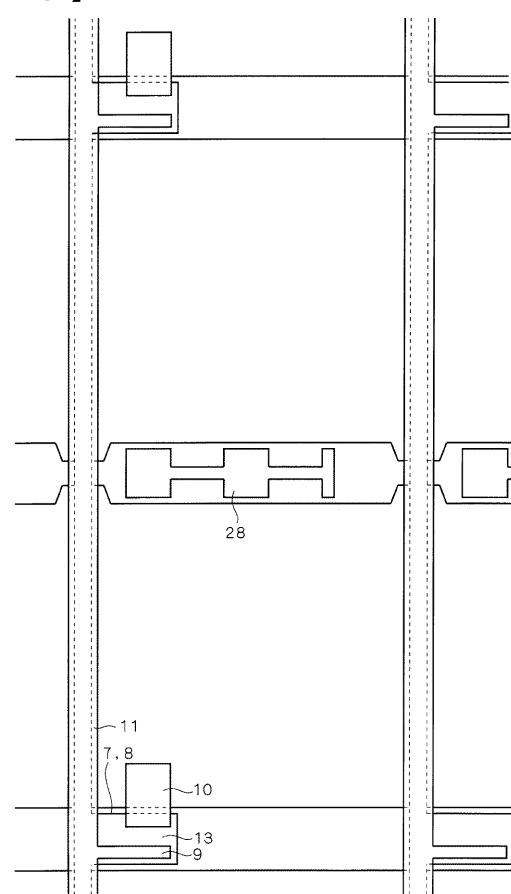

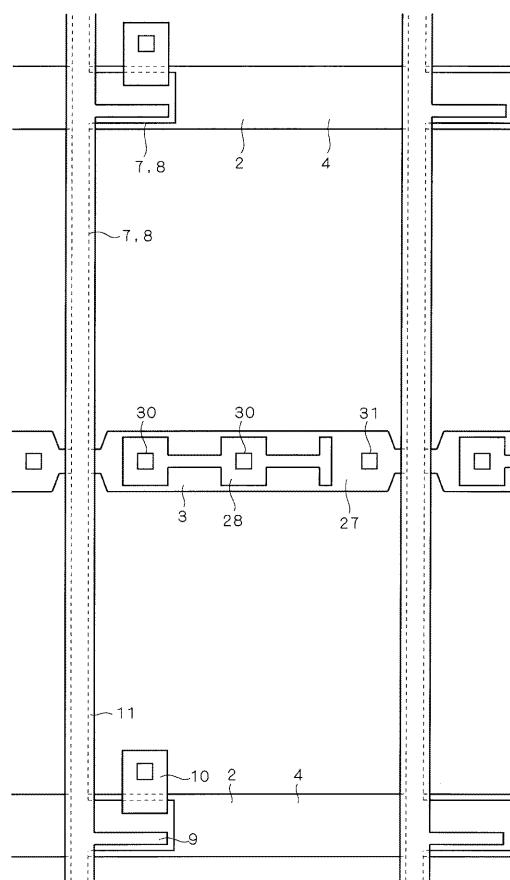

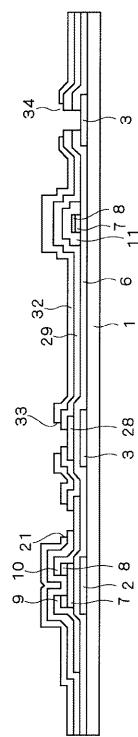

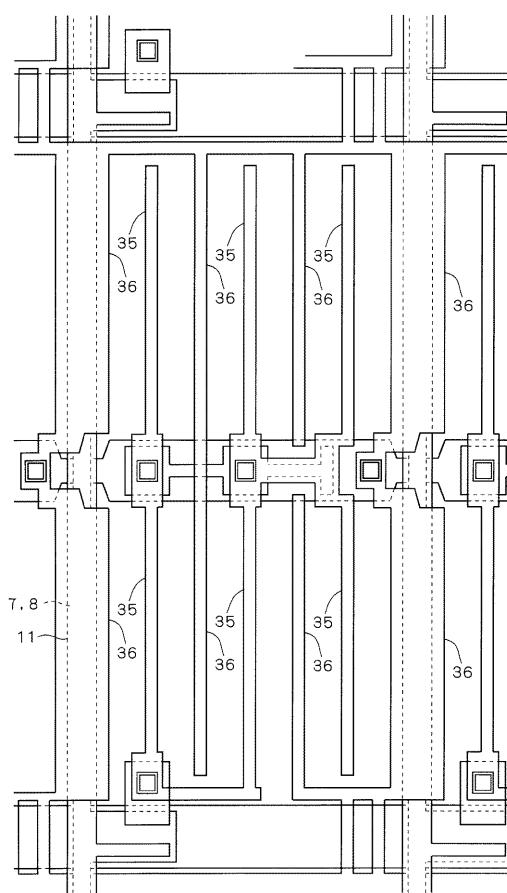

本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の平面図を図17に、同じくその断面図を図18にそれぞれ示す。図18の断面図は、図17におけるX-X'部の断面に加え、ゲート端子部とソース端子部の断面構造を示している。尚、この実施の形態2では、上述した実施の形態1と同様の機能を有する要素については同一符号を付している。

【0047】

この本液晶表示装置用TFTアレイ基板は、図17及び図18の如く、コンタクトホール17、21とコンタクトホール30,33を介して、それぞれドレイン電極10と、保持容量コンタクト膜28と電気的に接続された画素電極35と、コンタクトホール31,34を介して保持容量共通電極3と電気的に接続された対向電極36とが、互いに対向するように配置され、画素電極35と対向電極36との間で膜面に対して概略平行となる方向に電界が印加される構造を有するものである。 40

【0048】

この液晶表示装置用TFTアレイ基板の製造方法を、図18～図30を参考にして説明する。

【0049】

(A) 第1の工程

まず、ガラス基板などの透明絶縁性基板1上に第1の金属薄膜を成膜した後、第1回目 50

のフォトリソグラフィプロセス（写真製版工程）により第1の金属薄膜をパターニングし、図18、図19及び図20の如く、少なくともゲート電極2、保持容量共通電極3、ゲート配線4を形成する。

#### 【0050】

尚、図19に示すように、保持容量共通電極3は、平面上同一のパターンで形成される。第1の金属薄膜としては、電気的比抵抗値の低いAl、Moや、これらを主成分とする合金を用いることが好ましい。

#### 【0051】

この第1の工程の好適な実施例として、まず、公知のArガスを用いたスパッタリング法でAl膜を200nmの厚さで成膜する。スパッタリング条件はDCマグネットロンスパッタリング方式で、成膜パワー密度3W/cm<sup>2</sup>、Arガス流量40sccmとする。

#### 【0052】

続けて公知のArガスにN<sub>2</sub>ガスを混合したガスを用いた反応性スパッタリング法により窒素（N）原子を添加したAlN合金を50nmの厚さで成膜する。このスパッタリング条件は、成膜パワー密度3W/cm<sup>2</sup>、Arガス流量40sccm、N<sub>2</sub>ガス流量20sccmとする。以上により第1の金属薄膜として200nm厚のAl膜とその上層に50nm厚のAlN膜を有する2層膜を形成する。尚、このときの上層AlN膜のN元素組成は例えば約18wt%とされる。

#### 【0053】

その後、レジストパターンを形成し、公知のリン酸+硝酸を含む溶液を用いて前記2層膜をエッチングした後にレジストパターンを除去して、ゲート電極2、保持容量共通電極3、及びゲート配線4のそれぞれをパターン形成する。

#### 【0054】

##### （B）第2の工程

次に、図18、図21及び図22の如く、第1の絶縁膜（ゲート絶縁膜）6と、シリコン等からなる半導体能動膜7と、不純物原子を添加したシリコン等からなるオーミックコンタクト膜8とを順次成膜した後に、第2回目のフォトリソグラフィプロセス（写真製版工程）で、半導体能動膜7とオーミックコンタクト膜8とをパターン形成する。この際、半導体能動膜7及びオーミックコンタクト膜8は、薄膜トランジスタ（TFT）を形成する領域を含み、かつこのTFTを形成する領域から延在するとともに後述の第3の工程で形成されるソース配線11のパターンに包括されるように連続した形状になるようにパターン形成される。

#### 【0055】

この第2の工程の好適な実施例として、化学的気相成膜（CVD）法を用いて第1の絶縁膜（ゲート絶縁膜）6として窒化シリコン（SiNx：xは正数）膜を400nm、半導体能動膜7としてアモルファスシリコン（a-Si）膜を150nm、オーミックコンタクト膜8としてリン（P）を不純物原子として添加したn+型のアモルファスシリコン（n+a-Si）膜を30nmの厚さで順次成膜した後に、レジストパターンを形成し、公知の弗素系ガスを用いたドライエッティング法でアモルファスシリコン膜とオーミックコンタクト膜8とをエッチングした後にレジストパターンを除去して半導体膜7、8を形成する。

#### 【0056】

##### （C）第3の工程

次に、図18、図23及び図24の如く、第2の金属薄膜を成膜した後に、第3回目のフォトリソグラフィプロセス（写真製版工程）によりパターニングしてソース電極9、ドレイン電極10、ソース配線11及び保持容量コンタクト膜28を形成する。第2の金属薄膜としては、電気的比抵抗値が低いこと、オーミックコンタクト膜8との良好なコンタクト特性をもつこと、及びこのあとのプロセスで形成される画素電極35とのコンタクト特性に優れる等の利点を有する材料を用いることが好ましい。このような特性をもつ材料として例えばモリブデン（Mo）を基としてこれにニオブ（Nb）やタンゲステン（W）

10

20

30

40

50

等を添加した合金を選ぶことが可能である。

【0057】

この第3の工程の好適な実施例として、Moに10wt%以下、例えば5wt%のNbを添加したMoNb合金を、公知のArガスを用いたスパッタリング法で200nmの厚さで成膜した後に、レジストパターンを形成し、公知のリン酸+硝酸を含む溶液を用いてエッチングする。さらに続けて公知の弗素系ガスを用いたドライエッチング法で少なくともソース電極9とドレイン電極10の間のオーミックコンタクト膜8を除去した後に、レジストパターンを除去してソース電極9、ドレイン電極10、ソース配線11、保持容量コンタクト膜28、及びTFTのチャネル部13を形成する。

【0058】

10 (D) 第4の工程

次に、図18、図25及び図26の如く、第2の絶縁膜を第1の層間絶縁膜29として成膜した後に、第4回目のフォトリソグラフィプロセス(写真製版工程)によりパターニングして、少なくとも第1の金属薄膜の保持容量共通電極3の表面まで貫通するコンタクトホール31と、第2の金属薄膜のうち保持容量コンタクト膜28の表面まで貫通するコンタクトホール30と、ドレイン電極10の表面まで貫通するコンタクトホール17とを同時に形成する。

【0059】

20 この第4の工程の好適な実施例として、第1の層間絶縁膜29としてCVD法を用いて窒化シリコン(SiNx)膜を200nmの厚さで成膜した後にレジストパターンを形成し、公知の弗素系ガスを用いたドライエッチング法で前記窒化シリコン膜をエッチングした後に、レジストパターンを除去して、保持容量共通電極3用コンタクトホール31、保持容量コンタクト膜28用コンタクトホール30及びドレイン電極10(画素ドレイン)用コンタクトホール17を形成する。

【0060】

この場合、レジストパターンにおいて泡などにより生じた欠陥部が存在すると、ドライエッチングにより、その欠陥部直下の窒化シリコン膜(第1の層間絶縁膜)29はエッチングされてしまうためピンホール25が形成されてしまう。

【0061】

30 (E) 第5の工程

次に、第5の工程として、再度第4の工程(D)と同様の工程を繰り返す。即ち、図18、図27及び図28の如く、第3の絶縁膜を第2の層間絶縁膜32として成膜した後に、第5回目のフォトリソグラフィプロセス(写真製版工程)によりパターニングして、第4の工程(D)と同様にして、保持容量共通電極3用コンタクトホール34、保持容量コンタクト膜28用コンタクトホール33、及びドレイン電極10(画素ドレイン)用コンタクトホール21を形成する。

【0062】

このとき、コンタクトホール21、33、34は、第4の工程(D)でそれぞれに対応するよう形成されたコンタクトホール17、30、31の外径寸法よりも大きく、その断面形状が階段状になるようにしておくことが好ましい。

【0063】

40 また、第2の層間絶縁膜32の膜厚は、第1の層間絶縁膜29の膜厚よりも薄く形成しておくことが好ましい。

【0064】

この第5の工程の好適な実施例として、第2の層間絶縁膜32としてCVD法を用いて窒化シリコン(SiNx)膜を100nmの厚さで成膜した後にレジストパターンを形成し、公知の弗素系ガスを用いたドライエッチング法で前記窒化シリコン膜をエッチングした後にレジストパターンを除去して保持容量共通電極3用コンタクトホール34、保持容量コンタクト膜28用コンタクトホール33及びドレイン電極10(画素ドレイン)用コンタクトホール21を形成する。

## 【0065】

この場合、レジストパターンにおいて泡などにより生じた欠陥部が存在すると、ドライエッティングにより、その欠陥部直下の窒化シリコン膜（第2の層間絶縁膜）32はエッティングされてしまうためピンホール26が形成されてしまう。

## 【0066】

（F）第6の工程

最後に、図18、図29及び図30の如く、透明導電性薄膜を成膜した後に、第6回目のフォトリソグラフィプロセス（写真製版工程）により、この透明導電性薄膜を用いて画素電極35及び対向電極36をパターン形成する。

## 【0067】

この際、画素電極35は、コンタクトホール17, 21, 30, 33を介して、下層のドレイン電極10及び保持容量コンタクト膜28にそれぞれ電気的に接続される。

## 【0068】

また、対向電極36は、コンタクトホール31, 34を介して、下層の保持容量共通電極3に電気的に接続される。さらに、対向電極36は、少なくともその一部が下層のソース配線11の上を覆うような形状とされる。

## 【0069】

このようにして、この実施の形態2に係る液晶表示装置用TFTアレイ基板が完成する。

## 【0070】

このように、画素電極35と対向電極36は互いに完全に分離されており、かつ両者のパターンの一辺の少なくとも一部は互いに概略平行に対向するような形状を有するようにパターン形成される。

## 【0071】

この第6の工程の好適な実施例として、ここでは透明導電性膜として酸化インジウム（In<sub>2</sub>O<sub>3</sub>）と酸化スズ（SnO<sub>2</sub>）とを混合したITO膜を公知のArガスを用いたスパッタリング法で100nmの厚さで成膜した後に、レジストパターンを形成し、公知の塩酸+硝酸を含む溶液を用いてエッティングした後にレジストパターンを除去して画素電極35及び対向電極36を形成する。

## 【0072】

この実施の形態2においても、上述の実施の形態1と同様の効果を得ることができる。

## 【0073】

加えて、この実施の形態2の場合、図17及び図18に示すように、特に対向電極36が下層のソース配線11とオーバーラップする領域において、実施の形態1で図15及び図16を用いて説明した効果と同様の効果を奏している。即ち、層間絶縁膜が一層しかない構造は、層間絶縁膜29, 32の欠損、ピンホール欠陥等25, 26が両者の電気的短絡不良に直結する構造となるため、層間絶縁膜29, 32を二層積層し、さらにコンタクトホールを2回以上の工程により形成することを特徴とする本発明は、不良の防止に大きな効果をもたらす。

## 【0074】

したがって、この実施の形態2によるTFTアレイ基板と、共通電極及びカラーフィルタ等を有する対向基板とを貼り合わせ、これらの間に液晶を挟持して製造される横方向電界方式の液晶表示装置は、歩留りを向上させ生産能力を向上させることができるので生産コストを低減して安価で供給することが可能となる。

## 【0075】

尚、この実施の形態2でも、層間絶縁膜29と層間絶縁膜32との二層からなる積層構造を形成したが、これに限らず、例えばさらに第3の層間絶縁膜を形成した三層構造としてもよい。

## 【0076】

また、上記の実施の形態1, 2では、第1の金属薄膜としてAl（アルミニウム）膜と

10

20

30

40

50

その上層にN(窒素)原子を添加したAlN膜を形成した二層膜としたが、これは金属薄膜をAlとすることで電極や配線の電気抵抗を低くするとともに、上層にAlN膜を設けることで透明導電膜ITO膜からなるゲート端子パッド23(図2参照)がコンタクトホール15、19を介してゲート端子5と電気的に接続された場合や、対向電極36(図18参照)がコンタクトホール31、34を介して保持容量共通電極3と電気的に接続された場合等の界面のコンタクト抵抗を良好にするためである。また、上層にAlN膜を形成することによって、一般的にヒロックとして知られている約100以上に加熱したときにAl膜表面に生じる突起を抑制することができる。さらに、AlN/Alの二層構造とすることで、Al系金属のエッチング液として公知のリン酸+硝酸を含む溶液で一括エッチングできるというメリットもある。尚、上記各実施の形態においては、上層のAlには約18wt%のN原子を添加したAlN膜を用いたが、これに限定されるものではない。本出願人での評価によると、上層のAlに添加するN原子組成が5~26wt%であれば本発明と同等の効果を得られることを確認している。あるいは、添加元素もN(窒素)原子に限ることなく炭素(C)原子や酸素(O)原子を添加させてもよい。上層のAlに添加する元素の種類や添加量はスパッタリング法において、公知のArガスに混合するガスの種類と流量を任意に変えることにより実施することが可能である。例えばN<sub>2</sub>ガスの替わりにO<sub>2</sub>ガス、CO<sub>2</sub>ガスまたは大気ガスを混合した反応性スパッタリングを行うことが可能である。

#### 【0077】

さらに、母体となる金属薄膜として、Al膜の代わりに、Alにネオジム(Nd)やガドリニウム(Gd)、ランタン(La)等の希土類金属元素やイットリウム(Y)を添加したAl合金を用いたAl合金-N/Al合金の二層膜とすることも可能である。この場合には、上述したプロセスの加熱工程におけるヒロック発生防止のマージンを上げることができ、製品の歩留りや信頼性を向上させることができるのでさらに好ましい。Alに添加するNd、Gd、La、Y元素の添加量は5wt%以下、好ましくは0.1~5wt%の範囲とするのが好ましい。これは0.1wt%未満であればヒロック抑制効果を得るのが難しいこと、そして5wt%を超える添加量ではAl合金そのものの比抵抗が上がってしまい(5μcm以上)、低抵抗のメリットが損なわれてしまうからである。

#### 【0078】

さらにまた、上記の実施の形態1、2では、第2の金属薄膜としてMo(モリブデン)に添加量10wt%以下、例えば添加量5wt%でNbを加えたMoNb系合金を用いたが、これに限定されることはない。Nb原子の添加によりMoの耐食性、特に純水に対する耐食性を向上させることができること、さらにこれに加えてAl系金属として公知のリン酸+硝酸を含む溶液に対する急激なエッチング腐食速度を抑制して制御することができる所以になるので、この実施の形態1、2の場合には、第1の金属薄膜として用いたAl系合金膜のエッチング溶液をMoNb合金用のエッチング液として共用することができるというメリットがある。このような効果を得るためのMoへのNbの添加量は2.5~10wt%であることが好ましい。あるいはMoに30~50wt%のWを添加したMoW膜を用いた場合でも同様の効果を得ることが可能である。

#### 【0079】

また、上記実施の形態1、2においては、透明導電性膜として酸化インジウム(Indium Oxide)と酸化スズ(SnO<sub>2</sub>)とを混合させたITO膜を用いたが、これに限定されることなく、酸化インジウム、酸化スズ、酸化亜鉛(ZnO)の単体、あるいはこれらを混合させたものを用いてもよい。例えば、酸化インジウムに酸化亜鉛を混合させたIZO膜を用いた場合には、公知のArガスを用いたスパッタリング法で透明導電性膜を非晶質の状態で成膜することができ、上述の実施例で用いた塩酸+硝酸を含む強酸系溶液ではなく磷酸系のような弱酸溶液をエッチング液として用いることができるようになるので、この実施の形態のように第1及び第2の金属薄膜に耐酸性に乏しいAl系やMo系等の合金膜を用いた場合には、透明導電性膜エッチング時の薬液のしみ込みによるこれらAl系、Mo系合金膜の腐食断線を防止することができるので好ましい。また、酸化インジウムに酸化

10

20

30

40

50

スズと酸化亜鉛を適量混合させたITO膜を用いた場合には、非晶質状態で形成した膜を加熱することによって化学的に安定な結晶質状態にすることができるようになるので、非晶質状態でパターニング形成までを行った後に加熱して結晶質状態にすることによって、耐食性が高く、信頼性の高い液晶表示装置を歩留りよく製造することができるようになる。尚、酸化インジウム、酸化スズ、酸化亜鉛それぞれのスパッタ膜の酸素組成が酸化物の化学量論組成よりも少なく、その結果、透過率値や比抵抗値等の特性が不良の場合は、スパッタリングガスとしてArガスだけでなくO<sub>2</sub>ガスやH<sub>2</sub>Oガスを混合させたガスを用いて成膜するのが好ましい。

#### 【0080】

さらに、上記実施の形態1、2においては、第1、及び第2の層間絶縁膜をCVD法を用いて形成した窒化シリコン(SiNx)膜としたが、限定された膜を指定するものではなく、第1、第2のいずれか、あるいは両方の層間絶縁膜に、酸化シリコン(SiOx)膜や、その他にも有機系の樹脂膜を塗布形成して用いても良いことは言うまでもない。特に、感光性の有機樹脂膜を層間絶縁膜として用いる場合には、コンタクトホールをフォトリソグラフィプロセス(写真製版工程)で形成することが可能なので、これを第2の層間絶縁膜として用いる場合には、膜厚を第1の層間絶縁膜のそれよりも薄くするという必要はない。

#### 【0081】

また、上記各実施の形態では、コンタクトホール19, 20, 21の外径寸法を、コンタクトホール15, 16, 17の外径寸法よりもそれぞれ大きく形成して、その断面形状が階段状になるように設定していたが、コンタクトホール15, 16, 17, 19, 20, 21の壁面を傾斜させて、順テープ状に形成してもよい。

#### 【図面の簡単な説明】

#### 【0082】

【図1】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板を示す平面図である。

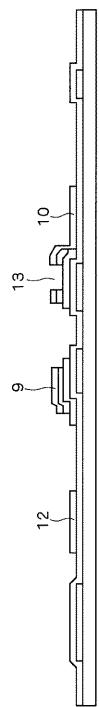

【図2】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板を示す断面図である。

【図3】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図4】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図5】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図6】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図7】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図8】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図9】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図10】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図11】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図12】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図13】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

10

20

30

40

50

【図14】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図15】本発明の実施の形態1に係る液晶表示装置用TFTアレイ基板の一部を示す断面図である。

【図16】他の比較例に係る液晶表示装置用TFTアレイ基板の一部を示す断面図である。

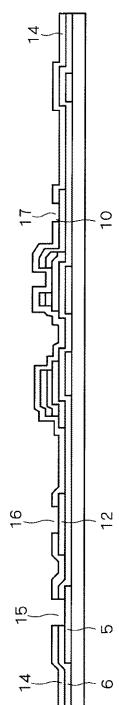

【図17】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板を示す平面図である。

【図18】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板を示す断面図である。

【図19】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図20】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図21】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図22】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図23】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図24】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図25】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図26】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図27】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図28】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

【図29】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す平面図である。

【図30】本発明の実施の形態2に係る液晶表示装置用TFTアレイ基板の製造工程を示す断面図である。

#### 【符号の説明】

##### 【0083】

1 透明絶縁性基板、2 ゲート電極、3 保持容量共通電極、4 ゲート配線、5 ゲート端子、6 ゲート絶縁膜、7 半導体能動膜、8 オーミックコンタクト膜、9 ソース電極、10 ドレイン電極、11 ソース配線、12 ソース端子、13 チャネル部、14, 18, 29, 32 層間絶縁膜、15, 16, 17, 19, 20, 21, 30, 31, 33, 34 コンタクトホール、20, 21, 33, 34 コンタクトホール、22 画素電極、23 ゲート端子パッド、24 ソース端子パッド、25, 26 ピンホール欠陥、28 保持容量コンタクト膜、31, 34 コンタクトホール、35 画素電極、36 対向電極。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

### 【 図 1 3 】

【図14】

【 図 1 5 】

【 図 1 6 】

【 図 1 7 】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

## フロントページの続き

(51) Int.CI. F I テーマコード(参考)

**H 0 1 L 23/522 (2006.01)** H 0 1 L 21/90 A

H 0 1 L 21/90 M

(72)発明者 荒木 利夫

熊本県菊池郡西合志町御代志 997番地 メルコ・ディスプレイ・テクノロジー株式会社内

(72)発明者 石賀 展昭

熊本県菊池郡西合志町御代志 997番地 メルコ・ディスプレイ・テクノロジー株式会社内

F ターム(参考) 2H092 GA29 HA04 JA24 JA46 JA47 JB57 KA05 KA18 KB04 KB25

MA05 MA15 MA19 NA01 NA27 NA28 NA29

5F033 GG04 HH38 JJ38 KK08 KK10 KK20 PP15 QQ11 QQ37 RR06

SS11 TT02 VV15 WW04 XX31

5F110 AA26 BB01 CC07 DD02 EE03 EE04 EE06 EE14 EE44 FF03

FF29 GG02 GG15 GG24 GG44 HK03 HK06 HK09 HK16 HK21

HK25 HK33 HK34 HL07 HL14 HL23 HM18 NN03 NN04 NN23

NN24 NN27 NN33 NN35 NN71 NN72 NN73

5G435 AA14 AA17 BB12 CC09 HH12 HH14 KK05