(12)发明专利

(10)授权公告号 CN 106030797 B

(45)授权公告日 2019.03.12

(21)申请号 201480075282.X

(72)发明人 木村圭佑 龟山悟

(22)申请日 2014.09.08

(74)专利代理机构 北京金信知识产权代理有限公司 11225

(65)同一申请的已公布的文献号

申请公布号 CN 106030797 A

代理人 黄威 苏萌萌

(43)申请公布日 2016.10.12

(51)Int.Cl.

H01L 27/04(2006.01)

(30)优先权数据

H01L 21/336(2006.01)

2014-023867 2014.02.10 JP

H01L 29/739(2006.01)

(85)PCT国际申请进入国家阶段日

H01L 29/78(2006.01)

2016.08.10

(56)对比文件

(86)PCT国际申请的申请数据

JP 特开2011-134861 A, 2011.07.07,

PCT/JP2014/073676 2014.09.08

JP 特开2011-82220 A, 2011.04.21,

(87)PCT国际申请的公布数据

CN 103325786 A, 2013.09.25,

W02015/118714 JA 2015.08.13

CN 101414816 A, 2009.04.22,

(73)专利权人 丰田自动车株式会社

US 2002/0153586 A1, 2002.10.24,

地址 日本爱知县

审查员 李元

权利要求书1页 说明书8页 附图5页

(54)发明名称

半导体装置

(57)摘要

本发明提供一种半导体装置，所述半导体装置具有形成有IGBT的主IGBT区、形成有二极管的主二极管区、形成有IGBT的感测IGBT区、和形成有二极管的感测二极管区。体区与阳极区之间的间隔长于二者之间的n型区的移动率与寿命的乘积。阳极区与集电区之间的间隔长于二者之间的n型区的移动率与寿命的乘积。集电区的端部与体区之间的间隔长于二者之间的n型区的移动率与寿命的乘积。

1. 一种半导体装置，其为具有半导体基板的半导体装置，所述半导体基板具有形成有绝缘栅双极性晶体管的主绝缘栅双极性晶体管区、形成有二极管的主二极管区、形成有绝缘栅双极性晶体管的感测绝缘栅双极性晶体管区、和形成有二极管的感测二极管区，其中，所述感测绝缘栅双极性晶体管区的面积小于所述主绝缘栅双极性晶体管区，所述感测二极管区的面积小于所述主二极管区，在所述感测绝缘栅双极性晶体管区内形成有：发射区，其为n型，并露出于所述半导体基板的表面；体区，其为p型，并与所述发射区相接；绝缘栅双极性晶体管漂移区，其为n型，并通过所述体区而与所述发射区分离；集电区，其为p型，并露出于所述半导体基板的背面，且通过所述绝缘栅双极性晶体管漂移区而与所述体区分离；栅绝缘膜，其与所述体区相接；栅电极，其隔着所述栅绝缘膜而与所述体区对置，在所述感测二极管区内形成有：阳极区，其为p型，并露出于所述半导体基板的所述表面；二极管漂移区，其为n型，并与所述阳极区相接；阴极区，其为n型，并通过所述二极管漂移区而与所述阳极区分离，且露出于所述半导体基板的所述背面，并且与所述二极管漂移区相比n型杂质浓度较高，通过所述绝缘栅双极性晶体管漂移区以及所述二极管漂移区而使所述体区与所述阳极区分离，在所述绝缘栅双极性晶体管漂移区与所述二极管漂移区之间，形成有与所述绝缘栅双极性晶体管漂移区以及所述二极管漂移区相比n型杂质浓度较高的高浓度n型区，所述高浓度n型区从半导体基板的上表面起延伸至与所述绝缘栅双极性晶体管漂移区以及所述二极管漂移区的厚度方向的中央部相比而较深的位置为止。

## 半导体装置

### 技术领域

[0001] (关联申请的相互参照)

[0002] 本申请为2014年2月10日提出的日本专利申请特愿2014-023867的关联申请,本申请要求基于该日本专利申请的优先权,并援引该日本专利申请所记载的全部内容来作为构成本说明书的内容。

[0003] 本说明书所公开的技术涉及一种半导体装置。

### 背景技术

[0004] 在国际公开第2011/138832号公报中公开了一种在同一半导体基板上形成有IGBT (Insulated Gate Bipolar Transistor: 绝缘栅双极性晶体管) 和二极管的半导体装置。此外,在该半导体基板上,在流有主电流的主IGBT之外还形成有流有较小的电流的感测IGBT。通过对流过感测IGBT的电流进行检测,从而能够检测出流过主IGBT的电流。此外,在该半导体基板上,在流有主电流的主二极管之外还形成有流有较小的电流的感测二极管。此外,通过对流过感测二极管的电流进行检测,从而能够检测出流过主二极管的电流。

### 发明内容

[0005] 发明所要解决的课题

[0006] 在上述的半导体装置中,期望使感测IGBT以及感测二极管的检测精度进一步提高。

[0007] 用于解决课题的方法

[0008] 本说明书所公开的第一半导体装置具有半导体基板,所述半导体基板具有形成有IGBT的主IGBT区、形成有二极管的主二极管区、形成有IGBT的感测IGBT区、和形成有二极管的感测二极管区。所述感测IGBT区的面积小于所述主IGBT区。所述感测二极管区的面积小于所述主二极管区。跨及所述感测IGBT区与所述感测二极管区而形成有n型区。在所述感测IGBT区内形成有:发射区,其为n型,并露出于所述半导体基板的表面;体区,其为p型,并与所述发射区相接;所述n型区,其通过所述体区而与所述发射区分离;集电区,其为p型,并露出于所述半导体基板的背面,且通过所述n型区而与所述体区分离;栅绝缘膜,其与所述体区相接;栅电极,其隔着所述栅绝缘膜而与所述体区对置。在所述感测二极管区内形成有:阳极区,其为p型,并露出于所述半导体基板的所述表面;所述n型区,其与所述阳极区相接,并露出于所述半导体基板的所述背面。通过所述n型区而使所述体区与所述阳极区分离。所述体区与所述阳极区之间的间隔长于所述体区与所述阳极区之间的所述n型区中的电子的移动率与电子的寿命的乘积。通过所述n型区而使所述阳极区与所述集电区分离。所述阳极区与所述集电区之间的间隔长于所述阳极区与所述集电区之间的所述n型区中的电子的移动率与电子的寿命的乘积。所述集电区的所述感测二极管区侧的端部与所述体区之间的间隔长于所述端部与所述体区之间的所述n型区中的电子的移动率与电子的寿命的乘积。

[0009] 另外,在本说明书中,“面积”是指在沿着半导体基板的厚度方向观察半导体基板

时的面积。

[0010] 在该半导体装置中,体区与阳极区之间的间隔长于二者之间的n型区中的电子的移动率与电子的寿命的乘积。因此,抑制了载流子在体区与阳极区之间移动的情况。此外,在该半导体装置中,阳极区与集电区之间的间隔长于二者之间的n型区中的电子的移动率与电子的寿命的乘积。因此,抑制了载流子在阳极区与集电区之间移动的情况。此外,在该半导体装置中,集电区的感测二极管区侧的端部与体区之间的间隔长于所述端部与体区之间的n型区中的电子的移动率与电子的寿命的乘积。在集电区的感测二极管区侧中,n型区露出于半导体基板的背面。该露出的n型区作为二极管的所谓的阴极而发挥功能。即,所述端部与体区之间的间隔相当于二极管的阴极与体区之间的间隔。由于该间隔长于n型区中的的移动率与电子的寿命的乘积,因此抑制了载流子在阴极与体区之间移动的情况。如此,在该半导体装置中,抑制了载流子在感测IGBT区与感测二极管区之间移动的情况。即,抑制了感测IGBT与感测二极管之间的电流干扰。因此,能够准确地检测出感测IGBT区以及感测二极管区的电流。

[0011] 上述的半导体装置可以采用如下的方式,即,在隔着所述感测二极管区而位于所述感测IGBT区的相反侧的区域内,还具有露出于所述半导体基板的所述背面的外部p型区。此外,通过所述n型区而使所述阳极区与所述外部p型区分离,所述阳极区与所述外部p型区之间的间隔长于所述阳极区与所述外部p型区之间的所述n区中的电子的移动率与电子的寿命的乘积。

[0012] 根据这样的结构,能够抑制载流子在阳极区与外部p型区之间移动的情况。

[0013] 本说明书公开的第二半导体装置具有半导体基板,所述半导体基板具有形成有IGBT的主IGBT区、形成有二极管的主二极管区、形成有IGBT的感测IGBT区、和形成有二极管的感测二极管区。所述感测IGBT区的面积小于所述主IGBT区。所述感测二极管区的面积小于所述主二极管区。在所述感测IGBT区内形成有:发射区,其为n型,并露出于所述半导体基板的表面;体区,其为p型,并与所述发射区相接;IGBT漂移区,其通过所述体区而与所述发射区分离;集电区,其为p型,并露出于所述半导体基板的背面,且通过所述IGBT漂移区而与所述体区分离;栅绝缘膜,其与所述体区相接;栅电极,其隔着所述栅绝缘膜而与所述体区对置。在所述感测二极管区内形成有:阳极区,其为p型,并露出于所述半导体基板的所述表面;二极管漂移区,其与所述阳极区相接;阴极区,其为n型,并通过所述二极管漂移区而与所述阳极区分离,且露出于所述半导体基板的所述背面,并且与所述二极管漂移区相比n型杂质浓度较高。通过所述IGBT漂移区以及所述二极管漂移区而使所述体区与所述阳极区分离,在所述IGBT漂移区与所述二极管漂移区之间,形成有与所述IGBT漂移区以及所述二极管漂移区相比n型杂质浓度较高的高浓度n型区。

[0014] 在n型杂质浓度较高的高浓度n型区中,通过n型杂质或缺陷而使载流子被扩散。在该半导体装置中,由于在IGBT漂移区与二极管漂移区之间形成有高浓度n型区,因此,抑制了在感测IGBT区与感测二极管区之间载流子移动的情况。因此,能够准确地检测出感测IGBT区以及感测二极管区的电流。

[0015] 在所述半导体装置中,可以采用如下的方式,即,所述高浓度n型区从半导体基板的上表面起延伸至与所述IGBT漂移区以及所述二极管漂移区的厚度方向的中央部相比而较深的位置为止。

[0016] 本说明书所公开的第三个半导体装置具有半导体基板，所述半导体基板具有形成有IGBT的主IGBT区、形成有二极管的主二极管区、形成有IGBT的感测IGBT区、和形成有二极管的感测二极管区。所述感测IGBT区的面积小于所述主IGBT区。所述感测二极管区的面积小于所述主二极管区。在所述感测IGBT区内形成有：发射区，其为n型，并露出于所述半导体基板的表面；体区，其为p型，并与所述发射区相接；IGBT漂移区，其通过所述体区而与所述发射区分离；集电区，其为p型，并露出于所述半导体基板的背面，且通过所述IGBT漂移区而与所述体区分离；栅绝缘膜，其与所述体区相接；栅电极，其隔着所述栅绝缘膜而与所述体区对置。在所述感测二极管区内形成有：阳极区，其为p型，并露出于所述半导体基板的所述表面；二极管漂移区，其与所述阳极区相接；阴极区，其为n型，并通过所述二极管漂移区而与所述阳极区分离且露出于所述半导体基板的所述背面，并且与所述二极管漂移区相比n型杂质浓度较高。通过所述IGBT漂移区以及所述二极管漂移区而使所述体区与所述阳极区分离。在所述IGBT漂移区与所述二极管漂移区之间形成有绝缘层。

[0017] 在该半导体装置中，由于在IGBT漂移区与二极管漂移区之间形成有绝缘层，因此，抑制了载流子在感测IGBT区与感测二极管区之间移动的情况。因此，能够准确地检测出感测IGBT区以及感测二极管区的电流。

[0018] 在上述的半导体装置中，可以采用如下的方式，即，所述绝缘层从半导体基板的上表面起延伸至与所述IGBT漂移区以及所述二极管漂移区的厚度方向的中央部相比而较深的位置为止。

## 附图说明

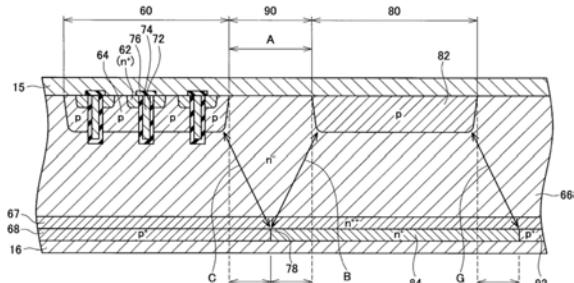

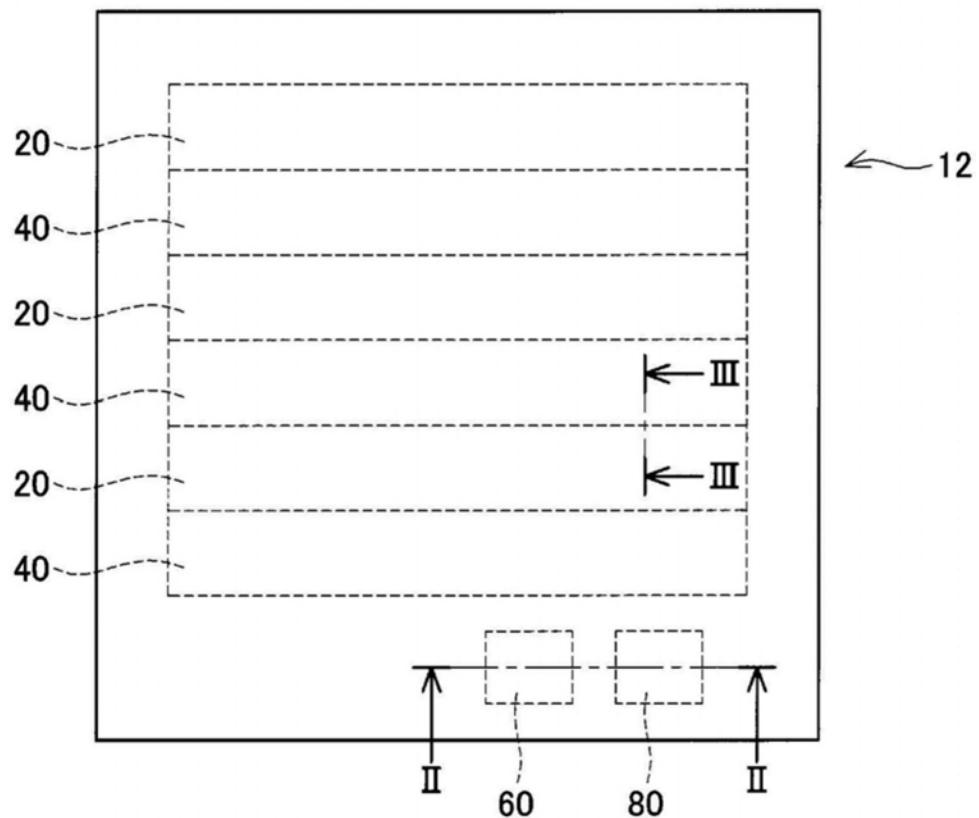

- [0019] 图1为半导体装置10的俯视图。

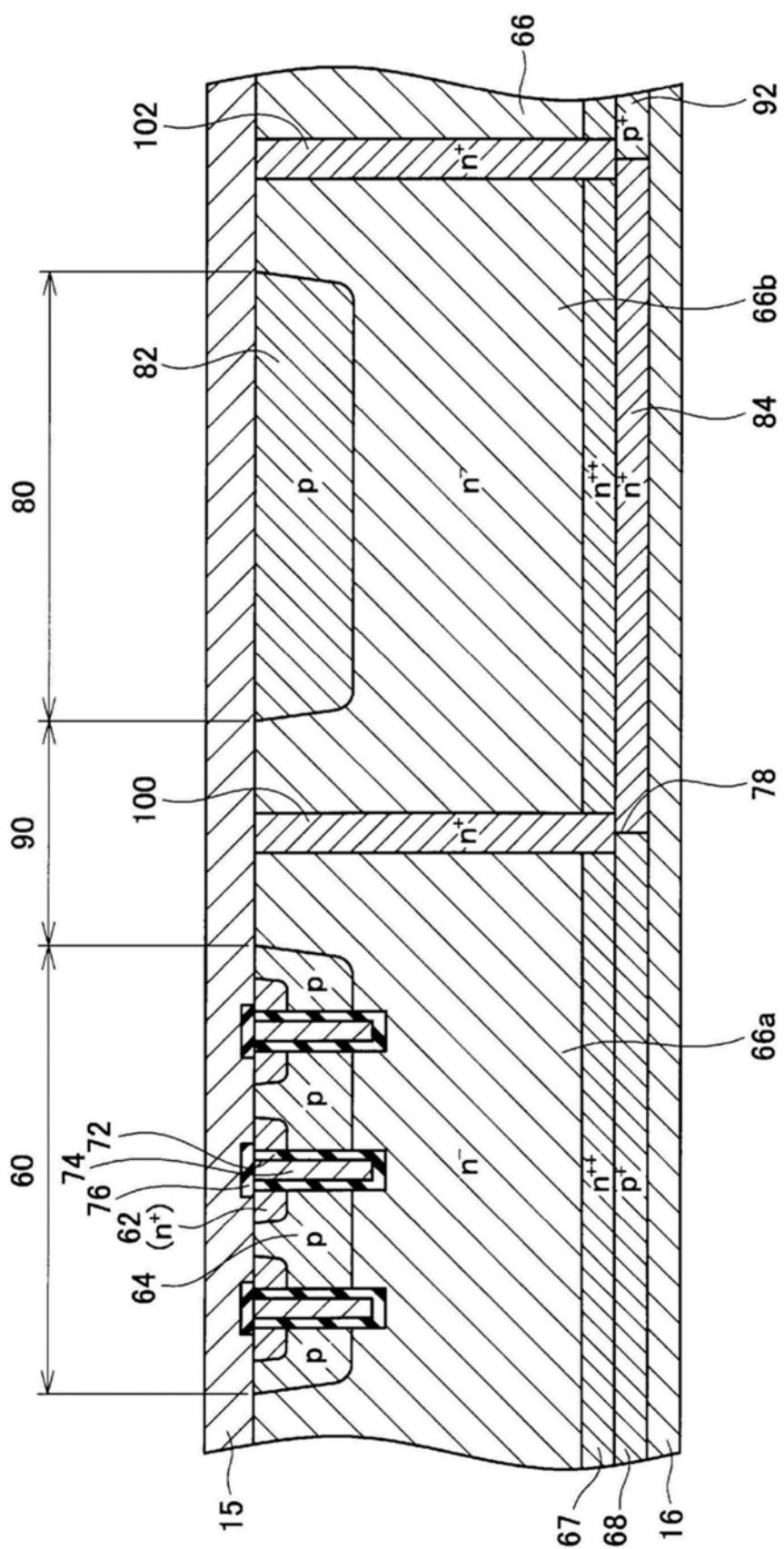

- [0020] 图2为图1的II-II线处的纵剖视图。

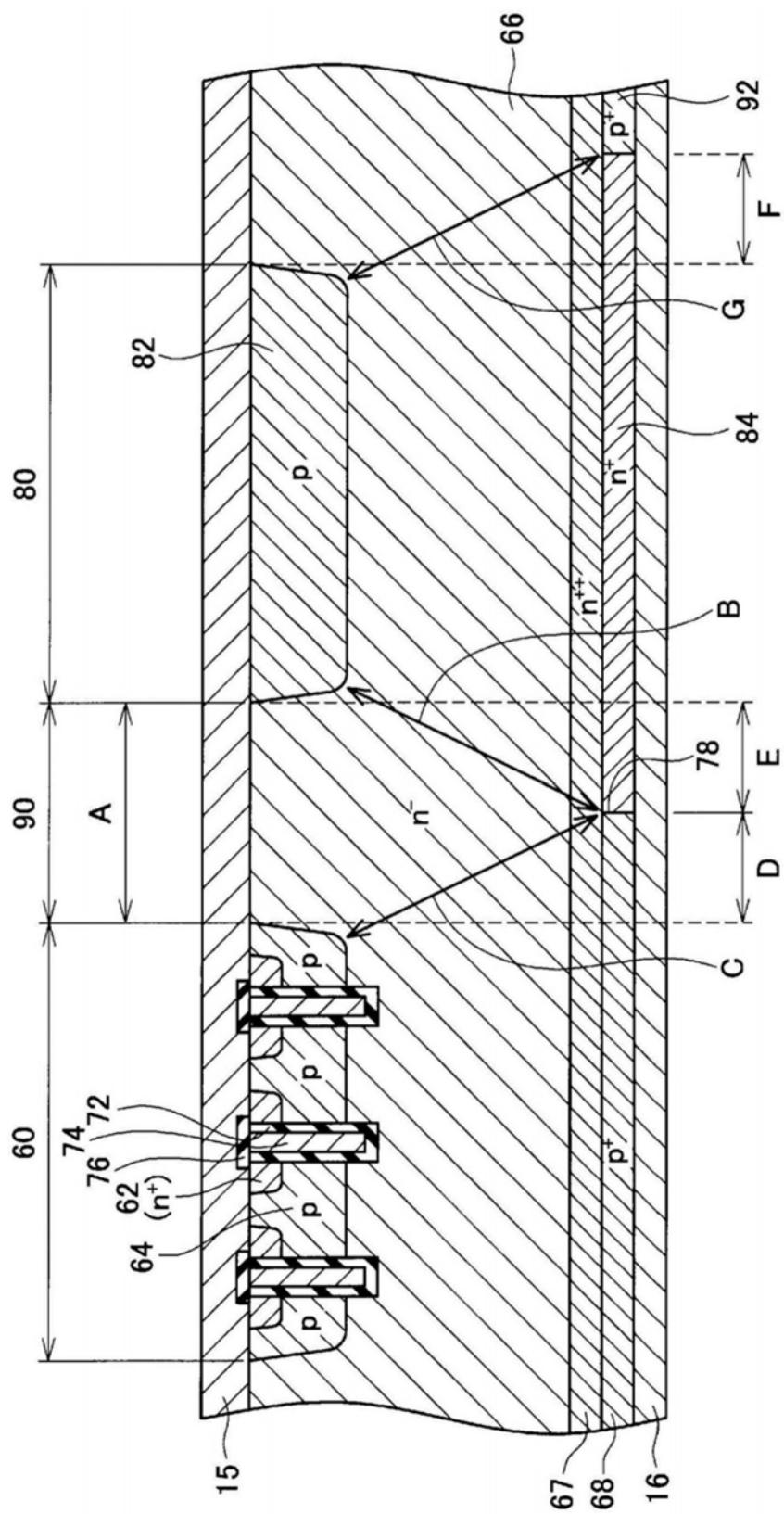

- [0021] 图3为图1的III-III线处的纵剖视图。

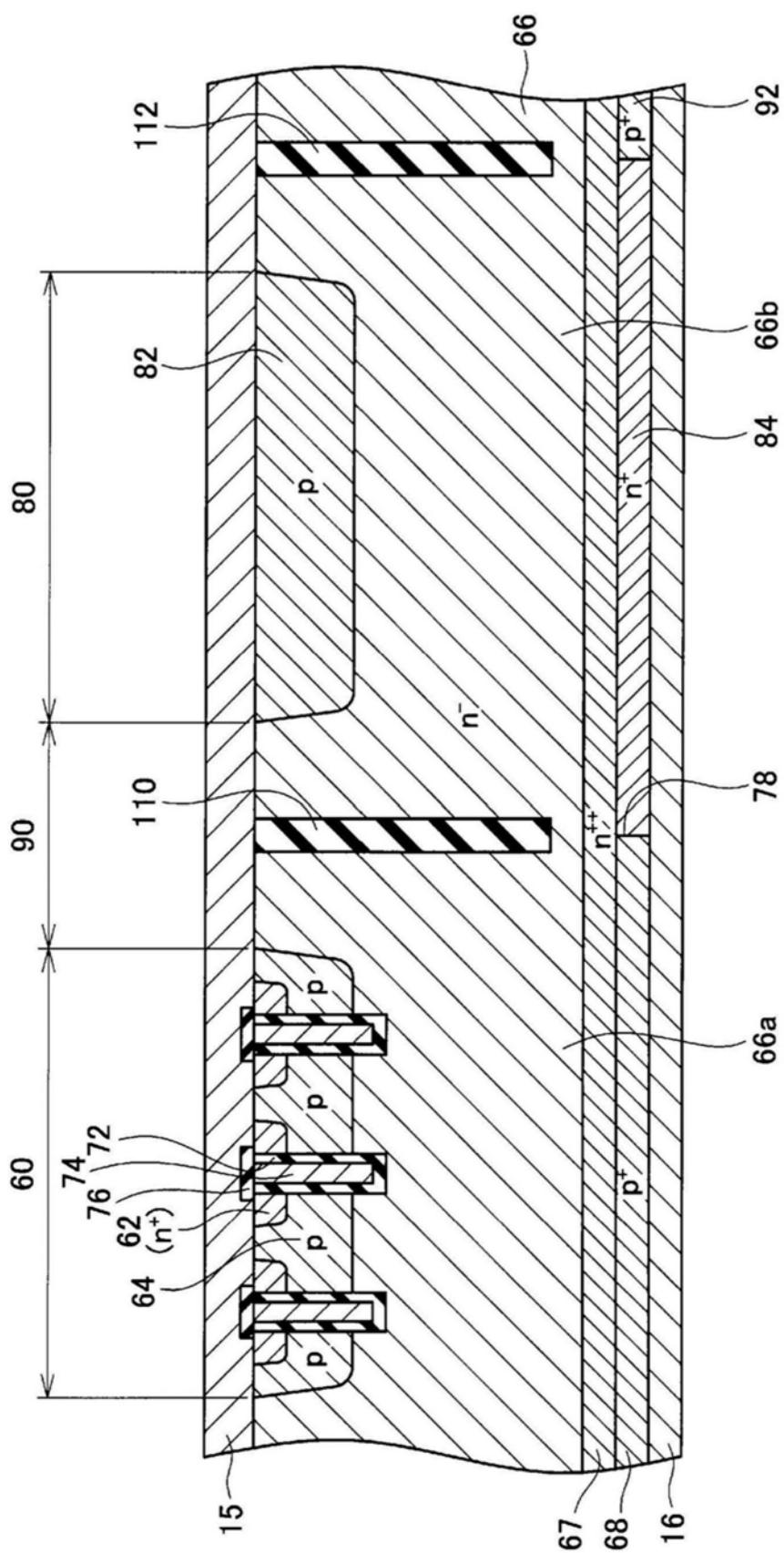

- [0022] 图4为实施例2的半导体装置的与图2对应的纵剖视图。

- [0023] 图5为实施例3的半导体装置的与图2对应的纵剖视图。

## 具体实施方式

- [0024] 实施例1

[0025] 图1所示的实施例的半导体装置10具有半导体基板12，所述半导体基板12上形成有主IGBT区20、主二极管区40、感测IGBT区60、感测二极管区80。以下，有时将主IGBT区20和主二极管区40统称为主区。此外，在下文中，有时将感测IGBT区60和感测二极管区80统称为感测区。主区被形成于半导体基板12的大致中央部处。在主区内交替反复地形成有多个主IGBT区20和多个主二极管区40。感测区被形成于主区的外侧。如图1所示，当俯视观察半导体基板12的表面时，感测IGBT区60的面积小于主IGBT区20的面积。在各个IGBT导通的情况下，在感测IGBT区60中将流有与相对于主IGBT区20的面积比率相对应的电流。因此，通过对流过感测IGBT区60的电流进行检测，从而能够检测出此时流过主IGBT区20的电流。此外，如图1所示，当俯视观察半导体基板12的表面时，感测二极管区80的面积小于主二极管区40的面积。因此，在各个二极管导通的情况下，感测二极管区80中将流有与相对于主二极管区40的面积比率相对应的电流。因此，通过对流过感测二极管区80的电流进行检测，从而能够检

测出流过主二极管区40的电流。

[0026] 图2表示感测区的截面结构。在感测区内,在半导体基板12的表面上形成有表面电极15,在半导体基板12的背面上形成有背面电极16。

[0027] 在感测IGBT区60内的半导体基板12内形成有发射区62、体区64、漂移区66、缓冲区67、集电区68。

[0028] 发射区62为n型区,并被形成在露出于半导体基板12的上表面的范围内。发射区62相对于表面电极15而被欧姆连接。

[0029] 体区64为p型区,并被形成在露出于半导体基板12的上表面的范围内。体区64从发射区62的侧方起延伸至发射区62的下侧。体区64相对于表面电极15而被欧姆连接。

[0030] 漂移区66为n型区,并被形成在体区64的下侧。漂移区66通过体区64而与发射区62分离。优选为,漂移区66的n型杂质浓度小于 $14 \times 10^{14}$ atoms/cm<sup>3</sup>。

[0031] 缓冲区67为n型区,并被形成在漂移区66的下侧。缓冲区67的n型杂质浓度高于漂移区66以及阴极区84。

[0032] 集电区68为p型区,并被形成在缓冲区67的下侧。集电区68被形成在露出于半导体基板12的下表面的范围内。集电区68相对于背面电极16而被欧姆连接。集电区68通过漂移区66而与体区64分离。

[0033] 在感测IGBT区60内的半导体基板12的上表面上形成有多个沟槽。各个沟槽被形成在与发射区62邻接的位置上。各个沟槽延伸至到达漂移区66的深度为止。

[0034] 感测IGBT区60内的各个沟槽的内表面被栅绝缘膜72覆盖。此外,在各个沟槽内配置有栅电极74。各个栅电极74通过栅绝缘膜72而与半导体基板12绝缘。各个栅电极74隔着栅绝缘膜72而与发射区62、体区64以及漂移区66对置。在各个栅电极74的上部形成有绝缘膜76。各个栅电极74通过绝缘膜76而与表面电极15绝缘。

[0035] 在感测二极管区80内的半导体基板12内形成有阳极区82、漂移区66、缓冲区67以及阴极区84。

[0036] 阳极区82被形成在露出于半导体基板12的上表面的范围内。阳极区82相对于表面电极15而被欧姆连接。

[0037] 在阳极区82的下侧形成有上述的漂移区66。在漂移区66的下侧形成有上述的缓冲区67。

[0038] 阴极区84为n型区,并被形成于感测二极管区80内的缓冲区67的下侧。阴极区84被形成在露出于半导体基板12的下表面的范围内。阴极区84具有与漂移区66相比而较高的n型杂质浓度。优选为,阴极区84的n型杂质浓度为 $1 \times 10^{18}$ atoms/cm<sup>3</sup>以上。阴极区84相对于背面电极16而被欧姆连接。

[0039] 在感测IGBT区60与感测二极管区80之间的分离区90中形成有上述的漂移区66以及缓冲区67。即,漂移区66以及缓冲区67从感测IGBT区60内起连续地延伸至感测二极管区80内。即,由漂移区66、缓冲区67、阴极区84构成的n型区以从感测IGBT区60跨至感测二极管区80的方式而延伸。通过分离区90内的漂移区66而使体区64与阳极区82分离。此外,通过分离区90内的漂移区66而使体区64与阴极区84分离。此外,通过分离区90内的漂移区66而使阳极区82与集电区68分离。此外,集电区68延伸至分离区90内,阴极区84延伸至分离区90内。在分离区90内形成有集电区68与阴极区84的边界78。

[0040] 此外,在露出于半导体基板12的背面的范围且在隔着阴极区84而位于集电区68的相反侧的区域中,形成有外部p型区92。即,阴极区84位于外部p型区92与集电区68之间。外部p型区92通过漂移区66而与阳极区82分离。

[0041] 体区64与阳极区82之间的距离A(最短距离)长于漂移区66的电子的移动率与漂移区66的电子的寿命的乘积。因此,防止了在体区64与阳极区82之间流有电子的情况。此外,由于漂移区66中的空穴的移动率与电子相比而较小,因此还防止了在体区64与阳极区82之间流有空穴的情况。因此,防止了在体区64与阳极区82之间流有电流的情况。

[0042] 阳极区82与集电区68之间的距离B(最短距离)长于漂移区66的电子的移动率与漂移区66的电子的寿命的乘积。另外,在本实施例中,缓冲区67的厚度相对于漂移区66的厚度而薄到可以忽视的程度。因此,通过如上述那样对距离B进行设定,从而防止了在阳极区82与集电区68之间流有电子的情况。此外,由于漂移区66中的空穴的移动率与电子相比而较小,因此还防止了在阳极区82与集电区68之间流有空穴的情况。因此,防止了在阳极区82与集电区68之间流有电流的情况。

[0043] 体区64与阴极区84之间的距离C(最短距离)长于漂移区66的电子的移动率与漂移区66的电子的寿命的乘积。另外,在本实施例中,缓冲区67的厚度相对于漂移区66的厚度而薄到可以忽视的程度。因此,通过如上述那样对距离C进行设定,从而防止了在体区64与阴极区84之间流有电子的情况。此外,由于漂移区66中的空穴的移动率与电子相比而较小,因此还防止了在体区64与阴极区84之间流有空穴的情况。因此,防止了在体区64与阴极区84之间流有电流的情况。另外,在将漂移区66和阴极区84视为共同的n型区的情况下,上述的距离C也可以称为体区64与集电区68的端面78之间的距离。

[0044] 阳极区82与外部p型区92之间的距离G(最短距离)长于漂移区66的电子的移动率与漂移区66的电子的寿命的乘积。另外,在本实施例中,缓冲区67的厚度相对于漂移区66的厚度而薄到可以忽视的程度。因此,通过如上述那样对距离G进行设定,从而防止了在阳极区82与外部p型区92之间流有电子的情况。此外,由于漂移区66中的空穴的移动率与电子相比而较小,因此还防止了在阳极区82与外部p型区92之间流有空穴的情况。因此,防止了在阳极区82与外部p型区92之间流有电流的情况。

[0045] 图3图示了主区(主IGBT区20和主二极管区40)的截面结构。在主区内的半导体基板12的表面上形成有表面电极14。在半导体基板12上,表面电极14与上述的表面电极15分离。在主区内的半导体基板12的背面上形成有与感测区共同的背面电极16。此外,在主区内也形成有上述的漂移区66和缓冲区67。即,漂移区66与缓冲区67以从主区跨至感测区的方式而延伸。主IGBT区20的结构与感测IGBT区60大致等同。即,主IGBT区20内的发射区22、体区24、集电区44、栅电极34、栅绝缘膜32以及绝缘膜36具备与感测IGBT区60大致相同的结构。此外,主二极管区40的结构与感测二极管区80大致等同。即,主二极管区40内的阳极区42以及阴极区30具备与感测二极管区80大致相同的结构。并且,在主二极管区40内也形成有上述的栅电极34以及栅绝缘膜32。但是在其他实施例中,也可以采用如下方式,即,不在主二极管区40内形成栅电极34以及栅绝缘膜32。

[0046] 接下来,对感测区的IGBT的动作进行说明。背面电极16相对于表面电极15为高电位,并且当栅电极74上被施加了阈值以上的电位时,感测IGBT区60内的IGBT将导通。即,在栅绝缘膜72的附近的体区64中形成有沟道,从而电子从表面电极15起经由发射区62、沟道、

漂移区66、缓冲区67以及集电区68而向背面电极16流动。此外，空穴从背面电极16起经由集电区68、缓冲区67、漂移区66以及体区64而向表面电极15流动。因此，在感测IGBT区60内，电流从背面电极16流向表面电极15。此时，由于在感测二极管区80内的二极管上施加有反向电压，因此二极管断开。即，在感测二极管区80中并未流有电流。在此，由于上述的距离A、B、C被设定为不会流有电流的距离，因此防止了在感测IGBT区60与感测二极管区80之间流有电流的情况。即，防止了感测IGBT区60与感测二极管区80之间的电流的干扰。

[0047] 此时，主区内的IGBT以及二极管以与感测区内的IGBT以及二极管同样的方式进行动作。因此，在感测区内的IGBT中流有电流时，在主区内的IGBT中也会流有电流。如上所述，由于防止了感测区中的电流干扰，因此流过感测IGBT区60的电流与流过主IGBT区20的电流的比率变得更接近于感测IGBT区60的面积与主IGBT区20的面积的比率。因此，通过对流过感测IGBT区60的电流(即，流过感测区的表面电极15的电流)进行检测，从而能够准确地检测出流过主IGBT区20的电流。

[0048] 接下来，对感测区的二极管的动作进行说明。当表面电极15相对于背面电极16为高电位时，感测二极管区80内的二极管将导通。即，电子从背面电极16起经由阴极区84、缓冲区67、漂移区66以及阳极区82而向表面电极15流动。此外，空穴从表面电极15起经由阳极区82、漂移区66、缓冲区67以及阴极区84而向背面电极16流动。因此，在感测二极管区80内，电流从表面电极15起流向背面电极16。此时，由于在感测IGBT区60内的IGBT上被施加有反向电压，因此IGBT断开。即，在感测IGBT区60中并未流有电流。在此，由于上述的距离A、B、C被设定为不会流有电流的距离，因此，防止了在感测IGBT区60与感测二极管区80之间流有电流的情况。此外，由于上述的距离G被设定为不会流有电流的距离，因此防止了在阳极区82与外部p型区92之间流有电流的情况。即，防止了感测二极管区80与其周围的区域(即，感测IGBT区60以及外部p型区92)之间的电流的干扰。

[0049] 此时，主区内的IGBT以及二极管以与感测区内的IGBT以及二极管同样的方式进行动作。因此，在感测区内的二极管中流有电流时，在主区内的二极管中也将流有电流。如上所述，由于防止了感测区中的电流干扰，因此流过感测二极管区80的电流与流过主二极管区40的电流的比率变得更接近于感测二极管区80的面积与主二极管区40的面积的比率。因此，通过对流过感测二极管区80的电流(即，流过感测区的表面电极15的电流)进行检测，从而能够准确地检测出流过主二极管区40的电流。

[0050] 另外，电子的移动率随着温度的变化而变化。因此，优选为，根据半导体装置10的动作时的温度而对所述距离A、B、C进行设定。例如，在半导体基板12为硅且半导体基板12的厚度为165μm且动作温度为150℃且漂移区66的n型杂质浓度为 $1 \times 10^{15} \sim 10^{17}$ atoms/cm<sup>3</sup>的情况下，通过将图2所示的距离D、E、F分别设为580μm以上，从而能够将上述的距离A、B、C、G设为不会产生电流干扰的距离。另外，距离D为体区64与边界78之间的横向(与半导体基板12的背面平行的方向)的距离，距离E为阳极区82与边界78之间的横向的距离，距离F为阳极区82与外部p型区92之间的横向的距离。

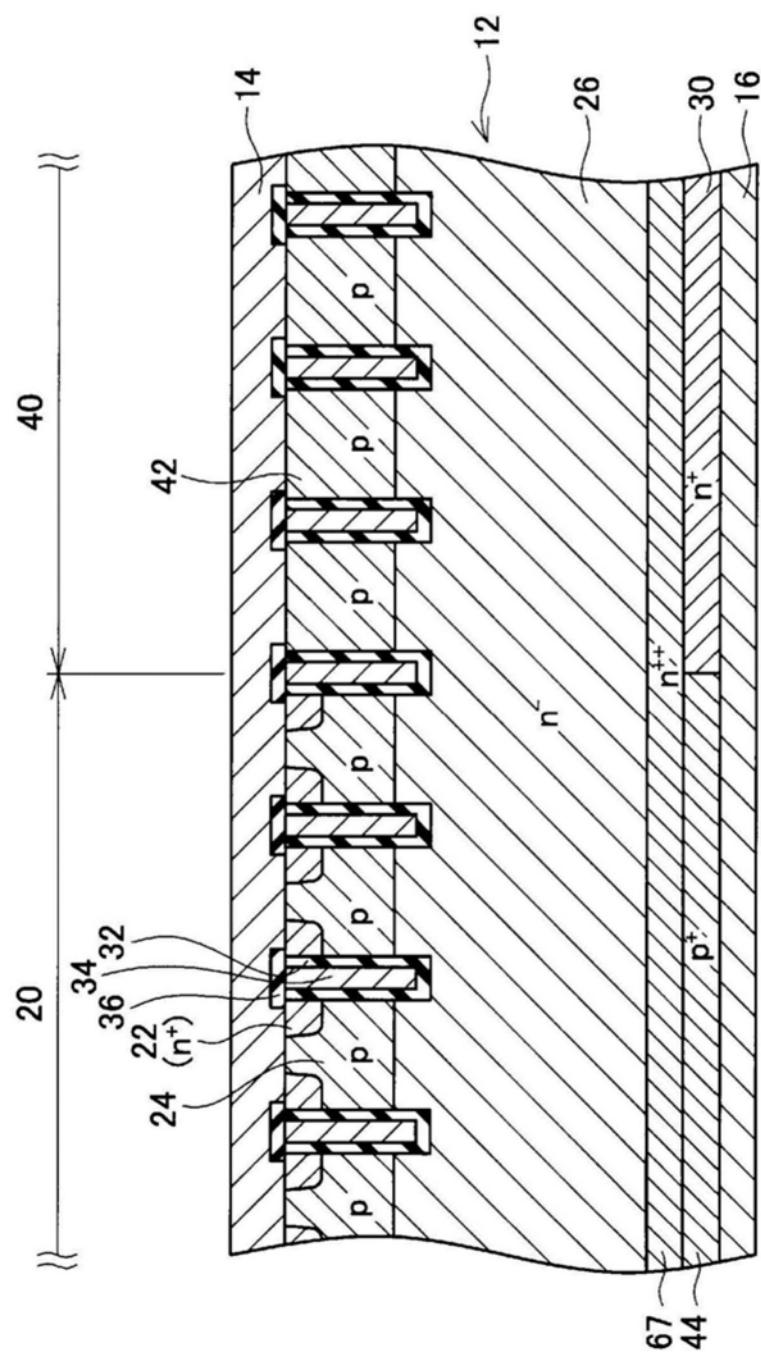

[0051] 实施例2

[0052] 除了高浓度n型区100、102之外，实施例2的半导体装置的结构与实施例1的半导体装置10等同。在实施例2的半导体装置中，如图4所示，在分离区90内的半导体基板12内形成有高浓度n型区100。高浓度n型区100具有与漂移区66相比而较高的n型杂质浓度。优选为，

高浓度n型区100的n型杂质浓度为 $1 \times 10^{16}$ atoms/cm<sup>3</sup>以上。高浓度n型区100从半导体基板12的表面起延伸至集电区68与阴极区84的边界78。因此,漂移区66被分隔为IGBT漂移区66a和二极管漂移区66b。此外,与高浓度n型区100大致相同的高浓度n型区102也被形成在外部p型区92与阴极区84的边界上。另外,在实施例2的半导体装置中,上述的距离A~G无论怎样设定均可。

[0053] 上述的高浓度n型区100、102具有高浓度的n型杂质。n型杂质使载流子扩散。由于高浓度n型区100被形成在感测IGBT区60与感测二极管区80之间,因此通过高浓度n型区100而防止了感测IGBT区60与感测二极管区80之间的电流干扰。此外,由于高浓度n型区102被形成在感测二极管区80与外部p型区92之间,因此通过高浓度n型区100而防止了感测二极管区80与外部p型区92之间的电流干扰。因此,通过对感测IGBT区60的电流进行检测,从而能够准确地检测出主IGBT区20的电流。此外,通过对感测二极管区80的电流进行检测,从而能够准确地检测出主二极管区40的电流。

[0054] 另外,虽然在图4中,高浓度n型区100、102从半导体基板12的表面起延伸至背面侧的区域(即,集电区68、阴极区84以及外部p型区92)为止,但是也可以采用如下方式,即,高浓度n型区100仅被形成于较浅的区域内。即,也可以采用以从半导体基板12的表面起至预定的深度为止的方式而形成高浓度n型区,并且在该高浓度n型区的下侧形成漂移区66(即,也可以不使IGBT漂移区66a与二极管漂移区66b完全分离)。但是,在这种情况下,优选为,高浓度n型区100、102从半导体基板12的表面起延伸至与漂移区66的厚度方向的中央相比而较深的位置处。通过到此程度的深度为止而预先形成高浓度n型区,从而能够有效地抑制电流干扰。此外,虽然在图4中高浓度n型区100、102以露出于半导体基板12的表面的方式而形成,但是也可以使高浓度n型区的上端位于半导体基板12的内部。在这种情况下,其他半导体层(例如,漂移区66)会存在于高浓度n型区的上端与半导体基板12的表面之间。即使采用这样的结构,但只要高浓度n型区的上端与半导体基板12的表面之间的间隔极短,则也能够充分地抑制电流干扰。

[0055] (实施例3)

[0056] 除了绝缘层110、112之外,实施例3的半导体装置的结构与实施例1的半导体装置10等同。在实施例3的半导体装置中,如图5所示,也可以在分离区90内的半导体基板12的表面上形成有沟槽,并且在该沟槽内形成有绝缘层110。绝缘层110从半导体基板12的表面起延伸至漂移区66内。在绝缘层110的下端的下侧存在漂移区66。即,在实施例3中,IGBT漂移区66a与二极管漂移区66b未完全分离。此外,与绝缘层110相同的绝缘层112也被形成在外部p型区92与阴极区84的边界上。并且,在实施例3的半导体装置中,上述的距离A~G无论怎样设定均可。

[0057] 由于绝缘层110被形成于感测IGBT区60与感测二极管区80之间,因此通过绝缘层110而防止了感测IGBT区60与感测二极管区80之间的电流干扰。此外,由于绝缘层112被形成在感测二极管区80与外部p型区92之间,因此通过绝缘层112而防止了感测二极管区80与外部p型区92之间的电流干扰。因此,通过对感测IGBT区60的电流进行检测,从而能够准确地检测出主IGBT区20的电流。此外,通过对感测二极管区80的电流进行检测,从而能够准确地检测出主二极管区40的电流。

[0058] 另外,在实施例3中,优选为,绝缘层110、112从半导体基板12的表面起延伸至与漂

移区66的厚度方向的中央相比而较深的位置处。通过到此程度的深度为止而预先形成绝缘层,从而能够有效地抑制电流干扰。此外,绝缘层110、112也可以贯穿漂移层66。此外,虽然在图5中绝缘层110、112以露出于半导体基板12的表面的方式而形成,但是也可以使绝缘层的上端位于半导体基板12的内部。即,绝缘层也可以埋入至半导体基板12内。在这种情况下,其他的半导体层(例如,漂移区66)会存在于绝缘层的上端与半导体基板12的表面之间。即使采用这样的结构,但只要绝缘层的上端与半导体基板12的表面之间的间隔极短,则也能够充分地抑制电流干扰。

[0059] 另外,虽然在上述的实施例1~3中对具有沟槽型的栅电极的半导体装置进行了说明,但是也可以将本说明书所公开的技术应用于具有平面型的栅电极的半导体装置中。

[0060] 此外,在其他的实施例中,也可以不形成缓冲区67。此时,集电区68、阴极区84以及外部p型区92与漂移区67相接。

[0061] 以上,虽然对本发明的具体示例进行了详细的说明,但是这些仅仅是例示而并非是对权利要求书进行限定的内容。权利要求书所记载的技术中包括对以上例示的具体示例进行各种各样的变形和变更的内容。

[0062] 本说明书或附图中所说明的技术要素通过单独或者各种组合而发挥技术上的有用性,但是并不限于申请时权利要求所记载的组合。此外,本说明书或附图所例示的技术为同时实现了多个目的的技术,并且实现其中的一个目的本身也具有技术上的有用性。

10

图1

图2

图3

图4

图5