(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5366552号

(P5366552)

(45) 発行日 平成25年12月11日(2013.12.11)

(24) 登録日 平成25年9月20日(2013.9.20)

(51) Int.Cl.

G06F 9/50 (2006.01)

F 1

G06F 9/46 465C

請求項の数 16 (全 22 頁)

(21) 出願番号 特願2008-538384 (P2008-538384)

(86) (22) 出願日 平成18年6月8日 (2006.6.8)

(65) 公表番号 特表2009-515246 (P2009-515246A)

(43) 公表日 平成21年4月9日 (2009.4.9)

(86) 國際出願番号 PCT/FR2006/050535

(87) 國際公開番号 WO2007/051935

(87) 國際公開日 平成19年5月10日 (2007.5.10)

審査請求日 平成21年6月8日 (2009.6.8)

(31) 優先権主張番号 0511266

(32) 優先日 平成17年11月4日 (2005.11.4)

(33) 優先権主張国 フランス (FR)

(73) 特許権者 510225292

コミサリア ア レネルジー アトミック

エ オ ゼネルジー アルテルナティブ

COMMISSARIAT A L' EN

ERGIE ATOMIQUE ET A

UX ENERGIES ALTERNA

TIVES

フランス, パリ エフー75015, リュ

ルブラン 25, バティマン ル ポ

ナン デ

Bâtiment Le Ponant

D, 25 rue Leblanc, F-

75015 Paris, FRANCE

(74) 代理人 100107641

弁理士 鎌田 耕一

最終頁に続く

(54) 【発明の名称】集中特化したマルチタスク及びマルチフロー処理をリアルタイム実行する手法及びシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

特定のマルチタスク及びマルチフロー処理をリアルタイム実行するシステムであって、

(a) タスク中の補助プロセッシング部 (APP) により処理されない演算処理を実行し、タスク制御を行う中央プロセッサコアと、(b) 前記補助プロセッシング部 (APP) により特定の演算処理を実行することを要求する追加の命令群を処理する制御ユニット (ESCU) と、を備えた標準プロセッシング部 (SPP) を備え、

前記補助プロセッシング部 (APP) が、(i) それぞれが、前記特定の演算処理に関して高速処理が可能となるように最適化され、かつ与えられた時間内でタスク中の1つの命令ストリームのみを実行するN個の補助演算ユニット (APU0, ..., APUN-1) と、(ii) エレメンタリな命令ストリームに分けられ、補助演算ユニットに割り当てる処理の並列処理を実行し、前記命令ストリームの実行環境の管理としてプリエンプション管理および前記補助演算ユニット間のデータ伝送管理を含む管理を行う補助リソース割り当て制御ユニット (ACU) と、(iii) 内部ネットワークを介して前記補助演算ユニット (APU0, ..., APUN-1) 間で共有されるメモリ空間 (SMS) と、を備え、

様々なシステム要素が、前記補助演算ユニット (APU0, ..., APUN-1) と前記中央プロセッサコアとの間の通信が前記共有メモリ空間 (SMS) と前記内部ネットワークとを介して行われるように配置されていることを特徴とするシステム。

## 【請求項 2】

10

20

前記補助演算ユニット( A P U 0 , . . . , A P U N - 1 )により取り扱うすべてのデータとプログラムを格納した大容量メモリ( M M )をさらに備えたことを特徴とする請求項 1 に記載のシステム。

**【請求項 3】**

前記大容量メモリ( M M )を制御するメインメモリ制御部( M M C )を備えたことを特徴とする請求項 2 に記載のシステム。

**【請求項 4】**

前記補助演算ユニット( A P U 0 , . . . , A P U N - 1 )がプログラマブルユニット、リコンフィギュラブルユニット、専用ユニットを備えたことを特徴とする請求項 1 から 3 のいずれか 1 項に記載のシステム。 10

**【請求項 5】**

前記中央プロセッサコアが、演算ユニット( S P U )と、メモリユニット( L 1 D - キャッシュ, L 2 I - キャッシュ, L 2 - キャッシュ)と、ローディングユニット( L S U )をさらに備えたことを特徴とする請求項 1 から 4 のいずれか 1 項に記載のシステム。 10

**【請求項 6】**

4 から 8 の補助演算ユニット( A P U 0 , . . . , A P U N - 1 )を備えたことを特徴とする請求項 1 から 5 のいずれか 1 項に記載のシステム。

**【請求項 7】**

第 1 にシステムバス( S B )の通信を優先し、第 2 に入出力装置( I O ) および前記大容量メモリ( M M )とともに前記中央プロセッサコアの通信を優先するように管理するバスアービター( S B A )を備えたことを特徴とする請求項 2 または 3 に記載のシステム。 20

**【請求項 8】**

システムバス( S B )に接続された複数個のプロセッサであって、前記プロセッサがそれぞれ、前記中央プロセッサコアと、前記 N 個の補助演算ユニット( A P U 0 , . . . , A P U N - 1 )と、前記共有メモリ空間( S M S )と、前記補助リソース割り当て制御ユニット( A C U )を備えたものであることを特徴とする請求項 1 から 7 のいずれか 1 項に記載のシステム。

**【請求項 9】**

前記システムバス( S B )に接続されている複数個のプロセッサ間で共有するシステムバスアービター( S B A )を備えたことを特徴とする請求項 8 に記載のシステム。 30

**【請求項 10】**

中央プロセッサコアを備えた少なくとも 1 つの標準プロセッサ部( S P P )と、 N 個の補助演算ユニット( A P U , . . . , A P U N - 1 )を備えた補助プロセッシング部( A P P )と、前記 N 個の補助演算ユニット( A P U , . . . , A P U N - 1 )で内部ネットワークを介して共有されるメモリ空間( S M S )と、前記補助プロセッシング部( A P P )および前記補助演算ユニット( A P U , . . . , A P U N - 1 )にタスク中の特定の演算処理を実行することを要求する追加の命令群を処理する制御ユニット( E S C U )と、補助リソース割り当て制御ユニット( A C U )と、を備えた少なくとも 1 つのプロセッサを用い、特定のマルチタスク及びマルチフロー処理をリアルタイム実行する方法であって、 40

前記中央プロセッサコアが、タスクにおける前記補助プロセッシング部( A P P )により処理されない演算処理を実行するとともにタスク制御を行い、前記補助演算ユニット( A P U , . . . , A P U N - 1 )が、それぞれ前記特定の演算処理に関して高速処理が可能となるように最適化され、かつ与えられた時間内でタスク中の 1 つの命令ストリームのみを実行し、前記補助リソース割り当て制御ユニット( A C U )が、エレメンタリな命令ストリームに分けられ、前記補助演算ユニット( A P U , . . . , A P U N - 1 )に割り当てる処理の並列処理を実行し、前記命令ストリームの実行環境の管理としてプリエンプション管理および前記補助演算ユニット間のデータ伝送管理を含む管理を行い、

前記補助演算ユニット( A P U 0 , . . . , A P U N - 1 )間の通信または前記補助演

算ユニット( A P U 0 、 . . . 、 A P U N - 1 )と前記中央プロセッサコアとの間の通信が前記共有メモリ空間( S M S )と前記内部ネットワークとを介して行われることを特徴とする方法。

**【請求項 1 1】**

各々の命令ストリームが一つの前記補助演算ユニットのみで実行されることを特徴とする請求項 1 0 に記載の方法。

**【請求項 1 2】**

前記補助演算ユニット( A P U 0 , . . . , A P U N - 1 )で取り扱われるすべてのデータおよびプログラムが大容量メモリ( M M )に格納され、前記プロセッサがシステムバス( S B )に接続され、前記中央プロセッサコア、入出力制御部( I O )および前記大容量メモリ( M M )からの前記システムバスへの通信がバスアービター( S B A )によって管理されていることを特徴とする請求項 1 0 に記載の方法。10

**【請求項 1 3】**

前記標準プロセッサ部( S P P )に割り当てられたタスクが、特定命令が出てくるまで前記標準プロセッサ部( S P P )のサイクルごとに処理されてゆき、前記特定命令に関してはデコードされると前記割り当て制御ユニット( A C U )に対するコマンドが生成され、前記割り当て制御ユニット( A C U )の制御によって前記補助演算ユニット( A P U 0 , . . . , A P U N - 1 )の一つで実行される命令ストリームが生成され、ひとたび、特定命令がデコードされ、対応する前記コマンドが生成された場合に、命令ストリームが生成され前記補助演算ユニットにおける実行が管理されても、前記標準プロセッサ部では干渉を受けることなく実行中の現タスクの継続が可能であることを特徴とする請求項 1 0 から 1 2 のいずれか 1 項に記載の方法。20

**【請求項 1 4】**

トラッピング処理がエクセプション処理、インタラプト処理、またはトラップ処理を伴う場合、トラッピングタイプの機能として、前記プロセッサ内のすべての構成要素が同期しなければならない、強い同期処理が選択される請求項 1 3 に記載の方法。

**【請求項 1 5】**

トラッピング処理がエクセプション処理、インタラプト処理、またはトラップ処理を伴う場合、トラッピングタイプの機能として、前記標準プロセッシング部に対応する実行環境は同期するが、補助リソース割り当て制御ユニット( A C U )は補助演算ユニットにて独立してアクティブとなっているファンクションの実行を継続させる、弱い同期処理が選択される請求項 1 3 または 1 4 に記載の方法。30

**【請求項 1 6】**

トラッピング処理が補助演算ユニットのローカルイベントを伴う場合、当該関係する前記補助演算ユニットのみが前記トラッピング処理を制御し、他のプロセッサとは独立して同期制御が実行される、選択的ローカル同期が有効となる請求項 1 3 から 1 5 のいずれか 1 項に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は集中特化したマルチタスク及びマルチフロー処理をリアルタイム実行する手法及びシステムに関する。

**【0 0 0 2】**

本発明は特に組み込み型マルチプロセッサーアーキテクチャに適している。

**【背景技術】**

**【0 0 0 3】**

本発明は以下の特徴を備えたシステムにおける処理に関する問題解決手段の提供を目的とする。

- ・高性能：組み込み型アプリケーションはますます複雑化しつつある。それは組み込み型システムにより多くの機能を実装する必要性にせまられていること(マルチメディア、ゲ

ーム、テレコミュニケーション、携帯電話におけるG P S機能利用等)、および、処理データ量が増大していること(ビデオセンサ、高速コンバーター等の能力向上)からも明らかである。組み込み型システムでは複数の情報処理を同時に並列処理する能力が求められている。それゆえシステム内に分散されている各ユニットにおいて並列処理に必要なすべての情報を効率的に収集、分配、処理することが独立に行われる必要がある。この多数の情報処理を同時に並列処理するという必要性は、マルチタスク実行環境においても同じである。

・柔軟性：ターゲットとなるシステムではオープン性が要求される。システムを利用するどのユーザーでも行いたい業務が自由に実行できなければならない。それゆえシステムのアーキテクチャは多様な利用用途に適するよう十分な柔軟性を備えていなければならぬ。このオープン性ゆえにアーキテクチャ全体にわたってアプリケーションコンテンツの実行前のオンライン状態での最適化は設計段階では十分に行うことができない。アルゴリズムによってはプロセスを単に静的に分割する並列制御が適當なもの(実行前のオンライン状態でも決められるもの)もあるが、その他のアルゴリズムでは実行中の動的ストリーム制御が要求されており、組み込みアプリケーションの複雑性の増大に伴ってこの傾向はますます強まるであろう。

・動作環境への統合性：システムは動作環境に統合されるように開発されなければならない。この統合性はリアルタイム性、消費電力、コスト、信頼性などの諸条件が反映される。

・異種処理(ヘテロプロセッシング)：アプリケーションの多様性と組み込みシステムにおける制御の流れの複雑性のため、様々なタイプの処理が組み込みアーキテクチャ内で共存せざるを得ない。それゆえ、集中処理タスクはアプリケーションの異なる要素間において干渉し合っても優先されるべき制御となっているタスクとして実行される必要がある。

#### 【0004】

以上まとめると、ターゲットとする組み込みシステムは、異なるデータストリームを実行環境に動的に適合させつつ処理する高い演算性能と通信性能とを備えている必要がある。組み込みシステムは同時に外部環境(消費電力、リアルタイム性等)により大きく制限され、オープンであることが要求され、複数マシンでの利用が前提となる。この環境には様々なタスクが(実行中にいて)動的に生成され、保持され、消去等されるというマルチアプリケーションシステム環境が含まれている。

#### 【0005】

このような組み込みシステムでは、アーキテクチャの実行前のオンラインでの最適化を行うと、リソース利用の正確な手順の決定が不可能であるために、リソースの利用不足を招いてしまうことが問題となる。そこで逆に、実行中のオンラインでの最適化に注力し、実行前にオンラインですべての処理動作を事前に予測する必要性を低減した方が良い。しかし、実行前にオンラインによるアーキテクチャの最適化ができないとなると余力あるコストパフォーマンスが高い高価な制御メカニズムが必要となってしまう。本発明は動的制御が統合されていない環境においてもパフォーマンスが低下しない計算機構造を提供することを目的とする。

#### 【0006】

実行中のシステムでの実行環境の競合において、並列処理を用いることはアプリケーションでのオペレーションレベルまたは命令レベルの並列処理での効果をもたらすものと考えられてきた。しかし、命令レベルでの高度な並列処理を可能とするアーキテクチャを研究することに注力されてきたものの、このアプローチには限界があることが明らかである。また、組み込みアプリケーションの複雑化により、単一の制御ストリームの形でモデリングすることは非常に難しいものである。それでもユーザやアーキテクチャ設計者はタスクレベルでの並列処理を求めている。その結果、現在の有力な技術トレンドは同じシリコン基板上にたくさんのプロセッサコアを組み込み、同一の回路基板上でタスクの並列処理を行うものとなっている。

#### 【0007】

10

20

30

40

50

パフォーマンスを向上させるものとして、並列処理を用いた手法に分類される多くの解決策が提案されている。主要なモデルは、同時マルチスレッディング (Simultaneous MultiThreading : SMT) と、チップマルチプロセッシング (Chip MultiProcessing : CMP) と、チップマルチスレッディング (Chip MultiThreading : CMT) である。

#### 【0008】

例えば、SMTテクノロジーは最新のインテル製品、IBMおよびHPのアルファプロセッサに実装されている。これらにおいて、複数の命令のストリームから選ばれた命令を実行処理する演算ユニットを割り当ててゆくために複数のプログラムカウンタが用いられている。タスクの相互依存性が限定的であるので、プロセッサにおける命令レベルでの並列処理 (ILP) が増加するため、プロセッサパフォーマンスも結果として向上する。これらプロセッサの実装は難しく、読み込みステージと命令分配ステージの複雑性が増す。結果として、これらアーキテクチャは大規模回路となってしまい、組み込みシステムの条件、特にコストと消費電力の条件面において合わなくなってしまう。

#### 【0009】

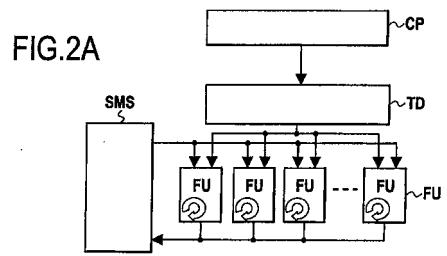

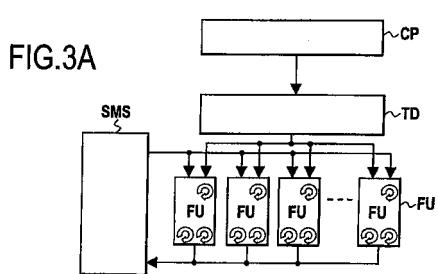

図1AはSMTアーキテクチャ理論を示すブロック図である。演算ユニットまたはファンクションユニットFUは、タスク割り当て器TDと連動する単一の制御リソースであるCPによりプロセスが与えられる。各サイクルにおいて、制御ブロックCPはタスク割り当て器TDと連動し、ファンクションユニットFUに対してデータ処理に利用可能な機能と処理上の問題点とを通知する。それぞれのファンクションユニットは共有メモリ空間SMSを共用し合う。

10

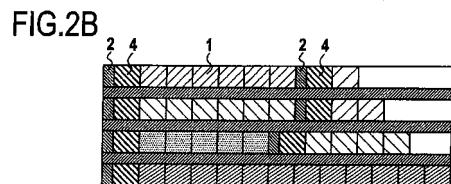

#### 【0010】

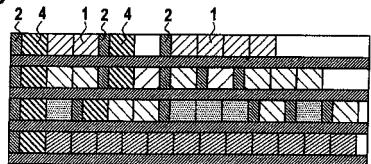

図1Bは、4つのファンクションユニットFUを備えた構成における処理操作の例を示している。この図では、各々のブロック1は命令を表わしており、縦軸2は命令割り当てと制御タスクを表わしている。

20

#### 【0011】

×印がついているブロック3は、データやリソースの依存性によりファンクションユニットには利用されていないタイムスロットに対応している。

#### 【0012】

次に、CMPを用いた技術は、比較的シンプルな実装で良いため、もともと組み込みシステムに適したものである。

30

#### 【0013】

このCMPを用いた技術は、利用可能性に応じて各々の演算リソースにタスクを分散するというものである。各々の演算リソースは次々と割り当てられたタスクを実行してゆく。これらアーキテクチャはホモ構造とヘテロ構造の2つのファミリーに分けることができる。

・ヘテロ構造：この構造はヘテロ構造で与えられたアプリケーション領域に最適化された演算ユニットが組み込まれ、コンパイル時に前もって認識されたリソースに対してタスクを分散するものである。コンパイル時にパーティション化されたソフトウェアは実行時ににおける（動的な）タスク分散のためにそのメカニズムが簡素化されている。これらアプリケーション指向のソリューションではOMAP、VIPER、PNXおよびノマディックプラットフォームを含んでいる。

40

・ホモ構造：これらの構造は、IBMセルプラットフォームやARMのMPコアプラットフォームや、与えられたアプリケーション領域に最適化されたもの、例えばMPEG4-AVCコーディング/デコーディング向けに最適化されたクレイドルテクノロジー社のCT3400のように、一般的に用いられるホモ構造の演算ユニットが組み込まれたものがベースとなっている。前者は広い範囲の問題を解決することをターゲットとしている。しかし後者は明らかに特定のアプリケーション領域に最適化されている。

#### 【0014】

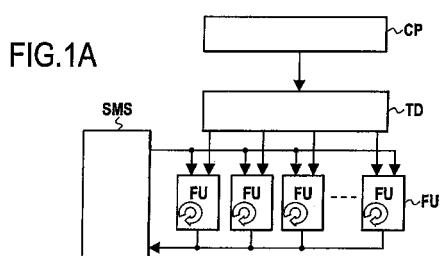

図2Aは、CMPアーキテクチャの理論を示すブロック図である。共有メモリ空間SMSと協働している演算ユニット（ファンクションユニット）FUに対して、タスク割り当

50

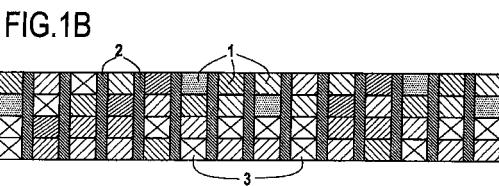

て器 T D と連動した単一の制御リソース C P によって処理が供給される。タスク割り当て器 T D に接続された制御ユニット C P は、タスクの実行準備が整っているか決定する。演算リソースが開放されるとすぐにタスクを割り当て、データがロードされるとすぐに処理が開始される。図 2 B は 4 つのファンクションユニット F U で構成された例を示しており、ハッチングが付けられて示されているブロック 4 がタスク処理開始を示している。ここで、ブロック 1 は命令を表し、縦線 2 は命令の割り当てとタスク制御を表している。

#### 【 0 0 1 5 】

次に、マルチプロセスアンド C M T アーキテクチャは、前記 2 つのモデルの組み合わせである。C M P コンセプトでは並列処理を専用の演算構成における複数タスクの実行処理まで拡張している。

10

#### 【 0 0 1 6 】

この技術は本質的にサーバータイプでの実行環境も想定されている。

#### 【 0 0 1 7 】

図 3 A は、汎用的 C M T アーキテクチャモデルを示している。演算ユニット（ファンクションユニット）にはタスク割り当て器 T D に接続されている単一の制御リソース C P によって処理が供給される。ファンクションユニット F U は共有メモリ空間 S M S と協働している。

#### 【 0 0 1 8 】

図 3 B はファンクションユニット F U における処理の例を示している。

#### 【 0 0 1 9 】

タスク割り当て器 T D と接続されている制御ユニット C P はタスクの実行準備が整ったか決定する。演算リソースが開放されるとすぐにタスクを割り当て、データがロードされるとすぐに処理が開始される。図 3 B にハッチングが付けられている領域 4 によってタスク処理開始が示されており、ブロック 1 は命令を表し、縦線 2 は命令の割り当てとタスク制御を表している。

20

#### 【 0 0 2 0 】

各々の演算リソースは多数のタスクを同時に管理している。例えばキャッシュ容量が足りなくなったりなどの理由でタスク処理が滞るとすぐに新しいファンクションユニット F U が割り当てられる。このような環境では、ファンクションユニット内でのタスクの切り替え処理には実行環境のロードペナルティが発生しない。

30

#### 【 0 0 2 1 】

実行性能を高めるために命令ストリーム（スレッド）の並列処理を用いるこれらアーキテクチャをベースとするエミュレーションにかかわらず、S M T であっても C M P であっても C M T であっても、これらアーキテクチャは組み込みシステムにおける諸問題を部分的にしか解決することができない。この事情の主な原因是、アプリケーションには異なる処理クラスのものが混在しておりそれらを区別ができないからである。そのため同じ処理リソースの中において、実行時間の観点からクリティカルであり制御が優先されるべき処理であっても他の通常処理と同一レベルに扱われてしまう。演算リソースは通常処理のサポートもクリティカル処理のサポートと同様に行ってしまい、最適化されていない演算結果しか得られないシステムとなり、消費電力の観点、コストパフォーマンスの観点、信頼性の観点の三重の観点からアプリケーションの要求には適さないものとなっている。

40

#### 【 0 0 2 2 】

しかしながら、C M P タイプのシステムでも通常処理とクリティカル処理を区別できるものがある。これらのアーキテクチャは特化した処理を実行できる専用の演算リソースが搭載されているものである。ここでイレギュラーな処理は汎用プロセッサのシステムソフトウェアを用いている。特化した処理を実行できる専用の演算リソースが搭載されているので、パフォーマンスや消費電力効率が改善されるように最適化されうるが、タスク処理間の通信、タスク処理とシステムソフトウェアまたは制御プロセス間の通信が非効率的であり、システムレベルではその最適化の恩恵を受けられない。アーキテクチャ内の様々な要素間の通信ではシステムバスが用られるが、通信バンド幅の不足によるペナルティを招

50

きやすい。そのため、システムには伝送制御情報が遅延してしまうというペナルティと、ビットレートが遅くなるというペナルティが発生し、データ伝送が乱れてしまう。これらペナルティにより応答性の遅いアーキテクチャということとなってしまい、システムソフトウェアは演算リソースを最適には使用できない。

#### 【0023】

このオーバーヘッドを低減するため、米国特許出願U.S.2005/0149937A1では演算リソース間の同期制御機構が専用構成となっているが、その解決方法ではタスク間のデータ伝送の問題には適用できない。米国特許出願U.S.2004/0088519A1では高性能プロセッサの実行環境におけるタスクの並列処理管理による解決方法を示しているが、その解決方法ではコスト面から組み込みシステムには適用できない。

10

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0024】

従来技術において開発されているタスクレベルでの並列処理を用いる解決方法は、上記問題のすべてを解決することはできない。SMTタイプの解決手段では、例えば、典型的には汎用プロセッサをベースとし、追加の制御ステージを付加するものであるが、しかしながら、その解決方法では従来の汎用プロセッサが持っている消費電力の問題を解決することはできず、加えて、多数のスレッドを並列処理管理するために複雑性が増大してしまう。

#### 【0025】

20

CMPタイプアーキテクチャの実装には多様なものがあるが、どれも上記問題を解決するために組み込みシステムに対して採用することは難しい。第1に、アプリケーション指向の解決は十分な柔軟性をもたらすことはできない。第2に、汎用アーキテクチャは演算による解決手段を提供できるものでなく、汎用プロセッサを開発するというコストのかかる解決方法をベースとし続けなければならない。同様に、CMTによる解決手段は、アーキテクチャによる並列処理を拡張したるものであるが、消費電力の要求を解決するものでなく、また、回路内での通信されるデータの一致性が保たれるように管理しなければならないという問題に直面してしまう。

#### 【0026】

本発明は、上記した障害を解決することを目的とし、特に、プロセッサにハイレベルの演算リソースを搭載することを可能とするものである。

30

#### 【課題を解決するための手段】

#### 【0027】

上記目的を達成するために本発明のシステムは、特定のマルチタスク及びマルチフロー処理をリアルタイム実行するシステムであって、アプリケーションのスレッドのうち、クリティカルでないスレッドは中央プロセッサコア自身で実行されるように割り当て、集中処理すべきまたは特定のスレッドは特定の命令に対して高速処理が可能なように最適化されているN個の補助演算ユニットを備えた補助プロセッシング部で実行されるように割り当て制御をする制御ユニットを備え、システムソフトウェアをサポートする中央プロセッサコアと、内部ネットワークを介して前記補助演算ユニット間で共有されるメモリ空間と、前記集中処理すべきまたは特定のスレッドに対応する各々の命令ストリームをまず並列に前記補助プロセッシング部に割り当て、次にこれら前記命令ストリームの実行を同期制御し、前記命令ストリームの実行環境を管理するように各々の補助リソースに対する制御を行う補助リソース割り当て制御ユニットとを備え、様々なシステム要素が、前記補助演算ユニット間の通信または前記補助演算ユニットと前記中央プロセッサコア間の通信が前記共有メモリ空間と前記内部ネットワークを介して行われるように配置されていることを特徴とする。

40

#### 【0028】

上記本発明のシステムは前記中央プロセッサコアに接続されたシステムバスを備えている。

50

**【 0 0 2 9 】**

また、上記本発明のシステムは、前記補助演算ユニットにより取り扱うすべてのデータとプログラムを格納した大容量メモリを備えている。

**【 0 0 3 0 】**

メインメモリ制御部は、前記大容量メモリに接続されている。

**【 0 0 3 1 】**

上記本発明のシステムにおいて、少なくとも一つの入出力周辺機器と接続された入出力制御部を備えている。入出力信号は共有メモリ空間を介して他のシステム要素において利用可能とされる。したがってクリティカルタイムにおいてもシステムの処理を行うことができる。

10

**【 0 0 3 2 】**

前記補助演算ユニットがプログラマブルユニット、リコンフィギュラブルユニット、専用ユニットから選ばれるユニットを備えた構成である。

**【 0 0 3 3 】**

前記共有メモリ空間が複数のメモリリソースと前記メモリリソースを統合する内部ネットワークを備え、前記共有メモリ空間において前記補助演算ユニットで取り扱うすべてのデータが格納されている。

**【 0 0 3 4 】**

前記共有メモリ空間がさらに、前記演算に関するリソースと前記共有メモリ空間内の前記メモリリソース間のリンクを確立せしめるメモリ空間制御部を備えている。

20

**【 0 0 3 5 】**

前記中央プロセッサコアが、演算ユニットと、メモリユニットと、ローディングユニットを備えている。

**【 0 0 3 6 】**

前記制御ユニットが、前記補助プロセッシング部を制御するための追加の命令群を備えている。

**【 0 0 3 7 】**

前記ローディングユニットが、前記中央プロセッサコアと前記補助プロセッシング部間でデータ交換するための追加レジスタキューを備えている。

**【 0 0 3 8 】**

前記補助演算ユニットのそれぞれが、一時にタスク中の一つの命令ストリームのみを処理するように制御され、アプリケーション向けに最適化され、N個の数が2から100で構成されている。

30

**【 0 0 3 9 】**

補助リソース割り当て制御ユニットが、動的消費電力管理、障害管理、クライシスマード管理の少なくとも一つ以上の管理機能を担っている。

**【 0 0 4 0 】**

一実施例として、第1に前記システムバスの通信を優先し、第2に前記中央プロセッサコアと前記大容量メモリ間の通信を優先するように管理するバスアービターを備えた構成がある。

40

**【 0 0 4 1 】**

また、一実施例として、システムバスに接続された複数個のプロセッサであって、前記プロセッサがそれぞれ、前記中央プロセッサコアと、前記N個の補助演算ユニットと、前記共有メモリ空間と、前記補助リソース割り当て制御ユニットを備えた構成がある。

**【 0 0 4 2 】**

上記システム構成として、前記システムバスと前記中央プロセッサコア間の通信を管理するバスアービターを備えた構成がある。

**【 0 0 4 3 】**

上記システム構成として、前記複数のプロセッサ間で共有される大容量メモリを備えた構成がある。

50

**【0044】**

また、本発明は、中央プロセッサコアと、コントロールユニットと、N個の補助演算ユニットと、前記N個の補助演算ユニットで内部ネットワークを介して共有されるメモリ空間と、補助リソース割り当て制御ユニットを備えた少なくとも一つのプロセッサ上で用いられる特定のマルチタスク及びマルチフロー処理をリアルタイム実行する方法であって、前記中央プロセッサコアが、システムソフトウェアを実行するとともに、前記制御ユニットが、アプリケーションのスレッドのうち、クリティカルでないスレッドは前記中央プロセッサコア自身で実行されるように割り当て、集中処理すべきまたは特定のスレッドは特定の命令に対して高速処理が可能なように最適化されているN個の補助演算ユニットを備えた補助プロセッシング部で実行されるように前記補助リソース割り当て制御ユニットを介して割り当て制御をし、前記補助リソース割り当て制御ユニットが前記集中処理すべきまたは特定のスレッドに対応する各々の命令ストリームをまず並列に前記補助ユニットに割り当て、次にこれら前記命令ストリームの実行を同期制御し、前記命令ストリームの実行環境を管理するようにし、少なくとも、データ通信が前記補助演算ユニット間の通信または前記補助演算ユニットと前記中央プロセッサコア間の通信が前記共有メモリ空間と前記内部ネットワークを介して行われることを特徴とする。10

**【0045】**

上記システムにおいて、前記制御ユニットが、標準のリード命令／標準のライト命令または標準のエクセプション命令によって、前記補助リソースの前記割り当て制御ユニットを制御する。20

**【0046】**

前記制御ユニットが、通信および同期処理に特化した特別の命令群によって、前記補助リソースの前記割り当て制御ユニットを制御する。

**【0047】**

与えられた時間内で、前記補助演算ユニットのそれぞれが一時にタスク中の一つの命令ストリームのみを処理し、各々の命令ストリームが一つの前記補助演算ユニットで実行される。

**【0048】**

前記補助演算ユニットで取り扱われるすべてのデータおよびプログラムが大容量メモリに格納されている。30

**【0049】**

クリティカル時には、入出力信号が共有メモリ空間を介して前記補助演算ユニットに伝送される。

**【0050】**

前記プロセッサはシステムバスに接続されている。

**【0051】**

一実施例として、第1に前記システムバスの通信を優先し、第2に前記中央プロセッサコアと前記入出力装置間の通信を優先するように管理するバスアービターを備えた構成がある。

**【0052】**

前記中央プロセッサコアに割り当てられたタスクが、特定命令が出てくるまで前記中央プロセッサコアのサイクルごとに処理されてゆき、前記特定命令に関してはデコードされると前記割り当て制御ユニットに対するコマンドが生成され、前記割り当て制御ユニットの制御によって前記補助演算ユニットの一つで実行される命令ストリームが生成され、ひとたび、特定命令がデコードされ、対応する前記コマンドが生成された場合に、命令ストリームが生成され前記補助演算ユニットにおける実行が管理されても、前記中央プロセッサコアでは干渉を受けることなく実行中の現タスクの継続が可能である。40

**【0053】**

トラッピング処理がエクセプション処理、インタラプト処理、またはトラップ処理を伴う場合、トラッピングタイプの機能として、前記プロセッサ内のすべての構成要素が同期

しなければならない、強い同期処理が有効となる。

【0054】

また、トラッピング処理がエクセプション処理、インタラプト処理、またはトラップ処理を伴う場合、トラッピングタイプの機能として、前記標準プロセッシング部に対応する実行環境は同期するが、補助リソース割り当て制御ユニット（A C U）は補助演算ユニットにて独立して命令ストリームの実行を継続させる、弱い同期処理が選択される。

【0055】

トラッピング処理が補助演算ユニットのローカルイベントを伴う場合、当該関係する前記補助演算ユニットのみが前記トラッピング処理を制御し、他のプロセッサとは独立して同期制御が実行される、選択的ローカル同期が有効となる。

10

【0056】

従来技術とは異なり、本発明はプロセッサ内の演算リソースを強く統合することができる新しい結合メカニズムを実現している。

【0057】

本発明のシステムアーキテクチャは、第1のサブシステムは中央プロセッサコアを形成する標準プロセッシング部（S P P）を備え、第2のサブシステムは補助プロセッシング部（A P P）を備え、補助プロセッシング部（A P P）には補助演算ユニットと制御割り当て補助リソースと共にメモリ空間が実装されている。

【0058】

2つのサブシステムは異なる特性と機能を持っているが、タスクを実行するという同じ目的を持っている。結果として、これらの機能はデータ処理および制御レベルで強く結合されている。

20

【発明を実施するための最良の形態】

【0059】

本発明の他の特徴や利点は以下の実施例に関する詳細な説明と参照する添付図面から明らかになるであろう。

【0060】

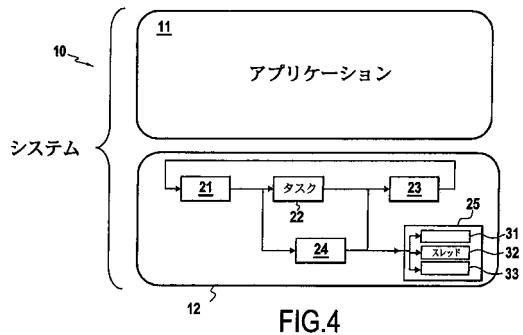

システム10は、アプリケーション11、12、さらにタスク21から25、最終的に命令（スレッド）31から33の流れに細分化されているが、まず、いわゆる“ライトプロセス”と呼ばれるものを図4を参照しつつ説明する。

30

【0061】

組み込みシステム10は典型的には多数のアプリケーション11や12などのプロセスの並列処理に用いられる。アプリケーションは組み込みシステムにより提供される機能やサービスを用いる。組み込みシステムで処理されるどのアプリケーション11、12もタスク21から25の形に分割され、アプリケーションの記述による制御依存性に応じて一連のものにまとめられている。これらのタスク21から25は、並列処理が可能となるようシーケンシャルに実行される操作処理ごとに並列スレッド31から33に分割される。

【0062】

この詳細な説明において、スレッドという語は、他のプロセスとアドレス空間全体を共有することができる実行ストリームであるライトプロセスを表わすものとして使用されている。

40

【0063】

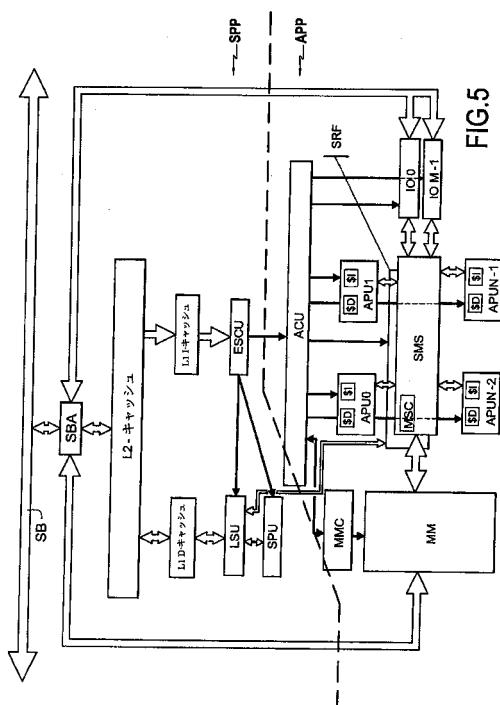

図5は、本発明のプロセッサアーキテクチャの例を示す図である。第1のサブシステムは中央プロセッサコアを形成する標準プロセッシング部S P Pを備え、第2のサブシステムは補助プロセッシング部A P Pを備えている。

【0064】

標準プロセッシング部S P Pは一般的なタスクの実行処理を担っている。処理されるべきプログラム命令とシステムソフトウェアとを含んでいる。従来技術のプロセッサとは違い、標準プロセッシング部S P Pは、補助プロセッシング部A P Pの補助実行ユニットA

50

P U 0、A P U 1、…、A P U N - 2、A P U N - 1をコールして、強力な演算パワーを必要とするアプリケーション部分を実行させる。

#### 【0065】

本発明は、補助演算ユニットをコールという方法によって特定のプロセスを実行する。

#### 【0066】

標準プロセッシング部S P Pは、アプリケーションにおける汎用的な演算処理を担う。また、標準プロセッシング部S P Pは、リソース共有とタスク制御とを管理するシステムソフトウェアも処理する。標準プロセッシング部S P Pは、汎用プロセッサにより形成されている。それゆえ、以下の従来型の4つのユニットを含んでいる。

1. コントロールユニットE S C U：このユニットは、命令読み込み処理と、デコード処理を担っている。このユニットの複雑さは多様である。多数の命令を同時に管理することができ、また、アプリケーションでの記述順序によらず、実行準備が整った順に命令を選ぶことができる。このユニットは命令分岐予測に必要な予測機構を実装している。このユニットはアーキテクチャ内の他のユニットに対する命令としてコマンドを送信する。10

2. 演算ユニットS P U：このユニットは命令により記述されている汎用的演算の実行を担っている。このユニットはコントロールユニットE S C Uが複数の命令を同時に管理できるように複数の演算リソースを実装している。

3. メモリユニット：このユニットはプログラムに関連するデータと命令の格納を担っている。メモリユニットはハーバード実行モデルの2階層レベルのキャッシュメモリ階層をベースとし、統合レベルの2つのキャッシュを伴っている。20

このメモリユニットは、レベル1のキャッシュメモリであるL 1 - キャッシュ、L 1 - キャッシュ、レベル2のキャッシュメモリであるL 2 - キャッシュを備えている。

4. ローディングユニットL S U：ローディングユニットはメモリに格納されているデータと演算ユニットS P Uによって稼動しているユニットとの間にリンクを張る処理を担っている。このリンクは標準プロセッシング部S P P内のサイクルあたりの命令処理数の能力に応じて決まる数のポート数のレジスタキューという形となっている。

標準プロセッシング部S P Pと補助プロセッシング部A P P間の密接なカップリングを提供するため、標準的な中央プロセッサコアと比較し、コントロールユニットE S C UとローディングユニットL S Uに対して幾つかの特徴が加えられている。

#### 【0067】

コントロールユニットE S C Uは、補助プロセッシング部A P Pを制御するための追加命令群を備えている。例えば、これらの命令群はクリティカルプロセスの実行を要求するものである。クリティカルプロセスは標準的なメカニズムによっても実行はできるが、追加命令群では命令実行によって新たな命令を要求することがない（例えば、実行後にメモリ空間へのマッピング処理を伴うようなメソッド）。

#### 【0068】

ローディングユニットL S Uは追加のレジスタキューが実装されている。このように標準の汎用レジスタキューに第2のレジスタキューをローディングユニットL S Uに追加実装し、S P PとA P Pの2つのサブシステム間でのデータ交換を可能としている。

#### 【0069】

構造の点から見て、ローディングユニットL S Uレベルの補助レジスタA R F列と汎用レジスタG P R F列では違いはない（図8および図9参照）。プロセッサはアドレスの違いにより汎用レジスタと補助レジスタとを区別している。このS P PとA P Pの2つのサブシステム間のコミュニケーションモードは特に少量のデータの伝送には適したものといえる。

#### 【0070】

補助プロセッシング部A P Pはアプリケーション内の特化した及び／又は集中的な演算処理を担っている。補助プロセッシング部A P Pは独自のメモリ空間S M Sを共有し合っている多数の補助演算ユニットA P U 0、A P U 1、…、A P U N - 2、A P U N - 1が実装されている。補助演算ユニットA P U 0、A P U 1、…、A P U N - 2、A40

50

20

30

40

50

PUN-1の数Nは特に制限は受けない。同様に、これら演算要素は、相互に区別ができないAPUで単純に定義されるものであるか、同期ロジックまたは非同期ロジックをベースとするものであるかによって違いはない。それゆえ補助プロセッシング部APPはGALS(グローバル非同期制御・ローカル同期制御)タイプの構成の実装に非常に便利である。補助プロセッシング部APPは典型的には4個から8個の演算要素APUを備えている。サイクル内では補助演算ユニットAPUは一つのスレッドのみを実行し、一つのスレッドは一つの補助演算ユニットAPUのみで実行される。

#### 【0071】

一組のライトプロセス(スレッド)は、コントロールユニットESCUから補助プロセッシング部APPに含まれている割り当て制御ユニットACUを介して、次の実行処理を要求する補助演算ユニットAPUに割り当てられる。10

#### 【0072】

スレッドの補助演算ユニットAPUへの物理割り当て処理、実行管理、異なるスレッドに含まれている同期処理は割り当て制御ユニットACUが担う。

#### 【0073】

補助プロセッシング部APPには、クリティカル入出力コントローラI/Oが実装されている。これらは例えば、高速ADコンバータ、ラジオ周波数インターフェイス、ビデオセンサ等のクリティカル入出力周辺機器にダイレクトにリンクされている。これらM個の入出力コントローラI/OからIOM-1は割り当て制御ユニットACUにより補助演算ユニットAPUとして取り扱われる。割り当て制御ユニットACUは入出力コントローラに入出力アクセスを管理できるようにタスクを割り当てなければならない。データは共有メモリ空間SMSに対して送信され、または共有メモリ空間SMSから受信される。しかしながら、クリティカル入出力は、例えば、キーボードまたはマウス操作に応じて、システムバスSBなどのより汎用的手段によって標準プロセッシング部SPPを用いることができる。20

#### 【0074】

補助プロセッシング部APPは補助演算ユニットで取り扱われるすべてのデータとプログラムを格納する大容量メモリMMを含んでいる。このメモリMMは、システム(図5ではシステムバスSBとして示されている)と特化した演算スレッド間のデータ伝送を行うスレッドを割り当てる割り当て制御ユニットACUを制御するコントローラMMCを含んでいる。このコントローラMMCは共有メモリ空間SMSと大容量メモリMM間のデータ伝送にも関連している。30

#### 【0075】

補助演算ユニットAPUは、特定の処理に関して高速処理が可能なように最適化されている。補助演算ユニットAPUは機能に応じてパフォーマンス、フレキシビリティ、コスト、消費電力間においてトレードオフが成り立っている。どの種類の演算ユニットを選択するかはアプリケーション実行環境に強く影響される。

#### 【0076】

補助演算ユニットは、プログラマブルユニット、リコンフィギュラブルユニット、専用ユニットを備える構成も可能である。40

- ・**プログラマブルユニット**: このユニットタイプは、組み込み演算に対しては汎用プロセッサコア(MIPS、ARM等)または最適化プロセッサコア(DSP、ST2xx等)に相当するものである。演算に最適化されているため、結果として制御構造がシンプルなものとなっており、例えば分岐予測機構、割り込み処理機構、擬似データ処理機構などが省かれている。これらユニットは浮動小数点演算やベクトル演算などに特化した演算ユニットを構成することができる。

- ・**リコンフィギュラブルユニット**: リコンフィギュラブルユニットは演算アクセラレータ同等のものとして用いられる。大規模構造はその処理能力から再構成処理には有利であり、処理能力とフレキシビリティとはトレードオフの関係となる。小規模構成は、非常にフレキシビリティが必要とされる処理または非常に小さいサイズ(1ビットから4ビット)50

程度のデータ処理に適している。再構成処理のためには長い時間が必要となるため、プリエンプションによる優先割り当てを避けられるように小規模構成のリソースは別々に管理されることが好ましい。

・専用ユニット：特定のクリティカルな処理に最適化され、コンポーネントに組み込まれている。専用アクセラレータは、プログラマブルまたはリコンフィギュラブルな構成では十分な演算パワーを提供できない場合に、クリティカルな処理を担当することが想定されている。高速暗号処理や入出力ストリーム管理処理はこの専用ユニットを用いる良い対象である。

#### 【0077】

ユニットタイプにかかわらず、補助演算ユニットAPPは特定の記憶要素として利用することができる。アクセスを高速化するために中間データを記憶する用途や共有メモリ空間のバンド幅を最小化する用途、実行中のプログラム命令を記憶する用途のいずれでも利用することができる。タスク割り当て段階を高速化するために実行中のプログラムをローカルに記憶することができる。

10

#### 【0078】

2つのサブシステムSPPおよびAPPは他のシステムへのアクセス手段を共有することができる。通信経路はシステムバスSBであり、バスアービターSBAによりシステムバスの共有使用が管理される。例えばメインメモリと入出力コントローラI/Oなど補助プロセッシング部APPの2つの要素がシステムバスに対してアクセスを要求することができる。標準プロセッシング部SPPからみれば、システムバスSBへのアクセスは、キャッシュメモリL2 - キャッシュに大容量メモリまたは周辺機器から渡されるデータと命令がロードされることとなる。プロセッサの一つ以上の要素から同時にアクセス要求が出された場合、バスアービターSBAはシステムバスSBを介した通信を保証するためアクセス要求を順番に並べる。

20

#### 【0079】

アクセスする各構成要素から要求されるバンド幅はアプリケーション実行環境の機能に応じて可変となっている。このスキームはたくさんの構成要素が同時に大きいバンド幅を要求するようなアプリケーションに適している。システムのすべての構成要素に対して十分なバンド幅を提供するため第2の（場合によっては第3の）システムバスを追加する構成も可能となる。

30

#### 【0080】

一構成例を詳しく下記に示す。

#### 【0081】

標準プロセッシング部SPPで実行中のシステムソフトウェアによって同じSPPに対してタスクが割り当てられると、SPPはプログラマブルプロセッサで従来から用いられている方法にてプログラムを実行してゆく。命令処理は特定の命令が出てくるまでサイクルごとに進んでゆく。特定の命令が制御ユニットESCUによりデコードされると、割り当て制御ユニットACUに対してコマンドが生成され、補助演算ユニットの一つで実行されるスレッドが生じる。このような状況下、割り当て制御ユニットACUは実行管理を担う。この実行モデルはライブラリの最適ファンクションがコールされることにより演算スレッドがアクティブとなるようなプログラマブルモデルに適している。このアプローチは組み込みソフトウェアの分野では既に広く使われており、例えば汎用プロセッサのAltivec命令やMMX命令に相当するものである。

40

#### 【0082】

制御ユニットESCUによって特定命令が渡されると、標準プロセッシング部SPPは補助プロセッシング部APPによるスレッド管理に干渉することなくプログラムの実行を継続する。このプログラム実行は、スレッドの生成や破棄や補助プロセッシング部APPにおいてデータ読み込みなどを生じさせる次の特定命令の処理に至るまで継続される。

#### 【0083】

実行や割り込みやトラップを伴うトラッピング処理は以下の3つの動作を前提としている

50

る。

1. 強い同期性：（サブシステムAPPおよびSPPの両方の）すべてのプロセッサの構成要素が同期している。この同期処理には長時間を要するので、部分的な同期手法を採ればマルチタスク処理の実行環境におけるペナルティを低減させることができる。実行環境の書き換えを高速化するためにビクティムキャッシュなどを用いて大容量メモリへ書き込む内容はしばらくの間保持される。

2. 弱い同期性：標準プロセッシング部SPPに関する実行環境のみが同期しているものである。この状態では補助プロセッシングユニットAPUによりアクティブとなっているファンクションは補助プロセッシング部APPにおいて維持されている。割り当て制御ユニットACUは補助リソースの割り当てのみを担う。APPの自律的処理はスレッドが標準プロセッシング部SPPのタスクが生成したデータをコールしない限り継続される。10

3. ローカル同期性：トラッピングが例えば0の除算など補助演算ユニットAPUのイベントコールを伴う場合、ユニットはトラッピングのみを管理し、他のプロセッサからは独立した同期性をとる。

#### 【0084】

割り当て制御ユニットACUは制御ユニットESCUからの専用命令の処理を担う。制御ユニットESCUが割り当て制御ユニットACUと連動するカップリング処理の詳細を図6に示すモデルによって説明する。

#### 【0085】

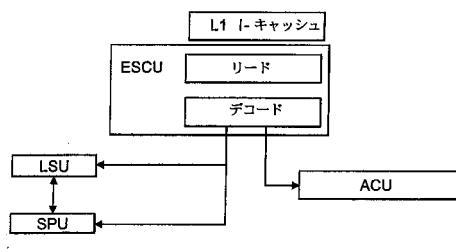

図6は制御ユニットESCUを示しており、標準プロセッシング部SPPのローディングユニットLSU、演算ユニットSPU、メモリユニットL1-I-キャッシュと共に示されている。図6には補助プロセッシング部APPの割り当て制御ユニットACUも示されている。20

#### 【0086】

標準プロセッシング部SPPの標準命令は制御ユニットESCUのリードステージ、デコードステージにおいてそれぞれリード、デコードされ、ローディングユニットLSUと演算ユニットSPUが制御される。逆に、専用命令の場合は制御ユニットESCUは割り当て制御ユニットACUのコマンドの流れとしてリダイレクトする。

#### 【0087】

これら専用命令は以下の異なる種類の命令に関連付けることができる。30

- スレッドの生成／破棄すること

- タスクに関連づけてスレッドを破棄すること

- メインメモリMMからシステムバスSBへまたは逆方向へデータを転送すること

- サブシステムSPPとAPP間でデータを転送すること

#### 【0088】

標準プロセッシング部SPPへのタスクの割り当てにおいて、システムソフトウェアは補助演算ユニットAPUへのスレッドの仮想割り当てを行う。割り当て制御ユニットACUは最適な割り当てを決定するパラメタをすべて勘案して物理的な割り当てを行う。割り当てとは別に、割り当て制御ユニットACUはスレッド間の同期とクリティカルな共有リソースのアクセスも制御する。この割り当て制御ユニットACUは例えばプリエンプション管理またはタスクのアップデートリスト管理などのシステムソフトウェアのサポートも担っている。40

#### 【0089】

これらファンクションにより割り当て制御ユニットACUは補助プロセッシング部APPにおいて実行されている各々のスレッドの実行環境が調整される。弱い同期性を持っている場合、割り当て制御ユニットACUのみがスレッドの展開を担っている。結果として、タスクが標準プロセッシング部SPPに対して再割り当てされると、演算が進んでいるスレッドに対してその旨を通知する必要がある。これにより、標準プロセッシング部SPPではターミネートされずに補助プロセッシング部APPにおいて実行されているプロセスのスレッドが再アクティブ化されてしまうことがなくなる。割り当て制御ユニットAC50

Uのローカル実行環境の利用管理によりタスクがプロセッサに割り当てられる状態が維持されることが確保される。このことは、標準プロセッシング部SPPにおいてタスクが正常に実行されない場合になおさらである。

#### 【0090】

基本となるサービスのもと、割り当て制御ユニットACUはアプリケーションドメインに関連したファンクションを担っている。これらファンクションはダイナミック消費電力管理、フォールト管理、クライシスマード管理などである。

#### 【0091】

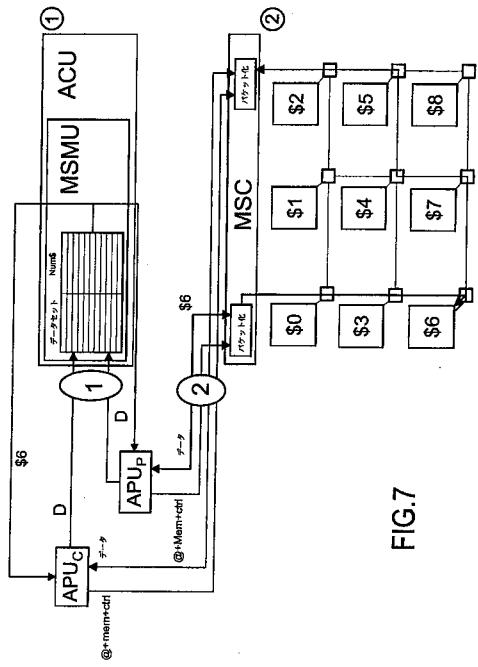

補助演算ユニットAPUで取り扱われる全てのデータは共有メモリ空間SMSに格納されている。共有メモリ空間SMSはマルチメモリリソースと同じ空間内にあるすべてのリソースをユニット化して内部接続するネットワークを備えている。メモリ空間コントローラMSCは演算リソースとメモリリソース間のリンク構築を担っている。割り当て制御ユニットACUは、補助演算ユニットAPUによって取り扱われる共有メモリ空間の仮想アドレス（変数名と変数の位置、例えばイメージ名とピクセルインデックス）と、メモリリソースで使用されることが宣言されている物理アドレスとのリンクに関する情報を供給する。図7はAPUpと表示されているプロデューサ側の補助演算ユニットAPUと、APUcと表示されているコンシューマー側の補助演算ユニットAPUとの間のデータ伝送のデータアクセス機構を示している。この補助プロセッシング部APP内でのデータアクセス機構は2つのステップに分けることができ、図7中のサークル1、サークル2として示されている。

10

20

#### 【0092】

データアクセスの第1のフェーズは補助演算ユニットAPUが初めて変数にアクセスしたときに用いられる。この状態ではまだデータとメモリ間のリンクはない。メモリ情報を得るため、まず補助演算ユニットAPUは割り当て制御ユニットACUに問い合わせる。ACUは変数名と関連付けることによりデータアクセスが実行できるように、メモリ空間管理ユニットMSMUと協働する。アクセスするデータがACUにより特定されると、管理ユニットMSMUは変数を格納しているメモリの特定情報を送信する。逆に、補助演算ユニットAPUが参照情報のないデータを書き込もうとすると（例えば変数を最初に書き込む場合）、管理ユニットMSMUは、共有メモリ空間SMS中の利用できるメモリから書き込むメモリを選んで割り当てる制御を行う。一度メモリが割り当てられるとメモリユニットは記憶されているメモリの変数名によって関連付けられ、更新されるたびにメモリの特定情報が補助演算ユニットAPUに対して送信される。補助演算ユニットAPUが参照情報のないデータを読み出そうとすると（例えば変数を最初に読み出す場合）、管理ユニットMSMUが取り出しを担い（メインメモリ制御部MMCと関連付けられる）、共有メモリ空間SMS中の利用できるメモリからメモリを選んで割り当てる制御を行う。パマネントデータが書き込まれると（最終結果として）、変数名が対応しているメモリのユニットのエントリが開放され、大容量メモリに書き戻されるべきデータのリクエストがメインメモリ制御部MMCに対して送信される。

30

#### 【0093】

データアクセスの第2フェーズでは補助演算ユニットAPUとデータを含むメモリの間にリンクを確立することがシステムティックに行われる。補助演算ユニットAPUはアクセスしたいメモリを知っているので、共有メモリ空間SMSに対して必要となるデータアドレスとメモリ制御信号とを同一サイクルタイム内に送る。メモリ空間制御部MSCはこれら信号の適切なメモリへのルーティングを担う（その結果データを返す）。この動作はメモリリソースの内部接続構成のタイプにより異なる。図7に示したモデルにおけるチップ内のネットワーク実行環境では、このメモリ空間制御部MSCによるデータのパケット化とは、例えば、ネットワークのルーティング情報をデータを加えることとなる。クロスバータイプのポイントツーポイントネットワークでは、メモリ空間制御部MSCはハードウェアのパスの形成を担っている。

40

#### 【0094】

50

補助演算ユニット APU のレベルのデータアドレスの管理は、例えば、データストリームやバーストコールを管理できる適切な能力を備えた専用の入出力ユニットにより取り扱われる。データ管理を担う構成要素は補助演算ユニット APU により取り扱われるデータのリカバリも担うこととなる。データへのアクセスができない場合またはアクセスが阻害された場合、制御モジュールは不安定なデータへの処理をさせないために補助演算ユニット APU におけるスレッドの実行をフリーズする。

#### 【0095】

アプリケーションドメインと共有メモリ空間 SMS の処理結果において、データにアクセスするリクエスト  $N_{b_{access}}$  の数がメモリのポート  $N_{b_{ports}}$  の数またはネットワークのノード数よりも大きい場合には実行中にコンフリクトが発生しうる。この阻害要因は発生しうることを考慮しておかなければならず、システムのディメンジョンを決定し、メモリアクセスタイム  $T_{access}$  を知り、以下の式(1)を考慮しなければならない。10

#### 【0096】

##### 【数1】

$$T_{access} = T_{mem} \times \text{Sup} \left( \frac{N_{b_{Access}}}{N_{b_{Port}}} \right) \quad (1)$$

式中の  $N_{b_{access}}$  はアクセス数を表わし、

$N_{b_{port}}$  は共有メモリ空間 SMS のポート数又はネットワークノード数を表わし、

$T_{mem}$  は最小メモリアクセスタイムを表わしている。20

#### 【0097】

オーバーヘッドを最小化するため、異なるメモリバンクのデータデカップリングにより仮想のメモリポート数を増やすことができ、同時マルチアクセスが可能となる。データ書き込み時間とデータ読み出し時間の兼ね合いはシステム全体のパフォーマンスを最適化するようにユーザが決定する。コンフリクトが発生している間は、特別なアクセスプライオリティポリシーは必要ない。メモリアクセス時間を最大限確保するなどのコンフリクト処理の機能を提供するためには単純な先入れ先出しタイプのソリューションで良い。

#### 【0098】

データが演算要素自体ではなくメモリ構造に依存しているので採用されているメモリ構造は重要である。実行環境の変更は演算リソース間のデータ伝送を必要としないためプリエンプションは即座に実行することができる。30

#### 【0099】

小容量データは、図 5 に示すように補助プロセッシング部 APP と標準プロセッシング部 SPP 間で交換できる。データ伝送はソースプログラムにおいて以下の情報を指定した命令として直接書き込むことができる。

- 補助プロセッシング部 APP から標準プロセッシング部 SPP 間へのデータ伝送またはその逆方向のデータ伝送

- 標準プロセッシング部におけるターゲットレジスタ

- 補助プロセッシング部 APP におけるターゲットスレッド

- スレッドのデータ

#### 【0100】

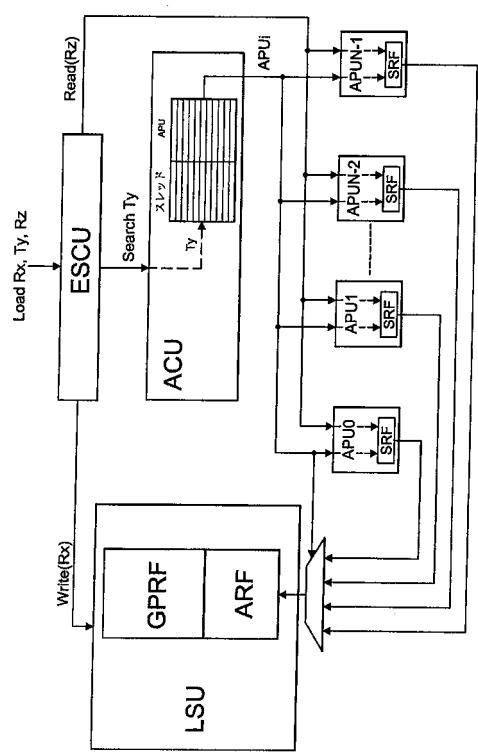

図 8 に示した例のようにロード命令  $R_x$ ,  $T_y$ ,  $R_z$  の読み込み処理は、標準プロセッシング部 SPP のレジスタ  $R_x$  に補助プロセッシング部 APP で実行されているスレッド  $T_y$  の変数  $R_z$  がロードされることで実行される。制御ユニット ESCU はこの命令をデコードし、以下の 3 つのコマンドを生成する。

1. Read ( $R_z$ ) : このコマンドは補助演算ユニット APU の変数  $R_z$  の読み込みを行うものである。

2. Search ( $T_y$ ) : このコマンドは割り当て制御ユニット ACU に対してどの補助演算ユニット APU がスレッド  $T_y$  を実行中であるかの識別子を送る。この識別子は、50

補助演算ユニット A P U の割り当て制御ユニット A C U 内でアクティブなスレッドに関連付けられたトランスレーションルックアサイドバッファ ( T L B ) と呼ばれるページのテーブルという形で示される。もし T L B が補助演算ユニット A P U の識別子を送り返して来なかつた場合、標準プロセッシング部 S P P が処理待ちの実行中のスレッドやタスクが存在しないことを意味する。スレッドが実行されている場合、T L B は当該スレッドを実行している補助演算ユニット A P U の識別子を送り返す。この識別子は標準プロセッシング部 S P P が補助プロセッシング部 A P P の補助レジスタキューに送るべきデータを選択するために利用される。この識別子は共有レジスタキュー S R F のリードデータを有効化するために補助演算ユニット A P U においても利用される。

3 . W r i t e ( R x ) : このコマンドは、補助プロセッシング部 A P P から返された書き込みデータを補助レジスタキューのレジスタ R x へ書き込むものである。 10

#### 【 0 1 0 1 】

コマンド A P U i を補助演算ユニット A P U 0 、 A P U 1 、 A P U N - 2 、 A P U N - 1 に送ることはオプションであり、伝送モードを邪魔することなく除去することができ、ユーティリティのないレジスタキューにアクセスすることを防ぐことができる。

#### 【 0 1 0 2 】

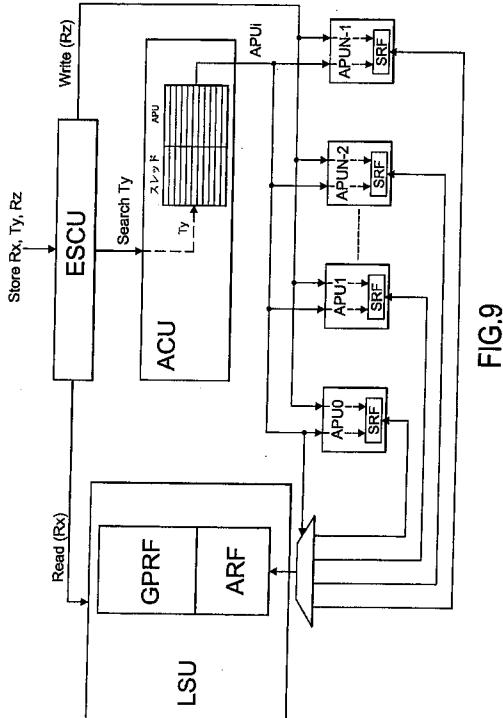

二重構造のメカニズムによって標準プロセッシング部 S P P から補助プロセッシング部 A P P にデータを伝送することができる。この機構は図 9 に示されており、図 8 と似通っているが、 S T O R E R x , T y , R z , W r i t e ( R z ) 、 R e a d ( R x ) という命令が、 L O A D R x , T y , R z , R e a d ( R z ) 、 W r i t e ( R x ) 命令の代わりにある。 20

#### 【 0 1 0 3 】

下記に説明する実施例では、システムへのアクセスがメインメモリ M M を介したものとなっている。メインメモリ制御部 M M C 、割り当て制御ユニット ( A C U ) 、メモリ空間制御部 M S C が、使用される通信タイプに応じて、通信制御に関与している。メインメモリ M M は 4 つの通信タイプに関与している。

1 . システムバス S B からメインメモリ M M への通信：データ通信の第 1 のタイプは、データをシステム外部から補助プロセッシング部 A P P のメインメモリ M M へ取り入れることである。この伝送は制御ユニット E S C U の特定命令のデコード後に発生しうる。特定命令は割り当て制御ユニット A C U によりメインメモリ制御部 M M C に対して割り当てられるデータ伝送処理を発生させる。後者はダイレクトメモリアクセス ( D M A ) 制御部と同様である。同時に、メインメモリ制御部 M M C はロードされているデータとメインメモリ M M におけるアドレスのリンクを確立できるようにテーブルを埋める。 30

2 . メインメモリ M M からシステムバス S B への通信：対称的に、通信されるデータはメインメモリ M M から制御ユニット E S C U の特定命令により識別されるデータ伝送の到着を知らせるシステムリマインダーデータである。メインメモリ M M から送信することはデータが最終結果であると通信内容のテーブル内のエントリが破棄される。制御ユニット E S C U によってデコードされた特定命令は破棄伝送か破棄しない伝送かの区別を決める。

3 . メインメモリ M M から共有メモリ空間 S M S への通信：補助演算ユニット A P U が共有メモリ空間 S M S に存在しないデータにアクセスしようとすると、共有メモリ空間 S M S にデータをルーティングするため伝送要求が割り当て制御ユニット A C U により制御部 M M C に送られる。補助演算ユニット A P U は伝送処理の間、ブロックされる。 40

4 . 共有メモリ空間 S M S からメインメモリ M M への通信：この伝送は補助プロセッシング部 A P P の共有メモリ空間 S M S に再リードされない最終結果の書き込みにおいて、補助演算ユニット A P U からの特定データの伝送である。これらの伝送処理は実行環境の格納において強い同期性の状態でも実行できる。例えば、共有メモリ空間 S M S は割り当て制御ユニット A C U を介してリクエストデータをメインメモリ制御部 M M C に対して送る。

#### 【 0 1 0 4 】

ターゲットアプリケーション空間の機能拡充のため、使用用途が限定されていない大容 50

量メモリの実装が可能である。この状態は大容量メモリMMが他のメモリリソースと同じ共有メモリ空間SMSに実装されている環境と同様である。このような環境下では、データが共有メモリ空間SMSとシステムバスの間で直接交換される。この交換は通信スレッドという形で管理され、メインメモリ制御部MMCの専用ユニットのどの補助演算ユニットAPUにおいても実行できるものである。

#### 【0105】

本発明のメソッドと拡張実装可能なアーキテクチャは補助演算ユニットAPUの実装数をサポートできる。

#### 【0106】

実際には、アーキテクチャのパフォーマンスは補助演算APUの数が大きすぎると、例 10 えば、数百個のオーダーの数であると、低下してしまう。

#### 【0107】

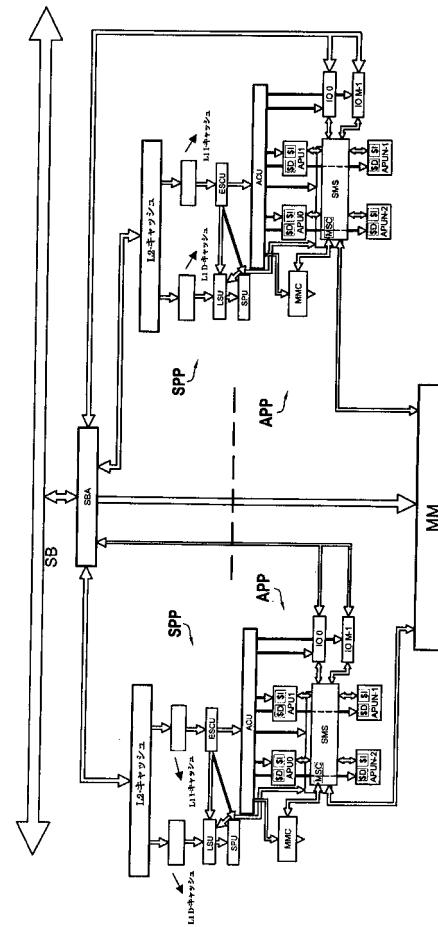

この問題を解決する手段の一つは、共有メモリマルチプロセッサシステムのアーキテクチャが適用されることである。このような実施例は図10に示されており、本発明が適用された2つのプロセッサが搭載されている例を示している。図5を参照して示したような上記の標準プロセッシング部SPPと補助プロセッシング部APPがカップリングされているものと同じ構成のコアを持った多数のプロセッサが搭載されたものも可能である。

#### 【0108】

共有メモリマルチプロセッサシステムにおいて、図10に示すように、専用バスを介したコア間で共有されているシステムバスアービターSBAや補助プロセッシング部APPの大容量メモリMMや高速入出力コントローラなどの構成要素を共有することは有利である。

#### 【0109】

要するに、本発明は、組み込みアーキテクチャでのスレッド制御やスレッド割り当てのデバイスやメソッドに関するものであり、マルチプルプロセッシングリソースに実装され、リアルタイムで集中特化したマルチタスク演算およびマルチストリーム演算に適したものである。

#### 【0110】

さらに、下記の構成要素を備えたリアルタイムパラレル演算アーキテクチャにも適用され得るものである。

- クリティカルではないタスク処理とシステムソフトウェアサポートの実行を担う中央プロセッサコアSPP

- プログラマブルでリコンフィギュラブルまたは特定処理の高速処理に最適化された補助演算ユニットAPU

- 補助演算ユニットAPUで内部ネットワークを介して共有されるメモリ空間SMS

- 補助演算ユニットAPUiによる集中特化した処理の並列処理の実行を管理する補助リソースを制御し割り当てるユニットACU

#### 【0111】

さらに、特に、様々な補助演算ユニットAPU間の通信、補助演算ユニットAPUと中央プロセッサコアSPP間の通信が、共有メモリ空間SMSまたは内部ネットワークを介して行われるものである。

#### 【0112】

タスク割り当てとタスク処理の手法において、中央プロセッサコアSPPで実行される制御タスクが、補助演算ユニットAPUで実行される集中特化した演算タスクとは分離されている。割り当て制御ユニットACUは集中特化した演算タスクを様々な補助演算ユニットAPUに対して割り当てる管理を並列処理にて行う。この補助制御部ACUは、補助演算ユニットAPUが、中央プロセッサコアSPPで実行されているタスクとは異なるスレッドの処理ができるという、いわゆる弱い同期機構により実装されている。このシステム状態はユニークな実行環境で表わされており、ノイマン型アーキテクチャとは異なるものとなっている。クリティカル入出力は、補助演算ユニットAPUによって共有メモリ空 50

間に直接リンクされている。このアーキテクチャおよびこの割り当て手法は、データローディング時間の低減や、異なるアプリケーションへの適合など、リアルタイムマルチタスクプロセッシングの最適化を実現できる。

【図面の簡単な説明】

【図 1】

【図 1】図 1 A および 1 B は、それぞれ汎用的な SMT アーキテクチャモデルおよび操作処理例を表わす図である。

【図 2】図 2 A および 2 B は、それぞれ汎用的な CMP アーキテクチャモデルおよび操作処理例を表わす図である。

【図 3】図 3 A および 3 B は、それぞれ汎用的な CMT アーキテクチャモデルおよび操作処理例を表わす図である。

10

【図 4】図 4 は、システム動作をアプリケーション、タスク、さらに命令（スレッド）の流れに分解して表わした図である。

【図 5】図 5 は、本発明のプロセッサのアーキテクチャの主要構成要素を示すブロック図である。

【図 6】図 6 は、補助プロセッシング部と標準プロセッシング部で構築されるメカニズムを示すブロック図である。

【図 7】図 7 は、補助プロセッシング部におけるデータアクセス処理のメカニズムを示す図である。

【図 8】図 8 は、補助プロセッシング部と標準プロセッシング部の間でのデータ転送処理のメカニズムを示す図である。

20

【図 9】図 9 は、標準プロセッシング部と補助プロセッシング部の間でのデータ転送処理のメカニズムを示す図である。

【図 10】図 10 は、本発明の実施例である共有メモリマルチプロセッサシステムの構成例を示すブロック図である。

【図 1】

【図 2】

【図3】

【 四 4 】

FIG.3B

【 四 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 ダヴィ , ラファエル

フランス、エフ - 91440 ピュル シュル イヴェット、アヴニュ シャルル ドゥ ゴール

17

(72)発明者 ダヴィ , ヴァンサン

フランス、エフ - 78000 ヴェルサイユ、リュ デ シヨンティエ 47

(72)発明者 ヴァントルー , ニコラ

フランス、エフ - 91440 ピュル シュル イヴェット、リュ シャルル ドゥ ゴール 2

8

(72)発明者 コレット , ティエリー

フランス、エフ - 91120 パレゾー、リュ マルソー 124

審査官 川崎 優

(56)参考文献 Wolf,W. , The Future of Multiprocessor Systems-on-Chips , Proc. of. the 41st annual Design Automation Conf. , 2004年 7月11日 , P.681-685

(58)調査した分野(Int.Cl. , DB名)

G 06 F 9 / 46 - 54