(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4533713号

(P4533713)

(45) 発行日 平成22年9月1日(2010.9.1)

(24) 登録日 平成22年6月18日(2010.6.18)

(51) Int.Cl.

F 1

G06F 13/28 (2006.01)

G06F 12/14 (2006.01)G06F 13/28 310M

G06F 12/14 510E

請求項の数 9 (全 12 頁)

(21) 出願番号 特願2004-288217 (P2004-288217)

(22) 出願日 平成16年9月30日 (2004. 9. 30)

(65) 公開番号 特開2006-99702 (P2006-99702A)

(43) 公開日 平成18年4月13日 (2006. 4. 13)

審査請求日 平成19年4月10日 (2007. 4. 10)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】情報処理装置およびデータ転送制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のプロセスを並列に実行可能な情報処理において、

特権モードとユーザモードとを有するプロセッサと、

メモリと、

前記ユーザモード上で動作するユーザプロセスがアクセス可能なアドレス空間にマッピングされた第1レジスタおよび前記特権モード上で動作する特権プロセスがアクセス可能なアドレス空間にマッピングされた第2レジスタを有し、I/Oデバイスを制御するとともに、I/Oバスを介して前記メモリに接続されるI/Oコントローラと、

前記I/Oコントローラに設けられ、前記ユーザプロセスによって前記第1レジスタに設定されるデータ転送制御情報に基づいて、前記I/Oデバイスと前記メモリとの間のデータ転送を前記ユーザプロセスが実行する直接メモリアクセスコントローラと、

前記I/Oコントローラに設けられ、前記直接メモリアクセスコントローラと前記I/Oバスとの間に位置し、前記直接メモリアクセスコントローラから出力されるアドレスと前記特権プロセスによって前記第2レジスタに設定されるアクセス制御情報に基づいて前記直接メモリアクセスコントローラのデータ転送動作を制限し、前記ユーザプロセスがアクセス可能な前記メモリ上の所定領域以外の他の領域が前記直接メモリアクセスコントローラによってアクセスされることを禁止するアクセス制御部とを具備することを特徴とする情報処理装置。

## 【請求項 2】

10

20

前記アクセス制御部は、前記直接メモリアクセスコントローラのデータ転送動作を制限するために前記直接メモリアクセスコントローラから出力されるアドレスを監視する手段を含むことを特徴とする請求項1記載の情報処理装置。

【請求項3】

前記アクセス制御情報は、前記所定領域に対応するアドレス範囲を指定するアドレス情報を含み、

前記アクセス制御部は、前記直接メモリアクセスコントローラから出力されるアドレスを監視し、前記アドレスが前記所定領域に対応するアドレス範囲内に属するか否かを判別する手段と、前記直接メモリアクセスコントローラから出力されるアドレスが前記所定領域に対応するアドレス範囲内に属さない場合、前記直接メモリアクセスコントローラによるデータ転送動作の実行を禁止する手段とを含むことを特徴とする請求項1記載の情報処理装置。

10

【請求項4】

前記アクセス制御情報は、前記所定領域に対応するアドレス範囲を指定するアドレス情報を含み、

前記アクセス制御部は、前記直接メモリアクセスコントローラから出力されるアドレスを監視し、前記アドレスが前記所定領域に対応するアドレス範囲内に属するか否かを判別する手段と、前記直接メモリアクセスコントローラから出力されるアドレスが前記所定領域に対応するアドレス範囲内に属さない場合、前記直接メモリアクセスコントローラによるデータ転送動作の実行を禁止する手段と、前記データ転送動作の実行が禁止された場合、前記直接メモリアクセスコントローラから出力されるアドレスを前記特権プロセスに通知するために、前記アドレスを前記第2レジスタに保存する手段とを含むことを特徴とする請求項1記載の情報処理装置。

20

【請求項5】

複数のプロセスを並列に実行可能な情報処理において、

特権モードとユーザモードとを有するプロセッサと、

メモリと、

前記ユーザモード上で動作する第1のユーザプロセスがアクセス可能なアドレス空間にマッピングされた第1レジスタおよび前記特権モード上で動作する特権プロセスがアクセス可能なアドレス空間にマッピングされた第2レジスタを有し、第1のI/Oデバイスを制御するとともに、I/Oバスを介して前記メモリに接続される第1のI/Oコントローラと、

30

前記ユーザモード上で動作する第2のユーザプロセスからアクセス可能なアドレス空間にマッピングされた第3レジスタおよび前記特権プロセスからアクセス可能なアドレス空間にマッピングされた第4レジスタを有し、第2のI/Oデバイスを制御するとともに、前記I/Oバスを介して前記メモリに接続される第2のI/Oコントローラと、

前記第1のI/Oコントローラに設けられ、前記第1のユーザプロセスによって前記第1レジスタに設定されるデータ転送制御情報に基づいて、前記第1のI/Oデバイスと前記メモリとの間のデータ転送を前記第1のユーザプロセスが実行する第1の直接メモリアクセスコントローラと、

40

前記第1のI/Oコントローラに設けられ、前記第1の直接メモリアクセスコントローラと前記I/Oバスとの間に位置し、前記第1の直接メモリアクセスコントローラから出力されるアドレスと前記特権プロセスによって前記第2レジスタに設定される第1のアクセス制御情報に基づいて前記第1の直接メモリアクセスコントローラのデータ転送動作を制限し、前記第1のユーザプロセスがアクセス可能な前記メモリ上の第1領域以外の他の領域が前記第1の直接メモリアクセスコントローラによってアクセスされることを禁止する第1のアクセス制御部と、

前記第2のI/Oコントローラに設けられ、前記第2のユーザプロセスによって前記第3レジスタに設定されるデータ転送制御情報に基づいて、前記第2のI/Oデバイスと前記メモリとの間のデータ転送を前記第2のユーザプロセスが実行する第2の直接メモリアクセスコントローラと、

50

クセスコントローラと、

前記第2のI/Oコントローラに設けられ、前記第2の直接メモリアクセスコントローラと前記I/Oバスとの間に位置し、前記第2の直接メモリアクセスコントローラから出力されるアドレスと前記特権プロセスによって前記第4レジスタに設定される第2のアクセス制御情報に基づいて前記第2の直接メモリアクセスコントローラのデータ転送動作を制限し、前記第2のユーザプロセスがアクセス可能な前記メモリ上の第2領域以外の他の領域が前記第2の直接メモリアクセスコントローラによってアクセスされることを禁止する第2のアクセス制御部とを具備することを特徴とする情報処理装置。

【請求項6】

前記第1のユーザプロセスは前記第1のI/Oデバイスを制御するための処理を実行し、前記第2のユーザプロセスは前記第2のI/Oデバイスを制御するための処理を実行することを特徴とする請求項5記載の情報処理装置。 10

【請求項7】

前記第1のアクセス制御情報は、前記第1領域に対応するアドレス範囲を指定するアドレス情報を含み、

前記第1のアクセス制御部は、前記第1の直接メモリアクセスコントローラから出力されるアドレスを監視し、前記アドレスが前記第1領域に対応するアドレス範囲内に属するか否かを判別する手段と、前記第1の直接メモリアクセスコントローラから出力されるアドレスが前記第1領域に対応するアドレス範囲内に属しない場合、前記第1の直接メモリアクセスコントローラによるデータ転送動作の実行を禁止する手段とを含むことを特徴とする請求項5記載の情報処理装置。 20

【請求項8】

前記第2のアクセス制御情報は、前記第2領域に対応するアドレス範囲を指定するアドレス情報を含み、

前記第2のアクセス制御部は、前記第2の直接メモリアクセスコントローラから出力されるアドレスを監視し、前記アドレスが前記第2領域に対応するアドレス範囲内に属するか否かを判別する手段と、前記第2の直接メモリアクセスコントローラから出力されるアドレスが前記第2領域に対応するアドレス範囲内に属しない場合、前記第2の直接メモリアクセスコントローラによるデータ転送動作の実行を禁止する手段とを含むことを特徴とする請求項5記載の情報処理装置。 30

【請求項9】

I/Oコントローラによって実行されるI/Oデバイスとメモリとの間のデータ転送を制御するデータ転送制御方法であって、前記I/Oコントローラは、I/Oバスを介して前記メモリに接続され、前記データ転送をユーザプロセスが実行する直接メモリアクセスコントローラと、前記ユーザプロセスがアクセス可能なアドレス空間にマッピングされた第1レジスタと、特権プロセスがアクセス可能なアドレス空間にマッピングされた第2レジスタとを含み、

前記第2レジスタにアクセス制御情報を設定する処理を前記特権プロセスによって実行するステップと、

前記直接メモリアクセスコントローラの動作を制御するデータ転送制御情報を前記第1レジスタに設定する処理を前記ユーザプロセスによって実行するステップと、 40

前記直接メモリアクセスコントローラから出力されるアドレスを監視し、前記アドレスが前記ユーザプロセスによりアクセス可能な前記メモリ上の所定領域に対応するアドレス範囲内に属するか否かを前記アクセス制御情報に基づいて判別するステップと、

前記直接メモリアクセスコントローラから出力されるアドレスが前記所定領域に対応するアドレス範囲内に属しない場合、前記直接メモリアクセスコントローラによるデータ転送動作の実行を禁止するステップとを具備することを特徴とするデータ転送制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、直接メモリアクセス (DMA : Direct Memory Access) によって I/O デバイスとメモリとの間のデータ転送を実行する情報処理装置および同装置で用いられるデータ転送制御方法に関する。

【背景技術】

【0002】

一般に、複数のプロセスを並列に実行可能なマルチプロセス機能を有するコンピュータシステムにおいては、各プロセスを他のプロセスから保護する機構が用いられている。この機構を実現するために、通常、プロセッサは、特権モードとユーザモードの 2 つの実行モードを有している。オペレーティングシステムのカーネル等は特権モード上で動作し、各ユーザプロセスはユーザモード上で動作する。ユーザモードは一般モードと称されることもある。特権モードにおいては、プロセッサ内のメモリ管理ユニット (MMU : Memory Management Unit) の制御等のための特殊命令を含む全ての命令を実行することができ、またアクセス可能なメモリ空間も制限されない。カーネルのような特権プロセスは、メモリ保護を実現するために、MMU を用いて各ユーザプロセスがアクセス可能なメモリ空間を管理する。

10

【0003】

また、最近では、I/O デバイス (Input / Output Device) とメモリとの間のデータ転送処理から CPU を解放するために、直接メモリアクセス (DMA) を利用したシステムアーキテクチャが利用されている (非特許文献 1 参照。)。この非特許文献 1 のシステムにおいては、DMA 機能を有する I/O コントローラが設けられている。I/O コントローラは、プロセッサが他のタスクを実行している間に、I/O デバイスとメモリとの間のデータ転送を DMA によって実行することができる。

20

【非特許文献 1】David A. Patterson and John L. Hennessy, 「Computer Architecture A Quantitative Approach Second Edition」, Morgan Kaufmann Publishers Inc., 1996 年 6 月 1 日, p. 501 - 504, FIGURE 6.15

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、DMA 機能を有する I/O コントローラを備えたシステムにおいては、メモリ保護を実現することが困難となる。MMU はプロセッサからメモリに対するアクセスを制限することはできるが、DMA によるメモリアクセスを制限することはできないからである。

30

【0005】

このため、DMA 機能を有する I/O コントローラを備えたシステムにおいては、DMA 転送の制御は、カーネルのような特権モード上で動作する特権プロセスによって行われることが多い。この場合、ユーザプロセスは、I/O コントローラの DMA 機能を直接制御することができないので、常に特権プロセス経由で DMA 機能を制御しなければならない。このことは、オーバヘッドの増大を招き、システム性能を低下させる大きな要因となる。

【0006】

40

本発明は上述の事情を考慮してなされたものであり、メモリ保護を実現でき、かつ DMA 転送を効率よく実行することが可能な情報処理装置およびデータ転送制御方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

上述の課題を解決するため、本発明は、複数のプロセスを並列に実行可能な情報処理において、特権モードとユーザモードとを有するプロセッサと、メモリと、前記ユーザモード上で動作するユーザプロセスがアクセス可能なアドレス空間にマッピングされた第 1 レジスタおよび前記特権モード上で動作する特権プロセスがアクセス可能なアドレス空間にマッピングされた第 2 レジスタを有し、I/O デバイスを制御するとともに、I/O バス

50

を介して前記メモリに接続されるI/Oコントローラと、前記I/Oコントローラに設けられ、前記ユーザプロセスによって前記第1レジスタに設定されるデータ転送制御情報に基づいて、前記I/Oデバイスと前記メモリとの間のデータ転送を前記ユーザプロセスが実行する直接メモリアクセスコントローラと、前記I/Oコントローラに設けられ、前記直接メモリアクセスコントローラと前記I/Oバスとの間に位置し、前記直接メモリアクセスコントローラから出力されるアドレスと前記特権プロセスによって前記第2レジスタに設定されるアクセス制御情報に基づいて前記直接メモリアクセスコントローラのデータ転送動作を制限し、前記ユーザプロセスがアクセス可能な前記メモリ上の所定領域以外の他の領域が前記直接メモリアクセスコントローラによってアクセスされることを禁止するアクセス制御部とを具備することを特徴とする。

10

【発明の効果】

【0008】

本発明によれば、メモリ保護を実現でき、かつDMA転送を効率よく実行することが可能となる。

【発明を実施するための最良の形態】

【0009】

以下、図面を参照して本発明の実施形態を説明する。

【0010】

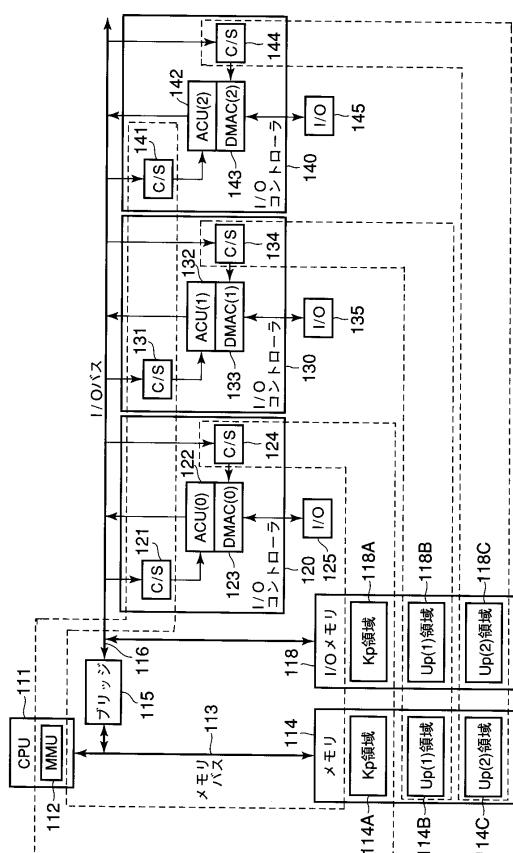

図1には、本発明の一実施形態の係わる情報処理装置の構成例が示されている。この情報処理装置はマイクロプロセッサを利用したコンピュータであり、例えば、パーソナルコンピュータ、サーバコンピュータ、あるいは各種電子機器のための組み込みシステム等として実現されている。

20

【0011】

この情報処理装置は、複数のプロセスを並列に実行可能なマルチプロセス機能をサポートしており、CPU111、メモリバス113、メモリ114、ブリッジ115、I/Oバス116、I/Oメモリ118、I/Oコントローラ120、130、140およびI/Oデバイス125、135、145から構成されている。

【0012】

メモリバス113には、CPU111およびメモリ114が接続されている。I/Oバス116には、I/Oメモリ118、およびI/Oコントローラ120、130、140が接続されている。メモリバス113とI/Oバス116との間にはブリッジ115が設けられている。ブリッジ115はメモリバス113とI/Oバス116とを相互接続するためのインターフェース装置である。

30

【0013】

I/Oデバイス125、135、145は互いに独立して動作可能に構成されている。これらI/Oデバイス125、135、145それぞれに対応して、I/Oコントローラ120、130、140が存在する。各I/Oコントローラ120、130、140は、対応するI/Oデバイス125、135、145を制御する。各I/Oコントローラ120、130、140は、DMA機能を有している。

【0014】

40

CPU111は、本情報処理装置に設けられた各コンポーネントを制御するプロセッサである。CPU111は、仮想アドレスおよびメモリ保護を実現するためのメモリ管理ユニット(MMU)112を備えている。このCPU111は、特権モードとユーザモードの二つの実行モードを持つ。特権モードにおいては、MMU112の制御等のための特殊命令を含む全ての命令を実行することができ、またアクセス可能なメモリ空間も制限されない。一方、ユーザモードにおいては、実行可能な命令の種類が制限されるとともに、アクセス可能なメモリ空間もMMU112によって制限される。カーネルのような特権プロセスは特権モード上で動作し、また各ユーザプロセスはユーザモード上で動作する。

【0015】

図1においては、特権プロセス、第1のユーザプロセスおよび第2のユーザプロセスの

50

計三つのプロセスが実行される場合を想定している。特権プロセス、第1のユーザプロセスおよび第2のユーザプロセスには、メモリ114上の互いに異なる領域がそれぞれ割り当てられる。例えば、第1のユーザプロセスはI/Oデバイス135を制御するプロセスであり、また第2のユーザプロセスはI/Oデバイス145を制御するプロセスである。

#### 【0016】

メモリ114上に割り当てられた領域とその領域を使用するプロセスとの関係は次の通りである。

#### 【0017】

- ・Kp領域114A：特権プロセス

- ・Up(1)領域114B：第1のユーザプロセス

- ・Up(2)領域114C：第2のユーザプロセス

10

また、特権プロセス、第1のユーザプロセスおよび第2のユーザプロセスには、I/Oメモリ118上の互いに異なる領域もそれぞれ割り当てられている。I/Oメモリ118上に割り当てられた領域とその領域を使用するプロセスとの関係は次の通りである。

#### 【0018】

- ・Kp領域118A：特権プロセス

- ・Up領域(1)118B：第1のユーザプロセス

- ・Up領域(2)118C：第2のユーザプロセス

Kp領域114AおよびKp領域118Aは、特権プロセスのみが使用可能である。Up領域(1)114Bおよび118Bは、第1のユーザプロセスがアクセス可能な領域である。Up領域(2)114Cおよび118Cは、第2のユーザプロセスがアクセス可能な領域である。

20

#### 【0019】

I/Oコントローラ120は、コントロール/ステータスレジスタ(以下：C/S)121、アクセス制御部(ACU：Access Control Unit)122、DMAコントローラ(以下、DMAC)123およびC/S124等から構成されている。

#### 【0020】

C/S121は、DMAC123によるメモリアクセスを制限するためのアクセス制御情報を記憶するレジスタである。アクセス制御情報は、DMAC123がアクセス可能なメモリ114およびI/Oメモリ118上の各領域のアドレス範囲を指定するアドレス情報である。C/S121は、特権プロセスがアクセス可能なアドレス空間にマッピングされている。このため、C/S121の操作は特権プロセスのみに許され、各ユーザプロセスはC/S121を操作することはできない。

30

#### 【0021】

ACU122は、特権プロセスによってC/S121に設定されたアクセス制御情報に基づいてDMAC123のデータ転送動作を制限する。つまり、ACU122は、DMA123から出力されるアドレスを監視し、そのアドレスがC/S121に記憶されているアクセス制御情報によって指定されるアドレス範囲に属するか否かを判別する処理を実行する。この判別処理の結果に従って、ACU122は、DMAC123によるメモリアクセスの可否を決定する。

40

#### 【0022】

C/S124は、DMAC123によるI/Oデバイス125とメモリ114およびI/Oメモリ118の各々との間のデータ転送動作を制御するデータ転送制御情報(DMAパラメタ)を記憶するレジスタ(DMAレジスタ)である。C/S124の操作は、I/Oデバイス125を制御するプロセスに対して許可されている。本実施形態においては、I/Oデバイスとプロセスとの対応関係は以下の通りである。

#### 【0023】

I/Oデバイス125とメモリ114, 118との間のDMA転送：特権プロセス

I/Oデバイス135とメモリ114, 118との間のDMA転送：第1のユーザプロセス

50

I / O デバイス 145 とメモリ 114, 118 との間の DMA 転送：第 2 のユーザプロセス

この場合、C / S 124 の操作は特権プロセスのみに許可される。つまり、C / S 124 は特権プロセスがアクセス可能なアドレス空間にマッピングされる。

【0024】

D MAC 123 は、特権プロセスによって C / S 124 に設定されたデータ転送制御情報にしたがって、I / O デバイス 125 とメモリ 114, 118 との間の DMA 転送を実行する。

【0025】

I / O コントローラ 130 は、I / O コントローラ 120 と同様に、C / S 131、A CU 132、D MAC 133 および C / S 134 等から構成されている。C / S 131 は、D MAC 133 によるメモリアクセスを制限するためのアクセス制御情報を記憶するレジスタである。アクセス制御情報は、D MAC 133 がアクセス可能なメモリ 114 および I / O メモリ 118 上の各領域のアドレス範囲を指定するアドレス情報である。C / S 131 は、特権プロセスがアクセス可能なアドレス空間にマッピングされている。このため、C / S 131 の操作は特権プロセスのみに許され、各ユーザプロセスは C / S 131 を操作することはできない。

【0026】

ACU 132 は、特権プロセスによって C / S 131 に設定されたアクセス制御情報に基づいて D MAC 133 のデータ転送動作を制限する。つまり、ACU 132 は、DMA C 133 から出力されるアドレスを監視し、そのアドレスが C / S 131 に記憶されているアクセス制御情報によって指定されるアドレス範囲に属するか否かを判別する処理を実行する。この判別処理の結果に従って、ACU 132 は、D MAC 133 によるメモリアクセスの可否を決定する。

【0027】

C / S 134 は、D MAC 133 による I / O デバイス 135 とメモリ 114 および I / O メモリ 118 の各々との間のデータ転送動作を制御するデータ転送制御情報 (DMA パラメタ) を記憶するレジスタ (DMA レジスタ) である。C / S 134 の操作は、I / O デバイス 135 を制御するプロセスに対して許可されている。本実施形態においては、第 1 のユーザプロセスが D MAC 133 を直接操作できるようにするために、C / S 134 は第 1 のユーザプロセスがアクセス可能なメモリ空間にマッピングされている。

【0028】

I / O コントローラ 140 も、I / O コントローラ 120 と同様に、C / S 141、A CU 142、D MAC 143 および C / S 144 等から構成されている。

【0029】

C / S 141 は、D MAC 143 によるメモリアクセスを制限するためのアクセス制御情報を記憶するレジスタである。アクセス制御情報は、D MAC 143 がアクセス可能なメモリ 114 および I / O メモリ 118 上の各領域のアドレス範囲を指定するアドレス情報である。C / S 141 は、特権プロセスがアクセス可能なアドレス空間にマッピングされている。このため、C / S 141 の操作は特権プロセスのみに許され、各ユーザプロセスは C / S 141 を操作することはできない。

【0030】

ACU 142 は、特権プロセスによって C / S 141 に設定されたアクセス制御情報に基づいて D MAC 143 のデータ転送動作を制限する。つまり、ACU 142 は、DMA C 143 から出力されるアドレスを監視し、そのアドレスが C / S 141 に記憶されているアクセス制御情報によって指定されるアドレス範囲に属するか否かを判別する処理を実行する。この判別処理の結果に従って、ACU 142 は、D MAC 143 によるメモリアクセスの可否を決定する。

【0031】

C / S 144 は、D MAC 143 による I / O デバイス 145 とメモリ 114 および I

10

20

30

40

50

/Oメモリ118の各々との間のデータ転送動作を制御するデータ転送制御情報(DMA

パラメタ)を記憶するレジスタ(DMAレジスタ)である。C/S144の操作は、I/

Oデバイス145を制御するプロセスに対して許可されている。本実施形態においては、

第2のユーザプロセスがDMAC143を直接操作できるようにするために、C/S14

4は第2のユーザプロセスがアクセス可能なメモリ空間にマッピングされている。

#### 【0032】

本実施形態においては、第1のユーザプロセスはI/Oバス116を介してC/S13

4にデータ転送制御情報をセットすることにより、特権プロセスの介在なしで、DMAC

133を直接制御することができる。同様に、第2のユーザプロセスはI/Oバス116

を介してC/S144にデータ転送制御情報をセットすることにより、特権プロセスの介

在なしで、DMAC143を直接制御することができる。

10

#### 【0033】

また、特権プロセスは、MMU112、C/S131, 141を操作することにより、

第1のユーザプロセスおよび第2のユーザプロセスによるメモリ114、I/Oメモリ1

18へのアクセスに対して以下のようなアクセス制御を実現することができる。

#### 【0034】

第1のユーザプロセスに対するアクセス制御：CPU111からのアクセスは、MM

U112によって、Up(1)領域114B, 118Bのみに制限される。DMAC13

3からのアクセスは、ACU132によって、Up(1)領域114B, 118Bのみに

制限される。また、CPU111は、C/S134に対するアクセスが許可されている。

20

#### 【0035】

第2のユーザプロセスに対するアクセス制御：CPU111からのアクセスは、MM

U112によって、Up(2)領域114C, 118Cのみに制限される。DMAC14

3からのアクセスは、ACU142によって、Up(2)領域114C, 118Cのみに

制限される。また、CPU111は、C/S144に対するアクセスが許可されている。

#### 【0036】

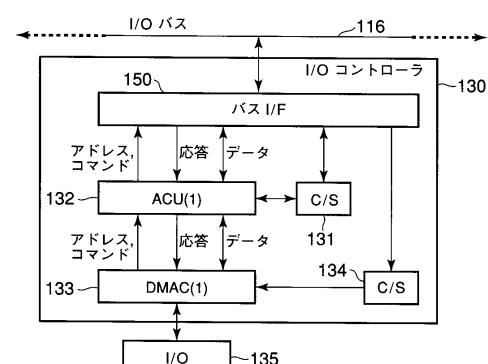

次に図2および図3を参照して、DMA転送処理の一連の動作を、I/Oコントローラ

130を例にとって説明する。

#### 【0037】

図2は、I/Oコントローラ130の内部で実行される処理の流れを示したブロック図

である。

30

#### 【0038】

I/Oコントローラ130は、その内部に設けられたバスI/F(Bus Interface)1

50を介してI/Oバス116に接続されている。

#### 【0039】

ACU132は、DMAC133とバスI/F150との間に設けられている。DMA

C133はメモリサイクルを実行する。DMAC133からのアドレス、コマンド(リード/

ライト)は、ACU132およびバスI/F150を介してI/Oバス116上に出

力される。メモリ114またはI/Oメモリ118からの応答は、バスI/F150、A

CU132を介してDMAC133に送られる。

40

#### 【0040】

ACU132は、DMAC133から出力されるアドレスを監視し、そのアドレスがC

/S131にセットされたアクセス制御情報によって指定される、Up(1)領域のア

ドレス範囲に属するか否かを判別する。この判別結果に従って、ACU132は、DMAC

133によるアクセスを許可または禁止する。DMAC133から出力されるアドレスが

Up(1)領域114Bまたは118Bのアドレス範囲に属しない場合、ACU132は

、DMAC133からのアドレス、コマンドをI/F150を介してI/Oバス116上

に出力せず、メモリサイクルを強制終了するための応答をDMAC133に送信すると共

に、DMAC133からのアドレスをエラーアドレス情報としてC/S131に保存する

。C/S131に保存されたエラーアドレス情報は、たとえば、I/Oコントローラ13

50

0 から C P U 1 1 1 に送信される割り込み信号によって、特権プロセスに通知される。

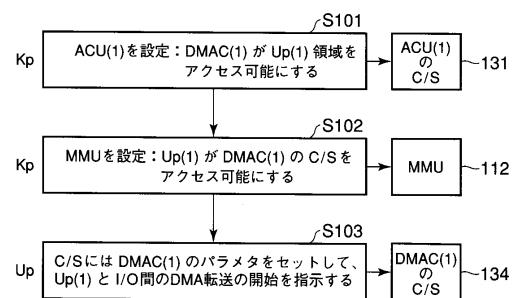

【 0 0 4 1 】

図 3 のフローチャートは、特権プロセスおよびユーザプロセスそれぞれによって実行される処理の手順を示している。

【 0 0 4 2 】

特権プロセス ( K p ) は、 D M A C 1 3 3 がメモリ 1 1 4 上の U p ( 1 ) 領域 1 1 4 B および I / O メモリ 1 1 8 上の U p ( 1 ) 領域 1 1 8 B をアクセスできるようにするために A C U 1 3 2 をセットアップする ( ステップ S 1 0 1 ) 。このステップ S 1 0 1 においては、特権プロセス ( K p ) は、 U p ( 1 ) 領域 1 1 4 B , 1 1 8 B のアドレス範囲を指定するアクセス制限情報を I / O バス 1 1 6 を介して C / S 1 3 1 に設定する。特権プロセス ( K p ) は、第 1 のユーザプロセス ( U p ( 1 ) ) が D M A C 1 3 3 を直接操作できるようにするために M M U 1 1 2 を操作し、これによって C / S 1 3 4 をアクセスするためのアドレス空間を第 1 のユーザプロセス ( U p ( 1 ) ) に割り当てる ( ステップ S 1 0 2 ) 。 10

【 0 0 4 3 】

第 1 のユーザプロセス ( U p ( 1 ) ) は、データ転送制御情報を I / O バス 1 1 6 を介して C / S 1 3 4 に設定することにより、 D M A C 1 3 3 に D M A 転送の実行を指示する ( ステップ S 1 0 3 ) 。

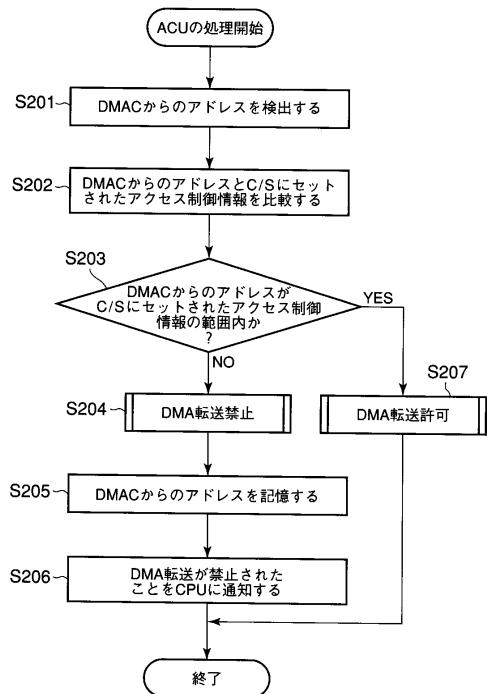

【 0 0 4 4 】

次に図 4 のフローチャートを参照して、 I / O コントローラ 1 3 0 内に設けられた A C 20 U 1 3 2 によって実行される一連の動作を説明する。

【 0 0 4 5 】

まず、 A C U 1 3 2 は、 D M A C 1 3 3 から出力されるメモリアドレスを検出する ( ステップ S 2 0 1 ) 。次に、 A C U 1 3 2 は、検出された D M A C 1 3 3 からのメモリアドレスと、 C / S 1 3 1 にセットされたアクセス制御情報を比較してメモリアドレスが、第 1 のユーザプロセスがアクセス可能なメモリアドレスの範囲内に属するか否かを判定する ( ステップ S 2 0 2 , S 2 0 3 ) 。 D M A C 1 3 3 からのメモリアドレスが、第 1 のユーザプロセスがアクセス可能なメモリアドレス範囲内に属する場合 ( ステップ S 2 0 3 の Y E S ) 、 A C U 1 3 2 は、 D M A 転送許可する ( ステップ S 2 0 7 ) 。ステップ S 2 0 7 においては、 A C U 1 3 2 は、 D M A C 1 3 3 からのメモリアドレスを I / F 1 5 0 に 30 送信する。

【 0 0 4 6 】

一方、 D M A C 1 3 3 からのメモリアドレスが、第 1 のユーザプロセスがアクセス可能なメモリアドレス範囲内に属さない場合 ( ステップ S 2 0 3 の N O ) 、 A C U 1 3 2 は、 D M A C 1 3 3 によって開始されたメモリサイクルを強制終了して D M A 転送の実行を禁止する ( ステップ S 2 0 5 ) 。この後、 A C U 1 3 2 は、 D M A C 1 3 3 からのメモリアドレスを C / S 1 3 4 に記憶する ( ステップ S 2 0 5 ) 。そして、 A C U 1 3 2 は、記憶した D M A C 1 3 3 からのメモリアドレスを C P U 1 1 1 に通知する ( ステップ S 2 0 6 ) 。

【 0 0 4 7 】

以上説明したように、本実施形態においては、各ユーザプロセスは対応する D M A C を直接操作することができるので、 I / O デバイスとメモリとの間のデータ転送を効率よく実行することができる。また、 D M A C 每に A C U が設けられているので、各 D M A C によって実行されるメモリアクセスを特権プロセスによって制限することができる。 40

【 0 0 4 8 】

なお、本発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合わせにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に構成要素を適宜組み合わせてもよい。

## 【図面の簡単な説明】

## 【0049】

【図1】本発明の一実施形態に係わる情報処理装置の構成の一例を示すブロック図。

【図2】図1の情報処理装置で用いられるI/Oコントローラの構成を説明するためのブロック図。

【図3】図1の情報処理装置で実行されるユーザプロセスおよび特権プロセスそれぞれによって実行される処理の手順を示すフローチャート。

【図4】図1の情報処理装置に設けられたアクセス制御ユニットの動作を説明するためのフローチャート。

## 【符号の説明】

## 【0050】

CPU...111、MMU...112、メモリバス...113、メモリ...114、I/Oメモリ...118、Kp領域...114A, 118A、Up(1)領域...114B, 118B、Up(2)領域...114C, 118C、ブリッジ115、I/Oバス...116、I/Oコントローラ...120, 130, 140、C/S(第2のレジスタ)...121, 131, 141、ACU(1)...122, 132、ACU(2)...123, 133、DMAC(0)...124, 134、DMAC(1)...125, 135、I/Oデバイス...140, 145。

10

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 畠山 哲夫

東京都青梅市末広町2丁目9番地 株式会社東芝青梅事業所内

審査官 坂東 博司

(56)参考文献 特開平10-289194 (JP, A)

特開平06-274450 (JP, A)

特開平02-144649 (JP, A)

特開平05-094406 (JP, A)

特開昭62-191950 (JP, A)

特開2001-297054 (JP, A)

特開2003-281076 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 14

G 06 F 13 / 28