(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6105845号

(P6105845)

(45) 発行日 平成29年3月29日(2017.3.29)

(24) 登録日 平成29年3月10日(2017.3.10)

(51) Int.Cl.

H02M 7/48 (2007.01)

F 1

H02M 7/48

H02M 7/48H

J

請求項の数 9 外国語出願 (全 8 頁)

(21) 出願番号 特願2011-287518 (P2011-287518)

(22) 出願日 平成23年12月28日 (2011.12.28)

(65) 公開番号 特開2012-143141 (P2012-143141A)

(43) 公開日 平成24年7月26日 (2012.7.26)

審査請求日 平成26年12月17日 (2014.12.17)

(31) 優先権主張番号 12/983,574

(32) 優先日 平成23年1月3日 (2011.1.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 390041542

ゼネラル・エレクトリック・カンパニー

アメリカ合衆国、ニューヨーク州 123

45、スケネクタディ、リバーロード、1

番

(74) 代理人 100137545

弁理士 荒川 智志

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100129779

弁理士 黒川 俊久

(74) 代理人 100113974

弁理士 田中 拓人

最終頁に続く

(54) 【発明の名称】 転流制御回路及び、電力変換器システム

## (57) 【特許請求の範囲】

## 【請求項 1】

電力バスに電気的に結合され、前記電力バスから受信される電圧信号を経時的に積分する

ように構成される積分型電圧カウンタ(116)と、

前記積分電圧信号を所定のしきい値と比較し、前記積分電圧信号が前記所定のしきい値に

等しいときにトリガ信号を発生させるように構成される比較器と、

前記比較器により発生されるトリガ信号を受信するように構成され、それぞれの電気巻線

(110)に電気的に結合される複数のトランジスタ対(108)と

を備える、転流制御回路。

## 【請求項 2】

前記積分型電圧カウンタ(116)が、フィールドプログラマブルゲートアレイ(FPGA)

デバイスを備える、請求項1記載の転流制御回路。

## 【請求項 3】

前記積分型電圧カウンタ(116)が、シグマデルタ変調器デバイスを備える、請求項1

または2に記載の転流制御回路。

## 【請求項 4】

前記トリガ信号が、前記複数のトランジスタ対(108)の状態を第1の状態から第2の

状態に変化させるように構成される、請求項1乃至3のいずれかに記載の転流制御回路。

## 【請求項 5】

前記積分型電圧カウンタ(116)が、

10

20

入力で電圧信号を受信し、

パルス列を生成するために前記電圧信号を積分し、

前記パルス列に応答してカウンタを増分する

ように構成される、請求項 1 乃至 4 のいずれかに記載の転流制御回路。

**【請求項 6】**

前記電圧信号が、外乱成分を含み、前記外乱成分が、前記電力変換器およびモータ（120）の少なくとも 1 つの物理的構成要素の望ましくないストレスを発生させる、請求項 1 乃至 5 のいずれかに記載の転流制御回路。 10

**【請求項 7】**

前記積分型電圧カウンタ（116）および前記比較器が、単一のプログラマブルデバイスに含まれる、請求項 1 乃至 6 のいずれかに記載の転流制御回路。 10

**【請求項 8】**

前記所定のしきい値が、前記複数のトランジスタ対（108）の出力の振幅および位相の少なくとも 1 つを使用して決定される、請求項 1 乃至 7 のいずれかに記載の転流制御回路。 10

**【請求項 9】**

少なくとも 1 つの変換器（104）を含む入力アセンブリ（102）と、

それぞれのモータ巻線（110）に電気的に結合される複数のトランジスタ対（108）

を含む出力アセンブリ（106）と、 20

前記入力アセンブリと前記出力アセンブリとの間に電気的に結合される直流（DC）リンク（112）と、 20

積分型電圧カウンタ（116）を備える制御ユニット（114）であって、

前記 DC リンクおよび前記出力アセンブリの出力の少なくとも 1 つから電圧信号を受信し、

、 10

パルス列を生成するために時間に関して前記電圧信号を積分し、

前記パルス列に応答してカウンタを増分し、

前記カウンタの前記増分を使用して前記出力アセンブリの状態の変化をトリガする

ように構成される制御ユニット（114）と

を備える、電力変換器システム（100）。 10

30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の分野は、一般には、電力変換器に、より具体的には、それに対して所望の出力波形へのスイッチングが時間的に高度に制約されている電力ブリッジの転流のためのシステムおよび方法に関する。 10

**【背景技術】**

**【0002】**

電力変換器における制御収束性を改善するには、測定と実施に対する離散的な機会との間のレイテンシを最小化することが役立つ。少なくとも一部の既知の電力変換器転流回路は、将来のスイッチング時間を決定するために、ブリッジの過去の実績に依存する。そのような回路および方法は、比較的遅いスイッチング構成要素が使用される場合には、高周波数の用途では不正確である。さらに、そのような方式は、高い効率を維持する一方で、存在し得る外乱信号に対しては対処しない。 40

**【0003】**

既知の機械制御は、通常、電流調整器（または他の 1 次調整器）の帯域幅を超える帯域幅に対して、振幅および周波数が一定のフェーザをエミュレートする電圧を供給する。定常状態でさえ、スイッチモード電源は、電圧およびボルト秒で、ならびに、半径方向と円周方向の両方の軸で、予測可能な誤差を生成する。さらに、過渡帯域幅は、通常、これらの誤差を低減するための従来の手法により、正味のスイッチング周波数に関して重大な制 50

限を伴う電力ブリッジに適用される場合に特に悪化する。

**【0004】**

高度に制約されている電力ブリッジをゲートする方法は、通常、非常に低いチョッピング周波数またはパターン発火を必要とする。低いチョッピング周波数は、供給される波形の最大基本周波数を制約する結果となる。パターン発火の技法は、外部の調整器の応答性を制限する結果となる。

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】**米国特許出願公開第2009/0189446号明細書

10

**【発明の概要】**

**【0006】**

一実施形態では、転流制御回路が、電力バスに電気的に結合される積分型電圧カウンタを含み、積分型電圧カウンタが、電力バスから受信される電圧信号を経時的に積分するよう、かつ、積分電圧信号が所定の計数に等しいときにトリガ信号を発生させるように構成される。システムは、積分型電圧カウンタにより発生されるトリガ信号を受信するよう構成され、モータのそれぞれの巻線に電気的に結合される複数のトランジスタ対をさらに含む。

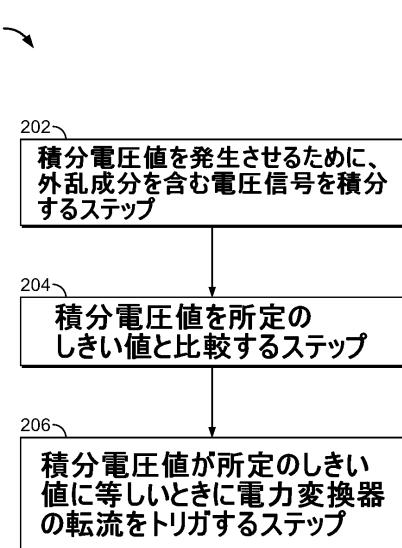

**【0007】**

別の実施形態では、電力変換器を転流する方法が、積分電圧値を発生させるために、直流成分および外乱成分を含む電圧信号を積分するステップと、積分電圧値を所定のしきい値と比較するステップと、積分電圧値が所定のしきい値に等しいときに電力変換器の転流をトリガするステップとを含む。

20

**【0008】**

さらに別の実施形態では、電力変換器システムが、少なくとも1つのインバータを含む入力アセンブリと、それぞれのモータ巻線に電気的に結合される複数のトランジスタ対を含む出力アセンブリと、入力アセンブリと出力アセンブリとの間に電気的に結合される直流(DC)リンクと、DCリンクおよび出力アセンブリの出力の少なくとも1つから電圧信号を受信し、パルス列を生成するために時間に関して電圧信号を積分し、パルス列に応答してカウンタを増分し、カウンタの増分を使用して出力アセンブリの状態の変化をトリガするように構成される制御ユニットとを含む。

30

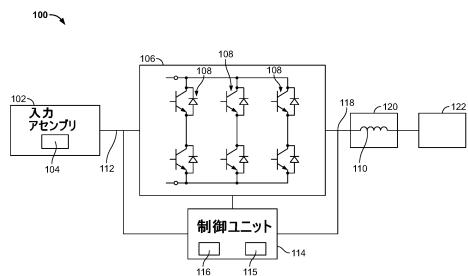

**【0009】**

図1および図2は、本明細書で説明される方法およびシステムの例示的な実施形態を示す。

**【図面の簡単な説明】**

**【0010】**

**【図1】**本発明の例示的な実施形態による電力変換器システム(PCS)の概略ブロック図。

**【図2】**本発明の例示的な実施形態による電力変換器を転流する方法の概略ブロック図。

**【発明を実施するための形態】**

40

**【0011】**

以下の詳細説明は、本発明の実施形態を例として説明するものであり、限定を目的としたものではない。本発明は、工業用、商業用、および住宅用の用途での、電力変換器システムの転流の分析的かつ組織的な実施形態に対する全般的な用途を生み出すことが企図されている。

**【0012】**

本明細書では、単数形で記載され、単語「a」または「a n」を伴って処置される、要素またはステップは、複数の要素またはステップを除外しないと、そのような除外が明示的に記載されていない限りは解釈されるべきである。さらに、本発明の「一実施形態」に対する言及は、記載された特徴をさらに組み込む、さらなる実施形態の存在を除外すると

50

解釈されることは意図されていない。

【0013】

本発明の実施形態は、過度の遅延なしに実施されるように、リアルタイムの状況を利用する。そのような状況は、外乱を含む状況に対して責任をもつリアルタイムの測定に基づいて、比較的単純な、機械化可能な遷移コントローラを使用して充足される。最大の懸念の外乱は、実施期間内でのシステムの発散に影響を与えるものである。

【0014】

単純な、機械化可能な遷移コントローラは、変化した可能性があるシステム変数に関して、システムが収束状態を継続するならばスイッチングが行われることになる将来の時間に外挿される、以前の状況の固定した判定に依存せず、遷移時間に向かっての状況の進展を評価することができ、遷移をトリガするために設定点に対する状況の継続的な比較を行う機構を含む。

10

【0015】

本発明の実施形態は、DCリンク電圧での外乱、転流回路および電源デバイスの影響を当然ながら含む、出力相電圧などのボルト秒の蓄積を使用する。例示的な実施形態では、(ブリッジに対抗する)循環電流のバイアス余弦の位相コントローラと両立する変調器が使用される。

【0016】

2つの重要な機械準拠の変換器の測定値は、半径方向および円周方向のボルト秒(磁束)誤差である。これらのタイプの制御されない誤差は、望ましくない加熱電流、トルク誤差、および磁化誤差に高度に関係しており、それらのすべては、機械にとってストレス要因である。

20

【0017】

これらの磁束誤差という用語は、所望の電圧ベクトルと実際の電圧ベクトルとの間の正味の誤差ベクトルの関連する成分の継続的な時間積分である。定常状態での理想的な所望の電圧は、一定の振幅の継続的に回転するベクトルであり、実際に供給される波形は、ブリッジにより生成される離散的なベクトルの時間刻みのシーケンスにより示される。適切に形成された供給波形に関しては、半径方向と円周方向の両方の磁束誤差が、好適な時間期間にわたってゼロ平均である。

【0018】

図1は、本発明の例示的な実施形態による電力変換器システム(PCS)100の概略ブロック図である。例示的な実施形態では、PCS100は、少なくとも1つの三相インバータを含み得る、少なくとも1つの変換器104を含む入力アセンブリ102と、それぞれのモータ巻線110に電気的に結合される複数のトランジスタ対108を含む出力アセンブリ106と、入力アセンブリ102と出力アセンブリ106との間に電気的に結合される直流(DC)リンク112とを含む。PCS100は、プロセッサ115を備える制御ユニット114をさらに含む。制御ユニット114は、DCリンク112から電圧信号を受信し、ボルト秒値を決定するために時間に関して電圧信号を積分し、所定のボルト秒値でカウンタ116を増分し、カウンタ116の増分を使用して出力アセンブリ106の状態の変化をトリガするように構成される。例示的な実施形態では、カウンタ116は、DCリンク112から電圧信号を受信し、ボルト秒計数を発生させるために受信電圧信号を積分する積分型電圧カウンタを備える。ボルト秒計数は、PCS100の出力118での電流を管理するために、十分なボルト秒が出力アセンブリ106に入ったときを指示するために、カウンタ116を増分する。一実施形態では、カウンタ116は、フィールドプログラマブルゲートアレイ(FPGA)デバイスにおいて実施されるとともに、シグマデルタ変調器デバイスにより駆動され得る。実施形態では、それぞれのモータ巻線110は、例えば、次のものに限らないが、コンプレッサなどの、負荷122を駆動するための電気モータ120内に配置される。変形の実施形態では、それぞれの巻線110は、次のものに限らないが、発電機、電力会社の変圧器の巻線、および原子炉などの、他のデバイスまたは構成要素内に配置される。

40

50

## 【0019】

図2は、本発明の例示的な実施形態による電力変換器を転流する方法200の概略ブロック図である。例示的な実施形態では、方法200は、積分電圧値を発生させるために、外乱成分を含み得る電圧信号を積分するステップ202を含む。一実施形態では、外乱成分は、ノイズ成分および干渉成分の少なくとも1つを含む。方法200は、積分電圧値を所定のしきい値と比較するステップ204と、積分電圧値が所望の電圧に由来するしきい値に等しいときに、電力変換器の転流をトリガするステップ206とをさらに含む。例示的な実施形態では、DCリンクの積分電圧が、ボルト秒で測定される。積分型電圧カウンタが、しきい値を満たす、またはそれを超えるとき、これが、複数のトランジスタ対を含む転流回路の次の状態をトリガする。

10

## 【0020】

プロセッサという用語は、本明細書では、中央処理装置、マイクロプロセッサ、マイクロコントローラ、縮小命令セットコンピュータ(RISC)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)、論理回路、ならびに、本明細書で説明される機能を実行可能な他の任意の回路もしくはプロセッサを指す。

## 【0021】

本明細書では、「ソフトウェア」と「ファームウェア」という用語は、互換的であり、プロセッサ115による実行のために、RAMメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、および不揮発性RAM(NVRAM)メモリを含むメモリに記憶される任意のコンピュータプログラムを含む。上記のメモリのタイプは、単に例示的なものであり、したがって、コンピュータプログラムを記憶するために使用可能なメモリのタイプに関して限定的ではない。

20

## 【0022】

前述の明細書に基づいて理解されるように、本開示の上述の実施形態は、コンピュータソフトウェア、ファームウェア、ハードウェア、またはそれらの任意の組み合わせもしくは部分集合を含む、コンピュータプログラミングまたはエンジニアリング技法を使用して実現され得るものであり、技術的な効果は、半径方向と円周方向の両方の軸で、電圧およびボルト秒での誤差を、過渡帯域幅に影響を与えることなく低減することであり、この過渡帯域幅は、これらの誤差を低減するための従来の手法では、重大なスイッチングの制限を伴う電力変換システムの出力での高忠実度の波形が容易にされるように、特に正味のスイッチング周波数に関して重大な制限を伴う電力ブリッジに適用される場合に悪化し得るものである。コンピュータ可読コード手段を有する、任意のそのような結果として得られるプログラムは、1つまたは複数のコンピュータ可読媒体内で、実施または提供され得るものであり、それによって、本開示の考察された実施形態によるコンピュータプログラム製品、すなわち、製造品を作製する。コンピュータ可読媒体は、例えば、次のものに限らないが、固定(ハード)ドライブ、ディスクケット、光ディスク、磁気テープ、リードオンリーメモリ(ROM)などの半導体メモリ、および/あるいは、インターネットまたは他の通信ネットワークもしくはリンクなどの任意の送信/受信媒体であってよい。コンピュータコードを含む製造品は、1つの媒体から直接コードを実行することにより、1つの媒体から別の媒体にコードをコピーすることにより、またはネットワークを介してコードを伝送することにより、作製かつ/または使用され得る。

30

## 【0023】

電力変換器を転流するシステムおよび方法の上述の実施形態は、電気量の高忠実度および高帯域幅の管理が必要になる用途での、大規模な電力ブリッジの用途を可能にするための、コスト効果の高い、かつ信頼性の高い手段を提供する。より具体的には、本明細書で説明されるシステムおよび方法により、リアルタイムの状況を使用する転流トリガを確立するためにボルト秒の蓄積を使用して、出力電圧が使用される場合に対して、DCリンク電圧での外乱、転流回路および電源デバイスの影響を拒絶することが容易になる。例示的な実施形態では、(ブリッジに対抗する)循環電流のバイアス余弦の位相コントローラと両立する変調器が使用される。結果として、本明細書で説明されるシステムおよび方法に

40

50

より、電力変換システムの出力での高忠実度の波形を、コスト効果の高い、かつ信頼性の高い方法で発生させることが容易になる。

#### 【0024】

この記述された説明は、最良の形態を含めて、発明を開示するために、さらには、任意のデバイスもしくはシステムを作製かつ使用すること、ならびに、任意の組み込まれた方法を実行することを含めて、任意の当業者が本発明を実施することを可能にするために、例を使用する。本発明の特許的な範囲は、特許請求の範囲により定義され、当業者が想到する他の例を含み得る。そのような他の例は、それらが特許請求の範囲の文字通りの文言と異なる構造的要素を有するならば、または、それらが特許請求の範囲の文字通りの文言と実質的な違いのない等価な構造的要素を含むならば、特許請求の範囲の範囲内にあることが意図されている。

10

#### 【符号の説明】

#### 【0025】

|     |                                        |    |

|-----|----------------------------------------|----|

| 100 | 電力変換器システム（P C S）                       | 20 |

| 102 | 入力アセンブリ                                |    |

| 104 | 変換器                                    |    |

| 106 | 出力アセンブリ                                |    |

| 108 | 複数のトランジスタ対                             |    |

| 110 | 巻線                                     |    |

| 112 | D C リンク                                |    |

| 114 | 制御ユニット                                 |    |

| 115 | プロセッサ                                  |    |

| 116 | カウンタ                                   |    |

| 118 | 出力                                     |    |

| 120 | 電気モータ                                  |    |

| 122 | 負荷                                     |    |

| 200 | 方法                                     |    |

| 202 | 積分電圧値を発生させるために、外乱成分を含む電圧信号を積分するステップ    |    |

| 204 | 積分電圧値を所定のしきい値と比較するステップ                 |    |

| 206 | 積分電圧値が所定のしきい値に等しいときに電力変換器の転流をトリガするステップ | 30 |

【図1】

【図2】

---

フロントページの続き

- (72)発明者 アレン・マイケル・リッター

アメリカ合衆国、バージニア州・24153、セイレム、ロアノーク・ブルーヴァード、1501番

- (72)発明者 ロバート・アレン・シーモア

アメリカ合衆国、バージニア州・24153、セイレム、ロアノーク・ブルーヴァード、1501番

- (72)発明者 ラジブ・ダッタ

アメリカ合衆国、バージニア州・24153、セイレム、ロアノーク・ブルーヴァード、1501番

- (72)発明者 ジョン・ダグラス・ドアトレ

アメリカ合衆国、ワシントン州・98685、ヴァンクーバー、ノースウェスト・ハンドレッド・トゥエンティー・セブンス・ストリート、2421番

審査官 津久井 道夫

- (56)参考文献 米国特許第07511439(US, B1)

特開2003-153549(JP, A)

特開2007-306709(JP, A)

特開平08-066079(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02P 7/42 - 7/98

H02P23/00 - 23/30