(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4212293号

(P4212293)

(45) 発行日 平成21年1月21日(2009.1.21)

(24) 登録日 平成20年11月7日(2008.11.7)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 23/12  | (2006.01) | HO1L 23/12 | 501P |

| HO1L 25/065 | (2006.01) | HO1L 25/08 | B    |

| HO1L 25/07  | (2006.01) |            |      |

| HO1L 25/18  | (2006.01) |            |      |

請求項の数 9 (全 9 頁)

(21) 出願番号

特願2002-1111571 (P2002-1111571)

(22) 出願日

平成14年4月15日 (2002.4.15)

(65) 公開番号

特開2003-309221 (P2003-309221A)

(43) 公開日

平成15年10月31日 (2003.10.31)

審査請求日

平成17年4月15日 (2005.4.15)

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100107906

弁理士 須藤 克彦

(74) 代理人 100091605

弁理士 岡田 敏

(72) 発明者 野間 崇

大阪府守口市京阪本通2丁目5番5号

三洋電機株式会社内

審査官 宮本 靖史

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表面側に金属パッドが形成された半導体ウエハを準備し、前記半導体ウエハの前記金属パッドが形成された表面側に対して、当該半導体ウエハを支持する支持体を溶液に溶ける有機膜から成るフィルムを介して貼り合わせる工程と、前記支持体が貼り合わされた前記半導体ウエハの裏面から前記金属パッドまで貫通する開口を形成する工程と、

前記開口の側壁部に絶縁膜を形成した後に、当該開口内に金属層を形成する工程と、前記支持体が貼り合わされた前記半導体ウエハの裏面から前記フィルムまでダイシングする工程と、

前記半導体ウエハと前記支持体とを分離する工程とを有することを特徴とする半導体装置の製造方法。

## 【請求項 2】

前記半導体ウエハの前記金属パッドが形成された表面側に対して、当該半導体ウエハを支持する支持体をフィルムを介して貼り合わせる工程が、前記半導体ウエハと前記支持体の外径よりも小さい外径を有するフィルムを前記半導体ウエハと前記支持体とで挟んだ状態で、その周端部のみエポキシ樹脂を用いて貼り合わせる工程であることを特徴とする請求項1に記載の半導体装置の製造方法。

## 【請求項 3】

前記フィルムが、粘着性を有するフィルムであることを特徴とする請求項1、2のいず

10

20

れかに記載の半導体装置の製造方法。

【請求項 4】

前記金属層上に電極を形成する工程を有することを特徴とする請求項 1 乃至請求項 3 のいずれかに記載の半導体装置の製造方法。

【請求項 5】

前記金属層上に電極を形成する工程が、当該金属層上に金属配線を形成し、当該金属配線上に電極を形成する工程を有することを特徴とする請求項 4 に記載の半導体装置の製造方法。

【請求項 6】

前記半導体ウエハ裏面に前記開口を形成する前に、その裏面を研磨することを特徴とする請求項 1 乃至請求項 5 のいずれかに記載の半導体装置の製造方法。 10

【請求項 7】

前記金属パッド上に電極接続用の金属層を形成する工程を有することを特徴とする請求項 1 乃至請求項 6 のいずれかに記載の半導体装置の製造方法。

【請求項 8】

一方の半導体装置の前記金属層と他方の半導体装置の前記電極とを積層する工程を有することを特徴とする請求項 7 に記載の半導体装置の製造方法。

【請求項 9】

前記支持体は、Si 基板、酸化膜、ガラス基板、セラミックのいずれかから成ることを特徴とする請求項 1 乃至請求項 8 のいずれかに記載の半導体装置の製造方法。 20

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体装置の製造方法に関し、更に言えば、ボール状の導電端子を有する BGA (Ball Grid Array) 型の半導体装置の製造方法に関する。

【0002】

【従来の技術】

従来より表面実装型の半導体装置の一種として BGA 型の半導体装置がある。これは、半田等の金属部材から成るボール状の導電端子をパッケージ基板一主面上に格子状に複数配列し、基板の他の主面上に搭載される半導体チップとボンディングしてパッケージングするものである。そして、電子機器に組み込まれる際には、各導電端子をプリント基板上の配線パターンに熱溶着し、半導体チップとプリント基板上に搭載される外部回路とを電気的に接続する。 30

【0003】

このような BGA 型の半導体装置は、半導体装置の側面に突出したリードピンを有する SOP (Small Outline Package) や QFP (Quad Flat Package) 等の他の表面実装型の半導体装置に比べ多数の接続端子を 設置 することができ、小型化が有利なものとして知られている。

【0004】

近年において、この BGA 型の半導体装置が CCD イメージセンサの分野にも取り入れられ、小型化の要望が強い携帯電話機に搭載されるデジタルカメラのイメージセンサチップとして用いられている。 40

【0005】

また、ウエハレベルの CSP (Chip Size Package) やシリコン (Si) 貫通技術を用いた 3 次元実装技術が注目されてきている。これらの技術は、チップを何層にも貼り合わせた後、Si を貫通させたり、Si ウエハを表面から Si 貫通させた後、積み上げる方法等が研究されている。

【0006】

【発明が解決しようとする課題】

しかし、従来の 3 次元実装技術は、表面から Si 貫通等の加工を行い、銅 (Cu) のピア 50

ホールを形成するため、表面側に C M P (Chemical Mechanical Polishing) 処理が必要であったり、Cu ビア形成後に当該 Cu ビアとパッドとを繋ぐための再配線が必要であるため、製造工数が多くなってしまう。

【0007】

【課題を解決するための手段】

そこで、本発明の半導体装置の製造方法上記課題に鑑み、表面側に金属パッドが形成された半導体ウエハを準備し、前記半導体ウエハの前記金属パッドが形成された表面側に対して、当該半導体ウエハを支持する支持体を溶液に溶ける有機膜から成るフィルムを介して貼り合わせる工程と、前記支持体が貼り合わされた前記半導体ウエハの裏面から前記金属パッドまで貫通する開口を形成する工程と、前記開口の側壁部に絶縁膜を形成した後に、当該開口内に金属層を形成する工程と、前記支持体が貼り合わされた前記半導体ウエハの裏面から前記フィルムまでダイシングする工程と、前記半導体ウエハと前記支持体とを分離する工程とを有することを特徴とするものである。

10

【0008】

また、前記ウエハと当該ウエハを支持する支持体とをフィルムを介して貼り合わせる工程が、前記ウエハと前記支持体の外径よりも小さい外径を有するフィルムを前記ウエハと前記支持体とで挟んだ状態で、その周端部のみエポキシ樹脂を用いて貼り合わせる工程であることを特徴とするものである。

【0010】

また、前記フィルムが、粘着性を有するフィルムであることを特徴とするものである。

20

【0012】

そして、前記金属層上に電極を形成する工程が、当該金属層上に金属配線を形成し、当該金属配線上に電極を形成する工程を有することを特徴とするものである。

【0013】

【発明の実施の形態】

以下、本発明の半導体装置の製造方法に係る一実施形態について図面を参照しながら説明する。

【0014】

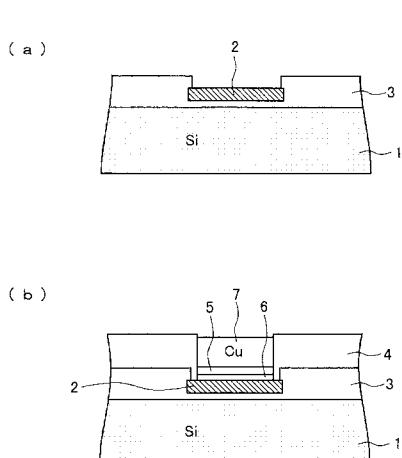

先ず、図1(a)に示すようにおよそ  $600 \mu\text{m}$  の膜厚のシリコンウエハ(以下、Si 基板)1上に酸化膜が形成され、当該酸化膜上に金属(例えば、Al)パッド2が形成され、当該Alパッド2を被覆するようにプラズマCVD法によるSiO<sub>2</sub>膜またはPSG膜から成る所定膜厚の酸化膜3を形成する。尚、特に平坦性を必要とする場合には酸化膜を例えばCMP研磨等しても良い。そして、不図示のフォトレジスト膜をマスクにAlパッド2上の酸化膜3をエッティングして当該Alパッド2の一部(表面部)を露出させる。尚、本実施形態では、前記酸化膜3の膜厚は、全体でおよそ  $5 \mu\text{m}$  程度としている。

30

【0015】

次に、図1(b)に示すように前記Alパッド2及び酸化膜3上にポリイミド膜を形成し、当該ポリイミド膜を不図示のフォトレジスト膜をマスクにエッティングして前記Alパッド2上に開口部を有するポリイミド膜4を形成する。そして、前記開口部内にニッケル(Ni)5、金(Au)6を形成した後に、その上に銅(Cu)メッキしてCu7を埋め込む。また、当該Cu7上に当該Cu7の腐食防止用としてAuをメッキ形成しても良い。尚、本実施形態では、前記開口部内に埋設された導電部材(Ni, Au, Cu, Au)の膜厚は、全体でおよそ  $25 \mu\text{m}$  程度としている。

40

【0016】

ここで、本プロセスが、CCDイメージセンサに採用される場合には、前記ポリイミド膜4は透明性のポリイミド膜または透明ガラスエポキシ樹脂等をスクリーン印刷法を用いて形成する必要がある。

【0017】

更に言えば、本プロセスを3次元プロセスに用いないCSPプロセスに適用するものである場合には、開口部を形成する必要はなく、ポリイミド膜4の全面塗布で構わない。

50

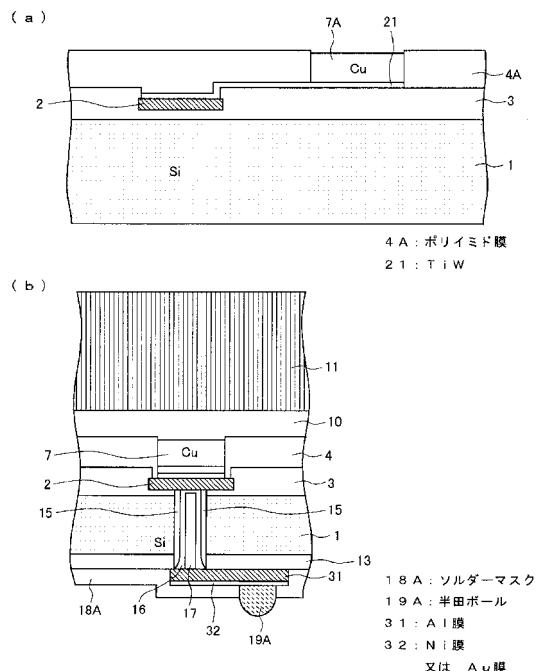

## 【0018】

また、図8(a)に示すように前記A1パッド2上を含む酸化膜3上にTiW21(もしくはTiW上にCuを形成しても良い。)を形成し、所定パターンと成るようにパターニングする。そして、ポリイミド膜4Aを介してCu7A(Au)を形成する、いわゆる再配線構造を採用しても良い。

## 【0019】

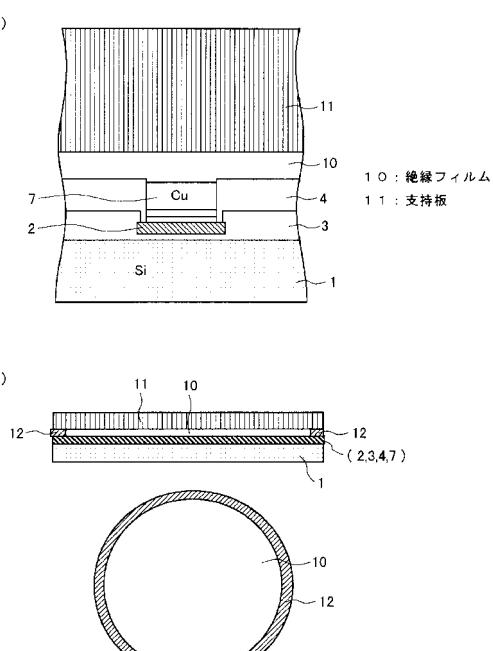

続いて、図2(a)に示すように前記Cu7(Au)上を含むポリイミド膜4上に絶縁フィルム10を貼り、当該フィルム10を介して支持板11と前記Si基板1側を貼り合わせる。

## 【0020】

ここで、前記支持板11は、後述するSi基板1のBG(バックグラウンド)時に、Si基板1の割れ等を防止するための支持体で、例えばSi基板や酸化膜(ガラス基板)やセラミック等を利用している。尚、本実施形態では、支持体として必要な膜厚として、およそ400μm程度としている。

## 【0021】

また、前記フィルム10は、後述するSi基板1と支持板11との分離工程における作業性向上を図る目的で、アセトンに溶ける有機膜を採用している。尚、本実施形態では、フィルム10の膜厚をおよそ400μm程度としている。

## 【0022】

更に、当該フィルム10の外周部には、図2(b)に示すようにエポキシ樹脂12を充填することで、当該フィルム10を密封し、固めている。これにより、各種作業中における有機溶媒等の薬液の侵入を防止している。

## 【0023】

尚、Si基板1のBG工程におけるバックグラウンド膜厚が少ない場合には、支持板11を貼り付ける工程は省略できる。

## 【0024】

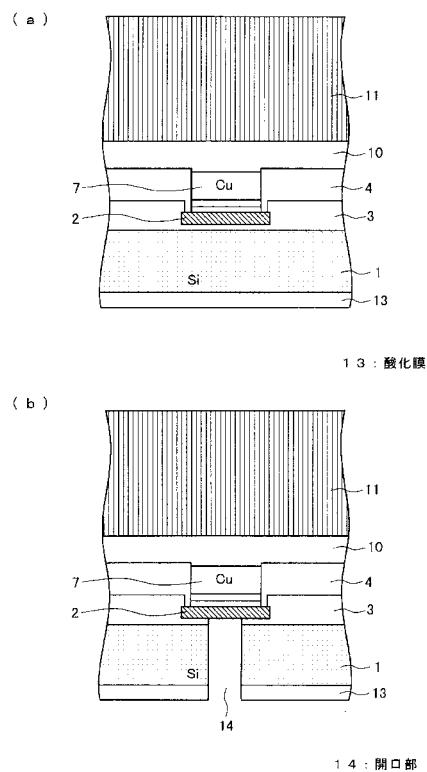

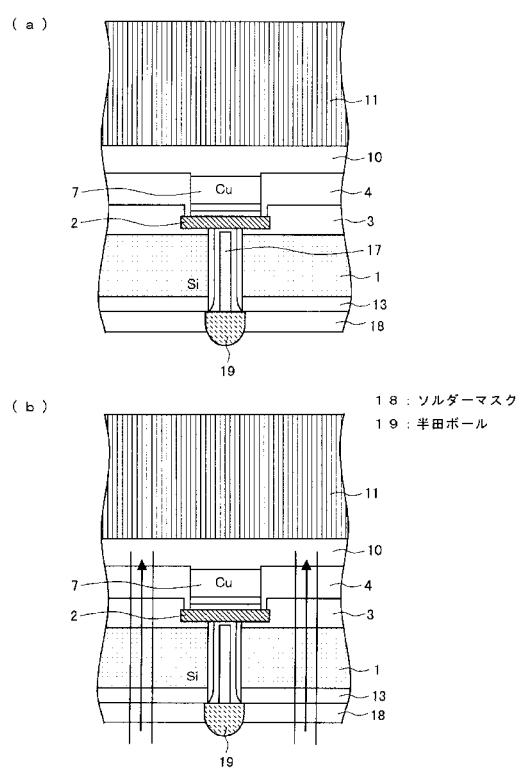

次に、図3(a)に示すようにSi基板1側をBG処理して、当該Si基板1の膜厚をおよそ10~100μm程度まで薄膜化できる。このとき、前記支持板11が、BG工程時にSi基板1を支持する。そして、BG処理したSi基板1の裏面側におよそ0.01μm程度の酸化膜13を形成する。尚、前記酸化膜13の代わりにシリコン窒化膜やポリイミドから成る有機系絶縁物を形成しても良い。更に言えば、前記BG工程において、Cu上の平坦性に左右されないため、そのままバックグラウンド可能であり、作業性が良い。

## 【0025】

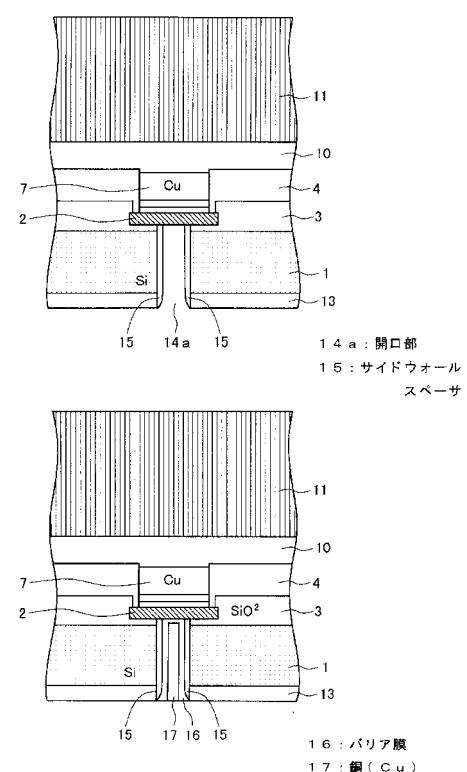

更に、図3(b)に示すように不図示のフォトレジスト膜をマスクに前記酸化膜13及びSi基板1をエッチングして開口部14を形成する。続いて、図4(a)に示すように前記開口部14から露出した酸化膜3をエッチングして、前記A1パッド2を露出させる。そして、開口部14a内の前記A1パッド2上を含む酸化膜13上を被覆するようにCVD法による酸化膜を形成し、当該酸化膜を異方性エッチングして開口部14aの側壁部に酸化膜を残膜させてサイドウォールスペーサ膜15を形成する。尚、酸化膜のCVD成膜処理温度は、200程度の低温度が良い。また、シリコン窒化膜を用いてサイドウォールスペーサ膜15を形成しても良い。

## 【0026】

次に、図4(b)に示すように前記開口部14a内にサイドウォールスペーサ膜15を介して窒化チタン(TiN)または窒化タンタル(TaN)等のバリア膜16をスパッタ形成し、当該バリア膜16を介して前記開口部14a内にCu17を埋設する。尚、本工程では、先ずバリア膜16上にCuシード、Cuメッキ処理を施し、当該Cuをアニール処理する。そして、当該Cuを開口部14a内に埋設させている。ここで、平坦性を特に必要とする場合は、当該CuをCMP研磨する。

## 【0027】

更に、図5(a)に示すように前記Cu17上に、当該Cu17が埋設された開口部14

10

20

30

40

50

a の開口サイズよりも幾分広い開口を有するソルダーマスク 18 を形成し、当該マスク 18 を介して当該開口上に半田ペーストをスクリーン印刷し、当該半田ペーストをリフロー処理することで、Cu 17 上に半田ボール 19 を形成する。尚、本実施形態では、ソルダーマスク 18 として、200 °でイミド化可能なりカコートから成るポリイミド膜を用いている。

【0028】

尚、図 8 (b) に示すように前記 Cu 17 上を含む酸化膜 13 上に Al 膜 31 及び Ni 膜 (Au 膜) 32 を形成し、所定パターンと成るようにパターニングする。そして、ソルダーマスク 18 A を介して半田ボール 19 A を形成する構造を採用しても良い。

【0029】

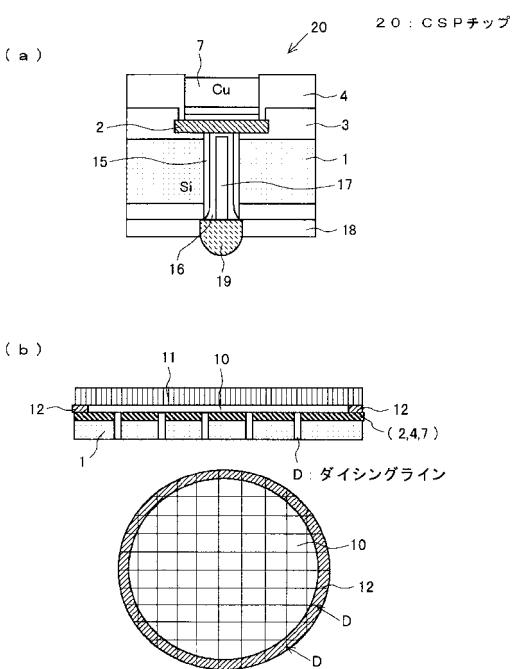

続いて、図 5 (b) に示すように前記 Si 基板 1 側を前記フィルム 10 に到達する位置までダイシングする。

【0030】

そして、不図示のアセトン溶液槽内に当該 Si 基板 1 を浸することで、図 6 (b) に示すように前記ダイシングライン (D) からアセトンが侵入し、前記フィルム 10 を溶解する。従って、前記 Si 基板 1 (各チップ) と支持板 11 とが自動的に分離され、図 6 (a) に示すような単体の CSP チップ 20 が完成する。

【0031】

このように本実施形態では、アセトンに溶解する有機系のフィルム 10 を用いて Si 基板 1 と支持板 11 とを貼り合わせているため、ダイシング後に、Si 基板 1 をアセトンに浸すだけで両者を簡単に分離することができ、作業性が良い。

【0032】

また、前記フィルム 10 の代わりに粘着力の弱いフィルムを用いて、ダイシング後に、物理的にチップを剥がすものであっても良い。更に言えば、支持板 11 として透明ガラスを用いる場合には、有機系フィルム 10 として UV テープを貼り、ダイシング後に UV 照射をし、チップを剥がせば良い。

【0033】

加えて、ダイシングした後に、例えばウエハの裏面からホットプレートで熱を加えて、ウエハと支持基板 11 で挟まれた有機膜 (フィルム 10) を溶かして軟化させることで両者を剥がすものであっても良い。このとき、フィルム 10 がアセトンに溶ける有機膜であるときは、200 °程度の加熱で、ポリイミド膜を利用した場合では 400 °程度の加熱で当該フィルム 10 は溶ける。

【0034】

Si 基板 1 と支持板 11 とを剥がす別形態としては、ダイシング前に、エッジのエポキシ樹脂を、ウエハを縦にして回転させ、外周だけ酸などの薬品に浸して剥がす方法もある。又、刃物をウエハとチップの間のエッジのエポキシ樹脂に入れて切り離す方法もある。そして、両方法の後、BG テープを貼ってダイシングする。

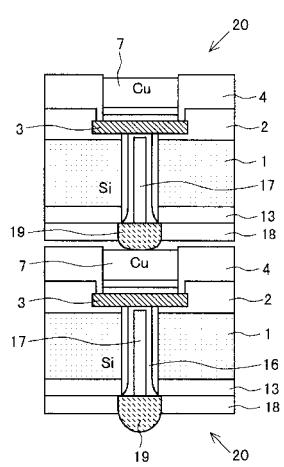

【0035】

そして、図 7 に示すように前記単体の CSP チップ 20 を Cu 7 (Au) と半田ボール 19 とを金属密着で CSP チップ 20 同士を密着 (積層) させることで、3 次元実装が (何層でも) 可能となり、チップサイズの同じもの (メモリ等) であれば大容量化が図れる。

【0036】

【発明の効果】

本発明では、従来の 3 次元実装技術のように表面から Si 貫通等の加工を行い、銅 (Cu) のビアホールを形成するため、表面側に CMP (Chemical Mechanical Polishing) 処理を必要としない。また、Cu ビア形成後に当該 Cu ビアとパッドとを繋ぐための再配線が不要であるため、製造工数が増大することがない。

【0037】

更に言えば、Cu 上の平坦性に左右されないため、そのままバックグラウンド可能である。

10

20

30

40

50

## 【0038】

また、支持板 11 と Si 基板 1 とは、貼り合わせた後に BG ( バックグラインド ) 及びその後の処理をしているため、チップの膜厚は 必要に応じて薄くできる。

## 【図面の簡単な説明】

【図 1】本発明の一実施形態の半導体装置の製造方法を示す断面図である。

【図 2】本発明の一実施形態の半導体装置の製造方法を示す断面図である。

【図 3】本発明の一実施形態の半導体装置の製造方法を示す断面図である。

【図 4】本発明の一実施形態の半導体装置の製造方法を示す断面図である。

【図 5】本発明の一実施形態の半導体装置の製造方法を示す断面図である。

【図 6】本発明の一実施形態の半導体装置の製造方法を示す断面図である。

【図 7】本発明の一実施形態の半導体装置の製造方法を示す断面図である。

【図 8】本発明の他の実施形態の半導体装置の製造方法を示す断面図である。

10

【図 1】

1 : Si 基板 2 : パッド 3 : 酸化膜

4 : ポリイミド膜 5 : ニッケル (Ni)

6 : 金 (Au) 7 : 銅 (Cu)

【図 2】

12 : エポキシ樹脂 (Epoxy resin)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2002-083785(JP,A)

特開2000-183025(JP,A)

特開平11-307624(JP,A)

特開平03-152942(JP,A)

特開昭62-101678(JP,A)

特開2001-210667(JP,A)

特開2001-068618(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 25/065

H01L 25/07

H01L 25/18