(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4406995号

(P4406995)

(45) 発行日 平成22年2月3日(2010.2.3)

(24) 登録日 平成21年11月20日(2009.11.20)

(51) Int.Cl.

H01L 21/205 (2006.01)

F 1

H01L 21/205

請求項の数 3 (全 7 頁)

|           |                               |           |                                             |

|-----------|-------------------------------|-----------|---------------------------------------------|

| (21) 出願番号 | 特願2000-86117 (P2000-86117)    | (73) 特許権者 | 000005821<br>パナソニック株式会社<br>大阪府門真市大字門真1006番地 |

| (22) 出願日  | 平成12年3月27日 (2000.3.27)        | (74) 代理人  | 100097445<br>弁理士 岩橋 文雄                      |

| (65) 公開番号 | 特開2001-274090 (P2001-274090A) | (74) 代理人  | 100109667<br>弁理士 内藤 浩樹                      |

| (43) 公開日  | 平成13年10月5日 (2001.10.5)        | (74) 代理人  | 100109151<br>弁理士 永野 大介                      |

| 審査請求日     | 平成18年11月16日 (2006.11.16)      | (72) 発明者  | 神澤 好彦<br>大阪府門真市大字門真1006番地 松下電器産業株式会社内       |

|           |                               | (72) 発明者  | 能澤 克弥<br>大阪府門真市大字門真1006番地 松下電器産業株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体基板および半導体基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

シリコン結晶基板と、前記シリコン結晶基板上に形成された前記シリコン結晶基板より大きな格子定数をもつ結晶層とを具備し、前記結晶層の少なくとも一部が、炭化珪素結晶を含有するシリコンとゲルマニウムと炭素からなる格子緩和された結晶であり、前記シリコン結晶基板と前記シリコンとゲルマニウムと炭素からなる格子緩和された結晶との界面から 20 nm 以内の領域にのみ結晶欠陥が存在していることを特徴とする半導体基板。

## 【請求項 2】

最表面がシリコン結晶層からなり、このシリコン結晶層が歪んでいることを特徴する請求項 1 に記載の半導体基板。

10

## 【請求項 3】

シリコン結晶基板上に、少なくとも一部にシリコンとゲルマニウムと炭素を含有する結晶層を堆積する工程と、前記結晶層を堆積した前記シリコン結晶基板を熱アニュールし、前記結晶層中に SiC 結晶を析出させる半導体基板の製造方法であって、

前記シリコンとゲルマニウムと炭素を含有する結晶層は格子緩和され、

前記シリコン結晶基板と前記シリコンとゲルマニウムと炭素からなる格子緩和された結晶層との界面から 20 nm 以内の領域にのみ結晶欠陥を発生させることを特徴とする半導体基板の製造方法。

## 【発明の詳細な説明】

## 【0001】

20

**【発明の属する技術分野】**

本発明は、半導体基板の形成方法に係り、特に歪を含有する半導体結晶からなる基板の形成方法に関する。

**【0002】****【従来の技術】**

バルクSi結晶を使った半導体デバイスが多機能性、高速性を次々と実現してきたのは、主として素子の微細化によるところが大きい。当然ながら、今後もデバイスの性能向上のためには、更なる微細化を進める必要があるが、デバイスの微細化を今以上に進めるには、技術的に乗り越えなければならない課題が多く存在し、困難であることが予想される。さらに、いくら微細化を行っても、デバイスの最高性能は、バルクSi結晶という材料のもつ物理的特性（例えば、移動度）によって制約をうける。つまり、バルクSi結晶という材料を使う限り、飛躍的にデバイス性能を向上させるのは難しいと言える。

10

**【0003】**

そこで、近年、バルクSi結晶以外の材料を導入し、デバイス特性の向上をはかろうという試みが行われている。このような取り組みの一つが、シリコンとゲルマニウム(SiGe)、シリコンとゲルマニウムと炭素の混晶(SiGeC)等といった、Siよりも移動度の大きな新規材料の利用である。そして、もう一つが、歪Si結晶の利用であり、これは、Si結晶に歪という新しい要素を加えて、intervalley scatteringと呼ばれる電子の散乱を低減し、移動度を向上させようというアプローチである。これらのうち、特に、後者の歪Si結晶は、バルクSi結晶を歪ませるだけで性能向上が図れる上、既存のSiプロセスの技術（例えば、酸化やエッチング工程の技術）を使ってそのままデバイスへの加工ができるため、工業的にも注目を集めている。

20

**【0004】**

従来、このような歪Siは、バルクSi結晶基板の上に厚いSiGe結晶層を堆積し、その上にSi結晶を堆積することで作製されている。一般にSiGe結晶はSiよりも大きな格子定数を持つ結晶であるので、基板平面内の格子をSiに整合させた状態でSiGe結晶を成長させると、SiGe結晶には、非常に大きな圧縮性の歪が生じる。そして、ある一定以上の膜厚（臨界膜厚）を超えてSiGe結晶を堆積すると、バルクSi結晶基板と、SiGe層の間に転位が発生し、歪が緩和する。その結果、SiGeの基板平面内の格子間隔はバルクSi結晶基板の格子間隔よりも大きくなる。そしてこのSiGe結晶の上にSi結晶をエピタキシャルに堆積すると、このSiの平面方向の格子間隔は、緩和したSiGe結晶の格子間隔と一致し、引っ張り応力を受ける形になり、歪Siが作製できる（なお、以下では、上記のSiGe結晶のように、格子緩和を起こし、バルクSi結晶基板よりも大きな格子間隔をもつ結晶層のことを、緩和バッファ層と呼ぶ）。

30

**【0005】****【発明が解決しようとする課題】**

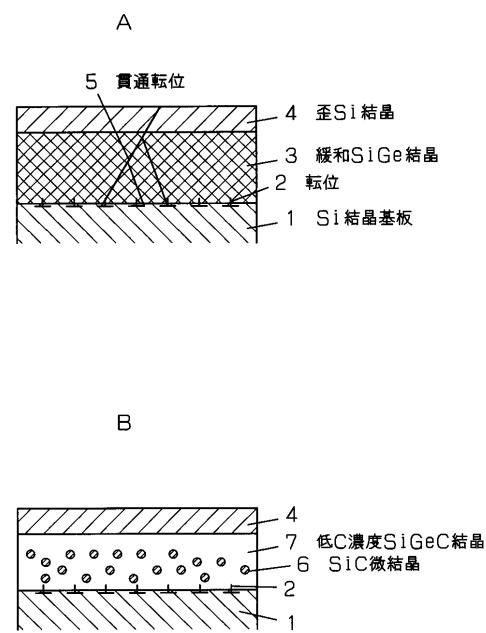

ここで、図1Aを参照して、もう少し詳しく従来の歪Si結晶を実現するための構造について説明する。まず、バルクSi結晶基板上に臨界膜厚を超える厚い緩和SiGe結晶層3を成長する。すると、上述のようにSi基板1とSiGe結晶層3の間には転位2が発生し、SiGe結晶は緩和する。そしてこの上にSi結晶4を堆積して歪Si結晶を得る。しかしながら、上記のような単に臨界膜厚より厚いSiGeによる緩和バッファ層では、図1Aの5に模式的に示したように貫通転位と呼ばれる大きな欠陥が発生することが知られている。そして状況によっては、この貫通転位が歪Si結晶4の中にまで入り込み、歪Si層にも欠陥を形成する要因となる。当然、このような欠陥は、デバイス特性の向上を妨げる要因となるため、できるだけ避けなければならない。

40

**【0006】**

そこで、貫通転位の密度を低減する構造として、SiGe結晶中のGe濃度を階段的、もしくは傾斜的に変化させた構造が良く用いられているが、いずれの場合も転位密度を下げるには、数μm以上のかなり厚いSiGe結晶を堆積する必要がある。当然ながら、この厚い緩和バッファ層の製造には、長時間の結晶成長が必要であり、基板製造の低コスト化は難しく

50

なる。そのため、現状では、緩和SiGe結晶を使った歪Si結晶の実際の半導体デバイスへの工業的な応用は困難であると考えられている。

### 【0007】

#### 【課題を解決するための手段】

上記の課題を解決するために、本発明では、図1Bに示したような、SiC結晶を含有するSiGeC結晶を緩和バッファ層として用いる、従来にはない新しい方法を提案する。この方法によれば、薄い膜厚で、欠陥の少ない緩和バッファ層が形成でき、歪Si結晶等の製造が可能となる。

### 【0008】

#### 【発明の実施の形態】

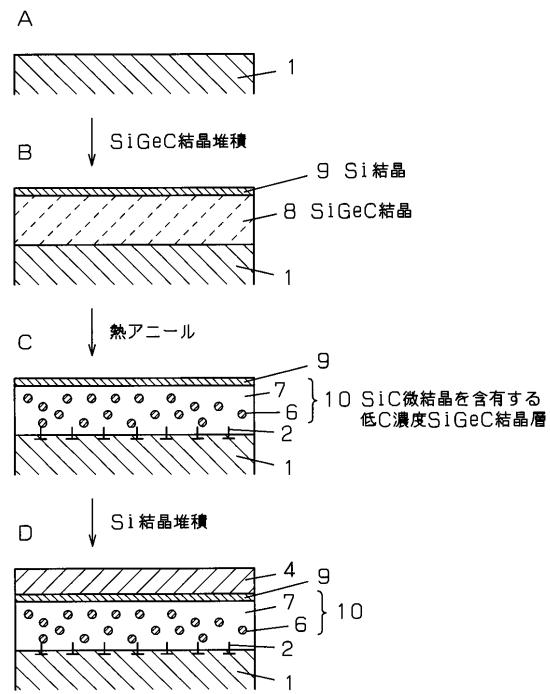

ここではまず、第一の実施形態として、図2のAからCを参照し、SiC微結晶を含むSiGeC結晶を使った緩和バッファ層について説明する。

### 【0009】

まず、はじめに、(001)面のSi基板1を洗浄後、SiGeC結晶8を超高真空化学気相堆積法(UHV-CVD法)で堆積した(図2 A B)。この方法について最初に詳しく述べる。

### 【0010】

Si基板の洗浄は次のようにして行った。まず、Si基板を硫酸-過酸化水素水混合溶液で洗浄し、基板表面上の有機物、金属汚染物質を除去した。次にアンモニア-過酸化水素水溶液にて洗浄し、ウエハー上の付着物を除去した。さらに、フッ酸溶液を用いてSi基板表面の自然酸化膜を取り去り、最後に再びアンモニア-過酸化水素水溶液にウエハーを浸し、Si基板表面に薄い保護酸化膜を形成した。その後、このSi基板を、UHV-CVD装置内に投入した。そして、一旦、UHV-CVD装置内を、 $2 \times 10^{-9}$ Torr(1Torr = 133.322Pa)まで真空引きした後、水素ガス雰囲気中で800の温度に基板を加熱し、上記の保護酸化膜を除去し、清浄Si基板表面を露出させた。次にSi基板1の温度を490まで低下させ、原料ガスとして、ジシラン( $\text{Si}_2\text{H}_6$ )ガスと、ゲルマン( $\text{GeH}_4$ )ガスとメチルシラン( $\text{SiCH}_6$ )ガスをUHV-CVD装置内に導入し、15分間の結晶成長を行い、約130nmのSiGeC結晶8を堆積した。なお、この時の各ガスの圧力は、 $\text{Si}_2\text{H}_6$ ガスを $7 \times 10^{-5}$ Torr、 $\text{GeH}_4$ ガスを $3 \times 10^{-4}$ Torr、 $\text{SiCH}_6$ ガスを $9 \times 10^{-6}$ Torrとした。その後、 $\text{GeH}_4$ と $\text{SiCH}_6$ ガスの供給を停止し、一旦、基板温度を550

に上げて、 $\text{Si}_2\text{H}_6$ ガスのみを $2.4 \times 10^{-4}$ の圧力で2分間供給し、約4nmのSi結晶9を堆積した。このSi保護膜は、この後に使用する洗浄装置等のプロセス装置へ、GeやC原子が流れ出し、汚染するのを防ぐために堆積したものである。

### 【0011】

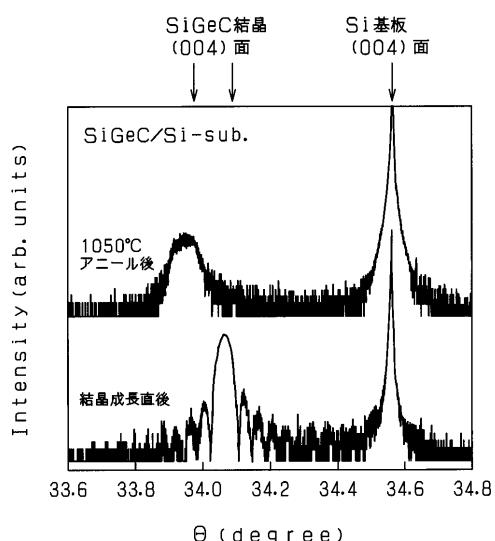

ここで次の工程の説明を行う前に、SiGeC結晶成長直後の結晶の状態について説明する。図3の下側に示したのが、図2Bの状態の試料の結晶のXRDスペクトルである。まず、この図で34.56°付近に観測されているピークは、基板として用いたSiの(004)面の回折によるピークであり、34.06°付近のピークが堆積したSiGeC結晶8によるものである。このSiGeC結晶は完全歪の状態、つまりSi基板に平行な方向のSiGeC結晶の格子定数がSi基板の格子定数と完全に一致した状態にあると考えられ、X線回折スペクトルのピーク角度から、Vegard則と呼ばれる結晶解析手法を用いて結晶の組成を見積ると、Geを30.5%、Cを約1.2%程度含有するSiGeC結晶であることが分かった。さらに、図2下のスペクトルを詳細に見ると、34.06°付近のSiGeC結晶のピークのまわりに小さなピークが観測されている。これはPendelloosung fringeと呼ばれるもので、これが観測されると言うことは、ここで作製したSiGeC結晶の結晶性並びに平坦性が非常に良好であることを意味している。結晶性に関しては、透過型電子顕微鏡(TEM)で断面観測も行って確かめたが、Si基板と堆積したSiGeC結晶の界面及びSiGeC結晶中にも全く欠陥等は全く観測されなかった。

### 【0012】

次に、図2Bの状態の基板をUHV-CVD装置から取り出し、熱アニールした(図2 B C)。ここで、熱アニールは、窒素雰囲気中で1050、15秒間行った。

### 【0013】

この熱アニールした基板の断面をTEMによって観測すると、図2のCに模式的に示したよう

10

20

30

40

50

に、均一なSiGeC結晶であった部分に、直径が約2nm程度のSiC結晶と考えられる微結晶6が析出していた。これは、準安定な結晶であるSiGeC結晶が熱アニールによって、安定な結晶であるSiC結晶とSiGe結晶へと相分離を起こしたために起こったと考えられる。この時、堆積層6中のほとんどのCがSiC結晶4の部分に集まっており、そのまわりの部分7は、C濃度がかなり低下したSiGeC結晶（以下、低C濃度SiGeC結晶層）になっていると予想される。なお、図2Cでは、わかり易く表現するために、SiC微結晶が大きな体積割合で表現されているが、実際には、SiC微結晶体積比率はかなり小さいことをここで断っておく。またTEM写真を詳細にみると、Si基板1とSiC結晶を含有する低C濃度SiGeC結晶層10の界面の20nm程度の領域にのみ、転移と考えられる欠陥が発生していた。しかし、SiC結晶を含有する低C濃度SiGeC結晶層10の中には欠陥はほとんど見られなかった。一般に、単なるSiGe結晶をSi上に堆積したもので熱アニールすると、大きな貫通転移等が発生することが知られているが、本実施例の試料では、このような欠陥は全く発生してなかった。10

#### 【0014】

ここで貫通転移のような大きな欠陥がなぜ発生しなかったかについて簡単に考えてみる。SiC微結晶とまわりのC濃度が低くなったSiGeC結晶の格子定数は大きく異なる（おそらく20%程度）。それ故に、SiC微結晶とまわりのC濃度が低くなったSiGeC結晶の間にはTEM写真では観測できないような微少な欠陥が形成されていると考えられる。おそらくこの微少な欠陥の存在によって、歪みが少しずつ緩和され、結果として貫通転位等の大きな欠陥の発生を伴わず、全体の緩和が進行したものと考えられる。

#### 【0015】

図2Cの状態でのX線回折を測定した結果が図3の上側のスペクトルである。33.95°に現れているピークが低C濃度SiGeC結晶層による回折ピークに相当する。このピーク角度とVegard則を使って詳細に解析すると、堆積層では予想通り、緩和が起こっており、基板の面内の格子間隔は、Siの格子定数より0.6%程度大きい、0.5494nm程度であることが分かった。厳密に言えば、この値は、低C濃度SiGeC結晶層7のみの値であり、SiC結晶を含有する低C濃度SiGeC結晶層10全体の格子定数ではない。しかしながら、上述したようにSiC結晶の体積比率はかなり小さな値であったため、低C濃度SiGeC結晶層10全体の格子定数と同等であると考えて良いと思われる。以上のことから、本発明で提案する、Si基板とSiC結晶を含有するSiGeC結晶層を具備する構造が、欠陥の少ない緩和バッファ層として機能することが明らかとなった。また、本実施例で作製した基板では、上記の様に、欠陥が基板と堆積層の界面近傍20nmにのみ発生していたことから、本実施例よりもかなり薄い堆積層のみで、貫通転位等の欠陥のない基板を製造できることも明らかとなった。30

#### 【0016】

なお、上記の実施例では、Si基板1上に直接SiGeC結晶8を成長したが、Si基板とSiGeC結晶の間にSiやSiGe等の堆積結晶が存在してもよい。また、SiGeC結晶8の上のSiの保護膜9は洗浄装置等のプロセス装置へ、GeやC原子が流れ出し、汚染するのを防ぐためだけに堆積したものであり、膜厚は上記の値よりも薄くても厚くても良く、必ずしも必要なものではない。また、SiGeC結晶8の組成も上記で述べた濃度に限定されるものではない。さらに、本実施例では、SiGeC結晶の堆積後、一旦、結晶成長装置から基板を取り出して、1050での熱アニールを行ったが、必ずしもこのような手順を踏む必要はなく、SiGeC結晶の成長後、結晶成長装置内で連続して熱アニール処理を行っても良いし、アニール温度も1050に限定されるものではない。40

#### 【0017】

次に、第2の実施例として、上述の緩和バッファ層を用いて、歪Siを作製した結果を図2CとDを用いて説明する。

#### 【0018】

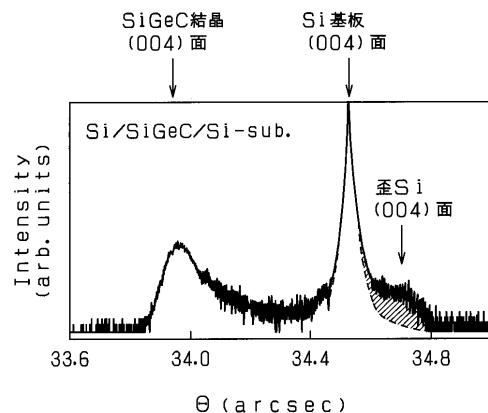

上述の方法で、図2Cのような、SiC結晶を含有する低C濃度SiGeC層を堆積したSi基板を作製する。この基板を、上記のSiGeC結晶8を堆積したときと同じ方法によって洗浄し、UHV-CVD装置内に導入後、清浄表面を露出させる。そして、基板の温度を550に設定し、Si<sub>2</sub>H<sub>6</sub>ガスを $2.4 \times 10^{-4}$ の圧力で15分間供給し、約30nmのSi結晶4を堆積した。この状態でのX線50

回折スペクトルを測定した結果が図4である。この図では、Si基板と、緩和したSiGeC結晶の回折ピークピークに加えて、34.7°付近に弱いプロードなピークが観測されているのが分かる。このピークは、上記の上記のSi基板より大きな格子定数をもつ、SiC結晶を含有する低C濃度SiGeC層10の上にSi結晶4を堆積したため、Si結晶が引っ張り応力を受けて、歪んだ結果現れたものあると考えられる。ここでもVegard則を用いて解析したところ、Si結晶4の基板面内の格子間隔は、0.5458nm程度であることが分かった。Si基板（バルクSi結晶）の格子間隔が、0.5431nmであるので、約0.5%程度歪んでいることになる。これらの結果により、SiC結晶を含有するSiGeC結晶の上にSi結晶を堆積することで、歪Si結晶も製造することが可能であることが分かった。

#### 【0019】

10

なお、上記の第2の実施例では、薄いSi結晶9を上部に堆積したSiC結晶を含有する低C濃度SiGeC層10の上にSi結晶4を堆積したが、Si結晶4を堆積する前に、SiGe結晶や、SiGeC結晶を堆積しておいてもよい。

#### 【0020】

##### 【発明の効果】

本発明で提案した、SiC結晶を含有する低C濃度SiGeC結晶は、薄い膜厚で、欠陥の緩和バッファ層を製造するのに適した材料であり、これを使って、バルクSi結晶より大きな格子定数をもつ半導体基板の製造が可能となる。

##### 【図面の簡単な説明】

【図1】歪Si結晶を得るための構造を説明するための図

20

【図2】歪Si結晶の製造方法を説明するための工程図

【図3】本発明の実施例で作製したSiGeC結晶と、この結晶に熱処理を加えた場合のX線回折スペクトルを比較した図

【図4】本発明で提案する緩和バッファ層上に歪Siを作製した場合のX線回折スペクトルを示す図

##### 【符号の説明】

1 Si結晶基板

2 転移

3 緩和SiGe結晶

4 歪Si結晶

5 貫通転移

6 SiC微結晶

7 低C濃度SiGeC結晶

8 SiGeC結晶

9 Si結晶

10 SiC微結晶を含有する低C濃度SiGeC結晶層

30

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 斎藤 徹

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 久保 実

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 大塚 徹

(56)参考文献 特開平11-233440 (JP, A)

特開平7-22330 (JP, A)

特開平6-224127 (JP, A)

WARREN P, MI J, OVERNEY F, DUTOIT M (Swiss Federal Inst. Technol., Lausanne, CHE), The thermal stability of Si/Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub>/Si heterostructures grown by rapid thermal chemical vapor deposition., J Cryst Growth, NE, 1995年12月, Vol.157 No.1/4, Page.414-419

LIU C W, ST AMOUR A, STURM J C (Princeton Univ., New Jersey), LACROIX Y R J, THEWALT M L W (Simon Fraser Univ., British Columbia, CAN), MAGEE C W (Evans East, New Jersey), Growth and photoluminescence of high quality SiGeC random alloys on silicon substrates ., J Appl Phys, 米国, 1996年 9月 1日, Vol.80 No.5, Page.3043-3047

S.Bodnar and J.L.Regolini, Growth of ternary alloy Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> by rapid thermal chemical vapor deposition, J. Vac. Sci. Technol. A, 米国, 1995年 9月, Vol.13, No.5, Page.2336-2340

(58)調査した分野(Int.Cl., DB名)

H01L 21/205

JSTPlus(JDreamII)