(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6966457号

(P6966457)

(45) 発行日 令和3年11月17日(2021.11.17)

(24) 登録日 令和3年10月25日(2021.10.25)

(51) Int.Cl.

F 1

|                       |               |

|-----------------------|---------------|

| GO2F 1/1368 (2006.01) | GO2F 1/1368   |

| HO1L 21/318 (2006.01) | HO1L 21/318 B |

| HO1L 21/316 (2006.01) | HO1L 21/316 C |

| HO1L 21/336 (2006.01) | HO1L 21/318 M |

| HO1L 29/786 (2006.01) | HO1L 21/316 X |

請求項の数 19 (全 18 頁) 最終頁に続く

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2018-541182 (P2018-541182)  |

| (86) (22) 出願日      | 平成29年1月18日 (2017.1.18)        |

| (65) 公表番号          | 特表2019-507903 (P2019-507903A) |

| (43) 公表日           | 平成31年3月22日 (2019.3.22)        |

| (86) 國際出願番号        | PCT/US2017/013953             |

| (87) 國際公開番号        | W02017/136141                 |

| (87) 國際公開日         | 平成29年8月10日 (2017.8.10)        |

| 審査請求日              | 令和2年1月20日 (2020.1.20)         |

| (31) 優先権主張番号       | 62/292,017                    |

| (32) 優先日           | 平成28年2月5日 (2016.2.5)          |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

|           |                                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390040660<br>アプライド マテリアルズ インコーポレ<br>イテッド<br>A P P L I E D M A T E R I A L S, I<br>N C O R P O R A T E D<br>アメリカ合衆国 カリフォルニア 950<br>54, サンタ クララ, パウアーズ<br>アヴェニュー 3050 |

| (74) 代理人  | 110002077<br>園田・小林特許業務法人                                                                                                                                            |

| (72) 発明者  | チャン, シュエナ<br>アメリカ合衆国 カリフォルニア 951<br>24, サン ノゼ, ロス ガトス ア<br>ルマデン ロード 1791                                                                                            |

最終頁に続く

(54) 【発明の名称】 液晶ディスプレイ用大容量コンデンサのための界面技術

## (57) 【特許請求の範囲】

## 【請求項 1】

薄膜トランジスタ構造体であって、

薄膜トランジスタ装置内に形成されたコンデンサを備え、前記コンデンサは、

基板の上方に配置された共通電極と、

前記共通電極上に形成された誘電体層であって、頂部界面保護層と底部界面保護層の間にはさまれたバルク誘電体材料を含む誘電体層と、

前記頂部界面保護層の上表面上に、該上表面に接触して形成されたピクセル電極とをさらに備え、

前記底部界面保護層が前記共通電極と接触して形成される、薄膜トランジスタ構造体。

10

## 【請求項 2】

前記誘電体層が、8よりも高い誘電率を有する高誘電体材料である、請求項1に記載の構造体。

## 【請求項 3】

前記頂部界面保護層は、ケイ素含有材料である、請求項1または2に記載の構造体。

## 【請求項 4】

前記誘電体層が窒化ケイ素層であり、前記頂部界面保護層は酸窒化ケイ素層である、請求項1または2に記載の構造体。

## 【請求項 5】

前記頂部界面保護層は、酸化ケイ素または酸窒化ケイ素層である、請求項2に記載の構

20

造体。

【請求項 6】

前記共通電極は、酸化インジウムスズ (ITO)、酸化インジウム亜鉛 (IZO)、酸化インジウムスズ亜鉛 (ITZO)、アルミニウム (Al)、タングステン (W)、クロム (Cr)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、マグネシウム (Mg)、銀 (Ag)、金 (Au)、またはこれらの合金からなる群から選択された材料から製造される、請求項 1 から 5 のいずれか一項に記載の構造体。

【請求項 7】

前記ピクセル電極は、酸化インジウムスズ (ITO)、酸化インジウム亜鉛 (IZO)、酸化インジウムスズ亜鉛 (ITZO)、アルミニウム (Al)、タングステン (W)、クロム (Cr)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、マグネシウム (Mg)、銀 (Ag)、金 (Au)、銀ナノインク、カーボンナノチューブ (CNT)、グラフェン、またはこれらの合金からなる群から選択された材料から製造される、請求項 1 から 6 のいずれか一項に記載の構造体。

10

【請求項 8】

前記共通電極または前記ピクセル電極は、グリッド電極である、請求項 1 から 7 のいずれか一項に記載の構造体。

【請求項 9】

前記ピクセル電極が、第 1 の電極及び前記第 1 の電極上に配置された第 2 の電極を含む、請求項 1 から 7 のいずれか一項に記載の構造体。

20

【請求項 10】

第 2 の電極はグリッド電極である、請求項 9 に記載の構造体。

【請求項 11】

薄膜トランジスタ向け用途の基板上にコンデンサ構造体を形成する方法であって、基板の上方に配置された共通電極を形成することと、

頂部界面保護層と底部界面保護層の間にはさまれたバルク誘電体材料を含む誘電体層を、前記共通電極上に形成することと、

前記頂部界面保護層の上表面上に、該上表面に接触してピクセル電極を形成することとを含み、

前記底部界面保護層が前記共通電極と接触して形成される、方法。

30

【請求項 12】

前記頂部界面保護層は、酸窒化ケイ素層または酸化ケイ素層である、請求項 11 に記載の方法。

【請求項 13】

前記ピクセル電極がグリッド電極である、請求項 11 または 12 に記載の方法。

【請求項 14】

前記共通電極は、酸化インジウムスズ (ITO)、酸化インジウム亜鉛 (IZO)、酸化インジウムスズ亜鉛 (ITZO)、アルミニウム (Al)、タングステン (W)、クロム (Cr)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、マグネシウム (Mg)、銀 (Ag)、金 (Au)、またはこれらの合金からなる群から選択された材料から製造される、請求項 1 から 13 のいずれか一項に記載の方法。

40

【請求項 15】

前記ピクセル電極は、酸化インジウムスズ (ITO)、酸化インジウム亜鉛 (IZO)、酸化インジウムスズ亜鉛 (ITZO)、アルミニウム (Al)、タングステン (W)、クロム (Cr)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、マグネシウム (Mg)、銀 (Ag)、金 (Au)、銀ナノインク、カーボンナノチューブ (CNT)、グラフェン、またはこれらの合金からなる群から選択された材料から製造される、請求項 1 から 14 のいずれか一項に記載の方法。

【請求項 16】

前記ピクセル電極が第 1 の電極及び前記第 1 の電極上に配置された第 2 の電極を含む、

50

請求項 1 1 または 1 2 に記載の方法。

【請求項 1 7】

前記第 2 の電極がグリッド電極である、請求項 1 6 に記載の方法。

【請求項 1 8】

薄膜トランジスタ向け用途の基板上に絶縁層を形成する方法であって、

基板の上方に配置された共通電極を形成することと、

原子層堆積処理または、原子層堆積と化学気相成長とを含むハイブリッド処理によって

、前記共通電極上に高誘電率層を形成することであって、前記高誘電率層は、頂部界面保

護層と底部界面保護層の間にはさまれたバルク誘電体材料を含み、前記高誘電率層は、薄

膜トランジスタ装置内の、ゲート絶縁層、パッシベーション層、コンデンサ、層間絶縁膜

、またはエッチング停止層のうちの 1 つである、高誘電率層を形成することと、

10

前記高誘電率層上にピクセル電極を形成することとを含み、

前記ピクセル電極は、前記頂部界面保護層の上表面上に、該上表面上に接触して形成され

、前記底部界面保護層は前記共通電極と接触して形成される、方法。

【請求項 1 9】

前記薄膜トランジスタ装置が低温ポリシリコン ( L T P S ) T F T 装置である、請求項

1 8 に記載の方法。

【発明の詳細な説明】

【技術分野】

【 0 0 0 1 】

20

本開示の実施形態は、概して、大容量低漏れ性のピクセルコンデンサ構造体を形成する

ことに関する。具体的には、本開示の実施形態は、液晶ディスプレイ ( L C D ) 用途向け

の大容量低漏れ性のピクセルコンデンサ構造体を形成する方法に関する。

【背景技術】

【 0 0 0 2 】

ディスプレイ装置は、テレビ、モニタ、携帯電話、M P 3 プレーヤー、電子書籍リーダー、及び携帯情報端末 ( P D A ) などといった、広い範囲の電子関連用途で使用されてきた。ディスプレイ装置は、概して、2 つの基板間 ( 例えばピクセル電極と共通電極との間 ) の空隙を充填し、誘電場の強度を制御する異方性誘電率を有している液晶に対して電荷

を印加することによって、所望の画像を生成するように設計されている。基板を通して伝

達される光量を調整することによって、光と画像の強度、画質、及び電力消費が有効に制

御され得る。

30

【 0 0 0 3 】

タッチスクリーンパネルを利用するディスプレイ装置用の光源として、アクティブマトリクス液晶ディスプレイ ( A M L C D ) やアクティブマトリクス有機発光ダイオード ( A M O L E D ) といった、様々な種々のディスプレイ装置が採用され得る。T F T 装置の製

造に際しては、高電子移動度、低漏れ電流、及び高破壊電圧の電子装置によって、光の透

過と回路の集積のためにより多くのピクセル領域をとることが可能になり、それによ

って、ディスプレイがより明るくなり、全体的な電気効率が上昇し、応答時間がより速くなり

、ディスプレイの解像度が向上する結果となった。一部の装置では、T F T 装置の稼働中

にときに電荷を貯蔵し得るコンデンサを形成するため、ピクセル電極と共通電極の間に誘

電体層が配置されている。形成されたコンデンサには、T F T 装置に所望の電気性能を与

えるため、大容量と低漏れ性を有することが求められる。容量は、ピクセル電極と共通電

極の間に形成された誘電体層の誘電率、及び / または誘電体層の厚さを変化させることに

よって、調整され得る。例えば、誘電体層をより高い誘電率を持つ材料と交換すると、コン

デンサの容量もまた増大する。しかし、誘電体層の材料の選択がコンデンサの容量に影

響するだけではなく、誘電体層の材料の電極 ( ピクセル電極または共通電極のどちらか )

との不適合によっても、膜構造の剥離や、界面接着の不良、界面材料の拡散という結果に

なり得る。

40

【 0 0 0 4 】

50

したがって、改良された装置の電気性能を生み出すTFT装置を製造するための、大容量且つ低漏れ性で、界面制御が良好なコンデンサを形成する方法を、改良する必要性が存在する。

#### 【発明の概要】

##### 【0005】

本開示の実施形態によって、概して、大容量且つ低漏れ性で、界面制御が良好な薄膜トランジスタ(TFT)向け用途のコンデンサの形成方法が提供される。一実施形態では、薄膜トランジスタ構造体は、薄膜トランジスタ装置内に形成されたコンデンサを含む。コンデンサはさらに、基板上に配置された共通電極と、共通電極上に形成された誘電体層と、誘電体層上に形成されたピクセル電極とを含む。界面保護層は、共通電極と誘電体層との間、または誘電体層とピクセル電極との間に形成される。

10

##### 【0006】

別の実施形態では、薄膜トランジスタ向け用途の基板上にコンデンサ構造体を形成する方法は、使用する基板上に共通電極を形成して薄膜トランジスタ装置を形成することと、共通電極上に誘電体層を形成することと、誘電体層上にピクセル電極を形成することとを含む。共通電極と誘電体層の間、または誘電体層とピクセル電極の間に、界面保護層が形成される。

##### 【0007】

さらに別の実施形態では、薄膜トランジスタ向け用途の基板上に絶縁層を形成する方法は、原子層堆積処理または、原子層堆積と化学気相成長とを含むハイブリッド処理によって基板上に高誘電率層を形成することを含み、高誘電率層は、薄膜トランジスタ装置内の、ゲート絶縁層、パッシベーション層、コンデンサ、層間絶縁膜、エッチング停止層である。

20

##### 【0008】

本開示の上記の特徴が得られる方法が詳細に理解できるように、上で簡潔に要約した本開示のより具体的な説明が、添付の図面に示されている本開示の実施形態を参照することによって得られてよい。

##### 【図面の簡単な説明】

##### 【0009】

【図1】本開示の一実施形態による誘電体層の堆積に用いられ得る、処理チャンバの断面図である。

30

【図2】本開示の一実施形態による材料層の堆積に用いられ得る、処理チャンバの断面図である。

【図3】TFT装置構造体の一部を形成する方法の一実施形態のプロセスフロー図である。

【図4】薄膜トランジスタ装置構造体の一実施例の断面図である。

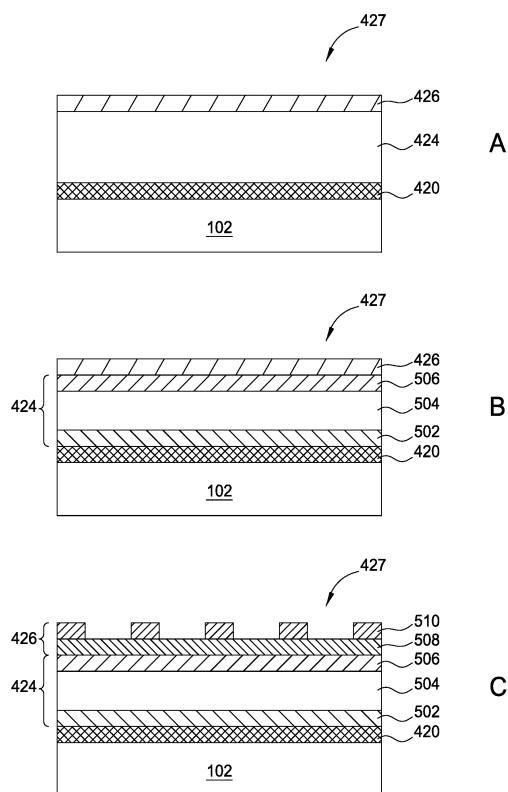

【図5】図5A～図5Cは、図4の薄膜トランジスタ内で使用され得る、膜構造の種々の例を示す。

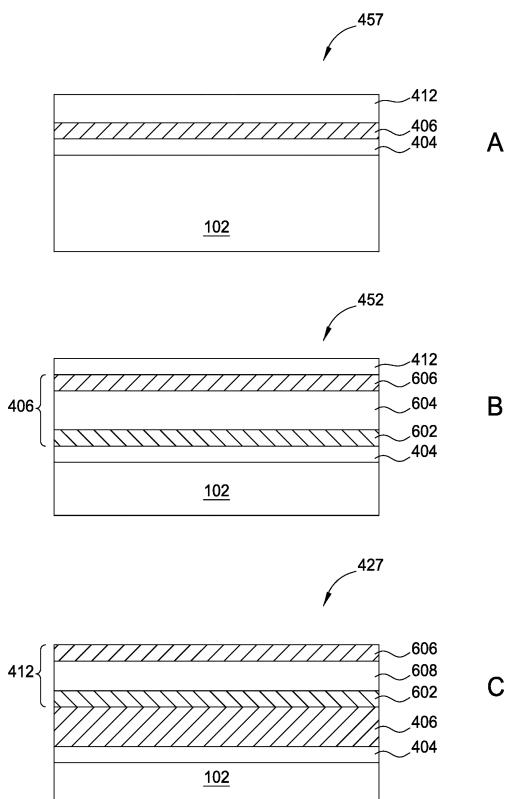

【図6】図6A～図6Cは、図4の薄膜トランジスタ内で使用され得る、膜構造の種々の例を示す。

40

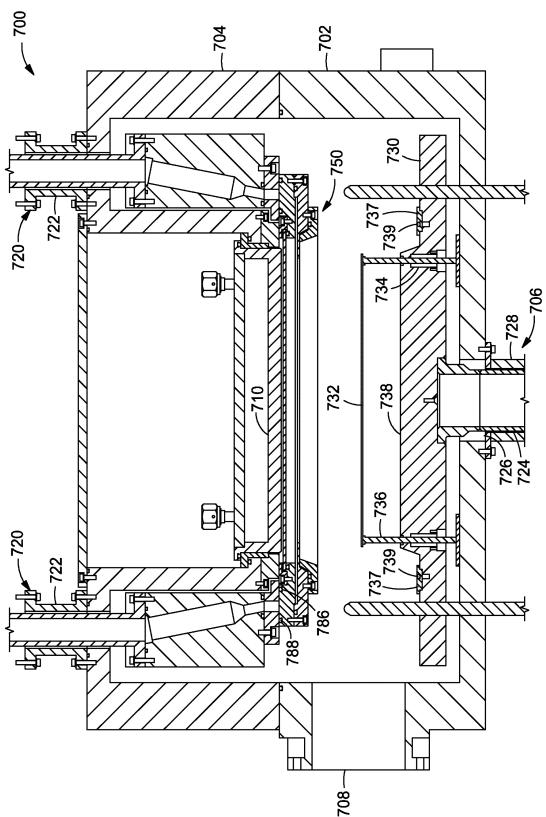

【図7】本開示の一実施形態による高誘電率材料の堆積に用いられ得る、処理チャンバの断面図である。

##### 【発明を実施するための形態】

##### 【0010】

理解しやすくするため、各図面に共通する同一の要素を指定する際に、可能であれば、同一の参照番号が使用されている。一実施形態のエレメント及び特徴は、さらなる記述がなくても、他の実施形態に有益に組み込まれ得ると考えられる。

##### 【0011】

しかし、本開示は他の等しく有効な実施形態も許容し得ることから、添付の図面は本開示の典型的な実施形態のみを例示しているのであって、本開示の範囲を限定するものと見

50

なすべきではないことに留意されたい。

【0012】

本開示の実施形態によって、概して、ディスプレイ装置用の、大容量且つ低漏れ性、または高誘電率の絶縁層といった、電気性能が強化されたコンデンサの形成方法が提供される。一実施例では、ディスプレイ装置内に形成されたコンデンサは、ピクセル電極と共に電極の間に形成された誘電体層を含んでいてよい。誘電体層は、8を超える誘電率を有する、高誘電率の誘電体材料であってよい。別の構成では、ピクセル電極と誘電体層との間に、及び／または共通電極と誘電体層との間に、界面保護層が形成されていてよい。こうしたコンデンサ構造体は、良好な界面接着制御によって、トランジスタ及びダイオード装置の電気性能を有効に強化し得る。別の実施例では、ゲート絶縁層、エッキング停止層、または界面保護層といった誘電率が高い任意の絶縁層もまた、電気性能の強化と向上のために高誘電率材料を使用し得る。 10

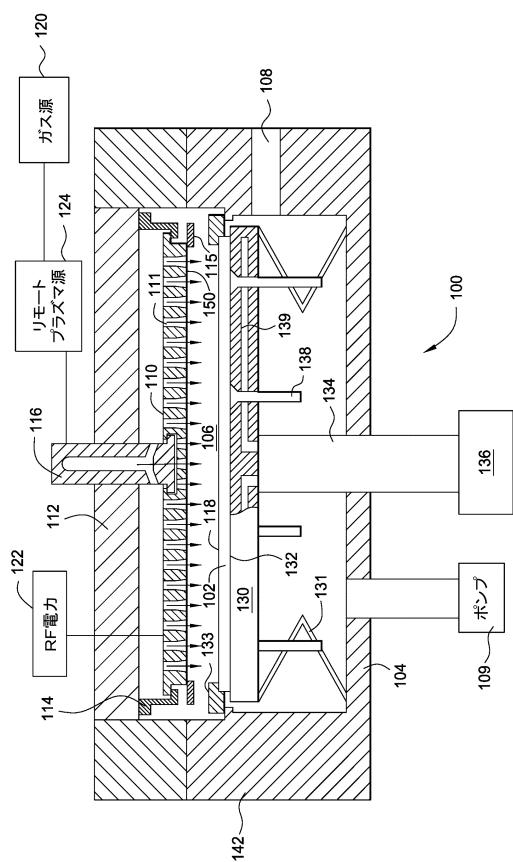

【0013】

図1は、プラズマ化学気相堆積（P E C V D）チャンバ（処理チャンバ）100の一実施形態の概略的断面図である。プラズマ化学気相堆積（P E C V D）チャンバ（処理チャンバ）100内では、絶縁層、ゲート絶縁層、エッキング停止層、パッシベーション層、層間絶縁膜、コンデンサ用誘電体層、またはTFT装置構造体内のパッシベーション層といった、誘電体層が堆積され得る。適切なプラズマ化学気相堆積チャンバの1つは、カリフォルニア州サンタクララにあるApplied Materials, Inc. から入手可能である。本開示を実施するために、他の製造業者から入手可能なものを含む他の堆積チャンバが使用され得ると考えられている。 20

【0014】

チャンバ100は、概して処理空間106を画定する壁142、底部104、及びリッド112を含む。処理空間106内には、ガス分配プレート110と基板支持体アセンブリ130が配置されていてよい。処理空間106は、壁142を貫通して形成されたバルブ108を通じてアクセスされ、それによって基板102がチャンバ100の内外へ移送され得る。

【0015】

基板支持体アセンブリ130は、その上で基板102を支持するための、基板受容面132を含む。基板支持体アセンブリ130は、ステム134によってリフトシステム136に連結されており、リフトシステム136は、基板移送位置と処理位置との間で基板支持体アセンブリ130を上昇及び下降させる。処理時にはオプションで、基板102のエッジにおける堆積を防止するために、基板102の外周上に、シャドウフレーム133が配置されてよい。リフトピン138が、基板支持体アセンブリ130を貫通して動作可能に配置されており、基板を基板受容面132から引き離すのに適合している。基板支持体アセンブリ130はまた、基板支持体アセンブリ130を所望の温度に維持するために使用される、加熱要素及び／または冷却要素139も含んでいてよい。基板支持体アセンブリ130は、基板支持体アセンブリ130の外周にRFリターンパスを設けるための接地ストラップ131もまた含んでいてよい。 30

【0016】

ガス分配プレート110は、その外周で、懸架装置114によってチャンバ100のリッド112または壁142に連結されている。ガス分配プレート110はまた、ガス分配プレート110の弛みの防止及び／または、真直度／湾曲度の制御を補助するために、1つ以上の中央支持体116によってリッド112に連結されていてもよい。ガス分配プレート110は、異なる寸法の異なる構成を有していてよい。例示の一実施形態においては、ガス分配プレート110は長方形の平面形状を有する。ガス分配プレート110は、内部に形成された複数の開口111を有する下流面150を有する。下流面150は、基板支持体アセンブリ130上に置かれた基板102の上面118に面している。開口111は、ガス分配プレート110全体にわたって、種々の形状、数、密度、寸法、及び分布を有していてよい。一実施形態では、開孔111の直径は、約0.01インチと約1インチ 40

の間から選択されてよい。

【0017】

リッド112を通り、次にガス分配プレート110内に形成された開口111を通って処理空間106にガスを供給するために、ガス源120がリッド112に連結されている。処理空間106内のガスを所望の圧力に維持するために、処理チャンバ100に、真空ポンプ109が連結されてよい。

【0018】

ガス分配プレート110と基板支持体アセンブリ130との間に電場を発生させるRF電力を供給し、それによってガス分配プレート110と基板支持体アセンブリ130との間に存在するガスからプラズマが生成され得るように、リッド112及び/またはガス分配プレート110に、RF電源122が連結されている。RF電力は、様々なRF周波数で印加されてよい。例えば、RF電力は約0.3MHzと約200MHzの間の周波数で印加されてよい。一実施形態では、RF電力は、13.56MHzの周波数で供給される。

【0019】

一実施形態では、ガス分配プレート110の下流面150のエッジは湾曲していてよく、それによって、ガス分配プレート110のエッジ及びコーナーと基板受容面132との間に、その結果、ガス分配プレート110と基板102の上面118との間に、間隔の傾斜(spacing gradient)が規定されている。下流面150の形状は、特定の処理要件を満たすようにして選択されてよい。例えば、下流面150の形状は、凸形、平面、凹形、または他の適切な形状であってよい。したがって、基板のエッジ全体にわたる膜特性の均一性を微調整し、それによって基板のコーナーに堆積した膜の特性の不均一性を是正するために、エッジからコーナーへの間隔の傾斜が利用されてよい。加えて、基板のエッジと中央との間で膜特性の分布の均一性が制御され得るように、エッジから中央部にかけての間隔もまた制御されてよい。一実施形態では、ガス分配プレート110のエッジの中央部では、ガス分配プレート110のコーナーと比べて、基板102の上面118との間隔がより遠くなるように、ガス分配プレート110の凹形に湾曲したエッジが使用されてよい。別の実施形態では、ガス分配プレート110のコーナーでは、ガス分配プレート110のエッジの中央部と比べて、基板102の上面118との間隔がより遠くなるように、ガス分配プレート110の凸形に湾曲したエッジが使用されてよい。

【0020】

ガス源とガス分配プレート110との間に、誘導結合された遠隔プラズマ源といった遠隔プラズマ源124もまた連結されていてよい。チャンバ構成要素を洗浄するのに使用されるプラズマを遠隔供給するため、基板処理と基板処理との間に、遠隔プラズマ源124内で洗浄ガスが励起されてよい。処理空間106に入る洗浄ガスは、電源122がガス分配プレート110に供給するRF電力によって、さらに励起され得る。限定しないが、適切な洗浄ガスは、NF<sub>3</sub>、F<sub>2</sub>、及びSF<sub>6</sub>を含む。

【0021】

一実施形態では、チャンバ100内で処理され得る基板102は、25,000cm<sup>2</sup>以上といった10,000cm<sup>2</sup>以上の表面積、例えば、例えば55,000cm<sup>2</sup>以上の表面積を有していてよい。基板が、処理後にカットされてより小さい他のデバイスを形成し得ることは、理解される。

【0022】

一実施形態では、堆積中の基板支持体アセンブリの温度を約600°C以下、例えば約100°Cと約500°Cの間、または約200°Cと約500°Cの間、例えば約300°Cと500°Cの間にするために、加熱要素及び/または冷却要素139がセットされてよい。

【0023】

堆積中に基板需要面132上に置かれている基板102の上面118とガス分配プレート110との間の名目的な間隔は、400ミルと約1,200ミルの間、例えば400ミ

10

20

30

40

50

ルと約 800 ミルの間、または所望の堆積結果を得るために必要なその他の距離で、概して変化していくよい。ガス分配プレート 110 が凹形の下流面を有している例示の一実施形態では、ガス分配プレート 110 のエッジの中央部と基板受容面 132 との間の間隔は、約 400 ミルと約 1400 ミルの間であり、ガス分配プレート 110 のコーナーと基板需要面 132 との間の間隔は、約 300 ミルと約 1200 ミルの間である。

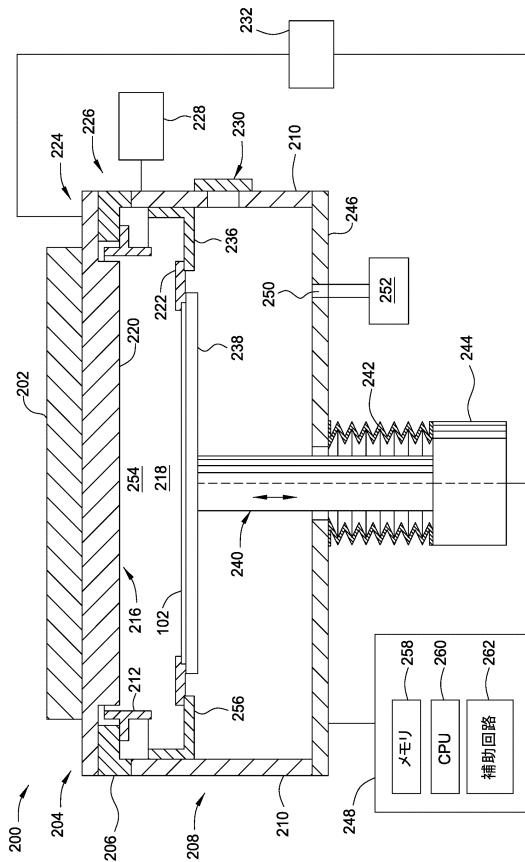

#### 【0024】

図 2 は、本発明の一実施形態による、界面保護層及び／または、ピクセル電極もしくは共通電極といった金属電極の形成に適切な、例示の反応性スパッタ処理チャンバ 200 である。処理チャンバ 200 は、複数の処理チャンバ 200 を有する真空処理システムの一部であってよい。本発明から受益するのに適合していくよい処理チャンバの一例は、カリフォルニア州サンタクララの Applied Materials, Inc. から入手可能な物理的気相堆積 (PVD) 処理チャンバである。他の製造業者から入手可能なものを含む他のスパッタ処理チャンバが、本発明を実施するために適合され得ることに留意されたい。

10

#### 【0025】

処理チャンバ 200 は、内部に画定され、リッドアセンブリ 204 によって取り囲まれた処理空間 218 を有する、チャンバ本体 208 を含む。チャンバ本体 208 は、側壁 210 及び底部 246 を有する。チャンバ本体 208 の寸法及び処理チャンバ 200 の関連部品の寸法は限定されておらず、一般的に、図 1 の基板 102 といった、中で処理する基板のサイズよりも相対的に大きい。その結果、適切にサイズ決めされた処理チャンバ内で、あらゆる適切な基板サイズが処理され得る。適切な基板サイズの例は、約 2000 cm<sup>2</sup> 以上の平面表面積を有する基板を含む。

20

#### 【0026】

チャンバ本体 208 は、アルミニウムまたは他の適切な材料から製造されていてよい。チャンバ本体 208 の側壁 210 を貫通して、基板アクセスポート 230 が形成されており、処理チャンバ 200 内外への基板 102 (即ち、ソーラーパネルもしくはフラットパネルディスプレイの基板、プラスチック基板もしくはフレキシブル基板、半導体ウエハ、または他のワークピース) の移送を容易にしている。アクセスポート 230 は、移送チャンバ及び／または基板処理システムの他のチャンバに連結されていてよい。

30

#### 【0027】

処理空間 218 内に処理ガスを供給するため、チャンバ本体 208 にガス源 228 が連結されている。ガス源 228 によって供給されてよい処理ガスの例は、不活性ガス、非反応性ガス、及び反応性ガスを含む。一実施例では、ガス源 228 によって供給される処理ガスは、限定しないが、アルゴンガス (Ar)、ヘリウム (He)、窒素ガス (N<sub>2</sub>)、酸素ガス (O<sub>2</sub>)、及び H<sub>2</sub>O を含み得る。

#### 【0028】

ポンピングポート 250 は、チャンバ本体 208 の底部 246 を通って形成される。処理空間 218 には、内部を排気し圧力を制御するため、ポンピング装置 252 が連結されている。一実施形態では、処理チャンバ 200 の圧力レベルは、約 1 Torr 以下に維持されていてよい。

40

#### 【0029】

リッドアセンブリ 204 は、概して、ターゲット 220 と、ターゲット 220 に連結されているかまたはターゲット 220 の付近に置かれている、接地シールドアセンブリ 226 とを含む。ターゲット 220 は、PVD 処理中に基板 102 の表面にスパッタ及び堆積させることができる材料源を提供する。ターゲット 200 またはターゲットプレートは、堆積種として利用される材料から製造されていてよい。ターゲット 220 からの材料のスパッタリングを促進するため、ターゲット 220 に、電源 232 といった高電圧電源が結合されている。一実施形態では、ターゲット 220 は、チタン (Ti)、タンタル (Ta)、マグネシウム (Mg)、銀 (Ag)、インジウム (In)、スズ (Sn)、酸化インジウムスズ (ITO)、酸化インジウムスズ (ITO)、酸化インジウム亜鉛 (IZO)

50

、酸化インジウムスズ亜鉛（ITO）、アルミニウム（Al）、タンゲステン（W）、金（Au）、モリブデン（Mo）、水銀（Hg）、クロム（Cr）、金属、合金、または他の好適な材料といった、金属含有材料から製造されていてよい。別の実施形態では、ターゲット220は、インジウムスズ合金などを含む材料から製造されていてよい。

#### 【0030】

ターゲット220は、概して、周辺部分224及び中央部分216を含む。周辺部分224は、チャンバ200の側壁210上に配置されている。ターゲット220の中央部分216は、基板支持体238の上に配置された基板102の表面に向かってわずかに延びる湾曲面を有し得る。ターゲット220と基板支持体238との間の間隔は、約50mmから約150mmの間で維持される。ターゲット220の寸法、形状、材料、構成及び直径が、特定の処理要件または基板要件によって変化し得ることは、留意されたい。一実施形態では、ターゲット220は、基板表面にスパッタされることが望ましい材料によって接着及び/または製造された中央部分を有する、バッキング板をさらに含んでいてよい。ターゲット220が、複数のタイルまたはセグメント材料を有していて、これらが一緒になってターゲットを形成していてよい。

10

#### 【0031】

リッドアセンブリ204は、処理中にターゲット220からの材料の効率的なスパッタリングを強化する、ターゲット220の上に装着されたマグネットロンアセンブリ202をさらに備えていてよい。マグネットロンアセンブリの例は、特に、線形マグネットロン、蛇行マグネットロン、螺旋マグネットロン、二指状（double-digitated）マグネットロン、長方形螺旋マグネットロンを含む。

20

#### 【0032】

リッドアセンブリ204の接地シールドアセンブリ226は、接地フレーム206及び接地シールド212を含む。接地シールドアセンブリ226はまた、他のチャンバシールド部材、ターゲットシールド部材、暗部シールド及び暗部シールドフレームも含み得る。接地シールド212は、接地フレーム206によって周辺部分224に連結されており、処理空間218内で、ターゲット220の中央部分216の下に上部処理領域254を画定している。接地フレーム206は、接地シールド212をターゲット220から電気的に絶縁しており、その一方で側壁210を通して処理チャンバ200のチャンバ本体208への接地経路を提供している。接地シールド212は、処理中に生成されるプラズマを上部処理領域254内部に拘束する。それによって、ターゲット220の中央部216から遊離されたターゲット源材料は、チャンバ側壁210ではなく主に基板表面に堆積する。一実施形態では、接地シールド212は、1つ以上の構成要素で形成されていてよい。

30

#### 【0033】

チャンバ本体208の底部246を通って延びるシャフト240が、基板支持体238をリフト機構244に連結している。リフト機構244は、下部の移送位置と上部の処理位置との間で基板支持体238を移動させるように構成されている。シャフト240をベローズ242が取り囲んでおり、ベローズ242は、基板支持体238に連結されてその間に弾力的なシールを提供している。それによって、チャンバ処理空間218の真空完全性が維持される。

40

#### 【0034】

基板支持体238の外周領域にはシャドウフレーム222が配置されており、ターゲット220からスパッタされた原材料の堆積を、基板表面の所望の位置に限定するように構成されている。基板支持体238が下降位置にあるときには、シャドウフレーム222は、チャンバ本体208の側壁210から延びているチャンバシールド236のリップ256から、基板支持体238の上方へと懸架されている。基板支持体238が処理のために上部位置まで上昇すると、基板支持体238上に置かれた基板102の外側エッジがシャドウフレーム222に接触する。それによってシャドウフレーム222が持ち上げられ、チャンバシールド236から離間する。下降位置への移動時または移動中に、基板102を基板支持体238の上方に持ち上げて、移送ロボットまたは他の適切な移送機構が基板

50

102にアクセスしやすくするために、リフトピン（図示せず）が、基板支持体238を貫通して選択的に動かされる。

【0035】

処理チャンバ200及び、オプションで処理チャンバ100に、コントローラ248が連結されている。コントローラ248は、中央処理装置（CPU）260、メモリ258、及び補助回路262を含む。コントローラ248は、ガス源228からチャンバ200内へのガス流の規制、及びターゲット220のイオン衝撃の制御を行って、処理シーケンスを制御するために用いられる。CPU260は、工業環境で使用することができる汎用コンピュータプロセッサの任意の形態であり得る。ソフトウェアルーチンは、ランダムアクセスメモリ、読み出し専用メモリ、フロッピーもしくはハードディスクドライブ、または他の形式のデジタルストレージといった、メモリ258に保存することができる。補助回路262は、従来方式でCPU260に接続されており、キャッシュ、クロック回路、出入力サブシステム、電源などを含んでいてよい。ソフトウェアルーチンがCPU260によって実行されると、CPUは処理チャンバ200を制御する特定目的のコンピュータ（コントローラ）248に変わり、本発明に従って処理が実行される。ソフトウェアルーチンはまた、チャンバ200から離れて位置している第2のコントローラ（図示せず）によって保存及び／または実行されてもよい。

【0036】

処理中、ターゲット220及び基板支持体238は、ガス源228によって供給された処理ガスから形成されたプラズマを維持するため、電源232によって互いに対してもバイアスされている。プラズマからのイオンは、ターゲット220に向かって加速されてターゲット220に衝突し、ターゲット材料がターゲット220から遊離されるようにする。遊離されたターゲット材料は、基板102上に層を形成する。チャンバ200内に特定の処理ガスが供給される実施形態では、チャンバ200内に存在する遊離されたターゲット材料と処理ガスが反応して、基板102上に複合膜が形成される。

【0037】

まず図7を参照すると、図7は、本明細書に記載されている堆積を実施するのに使用されてよい、ALD（原子層堆積）チャンバ700の概略断面図である。本明細書に記載の、絶縁層、ゲート絶縁層、エッチング停止層、層間絶縁膜、コンデンサ用誘電体層、またはTFT装置構造体内のパッシベーション層といった誘電体層を形成するために、ALD堆積処理が使用されてよい。チャンバ700は、概して、チャンバ本体702、リッドアセンブリ704、基板支持体アセンブリ706、及び処理キット750を含む。リッドアセンブリ704は、チャンバ本体702上に配置され、基板支持体アセンブリ706は、少なくとも部分的にチャンバ本体702の内部に配置される。チャンバ本体702は、処理チャンバ700の内部へのアクセスを提供するためにチャンバ本体702の側壁に形成された、スリットバルブ開口708を含む。ある実施形態では、チャンバ本体702は、真空システム（例えば真空ポンプ）と流体連通している1つ以上の開口を含む。開口は、チャンバ700内のガスの出口を提供する。真空システムは、プロセスコントローラによって、ALD処理にとって適切なALDチャンバ700内の圧力を維持するように制御される。リッドアセンブリ704は、1つ以上の差動ポンプ及びパージアセンブリ720を含み得る。差動ポンプ及びパージアセンブリ720は、ベローズ722でリッドアセンブリ704に装着されている。ベローズ722によって、ポンプ及びパージアセンブリ720が、ガス漏れに対する密封を維持しながらリッドアセンブリ704に対して垂直に動くことが可能になっている。処理キット750が処理位置へと上げられるとき、処理キット750上の柔軟な（compliant）第1のシール786及び柔軟な第2のシール788が、差動ポンプ及びパージアセンブリ720と接触する。差動ポンプ及びパージアセンブリ720は真空システム（図示せず）に接続されており、低圧に保たれている。

【0038】

図7に示すように、リッドアセンブリ704は、チャンバ700内及び／または処理キット750内に反応種のプラズマを生成することができる、RFカソード710を含んで

10

20

30

40

50

いる。R F カソード 710 は、例えば、電気式加熱要素（図示せず）によって加熱されてよく、例えば冷却流体の循環によって冷却されてよい。ガスを反応性核種に活性化させ、反応性核種のプラズマを維持することができる任意の電源が使用されてもよい。例えば、R F またはマイクロ波（M W）ベースの放電技法が使用されてよい。活性化は、熱に基づく技法、ガス絶縁破壊（gas breakdown）技法、高強度光源（例えば、U V エネルギー）、またはX線源への曝露によっても引き起こされ得る。

#### 【0039】

基板支持体アセンブリ 706 は、チャンバ本体 702 内に少なくとも部分的に配置され得る。基板支持体アセンブリ 706 は、チャンバ本体内での処理のために基板 732 を支持する基板支持部材またはサセプタ 730 を含むことができる。サセプタ 730 は、チャンバ本体 702 の底面に形成されている 1 つ以上の開口部 726 を通って延在する単数または複数のシャフト 724 を通じて、基板リフト機構（図示せず）に連結されていてよい。基板リフト機構は、シャフト 724 周囲からの真空漏れを防止するベローズ 728 によって、チャンバ本体 702 に弾力的にシールされ得る。基板リフト機構は、図示されている下部ロボット進入位置と、処理位置、処理キット移送位置、及び基板移送位置との間で、サセプタ 730 が A L D チャンバ 700 内を垂直に移動することを可能にしている。ある実施形態では、基板リフト機構が移動する位置の数は、記載されているものよりも少ない。

#### 【0040】

ある実施形態では、基板 732 は、真空チャック（図示せず）、静電チャック（図示せず）、または機械式クランプ（図示せず）を用いてサセプタに固定されてよい。A L D 処理の性能を向上させるために基板 732 と処理キット 750 の温度に影響を与えるように、A L D チャンバ 700 内における処理中に、サセプタ 730 の温度が（例えばプロセスコントローラによって）制御されてよい。サセプタ 730 は、例えばサセプタ 730 内の電気式加熱要素（図示せず）によって加熱され得る。サセプタ 730 の温度は、例えばチャンバ 700 内の高温計（図示せず）によって測定され得る。

#### 【0041】

図 7 に示すとおり、サセプタ 730 は、1 つ以上のリフトピン 736 を受容するため、サセプタ 730 を貫通する 1 つ以上のボア 734 を含むことができる。各リフトピン 736 は、ボア 734 内を自由に摺動し得るようにして装着されている。支持体アセンブリは、支持体アセンブリ 706 が下側位置にあるとき、リフトピン 736 の上面がサセプタ 730 の基板支持面 738 よりも上に位置し得るように、動くことができる。反対に、支持体 706 が上昇位置にある時には、リフトピン 736 の上面は、サセプタ 730 の上面 738 よりも下方に位置する。リフトピン 736 は、チャンバ本体 702 に接触するとき、基板 732 の下面に押し付けられ、基板をサセプタ 730 から離して持ち上げる。反対に、サセプタ 730 が基板 732 をリフトピン 736 から離して持ち上げてもよい。

#### 【0042】

ある実施形態では、サセプタ 730 は、1 つ以上の柔軟なシール 739 を含んでいてよい処理キット絶縁ボタン 737 を含んでいる。処理キット絶縁ボタン 737 は、処理キット 750 をサセプタ 730 上で支持するために使われてよい。処理キット絶縁ボタン 737 中の 1 つ以上の柔軟なシール 839 は、サセプタが処理キット 850 を処理位置へと持ち上げるときに、押圧される。

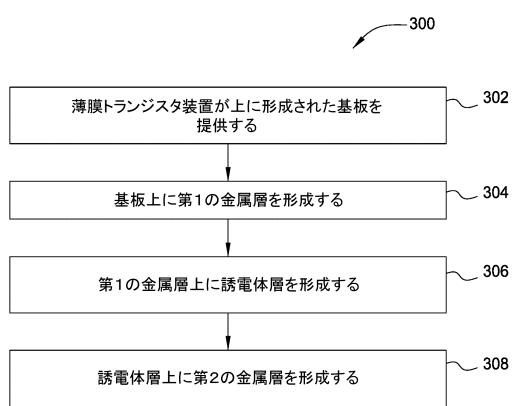

#### 【0043】

図 3 は、薄膜トランジスタ装置内の使用に適切なコンデンサまたは絶縁層を形成するプロセス 300 の、一実施形態のフロー図を示す。薄膜トランジスタ装置内で使用される絶縁層の適切な例は、絶縁材料が必要な、ゲート絶縁層、インターフェース層、コンデンサの形成に使われる誘電体層、エッチング停止層、またはパッシバーション層を含む。一実施例では、コンデンサは、ピクセル電極と共に電極の間に形成された誘電体層または絶縁層を含んでいてよい。誘電体層または絶縁層は、図 1 に記載の処理チャンバ 100 内で実施され得るプラズマ化学気相堆積（P E C V D）処理か、または図 7 に記載の処理チャ

10

20

30

40

50

ンバ 700 内もしくは他の適切な処理チャンバ内で実施され得る原子層堆積 (ALD) 処理によって、形成されてよい。ピクセル電極及び共通電極は、図2に記載の処理チャンバ 200 内で実施され得る物理的気相堆積 (PVD) によって形成されてよい。

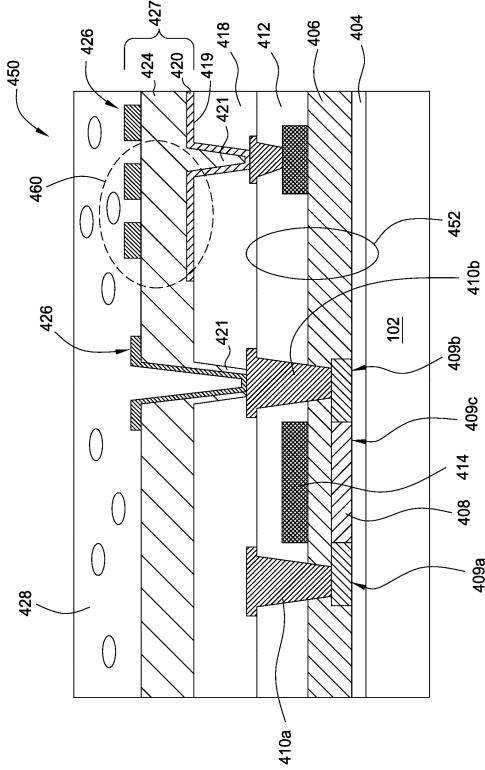

#### 【0044】

プロセス 300 は、図2に記載の処理チャンバ 200 (PVD チャンバ) といった処理チャンバ内に基板 102 を提供することによって、工程 302 で開始される。基板 102 上に共通電極を容易に形成するため、基板 102 は、その上に部分的に形成された TFT 装置を含んでいてよい。図4に示す例では、基板 102 は、上に共通電極 420 が形成される準備ができている、平坦化層 418 の平坦面 419 を含んでいてよい。橜円 460 で示される、誘電体層 424 (または絶縁層と呼ばれる) と共通電極 420、及びピクセル電極 426 は、合わせて、TFT 装置構造体 450 内でコンデンサ 427 を形成し得る。コンデンサ 427 は、図5A～図5C の、プロセス 300 の種々の製造段階におけるコンデンサ 427 の構造のバリエーションに関して、以下で詳細に記載されよう。誘電体層 424 (または絶縁層) の形成に使用される材料はまた、TFT 装置構造体 450 内で絶縁材料を必要とする他の層の形成にも使用されてよい。

#### 【0045】

図4に示す例では、基板 102 上に形成されている TFT 装置 450 は、低温ポリシリコン (LTPS) TFT 装置を含む。基板 102 上に種々の装置構造または種々の膜スタック (積層膜) が形成されるのを容易にするため、基板 102 は、それまでに基板上に形成された膜、構造体、または層の種々の組み合わせを有していてよい。基板 102 は、ガラス基板、プラスチック基板、ポリマー基板、金属基板、单一基板、ロール・トゥ・ロール基板、または、上に薄膜トランジスタを形成するのに適した他の適切な透明基板のうちの任意の 1 つであってよい。

#### 【0046】

低温ポリシリコン TFT 装置 450 は、オプション上で置かれた絶縁層 404 は有りまたは無しで、光学的に透明な基板上に形成されたソース領域 409a、チャネル領域 408、及びドレイン領域 409b を含んでいる、MOS 装置である。ソース領域 409a、チャネル領域 408、及びドレイン領域 409b は、一般的に、初めに堆積されたアモルファスシリコン (a-Si) 層から形成される。このアモルファスシリコン層は、典型的には、後で熱処理またはレーザ処理されて、ポリシリコン層を形成する。ソース領域 409a、ドレイン領域 408a、及びチャネル領域 409b は、光学的に透明な基板 402 上のエリアをパターニングし、初めに堆積された a-Si 層をイオンドープし、次に熱処理またはレーザ処理 (例えばエキシマレーザアニール処理) してポリシリコンを形成することによって形成され得る。次に、堆積したポリシリコン層の上にゲート絶縁層 406 が堆積し、ゲート電極 414 をチャネル領域 408、ソース領域 409、及びドレイン領域 409b から絶縁する。ゲート電極 414 は、ゲート絶縁層 406 の最上部に形成される。ゲート絶縁層 406 はまた、ゲート酸化物層としても一般に知られている。次に、絶縁層を通して層間絶縁膜 412 が作られ装置の接続が行われ、TFT 装置の制御が可能になる。

#### 【0047】

層間絶縁膜 412 が形成された後、ソース・ドレイン金属電極層 410a、410b が、ソース領域 409 及びドレイン領域 409b に電気的に接続された層間絶縁膜 412 内に堆積され、形成され、パターニングされる。ソース・ドレイン金属電極層 410a、410b がパターニングされた後、次は、ソース・ドレイン金属電極層 410a、410b 上に平坦化層 418 が形成され、平坦面 419 が設けられる。平坦面 419 上には、後に共通電極 420 が形成され、パターニングされてよい。平坦化層 418 は、ポリイミド、ベンゾシクロブテン系樹脂、スピノングラス (SOG)、またはアクリレートから製造されてよい。平坦化層 418 は後にパターニングされ、ビアコンタクトホール 421 が形成される。それによって、共通電極 420 (例えば、プロセス 300 の最初の、金属材料を提供するステップ) と、誘電体層 424 及び / またはピクセル電極 426 をビアコンタ

10

20

30

40

50

クトホール内に順次、充填することが可能になる。図4に示す構造体が、単にTFT装置450の例示的な実施形態にすぎないことは、留意されたい。ビアコンタクトホール421は、必要に応じた任意の構成で、共通電極420、誘電体層424、またはピクセル電極426によって部分的にまたは完全に充填されてよい。図4に記載された例が示すように、ピクセル電極426及び共通電極420、並びにこれらの間に形成された誘電体層424は、組み合わせて、TFT装置450内のコンデンサ427（例えば、MIM（金属-絶縁-金属）構造）を形成する。ピクセル電極426が形成された後、コンデンサ427の構造体上に有機層または液晶層といった他の絶縁層428が形成され、装置450の構造をさらに完成されてよい。

## 【0048】

10

図3のプロセス300が、基板102上に、共通電極420、誘電体層424、及びピクセル電極426を含むコンデンサ427を形成するプロセスのシーケンスを記載していることは、留意されたい。

## 【0049】

工程304では、図5Aに示すとおり、基板102上に共通電極420（例えば第1の金属層）を形成するために物理的気相堆積処理が実施される。図5A～図5Cに示す共通電極420、誘電体層424、及びピクセル電極426が、図4に示す共通電極420、誘電体層424、及びピクセル電極426に相当することは、留意されたい。

## 【0050】

20

一実施例では、基板102上に形成される共通電極420は、酸化インジウムスズ（ITO）、酸化インジウム亜鉛（IZO）、酸化インジウムスズ亜鉛（ITZO）、アルミニウム（Al）、タンゲステン（W）、クロム（Cr）、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、マグネシウム（Mg）、銀（Ag）、金（Au）、クロム（Cr）、これらの合金、またはこれらの組み合わせといった、適切な金属材料から製造される。具体的な一実施例では、共通電極420は、酸化インジウムスズ亜鉛（ITZO）層である。

## 【0051】

30

工程306で示すように、共通電極420が、その上に誘電体層424を形成するのに先立って、必要に応じて任意の形態または任意の様でパターニングされていてよいことは、留意されたい。

## 【0052】

工程306で、基板102上に共通電極420が形成され、さらに必要に応じてオプションでパターニングされた後、図5Aに示すとおり、基板102上に誘電体層424が形成される。誘電体層424は、基板102を図1に示すプラズマ化学気相堆積チャンバー100といった堆積チャンバーに移送し、基板102に対して化学気相堆積処理を実施することによって、基板102上に形成され得る。

## 【0053】

一実施例では、誘電体層424は、例えば8よりも大きい誘電率を有する誘電体材料といった高誘電率材料によって製造された、単一の層であってよい。高誘電率材料層の適切な例は、とりわけ、二酸化ハフニウム（HfO<sub>2</sub>）、酸窒化ハフニウム（HfON）、二酸化ジルコニウム（ZrO<sub>2</sub>）、酸窒化ジルコニウム（ZrON）、酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）、酸窒化アルミニウム（AlON）、酸化ハフニウムケイ素（HfSiO<sub>2</sub>）、酸化ハフニウムアルミニウム（HfAlO）、酸化ジルコニウムケイ素（ZrSiO<sub>2</sub>）、二酸化タンタル（Ta<sub>2</sub>O<sub>5</sub>）、酸化アルミニウム、Y<sub>2</sub>O<sub>3</sub>、La<sub>2</sub>O<sub>3</sub>、酸化チタン（TiO<sub>2</sub>）、アルミニウムドープ二酸化ハフニウム、ビスマスストロンチウムチタン（BST）、及びプラチナジルコニウムチタン（PZT）を含む。誘電体層424が、CVD処理、ALD処理、または任意の適切な堆積処理によって製造されてよいことは、留意されたい。誘電体層424が高誘電率材料であるように構成されている実施例では、誘電体層424の高誘電率材料は、図7に示す処理チャンバー700といったALDチャンバー内で、ALD処理によって製造されてよい。

40

50

## 【0054】

誘電体層424として形成された高誘電率材料を使用することによって、コンデンサ427の構造体内に高誘電率が生じてよく、したがって、コンデンサ内に形成される誘電体層の誘電率が上昇するのにつれてコンデンサの容量が増大するため、大容量が得られてよい。誘電体層424によって提供される高容量によって、望ましくない電流の漏れとトンネル効果を低減しながらTFT装置450の電気性能を向上し得る。こうして、高誘電率材料の誘電体層424を含むコンデンサの容量は、コンデンサ427内で誘電体層424を高誘電率材料として使用することによって、コンデンサ内で従来型の窒化ケイ素層または酸化ケイ素層を高誘電率材料として使用する場合と比べて増大し向上し得る。

## 【0055】

いくつかの例では、基板102上に形成される誘電体層424は、図5Bに示すとおり複数の層を有する複合構造の形態であり得る。一実施形態では、誘電体層424は、頂部界面保護層506と底部界面保護層502との間にはさまれた、バルク誘電体材料504を含んでいてよい。頂部界面保護層506は、後からその上に形成されたピクセル電極426と接触していてよい。その一方で、底部界面保護層502は、共通電極420に接触して形成されてよい。この具体的な実施例では、バルク誘電体材料504は窒化ケイ素(SiN)材料または高誘電率材料によって製造されてよいが、その一方、頂部界面保護層506及び底部界面保護層502は、酸化ケイ素(SiO<sub>2</sub>)、酸窒化ケイ素(SiON)、オキシ炭化ケイ素(SiOC)、炭化ケイ素(SiC)などといったケイ素含有誘電体材料であってよい。一実施例では、バルク誘電体材料504が窒化ケイ素(SiN)材料であるとき、頂部界面保護層506及び底部界面保護層502は酸窒化ケイ素(SiON)材料であってよい。別の実施例では、図5Aに示すようにバルク誘電体材料504が誘電体層424といった高誘電率材料であるときに、頂部界面保護層506及び底部界面保護層502は、酸化ケイ素材料(SiO<sub>2</sub>)または酸窒化ケイ素(SiON)であってよい。

## 【0056】

一実施例では、頂部と底部の界面保護層506、502は、CVD堆積処理によって形成され得る。別の実施例では、頂部界面保護層506は、バルク誘電体材料504が窒化ケイ素(SiN)材料であるときに、O<sub>2</sub>、O<sub>3</sub>またはH<sub>2</sub>Oといった酸素含有ガスによってバルク誘電体材料504に対して酸化、酸素イオン注入、または酸素表面処理を行い、それによって、バルク誘電体材料504から酸窒化ケイ素層へと窒化ケイ素の表面が酸化されることによって、形成されてよい。

## 【0057】

ピクセル電極426と共通電極420の間に形成された頂部界面保護層506及び底部界面保護層502は、バルク誘電体材料504から頂部界面保護層506及び/または底部界面保護層502へのブリッジングを補助してよく、それによって、膜剥離の懸念なしにコンデンサ427の構造体の接合が強化される。さらに、頂部界面保護層506及び底部界面保護層502は、熱的に安定した界面構造体としての役割を果たしてもよく、それによって、金属のピクセル電極426及び共通電極420からの漏れが低減される。

## 【0058】

頂部界面保護層506及び/または底部界面保護層502は、バルク誘電体材料504(窒化ケイ素材料または高誘電率材料)が形成されるのと同じ処理チャンバで形成されてよい。代わりに、頂部界面保護層506及び/または底部界面保護層502は、必要に応じて任意の適切なチャンバ内で形成されてよい。

## 【0059】

工程308で、基板102上に誘電体層424が形成された後、次にピクセル電極426(例えば、第2の金属層)が誘電体層424上に形成される。工程304に記載されている共通電極420を形成する処理と同様に、ピクセル電極426は、酸化インジウムスズ(ITO)、酸化インジウム亜鉛(IZO)、酸化インジウムスズ亜鉛(ITZO)、アルミニウム(Al)、タンクスチン(W)、クロム(Cr)、タンタル(Ta)、チタ

10

20

30

40

50

ン (Ti)、モリブデン (Mo)、マグネシウム (Mg)、銀 (Ag)、金 (Au)、クロム (Cr)、これらの合金、またはこれらの組み合わせといった、任意の適切な金属材料から製造されてよい。また、ピクセル電極 426 は、図 2 に示す処理チャンバ 200 といったプラズマ堆積チャンバ内で実施される、物理的気相堆積 (PVD) 処理によって形成されてもよい。

#### 【0060】

一実施形態では、図 5A ~ 図 5B に示すとおり、ピクセル電極 426 は、この段落中の上記で検討された金属材料によって形成された、単一層の形態であってよい。代わりに、ピクセル電極 426 は、図 5C に示すもののように、上に第 2 の金属電極 510 が形成された第 1 の金属電極 508 といった、複数の材料を有する複合構造の形態であってもよい。

10

#### 【0061】

一実施例では、第 1 の電極 508 及び第 2 の電極 510 は、酸化インジウムスズ (ITO)、酸化インジウム亜鉛 (IZO)、酸化インジウムスズ亜鉛 (ITZO)、アルミニウム (Al)、タンクステン (W)、クロム (Cr)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、マグネシウム (Mg)、銀 (Ag)、金 (Au)、クロム (Cr)、銀ナノインク、カーボンナノチューブ (CNT)、銀ナノインク、グラフェン、またはこれらの合金から選択される、金属材料であってよい。具体的な一実施例では、第 1 の電極 508 は ITO 層であり、第 2 の電極 510 は Ta、Ti、Al、Mg、Mo、W、Ag、Mg またはこれらの合金から選択される金属層であってよい。別の実施例では、対照的に、第 1 の電極 508 が Ta、Ti、Al、Mg、Mo、W、Ag、Mg またはこれらの合金から選択される金属層であってよく、第 2 の電極 510 が ITO 層であってよい。

20

#### 【0062】

具体的な一実施例では、第 2 の電極 510 は、第 1 の電極 508 上に形成されたメッシュ電極またはグリッド電極の形態にパターニングされてよい。別の実施例では、ピクセル電極 426 及び / または共通電極 420 もまた、必要に応じてメッシュ電極またはグリッド電極の形態であってよい。

#### 【0063】

同様に、TFT 装置 450 の他の箇所または位置で、絶縁材料を形成するために、高誘電率材料、例えば 8 よりも大きい誘電率を有する誘電体材料が使われてもよい。図 4 の構円 452 に示されるように、高誘電率材料は、例えばオプションの絶縁層 404、ゲート絶縁層 406、または層間絶縁膜 412 を形成するのにもまた使用されてよい。上記のように、高誘電率材料層の適切な例は、とりわけ、二酸化ハフニウム (HfO<sub>2</sub>)、酸窒化ハフニウム (HfON)、二酸化ジルコニウム (ZrO<sub>2</sub>)、酸窒化ジルコニウム (ZrON)、酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、酸窒化アルミニウム (AlON)、酸化ハフニウムケイ素 (HfSiO<sub>2</sub>)、酸化ハフニウムアルミニウム (HfAlO)、酸化ジルコニウムケイ素 (ZrSiO<sub>2</sub>)、二酸化タンタル (Ta<sub>2</sub>O<sub>5</sub>)、酸化アルミニウム、Y<sub>2</sub>O<sub>3</sub>、La<sub>2</sub>O<sub>3</sub>、酸化チタン (TiO<sub>2</sub>)、アルミニウムドープ二酸化ハフニウム、ビスマスストロンチウムチタン (BST)、及びプラチナジルコニウムチタン (PZT) を含む。

30

#### 【0064】

図 6A ~ 図 6C は、図 4 の構円 452 に示すように、オプションの絶縁層 404、ゲート絶縁層 406、及び層間絶縁膜 412 の、種々の膜スタックの配置または構成を示す。上記のように、オプションの絶縁層 404、ゲート絶縁層 406、及び層間絶縁膜 412 のうちの任意の 1 つ (または全て) が、必要に応じて図 6A に示す高誘電率材料、例えば 8 よりも大きい誘電率を有する誘電体材料であってよい。オプションの絶縁層 404、ゲート絶縁層 406、または層間絶縁膜 412 の高誘電率材料は、図 7 に示す処理チャンバ 700 といった ALD チャンバ内で実施される ALD 処理か、図 1 に示す処理チャンバ 100 といった PECVD チャンバ内で実施される CVD 処理か、または、必要に応じ製造

40

50

プロセス中の任意の順序及び任意の時点で、CVD処理チャンバ及びALD処理チャンバの両方で、CVD - ALDのハイブリッド処理によって、形成され得る。

#### 【0065】

ゲート絶縁層406は、代わりに、内部に形成された1つ以上の層を持つ複合構造体の形式であってもよい。図6Bに示す例では、ゲート絶縁層406は、内部に合計3つの層602、604、606が形成されており、図5B及び図5Cに示す絶縁層424と同様である。具体的には、上記のように、ゲート絶縁層406は、頂部界面保護層606と底部界面保護層602との間にはさまれた、バルクゲート誘電体材料604を含んでいてよい。頂部界面保護層606は、後からその上に形成された層間絶縁膜412と接触していてよい。その一方で、底部界面保護層602は、オプションの絶縁層404に接触して形成されてよい。この具体的な実施例では、バルクゲート絶縁材料604は高誘電率材料によって製造されてよいが、その一方、頂部界面保護層606及び底部界面保護層602は、酸化ケイ素(SiO<sub>2</sub>)、酸窒化ケイ素(SiON)、オキシ炭化ケイ素(SiOC)、炭化ケイ素(SiC)などといったケイ素含有誘電体材料であってよい。一実施例では、図5Bまたは図5Cに示すようにバルクゲート絶縁材料606が誘電体層424といった高誘電率材料であるときに、頂部界面保護層606及び底部界面保護層602は、酸窒化ケイ素(SiON)または窒化ケイ素(SiN)であってよい。

#### 【0066】

代わりに、図6Cに示す別の一実施例では、層間絶縁膜412もまた、内部に1つ以上の層が形成されて構築されてよい。図6Cに示す例では、層間絶縁膜412は、内部に合計3つの層602、608、606が形成されており、図6Cに示すゲート絶縁層406と同様である。具体的には、上記のように、ゲート層間絶縁膜412は、頂部界面保護層606と底部界面保護層602との間にはさまれた、バルク層間絶縁膜608を含んでいてよい。頂部界面保護層606は、後からその上に形成された平面化層418(図4に示す)と接触していてよい。その一方で、底部界面保護層602は、ゲート絶縁層406に接触して形成されてよい。この具体的な実施例では、バルク層間絶縁膜608は高誘電率材料によって製造されてよいが、その一方、頂部界面保護層606及び底部界面保護層602は、窒化ケイ素、酸化ケイ素(SiO<sub>2</sub>)、酸窒化ケイ素(SiON)、オキシ炭化ケイ素(SiOC)、炭化ケイ素(SiC)などといったケイ素含有誘電体材料であってよい。一実施例では、図5Bまたは図5Cに示すようにバルク層間絶縁膜608が誘電体層424といった高誘電率材料であるとき、または図6Bに示すように示すようにゲート絶縁層406であるときに、頂部界面保護層606及び底部界面保護層602は、酸化ケイ素材料(SiO<sub>2</sub>)または酸窒化ケイ素(SiON)材料であってよい。

#### 【0067】

こうして、本明細書に記載の方法によって、ゲート絶縁層の材料及び構造を制御することと、装置、ピクセル電極、共通電極、及びこれらの間に形成された誘電体層の材料を、TFT装置構造体内の高電気的性能コンデンサとして絶縁することで、TFT装置構造体の電子の安定性、電気的性能、大容量性、低漏れ性、及び膜スタックの良好な集積が有利に向上される。

#### 【0068】

上記は本開示の実施形態を対象としているが、本開示の他のさらなる実施形態は、その基本的な範囲並びに以下の特許請求の範囲によって決定されるその範囲を逸脱することなく考案され得る。

10

20

30

40

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

## フロントページの続き

| (51)Int.Cl.   |                         | F I                  |

|---------------|-------------------------|----------------------|

| <i>G 02 F</i> | <i>1/1343 (2006.01)</i> | H 01 L 21/316 M      |

| <i>C 23 C</i> | <i>14/06 (2006.01)</i>  | H 01 L 29/78 6 1 2 Z |

| <i>C 23 C</i> | <i>14/14 (2006.01)</i>  | H 01 L 29/78 6 1 7 J |

| <i>C 23 C</i> | <i>16/50 (2006.01)</i>  | H 01 L 29/78 6 1 9 A |

| <i>C 23 C</i> | <i>14/10 (2006.01)</i>  | G 02 F 1/1343        |

|               |                         | C 23 C 14/06 K       |

|               |                         | C 23 C 14/06 F       |

|               |                         | C 23 C 14/14 D       |

|               |                         | C 23 C 16/50         |

|               |                         | C 23 C 14/06 E       |

|               |                         | C 23 C 14/10         |

- (72)発明者 イム , ドンギル

アメリカ合衆国 カリフォルニア 94566 , プレザントン , パセオ サンタ マリア 6

333

- (72)発明者 タイ , ウエンチン

アメリカ合衆国 カリフォルニア 95132 , サン ノゼ , ウエストヘブン ドライブ 1

746

- (72)発明者 ユー , ハーヴェイ

アメリカ合衆国 カリフォルニア 94043 , マウンテン ビュー , ロック ストリート

2000 , 12番

- (72)発明者 ウォン , テギヨン

アメリカ合衆国 カリフォルニア 95129 , サン ノゼ , ベルヴェディア レーン 10

54

- (72)発明者 ヤン , シャオ - リン

台湾 台北市 116 , ウエンシャン ディストリクト , ワンニング ストリート , レーン

23 , 3番 , 5階

- (72)発明者 リン , ワン - ユイ

台湾 台北市 104 , ペイ - アン ロード , レーン 608 , 3番 , 3階 - 1

- (72)発明者 ツアイ , ユン - チュー

台湾 台中市 407 , シートウン ディストリクト , シートウン ノース レーン 8 - 7

8番

審査官 小濱 健太

- (56)参考文献 特開2011-059157 (JP, A)

特開2007-298976 (JP, A)

特開2012-118531 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

G 02 F 1/1343 - 1/1368