(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4391042号

(P4391042)

(45) 発行日 平成21年12月24日(2009.12.24)

(24) 登録日 平成21年10月16日(2009.10.16)

(51) Int.Cl.

F 1

|         |       |           |

|---------|-------|-----------|

| B 4 1 J | 5/30  | (2006.01) |

| B 4 1 J | 2/44  | (2006.01) |

| B 4 1 J | 2/45  | (2006.01) |

| B 4 1 J | 2/455 | (2006.01) |

|         |      |   |

|---------|------|---|

| B 4 1 J | 5/30 | Z |

| B 4 1 J | 3/21 | L |

請求項の数 6 (全 21 頁)

(21) 出願番号

特願2001-181254 (P2001-181254)

(22) 出願日

平成13年6月15日(2001.6.15)

(65) 公開番号

特開2002-370406 (P2002-370406A)

(43) 公開日

平成14年12月24日(2002.12.24)

審査請求日

平成16年4月2日(2004.4.2)

(73) 特許権者 591044164

株式会社沖データ

東京都港区芝浦四丁目11番22号

(74) 代理人 100082050

弁理士 佐藤 幸男

(72) 発明者 笠井 忠

東京都港区芝浦四丁目11番地22号 株式会社 沖データ内

審査官 松川 直樹

(56) 参考文献 特開平11-070697 (JP, A)

特開2000-177170 (JP, A)

最終頁に続く

(54) 【発明の名称】補正方法及びそれを用いたプリンタ

## (57) 【特許請求の範囲】

## 【請求項1】

画像形成装置における記録ヘッドの複数の記録素子の位置ずれを示す第1の位置補正值を、2の累乗で表される記録素子の値毎に求め、

前記第1の位置補正值に基づいたラスタバッファの読み出しがアドレスにより、

前記ラスタバッファから2の累乗単位で補正すべきラスタデータを読み出す補正方法であって、

前記第1の位置補正值が格納されている補正メモリから前記第1の位置補正值を取り込むステップと、

前記記録ヘッドの前記画像形成装置に対する配置ずれを示す第2の位置補正值を取り込むステップと、

前記取り込んだ前記第1の位置補正值と前記第2の位置補正值で示す各変化点の変化方向が同一で、変化点で変化する量が所定値より大きいか否かを判定するステップと、

前記変化する量が前記所定値より大きいときには前記第2の位置補正值の変化点をずらすステップと、

前記第1の位置補正值と前記変化点をずらした第2の位置補正值とを合成して補正データを生成するステップと、

を含むことを特徴とする補正方法。

## 【請求項2】

前記第1の位置補正值は差分データ構成を有することを特徴とする請求項1記載の補正

10

20

方法。

【請求項 3】

前記第1の位置補正值は、前記記録ヘッドの歪み及びヘッドアレイの段差を位置ずれとして示し、前記第2の位置補正值は前記記録ヘッドの配置の傾きを配置ずれとして示していることを特徴とする請求項1記載の補正方法。

【請求項 4】

複数の記録素子をライン状に配列したチップを主走査方向に複数個ライン状に配列した記録ヘッドを用いて画像を記録するプリンタにおいて、

特定のヘッド補正単位毎に予め記録された前記記録ヘッドの各記録素子の位置ずれを示す第1の位置補正值を読出すと共に、当該ヘッド補正単位の値を2の累乗でかつ前記チップを構成する複数の記録素子の約数となる値をデータ補正単位として、このデータ補正単位で前記第1の位置補正值を求め、かつ前記記録ヘッドのプリンタに対する位置ずれを示す第2の位置補正值を取り込み、前記第1の位置補正值と前記第2の位置補正值で示す各変化点の変化方向が同一で、変化点で変化する量が所定値より大きいときには前記第2の位置補正值の変化点をずらして前記第1及び第2の位置補正值を合成して補正データとして出力する補正データ書込み手段と、

前記補正データ書込み手段から出力された前記データ補正単位毎の補正データを記憶する補正值記憶部と、

画像データを一時格納するラスタバッファ記憶部と、

前記補正値記憶部の前記補正データに基づいて補正を行い、前記第1の位置補正值に基づくアドレスを、前記ラスタバッファ記憶部へのデータ補正単位毎の読み出しアドレスとして与えるラスタバッファ制御部と、

前記ラスタバッファ記憶部から前記読み出しアドレスに基づいて前記データ補正単位ずつ画像データを読み出し、前記記録ヘッドに与えるヘッド制御部とを備えたことを特徴とするプリンタ。

【請求項 5】

前記第1の位置補正值は差分データ構成を有することを特徴とする請求項4記載のプリンタ。

【請求項 6】

前記第1の位置補正值は、前記記録ヘッドの歪み及びヘッドアレイの段差を位置ずれとして示し、前記第2の位置補正值は前記記録ヘッドの配置の傾きを配置ずれとして示していることを特徴とする請求項4記載のプリンタ。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、ライン状に配列した記録素子を有する記録ヘッドを有するプリンタに関し、特にその記録素子の位置補正を行う補正方法に関する。

【0002】

【従来の技術】

一般に、カラープリンタでは、LEDといった記録素子をライン状に配列した記録ヘッドを有するイエロー、マゼンタ、シアン、ブラックの各画像形成手段を配設している。そして、記録媒体を記録素子の配列方向と直交する方向に搬送し、各カラー画像データに基づいて、イエロー、マゼンタ、シアン、ブラックのトナーにより、ライン単位で順次カラー画像の記録を行っている。このように、各色の画像形成手段によって同一の記録媒体上に順次異なる色のトナーを重ねて転写しているため、各画像形成手段が正規の位置からずれて取り付けられていると、色ずれが生じ、所望の色再現が実現できず、画像品位を劣化させことになる。

【0003】

このように記録素子をライン上に並べた記録ヘッドにより記録媒体に記録を行うプリンタにおいて、記録素子の取付位置の誤差等に対して、装置への取付後に記録ヘッドに対して

10

20

30

40

50

画像データの走査タイミングを電気的に調整して補正を行う方法がある。このような記録ヘッドに関する補正としては次のようなものがある。

1. 主走査補正：ヘッド取付時の主走査方向（媒体搬送方向と直交する方向；X方向ともいう）の補正

2. 副走査補正：ヘッド取付時の副走査方向（媒体搬送方向と平行な方向；Y方向ともいう）の補正

3. 傾き補正：ヘッド取付時の副走査方向へのヘッド傾き（主走査方向とヘッドとのなす角度）の補正

4. ヘッド歪み補正：副走査方向へのヘッド歪みの補正

5. ヘッド段差補正：ヘッド内のLEDアレイ間の副走査方向への段差の補正

10

#### 【0004】

ここで、上記1.～3.はヘッドを装置に取り付けた時の位置ずれであり、4.と5.はヘッド自身の位置ずれである。

これらの位置ずれに対する補正を行うため、ヘッドを特定のドット数の補正単位で補正值を求め、これらの補正值に基づいた補正データを作成し、この補正データにも基づいてラスタバッファから画像データを読み出し、補正した画像データを記録ヘッドに送っていた。

#### 【0005】

##### 【発明が解決しようとする課題】

しかしながら、記録ヘッドの場合は、記録するサイズや解像度といった要素に合わせて設計される関係上、その記録素子の補正単位もこれに応じて決定され、従って、ラスタバッファからデータを読み出すための効率的なデータ転送の単位には必ずしも一致していない場合がある。

20

例えば、従来、ヘッド補正単位が96ドットであった場合、ラスタバッファに格納されるデータの補正単位も96ドット単位であるため、メモリのバースト転送といった効率的なデータ読み出しができず、プリンタとしての高速化の妨げとなっていた。

#### 【0006】

更に、従来では、ページ外のアドレスの部分や、記録媒体のレフトマージンやライトマージンのアドレス等、正味の画像データが存在しない領域に対してはラスタバッファに0データを書込んでいた。このため、余分なデータ書き込みをラスタバッファに対して行わなければならず、これらの点からも高速化への妨げとなっていた。

30

#### 【0007】

そして、従来では、ヘッド歪み・段差の補正值とヘッド傾きの補正值との変化点が重なり、かつ、その変化点で変化する量が大きい場合、実際の記録ヘッドの位置ずれ量との差が大きくなってしまい、その結果、印刷時に縦縞が発生し易くなり画質劣化の恐れがあった。

#### 【0008】

また、記録ヘッドの副走査方向の補正值は、そのプリンタにおける副走査方向の解像度によって異なるが、従来では、印刷する解像度が切り替わった場合は、その都度、ラスタバッファから読み出す副走査方向のラインの値を設定し直す必要があり、解像度の切替えに柔軟に対応することができなかった。

40

#### 【0009】

##### 【課題を解決するための手段】

本発明は、前述の課題を解決するため次の構成を採用する。

###### 構成1

画像形成装置における記録ヘッドの複数の記録素子の位置ずれを示す第1の位置補正值を、2の累乗で表される記録素子の値毎に求め、前記第1の位置補正值に基づいたラスタバッファの読み出しアドレスにより、前記ラスタバッファから2の累乗単位で補正すべきラスタデータを読み出す補正方法であって、前記第1の位置補正值が格納されている補正メモリから前記第1の位置補正值を取り込むステップと、前記記録ヘッドの前記画像形成装置に対する配置ずれを示す第2の位置補正值を取り込むステップと、前記取り込んだ前記第

50

1の位置補正值と前記第2の位置補正值で示す各変化点の変化方向が同一で、変化点で変化する量が所定値より大きいか否かを判定するステップと、前記変化する量が前記所定値より大きいときには前記第2の位置補正值の変化点をずらすステップと、前記第1の位置補正值と前記変化点をずらした第2の位置補正值とを合成して補正データを生成するステップと、を含むことを特徴とする。

#### 【0010】

##### 構成 2

複数の記録素子をライン状に配列したチップを主走査方向に複数個ライン状に配列した記録ヘッドを用いて画像を記録するプリンタにおいて、特定のヘッド補正単位毎に予め記録された前記記録ヘッドの各記録素子の位置ずれを示す第1の位置補正值を読み出すと共に、当該ヘッド補正単位の値を2の累乗でかつ前記チップを構成する複数の記録素子の約数となる値をデータ補正単位として、このデータ補正単位で前記第1の位置補正值を求め、かつ前記記録ヘッドのプリンタに対する位置ずれを示す第2の位置補正值を取り込み、前記第1の位置補正值と前記第2の位置補正值で示す各変化点の変化方向が同一で、変化点で変化する量が所定値より大きいときには前記第2の位置補正值の変化点をずらして前記第1及び第2の位置補正值を合成して補正データとして出力する補正データ書き込み手段と、

前記補正データ書き込み手段から出力された前記データ補正単位毎の補正データを記憶する補正值記憶部と、画像データを一時格納するラスタバッファ記憶部と、前記補正值記憶部の前記補正データに基づいて補正を行い、前記第1の位置補正值に基づくアドレスを、前記ラスタバッファ記憶部へのデータ補正単位毎の読み出しアドレスとして与えるラスタバッファ制御部と、前記ラスタバッファ記憶部から前記読み出しアドレスに基づいて前記データ補正単位ずつ画像データを読み出し、前記記録ヘッドに与えるヘッド制御部とを備えたことを特徴とする。

#### 【0015】

##### 【発明の実施の形態】

以下、本発明の実施の形態を具体例を用いて詳細に説明する。

##### 《具体例1》

##### 構成

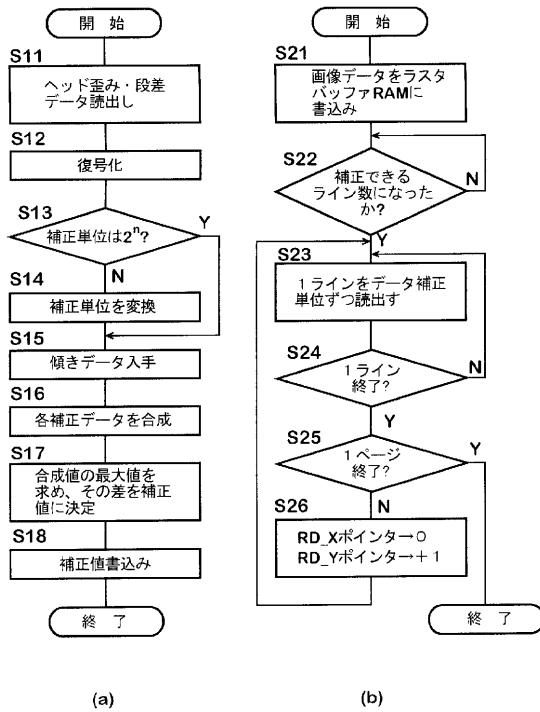

図1は、本発明のプリンタにおける補正方法を示すフローチャートであり、(a)は書き込み処理、(b)は読み出し処理を示す。

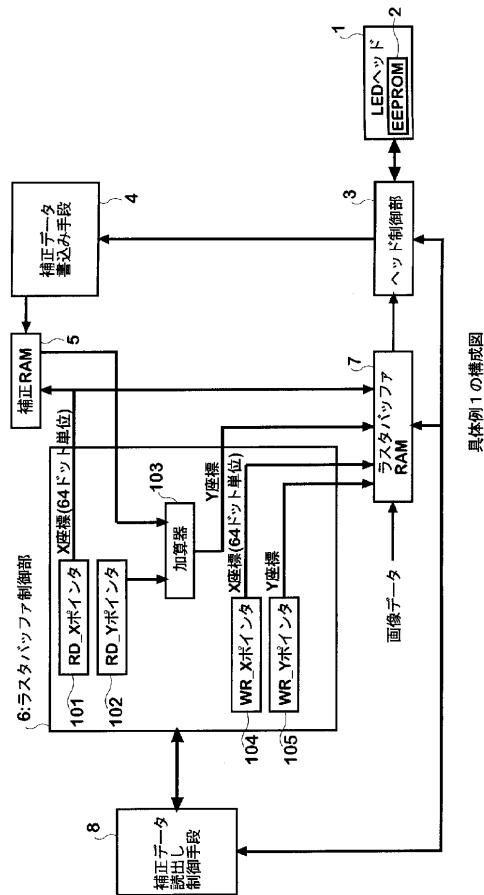

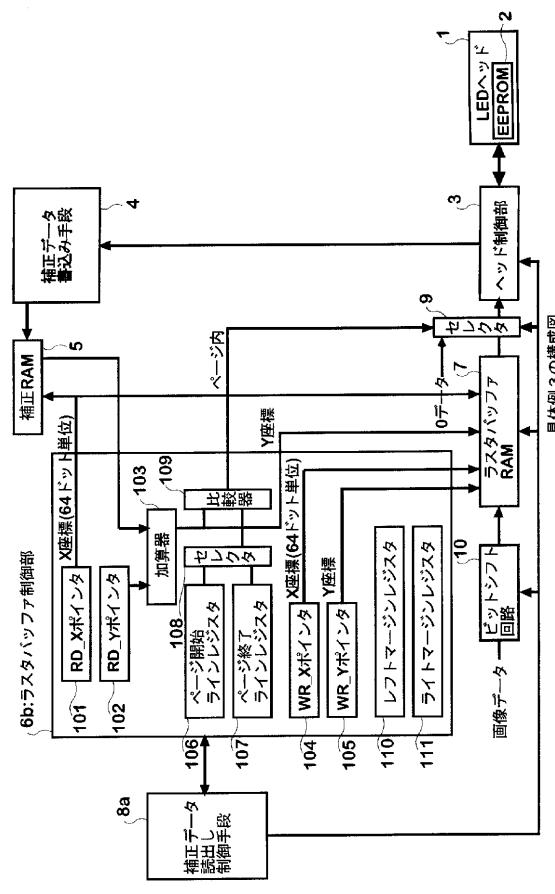

図2は、本発明のプリンタの具体例1の構成図である。

#### 【0016】

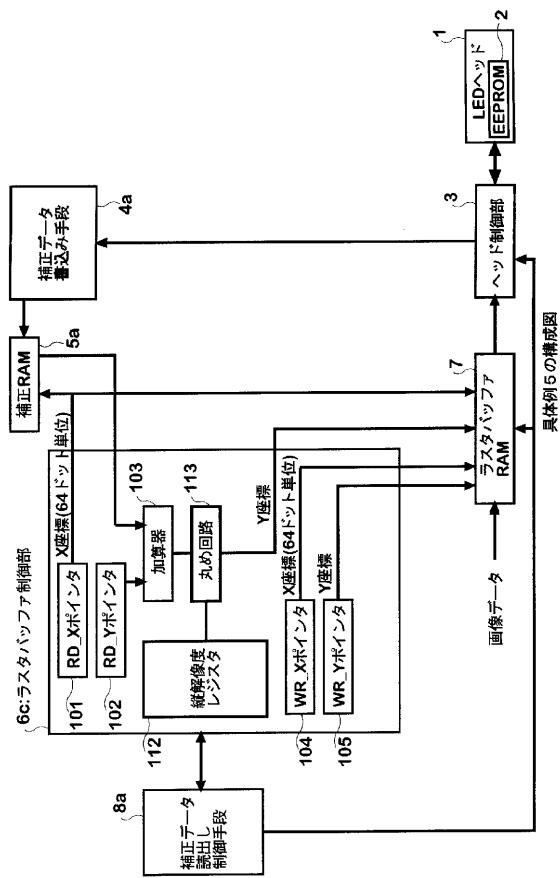

図2は、本発明のプリンタにおける1色あたりの構成を示すもので、カラープリンタとしてはこれが4色分(イエロー(Y)、マゼンタ(M)、シアン(C)、ブラック(B))あり、タンデム構成のドラムに対応するようになっている。尚、これらの機構部については公知であるためここでの説明は省略し、本発明の特徴点である制御構成を重点的に説明する。

図2に示す装置は、LEDヘッド1、EEPROM2、ヘッド制御部3、補正データ書き込み手段4、補正RAM(補正值記憶部)5、ラスタバッファ制御部6、ラスタバッファRAM(ラスタバッファ記憶部)7、補正データ読み出し制御手段8からなる。

#### 【0017】

LEDヘッド1は、複数のLEDアレイを一列に配置して構成されたプリンタにおける記録素子である。ここでは、説明を簡略化するため、LEDアレイが192ドット、全体で15360(1920バイト)ドットであるとする。即ち、192個のLED素子からなるLEDアレイのチップが、80個直列に並んで構成されている。

LEDヘッド1には、ヘッド歪み・段差データを格納するためのEEPROM2が内蔵されている。ヘッド歪み・段差データは、LEDヘッド1組立時に特定のドット単位に測定した位置情報であり、LEDヘッド1の副走査方向の位置ずれ(ヘッド歪み、チップ段差(LEDアレイ間の段差))を示す値である。尚、これらの値は公知の手段により別途測

10

20

30

40

50

定して書込むものである。ここでは、特定のドット単位として、96ドット単位でヘッド歪み・段差データが書込まれているとする。また、96ドットとは、一つのLEDアレイのチップのドット数である192を2分割した値であり、これをヘッド補正単位として以下説明を行う。即ち、LEDヘッド1の副走査方向の補正データとして、160個の位置補正値が格納されているものである。

#### 【0018】

ヘッド制御部3は、印刷時では、補正された画像データが格納されたラスタバッファ4から、その画像データを本具体例のデータ補正単位である64ビット単位で入力し、これをシリアル化してLEDヘッド1に送信する機能を有している。また、補正RAM5への補正値書込み時では、補正データ書込み手段4からのポート切替え指令によって、EEPROM2からヘッド歪み・段差データを読出して、これを補正データ書込み手段4に送信する機能を有している。10

#### 【0019】

補正データ書込み手段4は、CPUとRAM等により構成される機能部であり、EEPROM2からのヘッド歪み・段差データと、LEDヘッド1を取り付けた状態に測定される傾きデータを合成して補正データを生成すると共に、ヘッド補正単位が2の累乗ではなかった場合は、値の補間処理等を行い2<sup>n</sup>かつ一つのLEDアレイのドット数の約数で表されるデータ補正単位の補正データを生成し(本具体例では、96ドット毎のヘッド補正単位 64ドット毎のデータ補正単位)、この補正データを補正RAM5に書込む機能を有している。尚、これらの処理については、図1の(a)を参照して後で詳細に説明する。20

#### 【0020】

補正RAM5は、LEDヘッド1の上記補正データを格納するためのメモリであり、本具体例では、データ補正単位である64ドット毎の補正単位のデータを格納するものである。即ち、上記補正データ書込み手段4で生成した240個のデータがX方向に昇順で格納されている。また、本具体例では位置ずれ補正のためのライン数(Y方向のライン数)として256ライン分としている。従って、それぞれの補正データの値は8ビットで表され、この8ビットの値がラスタバッファ制御部6内の後述する加算器103に供給されるよう構成されている。

#### 【0021】

ラスタバッファ制御部6は、ラスタバッファRAM7への書込みアドレス(X座標、Y座標)を与えると共に、補正RAM5からの補正データを加算したアドレス(X座標、Y座標)をラスタバッファRAM7からの読み出しアドレスとして与えるための制御部であり、RD\_Xピントタ101、RD\_Yピントタ102、加算器103、WR\_Xピントタ104、WR\_Yピントタ105を備えている。30

#### 【0022】

RD\_Xピントタ101は、本具体例のデータ補正単位である64ドット単位でインクリメントするピントタであり、この値が補正RAM5へのアドレスとして与えられると共に、ラスタバッファRAM7への読み出し用下位アドレスとして与えられるようになっている。RD\_Yピントタ102は1ラインを読み出す度に1インクリメントするピントタであり、これはLEDヘッド1における補正なしのボトムラインを示すものである。加算器103は、RD\_Yピントタ102の値と、補正RAM5からの値を加算して生成したY座標のデータをラスタバッファRAM7への読み出し用上位アドレスとして与えるものである。WR\_Xピントタ104は64ドット単位でインクリメントした値を出力するピントタであり、ラスタバッファRAM7への書込み用下位アドレスとして供給する。WR\_Yピントタ105は、1ライン書込む度に1インクリメントし、Y座標としてラスタバッファRAM7の書込み用上位アドレスに入力するようになっている。40

#### 【0023】

RD\_Xピントタ101およびWR\_Xピントタ104はバイト単位、つまり64ドットずつ更新するためこれらピントタの出力値は8ずつ更新される。また、RD\_Yピントタ50

102およびWR\_Yポインタ105はライン単位である。尚、書き込み時は同一ラインを連続して書き込むので64ドット単位は必須ではない。書き込み効率を上げるために例えれば256ドット単位で書き込むよう構成してもよい。

#### 【0024】

ラスタバッファRAM7は、LEDヘッド1の副走査方向の位置ずれ(ヘッド歪み、チップ段差(LEDアレイ間の段差)、ヘッド傾き)の和に対応するライン分の画像データを、データ補正単位に合わせて格納するRAMである。本具体例では、上述したように位置ずれ補正のためのライン数として256ライン分とし、画像データの補正単位は64ビットであるとする。また、ラスタバッファRAM4は、画像データの書き込み/読み出しのためのバス幅を64ビットとしている。尚、32ビット幅であれば、連続2回アクセスを1単位とする。10

#### 【0025】

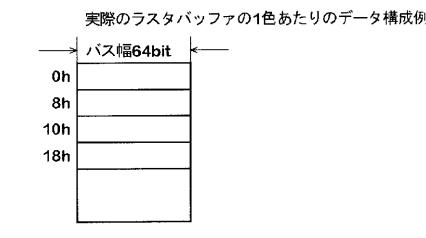

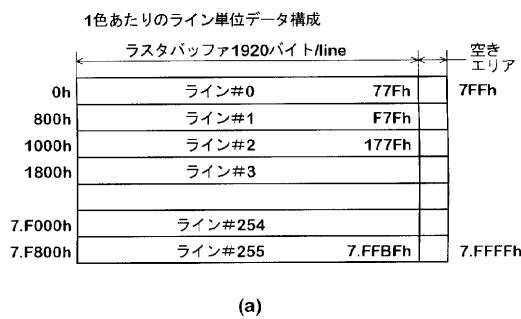

図3は、ラスタバッファRAM7のデータ構成例の説明図である。

図中の(a)に示すように、LEDヘッド1の1ラインのドット数に対応して、1ライン1920バイトを2Kバイト間隔で配置している。例えば、780h~7FFhのアドレスは空きエリアとして使用せず、800hを2ライン目の最初のX座標となるよう配置している。これはラスタバッファRAM7のアドレス下位がX座標、上位がY座標に対応し易くするためである。尚、実際にはラスタバッファRAM7のバス幅を64ビット幅としているため、(b)に示すように、64ビット単位の構成となっている。

#### 【0026】

補正データ読出制御手段8は、ラスタバッファ制御部6の制御情報に基づき、ラスタバッファRAM7からのデータ読出しを制御する機能を有しており、本具体例のデータ補正単位である64ドット分ずつラスタバッファRAM7からヘッド制御部3にデータ転送を行うための制御手段であり、図示しないCPUとRAM等により実現されている。20

#### 【0027】

##### 動作

本具体例の動作として、補正RAM5への補正データ書き込み処理と、印刷時の処理があり、最初に、図1に沿って補正RAM5への補正データ書き込み処理を説明する。

#### 【0028】

##### [ (a) 補正データ書き込み処理 ]

先ず、プリンタの電源投入がなされると、ヒートローラのウォーミングアップやドラムのクリーニング等、各機構部の初期設定が行われると共に、制御部の初期設定が行われる。即ち、補正RAM5やラスタバッファRAM7のメモリクリアが行われると共に、ラスタバッファ制御部6における各ポインタが0に初期化される。これらの初期化が終了すると上位の図示しないCPUは、補正RAM5への補正データ書き込み処理を指示する。これにより、補正データ書き込み手段4は、ヘッド制御部3のポートを切替え、EEPROM2からヘッド歪み・段差データを読出す(ステップS11)。このデータはデータ量を少なくするため、左隣96ドット単位のY方向位置を基準とした差分データになっている。

#### 【0029】

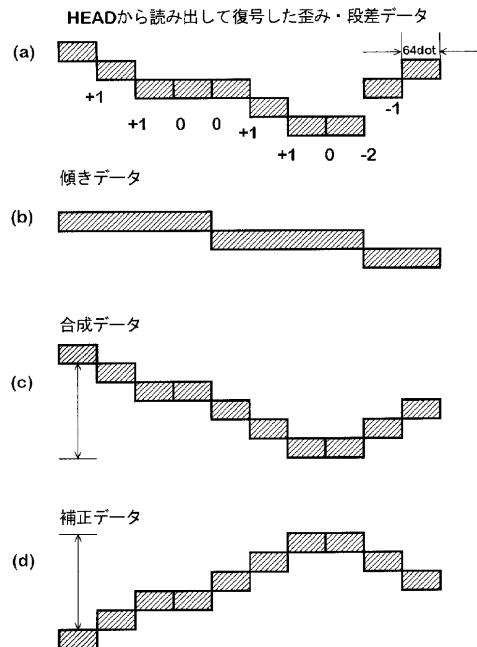

図4は、補正データの説明図である。40

図中、(a)に示すのが、EEPROM2から読出した歪み・段差データであり、左隣との差分データで表されている。尚、以下の説明で“左”“右”とは図面上での“左”“右”と同一であるとする。また、図4の(a)~(d)はLEDヘッド1のうち、左端からの部分データを示している。

#### 【0030】

LEDヘッド1の歪み・段差データは差分データとなっているため、補正データ書き込み手段4は、これを絶対値データに復号する(ステップS12)。この処理は、LEDヘッド1の左端のデータを0として差分値を順次加算する処理である。従って、(a)に示すように、+1,+1,0,0,+1,...のデータは、0,+1,+2,+2,+3,...といったデータに復号される。50

**【0031】**

次に、補正データ書込み手段4は、歪み・段差データの補正単位(=ヘッド補正単位A)が2の累乗の値であるかを調べ(ステップS13)、そうでない場合は、本具体例のデータ補正単位である64ドット単位の歪み・段差データに変換する(ステップS14)。この処理は、各データから64ドット単位の値を補間して求め、かつ、補間値が小数の場合は四捨五入等により整数値とする。また、ヘッド補正単位が2の累乗であった場合はステップS14の変換処理は行わない。

**【0032】**

次に、補正データ書込み手段4は傾きデータ入手する(ステップS15)。傾きデータは、図示しない傾き検出手段、傾き入力手段等により入手するものである。この傾きデータはLEDヘッド1左端のY座標を基準とした右端のY方向位置データであり、例えば+3という形で与えられる。+3という値は右肩下がりであり、1ラインを64ドットで分割し、かつ、1ラインを4分割したX座標で階段状に0から+3ラインになる。即ち、本具体例では、 $(15360 / 64) / 4 = 60$ であるため、64ドット単位で60番目の位置で切り替える。割り切れない場合は値を四捨五入する等の処理を行う。このようにして得られるのが、図4の(b)に示すデータである。

10

**【0033】**

補正データ書込み手段4は、ステップS12で求めた値(歪み・段差データ)またはステップS14で変換した値と、ステップS15で入手した傾きデータから合成した位置ずれデータを作成し、それから補正データを求める(ステップS16)。データは、歪み・段差データと傾きデータの64ドット単位で各々対応するY方向の値を加算して求める。このようにして求めたのが図4(c)に示すデータである。

20

**【0034】**

次に、補正データ書込み手段4は、ステップS16で求めた合成値の最大値を求め、その差を補正值とする(ステップS17)。また、この補正值は全て正になるようになる。このようにして求めたのが図4(d)に示すデータである。

尚、これらの処理は、実際には、補正データ書込み手段4におけるCPUがRAM上で行うものである。また、上記ステップS13、S14の補正值処理を傾きデータとの合成後に行ってもよい。

30

**【0035】**

最後に、補正データ書込み手段4は、求めた補正值を補正RAM5に書込む(ステップS18)。

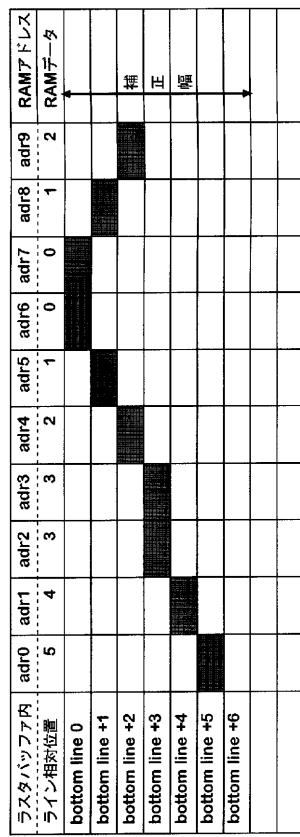

図5は、補正RAM5内のデータ構成の説明図である。

図示のように、アドレス0には値5、アドレス1には値4といったように値を格納する。尚、このアドレス0, 1, ...は、RD\_Xポインタ101から与えられたアドレスである。

**【0036】**

次に、印刷時の動作について図1の(b)に沿って説明する。

**[印刷時の動作]**

先ず、機構部の初期動作が行われ、また、カラー画像から色分解が行われて各色の図示しないメモリに格納されるが、これらの処理は従来と同様であるため、ここでの説明は省略する。

40

**【0037】**

画像データが、図示しない上位より送信され、図3に示すようなデータ構成でラスタバッファRAM7に格納される。即ち、WR\_Xポインタ104およびWR\_Yポインタ105でX座標、Y座標を制御し、画像データを格納する(ステップS21)。

**【0038】**

補正データ読出制御手段8は、ラスタバッファRAM7へのデータ書込みが補正できる256ライン分以上になったかを判定し(ステップS22)、256ライン分に達したらヘッド制御部3へのデータ読出しを開始し、データ補正単位である64ドットずつデータ転

50

送する（ステップS23）。この読み出し処理は次のようになる。先ず、RD\_Xポインタ<sub>101</sub>=0、RD\_Yポインタ<sub>102</sub>=0にする。これにより、補正RAM5より値5（図5参照）が出力され、その結果、加算器103の出力は5となり、ラスタバッファRAM7への上位アドレスとして値5が与えられる。これにより、ラスタバッファRAM7からは5ライン目のデータ（64ドット分のデータ）が、ヘッド制御部3に出力される。次に、RD\_Xポインタ<sub>101</sub>がインクリメントされ、次の64ドットのX座標を示す。これにより補正RAM5からは次の値である4が出力され、従って、ラスタバッファRAM7からは4ライン目のデータが出力される。このような処理を、ステップS24で1ライン分の読みしが終了したと判定されるまで繰り返して行い、1ライン分の読みしを行う。これにより、補正RAM5に格納されている補正データの通りの補正が行われる。

10

#### 【0039】

1ライン分の読みしが終了すると、RD\_Xポインタ<sub>101</sub>が0を戻し、RD\_Yポインタ<sub>102</sub>を1インクリメントする（ステップS25）。そして、上記と同様のステップS23の読み出し処理を実行する。即ち、補正RAM5からは値5が出力され、この値とRD\_Yポインタ<sub>102</sub>の値が加算器103で加算され、値6がラスタバッファRAM7に上位アドレスとして与えられる。これにより、ラスタバッファRAM7からは6ライン目のデータが、ヘッド制御部3に出力される。これを1ライン分繰り返して行い、1ページ分のラインを行うことで補正された印刷データが生成される。

#### 【0040】

以上のような、画像データの読み出し処理がイエロー、マゼンタ、シアン、ブラックの4色分行われ、各色毎に印刷動作が行われるが、これらの動作は従来と同様であるためここでの説明は省略する。

20

#### 【0041】

##### 効果

以上のように、具体例1によれば、ヘッド補正単位毎の補正值から、データ補正単位毎の補正值を求めて補正データを形成し、このデータ補正単位でラスタバッファRAM7へのアクセスを行うようにしたので、例えば、メモリのバースト転送等に対応でき、従って、ラスタバッファRAM7からのデータ読み出しの高速化が図れ、印刷処理の高速化を図ることができる。また、ヘッド補正単位がどのようなものであっても、効率的なデータ転送を行うことができる効果がある。

30

#### 【0042】

##### 《具体例2》

具体例2は、画像データ領域外のラスタバッファRAM7への余分な0データ書き込みを無くすようにしたものである。

#### 【0043】

##### 構成

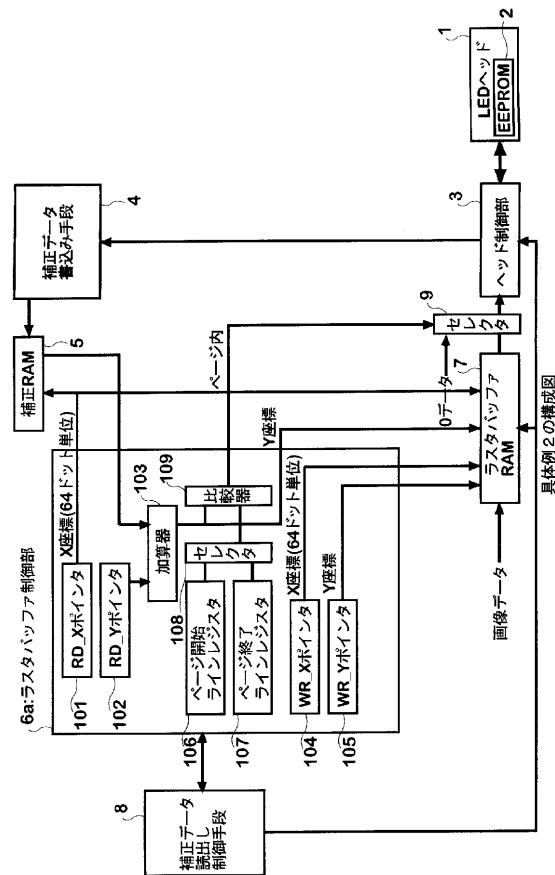

図6は、具体例2によるプリンタの1色あたりの構成図である。

図の装置は、LEDヘッド1、EEPROM2、ヘッド制御部3、補正データ書き込み手段4、補正RAM5、ラスタバッファ制御部6a、ラスタバッファRAM7、補正データ読み出制御手段8、セレクタ9からなる。ここで、ラスタバッファ制御部6aの構成とセレクタ9以外の構成は具体例1と同様であるため、対応する部分に同一符号を付してその説明を省略する。

40

#### 【0044】

ラスタバッファ制御部6aは、RD\_Xポインタ<sub>101</sub>、RD\_Yポインタ<sub>102</sub>、加算器103、WR\_Xポインタ<sub>104</sub>、WR\_Yポインタ<sub>105</sub>、ページ開始ラインレジスタ<sub>106</sub>、ページ終了ラインレジスタ<sub>107</sub>、セレクタ<sub>108</sub>、比較器<sub>109</sub>を備えている。ここで、RD\_Xポインタ<sub>101</sub>～WR\_Yポインタ<sub>105</sub>は、具体例1と同様であるため、ここでの説明は省略する。

ページ開始ラインレジスタ<sub>106</sub>は、ラスタバッファRAM7に格納する画像データのページ開始時のライン番号を保持するレジスタである。ページ終了ラインレジスタ<sub>107</sub>は

50

ラスタバッファRAM7に格納する画像データのページ終了時のライン番号を保持するレジスタである。これらのレジスタは、図示しない上位のCPUが、画像データ書き込み開始・終了時のY座標を検知して書込むものである。または、ハードウェアにより書き込み開始・終了時のWR\_Yポインタ105の値をコピーすることにより書き込まれるよう構成してもよい。

#### 【0045】

セレクタ108は、ページ開始ラインレジスタ106の値かページ終了ラインレジスタ107の値を選択して出力するセレクタであり、初期化後は、ページ開始ラインレジスタ106の出力を選択し、加算器103の出力値が全てページ開始ラインレジスタ106の値以上になったタイミングでページ終了ラインレジスタ107側の値を選択するよう構成されている。比較器109は、セレクタ108から出力されたレジスタの値と加算器103からの補正されたY座標とを比較するための比較器であり、セレクタ108で選択した値がページ開始ラインレジスタ106の値である範囲では、加算器103の出力値がセレクタ108の値よりも大きい場合にページ内であると判定し、加算器103の出力値が全てページ開始ラインレジスタ106の値以上になったタイミングで、加算器103の出力値がセレクタ108の値より大きくなった時点でページ外であると判定するものであり、ページ内と判定した場合にセレクタ9へのページ内信号をオンとするよう構成されている。尚、これらのセレクタ108の切替え制御、比較器109における値の比較制御はラスタバッファ制御部6a内の図示しない制御手段により行われるものである。

#### 【0046】

セレクタ9は、0データとラスタバッファRAM7の出力とを入力し、比較器109からのページ内信号を切替信号としてこれらの信号を切り替えるためのセレクタであり、0データ出力手段を構成している。

#### 【0047】

##### 動作

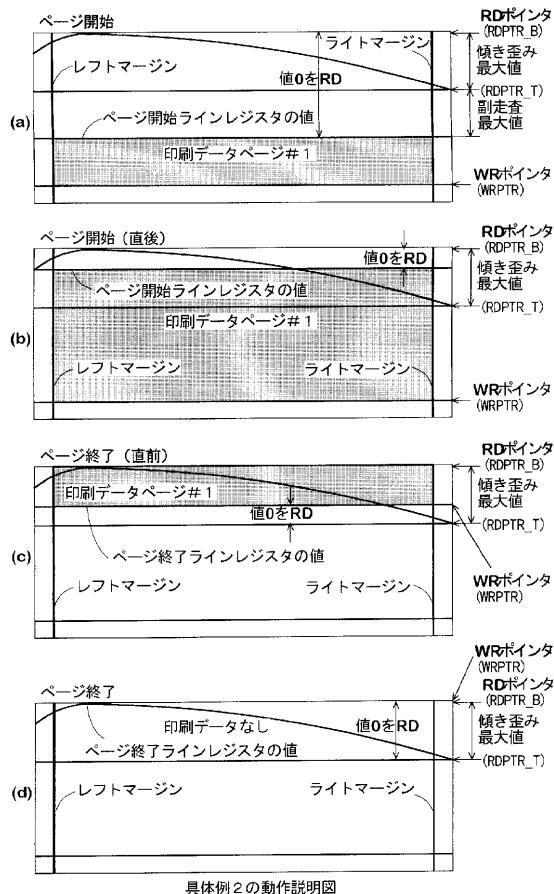

図7は、具体例2における動作説明図であり、これらの図はラスタバッファRAM7内のデータ格納状態を示すものである。

図において、(a)はページ開始時、(b)はページ開始直後、(c)はページ終了直前、(d)はページ終了の4ケースを示している。これらの図において、ラスタバッファRAM7に書き込まれた画像データ(印刷データ)の領域は網掛けで示しており、非表示の領域は何も書き込まれていないことを示している。つまり、非表示の領域のデータを仮に読み出すと不定値が出力されることになる。また、RDポインタであるRDPTR\_B(ボトムラインの読み出しアドレス用ポインタ)はRD\_Yポインタ102の値に対応しており、弓状の曲線で示すのが補正後のY座標の軌跡で、加算器103の出力に対応している。また、RDPTR\_T(トップラインの読み出しアドレス用ポインタ)は、その軌跡の最大値を示している。

#### 【0048】

また、印刷データの開始ラインがページ開始ラインレジスタ106の値と一致しており、印刷データの終了ラインがページ終了ラインレジスタ107の値と一致している。尚、図中のレフトマージン、ライトマージンについては、次の具体例3で説明するため、本具体例ではその説明は省略する。

#### 【0049】

まず、プリンタへの電源投入がなされると、図示しない上位のCPUにより、各ポインタやレジスタが初期化される。そして、具体例1で説明したのと同様に、ラスタバッファRAM7に画像データが格納される。先ず、(a)に示すように、ページ開始時はページ開始ラインレジスタ106の値より傾き歪み最大値分より小さい値からRDポインタは開始する。このとき、セレクタ108は図示しないラスタバッファ制御部6a内の制御手段により、ページ開始ラインレジスタ106の出力を選択している。補正後のY座標の軌跡は全てページ開始ラインレジスタ106の値より小さいため、比較器109はページ外であると判定する。これによりセレクタ9は0データを選択してヘッド制御部3に出力する。

10

20

30

40

50

**【 0 0 5 0 】**

次に、( b )に示すように、ページ開始直後では補正後の Y 座標の軌跡は途中からページ開始ラインレジスタ 106 の値を超える。つまり、加算器 103 の出力がページ開始ラインレジスタ 106 の値よりも大きくなる領域が存在する。従って、超えた領域ではページ内であるため、セレクタ 9 はラスタバッファ RAM 7 からの印刷データをそのまま選択してヘッド制御部 3 に出力し、そうでない領域では 0 データを選択してヘッド制御部 3 に出力する。そして、更に経過して補正後の Y 座標の軌跡が全てページ開始ラインレジスタ 106 の値を超えたとき以降はページ内であるため、セレクタ 9 は全て印刷データのみを出力する。このタイミングでセレクタ 108 は、図示しない制御手段によりページ終了ラインレジスタ 107 側に切り替えられる。

10

**【 0 0 5 1 】**

次に、( c )に示すように、ページ終了直前では、補正後の Y 座標の軌跡は途中からページ終了ラインレジスタ 107 の値を超える。即ち、セレクタ 108 の出力より加算器 103 の出力の方が大きな値となる。これにより比較器 109 はページ外であるかを判定し、ページ内信号をオフとする。これによりセレクタ 9 は、0 データを選択し、ヘッド制御部 3 に出力する。

**【 0 0 5 2 】**

次に、( d )に示すように、ページ終了時では、補正後の Y 座標の軌跡は全てページ終了ラインレジスタ 107 の値よりも大きいため、比較器 109 はページ内信号をオフとする。これにより、セレクタ 9 は 0 データを選択してヘッド制御部 3 に出力する。そして、RD ポインタがページ終了ラインレジスタ 107 の値と一致した時点で 1 ページ分の印刷データのラスタバッファ RAM 7 からの読み出しは終了する。

20

**【 0 0 5 3 】****効果**

以上のように具体例 2 によれば、具体例 1 の構成に加えて、補正後の Y 座標の軌跡がページ内であるか否かを判別し、ページ外ならば値 0 を選択してラスタバッファ RAM 7 からの読み出しデータの代わりのデータとするようにしたので、具体例 1 の効果に加えて、従来のようなラスタバッファ RAM 7 への値 0 の書き込み処理が不要となり、従ってより高速化を図ることができる。

**【 0 0 5 4 】**

30

尚、上記具体例 2 では、0 データ出力手段としてセレクタ 9 を用いたが、ラスタバッファ制御部 6a からのページ内信号をヘッド制御部 3 に与えるようにし、ページ内信号がオフの場合はヘッド制御部 3 で 0 データを生成するようにしてもよい。

**【 0 0 5 5 】****《具体例 3》**

具体例 3 は、LED ヘッド 1 における主走査方向の補正を行うようにしたものである。即ち、従来では、ラスタバッファに記録ヘッドのヘッド長分のデータを書き込み、それを読み出していた。しかし、実際に印刷する画像の大きさは用紙サイズの全てではなく、とじしろ等、用紙 4 辺から内側に余白領域を設定している。更に、ヘッド長は用紙横幅よりも長くなるように設定されている。従って、上位からの画像データは、画像データに対して、ヘッド長分になるよう余白分のデータが付加されたデータであるため、この余白分のデータを受信し、ラスタバッファに書き込む時間が余計にかかっていた。また、上位にしてもこの余白データを付加する処理と、データ送信の分時間がかかっていた。このため、本具体例では、正味の画像が存在しない領域ではラスタバッファへの書き込み・読み出しをしないようにしたものである。

40

**【 0 0 5 6 】****構成**

図 8 は、具体例 3 によるプリンタの 1 色あたりの構成図である。

図の装置は、LED ヘッド 1、EEPROM 2、ヘッド制御部 3、補正データ書き込み手段 4、補正 RAM 5、ラスタバッファ制御部 6b、ラスタバッファ RAM 7、補正データ読み出しへ向かう。

50

出制御手段 8 a、セレクタ 9、ビットシフト回路 10 からなる。ここで、ラスタバッファ制御部 6 b、補正データ読出制御手段 8 a およびビットシフト回路 10 以外の構成は具体例 1 と同様であるため、対応する部分に同一符号を付してその説明を省略する。

#### 【0057】

ラスタバッファ制御部 6 b は、RD\_X ポインタ 101、RD\_Y ポインタ 102、加算器 103、WR\_X ポインタ 104、WR\_Y ポインタ 105、ページ開始ラインレジスタ 106、ページ終了ラインレジスタ 107、セレクタ 108、比較器 109、レフトマージンレジスタ 110、ライトマージンレジスタ 111 を備えている。ここで、RD\_X ポインタ 101～比較器 109 は、具体例 2 と同様であるため、ここでの説明は省略する。10

#### 【0058】

レフトマージンレジスタ 110 は、LED ヘッド 1 の左端から正味の画像データ右端までの余白領域の値を保持するレジスタである。ライトマージンレジスタ 111 は、正味の画像データ右端から LED ヘッド 1 の右端までの余白領域の値を保持するレジスタである。両レジスタは単に余白領域設定だけでなく、主走査方向の補正值を加算した値を与える。従って、1 色毎に独立して存在する。

#### 【0059】

補正データ読出制御手段 8 a は、具体例 1 における補正データ読出制御手段 8 の機能に加えて次のような機能を有している。即ち、レフトマージンレジスタ 110 の値を含むデータ補正単位のアドレスから、ライトマージンレジスタ 111 の値を含むデータ補正単位のアドレスまでは、ビットシフト回路 10 からのデータをラスタバッファ RAM 7 に書き込み、ラスタバッファ RAM 7 からデータを読出す場合は、ビットシフト回路 10 からラスタバッファ RAM 7 にデータが書き込まれた領域では、ラスタバッファ RAM 7 からデータを読出すようセレクタ 9 に指示し、それ以外の領域では 0 データを出力するようセレクタ 9 の制御を行なう構成されている。20

#### 【0060】

ビットシフト回路 10 は、ラスタバッファ RAM 7 の手前に接続され、パレルシフタとレジスタ等により構成されるもので、レフトマージンレジスタ 110 の下位 6 ビットの値（0 から 63 ドット）分ビットシフトし、一つ前のデータの残りと連結して 64 ビット単位でラスタバッファ RAM 7 に出力する。また、レフトマージンレジスタ 110 の値で示す書き込み開始部分では一つ前のデータの残りの代わりに値 0 にする。そして、ライトマージンレジスタ 111 の値で示す書き込み終了部分ではライトマージンレジスタ 111 の下位 6 ビットの値（0 から 63 ドット）から 63 ドットまでを値 0 としてラスタバッファ RAM 7 に出力するよう構成されている。即ち、ビットシフト回路 10 は、レフトマージンレジスタ 110 の値のうち、データ補正単位（64 ドット）のビット数で切り捨てた値の残りのビット数分ビットシフトし、その結果、データが存在しない書き込みラインの開始および終了時は、0 データを埋めるようにした回路である。30

#### 【0061】

##### 動作

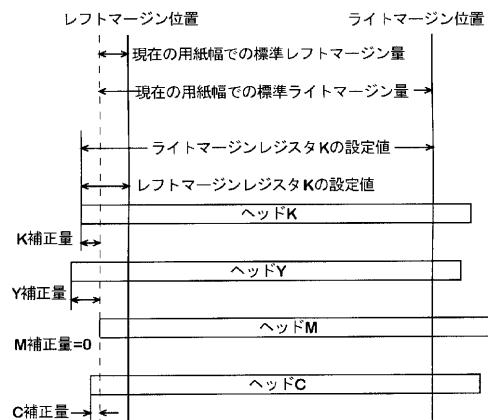

図 9 は、各色の LED ヘッド 1 とレフトマージン / ライトマージンとの関係を示す説明図である。40

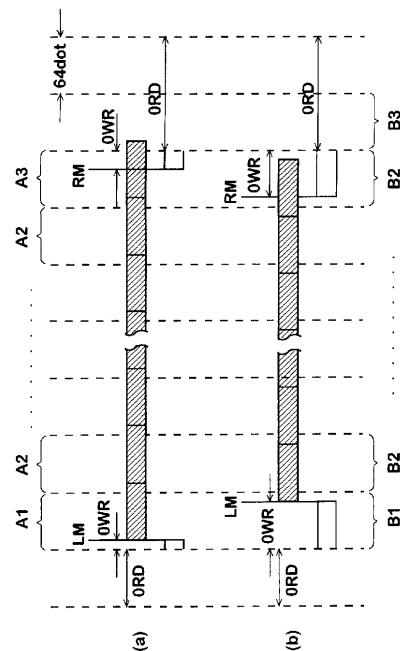

図 10 は、1 色分の動作説明図である。

#### 【0062】

図 9 に示すように、現在の用紙幅での標準レフトマージン値、標準ライトマージン値はアプリケーションの用紙余白設定等により予め決められている。例えば図 9 において、ヘッド K の主走査方向補正量が分かると、その値を標準レフトマージン値、標準ライトマージン値に加算した値をレフトマージンレジスタ 110 およびライトマージンレジスタ 111 に設定する。

#### 【0063】

例えば、本具体例では、補正をえた設定値が、レフトマージンレジスタ 110 の値（L

50

$M = 45h$  (69)、ライトマージンレジスタ111の値( $RM = 403h$  (1027))、LEDヘッド1のヘッド長= $7fffh$  (2047)として以下の動作を説明する。尚、ライトマージンレジスタ111の値は、LEDヘッド1の左端から正味の画像データの右端までの値を設定している。以下、ラスタバッファRAM7への書き込み処理と読み出し処理に分けて説明を行う。

#### 【0064】

##### [ラスタバッファRAM7への書き込み処理：A]

A1 : WR\_Xポインタ104はLM値を64ドット単位で切り捨てた $40h / 8ビット = 8h$ がロードされる。また、WR\_Yポインタ105=0でライン0から書き込みを開始する。上位から画像データがビットシフト回路10に入力されると、ビットシフト回路10では、LM値の下位6ビット= $05h$ であるため最初から5ビット分は0、残りは5ビット分シフトして64ビットにしたデータを出力する。このデータをラスタバッファRAM7のWR\_Xポインタ104に示すアドレスに書き込む。これが図10におけるA1に示す状態である。即ち、WR\_Xポインタ104で示す64ビット目のアドレスに、ビットシフト回路10で生成した最初の5ビット分が0、残りを5ビット分シフトして64ビットにしたデータを書き込む。図中の0WRが最初の0データを表している。

#### 【0065】

A2 : WR\_Xポインタ104はインクリメントし、 $10h$  ( $8h \times 2$ )となる。次に画像データがビットシフト回路10に入力されると、先程の残りの5ビットと今回5ビット分シフトしたデータを連結して64ビットにしたデータが出力される。これが、図中のA2に示す状態である。

#### 【0066】

A3 : 上記のA2の処理を繰り返し、WR\_Xポインタ104がRM値を64ドット単位で切り捨てた $400h / 8ビット = 80h$ になると、補正データ読み出し制御手段8aは、ビットシフト回路10に対して、ライン最後のデータ補正単位分のデータであることを知らせる。ビットシフト回路10は、この信号を受けて、LM値の下位6ビット<RM値の下位6ビットの判定を行い、この関係が成り立つ場合は、図10の(a)に示すように、残りビットと今回ビットシフトしたデータを連結して64ビットにした後、RM値の下位6ビットの値から63ドットまでを値0にして出力する。一方、LM値の下位6ビットRM値の下位6ビットの条件を満たした場合は、図10の(b)に示すように、残りビットの内、RM値の下位6ビットの値から63ドットまでを値0にして出力する。A3における0WRがこれらの0データとした範囲を表している。本具体例では $05h > 03h$ なので、図10(b)に示すケースである。つまり、残り5ビットのうち3ビットまでが有効で残りは値0にして出力する。このようなデータをラスタバッファRAM7に書き込む。

#### 【0067】

A4 : WR\_Yポインタ105は1インクリメントし、WR\_Xポインタ104は再び8hがロードされる。以降、同様にA1からの処理を繰り返す。

#### 【0068】

以上のように、WR\_Xポインタ104は、8hから80hまでしか動作していないため、それ以外の領域は何も書き込まれていないことになる。

#### 【0069】

##### [ラスタバッファRAM7からの読み出し処理：B]

B1 : RD\_Xポインタ101は値0、RD\_Yポインタ102=0から読み出しを開始する。尚、実際は具体例2で説明したようにRD\_Yポインタ102=0 - 傾き歪み最大値から読み出しを開始するが、ここでは説明を簡略にするため0からとする。先ず、RD\_Xポインタ101の値<LM値を64ドット単位で切り捨てた値( $40h / 8ビット = 8h$ )であるため、ラスタバッファRAM7から読み出さず、セレクタ9に対して0データを出力するよう補正データ読み出し制御手段8aが指示を行う。これが、図10のB1の状態である。

#### 【0070】

10

20

30

40

50

B 2 : 次に、RD\_Xポインタ101はインクリメントし、値は8hとなる。従って、RD\_Xポインタ101の値 = LM値を64ドット単位で切り捨てた値となるので、ラスタバッファRAM7からデータを読出すよう補正データ読出制御手段8aはセレクタ9に指示を行う。

#### 【0071】

B 3 : 上記のB 2 の処理を繰り返し、RD\_Xポインタ101の値 > RM値を64ドット単位で切り捨てた値 (400h / 8ビット = 80h) の条件を満たすようになったら、ラスタバッファRAM7からデータを読出さず、0データを選択するようセレクタ9に指示を行う。

#### 【0072】

B 4 : 更に、RD\_Xポインタ101 = ヘッド長 (7fffh + 1) / 8ビット = 100hになつたら RD\_Yポインタ102を1インクリメントし、RD\_Xポインタ101を0とする。

#### 【0073】

B 5 : B 1からの処理を繰り返す。

以上のように、データが書込まれていない領域では0を出力し、そうでない領域はラスタバッファRAM7から出力するようにしている。

#### 【0074】

##### 効果

以上のように具体例3によれば、レフトマージンレジスタ110の値を含むデータ補正単位のアドレスから、ライトマージンレジスタ111の値を含むデータ補正単位のアドレスまでは、ビットシフト回路10からのデータをラスタバッファRAM7に書き込み、ラスタバッファRAM7からデータを読出す場合は、ビットシフト回路10からラスタバッファRAM7にデータが書き込まれた領域ではラスタバッファRAM7からデータを読出し、それ以外の領域では0データを出力するようにしたので、ラスタバッファRAM7への余分なデータの書き込み・読出しがなくなると共に、主走査補正のための余分なデータをLEDヘッド1に送る必要がなくなり、ヘッド長分ラスタバッファRAM7に書き込み／読出しする必要がないため、その分高速化を図ることができる。

#### 【0075】

尚、上記具体例3では、ラスタバッファRAM7にデータが書込まれていない領域ではセレクタ9を切り替えて0データをヘッド制御部3に送るようにしたが、レフトマージンレジスタ110およびライトマージンレジスタ111の値に基づき、補正データ読出制御手段8aがヘッド制御部3に対して指示を行つて、0データを生成するよう構成してもよい。

#### 【0076】

##### 《具体例4》

具体例4は、LEDヘッド1における歪み・段差データの変化点と傾きデータとの変化点が重なり、変化する量が所定量より大きい場合に、傾きデータの変化点をずらして変化する量が大きい変化点を抑えるようにしたものである。

#### 【0077】

##### 構成

図面上の構成は図2に示した具体例1と同様であるため、図2を援用して説明する。

具体例4の補正データ書き込み手段4は、具体例1における補正データ書き込み手段4の機能を有すると共に、EEPROM2に格納されたLEDヘッド1の歪み・段差データから求めた補正值の変化点と、傾きデータから求めた補正值の変化点が重なり、かつ、その変化点で変化する量が所定値より大きい場合は、傾きデータの変化点をずらして補正值を求める機能を有している。

#### 【0078】

##### 動作

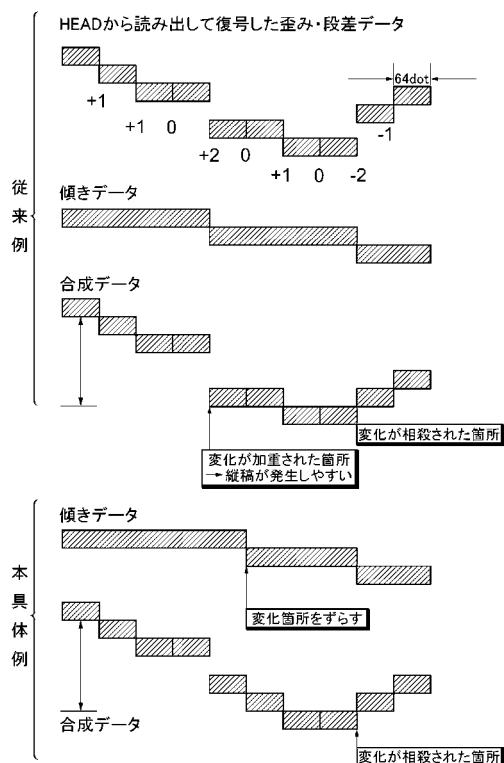

図11は、従来例と本具体例の補正データ作成の説明図である。

10

20

30

40

50

図中の従来例に示すように、傾きデータが右肩下がりに1変化(+1とする)箇所で、LEDヘッド1の歪み段差データは+2すると、合成したデータの変化は加重されるので+3になり、その結果、印刷時に縦縞が発生し易くなる。一方、傾きが+1変化する箇所では、LEDヘッド1の歪み段差データは-2なので合成したデータの変化は相殺されて-1になり、変化が目立たない。

#### 【0079】

ところで、LEDヘッド1の段差はLEDアレイ間のずれであるため、その箇所でしか補正できないが、歪みや傾きは段差に比べもともと変化がなだらかでその箇所でなくても、つまり位置を多少ずらしても問題はない。但し、歪みは段差と一緒にLEDヘッド1内のEEPROM2に格納されるので、歪み成分だけを抽出することは、歪みと段差を別に格納しない限りは困難である。そこで、本具体例では、傾きについて変化が加重される箇所では一つずらす処理を行う。これが図中の本具体例の図示部分であり、変化箇所を一つずらしているため、合成データではその変化が軽減されている。

10

#### 【0080】

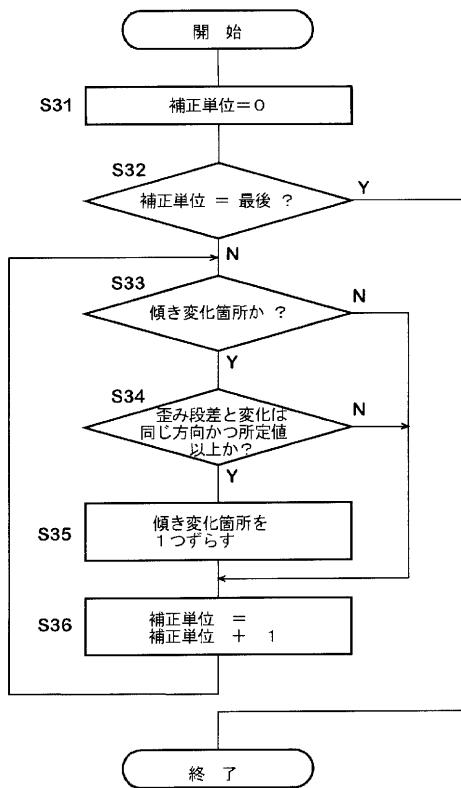

図12は、補正データ書き込み手段4が行う具体例4の処理のフローチャートである。先ず、補正単位(例えば64ドット単位)を0にする(ステップS31)。次に、補正単位がLEDヘッド1の最後( $15360 / 64 = 240$ )かを判断する(ステップS32)。そうであった場合はずらし処理を終了し、最後でなかった場合はステップS33に進み、その補正単位の箇所で傾きが変化しているかを判断する。傾きが変化している箇所であったならば、その傾き変化箇所は、歪み段差と変化が同じ方向でかつ変化する量が所定値以上であるかを判断する(ステップS34)。ここで、歪み段差変化が0である場合は“No”であり、それぞれの変化が+と-または-と+ならば違う方向で相殺されるのでこれも“No”である。これ以外の場合でかつ変化する量が所定値以上の場合が“Yes”でありステップS35に進む。尚、本具体例では所定値として+3としているが、この値は適宜選択が可能である。ステップS35では傾き変化箇所を右に一つずらす(ステップS36)。そして、補正単位を一つ加算してステップS33に戻る。また、ステップS33において、傾き変化箇所ではなかった場合は、そのままステップS36に移行する。

20

#### 【0081】

##### 効果

以上のように具体例4によれば、補正データを生成する処理において、LEDヘッド1の歪み段差データの変化点と傾きデータの変化点が重なった箇所で、変化する量が増える方向の場合は傾きデータの変化点をずらすようにしたので、補正データのずれ量を抑えることができ、その結果、印刷時の縦縞の発生を抑えることができる。

30

#### 【0082】

##### 《具体例5》

具体例5は、補正データの縦解像度が切り替わった場合でも補正RAM5への補正データの変更なしに切替えができるようにしたものである。

即ち、従来では、画像データの解像度が切り替わった場合、補正值の記憶部に格納する補正值を再度設定する必要があった。例えば、縦1200dpiと縦2400dpiである。そこで、本具体例では、補正の対象となる歪み・段差・傾きは全て長さで表される値であるため、一番細かい解像度の補正值を補正RAM5に格納しておき、印刷する解像度に合わせて切替え、再設定を不要としたものである。

40

#### 【0083】

##### 構成

図13は、具体例5によるプリンタの1色あたりの構成図である。

図の装置は、LEDヘッド1、EEPROM2、ヘッド制御部3、補正データ書き込み手段4a、補正RAM5a、ラスタバッファ制御部6c、ラスタバッファRAM7からなる。ここで、補正データ書き込み手段4a、補正RAM5aおよびラスタバッファ制御部6c以外の構成は具体例1と同様であるため、対応する部分に同一符号を付してその説明を省略する。

50

**【 0 0 8 4 】**

補正データ書込み手段 4 a は、具体例 1 の補正データ書込み手段 4 の機能を有すると共に、そのプリンタで使用する縦解像度のうち、最も細かい縦解像度の補正值を補正 R A M 5 に与える機能を有している。本具体例では、最も細かい縦解像度の補正值として 4 8 0 0 d p i の値としている。また、補正 R A M 5 a は、この、最も細かい解像度の補正值を格納するメモリである。

**【 0 0 8 5 】**

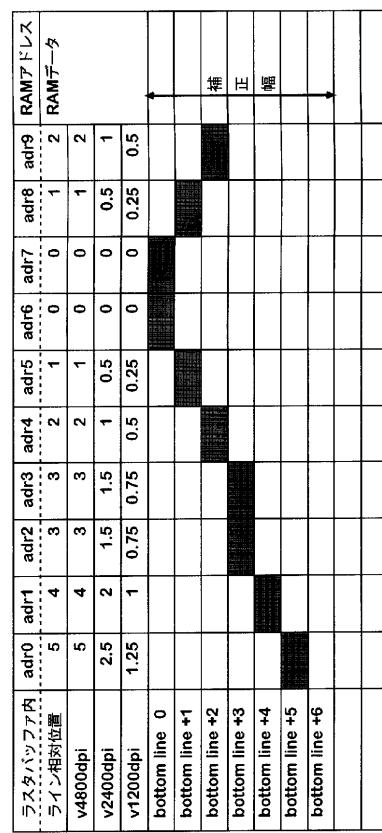

図 14 は、補正 R A M 5 a の補正值格納状態を示すと共に、解像度との関係を示す説明図である。

例えば、アドレス 0 には値 5 が格納されており、これを縦解像度 4 8 0 0 d p i ( v 4 8 0 0 d p i ) ではそのまま 5 、縦解像度 2 4 0 0 d p i では 2 . 5 、縦解像度 1 2 0 0 d p i では 1 . 2 5 に値を桁シフトして用いるものである。 10

**【 0 0 8 6 】**

ラスタバッファ制御部 6 c は、 R D \_ X ポインタ 1 0 1 、 R D \_ Y ポインタ 1 0 2 a 、加算器 1 0 3 、 W R \_ X ポインタ 1 0 4 、 W R \_ Y ポインタ 1 0 5 、縦解像度レジスタ 1 1 2 、丸め回路 1 1 3 を備えている。ここで、 R D \_ Y ポインタ 1 0 2 a 、縦解像度レジスタ 1 1 2 および丸め回路 1 1 3 以外の構成は、具体例 1 と同様であるため、ここでの説明は省略する。

R D \_ Y ポインタ 1 0 2 a は、縦解像度に応じてインクリメントする値を切り替えるポインタであり、縦解像度 4 8 0 0 d p i では + 1 インクリメント、縦解像度 2 4 0 0 d p i では + 2 インクリメント、縦解像度 1 2 0 0 d p i では + 4 インクリメントするよう構成されている。 20

**【 0 0 8 7 】**

縦解像度レジスタ 1 1 2 は、縦解像度を 4 8 0 0 d p i 、 2 4 0 0 d p i 、 1 2 0 0 d p i に切り替えるためのモードレジスタであり、上位のアプリケーション等からそのモードが設定されるよう構成されている。丸め回路 1 1 3 は、加算器 1 0 3 の値を縦解像度レジスタ 1 1 2 のモードにより整数に丸める（小数を含む値を整数値とする）処理を行う回路である。本具体例では、丸め回路 1 1 3 の整数値化処理として小数点以下の値を四捨五入しているが、切り捨てや切り上げによる整数値化であってもよい。

**【 0 0 8 8 】**

30

**動作**

先ず、補正データ書込み手段 4 a は、補正 R A M 5 a への補正值書込み処理として、一番細かい解像度である縦解像度 4 8 0 0 d p i の補正值を書込む。次に図示しない上位のアプリケーション等から縦解像度が縦解像度レジスタ 1 1 2 に指定されると、ラスタバッファ制御部 6 c では、補正 R A M 5 a からの補正值をそのモードに対応した値に桁シフトして加算器 1 0 3 に与え、かつ、 R D \_ Y ポインタ 1 0 2 a は、そのモードに対応したインクリメントを行う。また、丸め回路 1 1 3 は、加算器 1 0 3 からの出力された値に対して、丸め処理を行い、補正されたラインとしてラスタバッファ R A M 7 に与える。例えば、縦解像度 2 4 0 0 d p i の場合、補正 R A M 5 a のアドレス 0 から読出される値は、 2 . 5 であるため、 3 に丸め、ラスタバッファ R A M 7 から 3 ライン目のデータを読出す。縦解像度 1 2 0 0 d p i の場合、補正 R A M 5 a のアドレス 0 から読出される値は 1 . 2 5 であるため、 1 に丸め、ラスタバッファ R A M 7 から 1 ライン目のデータを読出す。 40

**【 0 0 8 9 】****効果**

以上のように、具体例 5 によれば、補正 R A M 5 a への補正值として最も細かい解像度の補正值を格納し、ラスタバッファ制御部 6 c では、印刷する解像度に応じて補正 R A M 5 a に格納された補正值を求め、この補正值と読み出しラインを指定するポインタの値とを加算すると共に、整数値化し、これをラスタバッファ R A M 7 の読み出しラインとして与えるようにしたので、縦解像度が切り替わっても補正 R A M への補正值の再設定が不要となり、解像度の変更にも柔軟に対処することができる。 50

## 【0090】

## 《利用形態》

上記各具体例では、記録ヘッドを複数具備するカラープリンタの場合を説明したが、記録ヘッドが単数であるモノクロプリンタであっても位置補正に関して効果を有する。

## 【0091】

また、上記具体例5では具体例1の構成に基づいて構成したが、具体例2～4に対しても適用可能である。

## 【図面の簡単な説明】

【図1】本発明のプリンタにおける補正方法を示すフローチャートである。

【図2】本発明のプリンタの具体例1の構成図である。

10

【図3】ラスタバッファRAM7のデータ構成例の説明図である。

【図4】補正データの説明図である。

【図5】補正RAM内のデータ構成の説明図である。

【図6】具体例2のプリンタの構成図である。

【図7】具体例2における動作説明図である。

【図8】具体例3のプリンタの構成図である。

【図9】LEDヘッドとレフトマージン／ライトマージンとの関係を示す説明図である。

【図10】具体例3の動作説明図である。

【図11】具体例4の補正データ作成を従来例と比較して示す説明図である。

【図12】具体例4の処理のフローチャートである。

20

【図13】具体例5のプリンタの構成図である。

【図14】具体例5の補正RAMの補正值格納状態を示す説明図である。

## 【符号の説明】

1 LEDヘッド(記録ヘッド)

2 EEPROM

3 ヘッド制御部

4、4a 補正データ書き込み手段

5、5a 補正RAM(補正值記憶部)

6、6a、6b、6c ラスタバッファ制御部

7 ラスタバッファRAM(ラスタバッファ記憶部)

30

8、8a 補正データ読み出制御手段

9 セレクタ(0データ出力手段)

10 ビットシフト回路

101 RD\_Xポインタ

102、102a RD\_Yポインタ

103 加算器

104 WR\_Xポインタ

105 WR\_Yポインタ

106 ページ開始ラインレジスタ

107 ページ終了ラインレジスタ

110 レフトマージンレジスタ

111 ライトマージンレジスタ

112 縦解像度レジスタ

113 丸め回路

40

【図1】

【図2】

【図3】

ラスタバッファRAMのデータ構成例の説明図

【図4】

補正データの説明図

【図5】

補正RAM内のデータ構成の説明図

【図6】

具体例2の構成図

【図7】

具体例2の動作説明図

【図8】

具体例3の構成図

【図9】

各色のLEDヘッドとレフトマージン/ライトマージンとの関係を示す説明図

【図10】

具体例3の動作説明図

【図11】

従来と具体例4の補正データ作成の説明図

【図12】

具体例4の処理フローチャート

【図13】

【図14】

具体例5の補正RAMの補正值格納状態の説明図

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

B41J 5/30

B41J 2/44

B41J 2/45

B41J 2/455