|                                     |                        |

|-------------------------------------|------------------------|

| <b>DOMANDA DI INVENZIONE NUMERO</b> | <b>102022000008348</b> |

| <b>Data Deposito</b>                | <b>27/04/2022</b>      |

| <b>Data Pubblicazione</b>           | <b>27/10/2023</b>      |

Classifiche IPC

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

|----------------|---------------|--------------------|---------------|--------------------|

| G              | 11            | C                  | 29            | 02                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

| G              | 11            | C                  | 11            | 56                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

| G              | 11            | C                  | 16            | 04                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

| G              | 11            | C                  | 16            | 10                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

| G              | 11            | C                  | 29            | 12                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

| G              | 11            | C                  | 29            | 24                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

| G              | 11            | C                  | 29            | 44                 |

Titolo

DISPOSITIVO DI MEMORIA 3D

## DESCRIZIONE

### Sfondo tecnologico dell'invenzione

#### **Campo dell'invenzione**

La presente invenzione si riferisce in generale al campo dei dispositivi di memoria. In particolare, la presente invenzione si riferisce ad un dispositivo di memoria a stato solido. 5 Più in particolare, la presente invenzione si riferisce ad un dispositivo di memoria tridimensionale (3D) che presenta rapidi tempi di programmazione.

#### **Panoramica del relativo stato della tecnica**

Un convenzionale dispositivo di memoria 3D comprende una pluralità di stringhe di 10 celle di memoria. Ciascuna stringa di celle di memoria tipicamente comprende una pluralità di celle di memoria impilate l'una sull'altra su un substrato ciascuno ad una rispettiva distanza verticale dal substrato.

Le celle di memoria sono programmabili per memorizzare ciascuna un livello logico tra una pluralità di livelli logici.

15 Ciascuna cella di memoria tipicamente comprende un transistore MOS con una struttura ad intrappolamento di carica (“charge trap”) o con una struttura a gate flottante (“floating gate”) (da qui in avanti, transistore di memoria), ovvero comprende un terminale di drain, un terminale di source, un terminale di controllo (control gate), ed una regione di controllo sepolta in uno strato di ossido in modo da essere elettricamente isolata. Ad 20 esempio, la regione di controllo può comprendere nitruro di silicio (struttura ad intrappolamento di carica) o silicio policristallino drogato (struttura a gate flottante).

Un livello logico è fisicamente memorizzato in ciascuna cella di memoria in forma di carica elettrica nella regione di controllo: una variazione di carica elettrica nella regione di controllo definisce una corrispondente variazione di una tensione di soglia del transistore di memoria. Tale variazione della tensione di soglia determina, durante un'operazione di lettura di una cella di memoria selezionata, una corrispondente modulazione di una corrente di canale attraverso il transistore di memoria, il cui valore rappresenta il livello logico memorizzato nella cella di memoria. 25

Ciascuna cella di memoria può essere una cella di memoria a singolo livello, ovvero

una cella di memoria in grado di memorizzare un bit (ovvero, livello logico 0 o 1), o una cella di memoria multilivello, ovvero una cella di memoria in grado di memorizzare due bit (ovvero, livello logico 00, 01, 10, o 11), tre bit (ovvero, livello logico 000, 001, 010, 011, 100, 101, 110 o 111), o più bit.

5 In accordo con una comune implementazione, una cella di memoria selezionata è programmata ad un livello logico obiettivo (o, equivalentemente, ad una tensione di soglia obiettivo) sulla base della tecnica ISPP (“*Incremental Step Pulse Programming*”).

10 In accordo con la tecnica ISPP, una sequenza di impulsi di programmazione a passo incrementale è applicata alla cella di memoria selezionata. La sequenza di impulsi di programmazione a passo incrementale (da qui in avanti concisamente indicata come sequenza di impulsi di programmazione) comprende una sequenza di brevi impulsi (di tensione) di programmazione successivi di ampiezza gradualmente crescente sulla base di gradini di tensione (“gradino di tensione ISPP”). Per compensare variazioni della dimensione delle celle di memoria in ciascuna stringa di celle di memoria, che altrimenti determinerebbe una variabilità del tempo di programmazione nelle rispettive celle di memoria, può essere fornito un certo numero di gradini di tensione ISPP, in cui ciascun gradino di tensione ISPP è associato ad un rispettivo gruppo di celle di memoria (da qui in avanti, gruppo ISPP di celle di memoria).

20 In accordo con la tecnica ISPP, una pluralità di operazioni di verifica della programmazione è eseguita per verificare se la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo.

25 Per ciascuna tensione di soglia obiettivo, l’applicazione dell’impulso di programmazione e la successiva operazione di verifica della programmazione sono ripetute fino a che la tensione di soglia della cella di memoria selezionata supera una corrispondente tensione di verifica della programmazione indicativa che la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo.

30 Per ottimizzare i tempi di programmazione, l’impulso di programmazione dal quale l’operazione di verifica della programmazione è avviata (da qui in avanti indicato come impulso di programmazione di avvio PV (“*Program Verify*”)) è tipicamente variabile tra le tensioni di soglia obiettivo.

Gli impulsi di programmazione di avvio PV associati a (tutte) le tensioni di soglia obiettivo a cui ciascuna cella di memoria può essere programmata sono indicati, nel

complesso, come schema PV (“*Program Verify*”).

### **Sommario dell'invenzione**

La Richiedente ha compreso che i dispositivi di memoria 3D convenzionali, ed in particolare gli schemi PV convenzionali su cui essi sono basati, possono essere non soddisfacenti quando sono richiesti tempi di programmazione molto rapidi.

Secondo la Richiedente, ciò è essenzialmente dovuto al fatto che, per ciascuna tensione di soglia obiettivo, l'impulso di programmazione di avvio PV è un impulso di programmazione predefinito tipicamente determinato durante una fase di caratterizzazione sulla base della cella di memoria, tra le celle di memoria del gruppo ISPP di celle di memoria, aventi tempi di programmazione più veloci (da qui in avanti, cella di memoria più veloce): infatti, per ciascun gruppo ISPP di celle di memoria, l'impulso di programmazione di avvio PV è tipicamente determinato come l'impulso di programmazione che precede, con un margine predefinito, un impulso di programmazione finale della cella di memoria più veloce del gruppo ISPP di celle di memoria.

Pertanto, gli schemi PV convenzionali prevedono impulsi di programmazione di avvio PV fissi per tutte le celle di memoria appartenenti ad uno stesso gruppo ISPP di celle di memoria.

La Richiedente ha compreso che gli schemi PV convenzionali prevedono operazioni di verifica della programmazione non necessarie per celle di memoria più lente del gruppo ISPP di celle di memoria, il che implica tempi di programmazione più lenti.

La Richiedente ha affrontato le problematiche sopra menzionate, ed ha escogitato un dispositivo di memoria 3D in grado di determinare schemi PV efficienti capaci di ridurre i tempi di programmazione.

Uno o più aspetti della presente invenzione sono esposti nelle rivendicazioni indipendenti, con caratteristiche vantaggiose della stessa invenzione che sono indicate nelle rivendicazioni dipendenti, la cui formulazione è qui allegata alla lettera per riferimento (con qualsiasi caratteristica vantaggiosa fornita con riferimento ad uno specifico aspetto della presente invenzione che si applica mutatis mutandis a qualsiasi altro aspetto).

Più specificamente, un aspetto della presente invenzione si riferisce ad un dispositivo di memoria tridimensionale. Il dispositivo di memoria tridimensionale può comprendere una pluralità di stringhe di celle di memoria; ciascuna stringa di celle di memoria può

comprendere una pluralità di celle di memoria impilate l'una sull'altra su un substrato ciascuna ad una rispettiva distanza verticale dal substrato. Il dispositivo di memoria tridimensionale può comprendere una pluralità di word line ciascuna associata a rispettive celle di memoria della pluralità di stringhe di celle di memoria disposte ad una stessa 5 distanza verticale dal substrato. Il dispositivo di memoria tridimensionale può comprendere un circuito di controllo configurato per:

(i) applicare una sequenza di impulsi di programmazione a passo incrementale ad una cella di memoria selezionata di una stringa di celle di memoria di riferimento per programmare la cella di memoria selezionata ad una tensione di soglia obiettivo tra una 10 pluralità di tensioni di soglia obiettivo;

(ii) eseguire operazioni di verifica della programmazione in risposta ad un rispettivo impulso di programmazione dopo l'applicazione di un primo impulso di programmazione della sequenza di impulsi di programmazione a passo incrementale, il primo impulso di programmazione per un avvio delle operazioni di verifica della programmazione essendo un 15 impulso di programmazione predefinito determinato dal dispositivo di memoria tridimensionale.

Il circuito di controllo può essere ulteriormente configurato per:

(iii) determinare un primo impulso di programmazione aggiornato per la cella di memoria selezionata e per la tensione di soglia obiettivo sulla base di un secondo impulso 20 di programmazione indicativo che la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo, e

(iv) eseguire le operazioni di verifica della programmazione a partire dal primo impulso di programmazione aggiornato per ciascuna cella di memoria successivamente selezionata da programmare alla tensione di soglia obiettivo ed associata alla stessa word 25 della cella di memoria selezionata.

In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, il circuito di controllo è configurato per ripetere i passi (i), (ii), (iii) e (iv) per ciascuna tensione di soglia obiettivo tra la pluralità di tensioni di soglia obiettivo.

30 In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, il primo impulso di programmazione aggiornato precede, nella sequenza di impulsi di programmazione a passo

incrementale, il secondo impulso di programmazione di un numero predefinito di impulsi di programmazione.

5 In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, il numero predefinito di impulsi di programmazione è lo stesso per ciascun gruppo di celle di memoria aventi uno stesso gradino di tensione incrementale tra impulsi di programmazione successivi.

10 In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, il circuito di controllo è configurato per eseguire le operazioni di verifica della programmazione a partire dal primo impulso di programmazione predefinito aggiornato per ciascuna cella di memoria successivamente selezionata associata alla stessa word line della cella di memoria selezionata e per ciascuna cella di memoria successivamente selezionata associata ad almeno una word line diversa da detta stessa word line.

15 In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, l'almeno una word line diversa da detta stessa word line comprende almeno una word line adiacente che è adiacente a detta stessa word line.

20 In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, il dispositivo di memoria tridimensionale comprende una pluralità di blocchi di memoria ciascuno comprendente un sottoinsieme della pluralità di stringhe di celle di memoria.

25 In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, la stringa di celle di memoria di riferimento comprende, per ciascun blocco di memoria, una stringa iniziale di celle di memoria del blocco di memoria o una stringa di celle di memoria programmata per prima nel blocco di memoria.

30 In accordo con una forma di realizzazione, le cui caratteristiche possono essere aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, il circuito di controllo è configurato per ripetere i passi (i), (ii), (iii) e (iv) per ciascuna di almeno una ulteriore cella di memoria selezionata della stringa di celle di memoria di riferimento.

In accordo con una forma di realizzazione, le cui caratteristiche possono essere

aggiuntive o alternative ad una qualsiasi delle precedenti caratteristiche, ciascuna delle celle di memoria è una cella di memoria a singolo livello o una cella di memoria multilivello.

Un altro aspetto della presente invenzione si riferisce ad un sistema elettronico comprendente almeno un dispositivo di memoria tridimensionale di cui sopra.

5 Un ulteriore aspetto della presente invenzione si riferisce ad un metodo per far operare un dispositivo di memoria tridimensionale. Il dispositivo di memoria tridimensionale può comprendere una pluralità di stringhe di celle di memoria ciascuna comprendente una pluralità di celle di memoria impilate l'una sull'altra su un substrato ciascuna ad una rispettiva distanza verticale dal substrato, ed una pluralità di word line 10 ciascuna associata a rispettive celle di memoria della pluralità di stringhe di celle di memoria disposte ad una stessa distanza verticale dal substrato. Il metodo può comprendere:

15 (i) applicare una sequenza di impulsi di programmazione a passo incrementale ad una cella di memoria selezionata di una stringa di celle di memoria di riferimento per programmare la cella di memoria selezionata ad una tensione di soglia obiettivo tra una pluralità di tensioni di soglia obiettivo;

20 (ii) eseguire operazioni di verifica della programmazione in risposta ad un rispettivo impulso di programmazione dopo l'applicazione di un primo impulso di programmazione della sequenza di impulsi di programmazione a passo incrementale, il primo impulso di programmazione per un avvio delle operazioni di verifica della programmazione essendo un impulso di programmazione predefinito determinato dal dispositivo di memoria tridimensionale;

25 (iii) determinare un primo impulso di programmazione aggiornato per la cella di memoria selezionata e per la tensione di soglia obiettivo sulla base di un secondo impulso di programmazione indicativo che la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo, e

30 (iv) eseguire le operazioni di verifica della programmazione a partire dal primo impulso di programmazione aggiornato per ciascuna cella di memoria successivamente selezionata da programmare alla tensione di soglia obiettivo ed associata alla stessa word line della cella di memoria selezionata.

### **Breve descrizione dei disegni annessi**

Queste ed altre caratteristiche e vantaggi della presente invenzione risulteranno

evidenti dalla seguente descrizione di alcune forme di realizzazione esemplificative e non limitative della stessa; per una sua migliore intelligenza, la descrizione che segue dovrebbe essere letta facendo riferimento ai disegni allegati, in cui:

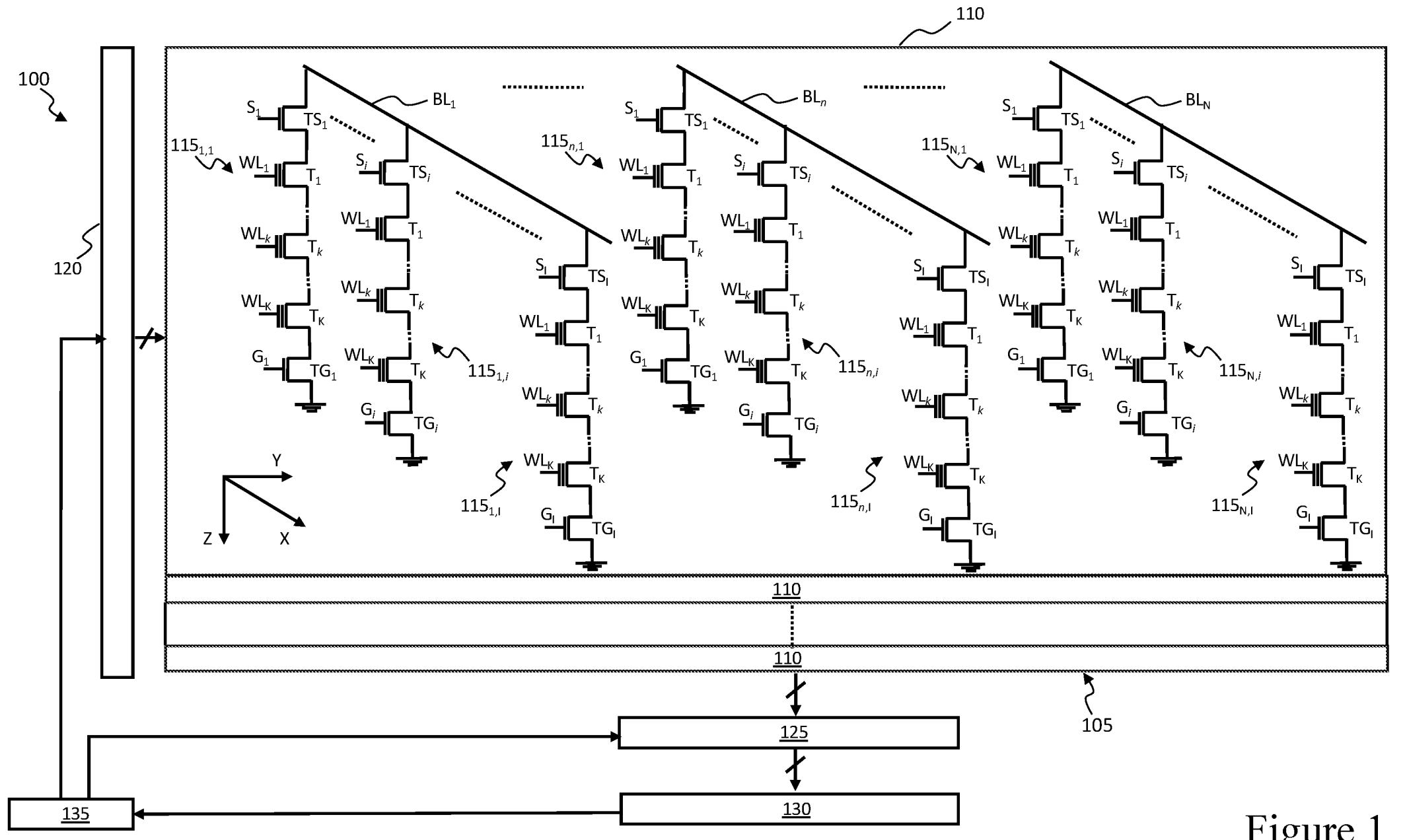

la **Figura 1** mostra schematicamente un dispositivo di memoria tridimensionale in

5 accordo con una forma di realizzazione della presente invenzione;

la **Figura 2A** mostra un esemplificativo schema di verifica della programmazione per celle di memoria TLC, in accordo con una forma di realizzazione della presente invenzione;

la **Figura 2B** mostra uno schema di verifica della programmazione predefinito per

10 le celle di memoria TLC, in accordo con una forma di realizzazione della presente invenzione;

la **Figura 2C** mostra uno schema di verifica della programmazione aggiornato in accordo con una forma di realizzazione della presente invenzione;

la **Figura 3** mostra un diagramma di attività di un metodo in accordo con una forma

15 di realizzazione della presente invenzione, e

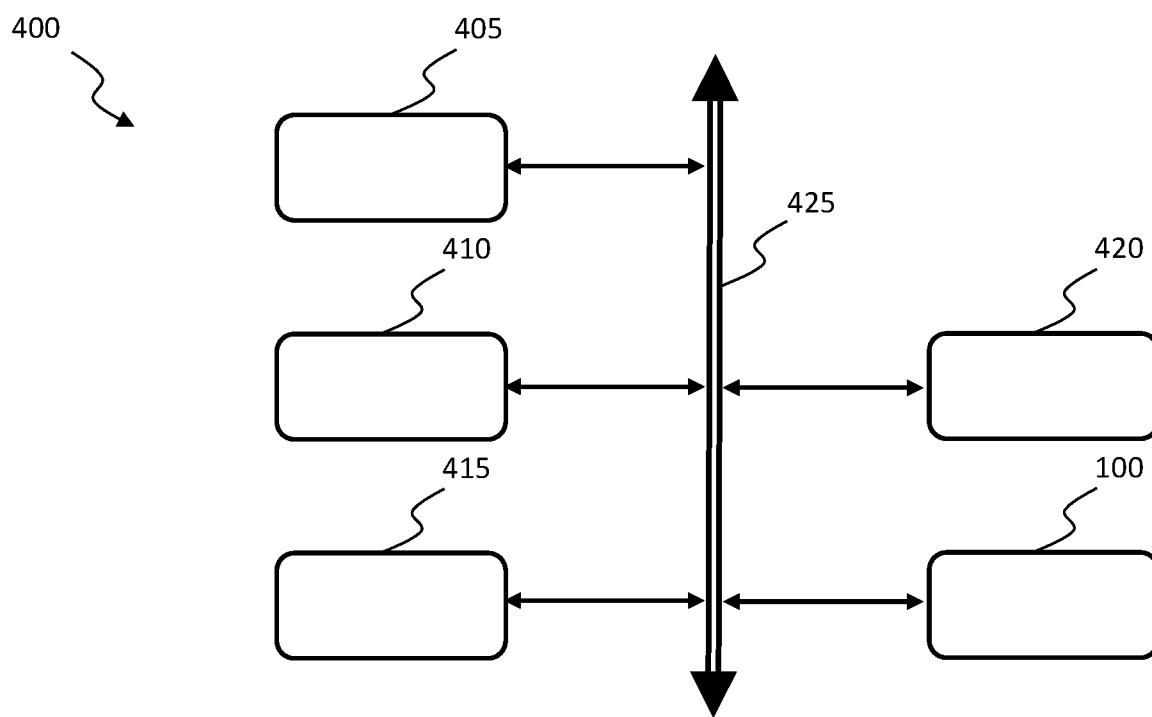

la **Figura 4** mostra uno schema a blocchi semplificato di un sistema elettronico in accordo con una forma di realizzazione della presente invenzione.

### **Descrizione dettagliata di forme di realizzazione preferite dell'invenzione**

20 La **Figura 1** mostra schematicamente un dispositivo di memoria tridimensionale (3D) **100** in accordo con una forma di realizzazione della presente invenzione.

Nel seguito, caratteristiche introdotte dalla dicitura “in accordo con una forma di realizzazione”, esse devono essere intese come caratteristiche aggiuntive o alternative ad una qualsiasi caratteristica precedentemente introdotta, a meno di indicazione contraria e/o

25 a meno che vi sia una evidente incompatibilità tra combinazioni di caratteristiche.

Nel seguito, saranno mostrati e discussi solo elementi ed operazioni ritenuti rilevanti per la comprensione della presente invenzione, con altri elementi ed operazioni ben noti che saranno intenzionalmente omessi per brevità.

Il dispositivo di memoria 3D **100** comprende un array di memoria **105**.

30 In accordo con una forma di realizzazione, l'array di memoria **105** comprende una pluralità di blocchi di memoria **110**.

In accordo con una forma di realizzazione, ciascun blocco di memoria **110**

comprende una pluralità di stringhe di celle di memoria  $\mathbf{115}_{n,i}$  ( $n = 1, 2, \dots N$ ;  $i = 1, 2, \dots I$ ). La pluralità di stringhe di celle di memoria  $\mathbf{115}_{n,i}$  di un generico blocco di memoria  $\mathbf{110}$  sono illustrate nella figura in una vista tridimensionale con riferimento agli assi  $\mathbf{X}, \mathbf{Y}, \mathbf{Z}$  reciprocamente ortogonali.

5 In accordo con una forma di realizzazione, ciascuna stringa di celle di memoria  $\mathbf{115}_{n,i}$  comprende una pluralità di celle di memoria  $\mathbf{T}_k$  ( $k=1, 2, \dots K$ ) impilate l'una sull'altra su un substrato (non mostrato) ciascuna ad una rispettiva distanza verticale (ovvero, la distanza lungo l'asse  $\mathbf{Z}$ ) dal substrato.

10 In accordo con una forma di realizzazione, le celle di memoria  $\mathbf{T}_k$  di ciascuna stringa di celle di memoria  $\mathbf{115}_{n,i}$  sono connesse in serie l'un l'altra (stringa di celle di memoria NAND).

In accordo con una forma di realizzazione, ciascuna cella di memoria  $\mathbf{T}_k$  è programmabile per memorizzare ciascuna un livello logico tra una pluralità di livelli logici.

15 In accordo con una forma di realizzazione, ciascuna cella di memoria  $\mathbf{T}_k$  comprende un transistore MOS con una struttura ad intrappolamento di carica (“*charge trap*”) o con struttura a gate flottante (“*floating gate*”) (da qui in avanti, transistore di memoria), ovvero comprende un terminale di drain, un terminale di source, un terminale di controllo (gate di controllo), ed una regione di controllo sepolta in uno strato di ossido in modo da essere elettricamente isolata. La regione di controllo può comprendere nitruro di silicio (struttura 20 ad intrappolamento di carica) o silicio policristallino drogato (struttura a gate flottante).

25 Un livello logico è fisicamente memorizzato in ciascuna cella di memoria  $\mathbf{T}_k$  in forma di carica elettrica nella regione di controllo: una variazione di carica elettrica nella regione di controllo definisce una corrispondente variazione di una tensione di soglia del transistore di memoria. Tale variazione della tensione di soglia determina, durante un'operazione di lettura di una cella di memoria selezionata, una corrispondente modulazione di una corrente di canale attraverso il transistore di memoria, il cui valore rappresenta il livello logico memorizzato nella cella di memoria  $\mathbf{T}_k$ .

30 Durante un'operazione di programmazione, avviene un'iniezione di cariche elettriche nella regione di controllo per effetto “*Fowler-Nordheim tunneling*” (struttura a gate flottante) o per effetto “*Hot Carrier Injection*” (struttura ad intrappolamento di carica): in accordo con gli effetti “*Fowler-Nordheim tunneling*” / “*Hot Carrier Injection*”, un campo elettrico tra la gate di controllo ed il terminale di drain del transistore di memoria consente

alle cariche elettriche di passare attraverso lo strato di ossido e raggiungere la regione di controllo.

In accordo con una forma di realizzazione, ciascuna cella di memoria  $T_k$  può essere una cella di memoria a singolo livello, ovvero una cella di memoria in grado di memorizzare 5 un bit. Ciascuna cella di memoria a singolo livello è programmabile per memorizzare un livello logico tra due livelli logici (ovvero, 0 e 1).

In accordo con una forma di realizzazione, ciascuna cella di memoria  $T_k$  può essere una cella di memoria multilivello, ovvero una cella di memoria in grado di memorizzare due o più bit.

10 Considerando, solo come esempio, una cella di memoria multilivello in grado di memorizzare due bit, la cella di memoria multilivello può essere programmabile per memorizzare un livello logico tra quattro livelli logici (ovvero, 00, 01, 10, e 11).

15 Considerando, solo come altro esempio, una cella di memoria multilivello in grado di memorizzare tre bit, la cella di memoria multilivello (cui solitamente ci si riferisce come cella di memoria TLC (“*Triple-Level Cell*”)) può essere programmabile per memorizzare un 20 livello logico tra otto livelli logici (ovvero, 000, 001, 010, 011, 100, 101, 110 e 111).

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende una pluralità di word line  $WL_k$  ( $k=1, 2, \dots, K$ ) ciascuna associata a rispettive 25 celle di memoria della pluralità di stringhe di celle di memoria  $115_{n,i}$  disposte ad una stessa distanza verticale dal substrato (ovvero, le celle di memoria disposte su uno stesso  $k$ -esimo piano **X-Y**).

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende, lungo l’asse **Y**, una pluralità di bit line  $BL_n$  ( $n = 1, 2, \dots, N$ ) ciascuna associata ad un corrispondente insieme di stringhe di celle di memoria  $115_{n,i}$ , ovvero con la bit line  $BL_1$  che è associata all’insieme di stringhe di celle di memoria  $115_{1,1}, 115_{1,i}, 115_{1,I}$ , con la bit line  $BL_n$  che è associata all’insieme di stringhe di celle di memoria  $115_{n,1}, 115_{n,i}, 115_{n,I}$ , e con la bit line  $BL_N$  che è associata all’insieme di stringhe di celle di memoria  $115_{N,1}, 115_{N,i}, 115_{N,I}$ .

30 In accordo con una forma di realizzazione, ciascuna stringa di celle di memoria  $115_{n,i}$  è elettricamente accoppiata tra la bit line  $BL_n$  associata ed una linea di massa che fornisce un potenziale elettrico di massa (o terra) (come 0 V, come è usuale nei circuiti elettronici).

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100**

comprende una pluralità di transistori di selezione di stringa  $TS_i$ . In accordo con una forma di realizzazione, ciascuna stringa di celle di memoria  $115_{n,i}$  è associata ad un rispettivo transistore di selezione di stringa  $TS_i$  per accoppiare selettivamente la (le celle di memoria  $T_k$  della) stringa di celle di memoria  $115_{n,i}$  alla rispettiva bit line  $BL_n$ . In accordo con una forma di realizzazione, ciascuna stringa di celle di memoria  $115_{n,i}$  è elettricamente connessa 5 alla bit line  $BL_n$  associata attraverso il rispettivo transistore di selezione di stringa  $TS_i$ .

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende una pluralità di transistori di selezione di massa  $TG_i$ . In accordo con una forma di realizzazione, ciascuna stringa di celle di memoria  $115_{n,i}$  è associata ad un rispettivo 10 transistore di selezione di massa  $TG_i$  per selettivamente accoppiare la (le celle di memoria  $T_k$  della) stringa di celle di memoria  $115_{n,i}$  alla linea di massa. In accordo con una forma di realizzazione, ciascuna stringa di celle di memoria  $115_{n,i}$  è elettricamente connessa alla linea di massa associata attraverso il rispettivo transistore di selezione di massa  $TG_i$ .

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende una pluralità di linee di selezione di stringa  $S_i$  ciascuna per selezionare i rispettivi 15 transistori di selezione di stringa  $TS_i$ , ed una pluralità di linee di selezione di massa  $G_i$  ciascuna per selezionare i rispettivi transistori di selezione di massa  $TG_i$ .

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende un circuito di selezione di word line **120** per selezionare una o più word line tra 20 la pluralità di word line  $WL_k$  in accordo con un indirizzo di riga.

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende un circuito di selezione di bit line **125** per selezionare una o più bit line tra la pluralità di bit line  $BL_n$  in accordo con un indirizzo di colonna.

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende un circuito di selezione di stringa/massa (non mostrato) per selezionare una o 25 più linee di selezione di stringa tra la pluralità di linee di selezione di stringa  $S_i$  e/o una o più linee di selezione di massa tra la pluralità di linee di selezione di massa  $G_i$ .

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende a circuito di lettura **130** per leggere il livello logico di (ovvero, memorizzato in) 30 una cella di memoria selezionata  $T_k$ .

In accordo con una forma di realizzazione, il circuito di lettura **130** è configurato per leggere il livello logico della cella di memoria selezionata in accordo con una corrente

elettrica che scorre attraverso la bit line **BL<sub>n</sub>** associata alla cella di memoria selezionata **T<sub>k</sub>**.

In accordo con una forma di realizzazione, il dispositivo di memoria 3D **100** comprende un circuito di controllo (da qui in avanti, controllore della memoria) **135** configurato per controllare un funzionamento complessivo del dispositivo di memoria 3D **100**. Come concettualmente rappresentato nella figura mediante rispettive connessioni a freccia, il controllore della memoria **135** può essere configurato per fornire l'indirizzo di riga al circuito di selezione di word line **120**, per fornire l'indirizzo di colonna al circuito di selezione di bit line **125**, per fornire un indirizzo della stringa di celle di memoria **115<sub>n,j</sub>** e per ricevere il livello logico letto dal circuito di lettura **130**.

In accordo con una forma di realizzazione, il controllore della memoria **135** è configurato per programmare una cella di memoria selezionata di una stringa di celle di memoria selezionata ad un livello logico obiettivo (o, equivalentemente, ad una tensione di soglia obiettivo) sulla base della tecnica ISPP (*“Incremental Step Pulse Programming”*).

In accordo con la tecnica ISPP, una sequenza di impulsi di programmazione a passo incrementale è applicata (ad esempio, dal o sotto il controllo del controllore della memoria **135**) alla cella di memoria selezionata **T<sub>k</sub>**. In accordo con una forma di realizzazione, la sequenza di impulsi di programmazione a passo incrementale (da qui in avanti concisamente indicata come sequenza di impulsi di programmazione) comprende una sequenza di brevi impulsi (di tensione) di programmazione successivi di ampiezza gradualmente crescente sulla base di gradini di tensione. L'ampiezza di questo “gradino” (ovvero, l'incremento di ampiezza di ciascun impulso di programmazione rispetto all'impulso di programmazione immediatamente precedente nella sequenza, o, equivalentemente, l'incremento di ampiezza tra impulsi di programmazione successivi nella sequenza) è qui indicato come “gradino di tensione ISPP”. Senza perdere di generalità, in implementazioni pratiche del dispositivo di memoria 3D **100**, può essere previsto un certo numero di gradini di tensione ISPP, ciascun gradino di tensione ISPP essendo associato ad un rispettivo gruppo di celle di memoria (nel seguito, ciascun gruppo di celle di memoria associato ad un rispettivo gradino di tensione ISPP sarà indicato come gruppo ISPP di celle di memoria): solo come esempio, differenti gradini di tensione ISPP per differenti gruppi ISPP di celle di memoria possono consentire di compensare variazioni nelle dimensioni delle celle di memoria in ciascuna stringa di celle di memoria (ovvero, lungo l'asse **Z**), che altrimenti determinerebbero una variabilità del tempo di programmazione tra le rispettive celle di memoria.

In accordo con la tecnica ISPP, una pluralità di operazioni di verifica della programmazione è eseguita (ad esempio, dal o sotto il controllo del controllore della memoria **135**) per verificare se la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo.

5 Come visibile in **Figura 2A**, la quale mostra un esemplificativo schema di verifica della programmazione (da qui in avanti, schema PV) risultante dall'applicazione della tecnica ISPP per programmare una o più celle di memoria TLC, per ciascuna tensione di soglia obiettivo  $V_{th_h}$  ( $h=1, 2, \dots, 7$ ), ciascuna operazione di verifica della programmazione (denotata mediante PV nella figura) è eseguita dopo un rispettivo impulso di

10 programmazione della sequenza di impulsi di programmazione  $P_1-P_{22}$  ( $P_1$  essendo un impulso di programmazione iniziale della sequenza di impulsi di programmazione), a partire da un primo impulso di programmazione (nell'esemplificativo schema PV, l'impulso di programmazione  $P_1, P_5, P_7, P_{10}, P_{12}, P_{15}, P_{17}$  per la tensione di soglia obiettivo  $V_{th_1}, V_{th_2}, V_{th_3}, V_{th_4}, V_{th_5}, V_{th_6}, V_{th_7}$ , rispettivamente) ad un secondo impulso di programmazione

15 (nell'esemplificativo schema PV, l'impulso di programmazione  $P_9, P_{12}, P_{14}, P_{16}, P_{19}, P_{21}, P_{22}$  per la tensione di soglia obiettivo  $V_{th_1}, V_{th_2}, V_{th_3}, V_{th_4}, V_{th_5}, V_{th_6}, V_{th_7}$ , rispettivamente), in cui, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , l'operazione di verifica della programmazione eseguita dopo il corrispondente secondo impulso di programmazione determina che la cella di memoria selezionata è stata programmata alla tensione di soglia

20 obiettivo  $V_{th_h}$ .

In altre parole, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , l'applicazione dell'impulso di programmazione e la successiva operazione di verifica della programmazione sono ripetute dal rispettivo primo impulso di programmazione fino a che

25 la tensione di soglia della cella di memoria selezionata supera una corrispondente tensione di verifica della programmazione indicativa che la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo  $V_{th_h}$ .

In accordo con una forma di realizzazione, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , il corrispondente primo impulso di programmazione rappresenta l'impulso di programmazione dal quale l'operazione di verifica della programmazione è avviata (ragione per cui, nel seguito, esso sarà indicato come impulso di programmazione di avvio PV (“*Program Verify*”)).

In accordo con una forma di realizzazione, per ciascuna tensione di soglia obiettivo

$V_{th_h}$ , il corrispondente secondo impulso di programmazione rappresenta l'impulso di programmazione dopo il quale l'operazione di verifica della programmazione è terminata, ovvero l'impulso di programmazione in risposta al quale la rispettiva operazione di verifica della programmazione determina che la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo  $V_{th_h}$  e, quindi, la fine della sequenza di impulsi di programmazione (detto in altro modo, il corrispondente secondo impulso di programmazione rappresenta, per la tensione di soglia obiettivo  $V_{th_h}$ , un impulso di programmazione finale della sequenza di impulsi di programmazione a partire dall'impulso di programmazione iniziale  $P_1$ ).

10 Nell'esempio illustrato di **Figura 2A**:

- quando si considera la tensione di soglia obiettivo  $V_{th_1}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_9$ , quindi una sequenza di nove impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e nove operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_1$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th_1}$ ;

15 - quando si considera la tensione di soglia obiettivo  $V_{th_2}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_{12}$ , quindi una sequenza di dodici impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  ed otto operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_1$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th_2}$ ;

20 - quando si considera la tensione di soglia obiettivo  $V_{th_3}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_{14}$ , quindi una sequenza di quattordici impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  ed otto operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_1$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th_3}$ ;

25 - quando si considera la tensione di soglia obiettivo  $V_{th_4}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_{16}$ , quindi una sequenza di sedici impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e sette operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_1$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th_4}$ ;

30 - quando si considera la tensione di soglia obiettivo  $V_{th_5}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_{18}$ , quindi una sequenza di dieci impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e tre operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_1$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th_5}$ ;

sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th4}$ ;

5 - quando si considera la tensione di soglia obiettivo  $V_{th5}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_{19}$ , quindi una sequenza di diciannove impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  ed otto operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_{12}$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th5}$ ;

10 - quando si considera la tensione di soglia obiettivo  $V_{th6}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_{21}$ , quindi una sequenza di ventuno impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e sette operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_{15}$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th6}$ , e

15 - quando si considera la tensione di soglia obiettivo  $V_{th7}$ , l'impulso di programmazione finale è l'impulso di programmazione  $P_{22}$ , quindi una sequenza di ventidue impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e sei operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_{17}$  sono stati necessari per programmare la cella di memoria selezionata alla tensione di soglia obiettivo  $V_{th7}$ .

20 In accordo con una forma di realizzazione, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , l'impulso di programmazione di avvio PV è un impulso di programmazione predefinito determinato durante una fase di caratterizzazione. In maniera simile ad un approccio convenzionale, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , l'impulso di programmazione di avvio PV può essere determinato, per ciascun gruppo ISPP di celle di memoria, sulla base della cella di memoria, tra le celle di memoria del gruppo ISPP di celle di memoria, avente tempi di programmazione più veloci (da qui in avanti, cella di memoria più veloce): solo come esempio, per ciascun gruppo ISPP di celle di memoria, l'impulso di programmazione di avvio PV può essere determinato come l'impulso di programmazione che precede, con un margine predefinito, l'impulso di programmazione finale della cella di memoria più veloce del gruppo ISPP di celle di memoria.

30 La **Figura 2B** mostra un esemplificativo schema PV (da qui in avanti indicato come

schema PV veloce) associato alla cella di memoria più veloce di un gruppo ISPP di celle di memoria. Come menzionato sopra, in accordo con l'approccio convenzionale, per ciascuna tensione di soglia  $V_{th_h}$  l'impulso di programmazione finale associato alla cella di memoria più veloce di ciascun gruppo ISPP di celle di memoria è utilizzato per determinare (per 5 quella tensione di soglia  $V_{th_h}$ ) l'impulso di programmazione di avvio PV per tutte le celle di memoria di quel gruppo ISPP di celle di memoria.

Nell'esempio illustrato della **Figura 2B**:

- quando si considera la tensione di soglia obiettivo  $V_{th_1}$ , l'impulso di programmazione  $P_7$  è l'impulso di programmazione finale della cella di memoria più veloce, 10 quindi una sequenza di sette impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e sette operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_1$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th_1}$ ;

- quando si considera la tensione di soglia obiettivo  $V_{th_2}$ , l'impulso di programmazione  $P_{10}$  è l'impulso di programmazione finale della cella di memoria più veloce, quindi una sequenza di dieci impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e sei operazioni di verifica della programmazione a partire 15 dall'impulso di programmazione di avvio PV  $P_5$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th_2}$ ;

- quando si considera la tensione di soglia obiettivo  $V_{th_3}$ , l'impulso di programmazione  $P_{12}$  è l'impulso di programmazione finale della cella di memoria più veloce, quindi una sequenza di dodici impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e otto operazioni di verifica della programmazione a partire 20 dall'impulso di programmazione di avvio PV  $P_7$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th_3}$ ;

- quando si considera la tensione di soglia obiettivo  $V_{th_4}$ , l'impulso di programmazione  $P_{14}$  è l'impulso di programmazione finale, quindi una sequenza di quattordici impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e cinque operazioni di verifica della programmazione a partire dall'impulso di programmazione di 25 avvio PV  $P_{10}$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th_4}$ ;

- quando si considera la tensione di soglia obiettivo  $V_{th_5}$ , l'impulso di programmazione  $P_{16}$  è l'impulso di programmazione finale, quindi una sequenza di dieci impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e dieci operazioni di verifica della programmazione a partire 30 dall'impulso di programmazione di avvio PV  $P_{15}$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th_5}$ ;

- quando si considera la tensione di soglia obiettivo  $V_{th_6}$ , l'impulso di programmazione  $P_{18}$  è l'impulso di programmazione finale, quindi una sequenza di sei impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e sei operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_{17}$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th_6}$ ;

programmazione  $P_{17}$  è l'impulso di programmazione finale, quindi una sequenza di diciassette impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e sei operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_{12}$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th5}$ ;

5 - quando si considera la tensione di soglia obiettivo  $V_{th6}$ , l'impulso di programmazione  $P_{19}$  è l'impulso di programmazione finale, quindi una sequenza di diciannove impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e cinque operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_{15}$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th6}$ , e

10 15 - quando si considera la tensione di soglia obiettivo  $V_{th7}$ , l'impulso di programmazione  $P_{21}$  è l'impulso di programmazione finale, quindi una sequenza di ventuno impulsi di programmazione dall'impulso di programmazione iniziale  $P_1$  e cinque operazioni di verifica della programmazione a partire dall'impulso di programmazione di avvio PV  $P_{17}$  sono richiesti per programmare la cella di memoria più veloce alla tensione di soglia obiettivo  $V_{th7}$ .

In accordo con una forma di realizzazione, il dispositivo di memoria **3D 100** (ad esempio, il controllore della memoria **135** o qualsiasi altro modulo o circuito del dispositivo di memoria **3D 100**) è configurato per memorizzare, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , un'indicazione del rispettivo impulso di programmazione di avvio PV (ovvero, l'impulso di programmazione predefinito determinato durante la fase di caratterizzazione del dispositivo di memoria **3D 100** sulla base dell'approccio convenzionale sopra menzionato).

25 In accordo con i principi della presente invenzione, il controllore della memoria **135** è configurato per, per una cella di memoria selezionata di una stringa di celle di memoria di riferimento (da qui in avanti, cella di memoria di riferimento) da programmare alla tensione di soglia obiettivo  $V_{th_h}$ :

30 (i) determinare, per la tensione di soglia obiettivo  $V_{th_h}$ , un impulso di programmazione di avvio PV aggiornato per l'avvio delle operazioni di verifica della programmazione, in cui l'impulso di programmazione di avvio PV aggiornato segue, nella sequenza di impulsi di programmazione, l'impulso di programmazione di avvio PV (ovvero,

l'impulso di programmazione di avvio PV predefinito determinato durante la fase di caratterizzazione del dispositivo di memoria 3D **100**), e

5 (ii) per ciascuna cella di memoria successivamente selezionata da programmare alla tensione di soglia obiettivo  $V_{th_h}$  e che mostra (ovvero, che ragionevolmente mostra) proprietà elettriche simili alla cella di memoria di riferimento (da qui in avanti indicata come cella di memoria simile), eseguire le operazioni di verifica della programmazione in accordo con l'impulso di programmazione di avvio PV aggiornato.

In accordo con una forma di realizzazione, iterando il passo (i) per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , si ottiene uno schema PV aggiornato per la cella di memoria di riferimento che contiene, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , il rispettivo impulso di programmazione di avvio PV aggiornato da utilizzare per programmare ciascuna cella di memoria simile successivamente selezionata (ovvero, la cella di memoria successivamente selezionata simile alla cella di memoria di riferimento, inclusa la stessa cella di memoria di riferimento).

15 In accordo con una forma di realizzazione, è prevista una pluralità di celle di memoria di riferimento. In accordo con una forma di realizzazione, iterando il passo (i) per ciascuna tensione di soglia obiettivo  $V_{th_h}$  e per ciascuna cella di memoria di riferimento, si ottiene una pluralità di schemi PV aggiornati, ciascuno associato ad una rispettiva cella di memoria di riferimento e contenente, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , il rispettivo impulso di programmazione di avvio PV aggiornato da utilizzare per programmare ciascuna cella di memoria simile successivamente selezionata (ovvero, ciascuna cella di memoria successivamente selezionata simile alla rispettiva cella di memoria di riferimento, inclusa la rispettiva stessa cella di memoria di riferimento).

25 In accordo con una forma di realizzazione, le celle di memoria simili possono comprendere (in aggiunta alla stessa cella di memoria di riferimento) celle di memoria associate ad una stessa word line della cella di memoria di riferimento. In questa forma di realizzazione, le celle di memoria di riferimento possono comprendere tutte le celle di memoria nella stringa di celle di memoria di riferimento, quindi può essere previsto un numero di schemi PV aggiornati uguale al numero di celle di memoria per ciascuna stringa 30 di celle di memoria.

Diversamente dai dispositivi di memoria 3D noti nella tecnica, in cui è fornito un impulso di programmazione di avvio PV fisso (ovvero, l'impulso di programmazione di

avvio PV predefinito determinato durante la fase di caratterizzazione del dispositivo di memoria **3D 100**) per tutte le celle di memoria appartenenti allo stesso gruppo ISPP di celle di memoria sulla base della cella di memoria più veloce del gruppo ISPP di celle di memoria, il dispositivo di memoria **3D 100** in accordo con la presente invenzione consente di evitare 5 operazioni di verifica della programmazione non necessarie per le celle di memoria più lente, quindi riducendo i tempi di programmazione: infatti, come meglio discusso nel seguito quando si discuterà un esemplificativo schema PV aggiornato, per ciascuna tensione di soglia obiettivo  $V_{th}$ , un certo numero di operazioni di verifica della programmazione può essere evitato o risparmiato o saltato rispetto allo schema PV che risulterebbe utilizzando 10 l'impulso di programmazione di avvio PV predefinito per le celle di memoria più lente.

In accordo con una forma di realizzazione, le celle di memoria simili possono comprendere (in aggiunta alla stessa cella di memoria di riferimento) celle di memoria associate ad una o più word line differenti dalla word line associata alla cella di memoria di riferimento. Solo come esempio, le celle di memoria simili possono comprendere (in 15 aggiunta alla cella di memoria di riferimento stessa) celle di memoria associate ad una o più word line adiacenti che sono adiacenti alla word line associata alla cella di memoria di riferimento. In questa forma di realizzazione, le celle di memoria di riferimento possono comprendere un sottoinsieme delle celle di memoria nella stringa di celle di memoria di riferimento, quindi può essere presente un numero di schemi PV aggiornati inferiore al 20 numero di celle di memoria per stringa di celle di memoria: ciò consente di ridurre ulteriormente i tempi di programmazione (in quanto, quando si selezionano celle di memoria simili associate a differenti word line, bisogna accedere ad un singolo schema PV aggiornato).

In accordo con una forma di realizzazione, la stringa di celle di memoria di riferimento comprende, per ciascuna blocco di memoria, una stringa iniziale di celle di memoria del blocco di memoria (nell'esempio in questione, la stringa di celle di memoria 25 **115<sub>1,1</sub>**).

In accordo con una forma di realizzazione, la stringa di celle di memoria di riferimento comprende, per ciascun blocco di memoria, una stringa di celle di memoria programmata per prima nel blocco di memoria (ovvero, la stringa di celle di memoria a cui 30 appartiene la prima cella di memoria selezionata da programmare).

Si assume che lo schema PV associato alla cella di memoria di riferimento sia

l'esemplificativo schema PV della **Figura 2A** (in cui, come menzionato sopra, per ciascuna tensione di soglia obiettivo  $V_{th_h}$  lo schema PV associato alla cella di memoria di riferimento (**Figura 2A**) e lo schema PV veloce (**Figura 2B**) hanno, alla prima selezione della cella di memoria selezionata per la sua programmazione alla tensione di soglia obiettivo  $V_{th_h}$ , lo stesso impulso di programmazione di avvio PV predefinito). In questo scenario:

5 - quando si considera la tensione di soglia obiettivo  $V_{th_1}$ , l'impulso di programmazione finale  $P_9$  della cella di memoria di riferimento segue l'impulso di programmazione finale  $P_7$  della cella di memoria più veloce (ovvero, la cella di memoria di riferimento è più lenta della cella di memoria più veloce programmata alla tensione di soglia obiettivo  $V_{th_1}$ );

10 - quando si considera la tensione di soglia obiettivo  $V_{th_2}$ , l'impulso di programmazione finale  $P_{12}$  della cella di memoria di riferimento segue l'impulso di programmazione finale  $P_{10}$  della cella di memoria più veloce (ovvero, la cella di memoria di riferimento è più lenta della cella di memoria più veloce programmata alla tensione di soglia obiettivo  $V_{th_2}$ );

15 - quando si considera la tensione di soglia obiettivo  $V_{th_3}$ , l'impulso di programmazione finale  $P_{14}$  della cella di memoria di riferimento segue l'impulso di programmazione finale  $P_{12}$  della cella di memoria più veloce (ovvero, la cella di memoria di riferimento è più lenta della cella di memoria più veloce programmata alla tensione di soglia obiettivo  $V_{th_3}$ );

20 - quando si considera la tensione di soglia obiettivo  $V_{th_4}$ , l'impulso di programmazione finale  $P_{16}$  della cella di memoria di riferimento segue l'impulso di programmazione finale  $P_{14}$  della cella di memoria più veloce (ovvero, la cella di memoria di riferimento è più lenta della cella di memoria di riferimento programmata alla tensione di soglia obiettivo  $V_{th_4}$ );

25 - quando si considera la tensione di soglia obiettivo  $V_{th_5}$ , l'impulso di programmazione finale  $P_{19}$  della cella di memoria di riferimento segue l'impulso di programmazione finale  $P_{17}$  della cella di memoria più veloce (ovvero, la cella di memoria di riferimento è più lenta della cella di memoria più veloce programmata alla tensione di soglia obiettivo  $V_{th_5}$ );

30 - quando si considera la tensione di soglia obiettivo  $V_{th_6}$ , l'impulso di programmazione finale  $P_{21}$  della cella di memoria di riferimento segue l'impulso di

programmazione finale  $P_{19}$  della cella di memoria più veloce (ovvero, la cella di memoria di riferimento è più lenta della cella di memoria più veloce programmata alla tensione di soglia obiettivo  $V_{th6}$ ), e

5 - quando si considera la tensione di soglia obiettivo  $V_{th7}$ , l'impulso di programmazione finale  $P_{22}$  della cella di memoria di riferimento segue l'impulso di programmazione finale  $P_{21}$  della cella di memoria più veloce (ovvero, la cella di memoria di riferimento è più lenta della cella di memoria più veloce programmata alla tensione di soglia obiettivo  $V_{th7}$ ).

10 La **Figura 2C** mostra un esemplificativo schema PV aggiornato che può essere derivato dal controllore della memoria **135** sulla base dello scenario di cui sopra (in cui ciascun simbolo “X” denota una rispettiva operazione di verifica della programmazione “risparmiata” o evitata rispetto allo schema PV associato alla cella di memoria di riferimento (più lenta)). In particolare, nell'esemplificativo schema PV aggiornato considerato:

15 - quando si considera la tensione di soglia obiettivo  $V_{th1}$ , l'impulso di programmazione di avvio PV aggiornato è l'impulso di programmazione  $P_5$  (invece che l'impulso di programmazione predefinito  $P_1$ ), quindi quattro operazioni di verifica della programmazione sono risparmiate o evitate o saltate quando si programma ciascuna cella di memoria simile successivamente selezionata alla tensione di soglia obiettivo  $V_{th1}$  in accordo con lo schema PV aggiornato;

20 - quando si considera la tensione di soglia obiettivo  $V_{th2}$ , l'impulso di programmazione di avvio PV aggiornato è l'impulso di programmazione  $P_8$  (invece che l'impulso di programmazione predefinito  $P_5$ ), quindi tre operazioni di verifica della programmazione sono risparmiate o evitate o saltate quando si programma ciascuna cella di memoria simile successivamente selezionata alla tensione di soglia obiettivo  $V_{th2}$  in accordo con lo schema PV aggiornato;

25 - quando si considera la tensione di soglia obiettivo  $V_{th3}$ , l'impulso di programmazione di avvio PV aggiornato è l'impulso di programmazione  $P_{10}$  (invece che l'impulso di programmazione predefinito  $P_7$ ), quindi tre operazioni di verifica della programmazione sono risparmiate o evitate o saltate quando si programma ciascuna cella di memoria simile successivamente selezionata alla tensione di soglia obiettivo  $V_{th3}$  in accordo con lo schema PV aggiornato;

- quando si considera la tensione di soglia obiettivo  $V_{th4}$ , l'impulso di

programmazione di avvio PV aggiornato è l'impulso di programmazione  $P_{12}$  (invece che l'impulso di programmazione predefinito  $P_{10}$ ), quindi due operazioni di verifica della programmazione sono risparmiate o evitate o saltate quando si programma ciascuna cella di memoria simile successivamente selezionata alla tensione di soglia obiettivo  $V_{th4}$  in accordo

5 con lo schema PV aggiornato;

- quando si considera la tensione di soglia obiettivo  $V_{th5}$ , l'impulso di programmazione di avvio PV aggiornato è l'impulso di programmazione  $P_{15}$  (invece che l'impulso di programmazione predefinito  $P_{12}$ ), quindi tre operazioni di verifica della programmazione sono risparmiate o evitate o saltate quando si programma ciascuna cella di memoria simile successivamente selezionata alla tensione di soglia obiettivo  $V_{th5}$  in accordo

10 con lo schema PV aggiornato;

- quando si considera la tensione di soglia obiettivo  $V_{th6}$ , l'impulso di programmazione di avvio PV aggiornato è l'impulso di programmazione  $P_{17}$  (invece che l'impulso di programmazione predefinito  $P_{15}$ ), quindi tre operazioni di verifica della programmazione sono risparmiate o evitate o saltate quando si programma ciascuna cella di memoria simile successivamente selezionata alla tensione di soglia obiettivo  $V_{th6}$  in accordo

15 con lo schema PV aggiornato, e

- quando si considera la tensione di soglia obiettivo  $V_{th7}$ , l'impulso di programmazione di avvio PV aggiornato è l'impulso di programmazione  $P_{18}$  (invece che l'impulso di programmazione predefinito  $P_{17}$ ), quindi una operazione di verifica della programmazione è risparmiata o evitata o saltata quando si programma ciascuna cella di memoria simile successivamente selezionata alla tensione di soglia obiettivo  $V_{th7}$  in accordo

20 con lo schema PV aggiornato.

In accordo con una forma di realizzazione, come visibile nello schema PV aggiornato della **Figura 2C**, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , l'impulso di programmazione di avvio PV aggiornato precede, nella sequenza di impulsi di programmazione, l'impulso di programmazione finale della cella di memoria di riferimento di un numero predefinito di impulsi di programmazione. In accordo con una forma di realizzazione, il numero predefinito di impulsi di programmazione può essere un numero atteso di impulsi di programmazione. In accordo con una forma di realizzazione, il numero predefinito di impulsi di programmazione è determinato durante la fase di caratterizzazione. In accordo con una forma di realizzazione, il numero predefinito di impulsi di

programmazione può essere impostato o cambiato dall'esterno dall'utente (ad esempio, per mezzo di un comando esterno sul bus dati). Nell'esempio illustrato, per ciascuna tensione di soglia obiettivo  $V_{th_h}$ , l'impulso di programmazione di avvio PV aggiornato precede, nella sequenza di impulsi di programmazione, l'impulso di programmazione finale della cella di memoria di riferimento di cinque impulsi di programmazione, e in particolare:

5 - quando si considera la tensione di soglia obiettivo  $V_{th_1}$ , l'impulso di programmazione di avvio PV aggiornato  $P_5$  precede l'impulso di programmazione finale  $P_9$  della cella di memoria di riferimento di cinque impulsi di programmazione;

10 - quando si considera la tensione di soglia obiettivo  $V_{th_2}$ , l'impulso di programmazione di avvio PV aggiornato  $P_8$  precede l'impulso di programmazione finale  $P_{12}$  della cella di memoria di riferimento di cinque impulsi di programmazione;

- quando si considera la tensione di soglia obiettivo  $V_{th_3}$ , l'impulso di programmazione di avvio PV aggiornato  $P_{10}$  precede l'impulso di programmazione finale  $P_{14}$  della cella di memoria di riferimento di cinque impulsi di programmazione;

15 - quando si considera la tensione di soglia obiettivo  $V_{th_4}$ , l'impulso di programmazione di avvio PV aggiornato  $P_{12}$  precede l'impulso di programmazione finale  $P_{16}$  della cella di memoria di riferimento di cinque impulsi di programmazione;

- quando si considera la tensione di soglia obiettivo  $V_{th_5}$ , l'impulso di programmazione di avvio PV aggiornato  $P_{15}$  precede l'impulso di programmazione finale  $P_{19}$  della cella di memoria di riferimento di cinque impulsi di programmazione;

20 - quando si considera la tensione di soglia obiettivo  $V_{th_6}$ , l'impulso di programmazione di avvio PV aggiornato  $P_{17}$  precede l'impulso di programmazione finale  $P_{21}$  della cella di memoria di riferimento di cinque impulsi di programmazione;

- quando si considera la tensione di soglia obiettivo  $V_{th_6}$ , l'impulso di programmazione di avvio PV aggiornato  $P_{18}$  precede l'impulso di programmazione finale  $P_{22}$  della cella di memoria di riferimento di cinque impulsi di programmazione.

In accordo con una forma di realizzazione, il numero predefinito di impulsi di programmazione può essere lo stesso per tutte le celle di memoria del dispositivo di memoria **3D 100**.

30 In accordo con una forma di realizzazione, il numero predefinito di impulsi di programmazione può essere lo stesso per ciascun gruppo ISPP di celle di memoria (ovvero, per ciascun gruppo di celle di memoria aventi lo stesso gradino di tensione ISPP): in altre

parole, in questa forma di realizzazione, può essere presente una pluralità di numeri predefiniti di impulsi di programmazione, ciascuno associato ad un rispettivo gruppo ISPP di celle di memoria.

5 La **Figura 3** mostra un diagramma di attività di un metodo **300** in accordo con una forma di realizzazione della presente invenzione.

In accordo con una forma di realizzazione, il metodo **300** comprende, alla selezione di una cella di memoria da programmare ad una tensione di soglia obiettivo  $V_{th_h}$  (nodo di azione **305**), verificare se la cella di memoria selezionata è una cella di memoria di riferimento (nodo di decisione **310**), ovvero se la cella di memoria selezionata appartiene 10 alla stringa di celle di memoria di riferimento. Come discusso sopra, la stringa di celle di memoria di riferimento può comprendere, per ciascun blocco di memoria, una stringa iniziale di celle di memoria del blocco di memoria, o la stringa di celle di memoria programmata per prima nel blocco di memoria.

In accordo con una forma di realizzazione, il metodo **300** comprende, se la cella di memoria selezionata non è una cella di memoria di riferimento (ramo di uscita **N** del nodo di decisione **310**), verificare se un impulso di programmazione di avvio PV aggiornato per la tensione di soglia obiettivo  $V_{th_h}$  (o, più in generale, uno schema PV aggiornato) è già stato associato alla cella di memoria selezionata (nodo di decisione **315**), ovvero verificare se un impulso di programmazione di avvio PV aggiornato è già stato determinato, per la tensione di soglia obiettivo  $V_{th_h}$ , per la cella di memoria di riferimento che mostra (ovvero, che ragionevolmente mostra) proprietà elettriche simili alla cella di memoria selezionata. Detto in altro modo, al nodo di decisione **315** il metodo **300** comprende verificare se, per la tensione di soglia obiettivo  $V_{th_h}$ , un impulso di programmazione di avvio PV aggiornato (o, più in generale, uno schema PV aggiornato) è già stato determinato per la cella di memoria 20 di riferimento rispetto alla quale la cella di memoria selezionata è una cella di memoria simile.

In accordo con una forma di realizzazione, il metodo **300** comprende, se nessun impulso di programmazione di avvio PV aggiornato è associato alla cella di memoria selezionata per la tensione di soglia obiettivo  $V_{th_h}$  (ramo di uscita **N** del nodo di decisione **315**), programmare la cella di memoria selezionata ed eseguire la corrispondente operazione 30 di verifica della programmazione sulla base dell'impulso di programmazione di avvio PV predefinito (nodo di azione **320**).

In accordo con una forma di realizzazione, il metodo **300** comprende, se un impulso di programmazione di avvio PV aggiornato è associato alla cella di memoria selezionata per la tensione di soglia obiettivo  $V_{th_h}$  (ramo di uscita **Y** del nodo di decisione **315**), programmare la cella di memoria selezionata sulla base dell'impulso di programmazione di avvio PV aggiornato (ovvero, avviando le corrispondenti operazioni di verifica della programmazione dall'impulso di programmazione di avvio PV aggiornato) (nodo di azione **325**).

In accordo con una forma di realizzazione, il metodo **300** comprende, se la cella di memoria selezionata è una cella di memoria di riferimento (ramo di uscita **Y** del nodo di decisione **310**), verificare se un impulso di programmazione di avvio PV aggiornato per la tensione di soglia obiettivo  $V_{th_h}$  (o, più in generale, uno schema PV aggiornato) è già stato determinato per la cella di memoria selezionata (nodo di decisione **330**), ovvero verificare se un impulso di programmazione di avvio PV aggiornato è già stato determinato, per la tensione di soglia obiettivo  $V_{th_h}$ , per la cella di memoria di riferimento selezionata.

In accordo con una forma di realizzazione, il metodo **300** comprende, se un impulso di programmazione di avvio PV aggiornato è associato cella di memoria di riferimento selezionata per la tensione di soglia obiettivo  $V_{th_h}$  (ramo di uscita **Y** del nodo di decisione **330**), programmare la cella di memoria di riferimento selezionata sulla base dell'impulso di programmazione di avvio PV aggiornato (nodo di azione **325**).

In accordo con una forma di realizzazione, il metodo **300** comprende, se nessun impulso di programmazione di avvio PV aggiornato è associato alla cella di memoria di riferimento selezionata per la tensione di soglia obiettivo  $V_{th_h}$  (ramo di uscita **N** del nodo di decisione **330**), programmare la cella di memoria selezionata ed eseguire la corrispondente operazione di verifica della programmazione sulla base dell'impulso di programmazione di avvio PV predefinito (ovvero, avviando le corrispondenti operazioni di verifica della programmazione dall'impulso di programmazione di avvio PV predefinito) (nodo di azione **335**).

In accordo con una forma di realizzazione, il metodo **300** comprende determinare, per la tensione di soglia obiettivo  $V_{th_h}$ , un impulso di programmazione di avvio PV aggiornato per la cella di memoria di riferimento selezionata (nodo di azione **340**) (il quale impulso di programmazione di avvio PV aggiornato sarà utilizzato per ciascuna cella di memoria simile successivamente selezionata da programmare alla tensione di soglia

obiettivo  $V_{thh}$ ). In accordo con una forma di realizzazione, come discusso in precedenza, l'impulso di programmazione di avvio PV aggiornato è determinato sulla base dell'impulso di programmazione finale della cella di memoria di riferimento. In accordo con una forma di realizzazione, come discusso in precedenza, l'impulso di programmazione di avvio PV aggiornato precede, nella sequenza di impulsi di programmazione, l'impulso di programmazione finale della cella di memoria di riferimento di un numero predefinito di impulsi di programmazione.

La **Figura 4** mostra un diagramma a blocchi semplificato di un sistema elettronico **400** in accordo con una forma di realizzazione della presente invenzione.

In accordo con una forma di realizzazione, il sistema elettronico **400** comprende il dispositivo di memoria 3D **100** (o più). Il dispositivo di memoria 3D (**100**) comprende la pluralità di stringhe di celle di memoria, la pluralità di word line ed il circuito di controllo. Il circuito di controllo esegue operazioni di verifica della programmazione in risposta ad un rispettivo impulso di programmazione dopo l'applicazione di un primo impulso di programmazione per un avvio delle operazioni di verifica della programmazione che è un impulso di programmazione predefinito. Il circuito di controllo determina un primo impulso di programmazione aggiornato sulla base di risultati delle operazioni di verifica della programmazione. Le operazioni di verifica della programmazione esegue le operazioni di verifica della programmazione a partire dal primo impulso di programmazione aggiornato per ciascuna cella di memoria successivamente selezionata.

In accordo con una forma di realizzazione, il sistema elettronico **400** può comprendere un controllore **405** (ad esempio, uno o più microprocessori e/o uno o più microcontrollori). In accordo con una forma di realizzazione, l'uno o più microprocessori e/o l'uno o più microcontrollori, o almeno un loro sottoinsieme, possono essere inglobati nel dispositivo di memoria 3D **100**.

In accordo con una forma di realizzazione, il sistema elettronico **400** può comprendere un dispositivo di ingresso/uscita **410**, come uno schermo e/o una tastiera.

In accordo con una forma di realizzazione, il sistema elettronico **400** può comprendere un'interfaccia wireless **415** (ad esempio, una o più antenne e/o uno o più ricetrasmettitori wireless) per scambiare in maniera wireless (senza fili) messaggi con una rete di comunicazione senza fili (non mostrata).

In accordo con una forma di realizzazione, il sistema elettronico **400** può

comprendere un dispositivo di alimentazione (ad esempio, una batteria) **420** per alimentare il sistema elettronico **400**.

In accordo con una forma di realizzazione, il sistema elettronico **400** può comprendere uno o più canali di comunicazione (bus) **425** per consentire lo scambio di dati tra il dispositivo di memoria 3D **100**, il controllore **405** (quando presente), il dispositivo di ingresso/uscita **410** (quando presente), l'interfaccia wireless **415** (quando presente), ed il dispositivo di alimentazione **420** (quando presente).

Naturalmente, al fine di soddisfare requisiti locali e specifici, un tecnico del ramo può applicare all'invenzione sopra descritta molte modifiche ed alterazioni logiche e/o fisiche. Più specificamente, sebbene la presente invenzione sia stata descritta con un certo grado di particolarità con riferimento a sue forme di realizzazione preferite, si dovrebbe comprendere che sono possibili varie omissioni, sostituzioni e cambiamenti nella forma e nei dettagli, nonché altre forme di realizzazione. In particolare, differenti forme di realizzazione dell'invenzione possono anche essere messe in pratica senza i dettagli specifici enunciati nella descrizione precedente per fornire una loro più completa comprensione; al contrario, caratteristiche ben note possono essere state omesse o semplificate per non appesantire la descrizione con dettagli non necessari. Inoltre, è espressamente inteso che elementi specifici e/o passi del metodo descritti in relazione a qualsiasi forma di realizzazione divulgata dell'invenzione possono essere incorporati in qualsiasi altra forma di realizzazione.

In particolare, considerazioni simili si applicano se il dispositivo di memoria 3D (e/o il sistema comprendente il dispositivo di memoria 3D) ha una struttura diversa o include componenti equivalenti. In ogni caso, qualsiasi suo componente può essere separato in più elementi, o due o più componenti possono essere combinati in un unico elemento; inoltre, ogni componente può essere replicato per supportare l'esecuzione delle corrispondenti operazioni in parallelo. Va inoltre notato che (salvo diversa indicazione) qualsiasi interazione tra componenti differenti generalmente non deve essere continua e può essere diretta o indiretta tramite uno o più intermediari.

\* \* \* \* \*

## RIVENDICAZIONI

1. Un dispositivo di memoria tridimensionale (100), comprendente:

una pluralità di stringhe di celle di memoria (115<sub>n,1</sub>), ciascuna stringa di celle di memoria comprendendo una pluralità di celle di memoria (T<sub>k</sub>) impilate l'una sull'altra su un substrato ciascuna ad una rispettiva distanza verticale dal substrato;

5 una pluralità di word line (WL<sub>k</sub>) ciascuna associata a rispettive celle di memoria della pluralità di stringhe di celle di memoria disposte ad una stessa distanza verticale dal substrato; e

10 un circuito di controllo (135) configurato per:

(i) applicare una sequenza di impulsi di programmazione a passo incrementale ad una cella di memoria selezionata di una stringa di celle di memoria di riferimento per programmare la cella di memoria selezionata ad una tensione di soglia obiettivo tra una pluralità di tensioni di soglia obiettivo;

15 (ii) eseguire operazioni di verifica della programmazione in risposta ad un rispettivo impulso di programmazione dopo l'applicazione di un primo impulso di programmazione della sequenza di impulsi di programmazione a passo incrementale, il primo impulso di programmazione per un avvio delle operazioni di verifica della programmazione essendo un impulso di programmazione predefinito determinato dal dispositivo di memoria tridimensionale;

20 (iii) determinare un primo impulso di programmazione aggiornato per la cella di memoria selezionata e per la tensione di soglia obiettivo sulla base di un secondo impulso di programmazione indicativo che la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo; e

25 (iv) eseguire le operazioni di verifica della programmazione a partire dal primo impulso di programmazione aggiornato per ciascuna cella di memoria successivamente selezionata da programmare alla tensione di soglia obiettivo e associata alla stessa word line della cella di memoria selezionata.

2. Il dispositivo di memoria tridimensionale (100) in accordo con la rivendicazione

30 1, in cui il circuito di controllo (135) è configurato per ripetere i passi (i), (ii), (iii) e (iv) per ciascuna tensione di soglia obiettivo tra la pluralità di tensioni di soglia obiettivo.

3. Il dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 1 o 2, in cui il primo impulso di programmazione aggiornato precede, nella sequenza di impulsi di programmazione a passo incrementale, il secondo impulso di programmazione di un numero predefinito di impulsi di programmazione.

5

4. Il dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 3, in cui il numero predefinito di impulsi di programmazione è lo stesso per ciascun gruppo di celle di memoria aventi uno stesso gradino di tensione incrementale tra impulsi di programmazione successivi.

10

5. Il dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 1, in cui il circuito di controllo (**135**) è configurato per eseguire le operazioni di verifica della programmazione a partire dal primo impulso di programmazione aggiornato per ciascuna cella di memoria successivamente selezionata associata alla stessa word line (**WL<sub>k</sub>**) 15 della cella di memoria selezionata e per ciascuna cella di memoria successivamente selezionata associata ad almeno una word line diversa da detta stessa word line.

15

6. Il dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 5, in cui l'almeno una word line diversa da detta stessa word line comprende almeno una 20 word line adiacente che è adiacente a detta stessa word line.

20

7. Il dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 1, comprendente una pluralità di blocchi di memoria (**110**) ciascuno comprendente un sottoinsieme della pluralità di stringhe di celle di memoria, in cui la stringa di celle di 25 memoria di riferimento comprende, per ciascun blocco di memoria, una stringa iniziale di celle di memoria del blocco di memoria o una stringa di celle di memoria programmata per prima nel blocco di memoria.

25

8. Il dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 30 1, in cui il circuito di controllo (**135**) è configurato per ripetere i passi (i), (ii), (iii) e (iv) per ciascuna di almeno una ulteriore cella di memoria selezionata della stringa di celle di memoria di riferimento.

9. Il dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 1, in cui ciascuna delle celle di memoria ( $T_k$ ) è una cella di memoria a singolo livello o una cella di memoria multilivello.

5 10. Sistema elettronico (**400**) comprendente almeno un dispositivo di memoria tridimensionale (**100**) in accordo con la rivendicazione 1.

10 15. Metodo (**300**) per operare un dispositivo di memoria tridimensionale (**100**), in cui il dispositivo di memoria tridimensionale comprende una pluralità di stringhe di celle di memoria ( $115_{n,1}$ ) ciascuna comprendente una pluralità di celle di memoria ( $T_k$ ) impilate l'una sull'altra su un substrato ciascuna ad una rispettiva distanza verticale dal substrato, ed una pluralità di word line ( $WL_k$ ) ciascuna associata a rispettive celle di memoria della pluralità di stringhe di celle di memoria disposte ad una stessa distanza verticale dal substrato, il metodo comprendendo:

15 (i) applicare una sequenza di impulsi di programmazione a passo incrementale ad una cella di memoria selezionata di una stringa di celle di memoria di riferimento per programmare la cella di memoria selezionata ad una tensione di soglia obiettivo tra una pluralità di tensioni di soglia obiettivo (**320; 335**);

20 (ii) eseguire operazioni di verifica della programmazione in risposta ad un rispettivo impulso di programmazione dopo l'applicazione di un primo impulso di programmazione della sequenza di impulsi di programmazione a passo incrementale (**320; 335**), il primo impulso di programmazione per un avvio delle operazioni di verifica della programmazione essendo un impulso di programmazione predefinito determinato dal dispositivo di memoria tridimensionale;

25 (iii) determinare un primo impulso di programmazione aggiornato per la cella di memoria selezionata e per la tensione di soglia obiettivo sulla base di un secondo impulso di programmazione indicativo che la cella di memoria selezionata è stata programmata alla tensione di soglia obiettivo (**340**); e

30 (iv) eseguire le operazioni di verifica della programmazione a partire dal primo impulso di programmazione aggiornato per ciascuna cella di memoria successivamente selezionata da programmare alla tensione di soglia obiettivo ed associata alla stessa word line della cella di memoria selezionata (**325**).

Figure 1

Figure 2A

Figure 2B

Figure 2C

|                              | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub> | P <sub>4</sub> | P <sub>5</sub> | P <sub>6</sub> | P <sub>7</sub> | P <sub>8</sub> | P <sub>9</sub> | P <sub>10</sub> | P <sub>11</sub> | P <sub>12</sub> | P <sub>13</sub> | P <sub>14</sub> | P <sub>15</sub> | P <sub>16</sub> | P <sub>17</sub> | P <sub>18</sub> | P <sub>19</sub> | P <sub>20</sub> | P <sub>21</sub> | P <sub>22</sub> |    |

|------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----|