(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-164491

(P2019-164491A)

(43) 公開日 令和1年9月26日(2019.9.26)

(51) Int.Cl.

G06F 12/0815 (2016.01)

F 1

G06F 12/0815

テーマコード(参考)

G06F 12/0808 (2016.01)

G06F 12/0808

5B205

G06F 12/0804 (2016.01)

G06F 12/0804 100

審査請求 未請求 請求項の数 15 O L (全 12 頁)

(21) 出願番号

特願2018-51258 (P2018-51258)

(22) 出願日

平成30年3月19日 (2018.3.19)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(71) 出願人 317011920

東芝デバイス&amp;ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100103034

弁理士 野河 信久

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100153051

弁理士 河野 直樹

最終頁に続く

(54) 【発明の名称】情報処理装置及びキャッシュ制御装置

## (57) 【要約】

【課題】指定アドレス範囲のキャッシュ・メンテナンス処理の高速化及び低消費電力化を実現することにある。

【解決手段】本実施形態の情報処理装置は、キャッシュメモリと、キャッシュ制御装置とを備えた構成である。前記キャッシュ制御装置は、第1の制御回路と、第2の制御回路とを含む。前記第1の制御回路は、指定したアドレス範囲に含まれる前記キャッシュメモリのアクセス対象アドレスであって、当該アクセス対象アドレスのキャッシュラインに対するキャッシュ・メンテナンス処理の実行を予約する。前記第2の制御回路は、前記第1の制御回路により予約されたキャッシュラインに対するキャッシュ・メンテナンス処理を実行する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

キャッシュメモリと、

キャッシュ制御装置と、

を具備し、

前記キャッシュ制御装置は、

指定したアドレス範囲に含まれる前記キャッシュメモリのアクセス対象アドレスであつて、当該アクセス対象アドレスのキャッシュラインに対するキャッシュ・メンテナンス処理の実行を予約する第1の制御回路と、

前記第1の制御回路により予約されたキャッシュラインに対するキャッシュ・メンテナンス処理を実行する第2の制御回路と、

を含む、情報処理装置。

**【請求項 2】**

前記第1の制御回路は、

前記キャッシュメモリのアクセス対象アドレスが入力された場合に、当該アクセス対象アドレスが、指定したアドレス範囲に含まれるか否かを判定する判定回路を含む、

請求項1に記載の情報処理装置。

**【請求項 3】**

前記第1の制御回路は、

前記キャッシュ・メンテナンス処理を予約したアクセス対象アドレス毎に予約情報を設定する記憶回路を含む、請求項1又は2に記載の情報処理装置。

**【請求項 4】**

前記第1の制御回路は、

キャッシュ・メンテナンス処理対象の指定アドレス範囲を設定するレジスタ回路と、

前記キャッシュメモリのアクセス対象アドレスが入力された場合に、当該アクセス対象アドレスが、前記レジスタ回路に設定された指定アドレス範囲に含まれるか否かを判定する判定回路と、

を含む、請求項1から3のいずれか1項に記載の情報処理装置。

**【請求項 5】**

前記第2の制御回路は、

前記キャッシュ・メンテナンス処理の実行指示に応じて、予約されたキャッシュラインに対するキャッシュ・メンテナンス処理を実行する、請求項1から4のいずれか1項に記載の情報処理装置。

**【請求項 6】**

前記第2の制御回路は、

前記キャッシュ・メンテナンス処理の実行指示に応じて、前記記憶回路に設定された予約情報に対応するキャッシュラインに対するキャッシュ・メンテナンス処理を実行する、

請求項3に記載の情報処理装置。

**【請求項 7】**

前記キャッシュ制御装置は、前記キャッシュメモリのキャッシュライン毎に、当該キャッシュラインの有効性を示す有効情報を設定する第3の制御回路を含み、

前記第2の制御回路は、

前記第1の制御回路により予約されたキャッシュラインに対応する前記有効情報をクリアする、請求項1から6のいずれか1項に記載の情報処理装置。

**【請求項 8】**

前記キャッシュ・メンテナンス処理は、

前記キャッシュメモリのアクセス対象アドレスのキャッシュラインを無効化する処理と、

前記キャッシュメモリのアクセス対象アドレスのキャッシュラインをフラッシュする処理と、

10

20

30

40

50

を含む、請求項 1 から 7 のいずれか 1 項に記載の情報処理装置。

【請求項 9】

前記キャッシュ制御装置は、

前記第 1 の制御回路により予約されたアクセス対象アドレスのキャッシュラインが前記キャッシュメモリから追い出される場合、前記第 1 の制御回路により設定される予約をクリアする、請求項 1 から 8 のいずれか 1 項に記載の情報処理装置。

【請求項 10】

キャッシュメモリを有する情報処理装置に適用するキャッシュ制御装置であって、

指定したアドレス範囲に含まれる、前記キャッシュメモリのアクセス対象アドレスのキャッシュラインに対するキャッシュ・メンテナンス処理の実行を予約する第 1 の制御回路と、

前記第 1 の制御回路により予約されたキャッシュラインに対するキャッシュ・メンテナンス処理を実行する第 2 の制御回路と、

を具備する、キャッシュ制御装置。

【請求項 11】

前記第 1 の制御回路は、

前記キャッシュメモリのアクセス対象アドレスが入力された場合に、当該アクセス対象アドレスが、指定したアドレス範囲にマッチングするか否かを判定するマッチング回路を含む、請求項 10 に記載のキャッシュ制御装置。

【請求項 12】

前記第 1 の制御回路は、

前記キャッシュ・メンテナンス処理を予約したアクセス対象アドレス毎に予約情報を設定する第 1 のデータアレイを含む、請求項 10 又は 11 に記載のキャッシュ制御装置。

【請求項 13】

前記キャッシュメモリのキャッシュライン毎に、当該キャッシュラインの有効性を示す有効情報を設定する第 2 のデータアレイを含み、

前記第 2 の制御回路は、

前記第 1 の制御回路により予約されたキャッシュラインに対応する前記有効情報をクリアする、請求項 10 から 12 のいずれか 1 項に記載のキャッシュ制御装置。

【請求項 14】

前記キャッシュ・メンテナンス処理は、

前記キャッシュメモリのアクセス対象アドレスのキャッシュラインを無効化する処理と、

前記キャッシュメモリのアクセス対象アドレスのキャッシュラインをフラッシュする処理と、

を含む、請求項 10 から 13 のいずれか 1 項に記載のキャッシュ制御装置。

【請求項 15】

前記第 1 の制御回路により予約されたアクセス対象アドレスのキャッシュラインが前記キャッシュメモリから追い出される場合、前記第 1 の制御回路により設定される予約をクリアする手段を含む、請求項 10 から 14 のいずれか 1 項に記載のキャッシュ制御装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、情報処理装置及びキャッシュ制御装置に関する。

【背景技術】

【0002】

コンピュータでは、アクセスの高速化のために、アクセス対象のデータを一時的に保持する（キャッシュする）キャッシュメモリ（cache memory）が使用されている。

【0003】

キャッシュメモリは、例えば、プロセッサ（CPU）と他のマスターとのコヒーレンス（

10

20

30

40

50

coherence) を維持するため、キャッシュされたデータ(キャッシュライン)を無効化(invalidate)する処理が必要となる。また、ライトバックキャッシュ(write back cache)方式では、キャッシュラインをメインメモリにフラッシュ(flush)する処理が必要となる。これらの処理を、総称してキャッシュ・メンテナンス(cache maintenance)処理と呼ぶ。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2014-178804号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来のキャッシュ・メンテナンス処理は、タグメモリを読み出し、指定アドレス範囲にマッチするか否かを判定し、マッチした場合にはバリッドビットをクリアする。この処理を、指定アドレス範囲の分だけ繰り返す。従って、キャッシュ・メンテナンス処理がある指定アドレス範囲に対して行う場合、指定アドレス範囲が広い場合には、繰り返しの実行によりキャッシュ・メンテナンス処理に要する実行時間や消費電力が増大する。

【0006】

そこで、目的は、指定アドレス範囲のキャッシュ・メンテナンス処理の高速化及び低消費電力化を実現することにある。

20

【課題を解決するための手段】

【0007】

本実施形態の情報処理装置は、キャッシュメモリと、キャッシュ制御装置とを備えた構成である。前記キャッシュ制御装置は、第1の制御回路と、第2の制御回路とを含む。前記第1の制御回路は、指定したアドレス範囲に含まれる前記キャッシュメモリのアクセス対象アドレスであって、当該アクセス対象アドレスのキャッシュラインに対するキャッシュ・メンテナンス処理の実行を予約する。前記第2の制御回路は、前記第1の制御回路により予約されたキャッシュラインに対するキャッシュ・メンテナンス処理を実行する。

【図面の簡単な説明】

【0008】

30

【図1】実施形態に関する情報処理装置の構成を説明するためのブロック図。

【図2】実施形態に関するキャッシュメモリの構成を説明するためのブロック図。

【図3】実施形態に関するキャッシュコントローラの構成を説明するためのブロック図。

【図4】実施形態に関するデータアレイとタグアドレスとの対応関係を説明するための図。

【図5】実施形態に関するCPU及びキャッシュコントローラの処理手順を説明するためのフローチャート。

【図6】実施形態に関するキャッシュ制御の処理内容の一例を説明する図。

【図7】実施形態に関するキャッシュ制御の処理内容の一例を説明する図。

【図8】実施形態に関するキャッシュ制御の処理内容の一例を説明する図。

【図9】実施形態に関するキャッシュ制御の処理内容の一例を説明する図。

【図10】実施形態に関するキャッシュ制御の処理内容の一例を説明する図。

40

【発明を実施するための形態】

【0009】

以下図面を参照して、実施形態を説明する。

[システム構成]

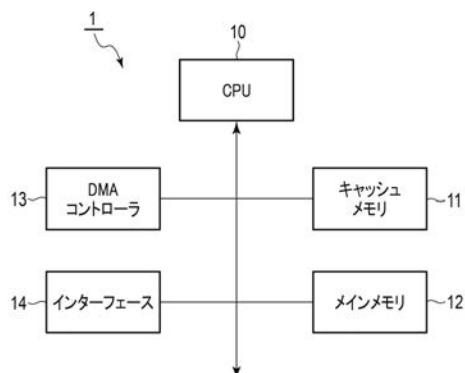

図1は、本実施形態の情報処理装置(以下、コンピュータと表記する)1の構成の一例を示すブロック図である。図1に示すように、コンピュータ1は、プロセッサ(CPU)10、キャッシュメモリ11、メインメモリ12、DMA(Direct Memory Access)コントローラ13、及びインターフェース14を有する。

50

## 【0010】

CPU10は、所定のソフトウェアに基づいて、キャッシュメモリ11及びメインメモリ12をアクセスし、例えば画像処理等の情報処理を実行する。キャッシュメモリ11は、後述するように、例えばSRAM(Static Random Access Memory)からなるデータ記憶領域及びタグ記憶領域を有する。また、本実施形態では、キャッシュメモリ11は、本実施形態の主要素であるキャッシュコントローラ(キャッシュ制御装置)を含む構成とする。

## 【0011】

DMAコントローラ13は、CPU10が関与しないメモリアクセスを制御する。DMAコントローラ13は、例えば、インターフェース14を介して、メインメモリ12と周辺装置との間で直接的なデータ転送を実行する。10

## 【0012】

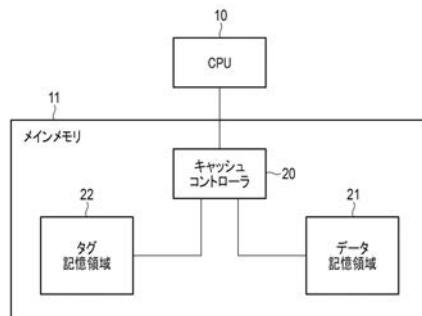

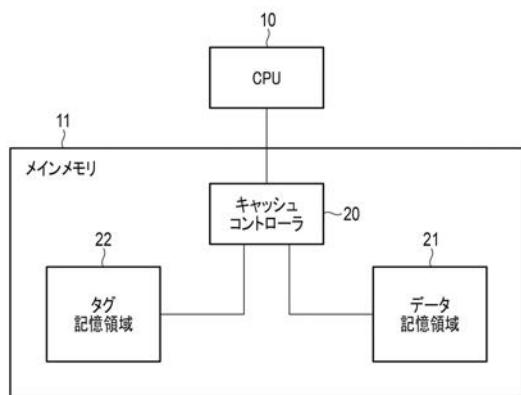

図2は、キャッシュメモリ11の構成の一例を示すブロック図である。図2に示すように、キャッシュメモリ11は、キャッシュコントローラ20、データ記憶領域21及びタグ記憶領域22を含む。キャッシュコントローラ20は、後述するように、本実施形態のキャッシュ・メンテナンス処理を含むキャッシュ制御を実行する。データ記憶領域21は、キャッシュライン(所定単位のキャッシュデータ)を格納する記憶領域である。タグ記憶領域22は、当該キャッシュラインのアドレス(タグアドレス)やアドレス履歴を格納する記憶領域である。

## 【0013】

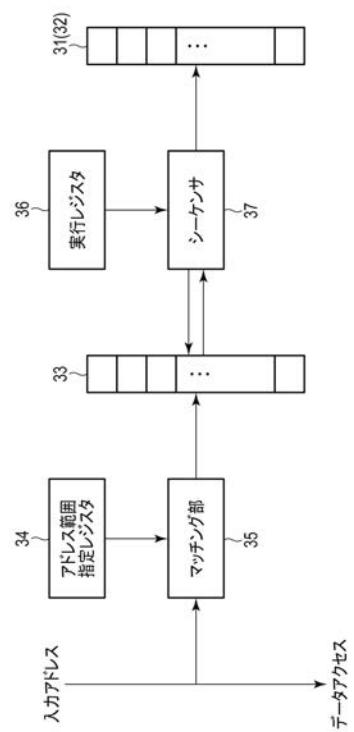

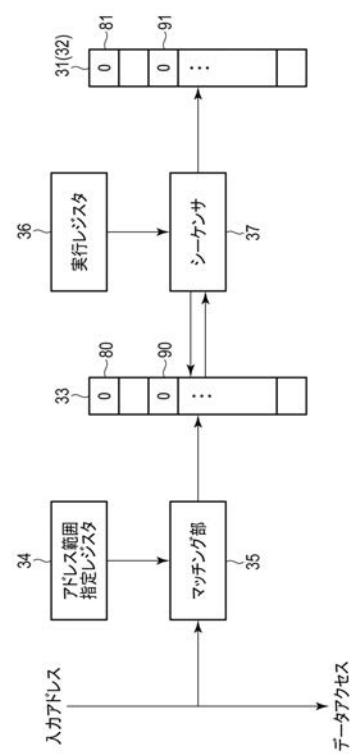

図3は、キャッシュコントローラ20の構成を示すブロック図である。図3に示すように、キャッシュコントローラ20は、複数のデータアレイ(データ配列:data array)31～33を有する。データアレイは、バリッドビット(valid bit)データアレイ(以下、VBデータアレイ)31、ダーティビット(dirty bit)データアレイ(以下、DBデータアレイ)32、及び予約ビットデータアレイ(以下、RBデータアレイ)33を含む。20

## 【0014】

図4は、各データアレイ31～33のそれぞれと、タグ記憶領域22のタグアドレス30との対応関係を示す図である。タグアドレス30は、キャッシュラインのアドレスであり、メインメモリ12のアドレスに対応している。各データアレイ31～33のそれぞれは、キャッシュライン毎に1ビットのデータ(フラグ情報)を保持する。30

## 【0015】

ここで、キャッシュ・メンテナンス処理に含まれるフラッシュ処理とは、無効化処理とライトバック処理を意味する。VBデータアレイ31は、無効化処理及びフラッシュ処理により、対応するキャッシュラインのバリッドビット「1」が「0」にクリアされる。DBデータアレイ32は、フラッシュ処理により、対応するキャッシュラインのダーティビット「1」が「0」にクリアされる。また、RBデータアレイ33は、キャッシュ・メンテナンス処理(無効化処理又はフラッシュ処理)の実行を予約するためのデータアレイである。

## 【0016】

図3に戻って、キャッシュコントローラ20は、アドレス範囲指定レジスタ34、マッチング部35、実行レジスタ36、及びシーケンサ37を含む。アドレス範囲指定レジスタ34は、CPU10により設定される、キャッシュ・メンテナンス処理の指定アドレス範囲を保持する。マッチング部35は、CPU10から入力される、キャッシュの入力アドレスが、アドレス範囲指定レジスタ34に設定された指定アドレス範囲にマッチングするか否かを判定する。40

## 【0017】

実行レジスタ36は、CPU10により設定される、無効化処理の実行を指示するフラグ情報を保持する。シーケンサ37は、実行レジスタ36に設定されたフラグ情報「1」に従って、RBデータアレイ33に予約ビットがセットされているキャッシュラインに対

応するバリッドビット「0」にクリアする。また、ライトバックキャッシュの場合には、データビットを「0」にクリアする。

[キャッシング制御]

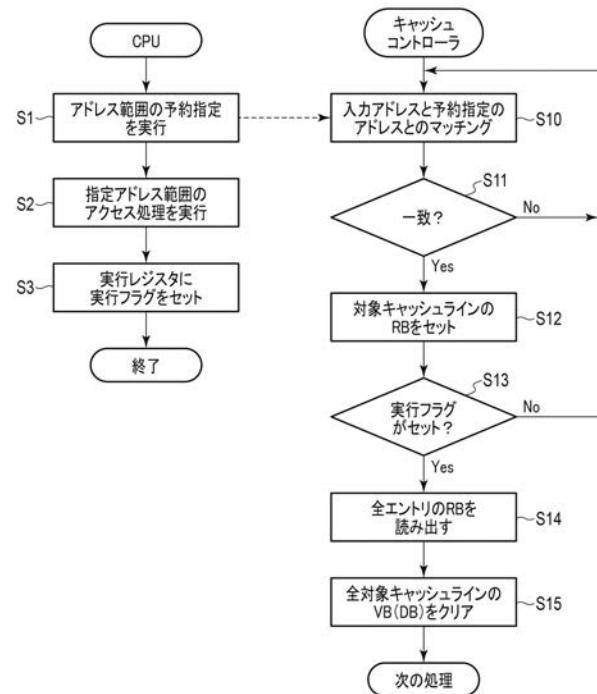

以下、図5から図10を参照して、本実施形態のキャッシングコントローラ20の動作を説明する。図5は、CPU10及びキャッシングコントローラ20の処理手順を説明するためのフローチャートである。

【0018】

まず、コンピュータ1では、例えば、CPU10は、メインメモリ12に確保されたフレームバッファに格納されている画像データ(バッファデータ)を加工し、インターフェース14を介して表示装置に当該画像データを転送する。ここで、例えばDMAコントローラ13が、次のバッファデータ(画像データ)をフレームバッファにロードする際に、キャッシングメモリ11に格納されている、前の不要なバッファデータ(画像データ)を無効化する処理が必要となる。この場合、フレームバッファのアドレス範囲に対して無効化処理が実行される。10

【0019】

なお、ライトバックキャッシングにおいて、先行してキャッシングメモリ11に書き込まれたバッファデータを、メインメモリ12に確保されたフレームバッファにフラッシュ(書き出し)する処理の場合も同様である。即ち、フレームバッファのアドレス範囲に対してフラッシュ処理が実行される。20

【0020】

前述したように、無効化処理及びフラッシュ処理を総称して、キャッシング・メンテナンス処理と呼ぶ。ここで、以下のキャッシングコントローラ20の動作として、無効化処理について説明する。20

【0021】

図5に示すように、CPU10は、指定アドレス範囲に含まれるアドレスにアクセス処理を実行する前に、当該指定アドレス範囲に対する無効化処理の予約指定を実行する(S1)。具体的には、図3に示すように、CPU10は、キャッシングコントローラ20のアドレス範囲指定レジスタ34に無効化処理の予約対象である指定アドレス範囲を設定する。ここで、CPU10は、例えば、前述したように、キャッシングメモリ11に格納された前のバッファデータが格納されたアドレス範囲を、指定アドレス範囲とする場合である。30

【0022】

図5に戻って、CPU10は、指定アドレス範囲のアドレスに対するアクセス処理を実行する(S2)。キャッシングコントローラ20は、CPU10のアクセス対象である入力アドレスをマッチング部35に入力し、マッチング部35により当該入力アドレスがアドレス範囲指定レジスタ34に設定された指定アドレス範囲にマッチングするか否かを判定する(S10)。30

【0023】

キャッシングコントローラ20は、マッチング部35により入力アドレスが指定アドレス範囲にマッチした場合には(S11のYES)、RBデータアレイ33の対応するキャッシングラインの予約ビット(RB)をセットする(S12)。これにより、RBデータアレイ33は、指定アドレス範囲にマッチする入力アドレスに対応する、全てのキャッシングラインの予約ビット(RB)がセットされる。40

【0024】

一方、CPU10は、当該アクセス処理が終了すると、実行レジスタ36に無効化処理の実行を指示するフラグ情報「1」をセットする(S3)。これにより、キャッシングコントローラ20は、無効化処理を実行することになる。

【0025】

具体的には、シーケンサ37は、実行レジスタ36にフラグ情報「1」がセットされている場合(S13のYES)、RBデータアレイ33の全エントリを検索し、セットされている予約ビットを読み出す(S14)。シーケンサ37は、VBデータアレイ31に対して50

、予約ビットがセットされている全キャッシュラインのバリッドビット（V B）を「0」にクリアする（S 1 5）。

【0 0 2 6】

これにより、予約対象である指定アドレス範囲に含まれる全キャッシュラインは、無効化される。即ち、キャッシュメモリ1 1のデータ記憶領域2 1に格納された、例えば前述した前の不要なバッファデータ（画像データ）が無効化される。

【0 0 2 7】

ここで、V Bデータアレイ3 1及びR Bデータアレイ3 3が、フリップフロップ（flip-flop）により構成されている場合には、シーケンサ3 7は、一括して全キャッシュラインのバリッドビット（V B）を「0」にクリアできる。一方、V Bデータアレイ3 1及びR Bデータアレイ3 3が、S R A Mにより構成されている場合には、シーケンサ3 7は、R Bデータアレイ3 3の全エントリを逐次的に処理することになる。10

【0 0 2 8】

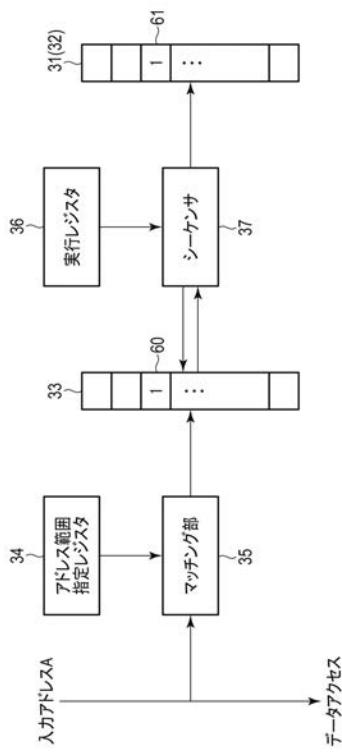

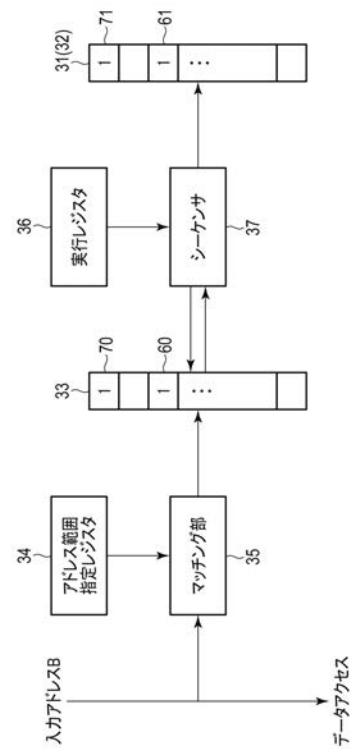

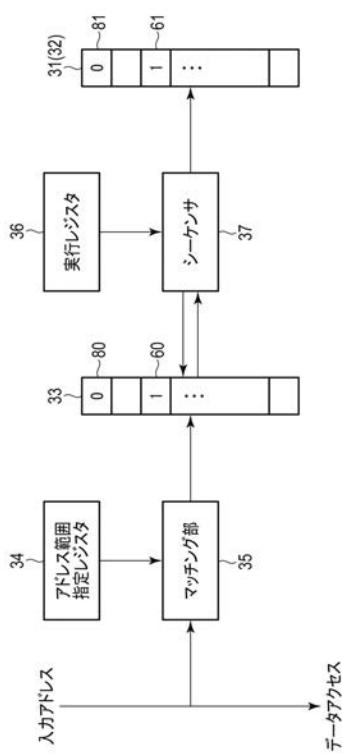

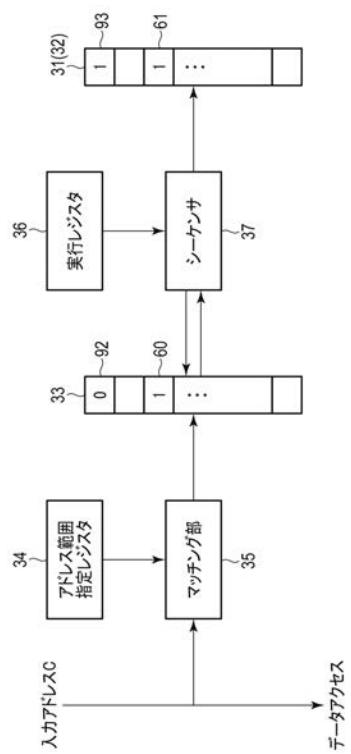

図6から図10は、以上のようなキャッシュコントローラ2 0の無効化処理において、V Bデータアレイ3 1及びR Bデータアレイ3 3の各ビットの変化を示す図である。

【0 0 2 9】

まず、図6に示すように、C P U 1 0からの入力アドレス（A）が指定アドレス範囲にマッチした場合、R Bデータアレイ3 3の対応する予約ビット（R B）6 0は「1」がセットされる。一方、V Bデータアレイ3 1では入力アドレス（A）のキャッシュラインがエントリされているため、対応するバリッドビット（V B）6 1は「1」がセットされている。20

【0 0 3 0】

次に、図7に示すように、C P U 1 0からの入力アドレス（B）が指定アドレス範囲にマッチした場合、R Bデータアレイ3 3の対応する予約ビット（R B）7 0は「1」がセットされる。一方、V Bデータアレイ3 1では入力アドレス（B）のキャッシュラインがエントリされているため、対応するバリッドビット（V B）7 1は「1」がセットされている。

【0 0 3 1】

次に、シーケンサ3 7は、実行レジスタ3 6にフラグ情報「1」がセットされている場合、R Bデータアレイ3 3からセットされている予約ビット（ここでは、図7に示す7 0）を読み出す。図8に示すように、シーケンサ3 7は、V Bデータアレイ3 1に対して、当該予約ビットに対応するキャッシュラインのバリッドビット（V B）8 1を「0」にクリアする。シーケンサ3 7は、キャッシュラインの無効化処理後に、R Bデータアレイ3 3の該当する予約ビット（R B）8 0を「0」にクリアする。30

【0 0 3 2】

同様にして、シーケンサ3 7は、R Bデータアレイ3 3からセットされている予約ビット（ここでは、図8に示す6 0）を読み出す。図9に示すように、シーケンサ3 7は、V Bデータアレイ3 1に対して、当該予約ビットに対応するキャッシュラインのバリッドビット（V B）9 1を「0」にクリアする。シーケンサ3 7は、キャッシュラインの無効化処理後に、R Bデータアレイ3 3の該当する予約ビット（R B）9 0を「0」にクリアする。40

【0 0 3 3】

ここで、図6に示す状態において、指定アドレス範囲にマッチしないアドレス（C）が入力された場合を想定する。この入力アドレスは、アドレス（A）に対応するキャッシュラインと同じエントリに格納されるアドレス（即ち、アドレス（A）、（C）はインデックス部が同じで、タグ部が異なる）とする。アドレス（C）の入力により、入力アドレス（C）に対応するキャッシュラインがキャッシュメモリ1 1に取り込まれる。この場合、アドレス（A）に対応するキャッシュラインは、キャッシュメモリ1 1から追い出されることになる。

【0 0 3 4】

10

20

30

40

50

これにより、図10に示すように、VBデータアレイ31には、入力アドレス(C)に対応するキャッシュラインに対応するバリッドビット(VB)93は「1」にセットされる。また、入力アドレス(C)は、指定アドレス範囲にマッチしないため、RBデータアレイ33の該当する予約ビット(RB)92はセットされずに、「0」である。一方、アドレス(A)に対応するキャッシュラインはキャッシュメモリ11から追い出されるため、アドレス(A)は無効化対象となる。このため、現時点では、対応する予約ビット(RB)60は「1」にセットされているが、「0」にクリアされることになる。

#### 【0035】

なお、前述したように、本実施形態は、フラッシュ処理に対しても適用できる。フラッシュ処理は、前述したように、無効化処理とライトバック処理を意味する。従って、フラッシュ処理の場合には、VBデータアレイ31に加えて、DBデータアレイ32も使用される。即ち、フラッシュ処理が実行されると、対応するキャッシュラインのダーティビット(DB)の「1」が「0」にクリアされる。

10

#### 【0036】

以上のように本実施形態によれば、指定アドレス範囲の全キャッシュラインに対応する予約ビットを予約ビットデータアレイ(RBデータアレイ)に設定することにより、全キャッシュラインに対するキャッシュ・メンテナンス処理を、タグアドレスを読み出すことなく、高速に実行することが可能となる。特に、指定アドレス範囲が広い場合には、有効である。

20

#### 【0037】

従来のキャッシュ・メンテナンス処理では、「アドレス範囲(byte) / キャッシュラインサイズ(byte)」回のデータ検索が必要であった。これに対して、本実施形態は、全キャッシュラインに対応する予約ビットの検索により、キャッシュ・メンテナンス処理に要する実行時間の短縮化を実現できる。特に、RBデータアレイをフリップフロップにより構成することで、1サイクルで指定アドレス範囲の処理を実行することができるため、キャッシュ・メンテナンス処理の高速化が可能となる。また、タグアドレスを読み出し処理が不要であるため、キャッシュ・メンテナンス処理に伴う消費電力の低減化を実現できる。

また、RBデータアレイをSRAMにより構成する場合には、逐次実行となるため、SRAMのエントリ数分のサイクル数がかかるが、「アドレス範囲(byte) / キャッシュラインサイズ(byte)」よりも少ない場合には、同様に、実行時間の短縮化及びキャッシュ・メンテナンス処理に伴う消費電力の低減化を実現できる。

30

#### 【0038】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【符号の説明】

#### 【0039】

40

- 1 … コンピュータ、10 … プロセッサ(CPU)、11 … キャッシュメモリ、

- 12 … メインメモリ、13 … DMAコントローラ、14 … インターフェース、

- 20 … キャッシュコントローラ、31 … バリッドビット(VB)データアレイ、

- 32 … ダーティビット(DB)データアレイ、

- 33 … 予約ビット(RB)データアレイ。

【図1】

【図3】

【図2】

【図4】

【図5】

【図 6】

【図 7】

【図 8】

【図 9】

【図10】

---

フロントページの続き

(74)代理人 100189913

弁理士 鵜飼 健

(72)発明者 坂本 伸昭

東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内

F ターム(参考) 5B205 KK16 LL15 MM01 MM03 NN42 NN43 PP03 PP21 QQ11