(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-82729

(P2016-82729A)

(43) 公開日 平成28年5月16日(2016.5.16)

(51) Int.Cl.

HO2M 3/155 (2006.01)

F 1

HO2M 3/155

HO2M 3/155

テーマコード(参考)

P 5H73O

V

審査請求 有 請求項の数 6 O L (全 22 頁)

(21) 出願番号

特願2014-212227 (P2014-212227)

(22) 出願日

平成26年10月17日 (2014.10.17)

(71) 出願人 000003207

トヨタ自動車株式会社

愛知県豊田市トヨタ町1番地

110001210

特許業務法人Y K I 国際特許事務所

井手 晓彦

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

浜田 英嗣

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

篠原 正俊

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

最終頁に続く

(54) 【発明の名称】電源システム

## (57) 【要約】

【課題】2つのパルス幅変調制御信号によって2つのバッテリの電圧変換制御を行う電源システムの騒音を低減する。

【解決手段】2つのパルス幅変調制御信号(PWM1, PWM2)によって2つのバッテリ(B1(20)、B2(23))の電圧変換制御を行う電圧変換器10を用いた電源システム100において、PWM1の第1ハイレベル期間とPWM2の第2ハイレベル期間とが重ならないように、PWM1とPWM2との位相を制御する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1バッテリと、

第2バッテリと、

前記第1バッテリまたは前記第2バッテリのいずれか一方または両方と出力電路との間で双方向に電圧変換を行うと共に、前記出力電路に対する前記第1バッテリおよび前記第2バッテリの接続を直列または並列に切換える複数のスイッチング素子を含む電圧変換器と、

前記複数のスイッチング素子をパルス幅変調制御に従ってオン・オフする制御部と、を含む電源システムであって、

前記出力電路は、第1の電路と前記第1の電路よりも電位の低い第2の電路とを含み、

前記複数のスイッチング素子は、前記第1の電路から前記第2の電路に向かって直列に設けられた第1、第2、第3、第4スイッチング素子を含み、

前記第1バッテリは、前記第3および前記第4スイッチング素子と並列に接続され、

前記第2バッテリは、前記第2および前記第3スイッチング素子と並列に接続され、

前記制御部は、前記第1バッテリと前記出力電路との間に形成される第1電圧変換回路による第1電圧変換を制御する第1パルス幅変調制御信号のハイレベル期間である第1ハイレベル期間と、前記第2バッテリと前記出力電路との間に形成される第2電圧変換回路による第2電圧変換を制御する第2パルス幅変調制御信号のハイレベル期間である第2ハイレベル期間との合計期間である合計ハイレベル期間が、各パルス幅変調制御信号の各ハイレベル期間と各ローレベル期間の合計期間であるデューティサイクル期間よりも短い場合に、前記第1パルス幅変調制御信号の前記第1ハイレベル期間と前記第2パルス幅変調制御信号の前記第2ハイレベル期間とが重ならないように、各パルス幅変調制御信号の位相を制御する電源システム。

**【請求項 2】**

請求項1に記載の電源システムであって、

前記制御部は、前記各パルス幅変調制御信号の前記各ハイレベル期間がそれぞれ前記デューティサイクル期間の50%未満である場合、前記各パルス幅変調制御信号の位相をデューティサイクル期間の半期間毎に前記各ハイレベル期間が交互に発生するように位相を制御する電源システム。

**【請求項 3】**

第1バッテリと、

第2バッテリと、

前記第1バッテリまたは前記第2バッテリのいずれか一方または両方と出力電路との間で双方向に電圧変換を行うと共に、前記出力電路に対する前記第1バッテリおよび前記第2バッテリの接続を直列または並列に切換える複数のスイッチング素子を含む電圧変換器と、

前記複数のスイッチング素子をパルス幅変調制御に従ってオン・オフする制御部と、を含む電源システムであって、

前記出力電路は、第1の電路と前記第1の電路よりも電位の低い第2の電路とを含み、

前記複数のスイッチング素子は、前記第1の電路から前記第2の電路に向かって直列に設けられた第1、第2、第3、第4スイッチング素子を含み、

前記第1バッテリは、前記第3および前記第4スイッチング素子と並列に接続され、

前記第2バッテリは、前記第2および前記第3スイッチング素子と並列に接続され、

前記制御部は、前記第1バッテリと前記出力電路との間に形成される第1電圧変換回路による第1電圧変換を制御する第1パルス幅変調制御信号のハイレベル期間である第1ハイレベル期間と、前記第2バッテリと前記出力電路との間に形成される第2電圧変換回路による第2電圧変換を制御する第2パルス幅変調制御信号のハイレベル期間である第2ハイレベル期間との合計期間である合計ハイレベル期間が、各パルス幅変調制御信号の各ハイレベル期間と各ローレベル期間の合計期間であるデューティサイクル期間よりも短い場

合に、

前記第1パルス幅変調制御信号の前記第1ハイレベル期間と前記第2パルス幅変調制御信号の前記第2ハイレベル期間とが重なるように各パルス幅変調制御信号の位相を制御する第1の制御と、前記第1パルス幅変調制御信号の前記第1ハイレベル期間と前記第2パルス幅変調制御信号の前記第2ハイレベル期間とが重ならないように各パルス幅変調制御信号の位相を制御する第2の制御と、を混在させて位相制御を行う電源システム。

**【請求項4】**

第1バッテリと、

第2バッテリと、

前記第1バッテリまたは前記第2バッテリのいずれか一方または両方と出力電路との間で双方に電圧変換を行うと共に、前記出力電路に対する前記第1バッテリおよび前記第2バッテリの接続を直列または並列に切換える複数のスイッチング素子を含む電圧変換器と、

前記複数のスイッチング素子をパルス幅変調制御に従ってオン・オフする制御部と、を含む電源システムであって、

前記出力電路は、第1の電路と前記第1の電路よりも電位の低い第2の電路とを含み、

前記複数のスイッチング素子は、前記第1の電路から前記第2の電路に向かって直列に設けられた第1、第2、第3、第4スイッチング素子を含み、

前記第1バッテリは、前記第3および前記第4スイッチング素子と並列に接続され、

前記第2バッテリは、前記第2および前記第3スイッチング素子と並列に接続され、

前記制御部は、前記第1バッテリと前記出力電路との間に形成される第1電圧変換回路による第1電圧変換を制御する第1パルス幅変調制御信号がローレベルの期間に、前記第2バッテリと前記出力電路との間に形成される第2電圧変換回路による第2電圧変換を制御する第2パルス幅変調制御信号をローレベルからハイレベルとした後にローレベルに戻すように変化させる電源システム。

**【請求項5】**

請求項4に記載の電源システムであって、

前記制御部は、第1三角波と第1の閾値に基づいて第1パルス幅変調制御信号を生成し、第2三角波と第2の閾値に基づいて第2パルス幅変調制御信号を生成し、

第1パルス幅変調制御信号がローレベルの期間に、前記第2三角波の周波数を前記第1三角波の周波数よりも高くする電源システム。

**【請求項6】**

請求項5に記載の電源システムであって、

前記制御部は、第1パルス幅変調制御信号がローレベルの期間に、前記第2三角波の値が前記第2の閾値を超える期間と超えない期間とができるように、前記第2の三角波の周波数を前記第1三角波の周波数よりも高くする電源システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、電源システムの構造、特に2電源を並列接続してPWM制御により電圧変換するシステムの制御装置に関する。

**【背景技術】**

**【0002】**

従来からスイッチング素子をパルス幅変調制御でオン・オフ動作させてバッテリの電圧変換を行う電圧変換器が多く用いられているが、近年、4つのスイッチング素子によって構成され、スイッチング素子のオン・オフ動作の組み合わせによって2つのバッテリを直列に接続して電圧変換するシリーズモードと、2つのバッテリを並列に接続して電圧変換するパラレルモードとを備える電圧変換器を用いた電源システムが提案されている（例えば、特許文献1参照）。このような電源システムに用いられる電圧変換器をパラレルモードで動作させる際には、2つのバッテリに対応する2つのパルス幅変調制御信号に従って

10

20

30

40

50

各スイッチング素子をオン・オフさせて各バッテリの電圧変換制御を行う。特許文献1では、このような電圧変換器をパラレルモードで動作させる際に、2つのパルス幅変調制御信号の位相を変化させてスイッチング素子の損失を抑制することが提案されている。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【特許文献1】特開2013-13234号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

ところで、スイッチング素子のオン・オフ動作によりバッテリの電圧変換を行う従来の電圧変換器では、スイッチング素子のオン・オフ動作に起因して電磁音が発生することが知られている。この電磁音が人間の可聴域に入ると耳障りな騒音となるため、例えば、パルス幅変調制御のキャリア周波数を高くして電磁音の周波数を可聴域より高くすることにより騒音を低減する方法等が検討されている。しかし、特許文献1に記載されたような2つのパルス幅変調制御信号によって2つのバッテリの電圧変換制御を行う電圧変換器を用いた電源システムの騒音低減については十分には検討されていなかった。

**【0005】**

そこで、本発明は、2つのパルス幅変調制御信号によって2つのバッテリの電圧変換制御を行う電源システムの騒音を低減することを目的とする。

10

20

**【課題を解決するための手段】**

**【0006】**

本発明の電源システムは、第1バッテリと、第2バッテリと、前記第1バッテリまたは前記第2バッテリのいずれか一方または両方と出力電路との間に双向に電圧変換を行うと共に、前記出力電路に対する前記第1バッテリおよび前記第2バッテリの接続を直列または並列に切換える複数のスイッチング素子を含む電圧変換器と、前記複数のスイッチング素子をパルス幅変調制御に従ってオン・オフする制御部と、を含む電源システムであって、前記出力電路は、第1の電路と前記第1の電路よりも電位の低い第2の電路とを含み、前記複数のスイッチング素子は、前記第1の電路から前記第2の電路に向かって直列に設けられた第1、第2、第3、第4スイッチング素子を含み、前記第1バッテリは、前記第3および前記第4スイッチング素子と並列に接続され、前記第2バッテリは、前記第2および前記第3スイッチング素子と並列に接続され、前記制御部は、前記第1バッテリと前記出力電路との間に形成される第1電圧変換回路による第1電圧変換を制御する第1パルス幅変調制御信号のハイレベル期間である第1ハイレベル期間と、前記第2バッテリと前記出力電路との間に形成される第2電圧変換回路による第2電圧変換を制御する第2パルス幅変調制御信号のハイレベル期間である第2ハイレベル期間との合計期間である合計ハイレベル期間が、各パルス幅変調制御信号の各ハイレベル期間と各ローレベル期間の合計期間であるデューティサイクル期間よりも短い場合に、前記第1パルス幅変調制御信号の前記第1ハイレベル期間と前記第2パルス幅変調制御信号の前記第2ハイレベル期間とが重ならないように、各パルス幅変調制御信号の位相を制御することを特徴とする。

30

**【0007】**

本発明の電源システムにおいて、前記制御部は、前記各パルス幅変調制御信号の前記各ハイレベル期間がそれぞれ前記デューティサイクル期間の50%未満である場合、前記各パルス幅変調制御信号の位相をデューティサイクル期間の半期間毎に前記各ハイレベル期間が交互に発生するように位相を制御することとしても好適である。

40

**【0008】**

本発明の電源システムは、第1バッテリと、第2バッテリと、前記第1バッテリまたは前記第2バッテリのいずれか一方または両方と出力電路との間に双向に電圧変換を行うと共に、前記出力電路に対する前記第1バッテリおよび前記第2バッテリの接続を直列または並列に切換える複数のスイッチング素子を含む電圧変換器と、前記複数のスイッチ

50

グ素子をパルス幅変調制御に従ってオン・オフする制御部と、を含む電源システムであって、前記出力電路は、第1の電路と前記第1の電路よりも電位の低い第2の電路とを含み、前記複数のスイッチング素子は、前記第1の電路から前記第2の電路に向かって直列に設けられた第1、第2、第3、第4スイッチング素子を含み、前記第1バッテリは、前記第3および前記第4スイッチング素子と並列に接続され、前記第2バッテリは、前記第2および前記第3スイッチング素子と並列に接続され、前記制御部は、前記第1バッテリと前記出力電路との間に形成される第1電圧変換回路による第1電圧変換を制御する第1パルス幅変調制御信号のハイレベル期間である第1ハイレベル期間と、前記第2バッテリと前記出力電路との間に形成される第2電圧変換回路による第2電圧変換を制御する第2パルス幅変調制御信号のハイレベル期間である第2ハイレベル期間との合計期間である合計ハイレベル期間が、各パルス幅変調制御信号の各ハイレベル期間と各ローレベル期間の合計期間であるデューティサイクル期間よりも短い場合に、前記第1パルス幅変調制御信号の前記第1ハイレベル期間と前記第2パルス幅変調制御信号の前記第2ハイレベル期間とが重なるように各パルス幅変調制御信号の位相を制御する第1の制御と、前記第1パルス幅変調制御信号の前記第1ハイレベル期間と前記第2パルス幅変調制御信号の前記第2ハイレベル期間とが重ならないように各パルス幅変調制御信号の位相を制御する第2の制御と、を混在させて位相制御を行うことを特徴とする。

10

## 【0009】

本発明の電源システムは、第1バッテリと、第2バッテリと、前記第1バッテリまたは前記第2バッテリのいずれか一方または両方と出力電路との間で双方向に電圧変換を行うと共に、前記出力電路に対する前記第1バッテリおよび前記第2バッテリの接続を直列または並列に切換える複数のスイッチング素子を含む電圧変換器と、前記複数のスイッチング素子をパルス幅変調制御に従ってオン・オフする制御部と、を含む電源システムであって、前記出力電路は、第1の電路と前記第1の電路よりも電位の低い第2の電路とを含み、前記複数のスイッチング素子は、前記第1の電路から前記第2の電路に向かって直列に設けられた第1、第2、第3、第4スイッチング素子を含み、前記第1バッテリは、前記第3および前記第4スイッチング素子と並列に接続され、前記第2バッテリは、前記第2および前記第3スイッチング素子と並列に接続され、前記制御部は、前記第1バッテリと前記出力電路との間に形成される第1電圧変換回路による第1電圧変換を制御する第1パルス幅変調制御信号がローレベルの期間に、前記第2バッテリと前記出力電路との間に形成される第2電圧変換回路による第2電圧変換を制御する第2パルス幅変調制御信号をローレベルからハイレベルとした後にローレベルに戻すように変化させることを特徴とする。

20

## 【0010】

本発明の電源システムにおいて、前記制御部は、第1三角波と第1の閾値に基づいて第1パルス幅変調制御信号を生成し、第2三角波と第2の閾値に基づいて第2パルス幅変調制御信号を生成し、第1パルス幅変調制御信号がローレベルの期間に、前記第2三角波の周波数を前記第1三角波の周波数よりも高くすることとしても好適である。

30

## 【0011】

本発明の電源システムにおいて、前記制御部は、第1パルス幅変調制御信号がローレベルの期間に、前記第2三角波の値が前記第2の閾値を超える期間と超えない期間とができるように、前記第2の三角波の周波数を前記第1三角波の周波数よりも高くすることとしても好適である。

40

## 【発明の効果】

## 【0012】

本発明は、2つのパルス幅変調制御信号によって2つのバッテリの電圧変換制御を行う電圧変換器を用いた電源システムの騒音を低減することができるという効果を奏する。

## 【図面の簡単な説明】

## 【0013】

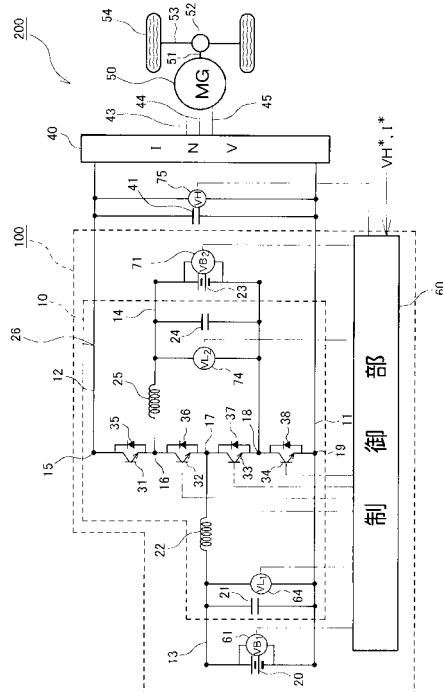

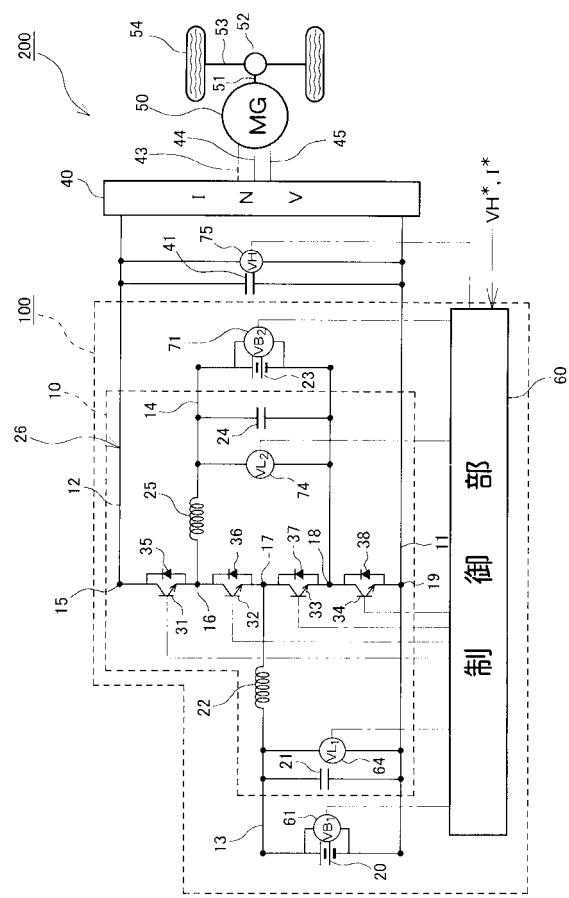

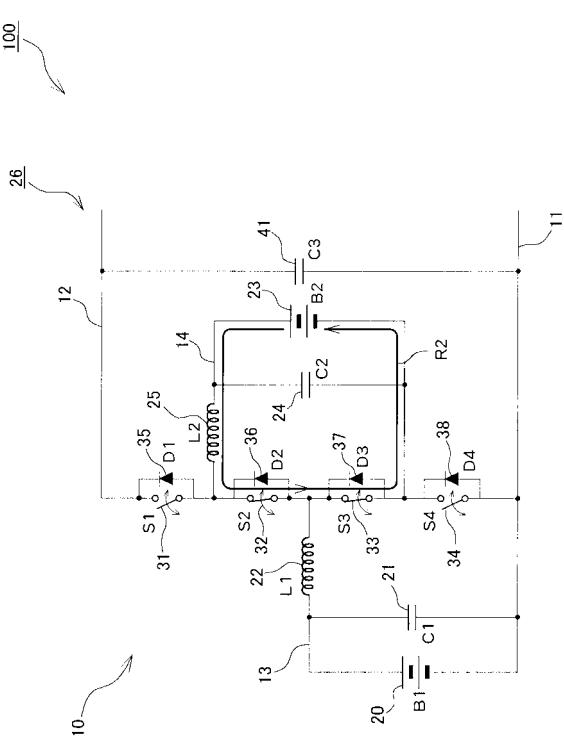

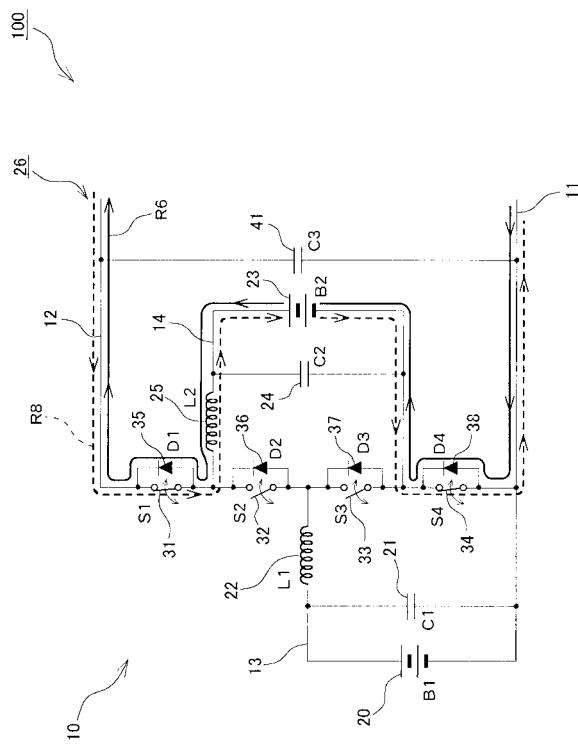

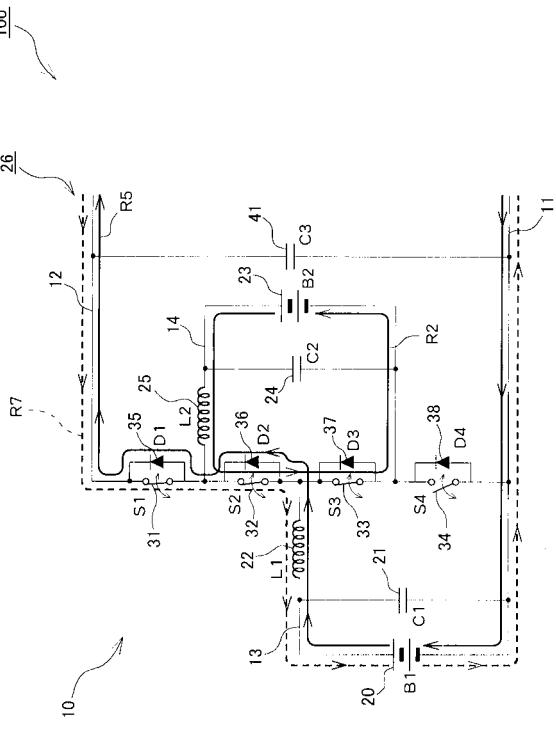

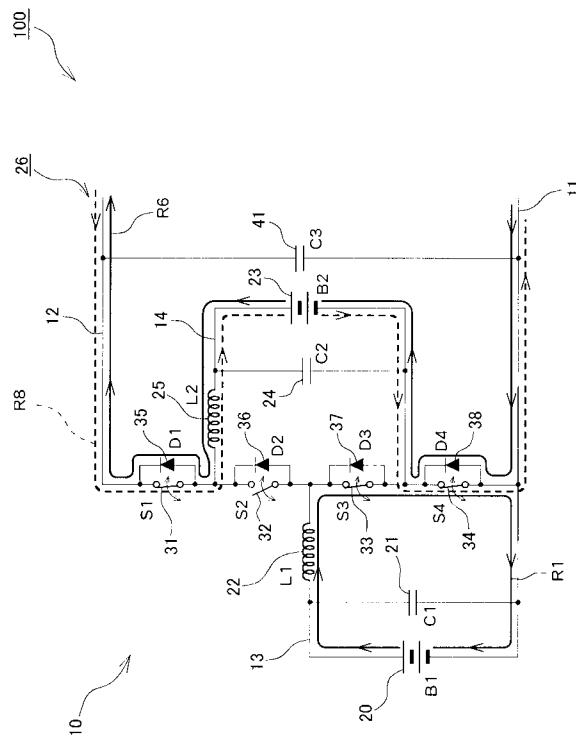

【図1】電動車両に搭載した本発明の電源システムの構成を示すシステム系統図である。

50

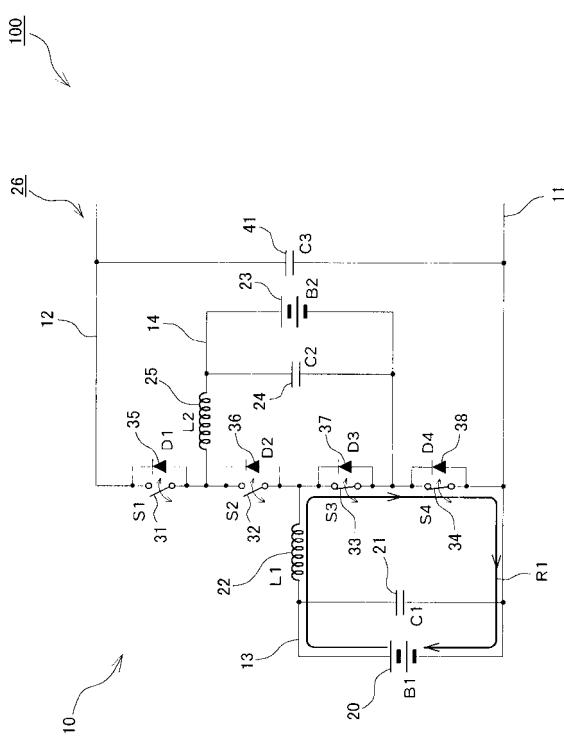

【図2】本発明の電源システムの基本動作における第1バッテリにより第1リアクトルをチャージする際の電流の流れを示す説明図である。

【図3】本発明の電源システムの基本動作における第1リアクトルにチャージした電力を出力電路に出力する際の電流の流れを示す説明図である。

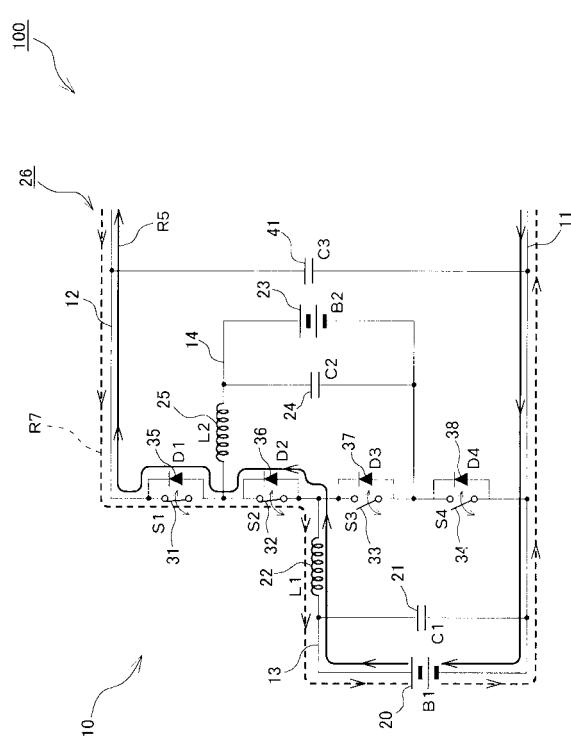

【図4】本発明の電源システムの基本動作における第2バッテリにより第2リアクトルをチャージする際の電流の流れを示す説明図である。

【図5】本発明の電源システムの基本動作における第2リアクトルにチャージした電力を出力電路に出力する際の電流の流れを示す説明図である。

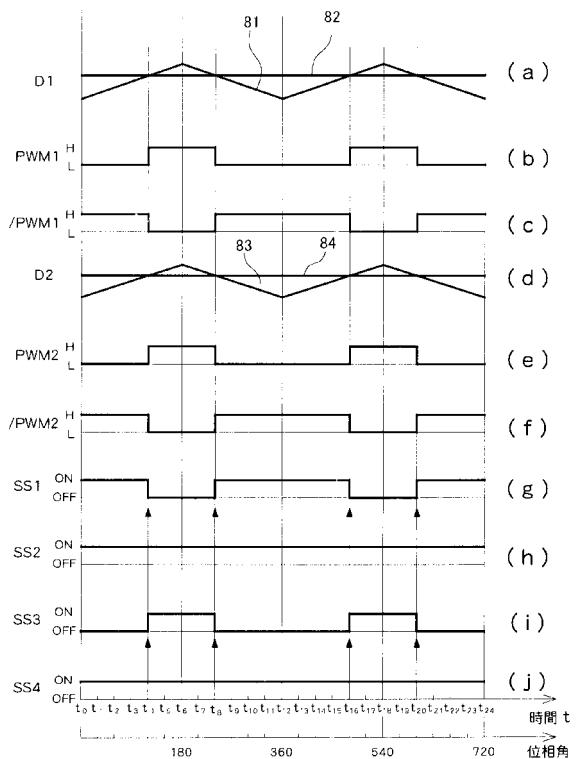

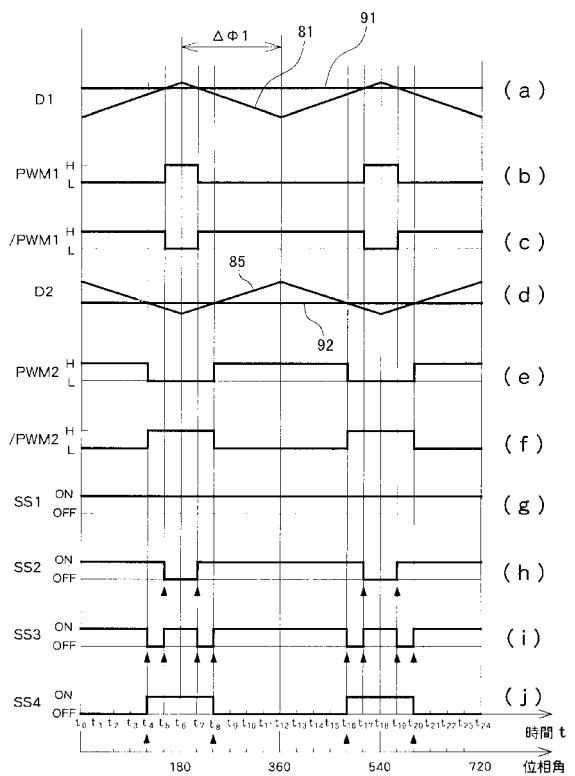

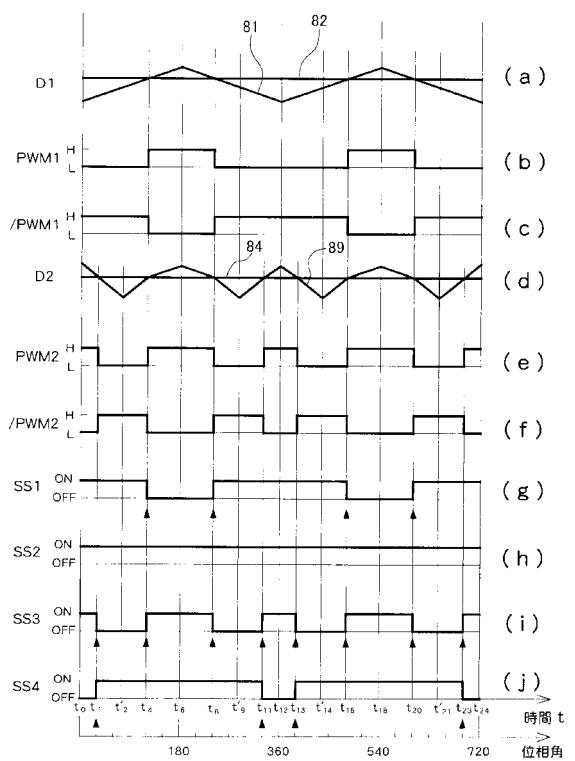

【図6】本発明の電源システムの基本動作の際のパルス幅変調制御信号及びスイッチング素子制御信号を示すタイムチャートである。 10

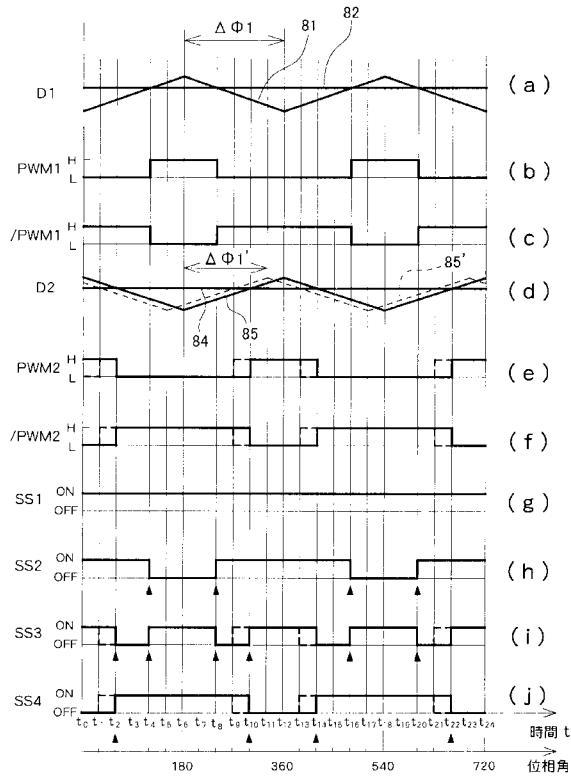

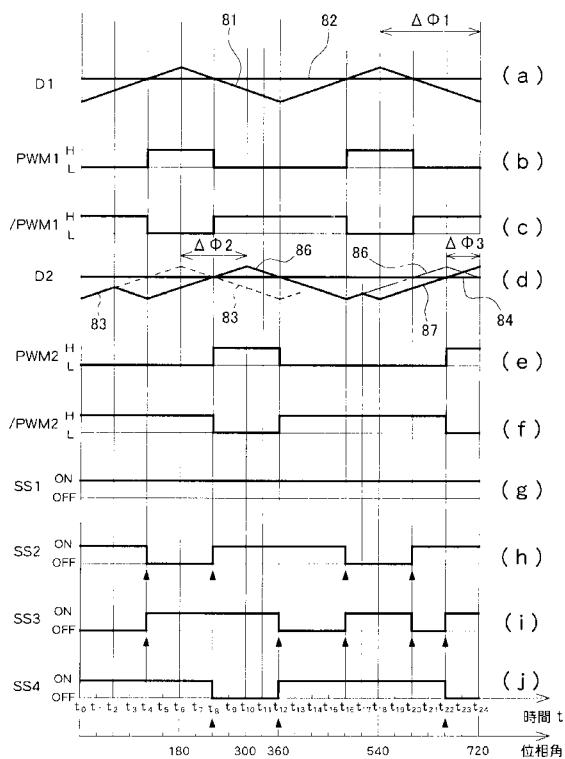

【図7】本発明の電源システムにおいて、PWM1に対するPWM2の位相を180度または150度ずらした際のパルス幅変調制御信号とスイッチング素子制御信号を示すタイムチャートである。

【図8】図7に示す動作において、第2リアクトルへのチャージと第1バッテリからの電力出力の際の電流の流れを示す説明図である。

【図9】図7に示す動作において、第1リアクトルへのチャージと第2バッテリからの電力出力の際の電流の流れを示す説明図である。

【図10】本発明の電源システムにおいて、PWM2のデューティ比が50%以上でPWM1の第1ハイレベル期間とPWM2の第2ハイレベル期間の合計期間がデューティサイクル期間よりも短い場合にPWM1に対するPWM2の位相を180度ずらした際のパルス幅変調制御信号とスイッチング素子制御信号のタイミングを示すタイムチャートである。 20

【図11】本発明の電源システムにおいて、第2パルス幅変調制御信号の位相をスケジュールによって変化させた際のパルス幅変調制御信号とスイッチング素子制御信号を示すタイムチャートである。

【図12】本発明の電源システムにおいて、第2三角波の周波数を一時的に増加させた際のパルス幅変調制御信号とスイッチング素子制御信号とを示すタイムチャートである。

#### 【発明を実施するための形態】

##### 【0014】

以下、図面を参照しながら本発明の電源システム100について説明する。以下の実施形態では、電源システム100は電動車両200のモータジェネレータ50に電力を供給するものとして説明するが、汎用機械のモータ或いはモータジェネレータに電力を供給するものであってもよい。 30

##### 【0015】

図1に示すように、本発明の電源システム100は、第1バッテリ20と、第2バッテリ23と、複数のスイッチング素子31～34及び第1リアクトル22、第2リアクトル25、第1コンデンサ21、第2コンデンサ24、出力電路26を含む電圧変換器10と、複数のスイッチング素子31～34をオン・オフする制御部60とを含んでいる。出力電路26には平滑コンデンサ41とインバータ40とが接続され、インバータ40には電動車両200を駆動するモータジェネレータ50が接続されている。なお、図1中的一点鎖線は信号線を示す。 40

##### 【0016】

電圧変換器10の出力電路26は、電圧変換器10で昇圧した高電圧を出力する高圧電路12と、各バッテリ20, 23のマイナス側に接続され、高圧電路よりも電位の低い基準電路11とを含み、複数のスイッチング素子31～34は、高圧電路12から基準電路11に向って直列に接続され、各スイッチング素子31～34には、それぞれダイオード35～38が逆並列に接続されている。また、電圧変換器10は、スイッチング素子32とスイッチング素子33との間の第2接続点17と基準電路11との間を接続する第1電路13と、スイッチング素子31とスイッチング素子32との間の第1接続点16と、スイッチング素子33とスイッチング素子34との間の第3接続点18との間を接続する第50

2電路14と、を有している。第1バッテリ20と第1リアクトル22とは第1電路13の上に直列に配置され、第2バッテリ23と第2リアクトル25とは第2電路14の上に直列に配置されており、第1コンデンサ21は第1バッテリ20と並列に接続され、第2コンデンサ24は第2バッテリ23と並列に接続されている。また、平滑コンデンサ41は、高圧電路12と基準電路11との間に接続されている。このように、第1バッテリ20は、スイッチング素子33, 34と並列に接続され、第2バッテリ23は、スイッチング素子32, 33と並列に接続されている。

#### 【0017】

第1, 第2バッテリ20, 23には、電圧VB1, VB2を検出する電圧センサ61, 71が取り付けられ、第1電路13と基準電路11との間には第1コンデンサ21の両端の電圧VL1を検出する電圧センサ64が取り付けられ、第2電路14には、第2コンデンサ24の両端の電圧VL2を検出する電圧センサ74が取り付けられており、高圧電路12と基準電路11との間には、平滑コンデンサ41の両端の電圧VHを検出する電圧センサ75が取り付けられている。10

#### 【0018】

インバータ40は、内部に図示しない複数のスイッチング素子を備え、各スイッチング素子をオン・オフ動作させて電圧変換器10の出力電路26（基準電路11と高圧電路12とで構成される）から出力された直流電力をU, V, Wの三相交流電力に変換して各相の出力線43, 44, 45から出力する。U相、V相、W相の各出力線43, 44, 45はモータジェネレータ50に接続されている。モータジェネレータ50の出力軸51はギヤ装置52に接続され、ギヤ装置52には車軸53が接続され、車軸53には車輪54が取り付けられている。20

#### 【0019】

制御部60は、演算及び情報処理を行うCPUと、制御プログラム及び制御データを格納する記憶部と、各機器、センサが接続される機器・センサインターフェースとを含み、CPUと記憶部と機器・センサインターフェースとは相互にデータバスで接続されるコンピュータである。電圧変換器10の各スイッチング素子31～34は、機器・センサインターフェースを介して制御部60に接続され、制御部60の指令によってオン・オフ動作する。また、電圧センサ61, 64, 71, 74, 75は機器・センサインターフェースを介して制御部60に接続され、各センサによって検出されたデータは制御部60に入力される。また、制御部60には、他の制御装置から高電圧指令値VH\*、電流指令値I\*が入力される。30

#### 【0020】

##### <電圧変換器10の基本動作>

電圧変換器10は、4つのスイッチング素子31～34のオン・オフ動作パターンを切換えることにより、第1、第2バッテリ20, 23の電圧を昇圧して出力電路26に出力或いは出力電路26の電圧を降圧して第1、第2バッテリ20, 23に充電するように、第1、第2バッテリ20, 23のいずれか一方または両方と出力電路26との間で双方向に電圧変換を行うと共に、出力電路26に対する第1、第2バッテリ20, 23の接続を直列と並列との間で切換え可能である。以下、図2～図4を参照して第1、第2バッテリ20, 23の接続を並列とした場合の電圧変換器10の基本動作について簡単に説明する。なお、以下の説明では、第1スイッチング素子31は、記号S1と符号31を用いてS1(31)と記載し、第2スイッチング素子32は、記号S2と符号32を用いてS2(32)と記載し、第3スイッチング素子33は、記号S3と符号33を用いてS3(33)と記載し、第4スイッチング素子34は、記号S4と符号34を用いてS4(34)と記載する。また、各スイッチング素子31～34に逆並列に接続されている各ダイオード35～38は、記号D1～D4と符号35～38を用いてD1(35)～D4(38)と記載する。同様に、第1バッテリ20、第2バッテリ23はそれぞれ記号B1, B2と符号20, 23を用いてB1(20)、B2(23)と記載し、第1、第2コンデンサ21, 24はそれぞれ記号C1, C2と符号21, 24を用いてC1(21)、C2(24)。4050

と記載し、第1、第2リアクトル22、25はそれぞれ記号L1、L2と符号22、25を用いてL1(22)、L2(25)と記載する。また、各スイッチング素子31～34は、オンとなると図1の矢印の方向にのみ電流が流れ、矢印と反対方向には電流が流れないIGBT等の半導体素子であるが、図3、4、6、7ではスイッチング素子31～34のオン・オフの状態が表示できるように単純なオン・オフスイッチとして図示する。

#### 【0021】

< B1(20), B2(23)並列接続の場合の昇降圧動作 >

図2～図5を参照して電圧変換器10におけるB1(20), B2(23)を並列接続した場合の昇降圧動作について説明する。

#### 【0022】

10

まず、図2、図3を参照して、B1(20)と出力電路26との間の第1電圧変換について説明する。図2に示すように、S3(33)、S4(34)のペアをオンにし、S1(31)、S2(32)のペアをオフとすることによって、[B1(20) L1(22) S3(33) S4(34) B1(20)]と電流が流れる回路R1が形成され、B1(20)から出力された電力は回路R1を還流してL1(22)にチャージされる。次に、図3に示すように、S3(33)、S4(34)のペアをオフにし、S1(31)、S2(32)のペアをオンとすることによって、[B1(20) L1(22) D2(36) D1(35) 高圧電路12 基準電路11 B1(20)]と電流が流れる回路R5(実線で示す)と、[高圧電路12 S1(31) S2(32) L1(22) B1(20) 基準電路11 高圧電路12]と電流が流れる回路R7(破線で示す)とが形成され、L1(22)にチャージされた電力は回路R5を通って出力電路26に出力され、モータジェネレータ50からの回生電力は、回路R7(破線で示す)を通ってB1(20)に充電される。また、回生時にS1(31)、S2(32)のペアをオフとした場合、L1(22)にチャージされた電力は回路R1と逆向きの電流回路によってB1(20)へ回生される。そして、S3(33)、S4(34)のペアがオンされている一方で、S1(31)、S2(32)の少なくとも一方がオフされている第1オン期間と、S1(31)、S2(32)がオンされる一方でS3(33)、S4(34)の少なくとも一方がオフとされる第1オフ期間とを交互に繰り返すことにより、B1(20)の電圧VB1を昇圧して出力電路26に出力する。

20

#### 【0023】

30

このように、電圧変換器10では、B1(20)に対してはS3(33)、S4(34)のペアをL1(22)のチャージの際にオンとするスイッチング素子(第1の等価的な下アーム素子)とし、S1(31)、S2(32)のペアを電力出力の際にオンとするスイッチング素子(第1の等価的な上アーム素子)とする双方向の昇圧チョッパ回路が形成される。この昇圧チョッパ回路は、図2、3を参照して説明した回路R1と回路R5、R7であり、B1(20)と出力電路26との間に形成されてB1(20)と出力電路26との間の第1電圧変換を行う第1電圧変換回路である。

#### 【0024】

40

第1電圧変換回路における第1オン期間と第1オフ期間との合計期間はデューティサイクル期間であり、デューティサイクル期間に対する第1オン期間の比率は第1デューティ比D1である。第1電圧変換回路において、B1(20)の電圧VB1を高電圧指令値VH\*に昇圧する際には、第1デューティ比D1と、高電圧指令値VH\*、B1(20)の電圧VB1との関係が、

$$VH^* = [1 / (1 - D1)] \times VB1 \quad \text{----- (式1)}$$

となるように、S1(31)、S2(32)のペア(第1の等価的な上アーム素子)とS3(33)、S4(34)のペア(第1の等価的な下アーム素子)とをパルス幅変調制御(PWM制御)する。実際の制御では、VB1に代えてC1(21)の両端の電圧であるVL1を用いて、

$$VH^* = [1 / (1 - D1)] \times VL1 \quad \text{----- (式2)}$$

となるように、S1(31)、S2(32)のペア(第1の等価的な上アーム素子)とS

50

3 ( 3 3 )、 S 4 ( 3 4 ) のペア ( 第 1 の等価的な下アーム素子 ) とを PWM 制御する。この PWM 制御の制御信号を第 1 パルス幅変調制御信号 ( PWM 1 ) という。

#### 【 0 0 2 5 】

次に、図 4、図 5 を参照して、B 2 ( 2 3 ) と出力電路 2 6 との間の第 2 電圧変換について説明する。図 4 に示すように、S 2 ( 3 2 )、S 3 ( 3 3 ) のペアをオンにし、S 1 ( 3 1 )、S 4 ( 3 4 ) のペアをオフとすることによって、[ B 2 ( 2 3 ) L 2 ( 2 5 ) S 2 ( 3 2 ) S 3 ( 3 3 ) B 2 ( 2 3 ) ] と電流が流れる回路 R 2 が形成され、B 2 ( 2 3 ) から出力された電力は回路 R 2 を還流して L 2 ( 2 5 ) にチャージされる。次に、図 5 に示すように、S 2 ( 3 2 )、S 3 ( 3 3 ) のペアをオフにし、S 1 ( 3 1 )、S 4 ( 3 4 ) のペアをオンとすることによって、[ B 2 ( 2 3 ) L 2 ( 2 5 ) D 1 ( 3 5 ) 高圧電路 1 2 基準電路 1 1 D 4 ( 3 8 ) B 2 ( 2 3 ) ] と電流が流れる回路 R 6 ( 実線で示す ) と、[ 高圧電路 1 2 S 1 ( 3 1 ) L 2 ( 2 5 ) B 2 ( 2 3 ) S 4 ( 3 4 ) 基準電路 1 1 高圧電路 1 2 ] と電流が流れる回路 R 8 ( 破線で示す ) とが形成され、L 2 ( 2 5 ) にチャージされた電力は回路 R 6 を通って出力電路 2 6 に出力され、モータジェネレータ 5 0 からの回生電力は、回路 R 8 ( 破線で示す ) を通って B 2 ( 2 3 ) に充電される。また、回生時に S 1 ( 3 1 )、S 4 ( 3 4 ) のペアをオフとした場合、L 2 ( 2 5 ) にチャージされた電力は回路 R 2 と逆向きの電流回路によって B 2 ( 2 3 ) へ回生される。そして、S 2 ( 3 2 )、S 3 ( 3 3 ) のペアがオンされている一方で、S 1 ( 3 1 )、S 4 ( 3 4 ) の少なくとも一方がオフされている第 2 オン期間と、S 1 ( 3 1 )、S 4 ( 3 4 ) がオンされる一方で S 2 ( 3 2 )、S 3 ( 3 3 ) の少なくとも一方がオフとされる第 2 オフ期間とを交互に繰り返すことにより、B 2 ( 2 3 ) の電圧 V B 2 を昇圧して出力電路 2 6 に出力する。

10

#### 【 0 0 2 6 】

このように、電圧変換器 1 0 では、B 2 ( 2 3 ) に対しては S 2 ( 3 2 )、S 3 ( 3 3 ) のペアを L 2 ( 2 5 ) のチャージの際にオンとするスイッチング素子 ( 第 2 の等価的な下アーム素子 ) とする一方で、S 1 ( 3 1 )、S 4 ( 3 4 ) のペアを電力出力の際にオンとするスイッチング素子 ( 第 2 の等価的な上アーム素子 ) とする双方向の昇圧チョッパ回路が形成される。この昇圧チョッパ回路は、図 4、5 を参照して説明した回路 R 2 と回路 R 6、R 8 であり、B 2 ( 2 3 ) と出力電路 2 6 との間に形成されて B 2 ( 2 3 ) と出力電路 2 6 との間の第 2 電圧変換を行う第 2 電圧変換回路である。

20

#### 【 0 0 2 7 】

第 2 電圧変換回路における第 2 オン期間と第 2 オフ期間との合計期間はデューティサイクル期間であり、デューティサイクル期間に対する第 2 オン期間の比率は第 2 デューティ比 D 2 であり、第 2 電圧変換回路において、B 2 ( 2 3 ) の電圧 V B 2 を高電圧指令値 V H \* に昇圧する際には、第 2 デューティ比 D 2 と、高電圧指令値 V H \*、B 2 ( 2 3 ) の電圧 V B 2 との関係が、

30

$$V H^* = [ 1 / ( 1 - D 2 ) ] \times V B 2 \quad \text{----- ( 式 3 )}$$

となるように、S 1 ( 3 1 )、S 4 ( 3 4 ) のペア ( 第 2 の等価的な上アーム素子 ) と S 2 ( 3 2 )、S 3 ( 3 3 ) のペア ( 第 2 の等価的な下アーム素子 ) とをパルス幅変調制御 ( PWM 制御 ) する。実際の制御では、V B 2 に代えて C 2 ( 2 4 ) の両端の電圧である V L 2 を用いて、

40

$$V H^* = [ 1 / ( 1 - D 2 ) ] \times V L 2 \quad \text{----- ( 式 4 )}$$

となるように、S 1 ( 3 1 )、S 4 ( 3 4 ) のペア ( 第 2 の等価的な上アーム素子 ) と S 2 ( 3 2 )、S 3 ( 3 3 ) のペア ( 第 2 の等価的な下アーム素子 ) とを PWM 制御する。この PWM 制御の制御信号を第 2 パルス幅変調制御信号 ( PWM 2 ) という。

#### 【 0 0 2 8 】

< パルス幅変調制御信号とスイッチング素子制御信号の生成と電圧変換器の基本動作 >

次に、図 6 ( a ) から図 6 ( j ) を参照しながら第 1 パルス幅変調制御信号 ( PWM 1 ) と第 2 パルス幅変調信号 ( PWM 2 ) の生成及び、各パルス幅変調制御信号 ( PWM 1、PWM 2 ) から各スイッチング素子 S 1 ( 3 1 ) から S 4 ( 3 4 ) をオン・オフ動作さ

50

せるスイッチング素子制御信号 S S 1 ~ S S 4 を生成する方法について説明する。

#### 【0029】

図 6 ( a )、図 6 ( d )に示すように、制御部 6 0 の内部で、第 1 パルス幅変調制御信号 ( PWM1 )を生成するための所定の周波数の第 1 三角波 8 1 と、第 2 パルス幅変調制御信号 ( PWM2 )を生成するための第 2 三角波 8 3 とを発生させる。図 6 ( a ) ~ 図 6 ( j )に示す本実施形態では、第 1 三角波 8 1 と第 2 三角波 8 3 の周波数 ( 周期 )は同一であり、この周波数をキャリア周波数という。なお、図 6 ( a ) ~ 図 6 ( j )の横軸は時間又は各三角波 8 1 , 8 3 の位相角であり、一周期は位相角 360 度に対応する。また、第 1 、第 2 三角波 8 1 , 8 3 の一周期をデューティサイクル期間という。図 6 ( a ) ~ 図 6 ( j )の横軸に記載した  $t_0$  から  $t_{24}$  は時刻を表し、各時刻の間隔は一周期或いはデューティサイクル期間を 12 等分した時間となっている。各時刻の間隔 ( 例えば、時刻  $t_0$  と時刻  $t_1$  の間 ) を 1 区間という。従って、12 区間が 1 デューティサイクル期間であり、第 1 、第 2 三角波 8 1 , 8 3 の一周期で、位相角 360 度に対応する。

10

#### 【0030】

次に、第 1 、第 2 三角波 8 1 , 8 3 の山と谷の間に直線 8 2 , 8 4 を設定する。そして、デューティサイクル期間の中で第 1 三角波 8 1 の値の方が直線 8 2 の値よりも大きくなる期間 ( ハイレベル期間 ) の割合が先に説明した第 1 デューティ比 D 1 となるように直線 8 2 の高さ ( 閾値 ) を設定する。同様に、デューティサイクル期間の中で第 2 三角波 8 3 の値の方が直線 8 4 の値よりも大きくなる期間 ( ハイレベル期間 ) の割合が先に説明した第 2 デューティ比 D 2 となるように直線 8 4 の高さ ( 閾値 ) を設定する。このように各三角波 8 1 , 8 3 、直線 ( 閾値 ) 8 2 , 8 4 を設定することにより、図 6 ( b )に示すように、デューティサイクル期間の中で信号がハイレベルとなる期間の割合が第 1 デューティ比 D 1 となる第 1 パルス幅変調制御信号 ( PWM1 ) と、図 6 ( e )に示すように、デューティサイクル期間の中で信号がハイレベルとなる期間の割合が第 2 デューティ比 D 2 となる第 2 パルス幅変調制御信号 ( PWM2 ) とが生成される。

20

#### 【0031】

図 6 ( b )に示すように、PWM1 では、デューティサイクル期間は時刻  $t_0$  から時刻  $t_{12}$  の 12 区間であり、信号がハイレベルとなる第 1 ハイレベル期間は時刻  $t_4$  から時刻  $t_8$  間の 4 区間で、信号がローレベルとなる第 1 ローレベル期間は時刻  $t_0$  から時刻  $t_4$  及び時刻  $t_8$  から時刻  $t_{12}$  の間の 8 区間であり、第 1 デューティ比  $D_1 = 4 / ( 4 + 8 ) = ( 4 / 12 ) < 50\%$  となる。図 6 ( e )に示すように、PWM2 も PWM1 と同様である。また、図 6 ( c )に示すように、PWM1 の反転信号 / PWM1 は、信号がローレベルとなる期間が時刻  $t_4$  から時刻  $t_8$  間の 4 区間で、信号がハイレベルとなる期間が時刻  $t_0$  から時刻  $t_4$  及び時刻  $t_8$  から時刻  $t_{12}$  の間の 8 区間である。PWM2 の反転信号である / PWM2 も同様である。つまり、図 6 ( a ) ~ 図 6 ( j )に示す動作では、PWM1 、 PWM2 のハイレベル、ローレベルになるタイミングが同一、つまり、PWM1 と PWM2 との位相差がゼロで、各デューティ比 D 1 , D 2 が ( 4 / 12 ) < 50 % である。

30

#### 【0032】

S 1 ( 31 ) ~ S 4 ( 34 ) をオン・オフ動作させるスイッチング素子制御信号 S S 1 ~ S S 4 は、上記の各パルス幅変調制御信号 PWM1 , / PWM1 , PWM2 , / PWM2 を用いて次の論理式で表わされる。

40

$$S S 1 : ( / PWM1 ) \text{ or } ( / PWM2 ) \quad \dots \quad ( 式 5 )$$

$$S S 2 : ( / PWM1 ) \text{ or } ( \quad PWM2 ) \quad \dots \quad ( 式 6 )$$

$$S S 3 : ( \quad PWM1 ) \text{ or } ( \quad PWM2 ) \quad \dots \quad ( 式 7 )$$

$$S S 4 : ( \quad PWM1 ) \text{ or } ( / PWM2 ) \quad \dots \quad ( 式 8 )$$

#### 【0033】

図 6 ( a )から図 6 ( j )に示す動作において、SS1 は、図 6 ( g )に示すように、一周期 ( デューティサイクル期間 )において、時刻  $t_0$  から時刻  $t_4$  の 4 区間は S 1 ( 31 ) をオンとし、時刻  $t_4$  から時刻  $t_8$  の 4 区間は S 1 ( 31 ) をオフとし、時刻  $t_8$  か

50

ら時刻  $t_{12}$ までの4区間は  $S_1(31)$ をオンとすることをデューティサイクル毎に繰り返す信号である。また、図6(h)に示すように、 $S_2$ は  $S_2(32)$ を常時オンとする信号であり、図6(i)に示すように、 $S_3$ は、時刻  $t_0$ から時刻  $t_4$ の4区間は  $S_3(33)$ をオフとし、時刻  $t_4$ から時刻  $t_8$ の4区間は  $S_3(33)$ をオンとし、時刻  $t_8$ から時刻  $t_{12}$ までの4区間は  $S_3(33)$ をオフとすることをデューティサイクル毎に繰り返す信号であり、図6(j)に示すように、 $S_4$ は、 $S_4(34)$ を常時オンとする信号である。従って、図6(a)～図6(j)の時刻  $t_4$ から時刻  $t_8$ の間は、 $S_1(31)$ がオフ、 $S_2(32)$ 、 $S_3(33)$ 、 $S_4(34)$ がオンとなり、図2に示す回路  $R_1$ と図4に示す回路  $R_2$ とが同時に形成され、 $B_1(20)$ により  $L_1(22)$ がチャージされ、 $B_2(23)$ により  $L_2(25)$ がチャージされる。そして、時刻  $t_0$ から時刻  $t_4$ の間及び時刻  $t_8$ から  $t_{12}$ の間は、 $S_1(31)$ 、 $S_2(32)$ 、 $S_4(34)$ がオン、 $S_3(33)$ がオフであり、図3に示す回路  $R_5$ 、 $R_7$ と図5に示す回路  $R_6$ 、 $R_8$ とが同時に形成され、 $L_1(22)$ にチャージされた電力及び  $L_2(25)$ にチャージされた電力が同時に出力電路  $2_6$ に出力される。

10

#### 【0034】

図6(a)から図6(j)に示す動作では、図6(g)、図6(i)の黒三角マークで示すように、第1、第2三角波  $8_1$ 、 $8_3$ の一周期(位相角360度)或いは、1デューティサイクル期間(時刻  $t_0$ から時刻  $t_{12}$ )の間に  $S_1(31)$ 、 $S_3(33)$ はオンからオフ或いはオフからオンへの切換えが2回ずつ行われている。また、切換えのタイミングは同時である。従って、電圧変換器  $1_0$ では、第1、第2三角波  $8_1$ 、 $8_3$ の一周期(位相角360度)或いは、1デューティサイクル期間(時刻  $t_0$ から時刻  $t_{12}$ )の間に時刻  $t_4$ 、時刻  $t_8$ に1回ずつ合計2回、 $C_1(21)$ 、 $L_1(22)$ 、 $C_2(24)$ 、 $L_2(25)$ 、バスバー等の構成部品がローレンツ力や静電気力の変化を受け、これらの構成部品に1デューティサイクル期間(時刻  $t_0$ から時刻  $t_{12}$ )の間に2回の振動が発生することになるから、第1、第2三角波  $8_1$ 、 $8_3$ の周波数(キャリア周波数)の2倍の周波数の振動或いは騒音が発生することとなる。第1、第2三角波  $8_1$ 、 $8_3$ の周波数(キャリア周波数)が10kHzの場合には発生する電磁音の周波数は20kHzとなり人間の可聴域の上限近傍の周波数となり、騒音として感じられる場合がある。

20

#### 【0035】

< PWM1、PWM2の位相を変化させる >

次に、図7(a)から図7(j)を参照しながら、第1、第2パルス幅変調制御信号  $PWM_1$ 、 $PWM_2$ の位相を図6(a)から図6(j)に示した位相差ゼロの動作から位相差180度(デューティサイクル期間(時刻  $t_0$ から時刻  $t_{12}$ )の半分)とした際の動作と発生騒音について説明する。

30

#### 【0036】

図7(a)、図7(d)に示すように、 $PWM_2$ を発生させる第2三角波を、 $PWM_1$ を発生させる第1三角波  $8_1$ の位相に対する位相差  $\Delta\theta$ が180度となる第2三角波  $8_5$ とする。より具体的には、図7(d)に示す第2三角波  $8_5$ の山のピークが時刻  $t_{12}$ 、時刻  $t_{24}$ となるように、図6(d)に示した第2三角波  $8_3$ を時間で6区間だけずらし、第1三角波  $8_1$ の山のピークとの時間差が6区間( $t_{12} - t_6$ )、( $t_{24} - t_8$ )となるようにする。これにより、図7(b)、図7(e)に示すように、 $PWM_2$ の位相は  $PWM_1$ の位相に対して180度、時間でデューティサイクル期間の12区間の半分の6区間だけずれる。同様に/ $PWM_2$ の位相は/ $PWM_1$ の位相に対して180度、時間でデューティサイクル期間の12区間の半分の6区間だけずれる。また、 $PWM_1$ の第1デューティ比  $D_1$ 、 $PWM_2$ の第2デューティ比  $D_2$ は、図6(a)から図6(j)を参照して説明した動作と同様、それぞれ( $4/12$ )<50%である。図7(b)、図7(e)に示すように、 $PWM_1$ がハイレベルになる第1ハイレベル期間は時刻  $t_4$ と時刻  $t_8$ の間であるのに対し、 $PWM_2$ がハイレベルになる第2ハイレベル期間は時刻  $t_0$ から時刻  $t_2$ の間と時刻  $t_{10}$ から時刻  $t_{12}$ の間である。したがって、 $PWM_1$ の第1ハイレベル期間と  $PWM_2$ の第2ハイレベル期間とは重なっておらず、時刻  $t_2$ から時刻

40

$t_4$  の間、時刻  $t_8$  から時刻  $t_{10}$  の間は、PWM1、PWM2 共にローレベルとなる。このように、PWM1 の第1ハイレベル期間(4区間)と PWM2 の第2ハイレベル期間(4区間)の合計期間(8区間)がデューティサイクル期間(12区間)よりも短い場合、別の表現をすると、パーセンテージで表した PWM1 の第1デューティ比 D1 の数値( $4/12 = 1/3 = 33\%$  数値は 33)と、パーセンテージで表した PWM2 の第2デューティ比 D2 の数値( $4/12 = 1/3 = 33\%$  数値は 33)との合計数値( $33 + 33 = 66$ )がパーセンテージで表したデューティサイクル期間の数値( $12/12 = 100\%$  数値は 100)未満で、PWM2 の位相を PWM1 の位相に対して 180 度、時間でデューティサイクル期間の 12 区間の半分の 6 区間だけずらした場合には、PWM1 の第1ハイレベル期間と PWM2 の第2ハイレベル期間とは重ならない。つまり、PWM1、PWM2 の位相はデューティサイクル期間の半期間毎に各ハイレベル期間が交互に発生するように制御される。

#### 【0037】

この際の S1(31) から S4(34) をオン・オフさせる各制御信号 SS1 から SS4 は先に説明した(式5)から(式8)により計算され、図7(g)から図7(j)に示すようになる。SS1 は、図7(g)に示すように S1(31) を常時オンとする信号となり、SS2 は、図7(h)に示すように、一周期(デューティサイクル期間)において、時刻  $t_0$  から時刻  $t_4$  の 4 区間は S2(32) をオンとし、時刻  $t_4$  から時刻  $t_8$  の 4 区間は S2(32) をオフとし、時刻  $t_8$  から時刻  $t_{12}$  までの 4 区間は S2(32) をオンとすることをデューティサイクル毎に繰り返す信号となる。また、SS3 は、図7(i)に示すように、時刻  $t_0$  から  $t_2$  の 2 区間は S3(33) をオンとし、時刻  $t_2$  から  $t_4$  の 2 区間は S3(33) をオフとし、時刻  $t_4$  から時刻  $t_8$  までは S3(33) をオンとし、時刻  $t_8$  から時刻  $t_{10}$  までは S3(33) をオフとし、時刻  $t_{10}$  から  $t_{12}$  までは S3(33) をオンとすることをデューティサイクル毎に繰り返す信号であり、SS4 は、図7(j)に示すように、時刻  $t_0$  から時刻  $t_2$  の間は S4(34) をオフとし、時刻  $t_2$  から時刻  $t_{10}$  までは S4(34) をオンとし、時刻  $t_{10}$  から時刻  $t_{12}$  までは S4(34) をオフとすることをデューティサイクル毎に繰り返す信号である。従って、図7(a)～図7(j)の時刻  $t_0$  から  $t_2$ 、時刻  $t_{10}$  から  $t_{12}$  の間は、S1(31)～S3(33) がオン、S4(34) がオフとなり、図8に示すように回路 R5、R7 と回路 R2 とが同時に形成され、B1(20) により L1(22) にチャージされていた電力が回路 R5 から出力電路 26 に出力されるとともに、B2(23) により L2(25) がチャージされる。そして、時刻  $t_2$  から時刻  $t_4$ 、時刻  $t_8$  から時刻  $t_{10}$  の間は、S1(31)、S2(32)、S4(34) がオン、S3(33) がオフであり、図3に示す回路 R5、R7 と図5に示す回路 R6、R8 とが同時に形成され、L1(22) にチャージされた電力及び L2(25) にチャージされた電力が同時に出力電路 26 に出力される。また、時刻  $t_4$  から  $t_8$  の間は、S1(31)、S3(33)、S4(34) がオン、S2(32) がオフであり、図9に示すように回路 R1 と回路 R6、R8 とが同時に形成され、B2(23) により L2(25) にチャージされていた電力が回路 R6 から出力電路 26 に出力されるとともに、B1(20) により L1(22) がチャージされる。

#### 【0038】

図7(a)から図7(j)に示す動作では、図7(h)から図7(j)の黒三角マークで示すように、第1、第2三角波 81, 85 の一周期(位相角 360 度)或いは、1 デューティサイクル期間(時刻  $t_0$  から時刻  $t_{12}$ )の間に S2(32) は、時刻  $t_4$ 、時刻  $t_8$  にオンからオフ或いはオフからオンへの切換えが行われ、S3(33) は、時刻  $t_2$ 、時刻  $t_4$ 、時刻  $t_8$ 、時刻  $t_{10}$  にオンからオフ或いはオフからオンへの切換えが行われる。したがって、この動作では、電圧変換器 10 では 1 デューティサイクル期間(時刻  $t_0$  から時刻  $t_{12}$ )の間の時刻  $t_2$ 、時刻  $t_4$ 、時刻  $t_8$ 、時刻  $t_{10}$  に 4 回の振動が発生し、第1、第2三角波 81, 85 の周波数(キャリア周波数)の 4 倍の周波数

の振動或いは騒音が発生することとなる。第1、第2三角波81, 83の周波数（キャリア周波数）が10kHzの場合には発生する電磁音の周波数は40kHzとなり人間の可聴域より高くなるので、人間には騒音として感じられなくなる。このように、PWM1、PWM2の各デューティ比D1, D2がいずれも50%以下の場合にPWM1を発生させる第1三角波81の位相に対するPWM2を発生させる第2三角波85の位相の位相差

1を180度とすると、電圧変換器10の発生する電磁音の周波数は、第1、第2三角波81, 85の周波数（キャリア周波数）の4倍となり、発生する電磁音の周波数を人間の可聴域外にすることができるので、電圧変換器10の発生騒音を低減することができる。つまり、PWM1に対するPWM2の位相を変化させることにより、疑似的にキャリア周波数を2倍にした場合と同様の騒音低減の効果を奏する。

10

20

30

40

### 【0039】

以上の説明では、第1三角波81に対するPWM2を発生させる第2三角波85の位相差を180度とすることとして説明したが、PWM1の第1ハイレベル期間とPWM2の第2ハイレベル期間とが重ならないような位相差であれば、180度以外の位相差となるように第1三角波81の位相と第2三角波の位相をずらすようにしてもよい。例えば、図7(d)に示すように、PWM1を発生させる第1三角波81の位相に対してPWM2を発生させる第2三角波の位相を位相差 $-1^\circ$ （150度）、時間で5区間とするような第2三角波85'としてもよい。これにより、図7(e)、図7(f)に示すように、PWM2、/ PWM2の位相は、それぞれPWM1、/ PWM1の位相に対して150度（時間で5区間）だけずれたものとなる。この際のS1(31)、S2(32)をオン・オフさせるスイッチング素子制御信号SS1, SS2は、図7(g)、図7(h)の破線に示すように、第2三角波85'の場合と同様で、S3(33)をオン・オフさせるスイッチング素子制御信号SS3は、第2三角波85'の場合の時刻t2, t10でオンからオフ或いはオフからオンへの切換えがされたのが、時刻t1, 時刻t9でオンからオフ或いはオフからオンへの切換えがされるようになり、1デューティサイクル期間（時刻t0から時刻t12）の間に時刻t1, 時刻t4, 時刻t8, 時刻t9に4回の振動が発生し、第2三角波85'の場合と同様、第1、第2三角波81, 85'の周波数（キャリア周波数）の4倍の周波数の振動或いは騒音が発生する。したがって、この場合も、第2三角波85'の場合と同様、電圧変換器10の発生する電磁音の周波数を人間の可聴域外にして騒音を低減することができる。

20

30

40

### 【0040】

図7(a)から図7(j)を参照して説明した上記の各動作では、PWM1の第1デューティ比D1、PWM2の第2デューティ比D2は、それぞれ(4/12)<50%として説明したが、PWM1の第1ハイレベル期間（4区間）とPWM2の第2ハイレベル期間（4区間）の合計期間（8区間）がデューティサイクル期間（12区間）よりも短ければ、PWM1の第1ハイレベル期間とPWM2の第2ハイレベル期間とが重ならないようにPWM1とPWM2との位相を調整することができる。別の表現をすると、パーセンテージで表したPWM1の第1デューティ比D1の数値と、パーセンテージで表したPWM2の第2デューティ比D2の数値との合計数値がパーセンテージで表したデューティサイクル期間の数値である100未満の場合には、PWM1の第1ハイレベル期間とPWM2の第2ハイレベル期間とが重ならないようにPWM1とPWM2との位相を調整することができる。

40

### 【0041】

例えば、図10(a)に示すように、第1デューティ比D1を設定する直線91の高さ（閾値）を図7(a)の直線82よりも高く（閾値を大きく）し、デューティサイクル期間が時刻t0から時刻t12の12区間で、PWM1の第1ハイレベル期間が時刻t5から時刻t7の2区間で第1ローレベル期間が時刻t0からt5および時刻t7から時刻t12までの10区間であり、第1デューティ比D1=2/(2+10)=(2/12)<50%とし、第2デューティ比D2を設定する直線92の高さ（閾値）を図7(d)の直線84よりも低く（閾値を小さく）し、PWM2の第2ハイレベル期間が時刻t0から時

50

刻  $t_4$  および時刻  $t_8$  から時刻  $t_{12}$  の 8 区間で第 2 ローレベル期間が時刻  $t_4$  から  $t_8$  までの 4 区間であり、第 2 デューティ比  $D_2 = 8 / (4 + 8) = (8 / 12) > 50\%$  とした場合、PWM1 の第 1 ハイレベル期間と PWM2 の第 2 ハイレベル期間の合計期間は、2 区間 + 8 区間 = 10 区間となり、デューティサイクル期間の 12 区間よりも短くなる。この場合に、図 7(a) から図 7(j) を参照して説明したように、第 2 三角波の第 1 三角波  $8_1$  に対する位相差が 180 度となる第 2 三角波  $8_5$  を用いると、図 10(h) から図 10(j) の黒三角マークで示すように、第 1、第 2 三角波  $8_1, 8_5$  の一周期（位相角 360 度）或いは、1 デューティサイクル期間（時刻  $t_0$  から時刻  $t_{12}$ ）の間に  $S_2(32)$  は、時刻  $t_5$ 、時刻  $t_7$  にオンからオフ或いはオフからオンへの切換えが行われ、 $S_3(33)$  は、時刻  $t_4$ 、時刻  $t_5$ 、時刻  $t_7$ 、時刻  $t_8$  にオンからオフ或いはオフからオンへの切換えが行われ、 $S_4(34)$  は、時刻  $t_4$ 、時刻  $t_8$  にオンからオフ或いはオフからオンへの切換えが行われる。したがって、この動作では、電圧変換器 10 では 1 デューティサイクル期間（時刻  $t_0$  から時刻  $t_{12}$ ）の間に時刻  $t_4$ 、時刻  $t_5$ 、時刻  $t_7$ 、時刻  $t_8$  に 4 回の振動が発生し、第 1、第 2 三角波  $8_1, 8_5$  の周波数（キャリア周波数）の 4 倍の周波数の振動或いは電磁音が発生する。このように、PWM1 または PWM2 のデューティ比  $D_1, D_2$  のいずれか一方が 50% 以上であっても、PWM1 の第 1 ハイレベル期間と PWM2 の第 2 ハイレベル期間の合計期間がデューティサイクル期間よりも短い場合には、PWM1 の第 1 ハイレベル期間と PWM2 の第 2 ハイレベル期間とが重ならないように PWM1 に対する PWM2 の位相を調整することによって、電圧変換器 10 の電磁音の周波数を人間の可聴域以上に高くして騒音を低減することができる。

なお、上記の説明では、PWM1 と PWM2 の位相差を 180 度として説明したが、PWM1 の第 1 ハイレベル期間と PWM2 の第 2 ハイレベル期間とが重ならないように位相を調整できれば、位相差は 180 度には限定されない。

#### 【0042】

< 第 1、第 2 パルス幅変調制御信号が重なる制御と重ならない制御とを混在させる >

以上説明した実施形態では、PWM1 と PWM2 の位相は、PWM1 の第 1 ハイレベル期間と PWM2 の第 2 ハイレベル期間とが重ならないような位相に設定して動作させることとして説明したが、図 11(a) から図 11(j) に示すように、第 1 パルス幅変調制御信号 (PWM1) の第 1 ハイレベル期間と第 2 パルス幅変調制御信号 (PWM2) の第 2 ハイレベル期間とが重なる、あるいは一部重なるように各パルス幅変調制御信号の位相を制御する第 1 の制御と、PWM1 の第 1 ハイレベル期間と PWM2 の第 2 ハイレベル期間とが重ならないように各パルス幅変調制御信号の位相を制御する第 2 の制御とを混在させて位相制御を行うようにしてもよい。以下の説明では、PWM1 に対する PWM2 の位相をスケジュールによって変化させて第 1 の制御と第 2 の制御とが混在するようにする場合について説明する。なお、図 7(a) から図 10(j) を参照して説明したのと同様の動作については簡単に説明する。

#### 【0043】

図 11(a) に示す第 1 三角波  $8_1$ 、直線  $8_2$ （閾値）は、図 6(a) と同様であり、図 11(b)、図 11(c) に示す PWM1、/ PWM1 は図 6(b)、図 6(c) を参照して説明した PWM1、/ PWM1 と同様である。図 11(d) に示すように、PWM2 を生成する第 2 三角波は、時刻  $t_0$  から時刻  $t_2$  までは、第 1 三角波  $8_1$  との位相差がゼロの第 2 三角波  $8_3$  であり、この間の PWM1、/ PWM1、PWM2、/ PWM2、 $S_1 \sim S_4$  は、図 6(a) から図 6(j) 各信号波形と同様である。

#### 【0044】

制御部 60 は、時刻  $t_2$  に第 2 三角波の位相を最初の第 2 三角波  $8_3$  或いは第 1 三角波  $8_1$  の位相から 2 (120 度) だけずらした第 2 三角波  $8_6$  に切換える。すると、図 11(d) の時刻  $t_2$  から第 2 三角波  $8_6$  が始まる。第 2 三角波  $8_6$  は、時刻  $t_4$  に谷になり、その後、時刻  $t_{10}$  に山、時刻  $t_{16}$  に谷となり、時刻  $t_{17}$  まで継続する。図 11(d) に示すように、この第 2 三角波  $8_6$  と PWM2 の第 2 デューティ比  $D_2$  を規定する直線  $8_4$ （閾値）とは、時刻  $t_8$ 、時刻  $t_{12}$  で交差し、時刻  $t_8$  から時刻  $t_{12}$  まで

10

20

30

40

50

の間は、第2三角波87の値は直線84の値より高くなっている、これにより時刻t8と時刻t12の間、PWM2はハイレベルとなり、その他の区間でPWM2はローレベルとなる。また、時刻t8と時刻t12の間、/PWM2はローレベルとなり、その他の区間ではハイレベルとなる。このように、PWM1とPWM2及び/PWM1と/PWM2は、それぞれ時刻t8で重なり、その他の期間では重ならない（第1の制御）。

#### 【0045】

第2三角波86が継続する時刻t2から時刻t17の間、S1(31)からS4(34)をオン・オフさせる各制御信号SS1からSS4は先に説明した（式5）から（式8）により計算され、図11(g)から図11(j)に示すようになる。SS1は、図11(g)に示すようにS1(31)を常時オンとする信号となり、SS2は、図11(h)に示すように、時刻t2から時刻t4の間はS2(32)をオンとし、時刻t4から時刻t8の間はS2(32)をオフとし、時刻t8から時刻t16の間はS2(32)をオンとし、時刻t16から時刻t17の間はS2(32)をオフとする信号となる。また、SS3は、図11(i)に示すように、時刻t2から時刻t4の間はS3(33)をオフとし、時刻t4から時刻t12の間はS3(33)をオンとし、時刻t12から時刻t16まではS3(33)をオフとし、時刻t16から時刻t17の間はS3(33)をオンとする信号となる。さらに、SS4は、図11(j)に示すように、時刻t2から時刻t8まではS4(34)をオンとし、時刻t8からt12まではS4(34)をオフとし、時刻t12から時刻t17の間はS4(34)をオンとする信号となる。

10

#### 【0046】

制御部60は、時刻t17に第2三角波の位相を更に3(60度)だけずらした第2三角波87に切換える。第2三角波87は、時刻t18で谷になり、その後、時刻t24に山となる。第2三角波87の最初の第2三角波83或いは第1三角波81に対する位相差は1(180度)となっている。したがって、図7(a)から図7(j)を参照して説明した動作と同様、PWM1とPWM2及び/PWM1と/PWM2は、全く重ならない（第2の制御）。

20

#### 【0047】

第2三角波87が継続する時刻t17から時刻t24の間、S1(31)からS4(34)をオン・オフさせる各制御信号SS1からSS4は先に説明した（式5）から（式8）により計算され、SS1は、図11(g)に示すようにS1(31)を常時オンとする信号となり、SS2は、図11(h)に示すように、時刻t17から時刻t20の間はS2(32)をオフとし、時刻t20から時刻t24の間はS2(32)をオンとする信号となる。また、SS3は、図11(i)に示すように、時刻t17から時刻t20の間はS3(33)をオンとし、時刻t20から時刻t22の間はS3(33)をオフとし、時刻t22から時刻t24の間はS3(33)をオンとする信号となる。更に、SS4は、図11(j)に示すように、時刻t17から時刻t22の間はS4(34)をオンとし、時刻t22から時刻t24の間はS4(34)をオフとする信号となる。

30

#### 【0048】

以上、SS1からSS4はt0からt24の間で上記のような信号となるので、時刻t0から時刻t12の間の第1三角波81の最初の周期では、S2(32)は時刻t4、時刻t8にオンからオフ或いはオフからオンへの切換えが行われ、S3(33)は、時刻t4、時刻t12にオンからオフ或いはオフからオンへの切換え行われ、S4(34)は、時刻t8、時刻t12にオンからオフ或いはオフからオンへの切換えが行われる。したがって、図11(h)から図11(j)の黒三角マークで示すように、電圧変換器10では第1三角波81の最初の周期（時刻t0から時刻t12）の間に時刻t4、時刻t8、時刻t12に3回の振動が発生し、第1三角波81周波数（キャリア周波数）の3倍の周波数の振動或いは電磁音が発生する。また、時刻t12から時刻t24の間の第1三角波81の次の周期では、S2(32)は時刻t16、時刻t20にオンからオフ或いはオフからオンへの切換えが行われ、S3(33)は、時刻t16、時刻t20、時刻t22にオンからオフ或いはオフからオンへの切換えが行われ、S4(34)は、時刻t22にオン

40

50

からオフ或いはオフからオンへの切換えが行われる。したがって、電圧変換器10では第1三角波81の次の周期（時刻t12から時刻t24）の間の時刻t16，時刻t20，時刻t22において3回の振動が発生し、第1三角波81周波数（キャリア周波数）の3倍の周波数の振動或いは電磁音が発生する。

#### 【0049】

また、第2三角波87は時刻t24以降の第1三角波81の次の周期（時刻t24から時刻t36の間）も継続する。第2三角波87は、第1三角波81に対して位相が180度ずれているので、時刻t24から時刻t36の間、PWM1とPWM2及び/PWM1と/PWM2は、全く重ならない（第2の制御）。時刻t24から時刻t36の間のPWM2、/PWM2は、図7(d)の時刻t0から時刻t12の間と同様の波形となるので、時刻t24以降の第1三角波81の次の周期（t24からt36の間）のSS1～SS4は図7(g)から図7(j)に実線で示す波形と同様の波形となる。したがって、図7(g)から図7(j)を参照して説明したのと同様、電圧変換器10では第1三角波81の次の周期（時刻t24から時刻t36）の間に4回の振動が発生し、第1三角波81周波数（キャリア周波数）の4倍の周波数の振動或いは電磁音が発生する。

10

#### 【0050】

このように、制御部60は、所定のスケジュールに従って、第1三角波81の周期毎に第2三角波の第1三角波81に対する位相差或いはPWM1に対するPWM2の位相差をゼロ（時刻t2以前、第1の制御）120度（時刻t2から時刻t17、第1の制御）

180度（時刻t17以降、第2の制御）と変化させていく。これにより、PWM1と

PWM2とが、(1) PWM1とPWM2とが重なる状態（第1の制御）(2) PWM

1とPWM2とが一部重なる状態（第1の制御）(3) PWM1とPWM2とが全く重

ならない状態（第2の制御）と変化させていく。

20

#### 【0051】

位相差がゼロの場合は、図6(a)から図6(j)を参照して説明した基本動作であり、電圧変換器10では第1三角波81の一周期の間に2回の振動が発生し、位相差を120度に切換えた第1三角波の最初の周期では先に説明したように、第1三角波81の一周期の間に3回の振動が発生し、位相差を180度に切換えた次の周期でも第1三角波81の一周期の間に3回の振動が発生し、位相差を180度に維持した次の第1三角波81の周期では第1三角波81の一周期の間に4回の振動が発生する。したがって、第1三角波81に対する第2三角波の位相差を第1三角波81の周期毎にゼロ 120度 180度

180度と変化させることにより、電圧変換器10から発生する電磁音の周波数は、第1三角波81の周波数の2倍 3倍 3倍 4倍と変化する。つまり、PWM1に対する

PWM2の位相差をPWM1の周期毎にゼロ 120度 180度 180度と変化させることにより、電圧変換器10から発生する電磁音の周波数は、PWM1の周波数の2倍

3倍 3倍 4倍と変化する。第1三角波81の周波数（キャリア周波数）が10kHz

の場合、電圧変換器10が発生する電磁音の周波数は、20kHz 30kHz 30

kHz 40kHzと変化する。これにより、騒音の周波数帯域が広い範囲で平均化され、人間の可聴域に入る20kHz近傍の電磁音の平均レベルを低減することができ、電圧

変換器10の騒音を抑制することができる。また、この動作は、先に図7(a)から図7

(j)を参照して説明した動作のように第1三角波81に対する第2三角波85の位相差

を180度に設定する場合に比べて各S2(32)からS4(34)のオン・オフの平均

回数を少なくすることができるので、先に図7(a)から図7(j)を参照して説明した

動作に比べてスイッチング損失の増加を抑制しつつ騒音低減を図ることができる、つまり

、スイッチング損失の増加と騒音低減とのバランスをとった動作である。

30

#### 【0052】

以上の説明では、制御部60は、所定のスケジュールに従って、第1三角波81に対する第2三角波の位相差或いはPWM1に対するPWM2の位相差を第1三角波81の周期毎にゼロ（第1の制御）120度（第1の制御）180度（第2の制御）180度

(第2の制御)と変化させ、PWM1とPWM2とが、(1) PWM1とPWM2とが重

50

なる状態（第1制御）（2）PWM1とPWM2とが一部重なる状態（第1の制御）（3）PWM1とPWM2とが全く重ならない状態（第2の制御）と変化させていくことにより、スイッチング損失の増加を抑制しつつ騒音低減を行うこととして説明したが、第1三角波81に対する第2三角波85の位相差を180度に設定する場合に比べて各S2(32)からS4(34)のオン・オフの平均回数を少なくすることができれば、第1三角波81の周期毎に位相を変化させるスケジュールは上記の例に限らず、例えば、ゼロ（第1の制御）180度（第2の制御）ゼロ（第1の制御）180度（第2の制御）のように、ゼロ（第1の制御）と180度（第2の制御）とを交互に切換える、つまり、PWM1とPWM2とが重なる状態（第1の制御）とPWM1とPWM2とが全く重ならない状態（第2の制御）とを交互に切換えるようにしてもよいし、ゼロ、120度、180度をランダムに組み合わせたスケジュールによって第1三角波81の位相を変化させてPWM1とPWM2の位相をランダムに変化せるようにしてもよい。即ち、第1パルス幅変調制御信号（PWM1）の第1ハイレベル期間と第2パルス幅変調制御信号（PWM2）の第2ハイレベル期間とが重なる、あるいは一部重なるように各パルス幅変調制御信号の位相を制御する第1の制御と、PWM1の第1ハイレベル期間とPWM2の第2ハイレベル期間とが重ならないように各パルス幅変調制御信号の位相を制御する第2の制御とをランダムに混在させて位相制御を行うようにしてもよい。これにより、騒音の周波数帯域が広い範囲で平均化され、人間の可聴域に入る20kHz近傍の電磁音の平均レベルを低減することができ、電圧変換器10の騒音を抑制することができる。

10

20

## 【0053】

< PWM1がローレベルの期間にPWM2をローレベルからハイレベルとした後にローレベルに戻すように変化させる >

次に、図12(a)から図12(j)を参照しながら、PWM1がローレベルとなっている期間（/ PWM1がハイレベルとなっている期間）にPWM2をローレベルからハイレベルとした後にローレベルに戻すように変化させる（/ PWM2をハイレベルからローレベルとした後にハイレベルに戻すように変化させる）動作について説明する。先に図6(a)から図6(j)を参照して説明した動作と同様の動作については簡略に説明する。

## 【0054】

図12(a)に示す第1三角波81、直線82（閾値）は、図6(a)と同様であり、図12(b)、図12(c)に示すPWM1、/ PWM1は図6(b)、図6(c)を参照して説明したPWM1、/ PWM1と同様である。図12(d)に示すように、時刻t4から時刻t8、時刻t16から時刻t20の間のPWM2を生成する第2三角波89は、図6(d)の時刻t4から時刻t8、時刻t16から時刻t20の間の第2三角波83と同様である。したがってこの間のPWM1、/ PWM1、PWM2、/ PWM2、SS1～SS4は、図6(a)から図6(j)に示した各信号波形と同様である。また、第2三角波89の谷位置の時刻を図12の符号t'2、t'9、t'14、t'14、t'21で示す。

30

## 【0055】

制御部60は、図12(d)に示すように、第2三角波89は、PWM1がローレベルとなる（/ PWM1がハイレベルとなる）時刻t0から時刻t4、時刻t8から時刻t16、時刻t20から時刻t24の間の各区間の間で、第2三角波89の値が直線84（閾値）を超える期間と第2三角波89の値が直線84（閾値）を超えない期間ができるよう一時的に第2三角波89の周波数を第1三角波81の周波数よりも高くする。これにより、時刻t0と時刻t1の間、時刻t11と時刻t13の間、時刻t23と時刻t24の間で第2三角波89の値が直線84（閾値）を超え、PWM2がハイレベルとなり、時刻t1から時刻t4の間、時刻t8から時刻t11の間、時刻t13から時刻t16の間、時刻t20から時刻t23の間は、第2三角波89の値が直線84（閾値）を下回り、PWM2がローレベルとなる。つまり、PWM1がローレベルの間（時刻t8から時刻t16の間）にPWM2はローレベルからハイレベルとなった後にローレベルに戻すように変化する。

40

50

## 【0056】

このような第2三角波89を用いた場合のS1(31)からS4(34)をオン・オフさせる各制御信号SS1からSS4は先に説明した(式5)から(式8)により計算され、図12(g)から図12(j)に示すようになる。SS1とSS2は、図6(g)、図6(h)を参照して説明した信号と同様の信号となる。SS3は、図6(i)を参照して説明した信号に加えて、時刻t1にS3(33)をオフとし、時刻t11にS3(33)をオンとする信号を追加した信号となる。また、SS4は、図6(j)ではS4(34)を常時オンとする信号であったが、時刻t0から時刻t1の間でS4(34)をオフとし、時刻t1と時刻t11の間はS4(34)をオンとし、時刻t11と時刻t13の間でS4(34)をオフとする信号となる。このように、本動作では、図6(a)から図6(j)を参照して説明した動作に加えて、第1三角波81の一周期(時刻t0から時刻t12)の間にスイッチング素子がオン・オフ動作する回数が2回(時刻t1, 時刻t11)増えて、合計4回となる。したがって、電圧変換器10から発生する電磁音の周波数は、図7(a)から図7(d)を参照して説明した動作と同様、第1三角波81の周波数の4倍の周波数となり、第1三角波81の周波数が10kHzの場合、発生する電磁音の周波数を人間の可聴域外の40kHzにできるので、電圧変換器10の騒音を低減することができる。10

## 【0057】

本動作では、S1(31)、S2(32)のスイッチング回数は、図6(a)から図6(j)を参照して説明した動作と同様なので、S1(31)、S2(32)のスイッチング回数を増加させないで電圧変換器10の騒音を低減することができる。このため、例えば、S1(31)、S2(32)の温度が上昇し、S1(31)、S2(32)のスイッチング回数を増加させることが難しい場合でも効果的に騒音を低減することができる。20

## 【0058】

以上説明したように、各実施形態は、2つのパルス幅変調制御信号(PWM1, PWM2)によって2つのバッテリ(B1(20)、B2(23))の電圧変換制御を行う電圧変換器10を用いた電源システム100において、PWM1とPWM2との位相を制御することによって効果的に騒音を低減することができる。

## 【符号の説明】

## 【0059】

10 電圧変換器、11 基準電路、12 高圧電路、13 第1電路、14 第2電路、16 第1接続点、17 第2接続点、18 第3接続点、20 第1バッテリ、21 第1コンデンサ、22 第1リアクトル、23 第2バッテリ、24 第2コンデンサ、25 第2リアクトル、26 出力電路、31-34 スイッチング素子、35-38 ダイオード、40 インバータ、41 平滑コンデンサ、43, 44, 45 出力線50 モータジェネレータ、51 出力軸、52 ギヤ装置、53 車軸、54 車輪、60 制御部、61, 64, 71, 74, 75 電圧センサ、81, 83, 85, 86, 87, 89 三角波、82, 84, 91, 92 直線、100 電源システム、200 電動車両、PWM1, / PWM1, PWM2, / PWM2 パルス幅変調制御信号、R1- R8 回路、SS1-SS4 スイッチング素子制御信号。3040

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 砂原 昌平

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

F ターク(参考) 5H730 AA01 AS04 AS05 AS08 AS17 BB13 BB14 BB98 CC12 CC14

DD02 EE65 FD01 FD11 FG05