#### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 22 July 2004 (22.07.2004)

**PCT**

# (10) International Publication Number WO 2004/061955 A1

(51) International Patent Classification<sup>7</sup>: H05K 3/46

H01L 23/14,

(21) International Application Number:

PCT/US2003/039693

(22) International Filing Date:

11 December 2003 (11.12.2003)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

10/335,187

31 December 2002 (31.12.2002) U-

- (71) Applicant: INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

- (72) Inventor: COOMER, Boyd; 10498 East Bella Vista, Scottsdale, AZ 85258 (US).

- (74) Agents: STEFFEY, Charles, E. et al.; Schwegman, Lundberg, Woessner & Kluth, P.A., P.O. Box 2938, Minneapolis, MN 55402 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: METHODS FOR PERFORMING SUBSTRATE IMPRINTING USING THERMOSET RESIN VARNISHES AND PRODUCTS FORMED THEREFROM

(57) Abstract: A method comprising coating a core surface with an A-stage thermoset resin to produce an A-stage thermoset resin layer; partially curing the A-stage resin layer to produce a partially cured thermoset resin layer; and imprinting a plurality of conductor features into the partially cured thermoset resin layer to produce an imprinted substrate is provided. An electronic package comprising a substrate having a plurality of conductor features formed by imprinting, the substrate formed from an A-stage resin that has partially cured; and an electronic component coupled to the substrate is also provided. Coating with an A-stage thermoset resin as part of the imprinting process reduces thickness variation in the layers, provides full, intimate contact with prior layers and eliminates damage to prior layers.

# Methods for Performing Substrate Imprinting Using Thermoset Resin Varnishes and Products Formed Therefrom

## Related Applications

|    | Kelated Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  | The present applications are related to the following applications, which are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | assigned to the same Assignee as the present application:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | G 1177 / 141 141 - 141 Cultivator and Mathoda of Many feature ' filed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | Serial No/, entitled "Imprinted Substrates and Methods of Manufacture," filed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | on 12/18/2002 (Attorney Docket 884.634US1); and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10 | and a second sec |

|    | Serial No/, entitled "Method of Semi-Additive Plating of Imprinted Layers and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | Resulting Product" filed on/_/_ (Attorney Docket 884.841US1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15 | The present subject matter relates generally to methods of imprinting and products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|    | formed therefrom, and, more particularly, to substrate imprinting using thermoset resins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|    | and products formed therefrom.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20 | Integrated circuits (ICs) are typically assembled into electronic packages by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | physically and electrically coupling them to a substrate made of organic or ceramic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | material using a variety of techniques, including surface mount technology (SMT). One or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|    | more such IC packages can then be physically and electrically coupled to a secondary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | substrate such as a printed circuit board (PCB) or motherboard to form an "electronic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25 | assembly."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | Each substrate in an electronic assembly may comprise a number of layers. Each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | layer may include a pattern of metal interconnect lines (referred to herein as "traces") on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|    | one or both surfaces. Each layer may also include vias to couple traces or other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | conductive structures on opposite surfaces of the layer or on other layers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 30 | An IC substrate typically includes one or more electronic components mounted on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | one or more surfaces of the substrate. The electronic component or components are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | functionally connected to other elements of an electronic system through a hierarchy of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

electrically conductive paths that include the substrate traces and vias. The substrate traces and vias typically carry signals that are transmitted between the electronic components, such as ICs, of the system. Some ICs have a relatively large number of input/output (I/O) terminals (also called "lands" or "pads"), as well as a large number of power and ground terminals.

5

10

15

20

25

30

The formation of conductor features, such as traces and vias, in a substrate typically requires a sequence of complex, time-consuming, and expensive operations that offer ample opportunities for error. For example, forming traces on a single surface of a substrate layer typically requires surface preparation, metallizing, masking, etching, cleaning, and inspecting. Forming vias typically requires drilling, using a laser or mechanical drill. Each process stage requires careful handling and alignment to maintain the geometric integrity of the myriad of traces, vias, and other features. To allow for alignment tolerances, feature sizes and relationships often must be kept relatively large, thus hindering significant reductions in feature density. For example, to provide sufficient tolerance for drilling vias, via pads are typically provided, and these consume significant "real estate."

Fabrication of a typical multi-layer substrate requires that a large number of process operations be performed. In a known example of a multi-layer substrate, a core layer has a plurality of vias (also referred to herein as "plated through holes" or "PTHs") and traces. Traces may be formed on one or both surfaces of the core layer. One or more build-up layers, each with traces on one or more surfaces, and typically with PTHs, are formed. The features of the build-up layers can be formed while these layers are separate from the core layer, and the build-up layers may then be subsequently added to the core layer. Alternatively, some features of the build-up layers may be formed after such layers have been added to the core layer.

For the reasons stated above, and for other reasons stated below which will become apparent to those skilled in the art upon reading and understanding the present specification, there is a significant need in the art for methods of electronics packaging that minimize the complexity, time, and cost of fabricating substrates.

Brief Description of the Drawings

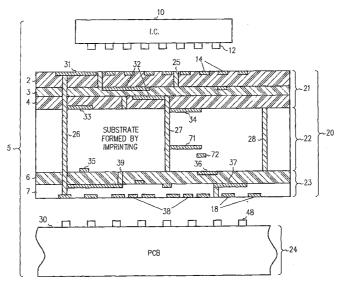

FIG. 1 illustrates a cross-sectional representation of an electronic assembly

incorporating a substrate that is formed by imprinting, in accordance with an embodiment of the invention;

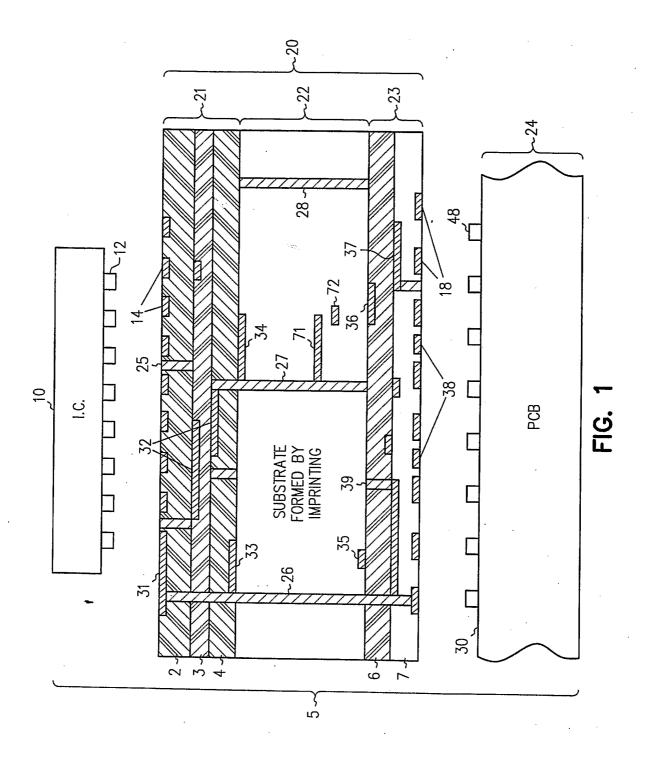

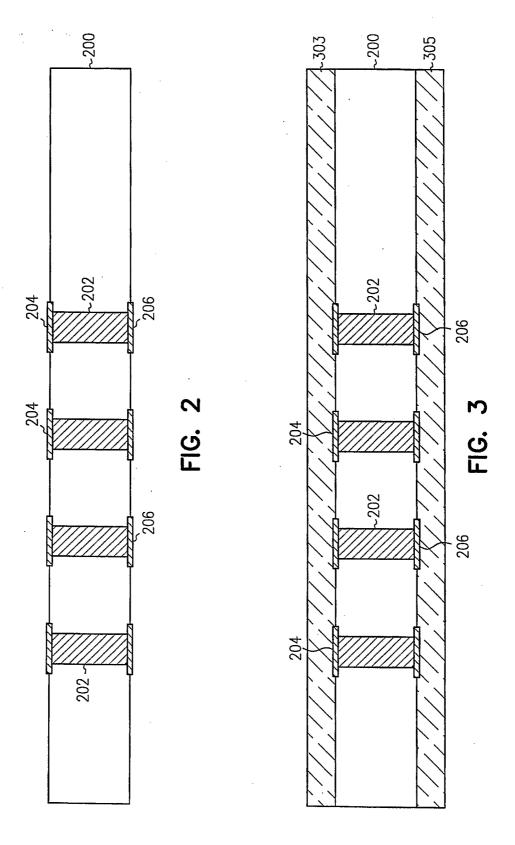

FIG. 2 illustrates a cross-sectional representation of a first step in a method for producing an imprinted substrate comprising providing a core layer, in accordance with an embodiment of the invention;

5

15

20

25

- FIG. 3 illustrates a cross-sectional representation of a subsequent step comprising coating the core layer of FIG. 2 with an A-stage thermoset resin in accordance with an embodiment of the invention;

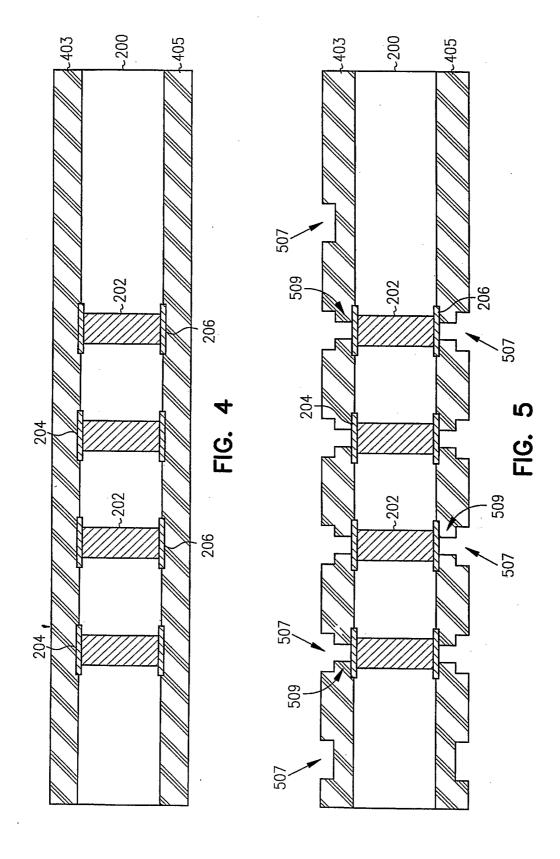

- FIG. 4 illustrates a cross-sectional representation of a subsequent step comprising partially curing A-stage resin of FIG. 3 to produce a partially cured resin.

- FIG. 5 illustrates a cross-sectional representation of a subsequent step comprising imprinting the partially cured thermoset resin of FIG. 4, in accordance with an embodiment of the invention;

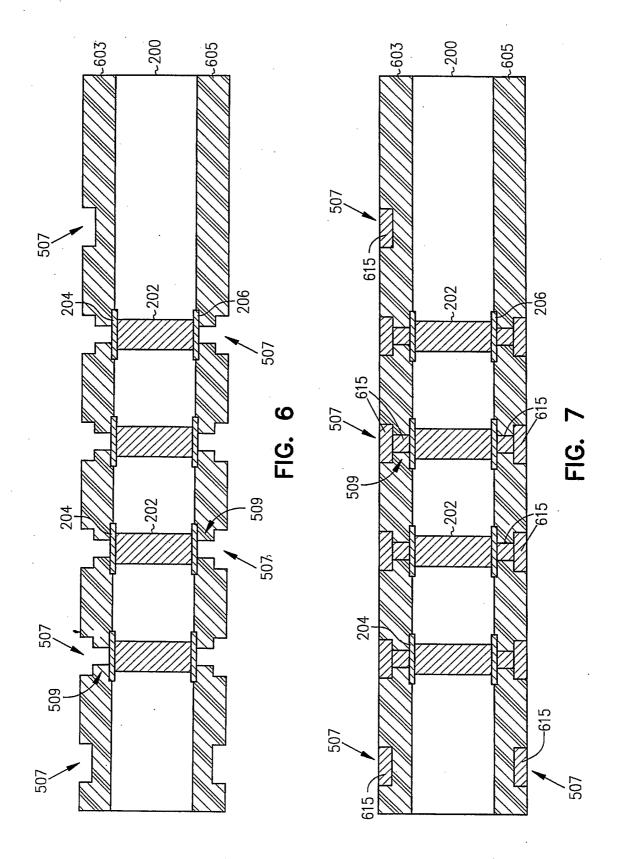

- FIG. 6 illustrates a cross-sectional representation of a subsequent step comprising curing the partially resin of FIG. 5 to the C-stage to produce an imprinted substrate;

- FIG. 7 illustrates a cross-sectional representation of a subsequent step comprising performing conventional plating and planarizing processes on the imprinted substrate of FIG. 6, in accordance with an embodiment of the invention;

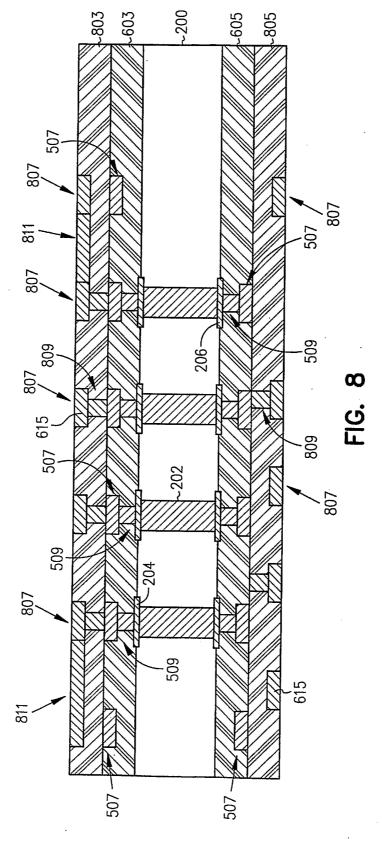

- FIG. 8 illustrates a cross-sectional representation of a subsequent step comprising adding additional layers to the imprinted and plated layers of FIG. 7 to produce a multilayer imprinted package, in accordance with an embodiment of the invention;

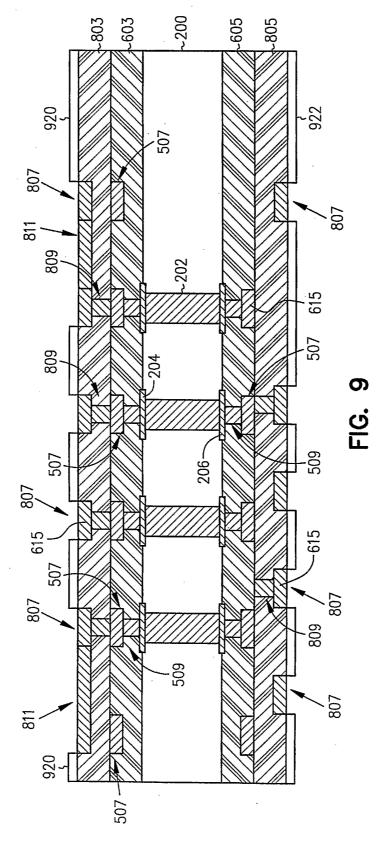

- FIG. 9 illustrates a cross-sectional representation of a subsequent step comprising applying soldermasks and final surface finish to the multilayer imprinted package of FIG. 8, in accordance with an embodiment of the invention;

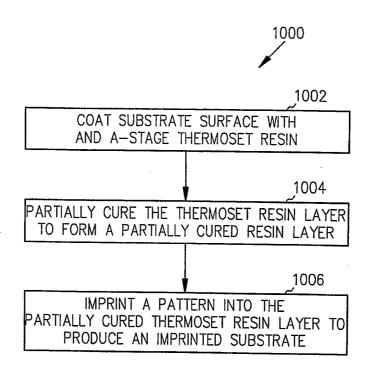

- FIG. 10 is a block diagram illustrating a method of producing an imprinted substrate, in accordance with an embodiment of the invention;

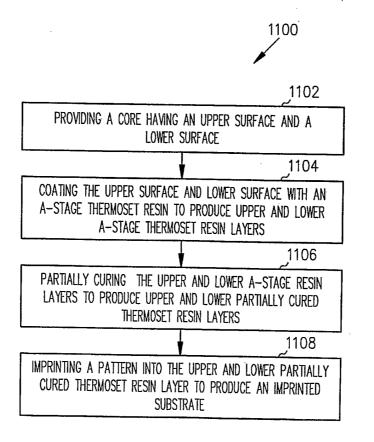

- FIG. 11 is a block diagram illustrating a method of producing an imprinted substrate according to an embodiment of the invention; and

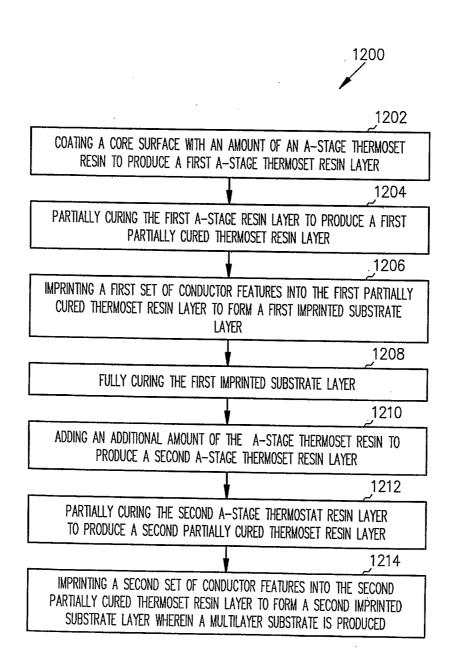

- FIG. 12 is a block diagram illustrating a method of producing a multilayer imprinted substrate according to an embodiment of the invention; and

In the following detailed description of embodiments of the invention, reference is made to the accompanying drawings that form a part hereof, and in which is shown by way of illustration specific preferred embodiments in which the subject matter may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice them, and it is to be understood that other embodiments may be utilized and that mechanical, chemical, structural, electrical, and procedural changes may be made without departing from the spirit and scope of the present subject matter. The following detailed description is, therefore, not to be taken in a limiting sense, and the scope of embodiments of the present invention is defined only by the appended claims.

The Detailed Description that follows begins with a definition section followed by a brief overview of imprinting, a description of the embodiments and a brief conclusion.

#### **Definitions**

5

10

15

20

25

30

The term "thermoplastic polymer" or "thermosoftening plastic" or "thermoplastic" as used herein refers to any plastic that can be repeatedly softened upon heating and hardened upon cooling, in contrast to a thermosetting plastic defined below. Thermoplastics do not undergo cross-linking upon heating and can therefore be resoftened. Examples include poly(ethane), polystyrene and polyvinyl chloride (PVC).

The term "thermoset resin" or "thermosetting plastic" or "resin" as used herein refers to any plastic that can be formed into a shape during manufacture, but which sets permanently rigid upon further heating. This is due to extensive cross-linking that occurs upon heating, which cannot be reversed by reheating. Examples include phenol-formaldehyde resins, epoxy resins, polyesters, polyurethane, silicones and combinations thereof. Thermoset resins most often used in the present invention include epoxy resins ("epoxies"), polyimide resins ("polyimides"), bismaleimide resins (e.g., bismaleimide trizaine (BT)) and combinations thereof.

The term "A-stage" as used herein refers to an initial stage (i.e., zero percent cure) in the reaction of some thermosetting resins wherein the resin continues to be soluble (in various solvents such as alcohols and acetone) and fusible. The "A-stage" is characterized by an initial lowering of viscosity as is known in the art. A material in the "A-stage" is typically a liquid that has been dissolved in a solvent. An "A-stage" thermoset resin is often referred to as a "varnish resin" or "resol."

The term "B-stage" as used herein refers to a secondary stage in the reaction of some thermosetting resins, characterized by a softening of the resin when heated and swelling when in the presence of certain liquids, but without complete fusing or dissolving. The "B-stage" is also characterized by a progressive increase in viscosity. The resin portion of an uncured thermosetting adhesive is usually in this stage. A "B-stage" material is considered a relatively soft, malleable solid, as is known in the art. Materials in the "B-stage" are considered to be more than zero percent cured, but not more than about 10% cured (as measured by Differential Scanning Calorimetry (DSC) described below). Typically, a "B-stage" material is produced from a varnish resin that has been previously applied to a surface and is at a point at which all of the solvent has evaporated due to the application of heat. It is the application of heat that causes some of the free polymers to begin to cure within a short time period, although given sufficient time, any thermoset resin will begin curing. A "B-stage" thermoset resin is also known as a "resitol."

5

10

15

20

25

30

The term "C-stage" as used herein refers to the third and final stage in the reaction of some thermosetting resins, characterized by the relatively insoluble and infusible state of the resin. Some thermosetting resins in this stage are fully cured, 100% cured, as measured by DSC. A "C-stage" resin is sufficiently rigid to enable additional chemical and mechanical processing to occur on its surface. A "C-stage" resin is also known as "resite."

The term "Differential Scanning Calorimetry (DSC)" as used herein refers to a thermal analysis method that can show the level of polymerization, such as with a thermoset resin, and hence the percent of cure. If no additional polymerization can occur, the sample being tested is 100% polymerized or cured. More specifically, during DSC heat energy is added to the system. If the added heat is utilized by the tested sample to drive a polymerization reaction, then the sample is not fully cured. If the added heat merely raises the temperature of the system, then the sample is assumed to be fully cured.

The term, "imprint" as used herein, means to form features in a material by forcing a tool against and/or into the material. Imprinting includes stamping, embossing, impressing, extruding, and like processes. Any suitable type of imprint apparatus can be used to make an imprint. The imprint apparatus can contain dies of a variety of shapes and sizes. Generally, shorter dies are used to form trenches while longer dies are used to form vias.

The term "conductor feature" as used herein, means any type of conducting element associated with a substrate, including vias (e.g. blind vias, through vias, etc.) and trenches, such as traces and planes (e.g. surface traces, internal traces, conductive planes, etc.), mounting terminals (e.g. pads, lands, etc.), and the like. •

The term "via" as used herein, means any type of conducting element to provide a conductive path between different depths in a substrate. For example, a "via" can connect conductive elements on opposite surfaces of a substrate as well as conductive elements at different internal layers within a substrate. Vias are also referred to as "plated through holes" or "PTHs."

5

10

15

20

25

30

The term "trench" as used herein, means any type of conducting element to provide a conductive path at a relatively constant depth in a substrate. A "trench" includes traces, ground planes, and terminals as well as lands. For example, a trace may connect conductive elements on one surface of a substrate. A ground plane may provide a conductive path at a relatively constant depth within a substrate. Terminals may provide conductive paths on one surface of a substrate.

The term "electronic assembly" as used herein refers to two or more electronic components coupled together.

The term "electronic system" as used herein refers to any product comprising an "electronic assembly." Examples of electronic systems include computers (e.g., desktop, laptop, hand-held, server, etc.), wireless communications devices (e.g., cellular phones, cordless phones, pagers, etc.), computer-related peripherals (e.g., printers, scanners, monitors, etc.), entertainment devices (e.g., televisions, radios, stereos, tape and compact disc players, video cassette recorders, MP3 (Motion Picture Experts Group, Audio Layer 3) players, etc.), and the like.

The term "substrate" as used herein refers to the physical object that is the basic workpiece transformed by various process operations into the desired microelectronic configuration. A substrate may also be referred to as a "printed circuit" or "printed wiring board." A "substrate" may include conducting material (such as copper or aluminum), insulating material (such as ceramic or plastic), and the like, or combinations thereof. Substrates can include layered structures, such as a sheet of material chosen for electrical and/or thermal conductivity (such as copper) covered with a layer of plastic chosen for

electrical insulation, stability, and embossing characteristics. A substrate can serve as a dielectric, i.e., an insulating medium that intervenes between two conductors.

#### Imprinting Overview

5

10

15

20

25

30

Single layer imprinting, imprinting on opposite sides of a core, as well as multilayer imprinting is possible. Single layers are used in applications not requiring significant I/O routing or a substantial power supply, such as flash memory devices, and the like. Two-sided imprinting is useful in flip chip applications, for example. Multilayers are commonly used in a number of applications as is known in the art.

Materials useful for imprinting include thermoplastic polymers and thermoset resins. However, with thermoplastic polymers, the entire package must be reheated to temperatures typically around 300 °C in order to add additional layers, i.e., to laminate. At these temperatures, it is possible to deform or destroy previously imprinted features. Each subsequent layer should be a thermoplastic material that has a lower melting point so that when the new layer is added, the previous layer is not melted and destroyed. The lower melting point thermoplastic can be a different material or can be the same thermoplastic material processed under different conditions to have a lower melting point. Care must also be taken to keep thickness variations between the layers to a minimum.

In contrast, thermoset resins typically do not require temperatures over about 250 °C to cure. Furthermore, once set, thermoset resins do not remelt. Therefore, it is not necessary to use different types of thermoset resins having different melting points when laminating with thermoset resins.

Additionally, high melting point thermoplastics used for imprinting typically require use of a carbon tetraflouride plasma to remove excess polymer at the bottom of imprinted vias. Typically, such plasmas require a high vacuum chamber into which a precursor gas, such as tetrafluoromethane, combined with small amounts of oxygen, is introduced. High frequency radio waves are used to cause the gas to ionize, thus forming the plasma, and attack the surfaces in the chamber. The resulting chemical reaction removes surface atoms from whatever organic material is located in the chamber.

In contrast, thermoset resins do not require the use of plasma for removal of excess material. Rather, the substrates are dipped into tanks of a corrosive chemical, such

as an alkaline potassium permanganate solution, concentrated sulfuric acid, and the like, for 10-15 minutes to etch away the surface atoms.

Further, when thermoplastics are used, deposition of a seed layer, i.e., catalyst, (for subsequent metallization) having sufficient adhesion requires use of a sputtering process. Sputtering takes place in a pressure chamber into which the surface needing the seed layer, i.e., the target, is placed. A chrome copper wire is evaporated, causing the deposition of a thin metallic layer onto the target.

5

10

15

20

25

30

In contrast, thermoset resins do not require sputtering to initiate an adequate seed layer. Rather, the substrate is chemically roughened using a suitable chemical, such as an alkaline potassium permanganate solution. The surface is then immersed into a solution, e.g., colloidal palladium chloride, capable of adsorbing onto the exposed surfaces to form a seed layer for subsequent plating processes.

As compared with conventional processes, imprinting has several advantages, including eliminating the laser drilling and photolith processes normally required to create the desired features. (Laser drilling is typically used to ablate the vias, while a photolith process is used to define the areas where plating has occurred and which will be subject to further plating). Furthermore, no "target" is required with imprinting. Therefore, via pads are not needed for the purpose of "locating" a drilled via, although via pads can still be used for other purposes.

Using thermoset resins for the imprinting process provides additional advantages as noted above. Additionally, by applying the thermoset resin as an "A-stage" or "varnish" resin, as described in the embodiments herein, many additional benefits are achieved. For example, use of an A-stage resin to add a layer as opposed to laminating a dry film, i.e., either a thermoplastic or partially cured, e.g., a B-stage, thermoset resin, not only eliminates the uncertainty with respect to whether air bubbles are trapped, material has flowed to the edges of the features, and so forth, it also eliminates any detrimental effects of attempting to overcome these problems. Specifically, use of conventional materials requires application of additional pressure on each layer (up to about 34 atm (500 psi) for thermoplastic materials and about 3.4 atm (50 psi) for thermoset resins applied as B-stage resins), at increased temperatures in order to make sure air bubbles are removed, material has flowed to the edges, as well as to ensure the resulting film sticks sufficiently to the surface being coated. Such pressure can cause damage to features already present on the

surface. Use of an A-stage resin eliminates the need for the application of pressure during lamination. Use of an A-stage resin also eliminates any issues regarding film thickness control. Specifically, with conventional lamination using either a thermoplastic or a partially cured thermoset material, the use of increased temperatures as noted above, i.e., in the range of about a 100 to 350 °C increase, also presents difficulties. Although the higher temperatures are required to obtain good adhesion and to cause the film to flow into the uneven surfaces being coated, it also makes it difficult to adequately control film thickness. Furthermore, the use of these elevated temperatures can have a detrimental effect on previously installed components. Use of an A-stage resin does not require elevated temperatures to achieve consistent film thickness as the liquid essentially "self-flattens" onto the surface being coated, thus creating a smooth and uniform layer.

#### Description of the Embodiments

5

10

15

20

25

30