(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-153827

(P2004-153827A)

(43) 公開日 平成16年5月27日(2004.5.27)

(51) Int.Cl.<sup>7</sup>

H03M 1/12

F 1

H03M 1/12

テーマコード(参考)

C

5 J 0 2 2

審査請求 未請求 請求項の数 25 O L (全 32 頁)

(21) 出願番号 特願2003-365742 (P2003-365742)

(22) 出願日 平成15年10月27日 (2003.10.27)

(31) 優先権主張番号 10/284890

(32) 優先日 平成14年10月30日 (2002.10.30)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100087642

弁理士 古谷 聰

(74) 代理人 100076680

弁理士 溝部 孝彦

(74) 代理人 100121061

弁理士 西山 清春

最終頁に続く

(54) 【発明の名称】 オン・チップ・メモリを備えたアナログ・デジタル変換器

## (57) 【要約】

【課題】より単純な構成で高サンプリングレートを実現するアナログ・デジタル変換システムを提供する。

【解決手段】アナログ・デジタル変換システム(100)は、デジタル出力(122)を有するアナログ・デジタル変換器(102)、データ入力(130)及びデータ出力(132)を有するメモリ(106)、出力ポート(110)、アナログ・デジタル変換器のデジタル出力からメモリのデータ入力まで延びる入力データバス(104)、及び、メモリのデータ出力から出力ポートまで延びる出力データバス(108)を備える。アナログ・デジタル変換器は、あるサンプリングレートでデジタルサンプルを生成するように構成される。入力データバスは、ADCのサンプリングレートで動作するよう構成される。メモリのデータ出力(132)、出力データバス(108)及び出力ポート(108)の少なくとも1つが、そのサンプリングレートよりも遅い最大レートで動作するよう構成される。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

アナログ・ディジタル変換システム(100)であって、

あるサンプリング・レートでディジタル・サンプルを生成するように構成された、ディ

ジタル出力(122)を有するアナログ・ディジタル変換器(102)と、

データ入力(130)及びデータ出力(132)を有するメモリ(106)と、

出力ポート(110)と、

前記アナログ・ディジタル変換器の前記ディジタル出力から前記メモリの前記データ入

力まで延び、前記サンプリング・レートで動作するように構成された入力データ・バス(104)

)と、

前記メモリの前記データ出力から前記出力ポートまで延びる出力データ・バス(108

)

を備え、

前記メモリの前記データ出力(132)、前記出力データ・バス(108)、及び、前

記出力ポート(110)の少なくとも1つが、前記サンプリング・レートより低い最大速

度で動作するように構成されることからなる、アナログ・ディジタル変換システム。

**【請求項 2】**

前記メモリ(206)がメモリ・モジュール(例えば、206-1)を備え、該メモリ

・モジュールの各々が、データ入力(230)及びデータ出力(232)を有し、

前記入力データ・バス(304)が、前記アナログ・ディジタル変換器の前記ディジタ

ル出力から前記メモリ・モジュールのそれぞれの前記データ入力まで延びることからなる

、請求項1に記載のアナログ・ディジタル変換システム。

**【請求項 3】**

前記入力データ・バスが、

前記アナログ・ディジタル変換器の前記ディジタル出力から延びる少なくとも1つのA

DCサブバス(370)と、

前記少なくとも1つのADCサブバスから前記メモリ・モジュールのうちのいくつかの

メモリ・モジュールの前記データ入力に接続する入力サブバス(例えば、304-1)

を備えることからなる、請求項2に記載のアナログ・ディジタル変換システム。

**【請求項 4】**

前記出力データ・バス(208)が、前記メモリ・モジュールのうちのいくつかのメモ

リ・モジュールの前記データ出力から延びる出力サブバス(例えば、208-1)を備え

る、請求項2に記載のアナログ・ディジタル変換システム。

**【請求項 5】**

前記出力サブバスが、それぞれ、前記出力ポート(210)まで延びることからなる

、請求項4に記載のアナログ・ディジタル変換システム。

**【請求項 6】**

前記出力データ・バス(208)が、前記出力ポート(210)まで延びる少なくとも

1つの出力ポート・サブバス(256)をさらに備え、

前記出力サブバスの1つが、少なくとも1つの前記出力ポート・サブバスに接続するこ

とからなる、請求項4に記載のアナログ・ディジタル変換システム。

**【請求項 7】**

前記出力データ・バス(208)が、さらに、

前記出力ポートまで延びる少なくとも1つの出力ポート・サブバス(256)と、

前記少なくとも1つの出力ポート・サブバスと前記出力サブバスとの間に配置されたデ

ータ・セレクタ

を備える、請求項4に記載のアナログ・ディジタル変換システム。

**【請求項 8】**

前記アナログ・ディジタル変換器(202)が、アナログ・ディジタル変換器モジュー

ル(例えば、202-1)を備え、該アナログ・ディジタル変換器モジュー

ルの各々が、

10

20

30

40

50

デジタル出力(222)を有し、

前記入力データ・バス(204)が、前記アナログ・ディジタル変換器モジュールのデジタル出力から前記メモリ・モジュールの前記データ入力まで延びることからなる、請求項2に記載のアナログ・ディジタル変換システム。

【請求項9】

前記入力データ・バス(204)が、前記アナログ・ディジタル変換器モジュールのデジタル出力から前記メモリ・モジュールの前記データ入力まで延びる入力サブバス(例えば、204-1)を備える、請求項8に記載のアナログ・ディジタル変換システム。

【請求項10】

前記メモリ・モジュール(例えば、406-1)の数が、前記アナログ・ディジタル変換器モジュールよりも少なく、10

前記入力データ・バス(404)が、

前記ADCモジュールの前記デジタル出力から延びるADCサブバス(例えば、470-1)と、

前記メモリ・モジュールの前記データ入力まで延びる入力サブバス(例えば、404-1)

を備え、

前記ADCサブバスの2つ以上が、前記入力サブバスのそれぞれに結合され、前記入力サブバスの幅(例えば、2m)が、それに結合される前記ADCサブバスの幅(m)の合計に等しいことからなる、請求項8に記載のアナログ・ディジタル変換システム。20

【請求項11】

前記出力データ・バス(208)が、前記メモリ・モジュールの前記出力から前記出力ポート(210)まで延びることからなる、請求項8に記載のアナログ・ディジタル変換システム。

【請求項12】

前記アナログ・ディジタル変換器(202)がアナログ・ディジタル変換器モジュール(例えば、202-1)を備え、該アナログ・ディジタル変換器モジュールの各々がデジタル出力(222)を有し、

前記入力データ・バス(204)が、前記アナログ・ディジタル変換器モジュールの前記デジタル出力から前記メモリ(206)まで延びることからなる、請求項1に記載のアナログ・ディジタル変換システム。30

【請求項13】

前記メモリ(206)がメモリ・モジュール(例えば、206-1)を備え、該メモリ・モジュールの各々が、データ入力(230)及びデータ出力(232)を有し、

前記出力データ・バス(208)が、前記メモリ・モジュールの前記出力から前記出力ポート(210)まで延びることからなる、請求項1に記載のアナログ・ディジタル変換システム。

【請求項14】

前記サンプリング・レートで前記アナログ・ディジタル変換器から前記デジタル・サンプルを受け取るように接続され、かつ、デジタル・サンプルが前記メモリに伝送される速度を低下させるように構成されたサンプル・プロセッサ(612)を前記入力データ・バスが備える、請求項1に記載のアナログ・ディジタル変換システム40

【請求項15】

アナログ入力信号をデジタル的にサンプリングする方法であって、

メモリを設けるステップ(702)と、

あるサンプリング・レートで、前記アナログ入力信号をデジタル的にサンプリングして、デジタル・サンプルを生成するステップ(704)と、

前記サンプリング・レートで前記メモリに前記デジタル・サンプルを記憶するステップ(706)と、

前記サンプリング・レートより低い速度で、前記メモリから前記デジタル・サンプル50

を読み出すステップ(708)

を含む、方法。

【請求項16】

メモリを設ける前記ステップ(702)において、メモリ・モジュールから構成されるメモリを設ける、請求項15に記載の方法。

【請求項17】

前記ディジタル・サンプルを記憶するステップ(706)が、記憶する前に、前記メモリ・モジュール間に前記ディジタル・サンプルを分配するステップを含む、請求項16に記載の方法。

【請求項18】

アナログ入力信号をディジタル的にサンプリングする前記ステップ(704)が、サンプル・ストリームの形態で前記ディジタル・サンプルを出力するステップを含み、前記サンプル・ストリームの速度が、全体として、前記サンプリング・レートに等しく、

前記ディジタル・サンプルを記憶するステップ(706)が、前記メモリ・モジュールのそれぞれに、前記サンプル・ストリームのそれそれぞれにおける(またはサンプル・ストリームの形態で)ディジタル・サンプルを記憶するステップを含むことからなる、請求項16に記載の方法。

【請求項19】

アナログ入力信号をディジタル的にサンプリングするステップ(704)が、サンプル・ストリームの形態で前記ディジタルサンプルを出力するステップを含み、前記サンプル・ストリームの速度が、全体として、前記サンプリング・レートに等しく、

前記ディジタル・サンプルを記憶するステップ(706)が、前記メモリ・モジュールのそれぞれに、前記サンプル・ストリームのうちの複数のストリームにおける(またはサンプル・ストリームの形態で)前記ディジタル・サンプルを記憶するステップを含むことからなる、請求項16に記載の方法。

【請求項20】

メモリから前記ディジタル・サンプルを読み出す前記ステップ(708)が、前記メモリ・モジュールの1つから複数の前記ディジタル・サンプルを読み出した後で、別のメモリ・モジュールから前記ディジタル・サンプルを読み出すステップを含むことからなる、請求項16に記載の方法。

【請求項21】

メモリから前記ディジタル・サンプルを読み出す前記ステップ(708)が、前記メモリ・モジュールの少なくとも2つから前記ディジタル・サンプルを並列に読み出すステップを含むことからなる、請求項16に記載の方法。

【請求項22】

メモリから前記ディジタル・サンプルを読み出す前記ステップ(708)が、前記メモリから前記ディジタル・サンプルを、それらが記憶された順に読み出すステップを含むことからなる、請求項16に記載の方法。

【請求項23】

ディジタル・サンプルが前記メモリに伝送される速度を前記サンプリング・レートに対して低下させるステップ(710)をさらに含み、

メモリに前記ディジタル・サンプルを記憶する前記ステップ(708)において、前記ディジタル・サンプルが、前記低下された速度で前記メモリに記憶されることからなる、請求項16に記載の方法。

【請求項24】

ディジタル・サンプルが前記メモリに伝送される速度を低下させる前記ステップ(710)が、前記ディジタル・サンプリングによって生成されたディジタル・サンプルの全てではなく、前記ディジタル・サンプリングによって生成されたディジタル・サンプルのうちから選択されたサンプルを前記メモリに伝送するステップを含むことからなる、請求項23に記載の方法。

10

20

30

40

50

**【請求項 25】**

ディジタル・サンプルが前記メモリに伝送される速度を低下させる前記ステップ(710)が、

前記ディジタル・サンプリングによって生成された前記ディジタル・サンプルの中からディジタル・サンプルの計算を実施するステップと、

前記ディジタル・サンプリングによって生成された前記ディジタル・サンプルの全てではなく、前記計算されたディジタル・サンプルを前記メモリに伝送するステップを含むことからなる、請求項23に記載の方法。

**【発明の詳細な説明】****【技術分野】**

10

**【0001】**

本発明は、アナログ・ディジタル変換器(ADC)、特に、メモリを備えるアナログ・ディジタル変換システムに関する。

**【背景技術】****【0002】**

高速アナログ・ディジタル変換器(ADC)は、極めて高いサンプリング・レートで動作して、ディジタル・サンプルを生成する。例えば、高速変換システムで用いられる8ビット、10GSa/秒のADCは、80ギガビット/秒のデータ転送速度(データレート)。本明細書では、速度をレートとも記載する)でディジタル・サンプルを生成する。従来のADCは、一般に、ディジタル・サンプルの生成速度で、すなわち、上記例の場合、80ギガビット/秒のデータ転送速度でディジタル・サンプルを出力する。こうした高データ転送速度でディジタル・サンプルを出力するために、従来のADCは、一般に、バス幅の広い出力バス、高速出力バス、または、バス幅が広くて、かつ、高速の出力バスを利用して、必要なデータ転送速度を達成する。バス幅の広い出力バスを備えたADCは、ピン数の多いパッケージを必要とする。これによって、パッケージのコスト、及び、パッケージに適応するようにプリント回路を設計する上での複雑さが大幅に増すことになる。高速データ・バスを備えたADCの場合、データ信号がADCチップからプリント回路基板に送られる際ににおける、データ信号の完全性が確保されるよう、慎重に設計する必要がある。これには、かなりの注意と努力を払って、パッケージ、及び、パッケージが取り付けられるプリント回路基板を設計することが必要になる。

20

**【0003】**

超高速データ・バスの設計に対する一般的なアプローチは、ADCが組み込まれる集積回路(チップ)の出力をできるだけ高速になるように設計することである。達成可能な最高出力速度は、チップの製作に用いられる処理テクノロジ、及び、カスタム・パッケージ及び特殊プリント回路基板設計の利用可能性などの要因によって影響される。最高出力速度が決まると、必要とされる出力データ転送速度の実現に必要なだけの数の出力が利用される。これによって、チップが多数の出力を備え、パッケージが、相応して多数のピンを備える設計が必要になる。この結果、プリント回路基板の広い領域を占有する大面積のパッケージに収容される大面積のチップ設計が生じることになる。多数の最高速度出力によって、全電力消費も増大し、それに応じた多量の熱をパッケージから除去する必要が生じることになる。

30

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

従って、本発明の目的は、高サンプリング・レートでアナログ入力信号のサンプリングを実施することが可能である一方で、上述の欠点のないアナログ・ディジタル変換システムを提供することにある。

40

**【課題を解決するための手段】****【0005】**

本発明によれば、ディジタル出力を有するアナログ・ディジタル変換器、データ入力及

50

びデータ出力を有するメモリ、出力ポート、アナログ・ディジタル変換器のディジタル出力からメモリのデータ入力まで延びる入力データ・バス、及び、そのメモリのデータ出力から出力ポートまで延びる出力データ・バスを備える、アナログ・ディジタル変換システムが得られる。アナログ・ディジタル変換器は、あるサンプリング・レートでディジタル・サンプルを生成するように構成される。入力データ・バスは、A D C のサンプリング・レートで動作するように構成される。メモリのデータ出力、出力データ・バス、及び、出力ポートの少なくとも1つが、サンプリング・レートより低い最高速度で動作するように構成される。

#### 【0006】

本発明によれば、ディジタル方式でアナログ入力信号のサンプリングを行う方法も得られる。この方法では、メモリが設けられ、あるサンプリング・レートで、アナログ入力信号のディジタル方式によるサンプリングを行って、ディジタル・サンプルを生成し、ディジタル・サンプルが、そのサンプリング・レートでメモリに記憶される。ディジタル・サンプルは、そのサンプリング・レートより低い速度で、メモリから読み取られる。10

#### 【0007】

本発明によれば、極めて高いサンプリング・レートでアナログ入力信号をサンプリングすることができ、この場合、結果生じるディジタル・サンプルと同じ高速度（高レート）で出力する必要がない。ディジタル・サンプルをメモリから読み取る速度でディジタル・サンプルを出力することが可能な構成は、サンプリング・レートでディジタル・サンプルを出力する構成に比べて、大幅に単純にでき、コストを下げることができる。20

#### 【発明の効果】

#### 【0008】

本発明によれば、より単純な構成で高サンプリングレートを実現するアナログ・ディジタル変換システムが提供される。

#### 【実施例】

#### 【0009】

本発明によれば、同じチップ上に集積化されたアナログ・ディジタル変換器（A D C）とメモリを含む、アナログ・ディジタル変換システムが得られる。A D C によってサポートされる最高サンプリング・レートで動作するチップ・レベルの入力データ・バスが、A D C からメモリまで延びる。サンプリング・レートより低い速度で動作する出力データ・バスが、メモリの出力から出力ポートまで延びる。出力ポートには、一般に、チップとパッケージ間の相互接続、及び、パッケージとプリント回路との間の相互接続が含まれる。A D C は、そのサンプリング・レートでディジタル・サンプルを生成する。入力データ・バスは、A D C のサンプリング・レートで動作して、A D C によって生成されたディジタル・サンプルをメモリに伝送する。メモリは、サンプリング・レートでディジタル・サンプルを記憶する。メモリに記憶されたディジタル・サンプルは、サンプリング・レートより低い速度で、メモリから読み取られる。出力データ・バスは、メモリからディジタル・サンプルを読み取る速度で、メモリから読み取られたディジタル・サンプルを出力ポートに伝送する。この速度は、サンプリング・レートより低いので、超高速出力回路を用いる必要がなく、出力データ・バスは、バス幅が広くなくても、高速でなくても、または、バス幅が広くなく、かつ、高速でなくてもかまわないし、データ信号の完全性に優れた、高データ転送速度の出力を行うように出力ポートを構成する必要がない。サンプリングレートより低い速度でメモリからディジタル・サンプルを読み取ることによって、出力ポートより下流の回路要素によるディジタル・サンプルの受信及び処理もまた容易に実施できるようになる。こうした回路要素は、一般に、アナログ・ディジタル変換システムより低い速度で動作する。3040

#### 【0010】

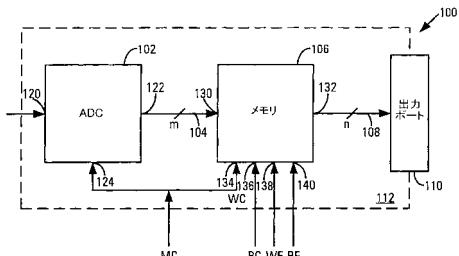

図1は、本発明によるアナログ・ディジタル変換システムの第1の実施態様100のブロック図である。アナログ・ディジタル変換システム100は、アナログ・ディジタル変換器102、入力データ・バス104、メモリ106、出力データ・バス108、及び、50

出力ポート 110 から構成されている。アナログ・ディジタル変換器、入力データ・バス、メモリ、出力データ・バス、及び、出力ポートの一部によって、少なくともチップ 112 の一部が構成されている。アナログ・ディジタル変換器は、アナログ入力 120、ディジタル出力 122、及び、クロック入力 124 を備えている。メモリは、データ入力 130、データ出力 132、書き込みクロック入力 134、読み取り（または読み出し。以下同じ）クロック入力 136、書き込み許可（またはライトイネーブル。以下同じ）入力 138、及び、読み取り許可（またはリードイネーブル。以下同じ）入力 140 を備えている。

#### 【0011】

マスタ・クロック信号 MC が、ADC 102 のクロック入力 124 及びメモリ 106 の書き込みクロック入力 134 に接続される。直接接続が示されているが、マスタ・クロック信号は、適正な周波数の 1 つ以上のクロック信号を ADC に供給する適正なクロック発生器（不図示）を介して、クロック入力 124 に接続することが可能である。ADC のサンプリング・レートは、マスタ・クロック信号の周波数によって決まるが、必ずしも、マスタ・クロック信号の周波数に等しいとは限らない。同様に、マスタ・クロック信号は、適正な周波数の 1 つ以上のクロック信号をメモリに供給する適正なクロック発生器（不図示）を介して、書き込みクロック入力 134 に接続することが可能である。代替的には、ADC によって、メモリにクロック信号を供給することも可能である。

#### 【0012】

当該技術分野では、アナログ・ディジタル変換器 102 として用いるのに適した多種多様なタイプのアナログ・ディジタル変換器が周知のところである。従って、ADC 102 については、これ以上の説明を控えることにする。以下では、図 5 を参照しながら、特定の例の 1 つについて述べることにする。

#### 【0013】

入力データ・バス 104 は、m の導体（個別には示されていない）から構成され、ADC 102 のデジタル出力 122 からメモリ 106 のデータ入力 130 まで延びている。入力データ・バスを構成する導体は、長さが短く、チップ 112 の表面を横切って、直接、ADC のデジタル出力からメモリのデータ入力まで延びている。従って、入力データ・バスは、ADC によってサポートされる最高のサンプリング・レートで動作することが可能である。

#### 【0014】

当該技術分野では、メモリ 106 として用いるのに適した多種多様なタイプのメモリ素子が周知のところである。例えば、メモリ 106 として、従来のランダム・アクセス・メモリ（RAM）素子を用いることが可能である。RAM のタイプが異なれば、得られる性能特性も異なる。例えば、スタティック RAM（SRAM）の場合は、速度が増し、ダイナミック RAM（DRAM）の場合は、密度が高くなり、フラッシュ RAM の場合は、不揮発性になる。代替的には、メモリ 106 として、非ランダム・アクセス・メモリ素子を用いることも可能である。例えば、メモリ 106 として、シフト・レジスタ、先入れ・先出し（FIFO）メモリ、後入れ・先出し（LIFO）メモリのようなメモリ素子、または、他のタイプの非ランダム・アクセス・メモリ素子を用いることが可能である。やはり、非ランダム・アクセス・メモリ素子のタイプが異なれば、得られる性能特性も異なる。

#### 【0015】

メモリ 106 のサイズによって、記憶することが可能なデジタル・サンプルの数が決まる。用途によっては、多数のデジタル・サンプルを記憶する能力は有利になる。例えば、持続時間の長い事象のサンプリングが可能になるし、または、より精密な時間分解能が得られるように、サンプリング・レートを高めることができくなる。

#### 【0016】

さまざまなサイズのメモリを組み込んだアナログ・ディジタル変換システムを具現化するチップを容易に製作することができるよう、メモリ 106 は、モジューラ構造にすることが可能である。

10

20

30

40

50

## 【0017】

メモリ106のデータ入力130は、入力データ・バス104に接続されている。データ出力132は、出力データ・バス108に接続されている。書き込みクロック入力134は、書き込みクロック信号WCを受信するように接続されている。読み取りクロック入力136は、読み取りクロック信号RCを受信するように接続されている。書き込み許可入力138は、書き込み許可信号WEを受信するように接続されている。読み取り許可入力140は、読み取り許可信号REを受信するように接続されている。

## 【0018】

メモリ106がランダム・アクセス・メモリ素子から構成される実施態様の場合、メモリには、さらに、アドレス発生器(不図示)も含まれる。書き込み許可信号WEがアサートされると、アドレス発生器は、書き込みクロック信号WCに応答して作動し、データ入力130で受信したディジタル・サンプルが記憶される記憶場所(メモリ位置)のアドレスを生成する。読み取り許可信号REがアサートされると、アドレス発生器は、読み取りクロック信号RCに応答して作動し、データ出力132に送られるディジタル・サンプルが読み取られる記憶場所(メモリ位置)のアドレスを生成する。適合するアドレス発生器は、当該技術分野においては周知のところであり、従って、ここでは説明を控えることとする。

## 【0019】

メモリ106として用いられるメモリ素子が單一クロック入力を備える実施態様には、書き込み許可信号WE及び読み取り許可信号REに応答して作動し、書き込みクロック及び読み取りクロックの適合する一方を單一クロック入力に供給するゲート回路要素(不図示)が含まれる。代替的には、読み取り許可信号によって、その出力が單一クロック入力に接続されているクロック分割回路を起動することが可能である。

## 【0020】

出力・データ・バス108は、nの導体から構成されており(個別には示されていない)、メモリ106のデータ出力132から出力ポート110まで延びている。図示の例では、入力データ・バスと出力データ・バスの導体数が等しい。他の例では、これらのバスの導体数が異なる場合もある。例えば、メモリからQのサンプルを並列に読み取る実施態様の場合、出力データ・バスのバス幅は、入力データ・バスのQ倍にすることが可能である。ADCによって、Mのディジタル・サンプルがメモリに並列に伝送されるが、ディジタル・サンプルが、メモリから1つずつ読み取られる実施態様の場合、出力データ・バスのバス幅は、入力データ・バスの1/Mになる。

## 【0021】

ADC102のサンプリング・レートより低い速度でメモリ106からディジタル・サンプルを読み取ることによって、メモリのデータ出力132、出力データ・バス108、及び、出力ポート110の少なくとも1つについて、幅を狭めるよう構成し、かつ、ADCのサンプリング・レートより低い最高速度で動作させるか、あるいは、そのいずれかを実施することが可能になる。例えば、データ出力に、比較的低速の出力回路を組み込むことが可能である。低速出力回路によって、例えば、チップ112のチップ面積を縮小し、電力消費を低減することが可能になる。出力データ・バス108は、比較的長く、細い導体から構成することが可能である。長くて、細い導体によって、例えば、チップ112のレイアウトをより都合のよいものにすることが可能になり、チップ面積を縮小することが可能になる。出力ポート110には、チップ112の表面に配置されたボンディング・パッド(不図示)、チップが取り付けられるパッケージのピン(不図示)、及び、ボンディング・パッドからピンのそれぞれにまで延びる、ボンディング・ワイヤのような相互接続が含まれている。ピンという用語は、本明細書では、ピン、及び、パッケージ化集積回路とプリント回路基板との間において、電気的接続、及び、一般には、さらに、機械的接続をもたらす他の構造を包含する総称として用いられている。

## 【0022】

上述した例は、許容し得るデータ信号の完全性を保って、メモリ106によって出力さ

10

20

30

40

50

れるデジタル・サンプルをパッケージ・ピンに送ることが可能な最高速度に対して、共同で、あるいは、個別に制限を課すことになる。従って、読み取りクロック信号RCの周波数は、デジタル・サンプルがメモリから読み取られ、出力データ・バス108によって出力ポート110に送られる速度が、上述の最高速度以下になるように設定される。最高速度は、ADC102のサンプリング・レート未満である。

#### 【0023】

さらに、チップ112が取り付けられたパッケージは、プリント回路基板（不図示）に取り付けることが可能であり、このプリント回路基板には、さらに、アナログ・デジタル変換システム100によって出力されるデジタル・サンプルを受信する下流の回路が取り付けられている。こうした下流の回路がデジタル・サンプルを受信することが可能な最高速度は、デジタル・サンプルが上述の最高データ転送速度より低いデータ転送速度でメモリから読み取られることを必要とする可能性がある。10

#### 【0024】

次に、アナログ・デジタル変換システム100の動作について述べることにする。アナログ・デジタル変換器102は、アナログ入力120を介してアナログ入力信号を受信する。アナログ・デジタル変換器は、クロック入力124を介して受信したマスター・クロック信号MCに応答して作動し、マスター・クロック信号によって決まるサンプリング・レートでアナログ入力信号のデジタル・サンプルを生成する。アナログ・デジタル変換器は、デジタル出力122からデジタル・サンプルを出力する。20

#### 【0025】

入力データ・バス104は、デジタル・サンプルをメモリ106のデータ入力130に伝送する。メモリは、書き込みクロック入力134を介して書き込みクロック信号WCを受信し、読み取りクロック入力136を介して読み取りクロック信号RCを受信する。書き込み許可信号WEが有効（イネーブル）になると、メモリは、書き込みクロック信号WCに応答して作動し、データ入力130で受信したデジタル・サンプルを記憶する。例えば、メモリは、そのデータ入力で連続して受信したデジタル・サンプルのいくつかを連続するアドレスを有する記憶場所（メモリ位置）に記憶することが可能である。30

#### 【0026】

書き込み許可信号WEがアサートされている間、入力データ・バス104を介して受信したデジタル・サンプルのメモリ106への記憶は継続される。ある動作モードの場合、メモリのサンプル容量未満の所望の数のサンプルがメモリに記憶されると、または、メモリが満杯になると、デジタル・サンプルの記憶が停止される。もう1つの動作モードでは、メモリが満杯になると、受信したデジタル・サンプルによって、メモリに記憶されているデジタル・サンプルのうち最古のものが上書きされる。この動作モードの場合、メモリには、常に、Jの最新の受信デジタル・サンプルが記憶されている。ここで、Jはメモリのサンプル容量である。この動作モードでは、サンプリングされる事象の発生前に、書き込み許可信号WEをアサートすることが可能になる。次に、こうした事象の発生を検出して、その事象が完了すると、書き込み許可信号WEのアサートを終了する（ディアサートする）ことが可能になる。事象の持続時間が、メモリのサンプル容量に等しい数のデジタル・サンプルを生成するのに必要な時間より短い場合には、書き込み許可信号のディアサート時に、事象を表わす1組のデジタル・サンプルがメモリ内に記憶されたままになる。40

#### 【0027】

ある事象を表わすデジタル・サンプルがメモリ106に記憶されていて、書き込み許可信号WEがディアサートされると、読み取り許可信号REがアサートされる。次に、メモリ106は、読み取りクロック信号RCに応答して作動し、それに記憶されているデジタル・サンプルをデジタル出力132から出力する。出力データ・バス108によって、デジタル・サンプルがデータ出力132から出力ポート110に送られる。デジタル・サンプルが、メモリ106から、従って、出力ポート110から出力される速度は、読み取りクロックRCの周波数によって決まり、ADC102のサンプリング・レート50

より低い。デジタル・サンプルがメモリから読み取られる最高速度は、上述のメモリのデータ出力の構成、出力データ・バス 108 の構成、及び、出力ポート 110 の構成といった要素によって決まる。デジタル・サンプルの読み取り速度は、やはり上述の、下流回路要素のデータ転送速度要件に適合するように、さらに低下させることが可能である。

#### 【0028】

デジタル・サンプルは、メモリ 106 へのデジタル・サンプルの記憶順に、メモリから読み取ることが可能である。これによって、デジタル・サンプルが表わす事象の解析に必要な下流処理（または以降の処理）が最小限に抑えられる。代替的には、サンプルを異なる順に読み取ることも可能である。例えば、デジタル・サンプルを異なる順に読み取ると、メモリにとってより好都合である場合もあり、また、下流の回路要素によって、デジタル・サンプルをより好適に順序付けし直すことも可能である。10

#### 【0029】

約 10 Gsa / s 以上のサンプリング・レートで動作するアナログ・デジタル変換器には、一般に、複数のアナログ・デジタル変換器モジュールが含まれている。アナログ・デジタル変換器が、M のアナログ・デジタル変換モジュールから構成される実施態様の場合、各アナログ・デジタル変換器モジュールのサンプリング・レートは、ADC 全体のサンプリング・レートの 1 / M になる。本発明は、メモリに各 ADC モジュールに対応するメモリ・モジュールが含まれている、この ADC アーキテクチャに対する適用が容易である。メモリ・モジュールは、ADC モジュールによって生成されるデジタル・サンプルを記憶する。次に、全体として、メモリに記憶されているデジタル・サンプルが、ADC のサンプリング・レートより低い速度で読み取られる。メモリから読み取られたデジタル・サンプルは、出力データ・バス及び出力ポートを介して、アナログ・デジタル変換システムから出力される。20

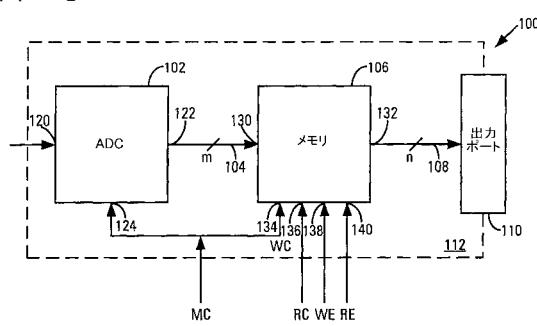

#### 【0030】

図 2 は、アナログ・デジタル変換器 202 が、M のアナログ・デジタル変換器モジュール 202-1 ~ 202-M から構成され、入力データ・バス 204 が、M の入力サブバス 204-1 ~ 204-M から構成され、メモリ 206 が、M のメモリ・モジュール 206-1 ~ 206-M から構成され、出力データ・バス 208 が、M の出力サブバス 208-1 ~ 208-M と、出力ポート・サブバス 256 から構成される、本発明によるアナログ・デジタル変換システムの第 2 の実施態様 200 のブロック図である。図 2 には、30

図面を単純化するため、アナログ・デジタル変換器 202-1、202-2、202-3、及び、202-M、入力サブバス 204-1、204-2、204-3、及び、204-M、メモリ・モジュール 206-1、206-2、206-3、及び、206-M、及び、出力サブバス 208-1、208-2、208-3、及び、208-M だけしか示されていない。

#### 【0031】

アナログ・デジタル変換システム 200 は、さらに、出力ポート 210 と、多相クロック発生器 250 から構成されている。アナログ・デジタル変換器、入力データ・バス、メモリ、出力データ・バス、多相クロック発生器、及び、出力ポートの一部によって、少なくとも、チップ 212 の一部が構成される。40

#### 【0032】

アナログ・デジタル変換 (ADC) 器モジュール 202-1 は、アナログ入力 220、デジタル出力 222、及び、クロック入力 224 を備えている。アナログ・デジタル変換器モジュール 202-2 ~ 202-M は、同様に構成されているので、個別の説明は控えることにする。アナログ・デジタル変換器モジュール 202-2、202-3、及び、202-M のアナログ入力、デジタル出力、及び、クロック入力を示す参照番号は、図面を単純化するため、図 2 から省略されている。ADC モジュール 202-1 ~ 202-M のアナログ入力 220 は、アナログ入力 120 と並列に接続されている。

#### 【0033】

メモリ・モジュール 206-1 は、データ入力 230、データ出力 232、書き込みク50

ロック入力 234、読み取りクロック入力 236、書き込み許可入力 238、及び、読み取り許可入力 240を備えている。メモリ・モジュール 206-2~206-Mは、同様に構成されているので、個別の説明は控えることにする。メモリ・モジュール 206-2、206-3、及び、206-Mのデータ入力、データ出力、書き込みクロック入力、読み取りクロック入力、書き込み許可入力、及び、読み取り許可入力を示す参照番号は、図面を単純化するため、図2から省略されている。

#### 【0034】

多相クロック発生器 250は、クロック入力 252、及び、Mのクロック出力 254-1~254-Mを備えているが、図面を単純化するため、クロック出力は、254-1、254-2、254-3、及び、254-Mだけしか示されていない。マスタ・クロック信号 MCは、クロック入力 252に接続されている。クロック出力 254-1~254-Mは、それぞれ、ADC モジュール 202-1~202-Mのクロック入力 224、及び、それぞれ、メモリ・モジュール 206-1~206-Mの書き込みクロック入力 234に接続されている。多相クロック発生器は、互いに 2 / M ラジアンだけ異なるMの位相を有する多相クロック信号を発生する。各位相の周波数は、ADC のサンプリング周波数の 1 / M である。多相クロック発生器は、クロック出力 254-1~254-Mから多相クロック信号を出力する。10

#### 【0035】

ディジタル・サンプルが、それらが記憶された時間順に、メモリ 206 から読み取られる実施態様の場合、読み取りクロック信号 RCは、多相クロック信号発生器 250によって生じる多相クロック信号に類似しているが、それより遅い多相クロック信号である。こうした多相読み取り読み取りクロック信号は、さらに、多相クロック信号発生器のクロック出力 254-1~254-Mを、それぞれ、メモリ・モジュール 206-1~206-Mの読み取りクロック入力 236に接続することによって供給することが可能である。マスタ・クロック信号 MCが、メモリ 206 からのディジタル・サンプルの読み取り中に、読み取り許可信号 REによって使用可能になる（イネーブルにされる）クロック信号分割器（不図示）を介して、多相クロック信号発生器に供給される。クロック信号分割器によって、マスタ・クロック信号の周波数が分割され、この結果、多相クロック発生器によって、低速の多相クロック信号がメモリ・モジュールに供給されることになる。20

#### 【0036】

もう1つの実施態様の場合、ディジタル・サンプルのうち複数のサンプルが、メモリ・モジュールの1つから読み取られ、その後、ディジタル・サンプルが、別のメモリ・モジュールから読み取られる。ディジタル・サンプルのうちから読み取られる複数のサンプルは、メモリ・モジュールに記憶されているディジタル・サンプルの部分集合から全ての範囲（全集合）におよびうる。この実施態様の場合、読み取りクロック信号 RCは、さらに、適合するクロック信号分割器（不図示）を介して、メモリ・モジュール 206-1~206-Mの読み取りクロック入力 236にマスタ・クロック信号 MCを供給することによって生じさせることが可能な单相信号である。クロック信号分割器は、周波数が、書き込みクロック入力 234 に供給される多相クロック信号の周波数の M 倍より低い読み取りクロック信号 RCを発生する。30

#### 【0037】

当該技術分野では、アナログ・ディジタル変換器モジュール 202-1~202-Mとして用いるのに適した多種多様なタイプのアナログ・ディジタル変換器モジュールが周知のところである。従って、ADC モジュールに関するこれ以上の詳細な説明は控えることにする。

#### 【0038】

入力サブバス 204-1~204-Mは、それぞれ、mの導体（個別には示されていない）から構成されており、それぞれ、ADC モジュール 202-1~202-Mのディジタル出力 222 から、それぞれ、メモリ・モジュール 206-1~206-Mのデータ入力 230まで延びている。入力サブバスを構成する導体は、長さが短く、ADC モジュー4050

ル 2 0 2 - 1 ~ 2 0 2 - M のディジタル出力 2 2 2 から、それぞれ、メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M のデータ入力 2 3 0 まで、直接、チップ 2 1 2 の表面を横切って延びている。従って、入力サブバスは、A D C モジュールによってサポートされる最高のサンプリング・レートで、動作可能である。

#### 【 0 0 3 9 】

当該技術分野では、メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M として用いるのに適した多種多様なタイプのメモリ素子が周知のところである。代替物及び代替物から選択する場合の考慮事項は、メモリ 1 0 6 に関して上述したものとほぼ同じである。

#### 【 0 0 4 0 】

メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M に、あるタイプのランダム・アクセス・メモリが含まれる実施態様の場合、メモリ・モジュールには、さらに、アドレス発生器（不図示）が含まれる。書き込み許可信号 W E がアサートされると、アドレス発生器は、書き込みクロック信号 W C に応答して作動し、データ入力 2 3 0 で受信したディジタル・サンプルを記憶する記憶場所（メモリ位置）のアドレスを生成する。読み取り許可信号 R E がアサートされると、アドレス発生器は、読み取りクロック信号 R C に応答して作動し、データ出力 2 3 2 に送られることになるディジタル・サンプルが読み取られる記憶場所（メモリ位置）のアドレスを生成する。適合するアドレス発生器は当該技術分野では周知であるので、ここでは説明はしない。代替的には、メモリ 2 0 6 に、單一アドレス発生器を含めることも可能である。アドレス発生器によって生じたアドレスは、アドレス分配バス（不図示）を介して、メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M に分配される。

#### 【 0 0 4 1 】

メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M として用いられるメモリ素子が、單一クロック入力を備える実施態様には、書き込み許可信号 W E 及び読み取り許可信号 R E に応答して作動し、書き込みクロック及び読み取りクロックの適合する一方を單一クロック入力に供給するゲート回路要素（不図示）が含まれている。代替的には、読み取り許可信号によって、その入力がマスタ・クロック信号 M C を受信し、その出力がメモリ・モジュールの單一クロック入力に接続される、クロック分割回路を起動することが可能である。

#### 【 0 0 4 2 】

出力サブバス 2 0 8 - 1 ~ 2 0 8 - M は、それぞれ、n の導体（個別には示されていない）から構成され、メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M のデータ出力 2 3 2 から、それぞれ、出力ポート 2 1 0 まで延びている。図示の例の場合、入力サブバスのそれぞれ、及び、出力サブバスのそれぞれは、等しい数の導体を備えている。他の例では、上述のように、これらのバスの導体数が異なる場合もある。

#### 【 0 0 4 3 】

図示の例の場合、出力データ・バス 2 0 8 は、さらに、出力ポート 2 1 0 まで延びる出力ポート・サブバス 2 5 6 から構成されている。出力サブバス 2 0 8 - 1 ~ 2 0 8 - M は、出力ポート・サブバスへと接続（またはファンイン）している。メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M の読み取り許可入力 2 3 8 を読み取り許可入力 2 6 0 に接続する読み取り許可バス 2 5 8 は、M ビット幅のバスであり、これを介して、メモリ・モジュールのそれぞれが、個別の読み取り許可信号を受信する。この実施態様の場合、メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M のデータ出力 2 3 2 は、トライステート構成である、すなわち、データ出力は、メモリ・モジュールの読み取り許可信号がアサートされる場合を除いて、O F F 状態（オフ状態）にある。ディジタル・サンプルがメモリ 2 0 6 から読み取られる場合には、ディジタル・サンプルが読み取られているメモリ・モジュールのデータ出力を除く、全てのメモリ・モジュールのデータ出力がO F F 状態にされる。

#### 【 0 0 4 4 】

代替実施態様の場合、メモリ・モジュール 2 0 6 - 1 ~ 2 0 6 - M のデータ出力 2 3 2 は、従来の 2 状態構成を有しており、読み取り許可バス 2 6 0 は、1 ビット幅のバスである。読み取り許可バスによって、メモリ・モジュールの読み取り許可入力 2 4 0 は、読み取り許可入力 2 6 0 と並列に接続されている。M 入力データ・セレクタ（不図示）が、出

10

20

30

40

50

力サブバス 208 - 1 ~ 208 - M と出力ポート・サブバス 256 の間に挿入されている。読み取り許可信号のアサートによって、全てのメモリ・モジュールが、ディジタル・サンプルを並列に読み取るよう設定される。出力サブバスによって、ディジタル・サンプルがデータ・セレクタに送られる。データ・セレクタの現在アクティブな入力に接続されたメモリ・モジュールから読み取られたディジタル・サンプルだけが、データ・セレクタによって出力され、出力ポート・サブバスを介して、出力ポート 210 に送られる。

#### 【0045】

もう 1 つの実施態様の場合、出力データバス 208 は、2 つ以上の出力ポート・サブバス（不図示）を含む。各組が出力サブバス 208 - 1 ~ 208 - M の少なくとも 2 つからなる出力サブバスの組が、出力ポート・サブバスのそれぞれに集束する（または、出力ポート・サブバスのそれぞれに送られる）。各出力ポート・サブバスは、出力ポート 210 まで延びている。M / P の出力ポート・サブバスが設けられた例の場合、P の出力サブバスが、各出力ポート・サブバスへ集束し、出力ポート 210 に含まれるピン数は、上述の実施態様の M / P 倍である。この実施態様の場合、上述のどの動作モードにおいても、メモリ・モジュール 206 - 1 ~ 206 - M からディジタル・サンプルを読み取ることが可能である。さらに、ディジタル・サンプルは、出力ポート・サブバスのそれぞれに接続されたメモリ・モジュールから並列に読み取ることが可能である。

#### 【0046】

もう 1 つの実施態様の場合、出力データ・バス 208 には、出力ポート・サブバス 256 がなく、出力サブバス 208 - 1 ~ 208 - M は、メモリ・モジュール 206 - 1 ~ 206 - M のデータ出力 232 から、それぞれ、出力ポート 210 まで直接延びている。この実施態様の場合、出力ポート 210 に含まれるピン数は、単一出力ポート・サブバスが出力ポートまで延びる実施態様の M 倍である。この実施態様の場合、上述のどの動作モードにおいても、メモリ・モジュールからディジタル・サンプルを読み取ることが可能であり、さらに、全てのメモリ・モジュールから並列に読み取ることが可能である。

#### 【0047】

メモリ・モジュール 206 - 1 ~ 206 - M のデータ出力 232、出力データ・バス 208 を構成する出力サブバス 208 - 1 ~ 208 - M 及び出力ポート・サブバス 256、及び、出力ポート 210 の 1 つ以上は、上述のものと同様に、ADC 202 のサンプリング・レートより低い最高速度で動作するように構成されている。ディジタル・サンプルは、メモリ 206 から読み取られ、許容し得るデータ信号の完全性を有して、出力ポートの一部を形成する出力ピンに送ることが可能な最高速度以下の速度で、出力ポート 210 に送られる。ディジタル・サンプルがメモリから読み取られ、出力ポートに送られる速度は、やはり上述のように、下流の回路が課す速度制限によってさらに低下する可能性がある。

#### 【0048】

次に、アナログ・デジタル変換システム（または、アナログ・デジタル変換器システム）200 の動作について述べることにする。アナログ・デジタル変換器モジュール 202 - 1 ~ 202 - M のそれぞれが、そのアナログ入力 220 を介してアナログ入力信号を受信する。各アナログ・デジタル変換器モジュールは、クロック入力 224 を介して受信した多相クロック信号のある位相に応答して作動し、ADC 202 全体のサンプリング・レートの 1 / M のサンプリング・レートでアナログ入力信号のデジタル・サンプルを生成する。アナログ・デジタル変換器モジュールに供給される多相クロック信号の位相は、2 / M ラジアンだけ異なっている。従って、隣接する多相クロック信号の位相を受信するアナログ・デジタル変換モジュールのいくつかによって生成されるデジタル・サンプルは、位相差に対応する時間だけ時間的に差がある。アナログ・デジタル変換モジュールは、それぞれ、そのデジタル出力 222 からデジタル・サンプルを出力する。

#### 【0049】

入力サブバス 204 - 1 ~ 204 - M は、それぞれ、ADC モジュール 202 - 1 ~ 2

10

20

30

40

50

02-Mによって生成されたデジタル・サンプルを、それぞれ、メモリ・モジュール・206-1～206-Mのデータ入力230に伝送する。各メモリ・モジュール206-1～206-Mは、さらに、書き込みクロック入力234を介して、多相クロック発生器250によって生じるある位相の多相クロック信号を受信する。メモリ・モジュールは、さらに、その読み取りクロック入力236を介して、読み取りクロック信号RCを受信する。書き込み許可信号WEが有効（イネーブル）になると、メモリ・モジュールは、多相クロック信号に応答して作動し、そのデータ入力230で受信したデジタル・サンプルを記憶する。例えば、各メモリ・モジュールは、そのデータ入力で連続して受信するデジタル・サンプルのいくつかを、連続したアドレスを有する記憶場所（メモリ位置）に記憶することが可能である。

10

## 【0050】

入力サブバス204-1～204-Mを介して受信したデジタル・サンプルの、メモリ・モジュール206-1～206-Mへの記憶は、それぞれ、書き込み許可信号WEがアサートされている間継続される。上述のように、動作モードの1つでは、デジタル・サンプルの記憶は、メモリのサンプル容量未満の所望の数のサンプルがメモリ206に記憶されるか、または、メモリが満杯になると、停止され、もう1つの動作モードでは、各メモリ・モジュールは、Jの最新の受信デジタル・サンプルを連続して記憶する。ここで、Jは、メモリ・モジュールのサンプル容量である。

## 【0051】

デジタル・サンプルがメモリ206に記憶され、書き込み許可信号WEがディアサートされると、メモリからデジタル・サンプルを読み取ることが可能になる。動作モードの1つでは、デジタル・サンプルは、それらが記憶された時間順に、メモリ・モジュールから読み取られる。この動作モードの場合、読み取りクロック信号RCは、多相クロック信号発生器250によって生じる多相クロック信号に類似しているが、それより遅い多相クロック信号である。もう1つの動作モードでは、メモリ・モジュールの1つから複数のデジタル・サンプルが読み取られた後、別のメモリ・モジュールからデジタル・サンプルが読み取られる。この場合、必要があれば、アナログ・デジタル変換システム200の下流の回路要素（不図示）によって、デジタル・サンプルの時間順が復元される。読み取られた複数のデジタル・サンプルは、メモリ・モジュールに記憶されているデジタル・サンプルの部分集合から全ての範囲（全集合）にまでおよぶ。

20

## 【0052】

動作モードに関係なく、メモリ・モジュール206-1～206-Mは、読み取り許可信号RE及び読み取りクロック信号RCに応答して作動し、データ出力232からそれに記憶されているデジタル・サンプルを出力する。出力サブバス208-1～208-M及び出力ポート・サブバス256によって、それぞれ、メモリ・モジュール206-1～206-Mのデータ出力232から出力ポート210にデジタル・サンプルが送られる。デジタル・サンプルがメモリ・モジュールから出力される速度は、読み取りクロック信号RCの周波数によって決まる。出力ポート210においてデジタル・サンプルを受信する速度は、ADC202のサンプリング・レートより低い。メモリ206からデジタル・サンプルが読み取られる最高データ転送速度を決定する要因については、上述のことである。メモリ206からデジタル・サンプルが読み取られるデータ転送速度は、やはり上述のように、下流の回路要素のデータ転送速度要件に応じて、さらに、低下させることが可能である。

30

## 【0053】

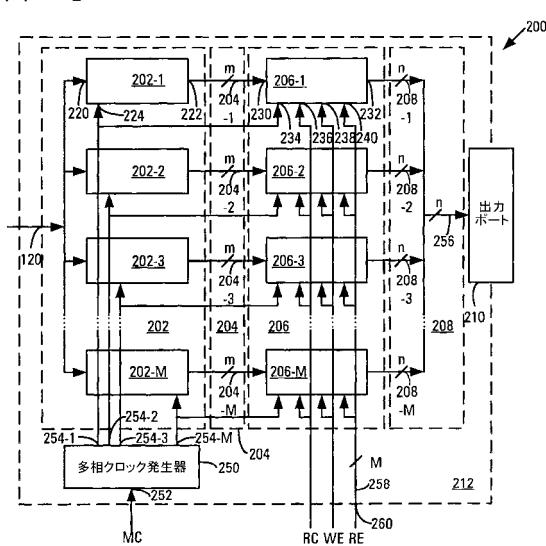

本発明によるアナログ・デジタル変換システムでは、メモリ・モジュールの数が、ADCまたはADCモジュールの数と異なる場合もある。次に、図3及び4を参照して、メモリ・モジュールの数がADCまたはADCモジュールの数を超えるか、または、それより少ない、アナログ・デジタル変換システムの例について述べることにする。

40

## 【0054】

図3は、單一アナログ・デジタル変換器によって生成されるデジタル・サンプルが

50

Mのメモリ・モジュール(M 2)に記憶される、本発明によるアナログ・デジタル変換システムの第3の実施態様300のブロック図である。この構成によれば、メモリ・モジュールのそれぞれが、ADCによって生成されるデジタル・サンプルのサブセットを記憶することが可能になり、従って、ADCの出力データ転送速度の1/Mで動作することが可能になる。これによって、より低速のメモリ素子をメモリ・モジュールとして用いることが可能になる。

#### 【0055】

アナログ・デジタル変換システム300において、入力データ・バス304は、ADCサブバス370と、Mの入力サブバス304-1~304-Mから構成され、メモリ206は、Mのメモリ・モジュール206-1~206-Mから構成され、出力データ・バス208は、Mの出力サブバス208-1~208-Mと、出力ポート・サブバス256から構成されている。図面を単純化するため、図3には、入力サブバス304-1、304-2、304-3、及び、304-M、メモリ・モジュール206-1、206-2、206-3、及び、208-Mだけしか示されていない。10

#### 【0056】

アナログ・デジタル変換システム300は、さらに、アナログ・デジタル変換器102、出力ポート210、及び、多相クロック発生器350から構成されている。アナログ・デジタル変換器、入力データ・バス、メモリ、出力データ・バス、多相クロック発生器、及び、出力ポートの一部によって、チップ312の少なくとも一部が構成される。20

図1及び2に関連して上述のアナログ・デジタル変換システムの構成要素に対応するアナログ・デジタル変換システム300の構成要素は、同じ参照番号を用いて示されており、ここでも詳細な説明は控えることにする。

#### 【0057】

入力データ・バス304の場合、ADCサブバス370は、アナログ・デジタル変換器102のデジタル出力122から延び、Mの入力サブバス304-1~304-Mへと接続(またはファンアウト(fan out))している。入力サブバス304-1~304-Mは、それぞれ、ADCサブバス370からメモリ・モジュール206-1~206-Mのデータ入力230まで延びている。30

#### 【0058】

多相クロック発生器350は、クロック入力352と、Mのクロック出力354-1~354-Mを備えているが、図面を単純化するため、クロック出力は、354-1、354-2、353-3、及び、354-Mだけしか示されていない。マスタ・クロック信号MCが、クロック入力352及びADC102のクロック入力124に接続されている。クロック出力354-1~354-Mは、それぞれ、メモリ・モジュール206-1~206-Mの書き込みクロック入力234に接続されている。多相クロック発生器は、互いに2/Mラジアンだけ異なるMの位相を有する多相クロック信号を発生する。各位相の周波数は、ADCのサンプリング周波数の1/Mである。多相クロック発生器は、クロック出力354-1~354-Mから多相クロック信号を出力する。40

#### 【0059】

図2に関連して上述したのと同様に、メモリ・モジュール206-1~206-Mは、さらに、メモリ206からデジタル・サンプルが読み取られる動作モードに従って、単相クロック信号または多相クロック信号とすることが可能な読み取りクロック信号RCを受信する。

#### 【0060】

ADCサブバス370及び入力サブバス304-1~304-Mは、それぞれ、mの導体(個別には示されていない)から構成されている。ADCサブバスは、ADC102のデジタル出力122から延びてあり、それぞれ、メモリ・モジュール206-1~206-Mのデータ入力230まで延びる入力サブバス304-1~304-Mへと接続(またはファンアウト)している。ADCサブバス及び入力サブバスを構成する導体は、長さ50

が短く、ADC102のデジタル出力122からメモリ・モジュール206-1~206-Mのデータ入力230まで、チップ312の表面を横切って直接延びている。従って、ADCサブバス及び入力サブバスは、ADCモジュールによってサポートされる最高サンプリング・レートで動作することが可能である。

#### 【0061】

当該技術分野では、メモリ・モジュール206-1~206-Mとして用いるのに適した多種多様なタイプのメモリ素子が周知のところである。代替物及び代替物の中から選択する場合の考慮事項は、図1のメモリ106に関連して上述のものとほぼ同じである。ADC102のある特定のサンプリング・レートの場合は、メモリ206には、メモリ106より低速のメモリ素子を組み込むことが可能である。

10

#### 【0062】

次に、アナログ・デジタル変換システム300の動作について述べることにする。アナログ・デジタル変換器102は、アナログ入力120を介してアナログ入力信号を受信する。アナログ・デジタル変換器は、クロック入力124を介して受信したマスタ・クロック信号MCに応答して作動し、マスタ・クロック信号の周波数によって決まるサンプリング・レートで、アナログ入力信号のデジタル・サンプルを生成する。アナログ・デジタル変換器は、デジタル出力122からデジタル・サンプルを出力する。

#### 【0063】

ADCサブバス370及び入力サブバス304-1~304-Mは、ADC102によって生成されたデジタルサンプルを、それぞれ、メモリ・モジュール206-1~206-Mのデータ入力230に伝送する。メモリ・モジュール206-1~206-Mは、さらに、その書き込みクロック入力234を介して、多相クロック発生器350によって発生した多相クロック信号を受信する。隣接する多相クロックの位相は、ADC102のサンプリング周期に等しい時間だけ、時間的に差がある。メモリ・モジュールは、さらに、その読み取りクロック入力236を介して、読み取りクロック信号RCを受信する。書き込み許可信号WEが有効（イネーブル）になると、メモリ・モジュール206-1~206-Mの書き込みクロック入力234に供給される多相クロック信号によって、ADCが連続して生成するMのデジタル・サンプルのそれぞれが、メモリ・モジュールのそれぞれに記憶されることになる。例えば、デジタル・サンプルの1番目、M+1番目、2M+1番目、...は、メモリ・モジュール206-1に記憶され、一方、デジタルサンプルの2番目、M+2番目、2M+2番目、...は、メモリ・モジュール206-2に記憶される。例えば、各メモリは、書き込みクロック入力234で受信したクロック信号と符合して（例えば同期して）順次記憶されるデジタル・サンプルのいくつかを連続したアドレスを有する記憶場所（メモリ位置）に記憶することができる。

20

30

30

#### 【0064】

入力サブバス304-1~304-Mを介して受信したデジタル・サンプルのメモリ・モジュール206-1~206-Mへのそれぞれの記憶は、書き込み許可信号WEがアサートされている間継続される。上述のように、ある動作モードの場合、デジタル・サンプルの記憶は、メモリのサンプル容量より少ない、所望の数のサンプルがメモリ206に記憶されるか、または、メモリが満杯になると停止し、もう1つの動作モードでは、各メモリ・モジュールが、Jの最新の受信デジタル・サンプルを記憶する。ここで、Jは、メモリ・モジュールのサンプル容量である。

40

#### 【0065】

デジタル・サンプルがメモリ・モジュール206-1~206-Mに記憶され、書き込み許可信号WEがディアサートされると、デジタル・サンプルは、図2に関連して上述したのと同様のやり方で、メモリ・モジュールから読み取られる。デジタル・サンプルがメモリ・モジュールから読み取られ、出力ポートに送られる速度は、読み取りクロックRCの周波数によって決まる。この速度は、ADC102のサンプリング・レート、及び、メモリ206が入力データ・バス204を介してデジタル・サンプルを受信した速度より低い。メモリ206からサンプルが読み取られる最高データ転送速度は、上述の要

50

因によって決まる。

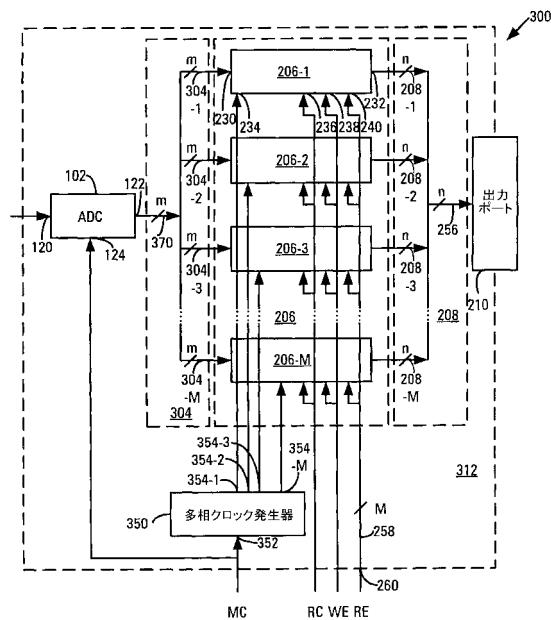

【0066】

図4は、アナログ・デジタル変換器202を構成するアナログ・デジタル変換器モジュールが、それぞれ、 $m$ ビットのデジタル・サンプルを生成し、メモリ406を構成するメモリ・モジュールが、 $2m$ ビット・ワードとして対をなすデジタル・サンプルを記憶する、本発明によるアナログ・デジタル変換システムの第4の実施態様400のブロック図である。メモリ・モジュールは、アナログ・デジタル変換器モジュールより数が少ない。

【0067】

アナログ・デジタル変換システム400において、アナログ・デジタル変換器202は、Mのアナログ・デジタル変換器モジュール202-1～202-Mから構成され、入力データ・バス404は、MのADCサブバス470-1～470-Mと、M/2の入力サブバス404-1～404-M/2から構成され、メモリ406は、M/2のメモリ・モジュール406-1～406-M/2から構成され、出力データ・バス408は、M/2の出力サブバス408-1～408-M/2と、出力ポート・サブバス456から構成されている。図面を単純化するため、図4には、アナログ・デジタル変換器モジュール202-1、202-2、202-3、202-4、202-(M-1)及び、202-M、ADCサブバス470-1、470-2、470-3、470-4、470-(M-1)、及び、470-M、メモリ・モジュール406-1、406-2、及び、406-M/2、及び、出力サブバス408-1、408-2、及び、408-M/2だけしか示されていない。10 20

【0068】

アナログ・デジタル変換システム400は、さらに、出力ポート410と多相クロック発生器250から構成されている。アナログ・デジタル変換器、入力データ・バス、メモリ、出力データ・バス、多相クロック発生器、及び、出力ポートの一部によって、チップ412の少なくとも一部が構成されている。図1及び2に関連して上述のアナログ・デジタル変換システムの構成要素に対応するアナログ・デジタル変換システム400の構成要素は、同じ参照番号を用いて示されており、やはり、詳細な説明は控えることにする。30

【0069】

メモリ・モジュール406-1は、データ入力430、データ出力432、書き込みクロック入力434、読み取りクロック入力436、書き込み許可入力438、及び、読み取り許可入力440を備えている。メモリ・モジュール406-2～406-M/2は、同様に構成されており、個別の説明は控えることにする。メモリ・モジュール406-2～406-M/2のデータ入力、データ出力、書き込みクロック入力、読み取りクロック入力、書き込み許可入力、及び、読み取り許可入力を示す参照番号は、図面を単純化するため、図4から省略されている。40

【0070】

図面を単純化するため、クロック出力254-1、254-2、254-3、254-4、254-(M-1)、及び、254-Mだけしか示されていない、多相クロック発生器250のクロック出力254-1～254-Mは、それぞれ、ADCモジュール202-1～202-Mのクロック入力224に接続されている。クロック出力254-1～254-Mのうち奇数番号のものは、さらに、それぞれ、メモリ・モジュール406-1～406-M/2の書き込みクロック入力434に接続されている。代替的には、メモリ・モジュールのそれぞれに接続されたADCの1つによって、メモリ・モジュールに書き込みクロック信号を供給することが可能である。40

【0071】

図2に関連して上述したのと同様のやり方で、メモリ・モジュール406-1～406-M/2は、さらに、読み取りクロック信号RCを受信する。読み取りクロック信号は、上述のように、デジタル・サンプルがメモリ406から読み取られる動作モードに従つ50

て、单相クロック信号または多相クロック信号になる。

#### 【0072】

A D C サブバス 4 7 0 - 1 ~ 4 7 0 - M は、それぞれ、m の導体（個別には示されていない）から構成されており、それぞれ、A D C モジュール 2 0 2 - 1 ~ 2 0 2 - M のデジタル出力 2 2 2 から延びている。A D C サブバス 4 7 0 - 1 ~ 4 7 0 - M の対をなす隣接サブバスが、それぞれ、結合して、それぞれ、メモリ・モジュール 4 0 6 - 1 ~ 4 0 6 - M / 2 のデータ入力 4 3 0 まで延びる入力サブバス 4 0 4 - 1 ~ 4 0 4 - M / 2 になる。例えば、A D C サブバスのうち対をなす隣接サブバス 4 7 0 - 1 及び 4 7 0 - 2 、 4 7 0 - 3 及び 4 7 0 - 4 、 4 7 0 - (M - 1) 及び 4 7 0 - M が結合して、それぞれ、入力・サブバス 4 0 4 - 1 、 4 0 4 - 2 、及び、 4 0 4 - M / 2 になる。この図示の例の場合、入力サブバスは、それぞれ、幅が A D C サブバスの 2 倍である、すなわち、入力サブバスは、2 m の導体から構成されている。一般に、入力サブバスの幅は、A D C サブバスの x 倍になる。ここで、x は、結合して、各入力サブバスになる A D C サブバスの数である。

#### 【0073】

A D C サブバス 4 7 0 - 1 ~ 4 7 0 - M 及び入力サブバス 4 0 4 - 1 ~ 4 0 4 - M / 2 を構成する導体は、長さが短く、それぞれ、A D C モジュール 2 0 2 - 1 ~ 2 0 2 - M のデジタル出力 2 2 2 から、それぞれ、メモリ・モジュール 4 0 6 - 1 ~ 4 0 6 - M / 2 のデータ入力 4 3 0 まで、チップ 4 1 2 の表面を横切って直接延びている。従って、A D C サブバス及び入力サブバスは、A D C モジュールによってサポートされる最高サンプリング・レートで動作可能である。

#### 【0074】

当該技術分野では、メモリ・モジュール 4 0 6 - 1 ~ 4 0 6 - M / 2 として用いるのに適した多種多様なタイプのメモリ素子が周知のところである。代替物及び代替物から選択する場合の考慮事項については、メモリ 2 0 6 に関連して上述したのとほぼ同じである。

#### 【0075】

メモリ・モジュール 4 0 6 - 1 ~ 4 0 6 - M / 2 の読み取り許可入力 4 3 8 を読み取り許可入力 4 6 0 に接続する読み取り許可バス 4 5 8 は、M / 2 ビット幅のバスであり、これを介して、メモリ・モジュールのそれぞれが、個別の読み取り許可信号を受信する。この実施態様の場合、メモリ・モジュール 4 0 6 - 1 ~ 4 0 6 - M / 2 のデータ出力 4 3 2 は、上述のようにトライステート構成を有する。

#### 【0076】

出力データ・バス 4 0 8 は、出力サブバス 4 0 8 - 1 ~ 4 0 8 - M / 2 と、出力ポート・サブバス 4 5 6 から構成されている。出力サブバス及び出力ポート・サブバスは、それぞれ、2 m の導体（個別には示されていない）から構成されている。出力サブバス 4 0 8 - 1 ~ 4 0 8 - M / 2 は、それぞれ、メモリ・モジュール 4 0 6 - 1 ~ 4 0 6 - M / 2 のデータ出力 4 3 2 から延びており、出力ポート・サブバス 4 5 6 に接続（またはファンイン）している。出力データ・バス 4 0 8 は、出力データ・バス 2 0 8 に関連して上述したものと同様の代替構成を有することが可能である。

#### 【0077】

メモリ・モジュール 4 0 6 - 1 ~ 4 0 6 - M / 2 のデータ出力 4 3 2 、出力データ・バス 4 0 8 を構成する出力サブバス 4 0 8 - 1 ~ 4 0 8 - M / 2 及び出力ポート・サブバス 4 5 6 、及び、出力ポート 4 1 0 の 1 つ以上が、上述のものと同様に、A D C 2 0 2 のサンプリング・レートより低い最高速度で動作するように構成されている。デジタル・サンプルは、メモリ 4 0 6 から読み取られ、許容し得るデータ信号の完全性を有して出力ポートの一部を形成する出力ピンに送られることが可能な最高速度以下の速度で、出力ポート 4 1 0 に送られる。デジタル・サンプルがメモリから読み取られ、出力ポートに送られる速度は、やはり上述のように、下流の回路が課す速度制限によってさらに低下する可能性がある。

#### 【0078】

10

20

30

40

50

次に、アナログ・ディジタル変換システム400の動作について述べることにする。アナログ・ディジタル変換器モジュール202-1～202-Mが、それぞれ、そのアナログ入力220を介してアナログ入力信号を受信する。各アナログ・ディジタル変換器モジュールは、クロック入力224を介して受信したある位相の多相クロック信号に応答して作動し、ADC202全体のサンプリング・レートの1/Mのサンプリング・レートで、アナログ入力信号のデジタル・サンプルを生成する。アナログ・ディジタル変換モジュールに供給される多相クロック信号の位相は2/Mラジアンだけ異なっている。従って、隣接する多相クロック信号の位相を受信するアナログ・ディジタル変換器モジュールのいくつかによって生成されたデジタル・サンプルは、位相差に対応する時間的に差がある。各アナログ・ディジタル変換器モジュールは、そのデジタル出力222からデジタル・サンプルを出力する。

10

## 【0079】

ADCサブバス470-1～470-Mは、それぞれ、ADCモジュール202-1～202-Mによって生成されるmビットのデジタル・サンプルを受信する。隣接対をなすADCサブバスは、結合して、それぞれ、2mビットのサンプル対をメモリ・モジュール406-1～406-M/2の2mビット・データ入力430に伝送する入力サブバス404-1～404-M/2を形成している。メモリ・モジュール406-1～406-M/2のそれぞれは、さらに、その書き込みクロック入力434を介して多相クロック発生器250から位相の異なる多相クロック信号を受信する。メモリ・モジュールは、さらに、その読み取りクロック入力436を介して読み取りクロック信号RCを受信する。

20

## 【0080】

書き込み許可信号WEが有効（イネーブル）になると、メモリ・モジュール406-1～406-M/2は、書き込みクロック信号WCのそれぞれの位相に応答して作動し、データ入力430に生じるデジタル・サンプル対をメモリ・モジュールに書き込む。例えば、各メモリ・モジュールは、連続したアドレスを有する記憶場所（メモリ位置）に、そのデータ入力で連続して受信したデジタル・サンプル対を記憶することが可能である。

## 【0081】

入力サブバス404-1～404-M/2を介して受信したデジタル・サンプル対の、メモリ・モジュール406-1～406-M/2へのそれぞれの記憶は、書き込み許可信号WEがアサートされている間継続される。上述のものと同様に、動作モードの1つでは、デジタル・サンプル対の記憶は、メモリのサンプル対容量より少ない、所望の数のサンプル対がメモリ406に記憶されるか、または、メモリが満杯になると、停止され、もう1つの動作モードでは、各メモリ・モジュールは、Kの最新の受信デジタル・サンプル対を連続して記憶する。ここで、Kはメモリ・モジュールのサンプル対容量である。

30

## 【0082】

デジタル・サンプル対がメモリ406に記憶され、書き込み許可信号WEがディアサートされると、メモリからデジタル・サンプル対を読み取ることが可能になる。動作モードの1つでは、デジタル・サンプル対は、單一デジタル・サンプルの読み取りに関して上述のものと同様に、それらが記憶された時間順に、メモリから読み取られる。もう1つの動作モードでは、單一デジタル・サンプルの読み取りに関して上述のものと同様に、メモリ・モジュールの1つから複数のデジタル・サンプル対が読み取られた後、別のメモリ・モジュールからデジタル・サンプル対が読み取られる。読み取られた複数のデジタル・サンプル対は、メモリ・モジュールに記憶されているデジタル・サンプル対の部分集合から全てにまで及ぶ可能性がある。後者の場合、必要があれば、アナログ・ディジタル変換システム400の下流の回路要素（不図示）によって、デジタル・サンプルの時間順を復元することが可能である。

40

## 【0083】

動作モードに関係なく、メモリ・モジュール406-1～406-M/2は、読み取り許可信号RE及び読み取りクロック信号RCに応答して作動し、そのデータ出力432からそれに記憶されているデジタル・サンプル対を出力する。出力サブバス408-1～

50

408-M/2 及び出力ポート・サブバス 456 によって、それぞれ、メモリ・モジュール 406-1 ~ 406-M/2 のデータ出力 432 から出力ポート 410 にデジタル・サンプルが送られる。デジタル・サンプル対がメモリ・モジュールから出力されるデータ転送速度は、読み取りクロック RC の周波数によって決まる。デジタル・サンプル対が出力ポート 410 に送られる速度は、デジタル・サンプル対が入力データ・バス 404 を介してメモリ 406 に伝送された速度より低い。メモリからデジタル・サンプルが読み取られ、出力ポートへ送られる最高データ転送速度は、上述のように、メモリ・モジュールのデータ出力の構成、出力サブバス及び出力ポート・サブバスの構成、及び、出力ポートの構成といった要因によって決まる。メモリ 406 からデジタル・サンプルが読み取られるデータ転送速度は、やはり上述のように、下流の回路要素のデータ転送速度要件に応じて、さらに、低下させることが可能である。

10

#### 【0084】

上述の例の場合、それぞれ、対をなす ADC モジュール 202-1 ~ 202-M から延びる ADC サブバス 470-1 ~ 470-M が結合して、それぞれ、メモリ・モジュール 406-1 ~ 406-M/2 のそれぞれのデータ入力まで延びる、倍幅の各入力サブバス 404-1 ~ 404-M/2 をなしている。より一般的には、ADC 202 は、M = P × Q の ADC モジュール 202-1 ~ 202-M から構成することが可能であり、Q の ADC モジュールの組から延びる ADC サブバスが結合して、メモリ・モジュールの 1 つのデータ入力まで延びる入力サブバスのそれをなすことが可能である。この場合、P の入力サブバスと P のメモリ・モジュールが設けられており、入力サブバスの幅は、ADC サブバスの幅の Q 倍になる。

20

#### 【0085】

図 5 は、本発明によるアナログ・デジタル変換システムの第 5 の実施態様 500 の一例のブロック図である。第 5 の実施態様は、システムを具現化するチップが取り付けられるパッケージの 16 のピンが出力ポートに割り当てられる、20G Sa/s のアナログ・デジタル変換システムの実際例である。16 のピンが利用可能であるため、出力ポートは、2 つのデジタル・サンプルを並列に同時に出力することが可能である。後述する、それぞれのモジュール及びサブバスの数、それぞれのサブバスの幅、出力ピンの数、及び、周波数は、単なる例示のためのものであって、第 5 の実施態様は、例示のものとは異なる値になるように構成することが可能である。

30

#### 【0086】

アナログ・デジタル変換システム 500 の場合、アナログ・デジタル変換器 502 は、80 (M = 80) のアナログ・デジタル変換器モジュール 502-1 . . . 502-80 から構成され、入力データ・バス 504 は、80 の ADC サブバス 570-1 . . . 570-80 と、8つ (M/10) の入力サブバス 504-1 . . . 504-8 から構成され、メモリ 506 は、8つ (M/10) のメモリ・モジュール 506-1 . . . 506-8 から構成され、出力データ・バス 508 は、8 つの出力サブバス 508-1 . . . 508-8、出力バッファ 580、及び、2 つの出力ポート・サブバス 556-1 及び 556-2 から構成されている。図面を単純化するため、図 5 には、アナログ・デジタル変換器モジュール 502-1、502-2、502-10、502-11、502-12、502-20、502-71、502-72、及び、502-80、ADC サブバス 570-1、570-2、507-10、570-11、570-12、570-20、570-71、570-72、及び、570-80、入力サブバス 504-1、504-2、及び、504-8、メモリ・モジュール 506-1、506-2、及び、506-8、及び、出力サブバス 508-1、508-2、及び、508-8だけしか示されていない。

40

#### 【0087】

アナログ・デジタル変換システム 500 は、さらに、出力ポート 510、多相クロック発生器 550、及び、クロック分割器 590 から構成されている。アナログ・デジタル変換器 502、入力データ・バス 504、メモリ 506、出力データ・バス 508、多

50

相クロック発生器、クロック分割器、及び、出力ポートの一部によって、チップ 512 の少なくとも一部が構成されている。図1、2、及び、4に関連して上述のアナログ・デジタル変換システムの構成要素に対応するアナログ・デジタル変換システム 500 の構成要素は、同じ参照番号を用いて示されており、ここでも、詳細な説明は控えることにする。

#### 【0088】

アナログ・デジタル変換器(ADC)モジュール 502-1 は、アナログ入力 520 、デジタル出力 522 、及び、クロック入力 524 を備えている。アナログ・デジタル変換器モジュール 502-2 ~ 502-80 は、同様の構成が施されており、個別の説明は控えることとする。図5に示す残りのアナログ・デジタル変換器モジュールのアナログ入力、デジタル出力、及び、クロック入力を示す参照番号は、図面の単純化のため省略されている。多相クロック信号発生器 550 から ADC モジュールのクロック入力 524 への接続も、図面の単純化のため省略されている。しかし、図示の ADC モジュールに接続された多相クロック信号の位相は示されている。ADC モジュール 502-1 ~ 502-80 のアナログ入力 520 は、アナログ入力 120 と並列に接続されている。

#### 【0089】

メモリ・モジュール 506-1 は、データ入力 530 、データ出力 532 、書き込みクロック入力 534 、読み取りクロック入力 536 、書き込み許可入力 538 、及び、読み取り許可入力 540 を備えている。メモリ・モジュール 506-2 ~ 506-8 は、同様の構成が施されており、個別の説明は控えることとする。メモリ・モジュール 506-2 及び 506-8 のデータ入力、データ出力、書き込みクロック入力、読み取りクロック入力、書き込み許可入力、及び、読み取り許可入力を示す参照番号は、図面を単純化するため、図5から省略されている。ADC モジュールからメモリ・モジュール 506-1 、 506-2 、及び、 506-8 のクロック入力 534 への書き込みクロック信号の接続も、図面の単純化のため、省略されている。

#### 【0090】

多相クロック発生器 550 は、クロック入力 552 と、 80 の多相クロック出力 534 を備えている。クロック入力 552 には、 250MHz のマスター・クロック信号 MC が接続される。多相クロック出力は、 ADC モジュール 502-1 ~ 502-80 のクロック入力 524 に接続されている。多相クロック発生器は、互いに 2 / 80 ラジアンだけ異なる 80 の位相 1 ~ 80 を有する多相クロック信号を発生する。ADC のサンプリング周波数は、多相クロック信号の位相の周波数の 80 倍、すなわち、  $250 \times 80 = 20$  GHz である。多相クロック発生器は、クロック出力 554 から多相クロック信号を出力する。

#### 【0091】

メモリ・モジュール 506-1 、 506-2 、 . . . 、 506-8 は、それぞれ、その書き込みクロック入力 534 において、 ADC モジュール 502-1 、 502-11 、 . . . 、 502-71 から 250MHz の書き込みクロック信号 WC を受信し、さらに、その読み取りクロック入力 536 において、クロック分割器 582 の出力から読み取りクロック信号 RC を受信する。読み取りクロック信号 RC は、さらに後述するように、デジタル・サンプルがメモリ・モジュールから並列に読み取られる際は、単相クロック信号である。

#### 【0092】

ADC サブバス 570-1 ~ 570-80 は、それぞれ、 8 つの導体（個別には示されていない）から構成され、それぞれ、 ADC モジュール 502-1 ~ 502-80 のデジタル出力 522 から延びている。各組が ADC サブバス 570-1 ~ 570-80 の 10 の隣接サブバスからなる、複数組の ADC サブバスが、それぞれ、結合して、それぞれ、メモリ・モジュール 506-1 ~ 506-8 のデータ入力 530 まで延びる、入力サブバス 504-1 ~ 504-8 のそれぞれを形成している。例えば、 ADC サブバスの組をなす 10 の隣接サブバス 570-1 ~ 570-10 、 570-11 ~ 570-20 、及び

10

20

30

40

50

、 570-71 ~ 570-80 が結合して、それぞれ、入力サブバス 504-1、504-2、及び、504-8 を形成している。図示の例の場合、入力サブバスのバス幅は、それぞれ、ADC サブバスの 10 倍である、すなわち、入力サブバスは、それぞれ、80 の導体から構成されている。

#### 【0093】

ADC サブバス 570-1 ~ 570-80、及び、入力サブバス 504-1 ~ 504-8 を構成する導体は、長さが短く、それぞれ、ADC モジュール 502-1 ~ 502-80 のデジタル出力 522 から、それぞれ、メモリ・モジュール 506-1 ~ 506-80 のデータ入力 530 まで、チップ 512 の表面を横切って直接延びている。従って、ADC サブバス及び入力サブバスは、ADC モジュールによってサポートされる最高のサンプリング・レートで動作することが可能である。10

#### 【0094】

当該技術分野では、メモリ・モジュール 506-1 ~ 506-8 として用いるのに適した多種多様なタイプのメモリ素子が周知のところである。代替物及び代替物を選択する場合の考慮事項については、メモリ 106 に関連して上述のところとほぼ同じである。

#### 【0095】

メモリ・モジュール 506-1 ~ 506-8 の読み取り許可入力 538 を読み取り許可入力 560 に接続する読み取り許可バス 558 は、1 ピット幅のバスであり、これを介して、メモリ・モジュールが共通読み取り許可信号を受信する。この実施態様の場合、メモリ・モジュール 506-1 ~ 506-8 のデータ出力 532 は、上述のように、2 状態構成を有している。20

#### 【0096】

出力データ・バス 508 は、出力サブバス 508-1 ~ 508-8、出力バッファ 580、及び、2 つの出力ポート・サブバス 556-1 及び 556-2 から構成されている。出力サブバスは、それぞれ、80 の導体（個別には示されていない）から構成されている。出力サブバス 508-1 ~ 508-8 は、それぞれ、メモリ・モジュール 506-1 ~ 506-8 のデータ出力 532 から、出力バッファのデータ入力 582 まで延びている。出力ポート・サブバス 556-1 及び 556-2 は、データ・バッファのデータ出力 584 から出力ポート 510 まで延びている。

#### 【0097】

出力バッファ 580 は、さらに、そのクロック入力 586 においてマスタ・クロック信号 MC を受信する。マスタ・クロック信号は、さらに、クロック分割器 590 のクロック入力 592 に接続される。クロック分割器のクロック出力 594 は、メモリ・モジュール 506-1 ~ 506-8 の読み取りクロック入力 536 に並列に接続される。出力バッファは、そのサンプル入力で並列に受信する組をなす 80 のデジタル・サンプルを、デジタルサンプル対に再構成するように構成されている。出力バッファは、組をなす 80 のデジタル・サンプルを受信する速度の 40 倍の速度で、デジタル・サンプル対をそのサンプル出力から出力する。出力バッファは、説明したばかりの単純な再構成及び速度変換よりも複雑なサンプル処理を実施するように構成することも可能である。30

#### 【0098】

クロック分割器 590 は、マスタ・クロック信号 MC を 40 で分割して、読み取りクロック RC を生成するよう構成されている。マスタ・クロック信号 MC は、周波数が 250 MHz であり、従って、読み取りクロックの周波数は、6.25 MHz である。40

#### 【0099】

メモリ・モジュール 506-1 ~ 506-8 のデータ出力 532、出力データ・バス 508 を構成する出力サブバス 508-1 ~ 508-8 と、出力ポート・サブバス 556-1 及び 556-2、及び、出力ポート 510 の 1 つ以上が、上述のものと同様に、ADC 502 のサンプリング・レートより低い最大速度で動作するように構成されている。デジタル・サンプルは、メモリ 506 から読み取られ、許容し得るデータ信号の完全性を保って、出力ポートの一部を形成する出力ピンに送られることが可能な最高速度以下の速度50

で、出力ポート 510 に送られる。デジタル・サンプルがメモリから読み取られ、出力ポートに送られる速度は、やはり上述のように、下流の回路が課す速度制限によってさらに低下する可能性がある。図示の例の場合、8 ビットのデジタル・サンプルが、250 M S a / s の速度でメモリ 506 から読み取られる。データ出力 532 及び出力サブバス 508 - 1 ~ 508 - 8 は、共同して、250 M S a / s の速度でデジタル・サンプルを出力バッファ 580 に送り、出力ポート・サブバス 556 - 1 及び 556 - 2 は、共同して、250 M S a / s の速度でデジタル・サンプルを出力ポートに送る。デジタル・サンプルがメモリ 506 から読み取られ、出力ポートに送られる速度は、A D C 502 の 20 G S a / s のサンプリング・レートよりかなり低い(1 / 80)。

## 【0100】

10

次に、アナログ・デジタル変換システム 500 の動作について述べることにする。アナログ・デジタル変換器モジュール 502 - 1 ~ 502 - 80 は、それぞれ、そのアナログ入力 520 を介してアナログ入力信号を受信する。各アナログ・デジタル変換器モジュールは、クロック入力 524 を介して受信した多相クロック信号の位相に応答して作動し、A D C 502 の 20 G S a / s のサンプリング・レートの 1 / 80 のサンプリング・レートで、アナログ入力信号のデジタル・サンプルを生成する。アナログ・デジタル変換器モジュールに供給される多相クロック信号の位相は、2 / 80 ラジアンだけ異なる。隣接する多相クロック信号の位相を受信するアナログ・デジタル変換器モジュールによって生成されるデジタル・サンプルは、時間的に 50 ピコ秒の差がある。各アナログ・デジタル変換器モジュールは、そのデジタル出力 522 からデジタル・サンプルを出力する。

## 【0101】

20

A D C サブバス 570 - 1 ~ 570 - 80 は、それぞれ、A D C モジュール 502 - 1 ~ 502 - 80 によって生成される 8 ビットのデジタル・サンプルを受信する。各組が 10 の隣接する A D C サブバスからなる複数組のサブバスが結合して、入力サブバス 504 - 1 ~ 504 - 8 を形成している。各入力サブバスは、メモリ・モジュール 506 - 1 ~ 506 - 8 のそれぞれの 80 ビット・データ入力 530 に、組をなす 10 のデジタル・サンプル(80 ビット)を伝送する。メモリ・モジュール 506 - 1 ~ 506 - 8 のそれぞれの書き込みクロック入力 534 は、それに接続された A D C モジュールの 1 つから書き込みクロック信号 W C を受信する。メモリ・モジュールは、さらに、その読み取りクロック入力 536 を介して、読み取りクロック信号 R C を受信する。

30

## 【0102】

書き込み許可信号 W E が有効(イネーブル)になると、メモリ・モジュール 506 - 1 ~ 506 - 8 のそれぞれは、そのそれぞれの書き込みクロック信号 W C に応答して作動し、そのデータ入力 530 に生じる組をなす 10 のデジタル・サンプルをメモリ・モジュールに書き込む。例えば、各メモリ・モジュールは、そのデータ入力において連続して受信した組をなす 10 のデジタル・サンプルを、連続したアドレスを有する記憶場所(メモリ位置)に記憶することが可能である。

## 【0103】

40

メモリ・モジュール 506 - 1 ~ 506 - 8 への入力サブバス 504 - 1 ~ 504 - 8 を介して受信した組をなす 10 のデジタル・サンプルの記憶は、それぞれ、書き込み許可信号 W E がアサートされている間継続される。上述のように、動作モードの 1 つでは、組をなすデジタル・サンプルの記憶は、メモリのサンプル組容量(記憶可能なサンプルの組の容量)より少ない、所望の組数のサンプルがメモリ 506 に記憶されるか、または、メモリが満杯になると、停止される。もう 1 つの実施態様では、各メモリ・モジュールは、各組が 10 のデジタル・サンプルからなる、L 組の最新の受信デジタル・サンプルを連続して記憶する。ここで、L はメモリ・モジュールのサンプル組容量である。

## 【0104】

組をなすデジタル・サンプルがメモリ 506 に記憶され、書き込み許可信号 W E がディアサートされると、メモリから組をなす 10 のデジタル・サンプルを読み取ることが

50

可能になる。組をなす 10 のデジタル・サンプルは、それらが記憶された時間順にメモリ・モジュール 506-1 ~ 506-8 のそれぞれから読み取られる。デジタル・サンプルは、メモリ・モジュールの全てから同時に読み取られる。

#### 【0105】

メモリ・モジュール 506-1 ~ 506-8 は、読み取り許可信号 RE 及び読み取りクロック信号に応答して作動し、そのデータ出力 532 から、それに記憶されている組をなす 10 のデジタル・サンプルを出力する。出力サブバス 508-1 ~ 508-8 は、組をなす 10 のデジタル・サンプルを出力バッファ 580 に並列に送る。6.25 MHz の読み取りクロック信号の各周期毎に、サブバスは、全体として、800 のデジタル・サンプルを出力バッファのデータ入力 582 に送る。

10

#### 【0106】

出力バッファ 580 は、250 MHz のマスター・クロック信号 MC に応答して作動し、そのデータ入力 582 で並列に受信したデジタル・サンプルを、時間順に、並列対をなすデジタル・サンプルに再構成する。出力バッファは、そのデータ出力 584 から各対をなすデジタル・サンプルを出力する。デジタル・サンプル対が出力される速度は、125 MHz である。従って、個々のデジタル・サンプルは、250 MHz の速度で出力ポートに送られる。

#### 【0107】

出力ポート・サブバス 556-1 及び 556-2 は、出力バッファ 580 のデータ出力 586 から出力ポート 510 にデジタル・サンプル対を送る。デジタル・サンプルが出力ポートに送られるデータ転送速度は、ADC 502 のサンプリング・レートよりもかなり低い。デジタル・サンプルの各ストリームが出力ポートに送られる速度は、125 MHz、すなわち、出力ポートの一部を構成するパッケージ・ピンから、信号の完全性が高いデジタル信号を容易に伝送することが可能な速度である。この速度は、さまざまなタイプの下流回路要素のデータ転送要件にも適合する。

20

#### 【0108】

上述のアナログ・デジタル変換システム 500 の場合、メモリ・モジュール 506-1 ~ 506-8 のそれぞれが、125 キロバイトのスタティック・ランダム・アクセス・メモリ (SRAM) から構成される例では、最大持続時間が約 50 マイクロ秒の事象が記憶されることになる。これは、多くの用途において十分であるが、メモリ・モジュールとして用いられるメモリ素子のサイズ及び／または数を増大させるという犠牲を払うことなく、より最大持続時間の長い事象を記憶することが望ましい場合もある。こうした持続時間の長い事象は、上述のアナログ・デジタル変換システムの最高サンプリング・レートによって得られる極めて高い時間的分解能を必要としない可能性がある。アナログ・デジタル変換システムは、一般に、特定のサンプリング・レートで動作するように設計されており、サンプリング・レートを可変にするのは、些細なことではない。

30

#### 【0109】

図 6 は、より持続時間の長い事象を捕捉するオプションを可能にする、本発明によるアナログ・デジタル変換システムの第 6 の実施態様 600 に関するブロック図である。図示のアナログ・デジタル変換システム 600 の例は、図 1 に示すアナログ・デジタル変換システム 100 に基づくものである。図 2 ~ 5 に示すアナログ・デジタル変換システムの実施態様にも同様の修正が可能であることは明らかであろう。図 1 に関連して上述のアナログ・デジタル変換システムの構成要素に対応するアナログ・デジタル変換システム 600 の構成要素は、同じ参照番号を用いて示されており、ここでの説明は控えることにする。

40

#### 【0110】

アナログ・デジタル変換システム 600 の場合、入力データ・バス 604 は、ADC サブバス 670、サンプル・プロセッサ 612、及び、入力サブバス 604-1 から構成されている。サンプル・プロセッサは、サンプル入力 614、サンプル出力 616、クロック入力 618、クロック出力 626、及び、制御入力 628 を備えている。ADC 10

50

2、サンプル・プロセッサ612を含む入力データ・バス604、メモリ106、出力データ・バス108、及び、出力ポート110の一部によって、チップ612の少なくとも一部が構成されている。

#### 【0111】

ADCサブバス670は、ADC102のデジタル出力122からサンプル・プロセッサ612のサンプル入力614まで延びており、mの導体から構成されている。入力サブバス604-1は、サンプル・プロセッサのサンプル出力616からメモリ106のデータ入力130まで延びてあり、pの導体から構成されている。一般に、p = mである。しかし、サンプル・プロセッサは、さらに、各組がqのmビット・デジタル・サンプルからなる複数組のデジタル・サンプルを組み合わせて、メモリに出力される、pビットデジタル・サンプルのそれぞれの組にするよう動作可能である。この場合、p = q mである。10

#### 【0112】

マスター・クロック信号MCは、さらに、サンプル・プロセッサ612のクロック入力618に接続されている。クロック出力626は、メモリ106の書き込みクロック入力134に接続されている。制御入力628は、制御信号CTRLを受信するように接続されている。

#### 【0113】

ADCサブバス670及び入力サブバス604-1を構成する導体は、長さが短く、ADC102のデジタル出力122からサンプル・プロセッサ612のサンプル入力614まで、及び、サンプル・プロセッサのサンプル出力616からメモリ106のデータ入力130まで、チップ612の表面を横切って直接延びている。サンプル・プロセッサは、ADCによってサポートされる最高サンプリング・レートで動作するよう構成されている。従って、ADCサブバス、サンプル・プロセッサ、及び、入力サブバスは、全て、ADCによってサポートされる最高サンプリング・レートで動作可能である。20

#### 【0114】

サンプル・プロセッサ612は、ADC102から受信するデジタル・サンプルを処理して、デジタル・サンプルがメモリ106に伝送される速度を低下させることによって、メモリに記憶することが可能な事象の最大持続時間が延長されるようにする。サンプル・プロセッサは、いくつかの異なるやり方で、デジタル・サンプルがメモリに伝送される速度を低下させることが可能である。サンプル・プロセッサは、制御信号CTRLによって、ADC102のサンプリング・レートに等しい速度でメモリにデジタル・サンプルを伝送する第1の状態と、低下した速度でメモリにデジタル・サンプルを伝送する第2の状態との間でスイッチ（すなわち、切り換え）できるように構成されている。サンプル・プロセッサは、さらに、制御信号によって、それぞれに異なる低下速度で、メモリにデジタル・サンプルを伝送する状態にスイッチできるように構成することも可能である。最後に、サンプル・プロセッサは、さらに、制御信号によって、デジタル・サンプルを所与の低下速度でメモリに伝送する前に、それぞれに異なるやり方で、ADCから受信したデジタル・サンプルに処理を加える状態にスイッチできるように構成することも可能である。30

#### 【0115】

図示の例の場合、サンプル・プロセッサ612は、さらに、クロック出力626を介して、メモリ106に書き込みクロック信号WCを供給するように構成されている。書き込みクロック信号は、サンプル・プロセッサがメモリにデジタル・サンプルを伝送する速度に対応する周波数を有している。メモリ106の構造に応じて書き込みクロック信号を、単相クロック信号または多相クロック信号とすることが可能である。

#### 【0116】

サンプル・プロセッサ612の第1の動作例では、アナログ・デジタル変換システム600は、その最大時間分解能を有し、サンプル・プロセッサは、ADCサブバス670を介してADC102から受信する全てのデジタル・サンプルを、入力サブバス604

10

20

30

40

50

- 1を介して、メモリ106に伝送する。

【0117】

サンプル・プロセッサ612の第2の動作例では、サンプル・プロセッサは、ADC102から受信するディジタル・サンプルのうち選択されたものだけをメモリに伝送することによって、メモリ106に記憶することが可能な事象の最大持続時間を延長する。例えば、サンプル・プロセッサは、ADCから受信したディジタル・サンプルを交互にメモリに伝送することによって、メモリに記憶することが可能な事象の最大持続時間を2倍にすることが可能である。最大持続時間は、サンプル・プロセッサが、ADCから受信するディジタル・サンプルの3つに1つ、4つに1つ等だけしかメモリに伝送しないことによって、3倍、4倍等にすることが可能である。代替的には、サンプル・プロセッサは、ADCから受信するsのディジタル・サンプル毎に、rのサンプルだけしかメモリに伝送しないことによって、ある部分量だけ最大持続時間を延長することが可能である。ここで、 $1 < r < s$ である。10

【0118】

サンプル・プロセッサ612の第3の動作例では、サンプル・プロセッサは、ADC102から受信するSのディジタル・サンプルからなる各ブロック毎に、ディジタル・サンプルに算術演算を施すことによって、メモリ106に記憶することが可能な事象の最大持続時間を延長する。算術演算によって、ブロックをなすディジタル・サンプルの中間値、平均値、RMS値、中央値、最大値、最小値、または、別の値といった、1つ以上のディジタル・サンプルの計算が行われる（すなわち、1つ以上の計算されたディジタル・サンプルを求める）。サンプル・プロセッサは、次に、ブロックをなすディジタル・サンプルの全てではなく、計算されたディジタル・サンプルのうちの1つ、選択されたいつか、または、全てをメモリに伝送する。20

【0119】

上述の第3の例では、メモリ106に記憶することが可能な事象の最大持続時間の延長は、各ブロックをなすディジタル・サンプル数Sによって決まり、また、逆に、ブロックをなす全てのディジタル・サンプルではなく、メモリに伝送されるディジタル・サンプル数によって決まる。ブロックをなす全てのディジタル・サンプルではなく、メモリに伝送するために計算されたディジタル・サンプルの選択は、部分的には、ディジタル・サンプルを用いて実施されることになる測定によって決まる。アナログ入力信号の最大値及び最小値が測定されることになる例の場合、ブロックをなすディジタル・サンプルの全てではなく、ブロックをなすディジタル・サンプルの最大値及び最小値を有するディジタル・サンプルがそれぞれ計算され、メモリに伝送される。30

【0120】

アナログ・ディジタル変換システム600の実際の実施態様において、サンプル・プロセッサ612は、ディジタル信号プロセッサを利用して実施された。サンプル・プロセッサは、ADC102のサンプリング・レートで動作可能な他のタイプのプログラマブル（プログラム可能な）または非プログラマブル回路で実施することが可能である。

【0121】

図7Aは、アナログ入力信号をディジタル方式でサンプリングするための本発明による方法の第1の実施態様700を例示したフローチャートである。40

【0122】

ブロック702では、メモリが設けられる。

【0123】

ブロック704では、あるサンプリング・レートで、アナログ入力信号のディジタル方式によるサンプリングを実施して、ディジタル・サンプルが生成される。

【0124】

ブロック706では、ディジタル・サンプルが、そのサンプリング・レートでメモリに記憶される。

【0125】

10

20

30

40

50

ブロック 708 では、デジタル・サンプルが、そのサンプリング・レートより低い速度でメモリから読み取られる。

【0126】

図 7B ~ 7H は、本発明による方法のさらなる実施態様を例示したフローチャートである。このさらなる実施態様は、図 7A に示す第 1 の実施態様の変形である。

【0127】

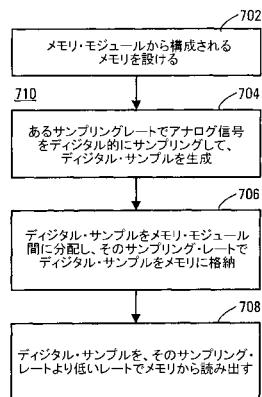

図 7B には、この方法の第 2 の実施態様 710 が示されている。ブロック 702 では、メモリがメモリ・モジュールから構成される。ブロック 706 では、デジタル・サンプルをメモリ・モジュール間に分配してから、記憶される。これによって、上記サンプリング・レートより低い速度で動作するメモリ素子をひとまとめに使用して、上記サンプリング・レートで生成されたデジタル・サンプルを記憶することが可能になる。10

【0128】

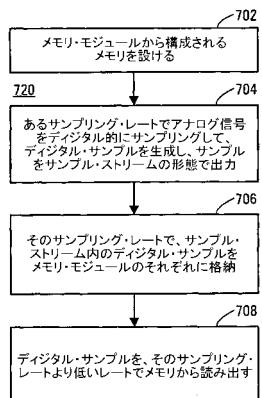

図 7C には、この方法の第 3 の実施態様 720 が示されている。ブロック 702 では、メモリが、メモリ・モジュールから構成される。ブロック 704 では、デジタル・サンプルが、全体としての速度が上記サンプリング・レートに等しい、サンプル・ストリームの形態で出力される。次に、ブロック 706 では、サンプル・ストリームのそれぞれにおけるデジタル・サンプルが、メモリ・モジュールのそれぞれに記憶される。

【0129】

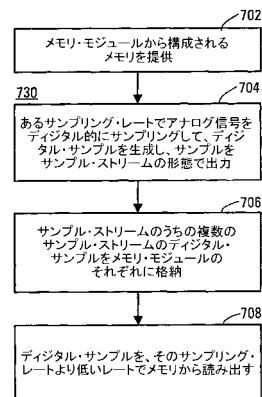

図 7D には、この方法の第 4 の実施態様 730 が示されている。ブロック 702 では、メモリが、メモリ・モジュールから構成される。ブロック 704 では、デジタル・サンプルが、全体としての速度が前記サンプリング・レートに等しい、サンプル・ストリームをなすように出力される。次に、ブロック 706 では、例えば、2つ以上といった、複数のサンプル・ストリームをなすデジタル・サンプルが、メモリ・モジュールのそれぞれに記憶される。20

【0130】

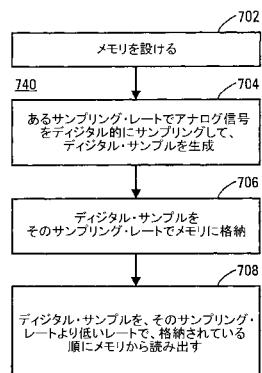

図 7E には、この方法の第 5 の実施態様 740 が示されている。ブロック 708 では、デジタル・サンプルが、それらがメモリに記憶された順に、メモリから読み取られる。

【0131】

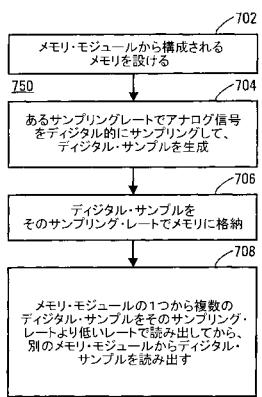

図 7F には、この方法の第 6 の実施態様 750 が示されている。ブロック 702 では、メモリが、メモリ・モジュールから構成される。ブロック 708 では、メモリ・モジュールの 1 つから複数のデジタル・サンプルの読み取りが済んでから、別のメモリ・モジュールからデジタル・サンプルの読み取りが行われる。複数のデジタル・サンプルの読み取りは、メモリ・モジュールに記憶されているデジタル・サンプルの部分集合から、メモリ・モジュールに記憶されているデジタル・サンプルの全てにまで及ぶ可能性がある。30

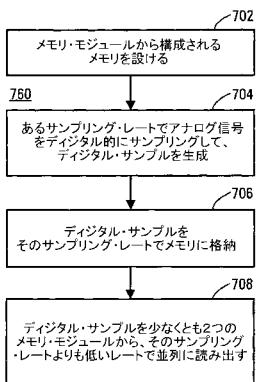

【0132】

図 7G には、この方法の第 7 の実施態様 760 が示されている。ブロック 702 では、メモリが、メモリ・モジュールから構成される。ブロック 708 では、デジタル・サンプルが、メモリ・モジュールの少なくとも 2 つから並列に読み取られる。

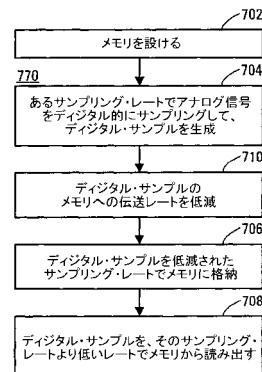

【0133】

図 7H には、この方法の第 8 の実施態様 770 が示されている。ブロック 710 では、メモリへのデジタル・サンプルの伝送速度が、サンプリング・レートに対して低下させられる。次に、ブロック 706 では、デジタル・サンプルが、低下された速度でメモリに記憶される。メモリへのデジタル・サンプルの伝送速度は、デジタル・サンプリングによって生成されたデジタル・サンプルの全てではなく、デジタル・サンプリングによって生成されたデジタル・サンプルのうちから選択されたものをメモリに伝送することによって低下させることが可能である。さらに、または、代替的に、メモリへのデジタルサンプルの伝送速度は、デジタル・サンプリングによって生成されたデジタル・サンプルからデジタル・サンプルの計算を実施し（すなわち、デジタル・サンプルから計算によってデジタル・サンプルを求め）、デジタル・サンプリングによって生4050

成されたデジタル・サンプルの全てではなく、計算されたデジタル・サンプルをメモリに送ることによって低下させることが可能である。

【0134】

本発明によるアナログ・ディジタル変換システム(100)は、ディジタル出力(122)を有するアナログ・ディジタル変換器(102)、データ入力(130)及びデータ出力(132)を有するメモリ(106)、出力ポート(110)、アナログ・ディジタル変換器のディジタル出力からメモリのデータ入力まで延びる入力データバス(104)、及び、メモリのデータ出力から出力ポートまで延びる出力データバス(108)を備える。アナログ・ディジタル変換器は、あるサンプリングレートでデジタルサンプルを生成するように構成される。入力データバスは、A D C のサンプリングレートで動作するよう構成される。メモリのデータ出力(132)、出力データバス(108)及び出力ポート(108)の少なくとも1つが、そのサンプリングレートよりも遅い最大レートで動作するよう構成される。

10

【0135】

この開示では、本発明の例示的な実施態様を詳細に説明したが、本発明は、説明した実施態様そのものに限定されるものではなく、特許請求の範囲によって画定される本発明の範囲内においてさまざまな変更を施すことが可能である。

【図面の簡単な説明】

【0136】

【図1】本発明によるアナログ・ディジタル変換システムの第1の実施態様に関するプロック図である。

20

【図2】本発明によるアナログ・ディジタル変換システムの第2の実施態様に関するプロック図である。

【図3】本発明によるアナログ・ディジタル変換システムの第3の実施態様に関するプロック図である。

【図4】本発明によるアナログ・ディジタル変換システムの第4の実施態様に関するプロック図である。

【図5】本発明によるアナログ・ディジタル変換システムの第5の実施態様に関するプロック図である。

【図6】本発明によるアナログ・ディジタル変換システムの第6の実施態様に関するプロック図である。

30

【図7 A】アナログ入力信号をデジタル方式でサンプリングするための本発明による方法の第1の実施態様を例示したフローチャートである。

【図7 B】図7 Aに例示した方法の変形である別の実施態様を例示したフローチャートである。

【図7 C】図7 Aに例示した方法の変形である別の実施態様を例示したフローチャートである。

【図7 D】図7 Aに例示した方法の変形である別の実施態様を例示したフローチャートである。

【図7 E】図7 Aに例示した方法の変形である別の実施態様を例示したフローチャートである。

40

【図7 F】図7 Aに例示した方法の変形である別の実施態様を例示したフローチャートである。

【図7 G】図7 Aに例示した方法の変形である別の実施態様を例示したフローチャートである。

【図7 H】図7 Aに例示した方法の変形である別の実施態様を例示したフローチャートである。

【符号の説明】

【0137】

100 アナログ・ディジタル変換システム

102 アナログ・ディジタル変換器

50

- 1 0 6 メモリ

1 0 8 出力データ・バス

1 1 0 出力ポート

1 2 2 アナログ・ディジタル変換器のデジタル出力

1 3 0 メモリのデータ入力

1 3 2 メモリのデータ出力

【図1】

【図2】

【図3】

【 四 4 】

【図5】

【 四 6 】

【 図 7 A 】

【図7B】

【図7D】

【図7C】

【図7E】

【図7F】

【図7H】

【図7G】

## フロントページの続き

(72)発明者 ケネス・ディー・ポウルトン

アメリカ合衆国カリフォルニア州94306, パロアルト, ロス・ロブレス・アベニュー・884

(72)発明者 トーマス・イー・コブレイ

アメリカ合衆国カリフォルニア州94020, ラ・ホンダ, ビバリー・ドライブ・230

(72)発明者 ロバート・エム・アール・ネフ

アメリカ合衆国カリフォルニア州94306, パロアルト, エマーソン・ストリート・3150

F ターム(参考) 5J022 AA01 BA05 BA06 CA10 CD02 CE01 CF08 CG01