# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 2 June 2005 (02.06.2005)

**PCT**

# (10) International Publication Number WO 2005/050829 A2

(51) International Patent Classification<sup>7</sup>:

H<sub>0</sub>3F

(21) International Application Number:

PCT/US2004/038359

(22) International Filing Date:

16 November 2004 (16.11.2004)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

60/520,904 17 November 2003 (17.11.2003) US 10/990,288 15 November 2004 (15.11.2004) US

- (71) Applicant (for all designated States except US): TRI-PATH TECHNOLOGY, INC. [US/US]; 2560 Orchard Parkway, San Jose, CA 95131 (US).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): MAZDA, Babak [US/US]; 449 Mountain Laurel Court, Mountain View, CA 94043 (US).

- (74) Agent: VILLENEUVE, Joseph, M.; Beyer Weaver & Thomas, LLP, P.O. Box 70250, Oakland, CA 94612-0250 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: OVERCURRENT PROTECTION IN AMPLIFIER TOPOLOGIES EMPLOYING DC ISOLATION

(57) Abstract: An amplifier having output switch circuitry is described. A sense resistor is operable to transmit an output current associated with the output switch circuitry. Low-voltage circuitry is operable to provide a drive signal to the output switch circuitry. Isolation circuitry is operable to provide DC isolation between the low-voltage circuitry and the output switch circuitry. Current sensing circuitry is directly connected to the sense resistor and is operable to sense the output current in the sense resistor and generate a fault signal in response to an overcurrent condition. The fault signal is characterized by a signal level which is compatible with the low-voltage circuitry without additional DC isolation.

# OVERCURRENT PROTECTION IN AMPLIFIER TOPOLOGIES EMPLOYING DC ISOLATION

## RELATED APPLICATION DATA

5 [0001] The present application claims priority under 35 U.S.C. 119(e) to U.S. Provisional Patent Application No. 60/520,904 for OVERCURRENT PROTECTION IN AMPLIFIER TOPOLOGIES EMPLOYING DC ISOLATION filed November 17, 2003 (Attorney Docket No. TRIPP043P), the entire disclosure of which is incorporated herein by reference for all purposes.

10

15

20

25

## BACKGROUND OF THE INVENTION

[0002] The present invention relates generally to overcurrent protection, and more specifically to providing overcurrent protection in amplifier topologies which employ DC isolation.

[0003] DC isolation is employed in many amplifier topologies to separate relatively high power output stages from the relatively low power circuits which drive them. It is desirable to provide such isolation for a variety of reason, e.g., to reduce fabrication costs, especially in cases where the lower power circuits may be characterized by more than one signal or power supply level. Overcurrent protection schemes which are compatible with such isolation techniques are also desirable.

#### SUMMARY OF THE INVENTION

[0004] According to the invention, compatible overcurrent protection and DC isolation techniques are provided. According to a specific embodiment, an amplifier having output switch circuitry is provided. A sense resistor is operable to transmit an output current associated with the output switch circuitry. Low-voltage circuitry is

operable to provide a drive signal to the output switch circuitry. Isolation circuitry is operable to provide DC isolation between the low-voltage circuitry and the output switch circuitry. Current sensing circuitry is directly connected to the sense resistor and is operable to sense the output current in the sense resistor and generate a fault signal in response to an overcurrent condition. The fault signal is characterized by a signal level which is compatible with the low-voltage circuitry without additional DC isolation.

5

10

[0005] According to another embodiment, an amplifier is provided having an output switching stage, a low voltage stage operable to generate a drive signal for driving the output switching stage, and isolation circuitry operable to provide DC isolation between the low voltage stage and the output switching stage. Current sensing circuitry is operable to detect an overcurrent condition in the output switching stage and generate a fault signal. The fault signal is characterized by a signal level which is compatible with the low voltage stage without additional DC isolation.

15 [0006] A further understanding of the nature and advantages of the present invention may be realized by reference to the remaining portions of the specification and the drawings.

## BRIEF DESCRIPTION OF THE DRAWINGS

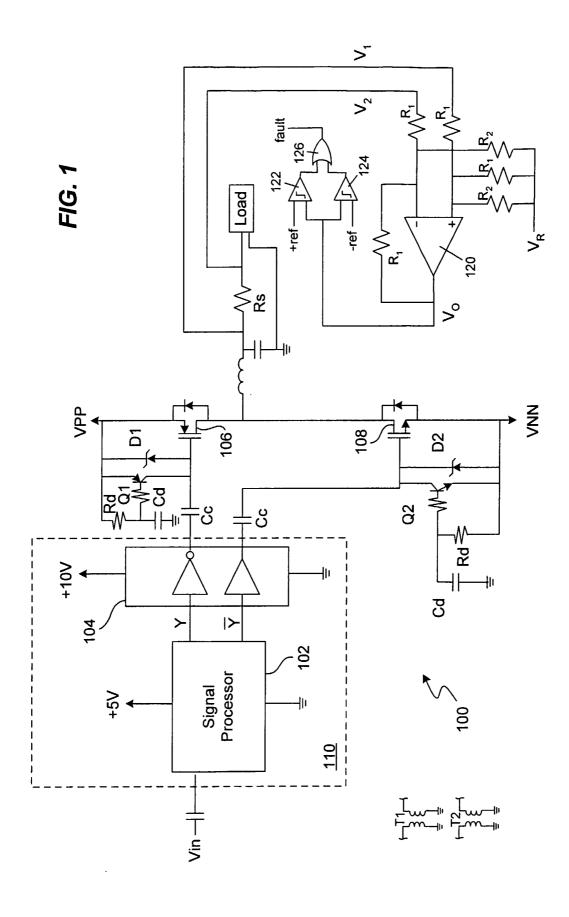

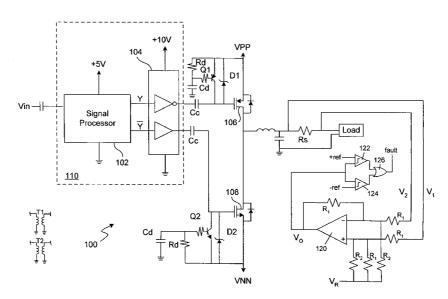

20 [0007] Fig. 1 is a schematic diagram illustrating a specific embodiment of the invention.

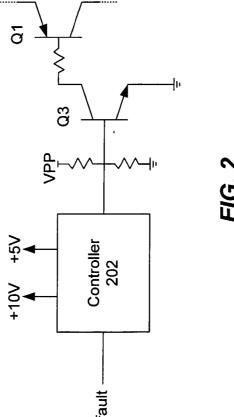

[0008] Fig. 2 is a schematic diagram of an alternative circuit for use with a specific embodiment of the invention.

#### DETAILED DESCRIPTION OF SPECIFIC EMBODIMENTS

[0009] Reference will now be made in detail to specific embodiments of the invention including the best modes contemplated by the inventor for carrying out the invention. Examples of these specific embodiments are illustrated in the accompanying drawings. While the invention is described in conjunction with these specific embodiments, it will be understood that it is not intended to limit the invention to the described embodiments. On the contrary, it is intended to cover alternatives, modifications, and equivalents as may be included within the spirit and scope of the invention as defined by the appended claims. In the following description, specific details are set forth in order to provide a thorough understanding of the present invention. The present invention may be practiced without some or all of these specific details. In addition, well known features may not have been described in detail to avoid unnecessarily obscuring the invention.

[0010] As mentioned above, a variety of techniques may be employed in switching circuit topologies to provide isolation between relatively high power output devices and the relatively low power circuitry which drives them. Such techniques include capacitive and inductive coupling. Embodiments of the present invention provide overcurrent sensing techniques which may be employed in conjunction with such isolation techniques.

15

20

[0011] Fig. 1 illustrates an exemplary switching amplifier in which a particular embodiment of the invention may be implemented. It should be noted that the amplifier topology of Fig. 1 is shown and described to provide an example of a context in which the present invention may be practiced. However, the present

invention is not limited to the described context and may be practiced in any of a wide variety of amplifier topologies in which DC isolation is provided.

- [0012] Switching amplifier 100 includes a low voltage, noise-shaping signal processor 102 which generates complementary 1-bit digital signals Y and  $\overline{Y}$ .

- According to the embodiment shown, these  $0 \sim 5V$  signals are level shifted by high current driver circuit 104 to  $0 \sim 10V$  signals to provide the appropriate voltage and current levels to drive output FETs 106 and 108.

- [0013] Two capacitors  $C_C$  provide DC isolation between the output FETs and current driver circuit 104 and, along with diodes D1 and D2, level shift the output signals of circuit 104 to VPP ~ VPP-10 volts at the gate of high side FET 106, and VNN ~ VNN+10 volts at the gate of low side FET 108. Where the FET driving voltages are relatively low, e.g., the 10 volt range, diodes D1 and D2 may comprise signal diodes. Where the FET driving voltages are higher, e.g., the 15 volt range, zener diodes may be used to clamp the gates to  $\pm 10$  volts.

10

15

- [0014] Transistors Q1 and Q2 squelch the gates of output FETs 106 and 108 (in accordance with the time constant corresponding to Rd and Cd) during the time when supply voltages VPP and VNN are ramping up. That is, because of the RC time constants, the base terminals of transistors Q1 and Q2 lag behind the supply voltages keeping transistors Q1 and Q2 turned on, effectively clamping the gates of the output FETs to the supply voltages, thereby ensuring that the output FETs remain off until the supply voltages have stabilized and transistors Q1 and Q2 subsequently turn off. This eliminates potentially catastrophic results which might otherwise occur at turn on as a result of the indeterminate state of the gates of the output FETs.

- [0015] Significant benefits may be derived from the DC isolation provided by capacitors C<sub>C</sub>. For example, because driver circuit 104 is isolated from the high

supply voltages (e.g., ±50V) required by the output FETs, it does not have the breakdown voltage requirements of a driver circuit directly coupled to the output switches. Thus, if driver circuit 104 is implemented as an integrated circuit, a lower voltage (and therefore less expensive) process may be employed in its fabrication.

5

- [0016] In addition, the isolation of driver circuit 104 from the output FETs creates an opportunity to integrate driver circuit 104 with the low voltage circuitry of signal processor 102 in a single monolithic integrated circuit (represented by dashed line 110). Thus, for example, in the exemplary embodiment shown in Fig. 1, a  $16 \sim 20$ V process with geometries around 0.5 uM could be used for such a monolithic IC instead of a  $80 \sim 100$ V process (with the correspondingly larger geometries) for driver circuit 104, and a  $5 \sim 10$ V process for processor 102. In general, lower voltage processes are less expensive and more common than their high voltage counterparts, allowing the designer to select from a greater variety of mature processes offered by a greater number of semiconductor fabs.

- 15 [0017] Overcurrent protection for amplifier 100 may be provided according to a specific embodiment of the invention using a current sensing circuit which senses the current flowing in sense resistor Rs (which might, for example, be in the range of 50-100 milliohms) and generates a fault signal in response to an overcurrent condition. Op amp 120 is configured with resistors  $R_1$  and  $R_2$  to generate an output  $V_0$  equal to  $V_1 V_2 + V_R$ . Exemplary values for  $R_1$  and  $R_2$  are 200 k $\Omega$  and 6 k $\Omega$ , respectively.  $V_R$  may be selected to place the output of op amp 120 at the desired level halfway between the +ref and -ref voltages associated with comparators 122 and 124, e.g., if -ref is zero volts and +ref is 5 volts,  $V_R$  may be set at 2.5 volts.

- [0018] If V<sub>O</sub> goes outside of the range between -ref and +ref (i.e., a large voltage appears across Rs), a fault signal is generated (e.g., at the output of OR gate 126)

5

10

15

20

25

and 104.

which may be used in any of a variety of ways to control or shut down operation of amplifier 100. For example, the signal may be used as an input to a "window" circuit. the output of which may be used to turn off the output switches. One exemplary use of the fault signal is described below with reference to Fig. 2. In view of the fact that the use of a fault indicator to control the operation of an amplifier is well within the knowledge of one of skill in the art, further details regarding the manner in which the fault signal generated according to the invention may be used are not provided here. [0019] The voltage levels associated with most of the current sensing circuitry are significantly lower than the voltages experienced by the sensing resistor Rs. Thus, the current sensing circuitry and any circuitry employing the fault signal are effectively isolated from the high voltages of the output stage of amplifier 100. Much of this circuitry can therefore be implemented as relatively inexpensive, low voltage circuitry as described above with reference to signal processor 102 and driver circuitry 104. In fact, the current sensing circuitry (with the exception of the resistors connected directly to Rs) could be implemented on a single die with either or both of circuits 102

[0020] While the invention has been particularly shown and described with reference to specific embodiments thereof, it will be understood by those skilled in the art that changes in the form and details of the disclosed embodiments may be made without departing from the spirit or scope of the invention. For example, the present invention relates generally to providing overcurrent protection in a switching amplifier topology which employs some form of DC isolation. The techniques described herein may be applied to any of a wide variety of switching circuit topologies such as, for example, any type of digital or class D amplifier including sigma delta modulators, and modified sigma delta modulators (e.g., Class T amplifiers

available from Tripath Technology Inc. of Santa Clara, California). Examples of suitable amplifier topologies are described in U.S. Patent No. 5,777,512 for METHOD AND APPARATUS FOR OVERSAMPLED, NOISE-SHAPING, MIXED-SIGNAL PROCESSING issued July 7, 1998, the entire disclosure of which is incorporated herein by reference for all purposes. However, it will be understood that the invention is not limited to the described topologies. For example, the present invention may also be applied to any type of pulse width modulation (PWM) amplifier, switch mode power supplies (SMPS), etc.

Moreover, the invention is not limited by the manner in which DC

[0021]

10

15

20

25

isolation is provided. That is, for example, the invention is not limited to topologies employing capacitive coupling. Other DC isolation techniques such as, for example, transformer or inductive coupling (e.g., transformers T1 and T2 of Fig. 1 in place of capacitors  $C_C$ ), may be employed with various embodiments of the invention. [0022] In addition, instead of controlling the bases of Q1 and Q2 with the RC circuits shown in Fig. 1, other types of control circuits may be employed which include, but are not limited to, active circuit elements which are enabled for a programmable period of time or in response to one or more control signals. For example, according to an alternative embodiment illustrated in Fig. 2, the base of O1 is coupled to the collector of another transistor Q3 which is driven to pull the base of Q1 down for a period of time. The driving signal of such a transistor and the period of time could be controlled by any of a variety of analog or digital circuitry (represented by controller 202) including, for example, a microprocessor or any other type of controller. This circuitry may be incorporated or integrated with the driver circuitry or separate therefrom. Such a controller may be configured to operate during

stabilization of the supply voltages (e.g., during power up). Such a controller may

5

10

also be configured to control Q1 and Q2 during amplifier operation independent of drive from the driver circuitry, e.g., in response to a fault condition such as, for example, an overcurrent condition indicated by the fault signal generated by OR gate 126 of Fig. 1. In addition, and as will be understood, such a controller may be configured to drive transistors Q1 and Q2 directly.

[0023] Finally, although various advantages, aspects, and objects of the present invention have been discussed herein with reference to various embodiments, it will be understood that the scope of the invention should not be limited by reference to such advantages, aspects, and objects. Rather, the scope of the invention should be determined with reference to the appended claims.

## What is claimed is:

1. An amplifier, comprising:

output switch circuitry;

a sense resistor operable to transmit an output current associated with the output switch circuitry;

low-voltage circuitry operable to provide a drive signal to the output switch circuitry;

isolation circuitry operable to provide DC isolation between the low-voltage circuitry and the output switch circuitry; and

current sensing circuitry directly connected to the sense resistor and operable to sense the output current in the sense resistor and generate a fault signal in response to an overcurrent condition, the fault signal being characterized by a signal level which is compatible with the low-voltage circuitry without additional DC isolation.

- 2. The amplifier of claim 1 wherein the isolation circuitry comprises one of a capacitor and a transformer.

- 3. The amplifier of claim 1 wherein the low-voltage circuitry comprises

first circuitry operable to generate complementary signals, and second circuitry

operable to level shift the complementary signals to signal levels appropriate for

driving the output switch circuitry.

- 4. The amplifier of claim 3 wherein the first and second circuitry are integrated on a single chip.

5. The amplifier of claim 4 wherein the current sensing circuitry is also integrated on the single chip.

- 5 6. The amplifier of claim 1 wherein the output switch circuitry comprises complementary field effect transistors.

- 7. The amplifier of claim 6 further comprising transient control circuitry operable to keep the field effect transistors off during stabilization of supply voltages associated with the field effect transistors.

- 8. The amplifier of claim 7 wherein the transient control circuitry comprises clamping circuits operable to clamp drive terminals of a corresponding one of the field effect transistors to the associated supply voltage for a predetermined period of time.

- 9. The amplifier of claim 8 wherein each clamping circuit comprises a clamping switch coupled between the corresponding supply voltage and drive terminal.

20

10

15

10. The amplifier of claim 9 wherein the each clamping circuit further comprises an RC circuit coupled to the corresponding supply voltage which is operable to supply a gating signal to the clamping switch which lags behind the corresponding supply voltage.

11. The amplifier of claim 10 wherein each clamping circuit further comprises a second clamping switch which is operable to provide a gating signal to the clamping switch.

- 12. The amplifier of claim 11 wherein each clamping circuit further comprises a controller circuit which is operable to drive the second clamping switch.

- 13. The amplifier of claim 12 wherein the controller circuit is operable to drive the second clamping switch in response to the fault signal.

10

5

- 14. The amplifier of claim 12 wherein the controller circuit is operable to drive the second clamping switch during stabilization of the supply voltage.

- 15. The amplifier of claim 1 wherein the current sensing circuitry is

operable to convert a first sense voltage across the sense resistor to a second sense voltage for comparison to upper and lower threshold voltages, the fault signal being generated when the second sense voltage does not fall between the upper and lower threshold voltages.

- 20 16. The amplifier of claim 1 wherein the amplifier comprises one of a digital amplifier, a pulse width modulator, and a switch mode power supply.

- 17. The amplifier of claim 16 wherein the digital amplifier comprises one of a sigma-delta modulator and a modified sigma-delta modulator.

operable to generate a drive signal for driving the output switching stage, and isolation circuitry operable to provide DC isolation between the low voltage stage and the output switching stage, the amplifier further comprising current sensing circuitry operable to detect an overcurrent condition in the output switching stage and generate a fault signal, the fault signal being characterized by a signal level which is compatible with the low voltage stage without additional DC isolation.

19. The amplifier of claim 18 wherein the low voltage stage and the current sensing circuitry are integrated on a single chip.