(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5837689号

(P5837689)

(45) 発行日 平成27年12月24日(2015.12.24)

(24) 登録日 平成27年11月13日(2015.11.13)

(51) Int.Cl.

H01L 31/107 (2006.01)

F 1

H01L 31/10

B

請求項の数 14 (全 15 頁)

(21) 出願番号 特願2014-519066 (P2014-519066)

(86) (22) 出願日 平成24年7月6日 (2012.7.6)

(65) 公表番号 特表2014-518458 (P2014-518458A)

(43) 公表日 平成26年7月28日 (2014.7.28)

(86) 國際出願番号 PCT/US2012/045744

(87) 國際公開番号 WO2013/009615

(87) 國際公開日 平成25年1月17日 (2013.1.17)

審査請求日 平成27年2月20日 (2015.2.20)

(31) 優先権主張番号 13/179,378

(32) 優先日 平成23年7月8日 (2011.7.8)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 512086149

エクセリタス カナダ, インコーポレイテッド

カナダ国, ケベック州 ジェイアヴィ 8

ピー7, ヴォードルイユードリオン, ダン

バリー ロード 22001

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(72) 発明者 ドーテ, ヘンリ

カナダ国, ケベック州 ジェー4ブイ1ケ

ー6, グリーン フィールド パーク, リ

ュ クミング 955

最終頁に続く

(54) 【発明の名称】光子計数UV-APD

## (57) 【特許請求の範囲】

## 【請求項1】

アバランシェフォトダイオード(ADP)であって、

第1のドーピング型を有する第1の半導体基板と、

前記第1の半導体基板の上部の第1の半導体層であって、前記第1のドーピング型をドープされる、第1の半導体層と、

前記第1の半導体層の上部の第2のエピタキシャル層であって、前記第1の半導体層内の前記第1のドーピング型の濃度より高い濃度で、前記第1のドーピング型を原位置で(*in-situ*)ドープされる、第2のエピタキシャル層と、

前記第2のエピタキシャル層の上部の第3のエピタキシャル層であって、第2のドーピング型を原位置でドープされ、第3のエピタキシャル層のドーピングは、第2のエピタキシャル層のドーピングと共に、第1のp-n接合を形成し、キャリア増倍領域は前記第1のp-n接合を含み、第3のエピタキシャル層は、光子のための吸収領域を形成する、第3のエピタキシャル層と、

前記第3のエピタキシャル層内第1の埋設領域であって、前記第2のドーピング型をドープされる、第1の埋設領域とを備えるAPD。

## 【請求項2】

前記第1の半導体層は、第1のエピタキシャル層であり、前記第1のドーピング型を原位置でドープされる請求項1に記載のAPD。

## 【請求項3】

10

前記第1の半導体層は、前記第1の半導体基板に接合される第2の半導体基板である請求項1に記載のA P D。

【請求項4】

前記第1のドーピング型はn型であり、前記第2のドーピング型はp型であり、前記半導体基板はシリコンで作られる請求項1に記載のA P D。

【請求項5】

前記第2のエピタキシャル層および前記第3のエピタキシャル層の部分にオーバラップする前記第1のドーピング型の第2の埋設領域をさらに備え、前記第2の埋設領域は、前記第1の埋設領域と共に第2のp-n接合を形成する請求項1に記載のA P D。

【請求項6】

前記第1または第2の半導体基板は、表面上に絶縁層を有し、前記絶縁層は、前記第2および第1の半導体基板にそれぞれ接合される請求項3に記載のA P D。

【請求項7】

前記第2の半導体基板内に埋め込みインプラント領域をさらに備え、前記埋め込みインプラント領域は、前記第2の半導体基板の前記接合表面に隣接し、前記埋め込みインプラント領域は、前記第1のドーピング型をドープされる請求項6に記載のA P D。

【請求項8】

前記第3のエピタキシャル層の上部表面上で前記第1の埋設領域に電気的に接続するアノード電極と、

前記半導体基板の下部表面上で前記半導体基板に電気的に接続するカソード電極とをさらに備える請求項4に記載のA P D。

【請求項9】

前記カソード電極は、前記アノード電極より高くバイアスされる請求項8に記載のA P D。

【請求項10】

アバランシェフォトダイオードを作製するためのプロセスであって、

第1のドーピング型を有する半導体ウェハを準備すること、

第1のエピタキシャル層であって、前記第1のドーピング型を原位置でドープされる、第1のエピタキシャル層を前記半導体ウェハの上部で成長させること、

第2のエピタキシャル層であって、前記第1のエピタキシャル層内の前記第1のドーピング型の濃度より高い濃度で、前記第1のドーピング型を原位置でドープされる、第2のエピタキシャル層を前記第1のエピタキシャル層の上部で成長させること、

第3のエピタキシャル層であって、第2のドーピング型を原位置でドープされ、第3のエピタキシャル層は、第2のエピタキシャル層と共に、第1のp-n接合を形成し、キャリア増倍領域は前記第1のp-n接合を含み、第3のエピタキシャル層は吸収領域を形成する、第3のエピタキシャル層を前記第2のエピタキシャル層の上部で成長させること、および、

前記第3のエピタキシャル層内の第1の領域に、前記第2のドーピング型のイオンを注入することを含むプロセス。

【請求項11】

エピタキシチャンバは、前記第1、第2、および第3のエピタキシャル層を成長させ、前記第1、第2、および第3のエピタキシャル層は、前記エピタキシチャンバ内で同時に成長される請求項10に記載のプロセス。

【請求項12】

前記第2のエピタキシャル層内の第2の領域に、前記第1のドーピング型のイオンを注入することをさらに含み、前記第2の領域は、前記第3のエピタキシャル層を成長させる前に注入され、前記第2の領域は、前記第1の領域と共に第2のp-n接合を形成する請求項10に記載のプロセス。

【請求項13】

前記第1のドーピング型はn型であり、前記第2のドーピング型はp型であり、前記半

10

20

30

40

50

導体ウェハはシリコンで作られる請求項 10 に記載のプロセス。

【請求項 14】

アノード電極であって、前記第 1 の領域に電気的に接続する、アノード電極を前記第 3 のエピタキシャル層の上部に形成すること、および、

カソード電極を前記半導体ウェハの下部に形成することをさらに含む請求項 13 に記載のプロセス。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、一般に、アバランシェフォトダイオード (A D P) に関し、より具体的には 10 、アレイ化デバイスで使用される A P D に関する。

【背景技術】

【0002】

A P D は、光を電気信号に変換する半導体光検出器である。基本的 A P D は、2 つの主要な領域、すなわち、吸収領域と増倍領域を有する。A P D の設計に応じて、吸収領域は、増倍領域の一方の面だけかまたは両面にあることができる。吸収領域で吸収される光子は、電子 - 正孔対を生成する。電子（吸収領域が p 型である場合）は、低レベル電界によって増倍領域までドリフトするかまたは運ばれる。増倍領域内の強い電界は、増倍領域内の衝撃イオン化を通してより多くの電子 - 正孔対を生成するのに十分なエネルギーを電子が有する点まで電子を加速する。半導体および A P D の設計に応じて、増倍領域に達する電子、正孔、または両方は、さらなる電子 - 正孔対を生成することができる点まで加速されることができる。このプロセスは、無期限にまたは全てのキャリアが、さらなるキャリアを生成することなく、増倍領域から掃き出されるまで継続することができる。衝撃イオン化のこのプロセスを通して、1 つの電子 - 正孔対は、数百か数千以上の（またはかなり多くの）電子 - 正孔対を生成することができる。電子および正孔が端子に達すると、電流が生成され、電流が、検出され測定されることができる。

【0003】

単一の吸収光子から生成される電子 - 正孔対の数（すなわち A P D 利得）は、A P D の設計および動作点に基づいて変動する。A P D について 2 つの主要な動作モード、すなわち、アナログモードおよびガイガーモードが存在する。

【0004】

アナログモードでは、A P D の利得は、A P D 構造および A P D に印加される逆バイアスの関数である。通常、逆バイアスが高ければ高いほど利得が高い。たとえば、A P D は、125 V で 20 の利得、また、185 V で 300 の利得を示す場合がある。1000 まで又はそれ以上の利得が、A P D の材料、製造プロセス、および設計に応じて可能である。アナログモードでは、増倍領域内の電界が、無期限に電子 - 正孔対を生成するほど強くないことに留意されたい。最終的に、キャリアの全ては、デバイスから掃き出され、別の光子が増倍領域に達する電子を生成するまで電流がゼロまで降下することになる。

【0005】

ガイガーモードでは、A P D は、アナログモードの場合より高くかつ A P D 絶縁破壊電圧を超えて逆バイアスされる。逆バイアスが、 $10^5$  または  $10^6$  の利得をもたらす場合がある非常に強い電界を生成する、または、上述した衝撃イオン化プロセスが、A P D をさらに「ラッチし(latch)」、自己持続的になる場合がある。プロセスが自己持続的になる場合、電界が維持される限り、電子 - 正孔対が生成され続け、電流が A P D を通って流れ続けることになる。

【0006】

A P D の動作モードに加えて、A P D に印加される逆バイアスはまた、生成される電子または正孔が衝撃イオン化プロセスを通して検出可能な信号を生成する確率を決定することができる。一部の A P D では、逆バイアスは、1 つのキャリア（たとえば、正孔）が A P D をトリガーする確率を、他のキャリア（たとえば、電子）が A P D をトリガーする確

率と比較して減少させるように設定することができる。

【0007】

光子が、生成される電子または正孔によって、自己持続的な衝撃イオン化プロセスを生成する場合、APDはクエンチを使用してそれ自身をリセットすることができる。特にAPDは受動又は能動クエンチを使うことができる。

【0008】

受動クエンチは、APDのカソードまたはアノードとAPDに逆バイアスを供給する電圧源との間で直列に接続された値が高い抵抗器によって実装することができる。増倍領域内で自己持続的な衝撃イオン化プロセスをトリガーする電子を光子が生成すると、電流がAPDを通して流れ始める。電流は、値が高い抵抗器を通してかなりの電圧降下を引起すことになる。値が高い抵抗器の両端の電圧降下は、増倍領域内で電界を減少することになり、そのことは、増倍領域内の電子および正孔がさらなる電子・正孔対を生成することになる機会を減少させることになる。電界が十分に低く降下すると、衝撃イオン化プロセスが終了し、APDがリセットすることになる。その理由は、値が高い抵抗器が、その両端に電圧降下がもはやなくなるからである。

10

【0009】

能動クエンチは、ラッチされるAPDを検出するクエンチ回路を使用する。APDがラッチされたことをクエンチ回路が検出すると、回路は、電圧源からAPDを切離すかまたはAPDに印加される逆バイアスを減少させることができる。これらの動作のいずれかが、増倍領域内の電界を減少させることになる。電界が十分に低く降下すると、自己持続的な衝撃イオン化プロセスが終了し、APDが伝導を停止することになる。その後、クエンチ回路は、APDに対して逆バイアスを回復して、次の光子のためにAPDをリセットすることができる。

20

【0010】

利得以外に、APDの性能を記述するいくつかの他の重要なパラメータが存在する。たとえば、量子効率は、光子が吸收領域内で電子・正孔対を生成し、電子または正孔が増倍領域に達し、早期に終了しない衝撃イオン化プロセスを始動することになる確率である。暗計数率は、非光子生成キャリアが衝撃イオン化プロセスを始動する率である。これらの信号を、光子によって生成される信号から区別することは不可能である。

【0011】

30

個々の離散的デバイスとしてAPDを使用することに加えて、複数のAPDを、統合化アレイにおいて使用することができる。アレイ化APDは、たとえばイメージング用途において有用である場合がある。シリコン光電子増倍管(silicon photomultiplier)(SiPM)は、APDのアレイを使用するデバイスの例である。APDのアレイでは、各APDは、アレイのピクセルとして知られる場合がある。

【0012】

個々のAPDの性能パラメータに加えて、他の性能パラメータが、アレイ化APDにとって重要である場合がある。たとえば、クロストークは、1つのAPD内の衝撃イオン化プロセスが、隣のAPD内の衝撃イオン化プロセスをトリガーすることになる確率である。

40

【0013】

APDのさらなる記述は、米国特許第7,759,623号および本発明の譲受人に譲渡された米国特許公報第2008/0012087号として公開された2007年3月20日に出願された米国特許出願第11/725,661号に見出すことができ、その両方が、全ての目的について、参照によりその全体を本明細書に組込まれる。

【発明の概要】

【課題を解決するための手段】

【0014】

アバランシェフォトダイオード(ADP)の例示的な実施形態は、第1のドーピング型を有する第1の半導体基板を有する。第1の半導体層は第1の半導体基板の上部にある。

50

第1の半導体層は、第1のドーピング型をドープされる。第2のエピタキシャル層は第1の半導体層の上部にある。第2のエピタキシャル層は、第1の半導体層内の第1のドーピング型の濃度より高い濃度で、第1のドーピング型を原位置でドープされる。第3のエピタキシャル層は第2のエピタキシャル層の上部にある。第3のエピタキシャル層は、第2のドーピング型を原位置でドープされる。第3のエピタキシャル層のドーピングは、第2のエピタキシャル層のドーピングと共に、第1のp-n接合を形成し、キャリア増倍領域は第1のp-n接合を含み、第3のエピタキシャル層は、光子のための吸収領域を形成する。第1の埋設領域は第3のエピタキシャル層内にある。埋設領域は第2のドーピング型をドープされる。

## 【図面の簡単な説明】

10

## 【0015】

【図1A-1F】APDの第1の実施形態を作製するための例示的なプロセスの種々のステージを示す図である。

【図2A-2D】APDの第2の例示的な実施形態を作製するための別の例示的なプロセスの早期ステージを示す図である。

## 【図2E-2F】APDの第2の例示的な実施形態のオプションの特徴を示す図である。

【図3A-3F】APDの第3の実施形態を作製するための別の例示的なプロセスの種々のステージを示す図である。

【図4】カソードに対する背面接触がアノードに対する受動または能動クエンチを可能にする第3の実施形態を示す図である。

20

【図5】アノードに対する背面ビアが前面にある状態の、図1Eに示す第1の実施形態と同様の第4の実施形態を示す図である。

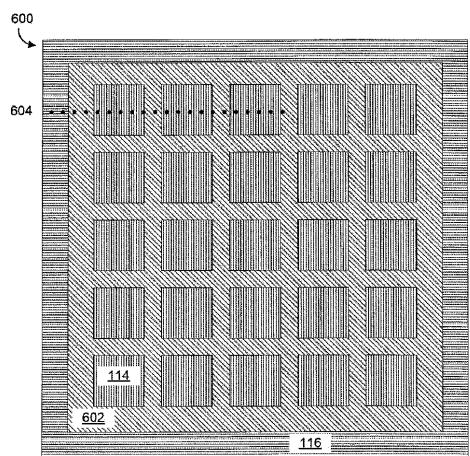

## 【図6】APDの5×5アレイの平面図である。

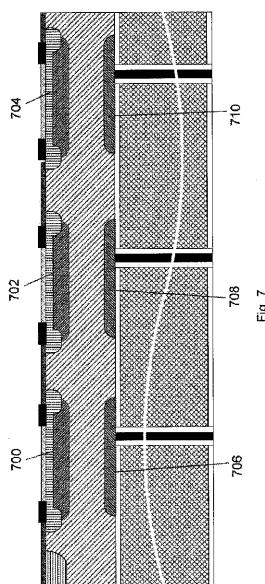

## 【図7】APDの5×5アレイの断面図である。

## 【発明を実施するための形態】

## 【0016】

以下の説明は、当業者が種々の実施形態を作り使用することを可能にするために提示される。特定のデバイス、技法、および適用形態の説明は、例としてだけ提供される。本明細書で述べる例に対する種々の変更は、当業者にとって容易に明らかになると思われ、また、本明細書で規定される一般的な原理は、種々の実施形態の精神および範囲から逸脱することなく、他の例および適用形態に適用することができる。そのため、種々の実施形態は、本明細書で述べ示される例に限定されることを意図されるのではなく、特許請求の範囲に矛盾しない範囲を与えられる。

30

## 【0017】

以下の議論は、400～500nmの波長を有する光子を検出するために設計された、シリコンで作られ、p型吸収領域（たとえば、ボロンをドープされた）を有するAPDの例示的な実施形態を参照する。しかし、以下で論じる概念を、他の半導体（たとえば、GeまたはInGaAs）、他のドーピングスキーム（たとえば、n型吸収領域を使用する）、および他の波長を検出することに同様に適用することができることを当業者は認識するであろう。

40

## 【0018】

図1A～1Eは、APDを作製するための例示的なプロセス中の種々のステージにおけるAPDの第1の実施形態を示す。図1A～1Eは、基板上の単一のAPDデバイスを示すが、製造中、多くのAPDが単一基板またはウェハ上に共に製造されることが理解されるべきである。さらに、以下の議論は、APDを作製するのに必要な全てのステップをカバーしない。当業者は、APDを作製するために他の必要なステップを認識するであろう。

## 【0019】

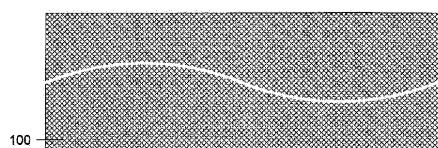

例示的なプロセスの第1のステップは、開始材料を設けることである。図1Aは、第1の実施形態について基板を形成するウェハ100を示す。ウェハ100は、約450μm

50

厚であり、約 50 m - cm 又はそれ以下の抵抗率をもたらす n 型ドーピングを有する。代替的に、ウェハ 100 は、約 200 ~ 500 μm 厚であり、約  $10^{19}$  cm<sup>-3</sup> ~  $10^{20}$  cm<sup>-3</sup> のドーピング濃度を有する。他のウェハ厚、抵抗率、およびドーピング型もまた使用することができる。

#### 【0020】

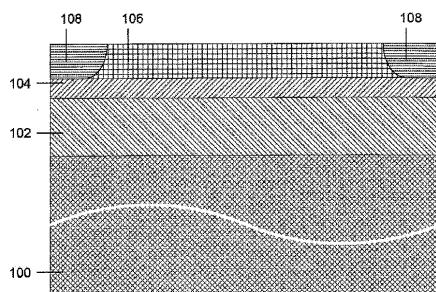

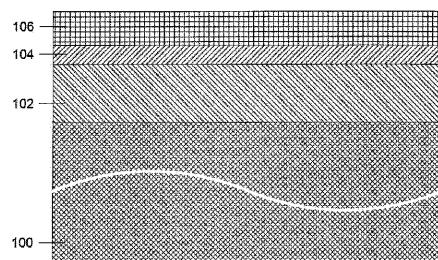

図 1B は、ウェハ 100 の上部で成長した 3 つのエピタキシャル層 102、104、および 106 を示す。層 102、104、および 106（ならびに開始材料）の厚さ、ドーピング、および材料は、光子の一定の波長を排除するかまたは含むために変動する場合がある。目下の実施形態では、APD は、400 ~ 500 nm の波長を有する光子がシリコンに吸収されるときに生成される電子に基づいて、これらの光子を検出するためシリコンを使用するように設計される。これらの型の光子についてのシリコン内の吸収深さは、1 μm 未満である。さらに、目下の実施形態では、生成される正孔に対する APD の応答を最小にするように設計される。したがって、第 1 の例示的な実施形態は、p 型半導体内で APD の表面の 1 μm 以内に吸収領域を有する。しかし、他の波長の光子を検出するように設計された他の実施形態では、吸収領域の場所は、層 102、104、106 の厚さまたはこれらの層のドーピングおよび開始材料を変動させることによって調節することができる。たとえば、吸収領域を、他の光子波長が検出されるように、層 104 と 106 との間の p - n 接合の下に移動することができる。吸収領域を、ウェハ 100 ならびに層 102、104、および 106 のドーピング型を逆にすることによって移動することができる。

10

20

#### 【0021】

層 102 は、層 106 と 104 との間の p - n 接合によって形成される空乏領域を広げる。空乏領域を広げることによって、第 1 の実施形態のキャパシタンスが減少し、第 1 の実施形態が動作する速度を増加することができる。層 102 は、開始材料と同じドーピング型（n 型）を有し、50 ~ 500 - cm の抵抗率または約  $10^{12}$  cm<sup>-3</sup> ~  $10^{15}$  cm<sup>-3</sup> のドーピング濃度および 10 ~ 50 μm の厚さを有することができる。層 102 を、そのエピタキシャル成長中に原位置でドープすることができる。

#### 【0022】

層 104 は、増倍領域の一部を形成する。層 104 は、開始材料と同じドーピング型（n 型）を有し、2 ~ 20 - cm の抵抗率または約  $10^{14}$  cm<sup>-3</sup> ~  $10^{16}$  cm<sup>-3</sup> のドーピング濃度および約 3 ~ 15 μm の成長厚さを有することができる。層 106 は、吸収領域および増倍領域の一部を形成する。層 106 は、開始材料、層 102、および層 104 と反対のドーピング型（p 型）を有し、2 ~ 20 - cm の抵抗率または約  $10^{14}$  cm<sup>-3</sup> ~  $10^{16}$  cm<sup>-3</sup> のドーピング濃度および 3 ~ 15 μm の成長厚を有することができる。層 104 および 106 を、同様にエピタキシャル成長中に原位置でドープすることができる。層 106 を成長させている間に、層 104 からのドーピングは、層 106 に拡散するため、層 106 と 104 との間の物理的境界に p - n 接合を形成する代わりに、p - n 接合が層 106 内に形成される。この p - n 接合の接合深さは、たとえば、表面下で 1 ~ 10 μm とすることができます。

30

40

#### 【0023】

吸収領域は、層 104 および 106 によって形成される p - n 接合の他の面に移動するかまたは他の面を含むことができる。これは、特定の適用形態について APD を調節することができる。たとえば、目下の実施形態では、光子検出が、生成される電子に加えて、生成される正孔に基づく場合、p - n 接合の他の面で生成される正孔は、APD に印加される逆バイアスが十分に高く、正孔が APD をトリガーすることを可能にするよう電界が整形される場合、同様に APD をトリガーすることができる。代替的に、層 102、104、および 106、ならびにウェハ 100 のドーピングが逆にされて、p - n 接合の下で生成される電子が APD をトリガーすることを可能にすることができる。これは、たとえば、シリコン内で他の光子波長を検出するのに有用である場合がある。

#### 【0024】

50

吸収領域および増倍領域における電界の適切な整形を、A P Dの性能を調節するために同様に使用することができる。たとえば、吸収領域又は増倍領域における電界の適切な形狀は、A P Dに印加される逆バイアスがたとえ高くても、吸収領域またはp - n接合の他の面で生成される正孔によってA P Dがトリガーされる確率を低減することができる。これは、たとえば生成される正孔がA P Dをトリガーするという低い確率を維持しながら、生成される電子がA P Dをトリガーする確率を増加させるためA P Dの逆バイアスを増加させるときに有用である場合がある。

【0025】

層102、104、106は全て、1つのプロセスステップで同時に成長することができる（すなわち、ウェハ100は、3つ全ての層が正長するまでエピタキシチャンバから除去されない）。代替的に、層は、異なるエピタキシチャンバ内で異なる時間に成長することができる。層104の成長と層106の成長との間にさらなる処理ステップを有するプロセスの例の場合、以下の図2に関する第2の実施形態の議論を参照されたい。10

【0026】

図1Cは、チャネル停止領域108が埋設された後のウェハ100を示す。これらの領域は、漏洩経路を防止することができる。領域108は、層104（n型）と同じ型のドーピングとすることができます。

【0027】

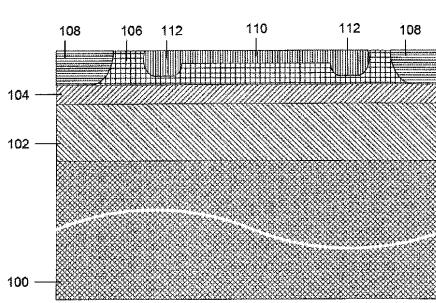

図1Dは、1つまたは複数のインプラントが層106内に領域110を形成した後のウェハ100を示す。この領域は、増倍領域内で電界を整形するのを助ける。領域110は、層106と同じドーピング型（p型）とすることができます。領域110を、増倍領域が層106の露出表面まで延在しないことを保証するために同様に形成することができる。層106の露出表面の近くの領域110内のピークドーピングは、約 $10^{20} \text{ cm}^{-3}$ とすることができる。20

【0028】

領域110のいずれかの端部におけるオプションの領域112は、増倍領域が横方向に延長するのを防止するために電界をさらに整形することができます。領域112が含まれる場合、領域112は、領域110を形成する同じインプラントによってまたは異なるインプラントによって形成することができます。たとえば、領域112の深さは、領域110の上の層106の表面と比較して領域112の上の層106の表面が異なるスクリーン酸化物厚を有する場合、領域110の深さに依存して変動する場合がある。30

【0029】

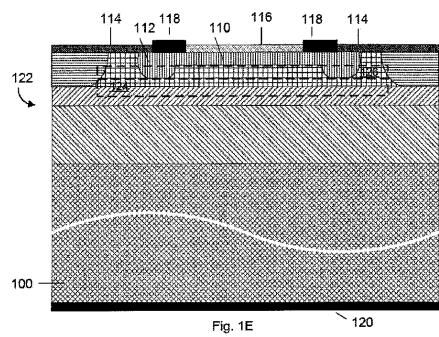

図1Eは、ウェハ100上に、アノード電極118、カソード電極120、絶縁層114、および反射防止被覆116を形成した後のA P Dの第1の実施形態122を示す。アノード電極118は領域110および112に電気的に接続し、カソード電極120はウェハ100に電気的に接続する。第1の実施形態122は、吸収領域126（点線の箱）および増倍領域124（点線の箱）を含む。第1の実施形態122は、 $15 \sim 100 \mu\text{m}$ 幅とすることができる。やはり、第1の実施形態は、吸収領域126において $400 \sim 500 \text{ nm}$ の波長を有する光子によって生成される電子を検出するように設計される。40

【0030】

上述したように形成されるデバイスの動作は次の通りである。カソード電極120とアノード電極118との間に大きな（たとえば、 $> 100 \text{ V}$ ）逆バイアスが印加されると、強い電界が、層104および106によって形成されるp - n接合の周りの増倍領域内に形成されることになる。光子が、吸収領域126に吸収される場合、電子 - 正孔対を生成することができる。正孔は、弱い電界によってアノード電極118に掃き出されることができる。電子は、弱い電界によって増倍領域124にドリフトするかまたは掃き出されることができ、そこで、強い電界が電子を加速する。電子が、十分なエネルギーを獲得(gain)する場合、増倍領域124内での衝撃イオン化を通してさらなる電子 - 正孔対を生成することができる。これらのキャリアは、強い電界によって分離されることになり、電極によって収集され、電流を生成する前に衝撃イオン化を通してさらなる電子 - 正孔対をトリ50

ガーすることができる。逆バイアスが十分に大きく、デバイスが適切に設計される場合、このプロセスは、自己持続的とすることができます。場合によっては、逆バイアスは、生成される電子が A P D をトリガーすることになる機会を増加させるのに十分に高いが、正孔が A P D を最小になるようトリガーする確率を維持することになる。

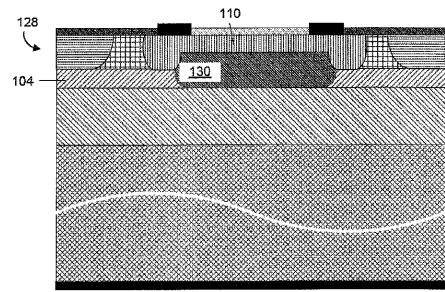

【 0 0 3 1 】

図 1 F は、図 1 A ~ 1 E に関して先に論じたのと同様なプロセスによって作製された第 1 の実施形態の変形である A P D 1 2 8 を示す。A P D 1 2 8 は、A P D 1 2 8 において、領域 1 3 0 が増倍領域内で電界をさらに整形することを除いて第 1 の実施形態 1 2 2 と同様である。領域 1 3 0 は、層 1 0 6 が成長する前に、層 1 0 4 に最初に埋設することによって形成することができる。インプラントが、十分に浅い場合、層 1 0 6 内に、また、層 1 0 6 が成長するにつれてさらに層 1 0 4 内に拡散することになる。

10

【 0 0 3 2 】

領域 1 2 0 は、層 1 0 4 のドーピングと同じドーピング型 ( n 型 ) とすることができる。A P D 1 2 8 では、領域 1 2 0 が電界を整形したため、増倍領域は、領域 1 1 0 および領域 1 2 0 の接合に集中する場合がある。

【 0 0 3 3 】

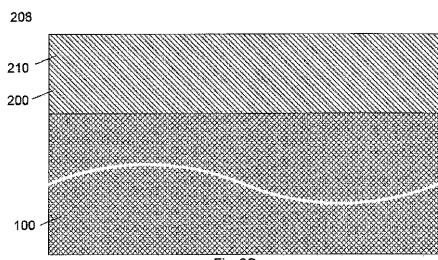

図 2 A ~ 2 D は、別の例示的なプロセスによる A P D の第 2 の実施形態におけるいくつかの早期ステージを示す。第 5 の実施形態は、第 1 の実施形態のエピタキシャル層 1 0 2 ( 図 1 B ) が第 5 の実施形態において共に 2 つのウェハを接合することによって形成されることを除いて第 1 の実施形態と同様である。

20

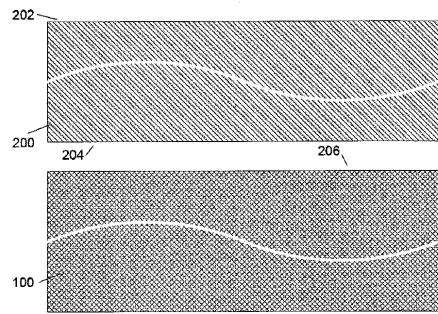

【 0 0 3 4 】

特に、図 2 A は、2 つのウェハ 2 0 0 および 1 0 0 を示す。ウェハ 1 0 0 は、図 1 A および第 1 の実施形態に関して述べた同じウェハ 1 0 0 とすることができます。ウェハ 2 0 0 は、ウェハ 1 0 0 と同じドーピングタイプ ( n 型 ) のウェハとすることができます、約 5 0 ~ 5 0 0 - c m の抵抗率を有する。ウェハ 2 0 0 は、上部露出表面 2 0 2 および下部露出表面 2 0 4 を有する。ウェハ 1 0 0 は上部露出表面 2 0 6 を有する。

【 0 0 3 5 】

図 2 B は、ウェハボンディングプロセスがウェハ 1 0 0 の表面 2 0 6 をウェハ 2 0 0 の表面 2 0 4 に接合した後にウェハ 2 0 0 および 1 0 0 で作られる接合済みウェハ 2 0 8 を示す。ウェハボンディングプロセスは、たとえば熱および印加電圧と共にウェハの一方で非水素化中間層を使用して、2 つのウェハ間に永久的接合部を生成することができます。ウェハボンディングプロセスのさらなる説明は、米国特許第 7,192,841 号において入手可能であり、その特許は、全ての目的のために、参照によりその全体が本明細書に組込まれる。

30

【 0 0 3 6 】

図 2 C は、化学機械的研磨 (chemical-mechanical polishing) ( C M P ) 、エッチバック、または C M P とエッチバックの両方の組合せなどの薄化技法を通して、ウェハ 2 0 0 が 1 0 ~ 7 0  $\mu$ m の厚さまで薄化された後の接合済みウェハ 2 0 8 を示す。上部露出表面 2 0 2 ( 図 2 B ) は、薄化プロセスにおいて除去された。ウェハ 2 0 0 を薄化することによって、層 2 1 0 が形成され、層 2 1 0 は、第 1 の実施形態の層 1 0 2 ( 図 1 B ) に対する類似層である。

40

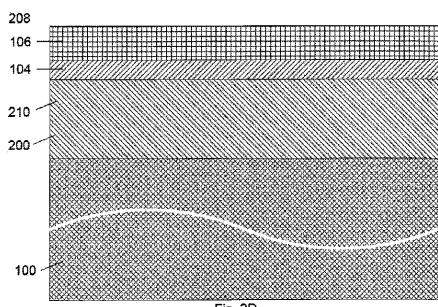

【 0 0 3 7 】

図 2 D は、層 2 1 0 上にエピタキシャル層 1 0 4 および 1 0 6 が成長した後の接合済みウェハ 2 0 8 を示す。層 1 0 4 および 1 0 6 は、上記図 1 B に関して述べた同じ層とすることができます。図 2 D に示すステージ後、接合済みウェハ 2 0 8 の処理は、図 1 C ~ 1 E または図 2 に関して先に説明したように継続することができる。

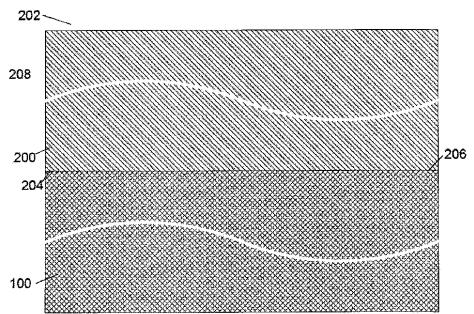

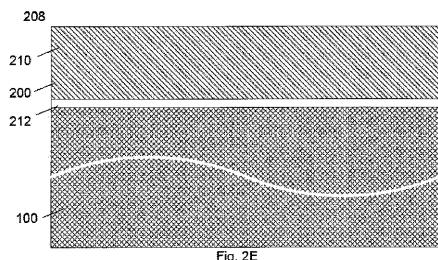

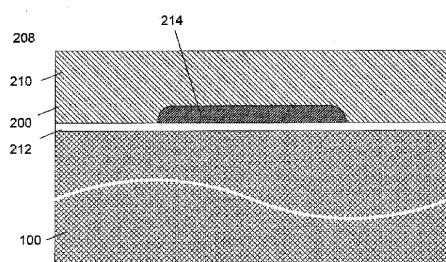

【 0 0 3 8 】

図 2 E および図 2 F は、図 2 A および図 2 B に関して述べた接合式ウェハプロセスに適用することができるオプションの変形を示す。特に、図 2 E は、ウェハを共に接合する前にウェハ 2 0 0 またはウェハ 1 0 0 の表面上にあることができる絶縁層 2 1 2 を示す。絶

50

縁層 212 の付加は、第 5 の実施形態を使用する A P D のアレイのクロストーク性能を改善することができる。A P D のアレイは、図 6 および図 7 に関して以下で論じられる。絶縁層 212 は、たとえば二酸化シリコンとすることができます。図 2 F は、ウェハ 200 内で形成されるインプラント領域 214 に加えて、絶縁層 212 を有する接合済みウェハ 208 を示す。インプラント領域 214 は、第 5 の実施形態のアレイが使用されるときに個々の A P D に対する背面接觸を可能にすることができる。A P D のアレイは、図 6 および図 7 に関して以下で論じられる。インプラント領域 214 の形成は、図 3 A ~ 3 F およびインプラント領域 306 に関して以下で論じられる。インプラント領域 214 を使用することによって、図 3 F および図 4 に関して以下で述べる背面接觸スキームは、図 1 E に関して先にまた図 5 に関して以下で述べた接觸スキームに対する代替法として使用することができる。

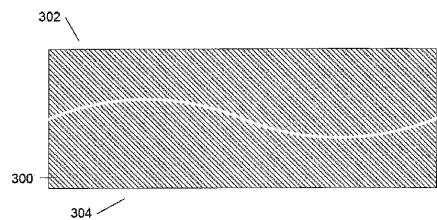

#### 【 0039 】

図 3 A ~ 3 F は、別の例示的なプロセスによる A P D の第 3 の実施形態の作製における種々のステージを示す。この例示的なプロセスは、図 3 A のウェハ 300 を開始材料として設けることによって始まる。ウェハ 300 は、第 3 の実施形態では、大多数の吸収領域を形成することができる。ウェハ 300 は、約  $450 \mu\text{m}$  厚であり、n 型ドーピングを有することができ、約  $10 \sim 500 \text{ cm}^{-3}$  の抵抗率または約  $10^{13} \text{ cm}^{-3} \sim 10^{16} \text{ cm}^{-3}$  のドーピング濃度をもたらす。ウェハ 300 はまた、前面 302 および背面 304 を有する。増倍領域および吸収領域がウェハ 300 内に形成されることになるため、高品質ウェハ（たとえば、フロートゾーンシリコンウェハ）が望ましい場合がある。

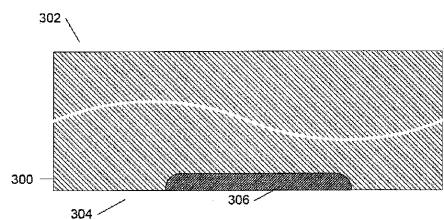

#### 【 0040 】

図 3 B は、インプラント領域 306 が背面 304 上に埋設された後のウェハ 300 を示す。インプラント領域 306 は、同じドーピング型（n 型）であるが、ウェハ 300 と比較してより高い濃度であることになる。たとえば、インプラント領域 306 は、 $10^{16} \text{ cm}^{-3} \sim 10^{19} \text{ cm}^{-3}$  のピーカドーピングを有することができる。

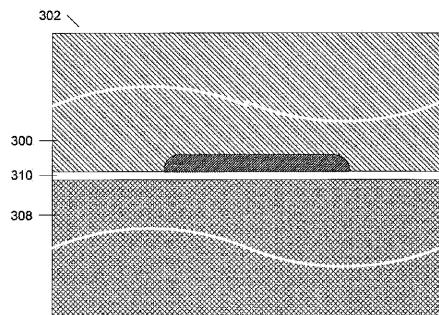

#### 【 0041 】

図 3 C は、ハンドルウェハ 308 がウェハ 300 の背面 304 に接合された後のウェハ 300 を示す。絶縁層 310 は、ウェハ 300 とハンドルウェハ 308 との間にあるとすることができる。絶縁層 310 は、たとえば二酸化シリコンとすることができます。ウェハ 300 およびハンドルウェハ 308 は、よく知られているウェハボンディング技法を使用して共に接合することができる。

#### 【 0042 】

図 3 D は、ウェハ 300 が約  $85 \mu\text{m}$  まで薄化された後のウェハ 300 を示すが、ウェハ 300 は、約  $10 \sim 90 \mu\text{m}$  の厚さまで薄化することができる。ウェハ 300 をハンドルウェハ 308 に最初に接合することによって、薄化される脆いウェハを処理する困難を回避することができる。ウェハ 300 を、研削、化学機械的研磨（C M P）、エッチバッケ、またはこれらの技法の組合せなどの従来の薄化技法によって薄化することができる。前表面 311 を高品質シリコン表面に戻すさらなる処理が必要とされる場合がある。たとえば、前表面 311 の熱酸化は、薄化プロセスによって損傷を受ける任意のシリコンを消費することができる。

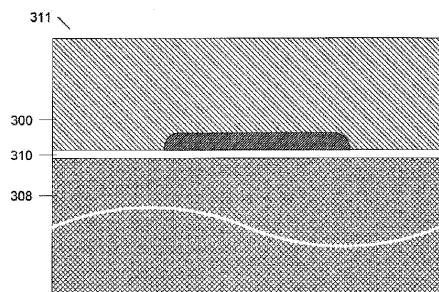

#### 【 0043 】

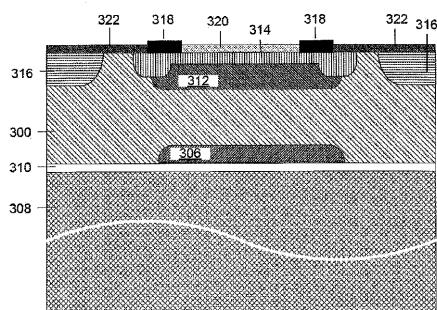

図 3 E は、いくつかのさらなるプロセスステップ後のウェハ 300 を示す。領域 312 は、ウェハ 300 と同じ型（n 型）のドーピングを注入される。領域 312 は、領域 312 および 314 によって形成される p - n 接合にある増倍領域内で電界を整形するのを助ける。領域 314 は、ウェハ 300 と反対のドーピング型（p 型）を注入される。領域 314 は、図 1 C に関して先に論じた領域 110 と同様である。領域 314 は、領域 312 および 314 によって形成される p - n 接合の上部領域を形成する。上部領域は、ウェハ 300 の表面に隣接する。チャネル停止領域 316 は、図 1 C に関して上述したチャネル停止領域 108 と同様とすることができます。アノード電極 318、反射防止層 320、および絶縁層 322 は、図 1 E のアノード電極 118、反射防止層 114、および絶縁層 1

10

20

30

40

50

16と同様とすることができる。

【0044】

図3Eに示す構造に対する代替として、第3の実施形態は、ウェハ300とハンドルウェハ308との間に酸化物層310が存在していれば、カソード電極120(図1E)が省略されることを除いて、図1B~1Eに関して上述したように図3Dに示すウェハ300を処理することによって処理されうる。

【0045】

図3Eにおいて付加される特徴部が、インプラント領域306におおまかに整列されるため、領域312と314との間に形成されるp-n接合がインプラント領域306にオーバラップすることに留意されたい。増倍領域および他の特徴部がウェハ300内にまたウェハ300上にどのように形成されるかによらず、これらの特徴部をインプラント領域306に整列させるための何らかの方法が存在しなければならない。たとえば、アライメントは、ウェハ300を薄化する前に、ハンドルウェハ308に対して背面アライメントマークを付加することによって達成することができる。他のアライメントスキームを、同様に使用することができる。

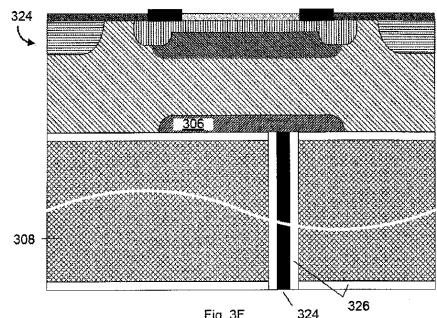

【0046】

図3Fは、APDの第3の実施形態324を示す。p-n接合のカソードは、インプラント領域306に接触するように、ハンドルウェハ308を貫通して形成されるビア324を通して接触されることができる。深掘り反応性イオンエッティング(deep reactive-ion etching) (DRIE) プロセスは、ビア324用の穴をエッティングするために使用することができる。その後、穴は、ビアを形成するために金属プラグで穴を充填する前に酸化物326で内張りされる。

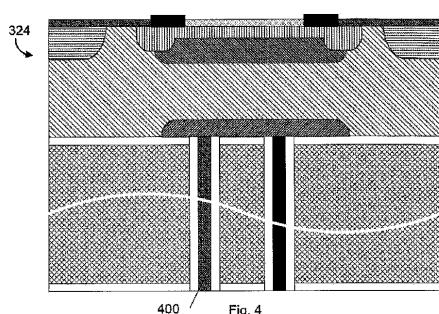

【0047】

図4は、オプションの背面ビア400を付加する第3の実施形態を示す。ビア400は、高抵抗率材料を充填されて、受動クエンチとして働くかまたは低抵抗率材料を充填されて、能動クエンチを可能にすることができます。

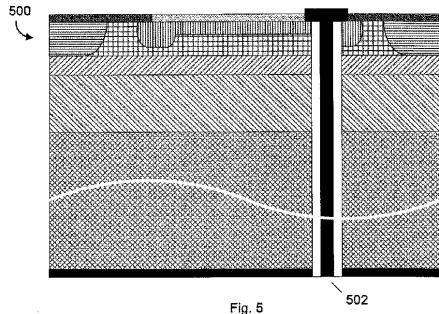

【0048】

図5は、前面アノードを有する代わりに、アノード電極がビア502を通してp-n接合のアノードに接触することができることを除いて、第1の実施形態と同様の構造を有するAPDに対する背面接点を付加する第4の実施形態500を示す。そして、カソード電極を、ハンドルウェハ308の背面に形成することができる。第4の実施形態の背面ビアを、同様にAPDの他の実施形態と共に使用することができる。たとえば、図5に示す背面ビアを使用することは、接合済みウェハ間の絶縁層が使用されていない場合、第3の実施形態に関して特に有用である場合がある。

【0049】

APDの第3の実施形態は、APDのアレイにおいて特に有用である場合がある。通常、APDアレイでは、いつ各APDが、他のAPDと独立して光子を吸収するかを検出することができる。これは、アレイ内の各APDが、そのAPDが光子を吸収したときを決定することを外部回路が可能にする少なくとも1つの検出ラインを有することを必要とする。アレイが多数のAPDを有する場合、これらのラインは、アレイの表面積のかなりの部分を占める場合がある。これらのラインをアレイの背面に移動させることによって、アレイは、より小さくなるかまたはAPDが光子を収集するために利用可能な多くのエリアを有する場合がある。図3Fまたは図4に示す第3の実施形態あるいは図5に示す第4の実施形態は、背面ラインを有するアレイに特に適する。その理由は、共通の背面接点を有する図1Eおよび図2の第1および第2の実施形態と対照的に、各APDが自分自身の個々の背面接点を有することになるからである。

【0050】

図6は、アノード電極、絶縁層、および反射防止層が、例示を明確にするために表面から省略されたことを除いて、第3の実施形態と同様の構造を有するAPDの5×5アレイ600の平面図を示す。各APDは、増倍領域を画定するのを助ける領域114によって

10

20

30

40

50

画定される。上から見た図はまた、ウェハ 100 (図 1A) のドーピングによって規定されるドーピングレベルを有する領域である領域 602 を示す。チャネル停止領域 116 もまた示される。図 7 は、切断ライン 604 (図 6) を通る  $5 \times 5$  アレイ 600 の断面図である。 $100 \times 100$  又はそれ以上のアレイもまた可能である。各 A P D は、離散的埋め込みインプラント領域 706、708、および 710 にそれぞれ垂直にオーバラップする離散的 p-n 接合 700、702、および 704 を有する。

【図 1 A】

Fig. 1A

【図 1 C】

Fig. 1C

【図 1 B】

Fig. 1B

【図 1 D】

Fig. 1D

【図 1 E】

Fig. 1E

【図 1 F】

Fig. 1F

【図 2 A】

Fig. 2A

【図 2 B】

Fig. 2B

【図 2 C】

Fig. 2C

【図 2 E】

Fig. 2E

【図 2 D】

Fig. 2D

【図 2 F】

Fig. 2F

【図3A】

Fig. 3A

【図3B】

Fig. 3B

【図3C】

Fig. 3C

【図3D】

Fig. 3D

【図3E】

Fig. 3E

【図3F】

Fig. 3F

324

326

【図4】

Fig. 4

【図5】

Fig. 5

502

【図6】

Fig. 6

【図7】

Fig. 7

---

フロントページの続き

(72)発明者 クチュール, マーティン

カナダ国, ケベック州 ジェー-7ブイ 9ピ-2, ボードレール-ドリオン, リュ デ マラーズ

2187

審査官 清水 靖記

(56)参考文献 特開平07-221341 (JP, A)

特開昭56-069876 (JP, A)

特開平07-038140 (JP, A)

特開昭49-051886 (JP, A)

実開昭56-016960 (JP, U)

特開昭58-114470 (JP, A)

特開2010-226074 (JP, A)

特開平09-148618 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L31/10