(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

26 January 2012 (26.01.2012)

(10) International Publication Number

WO 2012/012456 A1

(51) International Patent Classification:

H02M 3/156 (2006.01)

(21) International Application Number:

PCT/US2011/044572

(22) International Filing Date:

19 July 2011 (19.07.2011)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

12/841,608 22 July 2010 (22.07.2010) US

(71) Applicant (for all designated States except US): MO-

BIUS POWER, LLC [US/US]; 15260 Ventura Blvd.,

20th Floor, Sherman Oaks, CA 91403 (US).

(72) Inventor; and

(75) Inventor/Applicant (for US only): MCCUNE, Earl, W.,

Jr. [US/US]; 2383 Pruneridge Ave., Suite 3, Santa Clara,

CA 95050 (US).

(74) Agent: SIRITZKY, Brian; Davidson Berquist Jackson &

Gowdey, LLP, 4300 Wilson Blvd., 7th Floor, Arlington,

VA 22203 (US).

(81) Designated States (unless otherwise indicated, for every

kind of national protection available): AE, AG, AL, AM,

AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ,

CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO,

DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT,

HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP,

KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD,

ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NL,

NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD,

SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR,

TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every

kind of regional protection available): ARIPO (BW, GH,

GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG,

ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ,

TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK,

EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU,

LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK,

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ,

GW, ML, MR, NE, SN, TD, TG).

Declarations under Rule 4.17:

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

Published:

- with international search report (Art. 21(3))

(54) Title: AC/DC POWER CONVERSION METHODS AND APPARATUS

FIG. 9

(57) Abstract: An AC/DC converter that converts an AC input voltage Vin to a DC output voltage comprises an inductor, a capacitor selectively coupled to the inductor, a plurality of switches, and a controller. The controller configures the plurality of switches, inductor, and capacitor to operate as a buck converter during times when Vin > Vout and to operate as an inverting buck converter during times when Vin < -Vout. The controller modulates the duty cycles of the plurality of switches to regulate the DC output voltage Vout to the desired, constant output level.

## AC/DC Power Conversion Methods and Apparatus

### FIELD OF THE INVENTION

**[0001]** The present invention relates in general to power conversion and in particular to methods and apparatus for converting alternating current (AC) to direct current (DC).

### BACKGROUND OF THE INVENTION

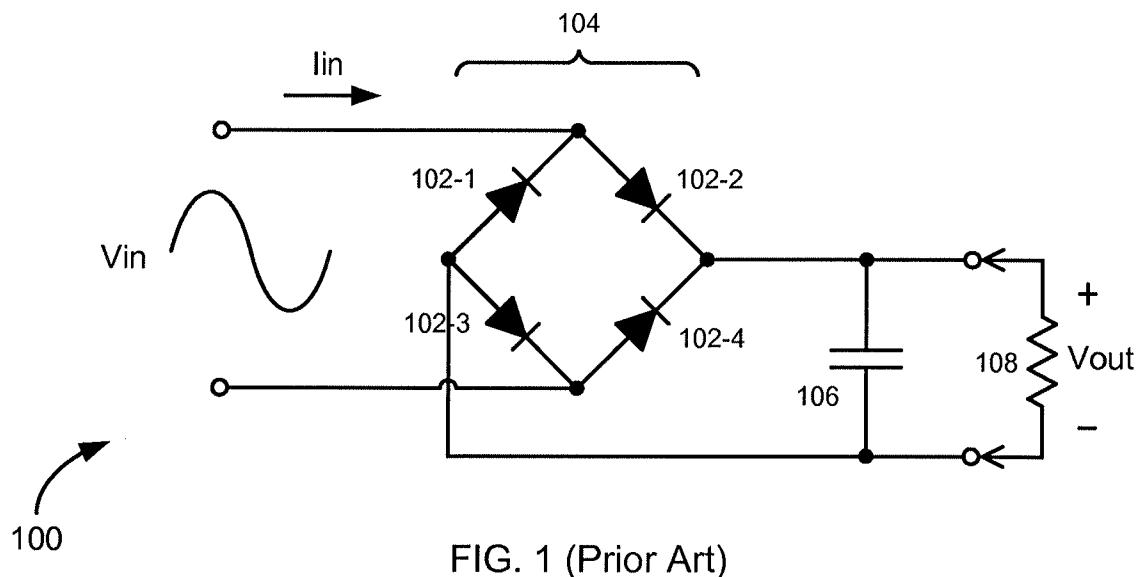

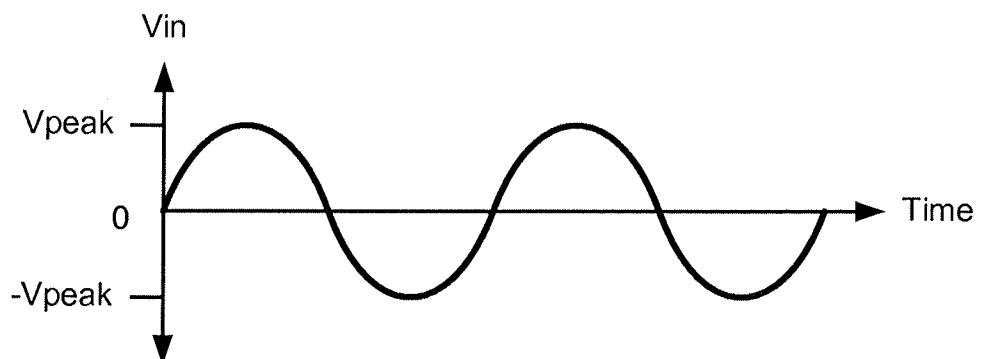

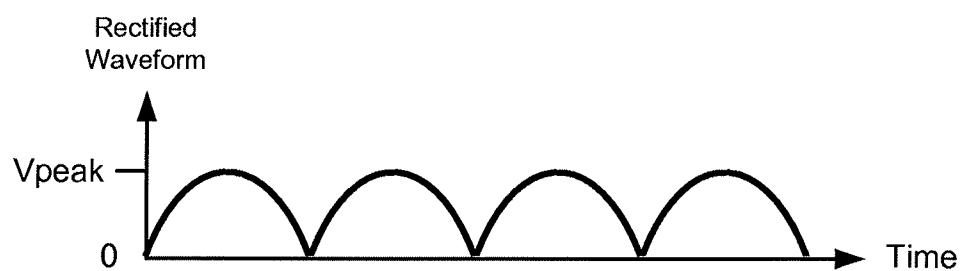

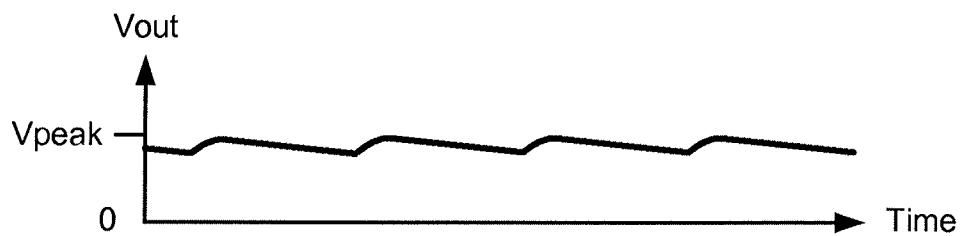

**[0002]** Many household and industrial machines and devices are powered by a direct current (DC) power source that has been rectified from alternating current (AC) power provided by the AC mains. The AC-to-DC rectification is typically accomplished using a bridge rectifier 104 (or “diode bridge”) comprised of four diodes 102-1, 102-2, 102-3 102-4 configured as shown in FIG. 1. The bridge rectifier 104 converts the positive and negative half cycles of the AC input voltage  $V_{in}$  to a full-wave-rectified waveform of constant polarity. (See FIGS. 2A and 2B). To produce the desired steady DC output voltage  $V_{out}$  across a load 108, the rectified waveform is filtered by a smoothing circuit, which in its simplest form comprises a smoothing capacitor 106 coupled to the output of the bridge rectifier 104. The smoothing capacitor 106 functions to maintain the DC output voltage  $V_{out}$  near the peak voltage  $V_{peak}$  during the low portions of the AC input voltage  $V_{in}$ , as shown in FIG. 2C. Some amount of AC ripple is superimposed on the DC output  $V_{out}$ , even following filtering by the smoothing capacitor 106. The ripple may or may not be tolerable, depending on the application. In applications where it is not tolerable, additional filtering can be employed to reduce it to an acceptable level.

**[0003]** The AC/DC converter 100 in FIG. 1 generates a DC output voltage  $V_{out}$

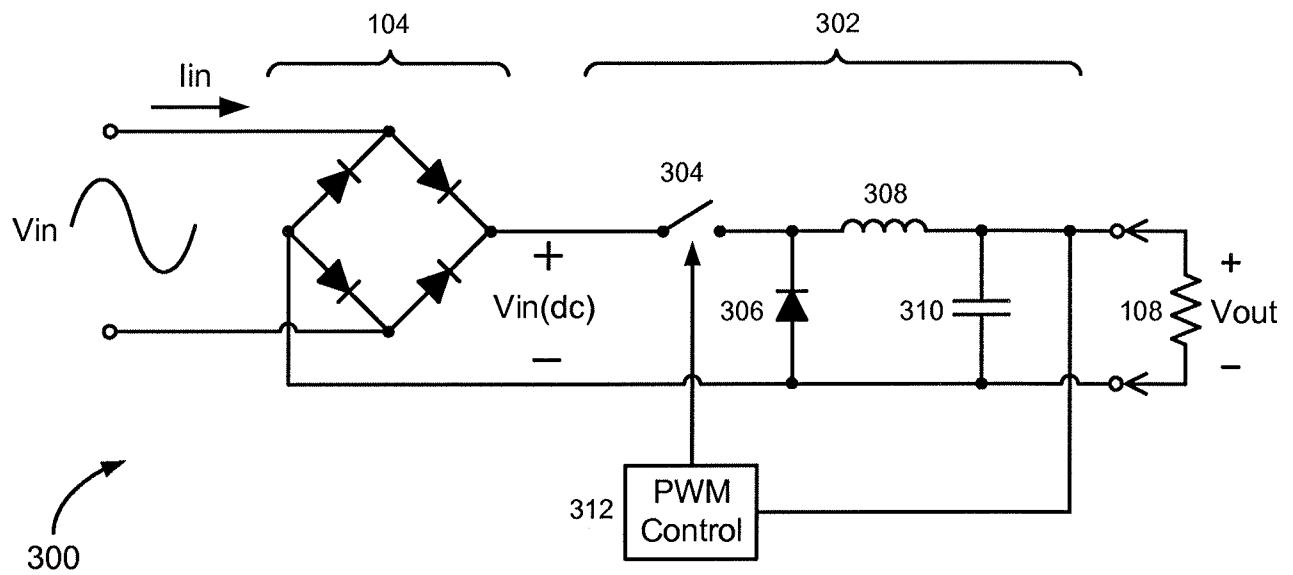

near the peak voltage  $V_{peak}$  of the AC input voltage  $V_{in}$  (see FIG. 2C). However, many applications require a much lower voltage. For example, many machines and devices require a DC voltage of 12 volts DC or less but the peak voltage  $V_{peak}$  of the center-tapped 120 volts RMS (root mean square) residential mains is near 170 V. To 5 lower the DC voltage to the required level, a step-down transformer or DC-DC converter 302 (i.e., “buck converter”) is used. FIG. 3 illustrates use of a DC-DC converter 302. The DC-DC converter 302 comprises a switch (typically a metal-oxide-semiconductor field effect transistor (MOSFET)) 304, a diode (or, alternatively, a second MOSFET) 306, an inductor 308, a filter capacitor 310, and a pulse-width 10 modulator (PWM) control 312. The PWM control 312 controls the opening and closing of the switch 304 at a fixed frequency  $f$  that is much higher than the 60 Hz line frequency (typically greater than 1 kHz). When the switch 304 is turned on, current flows through it, the inductor 308, and then into the filter capacitor 310 and the load 108. The increasing current causes the magnetic field of the inductor 308 to build up 15 and energy to be stored in the inductor’s magnetic field. When the switch 304 is turned off, the voltage drop across the inductor 308 quickly reverses polarity and the energy stored by the inductor 308 is used as a current source for the load 108. The DC output voltage  $V_{out}$  is determined by the proportion of time the switch 304 is on (t<sub>ON</sub>) in each period T, where  $T = 1/f$ . More specifically,  $V_{out} = D V_{in(dc)}$ , where 20 D = t<sub>ON</sub>/T is known as the “duty cycle” and  $V_{in(dc)}$  is the source DC input voltage provided at the output of the bridge rectifier 104. The PWM control 312 is configured in a feed back path, allowing it to regulate the DC output voltage  $V_{out}$  by modulating the duty cycle D.

**[0004]** Although the AC/DC converter 300 in FIG. 3 addresses the inability of the

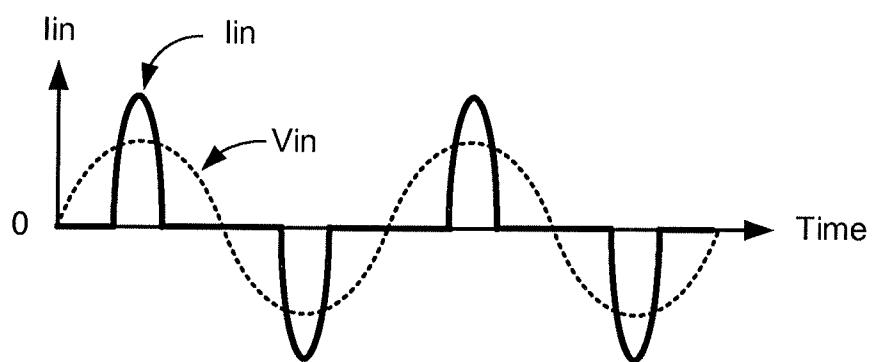

AC/DC converter 100 in FIG. 1 to step down the DC voltage to a lower DC voltage, it does not address another well-known problem of conventional AC/DC converters – low power factor. The power factor of an AC/DC converter is a dimensionless number between 0 and 1 indicating how effectively real power from an AC power source is transferred to a load. An AC/DC converter with a low power factor draws more current from the mains than one having a high power factor for the same amount of useful power transferred. A low power factor can result due to the input voltage  $V_{in}$  being out of phase with the input current  $I_{in}$  or by action of a nonlinear load distorting the shape of the input current  $I_{in}$ . The latter situation arises in non-power-factor-corrected AC/DC converters, such as those described in FIGS. 1 and 3, which as described above use a diode bridge 104. The filter capacitor 106 of the AC/DC converter 100 in FIG. 1 (and, similarly, the filter capacitor 310 of the AC/DC converter 300 in FIG. 3) remains charged near the peak voltage  $V_{peak}$  for most of the time. This means that the instantaneous AC line voltage  $V_{in}$  is below the filter capacitor 106 voltage for most of the time. The diodes 102-1, 102-2, 102-3 102-4 of the bridge rectifier 104 therefore conduct only for a small portion of each AC half-cycle, resulting in the input current  $I_{in}$  drawn from the mains being a series of narrow pulses, as illustrated in FIG. 4. Note that although the input current  $I_{in}$  is in phase with the AC input voltage  $V_{in}$ , it is distorted and, therefore, rich in harmonics of the line frequency. The harmonics lower the power factor, resulting in reduced conversion efficiency and undesirable heating in the AC mains generator and distribution systems. The harmonics also create noise that can interfere with the performance of other electronic equipment.

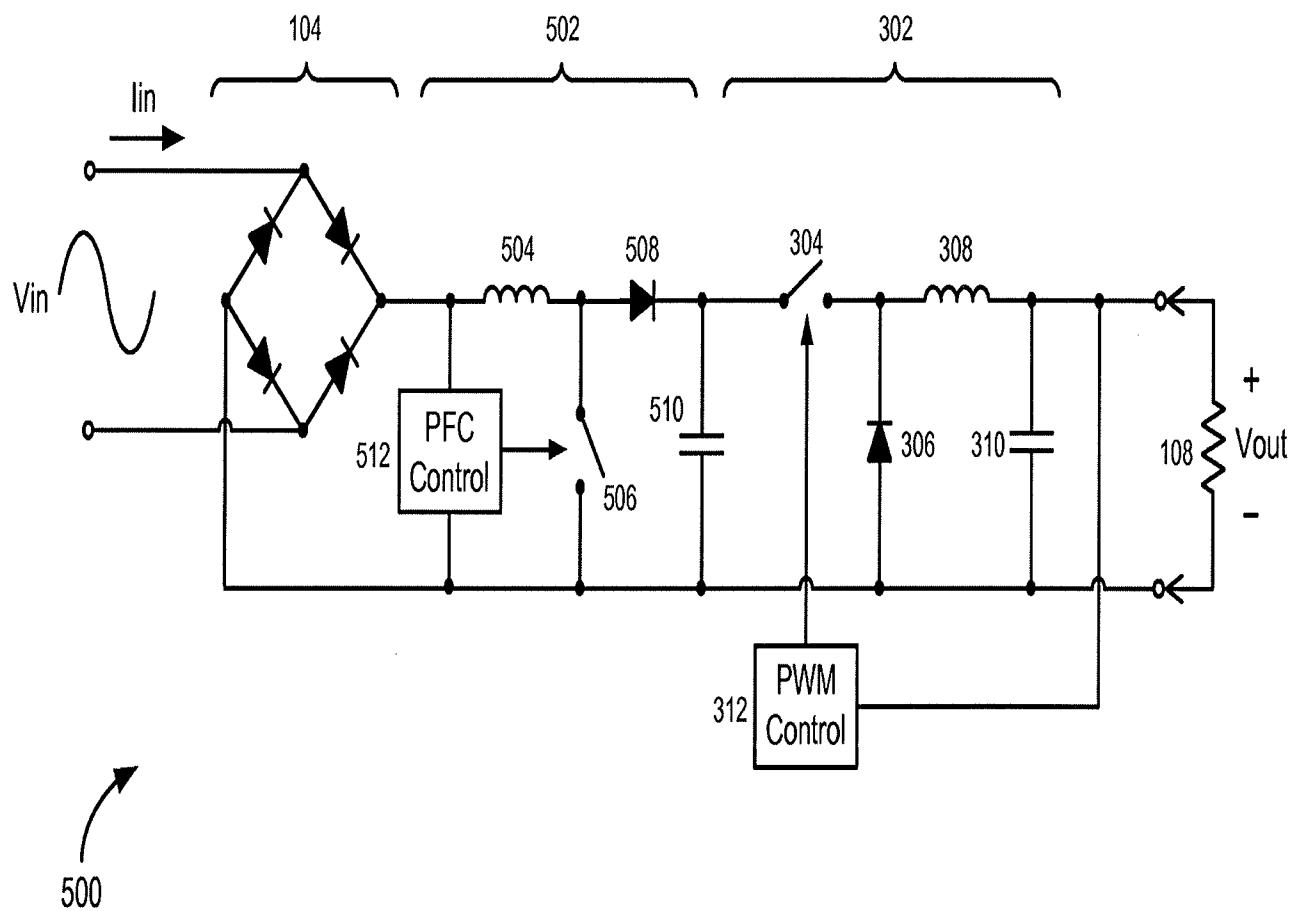

**[0005]** To reduce harmonics and increase the power factor, conventional AC/DC

converters are often equipped with a power factor correction (PFC) pre-regulator.

The PFC pre-regulator can be formed in various ways. One approach employs a PFC boost converter 502 coupled between the bridge rectifier 104 and the DC-DC converter 302, as shown in the power-factor-corrected AC/DC converter 500 in FIG.

- 5 5. The PFC boost converter 502 comprises an inductor 504, switch 506, diode 508, output capacitor 510 and a PFC control 512. The PFC control 512 controls the on and off state of the switch 506. When the switch 506 is switched on, current from the mains flows through the inductor 504, causing energy to build up and be stored in the inductor's magnetic field. During this time, current to the DC-DC converter 302 and

- 10 load 108 is supplied by the charge in the capacitor 510. When the switch 506 is turned off, the voltage across the inductor 504 quickly reverses polarity to oppose any drop in current, and current flows through the inductor 504, the diode 508 and to the DC-DC converter 302, recharging the capacitor 510 as well. With the polarity reversed, the voltage across the inductor 504 adds to the source input DC voltage,

- 15 thereby boosting the input DC voltage. The PFC boost converter 502 output voltage is dependent on the duty cycle D of the on-off switch control signal provided by the PFC control circuit 512. More specifically, the PFC boost converter 502 output voltage is proportional to  $1/(1 - D)$ , where D is the duty cycle and  $(1 - D)$  is the proportion of the switching cycle T (i.e., commutation period) that switch 506 is off.

- 20 In addition to setting the duty cycle D, the PFC control 512 forces the DC-DC converter 302 and load 108 to draw current that on average follows the sinusoidal shape of the AC input voltage  $V_{in}$ , thereby reducing harmonics and increasing the power factor of the AC/DC converter 500.

**[0006]** The power-factor-corrected AC/DC converter 500 is suitable for many

applications. However, it has a number of drawbacks. First, the AC/DC converter is less efficient than desired, particularly since the AC-to-DC power conversion requires two stages – the PFC boost converter 502 front end and the DC-DC converter 302 final stage. Second, the converter 500 has a large parts count, including parts 5 necessary to implement the two control circuits (PFC control 512 and PWM control 312), which increases design complexity and cost, and makes the converter 500 more susceptible to failure. Third, the PFC boost converter 502 generates very high voltages, which stress the converter's parts and raise safety concerns.

**[0007]** It would be desirable, therefore, to have AC/DC conversion methods and 10 apparatus that are efficient at converting AC to DC, avoid power factor degradation attributable to using a bridge rectifier, do not require voltage boosters to counteract power factor degradation, and do not have a large parts count.

## SUMMARY OF THE INVENTION

**[0008]** Methods and apparatus for converting alternating current (AC) to direct 15 current (DC) are disclosed. An exemplary AC/DC converter that converts an AC input voltage  $V_{in}$ , such as may be provided by the AC mains, to a DC output voltage comprises an inductor, a capacitor, a plurality of switches, and a controller. The controller configures the plurality of switches, inductor, and capacitor to operate as a buck converter during times when  $V_{in} > V_{out}$  and to operate as an inverting buck 20 converter during times when  $V_{in} < -V_{out}$ . The controller modulates the duty cycles of the plurality of switches to regulate the DC output voltage  $V_{out}$  to the desired, constant output level.

**[0009]** The AC/DC converter of the present invention converts the AC input

voltage  $V_{in}$  to the DC output voltage  $V_{out}$  directly, i.e., without the need for a bridge rectifier or transformer to complete the AC-to-DC conversion. Direct AC to DC conversion avoids power factor degradation problems attributable to use of bridge rectifiers, obviates the need for specialized power factor correction pre-regulator circuitry, and results in a low parts count and an energy-efficient design.

5 [00010] Further features and advantages of the invention, including descriptions of the structure and operation of the above-summarized and other exemplary embodiments of the invention, will now be described in detail with respect to accompanying drawings, in which like reference numbers are used to indicate 10 identical or functionally similar elements.

#### BRIEF DESCRIPTION OF THE DRAWINGS

15 [00011] FIG. 1 is a circuit diagram of a conventional alternating current to direct current (AC/DC) converter;

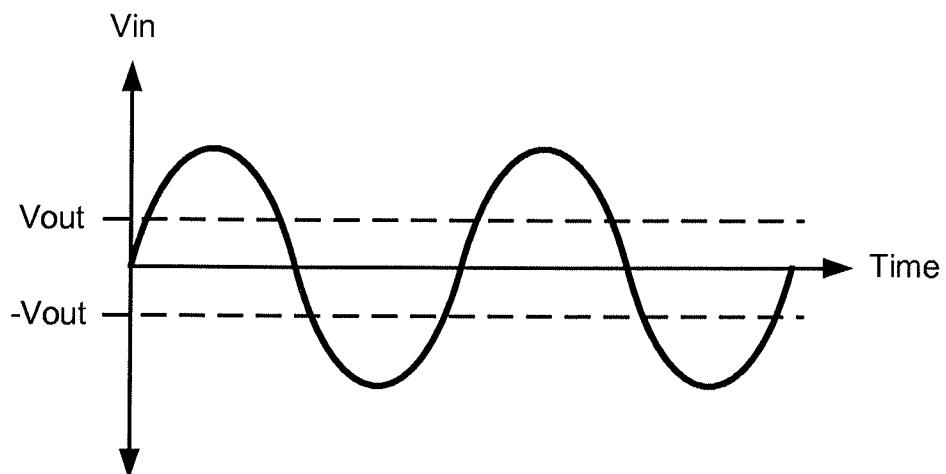

15 [00012] FIG. 2A is a signal diagram of the AC input voltage  $V_{in}$  applied to the AC input of the AC/DC converter in FIG. 1;

15 [00013] FIG. 2B is a signal diagram of the unfiltered, full-wave-rectified voltage waveform produced at the output of the bridge rectifier of the AC/DC converter in FIG. 1;

20 [00014] FIG. 2C is a signal diagram of the DC output voltage of the AC/DC converter in FIG. 1 after having been filtered by a smoothing capacitor;

15 [00015] FIG. 3 is a circuit diagram of an AC/DC converter equipped with a step-down buck converter to step down the DC output voltage to a level lower than

possible using just a bridge rectifier and smoothing capacitor;

**[00016]** FIG. 4 is a signal diagram illustrating how the bridge rectifier used by the AC/DC converters in FIGS. 1 and 3 causes current to be drawn from the AC power source in narrow pulses that are rich in harmonics;

5 **[00017]** FIG. 5 is a circuit diagram of an AC/DC converter having a step-down buck converter and a power-factor-correcting boost converter that compensates for power factor degradation caused by the AC/DC converter's bridge rectifier;

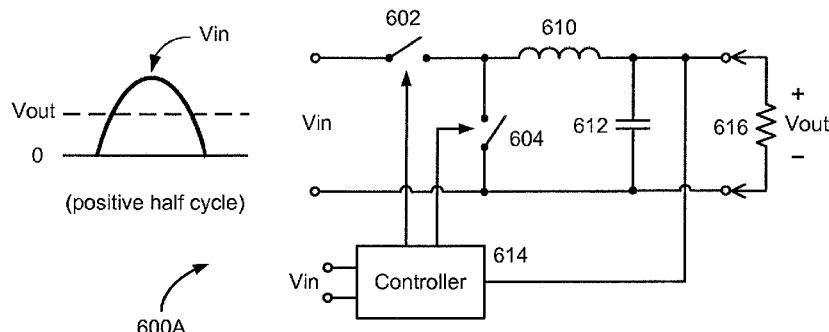

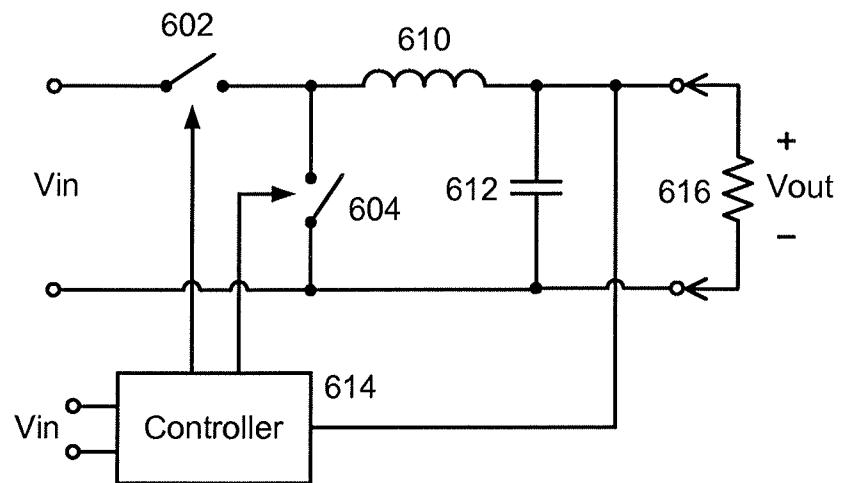

**[00018]** FIG. 6 is a circuit diagram of an AC/DC converter, according to an embodiment of the present invention;

10 **[00019]** FIG. 7 is a signal diagram of the AC input voltage  $V_{in}$  supplied to the AC/DC converter in FIG. 6 and its relationship to the DC output voltage  $V_{out}$  generated by the AC/DC converter and its inverse  $-V_{out}$ ;

15 **[00020]** FIG. 8 is a table showing how the switches of the AC/DC converter in FIG. 6 are switched and driven, depending on the instantaneous value of the AC input voltage  $V_{in}$  compared to the DC output voltage  $V_{out}$  generated by the AC/DC converter in FIG. 6 and its inverse  $-V_{out}$ ;

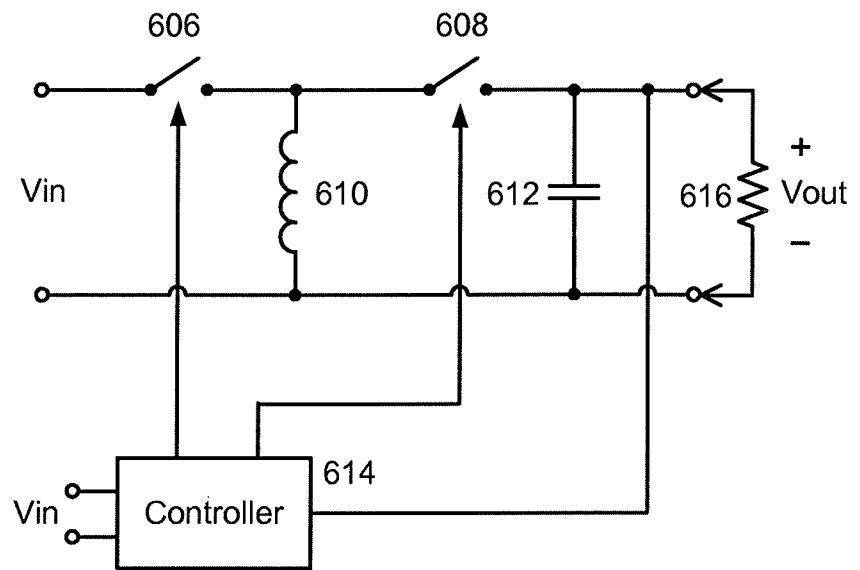

**[00021]** FIG. 9 is a circuit diagram illustrating how the AC/DC converter in FIG. 6 reduces to and operates as a buck converter during times of positive half cycles of the AC input voltage when  $V_{in} > V_{out}$ ;

20 **[00022]** FIG. 10 is a circuit diagram illustrating how the AC/DC converter in FIG. 6 reduces to and operates as an inverting buck converter during times of negative half cycles of the AC input voltage when  $V_{in} < -V_{out}$ ;

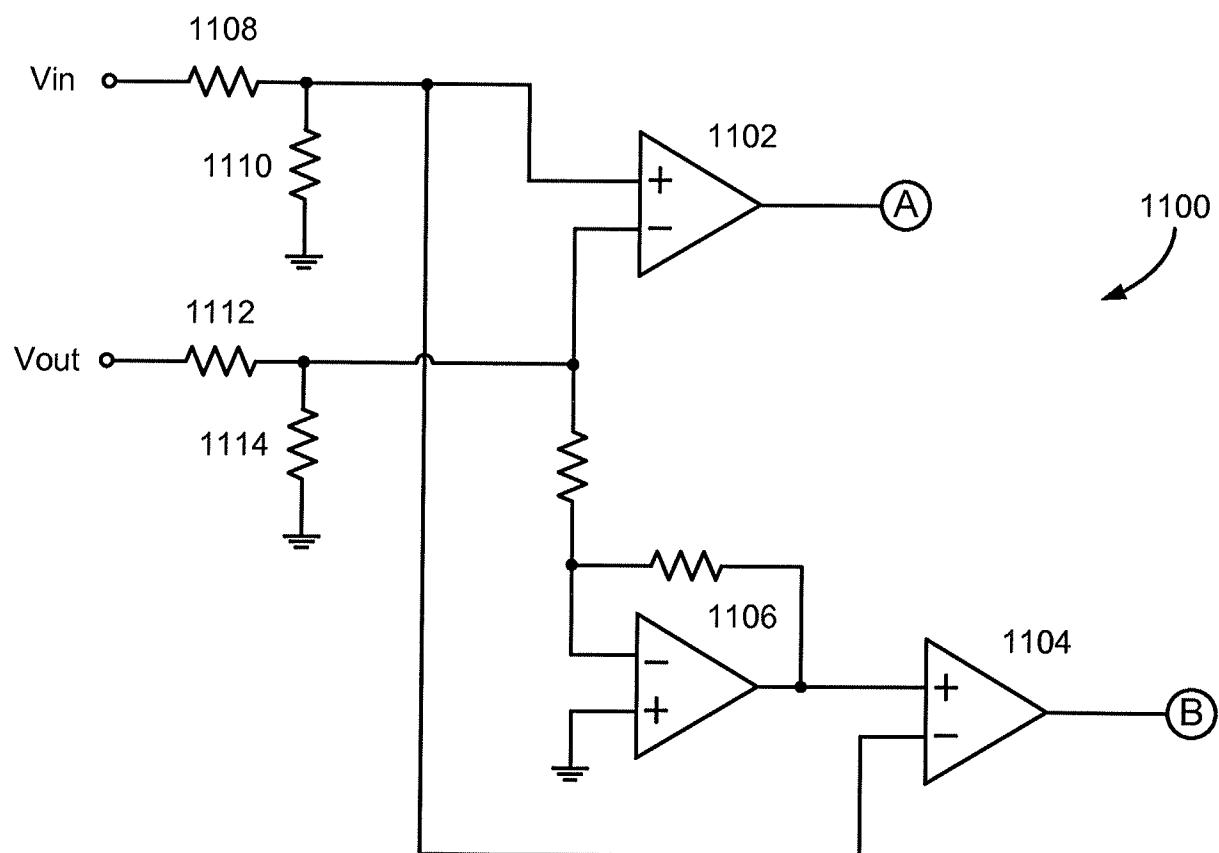

**[00023]** FIG. 11 is a circuit diagram of a comparison circuit that forms part of the controller of the AC/DC converter in FIG. 6 and which compare the AC input voltage  $V_{in}$  to the DC output voltage  $V_{out}$  to determine times whether  $V_{in} > V_{out}$  and  $V_{in} < -V_{out}$ ; and

5 **[00024]** FIG. 12 is a circuit diagram of a switch control circuit that forms part of the controller of the AC/DC converter in FIG. 6 and which operates to control the switching of the switches of the AC/DC converter in FIG. 6.

### DETAILED DESCRIPTION

**[00025]** Referring to FIG. 6, there is shown an alternating current to direct current (AC/DC) converter 600, according to an embodiment of the present invention. The AC/DC converter 600 comprises first, second, third and fourth switches 602, 604, 606 and 608, an inductor 610, a smoothing capacitor 612, and a controller 614. The first switch 602 is coupled between one terminal of the AC input and a first terminal of the inductor 610; the second switch 604 is coupled between the first terminal of the inductor 610 and the opposing-polarity terminal of the AC input; the third switch 606 is coupled between the AC input and the second terminal of the inductor 610; and the fourth switch 608 is coupled between the second terminal of the inductor 610 and the positive DC output terminal. The controller 614 generates switch drive signals for controlling the switching of the first, second, third and fourth switches 602, 604, 606 and 608, depending on the instantaneous AC input voltage  $V_{in}$  compared to the DC output voltage, and selectively modulates the duty cycles of the first, second, third and fourth switches 602, 604, 606 and 608 switches so that the DC output voltage  $V_{out}$  is maintained at the desired level, as is explained in more detail below.

**[00026]** The components of the AC/DC converter 600 comprise discrete devices, one or more integrated circuit (IC) chips, or a combination of discrete devices and IC chips. In one embodiment, the controller 614 and first, second, third, and fourth

5 switches 602, 604, 606 and 608 are integrated in a single IC chip manufactured in accordance with a standard complementary metal-oxide-semiconductor (CMOS) fabrication process, with the first, second, third, and fourth switches 602, 604, 606 and 608 comprising metal-oxide-semiconductor field-effect transistors (MOSFETs).

In another embodiment, the first, second, third, and fourth switches 602, 604, 606 and 608 are formed in a first IC chip and the controller is formed in a second IC chip.

10 Whereas the first, second, third, and fourth switches 602, 604, 606 and 608 comprise silicon-based MOSFETs in the exemplary embodiment just described, other types of switching devices may be used, including conventional switches, diodes, relays, or other semiconductor-based or non-semiconductor-based switching devices. For

example, in applications requiring fast switching speeds, compound-semiconductor-

15 based transistor devices, such as high electron mobility transistors (HEMTs) or

heterojunction bipolar transistors (HBTs), may be used to implement the first, second, third, and fourth switches 602, 604, 606 and 608 switches, instead of silicon-based

MOSFETs. For the purpose of this disclosure, the term “switch” is used in its

broadest sense to include all of these types of switches and any other suitable

20 switching device. The inductor 610 and capacitor 612 may also be integrated in the

one or more IC chips, or either or both of these devices may be discrete devices

coupled to external pins of the one or more IC chips.

**[00027]** The AC/DC converter 600 is configured to directly convert an AC input voltage  $V_{in}$ , such as may be provided by the AC mains, to a DC output voltage  $V_{out}$ ,

without the need for a diode bridge or a step-down transformer. Direct conversion is accomplished by controlling and modulating the on/off states of the first, second, third, and fourth switches 602, 604, 606 and 608 using the controller 614. More specifically, depending on the instantaneous AC input voltage  $V_{in}$  compared to the 5 DC output voltage  $V_{out}$ , the switches are turned on (closed), turned off (opened), driven by a switch drive signal of duty cycle  $D$ , or driven by a complementary switch drive signal of duty cycle  $(1 - D)$ . The switch drive signal (labeled “D” in FIG. 6) and the complementary switch drive signal (labeled “1-D” in FIG. 6) are periodic (or semi-periodic) and have a common, fixed switching frequency  $f = 1/T$ , where  $T$  is 10 the switching period. As illustrated in the signal diagram in FIG. 7 and shown in the switching table in FIG. 8, when  $V_{in} > V_{out}$ , the first switch 602 is driven by the switch drive signal at a duty cycle  $t_{ON}/T = D$ , the second switch 604 is driven by the complementary switch drive signal at a duty cycle  $(T - t_{ON})/T = (1 - D)$ , the third switch 606 is turned off, and the fourth switch 608 is turned on. When  $V_{in} < -V_{out}$ , 15 the first switch 602 is turned off, the second switch 604 is turned on, the third switch 606 is driven by the switch drive signal at a duty cycle  $D$ , and the fourth switch is driven by the complementary switch drive signal at a duty cycle  $(1 - D)$ . Finally, when  $V_{in}$  is greater than  $-V_{out}$  but less than  $V_{out}$ , i.e. when  $|V_{in}| < V_{out}$ , the first, second, third, and fourth switches 602, 604, 606 and 608 are turned off.

20 **[00028]** The DC output voltage of the AC/DC converter 600 is equal to  $D|V_{in}|$ , where  $|V_{in}|$  is the absolute value of the instantaneous AC input voltage. According to one embodiment, the controller 614 modulates the duty cycle  $D$ , regulating the DC output voltage  $V_{out}$  so that it is maintained at a constant level. The duty cycle  $D$  may also be managed to improve the power factor of the AC/DC converter 600. Whereas

D is modulated to maintain the DC output voltage Vout at a constant level in the exemplary embodiment described here, in general Vout, D, and Vin are all variables. Accordingly, Vout need not necessarily be maintained at a constant level.

**[00029]** That  $V_{out} = D|V_{in}|$  is more readily apparent by understanding that the

5 AC/DC converter 600 comprises an integrated (i.e., conjoined) buck converter and an inverting buck converter. During the positive half cycles of the AC input waveform when  $V_{in} > V_{out}$ , the third switch 606 is off, the fourth switch 608 is on, and the AC/DC converter 600 reduces to and operates as a buck converter 600A, as illustrated in FIG. 9. The first and second switches 602 and 604 serve as the high-side and low-side switches of the buck converter and are driven by the switch drive signal at duty cycle D and complementary switch drive signal at a duty cycle (1 - D), respectively. The first and second switches 602 and 604 therefore alternately configure the inductor 610 between storing energy and supplying current during positive half cycles of the AC input voltage when  $V_{in} > V_{out}$ , and the DC output voltage  $V_{out} = DV_{in}$ .

10

**[00030]** During the negative half cycles of the AC input waveform when

15  $V_{in} < -V_{out}$ , the first switch 602 is off, the second switch 604 is on, and the AC/DC converter 600 reduces to and operates as what may be referred to as an “inverting” buck converter 600B, as illustrated in FIG. 10. The third and fourth switches 606 and 608 are driven by the switch drive signal D and complementary switch drive signal (1-D), respectively. The inverting buck converter 600B inverts the negative input voltage  $V_{in}$ , alternately configuring, by the switching action of the third and fourth switches 606 and 608, the inductor 610 between storing energy and supplying current during the negative half cycles of the AC input voltage when  $V_{in} < -V_{out}$ , to produce an output voltage  $V_{out}$  equal to  $D|V_{in}|$ . Hence, considering both positive and

negative half cycles, the AC/DC converter 600 produces a DC output voltage

$$V_{out} = D|V_{in}|.$$

**[00031]** The controller 614 of the AC/DC converter 600 includes a comparison

circuit that continually compares the AC input voltage  $V_{in}$  to the DC output voltage

5 V<sub>out</sub>, to determine whether  $V_{in} > V_{out}$  or  $V_{in} < -V_{out}$ . FIG. 11 is a drawing of an exemplary comparison circuit 1100 that performs this task. The comparison circuit 1100 comprises first and second comparators 1102 and 1104, an inverting amplifier 1106, a first voltage divider including resistors 1108 and 1110, and a second voltage divider including resistors 1112 and 1114. The first voltage divider scales the AC

10 input voltage down to a scaled AC input voltage  $\alpha V_{in}$  so that the voltage is within the acceptable input voltage range limit of the first comparator 1102. The second voltage divider scales the DC output voltage down by the same amount to produce a scaled DC output voltage  $\alpha V_{out}$ . The first comparator 1102 compares the scaled AC input voltage  $\alpha V_{in}$  to the scaled DC output voltage  $\alpha V_{out}$ , producing a high output voltage when  $V_{in} > V_{out}$  and a low output voltage when  $V_{in} < V_{out}$ . The inverting amplifier 1106 inverts the scaled DC output voltage  $\alpha V_{out}$  to produce a scaled and inverted DC output voltage  $-\alpha V_{out}$ . The second comparator 1104 compares the scaled and inverted DC output voltage  $-\alpha V_{out}$  to the scaled AC input voltage  $\alpha V_{in}$ , producing a high output voltage when  $V_{in} < -V_{out}$  and a low output voltage when  $V_{in} > -V_{out}$ .

15

20 **[00032]** The controller 614 of the AC/DC converter 600 also includes a switch

control circuit 1200, shown in FIG. 12, which controls the switching of the first,

second, third, and fourth switches 602, 604, 606 and 608. The switch control circuit

1200 comprises an error amplifier 1202, a pulse-width modulator (PWM) 1204, and

switches 1206-1216 having on/off states that control the switching of the first, second, third and fourth switches 602, 604, 606 and 608. The error amplifier 1202 compares the DC output voltage  $V_{out}$  to a precise reference voltage  $V_{ref}$  that is equal to and defines the desired DC output voltage  $V_{out}$  and produces an error signal  $\epsilon$  based on

5 the difference between  $V_{ref}$  and  $V_{out}$ . The PWM 1204 generates the aforementioned switch drive signal (labeled “D” in FIG. 12) and complementary switch drive signal (labeled “1-D” in FIG. 12) and modulates D based on the error signal  $\epsilon$ , thereby providing the switch control circuit 1200 the ability to regulate the DC output voltage  $V_{out}$ . The switches 1206-1216 are controlled by the outputs of the first and second comparators 1102 and 1104 of the comparator circuit 1100 in FIG. 11 and control the switching states of the first, second, third and fourth switches 602, 604, 606 and 608, in accordance with the switching table in FIG. 8.

**[00033]** In the exemplary embodiment above, the switch control circuit 1200 is described as controlling the opening and closing of the switches 606, 604, 606 and 608, according to the switching table in FIG. 8. In another embodiment, the controller 614 is alternatively or further configured to hold switch 608 open during light load conditions. (What defines the light load condition is dependent on the application and established and set during design.) The remaining switches 602, 604 and 606 are configured to operate according to the switching table in FIG. 8, or are configured to not switch at all, with no effect on the load 616. Hence, during light load conditions, the capacitor 612 serves as the power supply for the load 616.

**[00034]** While various embodiments of the present invention have been described, they have been presented by way of example and not limitation. It will be apparent to

persons skilled in the relevant art that various changes in form and detail may be made to the exemplary embodiments without departing from the true spirit and scope of the invention. Accordingly, the scope of the invention should not be limited by the specifics of the exemplary embodiments. Rather, the scope of the invention should be 5 determined by the appended claims, including the full scope of equivalents to which such claims are entitled.

**CLAIMS**

What is claimed is:

5

1. An AC/DC converter for converting an AC input voltage  $V_{in}$  to a DC

output voltage  $V_{out}$ , comprising:

an inductor;

first and second switches that, during positive half cycles of the AC input

10 voltage when  $V_{in} > V_{out}$ , alternately configure said inductor between storing energy and supplying current;

third and fourth switches that, during negative half cycles of the AC input voltage when  $V_{in} < -V_{out}$ , alternately configure said inductor between storing energy and supplying current; and

15 a controller configured to control said first, second, third and fourth switches.

2. The AC/DC converter of Claim 1 wherein said controller includes a

comparison circuit configured to compare the AC input voltage  $V_{in}$  to the DC output voltage  $V_{out}$ .

20

3. The AC/DC converter of Claim 2 wherein said controller further

includes a switch control circuit that controls the switching of said first, second, third and fourth switches depending on comparisons of the AC input voltage  $V_{in}$  to the DC output voltage  $V_{out}$ .

25

4. The AC/DC converter of Claim 1 where said controller includes a

switch control circuit that controls the switching of said first, second, third and fourth switches depending on the AC input voltage  $V_{in}$  compared to the DC output voltage  $V_{out}$ .

5. The AC/DC converter of Claim 1 wherein during positive half cycles of the AC input voltage when  $V_{in} > V_{out}$  said controller is configured to switch said first switch on and off at frequency  $f$  and duty cycle D, and is configured to switch said second switch on and off at the frequency  $f$  and duty cycle (1-D).

10. The AC/DC converter of Claim 5 wherein during negative half cycles of the AC input voltage when  $V_{in} < -V_{out}$  said controller is configured to switch said third switch on and off at the frequency  $f$  and duty cycle D, and is configured to switch said fourth switch on and off at the frequency  $f$  and duty cycle (1-D).

15. The AC/DC converter of Claim 6 wherein said controller includes a pulse-width modulator configured to modulate D and regulate the DC output voltage  $V_{out}$ .

20. An AC/DC converter for converting an AC input voltage  $V_{in}$  to a DC output voltage  $V_{out}$ , comprising:

an inductor;

a capacitor selectively coupled to said inductor;

a plurality of switches; and

a controller that configures the plurality of switches, inductor and capacitor to

operate as a buck converter during times when  $V_{in} > V_{out}$ , and configures the plurality of switches, inductor and capacitor to operate as an inverting buck converter during times when  $V_{in} < -V_{out}$ .

5 9. The AC/DC converter of Claim 8 wherein said plurality of switches includes first and second switches that serve as switching transistors of the buck converter during the times when  $V_{in} > V_{out}$ .

10 10. The AC/DC converter of Claim 9 wherein said plurality of switches further includes third and fourth switches that serve as switching transistors of the inverting buck converter configuration during the times when  $V_{in} < -V_{out}$ .

11. The AC/DC converter of Claim 10 wherein said controller is configured to:

15 switch said first and second switches on and off at a common frequency  $f$  and at a duty cycle D and duty cycle (1-D), respectively, during the times when  $V_{in} > V_{out}$ ; and

switch said third and fourth switches on and off at the common frequency  $f$  and at the duty cycle D and duty cycle (1-D), respectively, during the times when

20  $V_{in} < -V_{out}$ .

12. The AC/DC converter of Claim 11 wherein said controller includes a pulse-width modulator configured to regulate the DC output voltage by modulating the duty cycle D of the first and third switches and by modulating the duty cycle (1-D)

of the second and fourth switches.

13. A method of converting an AC input voltage  $V_{in}$  to a DC output voltage  $V_{out}$ , comprising:

5 converting the AC input voltage during positive half cycles to the DC output voltage  $V_{out}$  using a buck converter; and

converting the AC input voltage during negative half cycles to the DC output voltage  $V_{out}$  using an inverting buck converter.

10 14. The method of Claim 13 wherein converting the AC input voltage to the DC output voltage during the positive and negative half cycles are performed by modulating duty cycles of switches of said buck converter and said inverting buck converter.

15 15. The method of Claim 13 wherein converting positive half cycles of the AC input voltage to the DC output voltage  $V_{out}$  using the buck converter comprises: determining times when  $V_{in} > V_{out}$ ; and for times it is determined that  $V_{in} > V_{out}$ , converting the AC input voltage to the DC output voltage  $V_{out}$ .

20

16. The method of Claim 13 wherein converting negative half cycles of the AC input voltage to the DC output voltage  $V_{out}$  using an inverting buck converter comprises:

determining times when  $V_{in} < -V_{out}$ ; and

for times it is determined that  $V_{in} < -V_{out}$ , converting the AC input voltage to the DC output voltage  $V_{out}$ .

17. The AC/DC converter of Claim 13 wherein the buck converter and

5 inverting buck converter comprise a conjoined buck and inverting buck converter circuit that shares a common inductor.

18. An AC/DC converter for converting an AC input voltage  $V_{in}$  to a DC output voltage  $V_{out}$ , comprising:

10 means for determining times when  $V_{in} > V_{out}$  and times when  $V_{in} < -V_{out}$ ;

first converting means for converting the AC input voltage during positive half cycles to the DC output voltage  $V_{out}$  during times when  $V_{in} > V_{out}$ ; and

second converting means for converting the AC input voltage during negative half cycles to the DC output voltage  $V_{out}$  during times when  $V_{in} < -V_{out}$ .

15

19. The AC/DC converter of Claim 18, further comprising means for controlling said first converting means and said second converting means.

20. The AC/DC converter of Claim 19 wherein:

20 said first converting means includes first switching means;

said second converting means includes second switching means; and

said controller is configured to control said first and second switching means to maintain the DC output voltage  $V_{out}$  at a constant level.

21. An AC/DC converter for converting an AC input voltage  $V_{in}$  to a DC output voltage  $V_{out}$ , comprising:

an inductor;

a capacitor; and

5 a plurality of switches configured to selectively couple and decouple said capacitor to and from said inductor to convert the AC input voltage  $V_{in}$  to the DC output voltage  $V_{out}$ .

22. The AC/DC converter of Claim 21 wherein said AC/DC converter is

10 configured to convert the AC input voltage  $V_{in}$  to the DC output voltage  $V_{out}$  without using a bridge rectifier.

23. The AC/DC converter of Claim 21 wherein said AC/DC converter is

configured to step down the AC input voltage to the DC output voltage  $V_{out}$  without

15 using a step-down transformer.

24. The AC/DC converter of Claim 21 wherein said inductor, capacitor, and switches of said plurality of switches are configured as a buck converter during times when  $V_{in} > V_{out}$ .

20

25. The AC/DC converter of Claim 21 wherein said inductor, capacitor, and switches of said plurality of switches are configured as an inverting buck converter during times when  $V_{in} < -V_{out}$ .

26. The AC/DC converter of Claim 21 wherein one or more switches of said plurality of switches is/are configured to isolate said capacitor from said inductor during light load conditions, allowing said capacitor to serve as a power supply for a load during said light load conditions.

FIG. 2A (Prior Art)

FIG. 2B (Prior Art)

FIG. 2C (Prior Art)

FIG. 3 (Prior Art)

FIG. 4 (Prior Art)

FIG. 5 (Prior Art)

FIG. 6

FIG. 7

| Switch | $V_{in} > V_{out}$ | $V_{in} < -V_{out}$ | $ V_{in}  < V_{out}$ |

|--------|--------------------|---------------------|----------------------|

| 602    | D                  | OFF                 | OFF                  |

| 604    | 1-D                | ON                  | OFF                  |

| 606    | OFF                | D                   | OFF                  |

| 608    | ON                 | 1-D                 | OFF                  |

FIG. 8

600A

FIG. 9

600B

FIG. 10

8/10

FIG. 11

FIG. 12

10/10

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US2011/044572

## A. CLASSIFICATION OF SUBJECT MATTER

IPC(8) - H02M 3/156 (2011.01)

USPC - 323/351

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC(8) - H02M 3/156, 7/04; G05F 1/00 (2011.01)

USPC - 323/271, 351; 363/143

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

MicroPatent, Google Patents, Google.com

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.      |

|-----------|------------------------------------------------------------------------------------|----------------------------|

| Y         | US 6,870,355 B2 (IWAHORI) 22 March 2005 (22.03.2005) (entire document)             | 1-26                       |

| Y         | US 2010/0014329 A1 (ZHANG et al) 21 January 2010 (21.01.2010) (entire document)    | 1-12, 14-16, 18-20, 24, 25 |

| Y         | US 6,577,517 B2 (JAIN et al) 10 June 2003 (10.06.2003) entire document             | 7, 12                      |

| Y         | US 6,483,730 B2 (JOHNSON JR) 19 November 2002 (19.11.2002) entire document         | 8-12, 21-26                |

| Y         | US 2009/0303762 A1 (JANG et al) 10 December 2009 (10.12.2009) entire document      | 8-17, 24, 25               |

Further documents are listed in the continuation of Box C.

\* Special categories of cited documents:

|                                                                                                                                                                         |                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| “A” document defining the general state of the art which is not considered to be of particular relevance                                                                | “T” later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| “E” earlier application or patent but published on or after the international filing date                                                                               | “X” document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| “L” document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) | “Y” document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| “O” document referring to an oral disclosure, use, exhibition or other means                                                                                            | “&” document member of the same patent family                                                                                                                                                                                                    |

| “P” document published prior to the international filing date but later than the priority date claimed                                                                  |                                                                                                                                                                                                                                                  |

Date of the actual completion of the international search

02 November 2011

Date of mailing of the international search report

07 NOV 2011

Name and mailing address of the ISA/US

Mail Stop PCT, Attn: ISA/US, Commissioner for Patents

P.O. Box 1450, Alexandria, Virginia 22313-1450

Facsimile No. 571-273-3201

Authorized officer:

Blaine R. Copenheaver

PCT Helpdesk: 571-272-4300

PCT OSP: 571-272-7774