(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4338045号

(P4338045)

(45) 発行日 平成21年9月30日(2009.9.30)

(24) 登録日 平成21年7月10日(2009.7.10)

(51) Int.Cl.

F 1

G 11 C 11/401 (2006.01)

G 11 C 11/34 371 K

G 11 C 11/405 (2006.01)

G 11 C 11/34 352 B

G 11 C 11/4097 (2006.01)

G 11 C 11/34 362 B

請求項の数 1 (全 36 頁)

|            |                                     |           |                                                 |

|------------|-------------------------------------|-----------|-------------------------------------------------|

| (21) 出願番号  | 特願2006-191467 (P2006-191467)        | (73) 特許権者 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区大手町二丁目6番2号 |

| (22) 出願日   | 平成18年7月12日 (2006.7.12)              | (74) 代理人  | 100081938<br>弁理士 德若 光政                          |

| (62) 分割の表示 | 特願2000-101204 (P2000-101204)<br>の分割 | (72) 発明者  | 菅野 雄介<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

| 原出願日       | 平成12年3月31日 (2000.3.31)              | (72) 発明者  | 伊藤 清男<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

| (65) 公開番号  | 特開2006-277938 (P2006-277938A)       |           |                                                 |

| (43) 公開日   | 平成18年10月12日 (2006.10.12)            |           |                                                 |

| 審査請求日      | 平成18年7月13日 (2006.7.13)              |           |                                                 |

|            |                                     | 審査官       | 須原 宏光                                           |

最終頁に続く

(54) 【発明の名称】半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1と第2配線と、第1スイッチと、複数の第1ワード線と、複数の第1メモリセルとを具備する第1メモリブロックと、

第2スイッチと、複数の第2ワード線と、複数の第2メモリセルとを具備する第2メモリブロックとを具備し、

前記複数の第1メモリセルのそれぞれは、第1と第2と第3トランジスタを具備し、前記第1と第2トランジスタのゲートは前記複数の第1ワード線のうちの一つと接続され、前記第3トランジスタのドレインは前記第2トランジスタのソース・ドレイン経路と接続され、

前記複数の第2メモリセルのそれぞれは、第4と第5と第6トランジスタを具備し、前記第4と第5トランジスタのゲートは前記複数の第2ワード線のうちの一つと接続され、前記第6トランジスタのドレインは前記第5トランジスタのソース・ドレイン経路と接続され、前記複数の第1メモリセルの前記第1トランジスタのソース・ドレイン経路は前記第1配線に接続され、

前記複数の第2メモリセルの前記第4トランジスタのソース・ドレイン経路は前記第2配線に接続され、

前記複数の第1メモリセルの前記第2トランジスタのソース・ドレイン経路は前記第1スイッチを介して前記第2配線に接続され、

前記複数の第2メモリセルの前記第5トランジスタのソース・ドレイン経路は前記第2

10

20

スイッチを介して前記第1配線に接続される半導体集積回路。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体集積回路装置に関し、大容量メモリと論理回路を同一チップに搭載する技術に関するものである。

【背景技術】

【0002】

この明細書で参照される文献のリストは以下の通りであり、文献の参照は文献番号をもってすることとする。[文献1]：伊藤清男著「超LSIメモリ」培風館、1996、頁12～15。[文献2]：特開昭62-226494号公報（対応米国特許公報の番号は4803664）。

【非特許文献1】伊藤清男著「超LSIメモリ」培風館、1996、頁12～15

【特許文献1】特開昭62-226494号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

最近、ダイナミック・ランダムアクセス・メモリ（DRAM）と論理回路（ロジック回路）を混載するシステム・オン・チップLSIが、マルチメディア用途で重要となってきている。

今後は、DRAMとスタティック・ランダムアクセス・メモリ（SRAM）とロジック回路、さらにはプロセッサ等を一つのチップ上に混載させることが必要となってきている。このようなシステム・オン・チップLSIにおいて、一つのトランジスタと一つの特殊で大きな容量のキャパシタで構成される現在のDRAMメモリセルでは、キャパシタ形成プロセスが煩雑なため、論理回路（ロジック）と同一のプロセス工程でDRAMを作成することが困難である。このため、低価格化には限界がある。そこでキャパシタを不要とするDRAMメモリセルが必要となる。

【0004】

この候補として、本願発明者等は、例えば[文献1]に示されるようないわゆる3トランジスタセルを再評価することを考え始めた。ここで3トランジスタセルとは、情報電圧をゲートに蓄える蓄積MOSFETと、上記ゲートに情報電圧を書き込む書き込み用MOSFET、さらに上記ゲート電圧の状態を読み出すための読み出し用MOSFETを備えるものである。このような3トランジスタセルは、製造プロセスも論理回路とほぼ同一にできるので作りやすく、低価格にできる可能性がある。またセル自身に増幅機能があるため、データ線に読み出される読み出し信号電圧は大きく動作が安定である。さらに低電圧動作に適するのでマルチメディア用途に好適な低消費電力が実現できるという特徴があることが本願発明者により見いだされた。

【0005】

更に、3トランジスタセルを用いたDRAMは、[文献2]に記載されている。このメモリは、データ線が対線構成になっているので、高速書き込み・読み出しが可能である。しかし、メモリセルの記憶情報をセンスアンプで弁別・増幅するために、各データ対線ごとにダミーセルを用いなければならず、その分だけ面積が増してしまう。また、そこで開示されているダミーセルにも増幅機能があるので、そのデータ線上に現れる参照電圧は時間とともに変化してしまう。したがって、センスアンプの起動タイミングの設定が難しく、場合によってはセンスアンプで読み出し情報が弁別できなくなる。なぜなら、センスアンプの起動タイミングの設定が遅すぎると対線間の差電圧が小さくなり動作が不安定になるからである。

【0006】

そこで、本願発明における第1の目的はダミーセルを用いないメモリを提供することにある。この発明の他の目的は、3トランジスタセルが接続されるグローバルデータ線対の寄生容量平衡することにある。

10

20

30

40

50

**【課題を解決するための手段】****【0007】**

本発明の代表的な例を示せば以下の通りである。即ち、複数の第1メモリセルは、第1と第2トランジスタのゲートが複数の第1ワード線のうちの一つと接続され、第3トランジスタのドレインが前記第2トランジスタのソース・ドレイン経路と接続される。複数の第2メモリセルは、第4と第5トランジスタのゲートが複数の第2ワード線のうちの一つと接続され、第6トランジスタのドレインが前記第5トランジスタのソース・ドレイン経路と接続される。前記第1メモリセルの第1トランジスタのソース・ドレイン経路は第1配線に接続され、前記第2メモリセルの第4トランジスタのソース・ドレイン経路は第2配線に接続される。前記第1メモリセルの第2トランジスタのソース・ドレイン経路は第1スイッチを介して前記第2配線に接続され、前記第2メモリセルの第5トランジスタのソース・ドレイン経路は第2スイッチを介して前記第1配線に接続される。10

**【発明の効果】****【0008】**

グローバルデータ線対の寄生容量を平衡させることができる。

**【発明を実施するための最良の形態】****【0009】****<実施例1>**

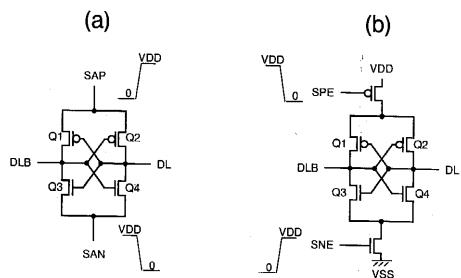

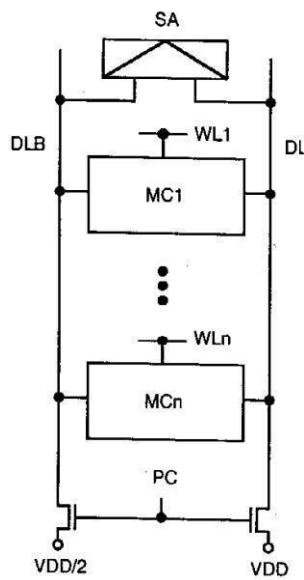

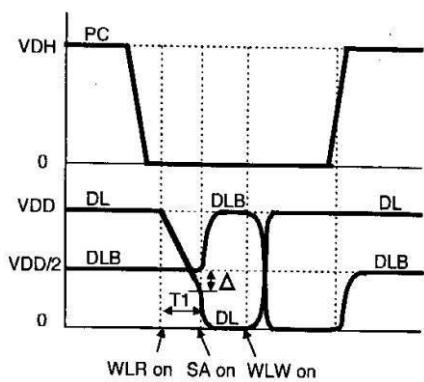

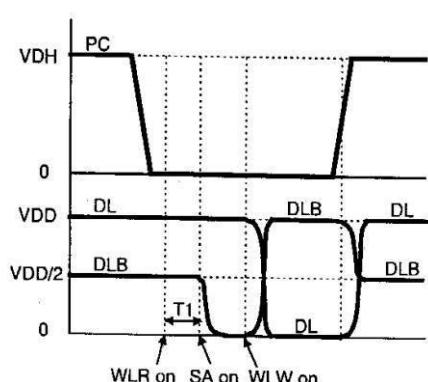

図1(a)は、本発明の概念を示したもので、DRAM内の一対のデータ線の構成と動作タイミングを示している。一対のデータ線(DL、DLB)には複数のメモリセル(MC1～MCn)と、センスアンプ(SA)と、プリチャージ回路が接続されている。メモリセルは、後述するようにゲインセルである。ここでゲインセルとは、例えば後述するようなN型MOSFETを用いる例では、あらかじめ高電位VDDにプリチャージされたデータ線を、メモリセルの記憶情報に応じて選択的に完全に0Vまで放電することができるメモリセルのことである。もちろんP型MOSFETを用いてもよく、その場合は、あらかじめ0Vにプリチャージされたデータ線を、選択的にVDDレベルへ完全に充電することができるメモリセルのことである。データ線は、メモリセルのデータを読出すために利用するデータ線DLと、差動増幅時の参照に用いるデータ線DLBからなる。また、DLBはメモリセルへの記憶データの書き込み用・再書き込み用にも利用する。本発明の特長は、上記対線のそれぞれのプリチャージ電圧を異なる値に設定することにある。すなわちDLのプリチャージ電圧は、例えばN型のゲインセルを用いる場合にはVDDとし、DLBのプリチャージ電圧はそれよりも低い値、例えばVD/2とする。ここでセンスアンプは、例えば図2に示すようなラッチ型のCMOSセンスアンプであり、データ対線間に現れた情報に対応した差動電圧を高速にVDDまで増幅する。センスアンプは、図2(a)では端子SANとSAPに、同図(b)では端子SPEとSNEにそれぞれ0V、VDDの電圧を印加することで起動する。20

30

**【0010】**

以下本発明の基本動作を、N型ゲインセルの場合について図1(b)及び(c)を用いて説明する。メモリセルから記憶情報を読み出すためには、まずプリチャージ回路によってDL、DLBをそれぞれVDD、VDD/2にプリチャージした後に、プリチャージ信号PCをロウレベルにし、その後一本のワード線を選択的に読み出しレベルにする(図中WLR on)。これによりデータ線DLの電位は、メモリセルの記憶情報にしたがって、プリチャージレベルを保つか、0Vに放電するかが決まる。図1(b)は、そのメモリセルがデータ線DLを放電するような記憶情報を保持している場合の波形図である。データ線DLの電圧がVDD/2より(センスアンプの感度)だけ小さくなる時間(T1)の後、センスアンプSAを起動し増幅を開始する(図中SA on)。これによりDLは0VへDLBはVDDへそれぞれ高速に増幅される。これはセンスアンプのオフセット電圧などできまり、ほぼ100mVである。一方、図1(c)は選択されたメモリセルがデータ線DLをプリチャージレベルに保つような記憶情報を保持している場合の波形図である。時間T1の後にセンスアンプを活性化すれば、DLはVDDに、DLBは0Vにそれぞれ高速に増幅される。つまり、ワード線WLを活性化した後、時間T1後にセンスアンプを起動することで、メモリセルの記憶情報を正確に弁別し読み出すことができる。4050

お、図では対線間のプリチャージ電圧の差はVDD/2であるが、この差は 以上であればよい。対線間のプリチャージ電圧の差を とするとT1が短くなるのでより高速に増幅できる。さらに、データ線DLBのプリチャージ電圧をVDD/2ではなく に設定すれば、2値情報に対する対線間の読み出し電圧差は等しくなる。この条件はデータ線DL及びDLBのプリチャージ電圧の最小値を与え、データ線DLのプリチャージ電圧は2 (およそ200mV) まで下げられる。しかし、データ線DLBのプリチャージ電圧をVDD/2とする利点は、回路設計が容易化し、かつ、プリチャージ電圧レベルを高精度で制御できるからである。したがってデータ対線 (DLBとDL) のプリチャージ電圧は、速度要求と回路設計の難しさの兼ね合いなどで決めればよい。なお、上述したプリチャージ電圧の条件から、動作電圧VDDの最小値は原理的には2 まで下げる事が許される。これはセンスアンプを必ずしも必要としない例である。したがって動作速度の要求が満たされれば、動作電圧を2 とし、センスアンプを設けずに構成することができる。

## 【0011】

メモリセルへの書き込みはワード線を選択的に書き込みレベル (たとえばVDHのような高電圧) にすることで行える (図中WLW on)。例えば図1 (b)、(c) のように、書き込みデータが、メモリセルの記憶電圧と異なる場合には、データ線DL及びDLBに逆極性の差動電圧を与えてメモリセルへ書きめばよい。また、再書き込み動作には、後述するように読み出したデータを増幅しその増幅電圧を再書き込みすればよい。

## 【0012】

以上述べたように、本発明では、データ線DLBのプリチャージレベルを増幅時の参照電圧とすることができる。したがって、ダミーセルを用いる必要がないので、従来のようなダミーセルによる面積増加はなく、またその参照電圧は時間的に一定なのでセンス動作を行える効果がある。

## 【0013】

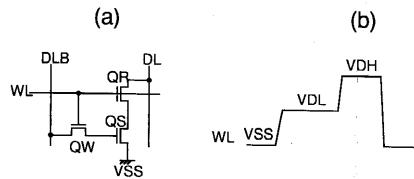

図3ならびに図4は、本発明に適用されるゲインセルの例で、N型MOSFETで構成された3トランジスタメモリセルである。ここでQSとQWならびにQRは、それぞれ蓄積用、書き込み用、読み出し用トランジスタである。このメモリセルは、QSのゲートに2値情報に対応したVDDあるいは0Vのデータを書き込み、その後、QWを非導通とすることによって、情報を保持する。図3のメモリセルは、書き込み用と読み出し用のトランジスタに同一のワード線が接続されている。このメモリセルは、面積は小さいが、ワード線駆動電圧として3値レベルを必要とする。すなわち、メモリセルが選択されない時 (行非選択時) には、ワード線の電圧は通常0VのVSSに固定され、読み出し時には中間電圧VDLが印加され、書き込みあるいは再書き込み時には十分高い電圧VDHが印加される。このように読み出し時にワード線電圧を中間レベルに設定する理由は、書き込みトランジスタQWを非導通にしたまま、読み出しトランジスタQRを導通させるためである。さもないと、QSのゲートに保持している情報電荷が、読み出し動作によってデータ線DLBに漏洩してしまう。ワード線電圧を上記のような3値で制御するためには、QRとQWの閾値電圧を各々適切に設定する必要がある。まず、読み出し時にQWが導通しにくく、かつQSが導通となる記憶情報を保持している場合にQRでデータ線DLを高速に放電するには、QWの閾値電圧(Vtw)はできるだけ高く、かつ、QRの閾値電圧(Vtr)はできるだけ低いことが望ましい。したがって、通常、同一ワード線につながるこれら2個のトランジスタの閾値電圧は異なる値に設定する方が好都合である。しかしVtwがあまり大きすぎると、QSのゲートにVDDを書き込むためには、VDH - VDD + Vtwの条件が必要であるから、いわゆるMOSFETの耐圧不良を起こす。したがってVtwのとりうる最大値には限界がある。一方、Vtrが小さくなりすぎると、データ線DLに接続されている多数の行非選択メモリセルがいわゆるサブスレショルド・リーク電流によって弱く導通するようになり、選択されたセルの正常な読み出しを妨げる。したがってVtrのとりうる最小値にも限界がある。通常、ワード線電圧0Vで行非選択とする場合にQRを非導通にするには、そのQRの閾値電圧Vtrは0.5V以上必要である。このようにVtrを高くしてしまうと、中間レベルの読み出し電圧では、読み出し動作が著しく低下してしまう。この問題を解決する一方法は、ワード線の行非選択レベル (VSS) を従来の0Vから負電圧に設定することである。例えば、Vtrを0Vに

10

20

30

40

50

しても行非選択時にQRが非導通になるためにはVSSを-0.5V以上に深くバイアスすれば良い。このときQRの駆動速度を決定する実効ゲート電圧はVDL-Vtrであるから、その値はVSSが0VでVtr=0.5Vの場合に比べて0.5Vだけ増加することになり、高速な読出しが可能となる。さらに、データ線をより高速に增幅するには、データ線の寄生容量を低減することである。これには後述する階層データ線が有効である。なお、QSの閾値電圧Vtsは、VDDのゲート電圧でQSは強く導通し、0Vのゲート電圧でQSは非導通になるか、あるいはきわめて弱く導通する条件のもと決められるが、通常Vtr=0Vである。なお、本メモリセルの動作例の詳細は後述する。

#### 【0014】

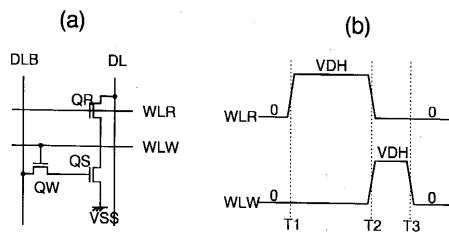

図4のメモリセルは、読出し用と書き込み用のトランジスタのゲートにはそれぞれ読出し用ワード線と書き込み用ワード線が接続されている。読出し用ワード線へ読出し電圧(VDH)を印加してメモリセルの記憶情報を読出し、書き込み用ワード線に書き込み電圧(VDH)を印加してメモリセルへの記憶情報の書き込み・再書き込みをする。なお、読出し電圧は、読出し速度が十分であれば、VDDでもよい。このメモリセルは図3のメモリセルに比べて面積は大きくなるが、ワード線の電圧は前述したように3値で制御する必要が無い。したがって読出し電圧を中間レベルに設定することに伴う低速動作の問題はなく、その上、駆動回路の設計は容易になる。また、QR、QWの閾値電圧も原理的には同じとができるので、複数のMOSFETを製造するためのプロセスコストを低下させる効果もある。さらに、低い動作電圧VDDでも高速動作をさせるためには、前述したようにVtrを低くくし、非選択レベルを負の電圧にすることが効果的である。また前述のように、データ線寄生容量を小さくすることも有効である。10

20

#### 【0015】

<実施例2>

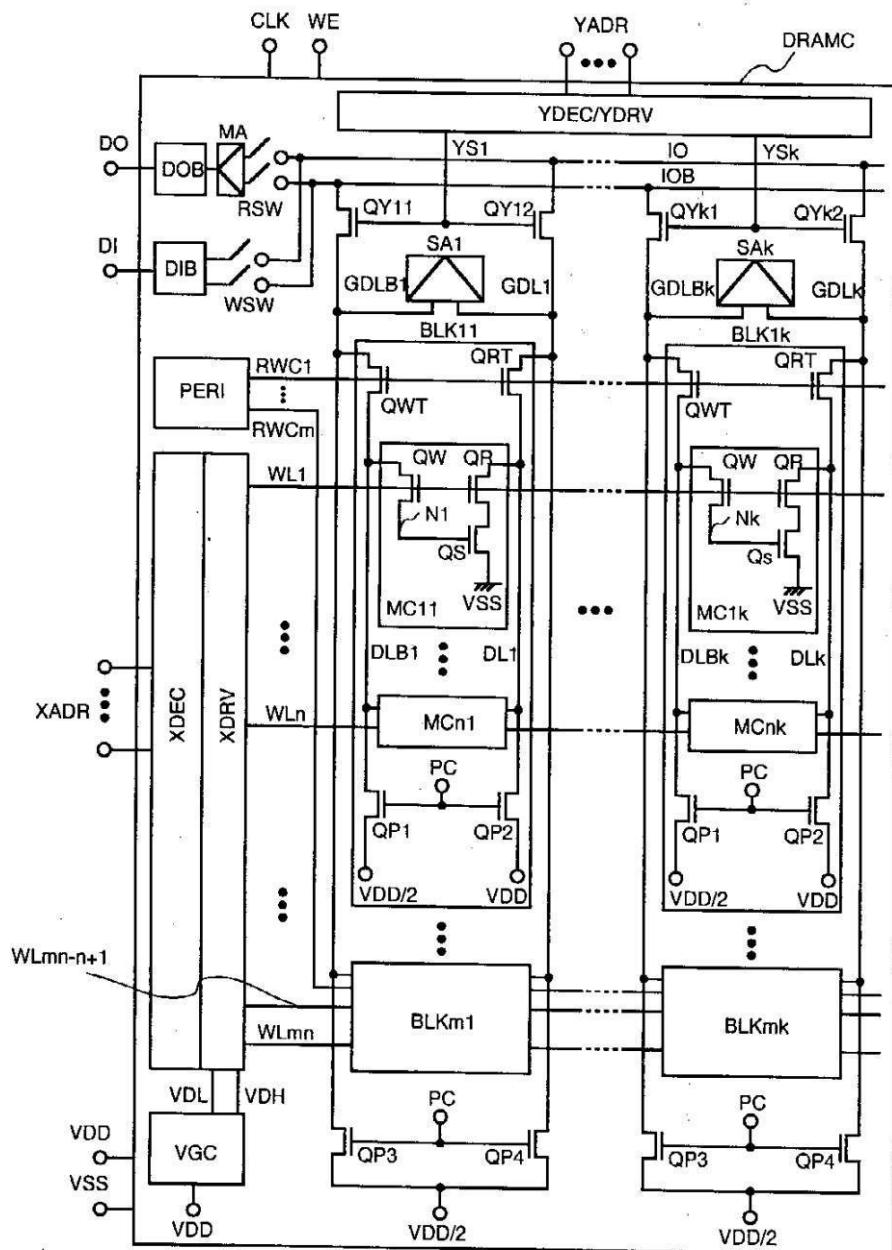

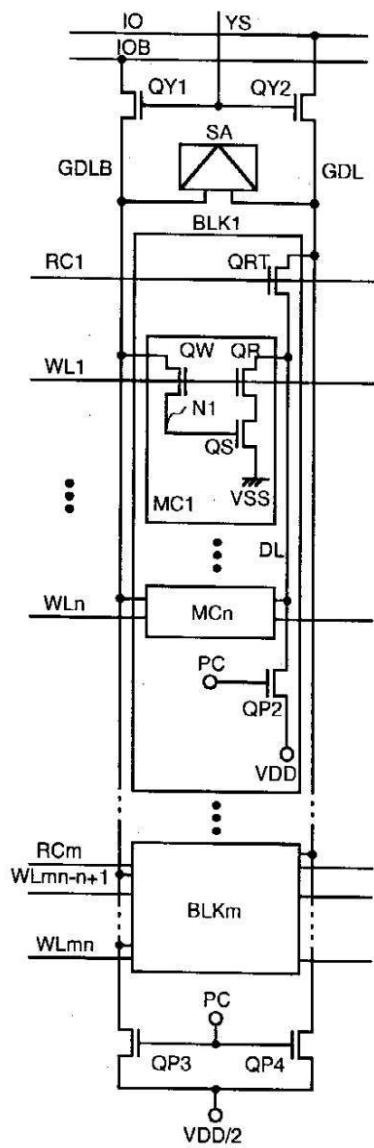

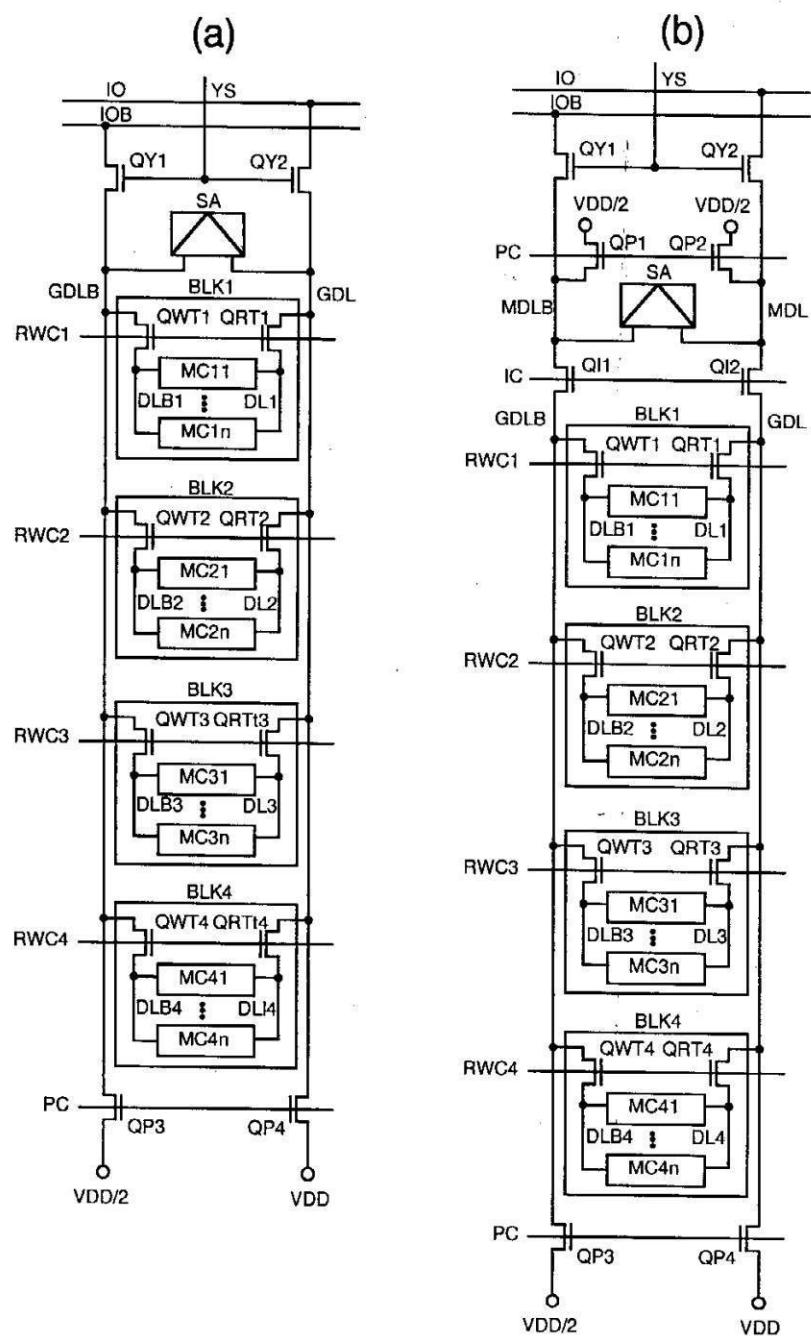

図5には、前述した実施例を具体的に適用したメモリ回路の一実施例が示されている。同図の各素子及び回路ブロックは、公知の半導体集積回路の製造技術によって、それが搭載される単結晶シリコンのような1個の半導体基板(LSI)上において形成される。

#### 【0016】

この実施例では、各データ線は、メモリセルとの間でデータの授受を行うローカルデータ対線DL(DL1～DLk), DLB(DLB1～DLBk)と、グローバルデータ対線GDL(GDL1～GDLk)、GDLB(GDLB1～GDLBk)の階層構造からなり、縦方向に並行に延在されている。一対のグローバルデータ線には、複数のブロックBLK(BLK11～BLKmk)が接続されている。各ブロックは、複数の図3(a)に示すメモリセルMC(MC11～MCn1など)が接続された一対のローカルデータ線と、グローバルデータ線とローカルデータ線を接続するためのスイッチ用MOSFET(QRT、QWT)から成っている。これらのスイッチ用MOSFETは、周辺回路(PER1)で発生されたブロック選択信号RWC(RWC1～RWCm)によって制御される。前記ある一対のグローバルデータ対線は、DRAMコア(DRAMC)の外部入力アドレス(YADR)をYデコーダ(YDEC)でデコードした後、対応するYドライバ(YDRV)で対応するスイッチQY1及びQY2等を駆動することによって、相補の共通データ対線(I0とI0B)に接続される。なお、前記各グローバルデータ対線には、特に制限されないが、図2(a)に示すようなP型MOSFET Q1及びQ2及びN型MOSFET Q3とQ4からなる周知のCMOSラッチ型差動アンプSAが設けられる。このセンスアンプSAは、共通ソースSANとSAPとに、それぞれ接地電位VSSと電源電圧VDDとが与えられることによって活性化される。また、たとえば、図3(b)に示した差動型センスアンプは、図2(a)のラッチ型差動アンプの高圧電源VDD側にP型MOSFETを、接地側にN型MOSFETを接続しており、制御信号SPE、SNEで増幅動作をスイッチ制御する。このセンスアンプは、スイッチ分の面積が増大してしまうが、このスイッチで電源と接続するため、駆動力が大きい特徴がある。以後本実施例は、図2(a)のセンスアンプを用いた場合にて説明する。30

40

#### 【0017】

本発明は、上述したようにデータ線を階層構造にすることで、センスアンプが直接駆動するデータ対線の容量を小さくできるため高速増幅動作が可能となる特長がある。なぜな50

ら、MOSFETの拡散層容量は配線層のメタルの寄生容量に比べて大きいので、寄生容量を少なくするためには、同一配線に接続されるMOSFETの数を少なくすることが効果的であるからである。また差動アンプを用いる理由は、メモリセルへの書き込み時にQR、QSで生じる貫通電流を防ぐためである。例えばブロックBLK11に着目し、その中のノードN1にVDDを書き込む場合、QSはオン状態となる。このときQR、及びQWもオンしているので、DL1はVSSへの経路ができる。そのため、DL1が0Vでない限り貫通電流がQRとQSにて発生してしまうのである。これは例えばノードN1が記憶している0情報を1情報に反転する動作時（いわゆる反転書き込み）に問題となる。このときDL1はプリチャージレベルとなっており、差動で書き込まないとQR、QSに貫通電流が流れてしまう。

## 【0018】

10

前記ローカルデータ線DL及びDLBには、プリチャージ信号PCにより制御されるプリチャージ用MOSFET QP1とQP2が設けられる。プリチャージ期間には、上記DLとDLBは、それぞれ電源電圧VDD（例えば1V）とその半分の電圧VDD/2（例えば0.5V）にプリチャージされる。また、上記各グローバルデータ対線GDLとGDLBは、プリチャージ信号PCにより制御されるプリチャージ用MOSFET QP3とQP4によって、プリチャージ期間にVDD/2レベルにプリチャージされる。

## 【0019】

20

メモリアレイは、前記複数対のデータ対線と、それと直交する複数のワード線（WL1～WLmnなど）とで構成される。同図においては4本のワード線WL1、WLn、WLmn-n+1、WLmnを代表して例示している。外部入力Xアドレス(XADR)をXデコーダ(XDEC)でデコードすることによって、これらのワード線の一本がXドライバ(XDRV)（ワードドライバとも呼ぶ）で選択的に駆動される。この図ではXアドレスとYアドレスが非多重化して入力されている例を示しているが、アドレスをアドレス・マルチプレックス方式で多重化して、アドレス端子数を半減することもできる。

## 【0020】

メモリセルはワード線とローカルデータ線DL及びDLBの交点に設けられ、そのワード線が選択された場合に、そのゲートの情報電圧によりオン状態またはオフ状態にされる蓄積MOSFET QSと、QSにより保持されていた情報を読み出してローカルデータ線DLに伝える読み出し用MOSFET QRと、ローカルデータ線DLBに与えられた書き込みデータを上記QSのゲートに伝える書き込み用MOSFET QWの3個で構成される。本実施例では上記QWとQRのゲートは、それぞれ同一のワード線に接続される。上記蓄積MOSFET QSのソース-ドライン経路は、上記読み出し用MOSFET QRと接地電位VSS(0V)に接続される。

30

## 【0021】

DRAMコア外部とのデータ入出力は以下の通りである。リードスイッチRSWをオンにして、メモリセルの読み出しによってI0及びI0Bに伝達されている記憶情報をメインアンプと、データアウトプットバッファDOBを経てデータアウトプット端子D0に出力する。一方、書き込み時には、データインプット端子DIからデータインプットバッファDIBへ入力されたデータを、ライトスイッチWSWをオンにすることによってI0及びI0Bに差動電圧で伝達し、後述する書き込み動作によりメモリセルへ書き込む。

## 【0022】

40

電源発生回路(VGC)は、外部から入力されたVDD電圧をレギュレータ等で降圧してVDL電源とする機能、VDLもしくはVDDをチャージポンプ回路等で昇圧してVDH電源を生成する機能を有し、これらのVDLとVDHは後述するワード線の読み出しレベル及び書き込みレベルに用いられる。なお、VDL電源をVDD電圧より高くする必要がある場合には、外部から入力されたVDD電圧をそのまま昇圧するか、一度降圧した後に昇圧して用いればよい。

## 【0023】

この実施例は、後述するように、増幅機能を有するメモリセルと、異なるプリチャージ電圧に設定されたローカルデータ対線を組みあわせることによって、ダミーセルを用いずに差動センサアンプの参照電圧レベルを発生させることに特長がある。

## 【0024】

50

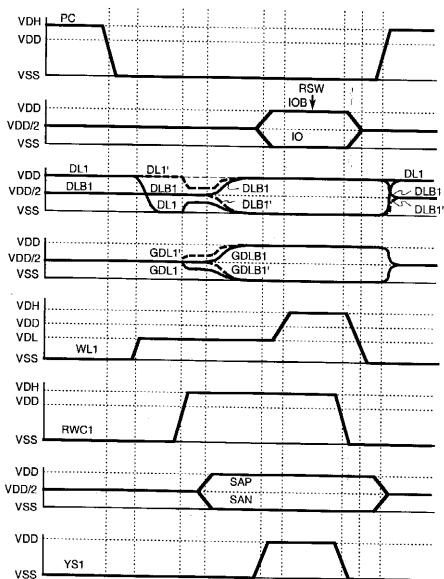

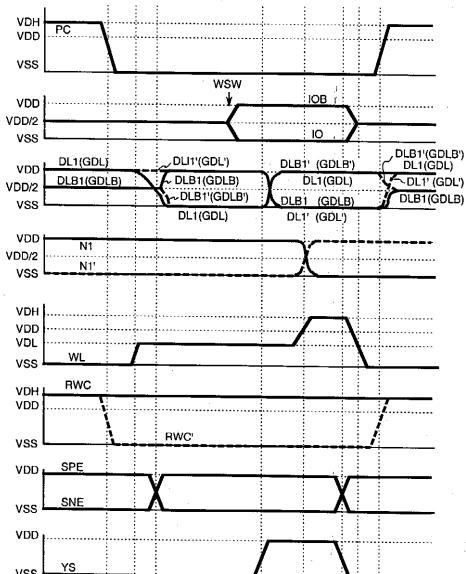

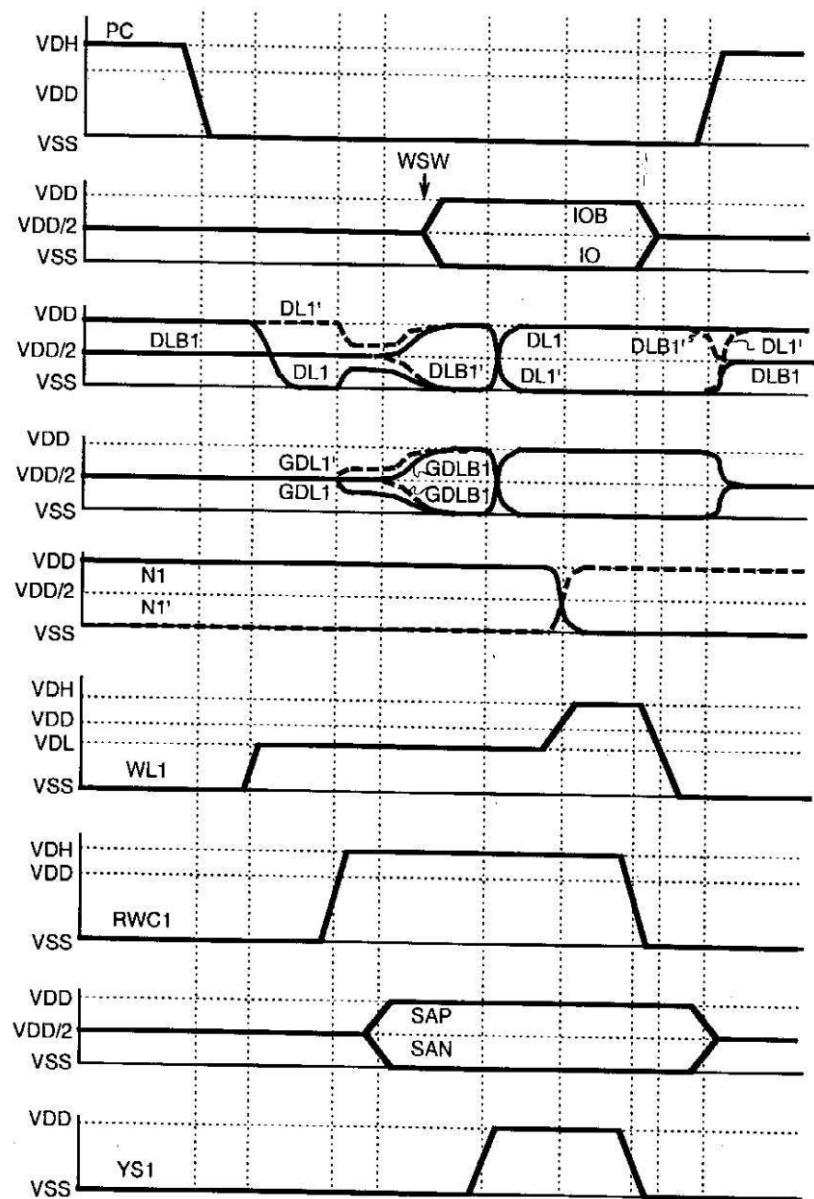

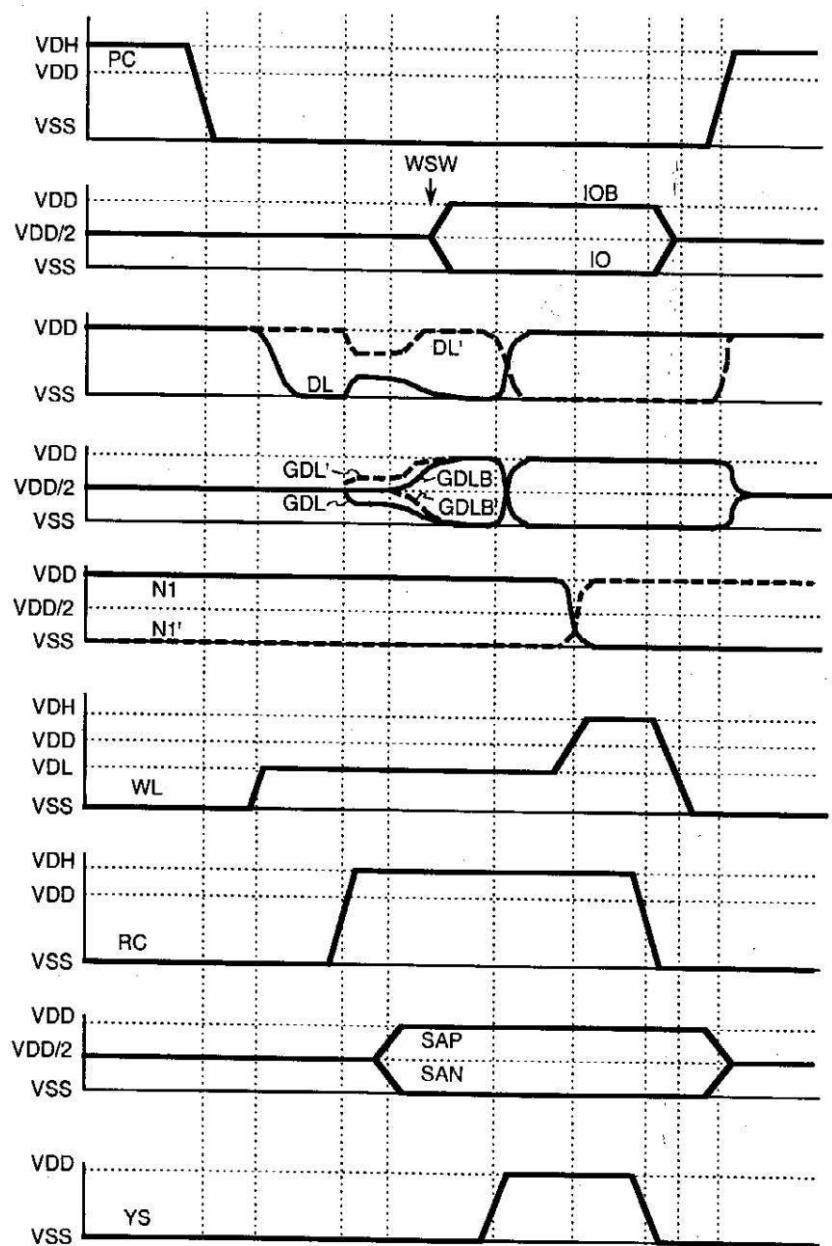

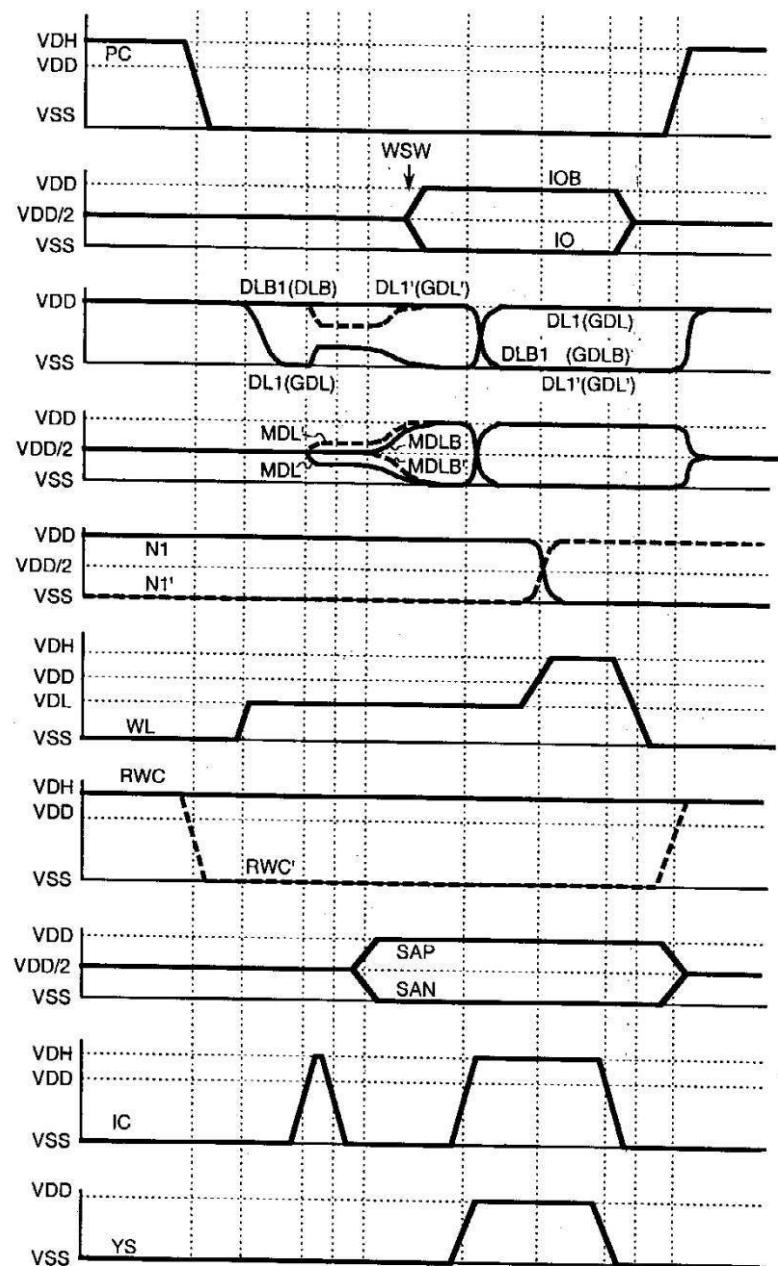

図6は、前記実施例のメモリセルの書き込み動作波形図である。ここではブロックBLK1を例に説明する。プリチャージ信号PCが高電圧VDH ( VDH = VDD + V<sub>tw</sub> ( 但し、V<sub>tw</sub>はQWの閾値電圧 ) ) レベルになると、上記ローカルデータ線DL及びDLBはそれぞれ電源電圧VDDならびにVDD/2にプリチャージされる。同様に、グローバルデータ対線 ( GDL及びGDLB ) と、センスアンプSAの共通ソース ( SANとSAP ) 、ならびに共通IO線 ( IO、IOB ) は、VDD/2にプリチャージされる。

#### 【 0 0 2 5 】

プリチャージ信号PCが0Vになると、上記プリチャージ用のMOSFETはオフ状態となるので、上記対線はフローティングとなり前記プリチャージ電圧を保持しつづける。この状態でメモリセルへの書き込み・読み出し等が行われる。以下、ワード線WL1と列線YS1が選択された場合のメモリセルの書き込み・読み出し・リフレッシュ動作を説明する。10

#### 【 0 0 2 6 】

##### (1) 書込み動作

メモリセルMC1の記憶ノード ( N1 ) に2値情報1あるいは0に対応した高電圧VDDあるいは低電圧VSSを書き込むためには、ワード線WL1に十分に昇圧した高電圧VDHを印加する必要がある。このVDHは書き込み用MOSFET QWの閾値をV<sub>tw</sub> ( 例えば0.5V ) とすると、VDH = VDD + V<sub>tw</sub>なる関係を満たす必要がある ( この場合例えばVDH=2.5V ) 。この条件下でブロック選択信号 ( RWC ) の一本 ( RWC1 ) が選択されると、データインプット端子DIより入力された書き込みデータに対応した差動電圧が、グローバルデータ線から対応するローカルデータ線を経由してQSのゲートに与えられて、MC11への書き込みがなされる。しかし、ここで注意を要することは、ワード線WL1に上記VDHを印加すると、同じワード線上にある、列選択信号で選択されない列非選択メモリセルの記憶情報が破壊されてしまうことである。すなわち、それぞれの列非選択メモリセル内の記憶ノードに、対応するローカルデータ線DLB1のプリチャージ電圧VDD/2が印加されてしまうからである。このような情報破壊20

を防ぐために、あらかじめ選択ワード線上のすべてのメモリセルを一旦読み出し、それぞれのセンスアンプで増幅し、その増幅電圧をそれぞれのメモリセルに再書き込みする。ただし、選択したメモリセルMC11には、増幅電圧を上記共通データ線IOBからの入力データ電圧で置き換えて書き込めばよい。したがって、書き込み動作に先行して読み出し動作が必須である。そこで以下にこの場合の読み出し動作を説明する。なお、前述したように、図3のメモリセルのワード線電圧には、読み出し時にはVDL、書き込み時にはVDH、行非選択時にはVSSと3値レベルの電圧が必要である。30

#### 【 0 0 2 7 】

まずメモリセルMC11に高電圧VDDが記憶されている場合の読み出しについて説明する。読み出し動作は、ワード線に中間レベルVDLのパルスを印加することで開始されるが、その振幅VDLはQRをオンするが、QWをオフとするように設定されなくてはならない。そのためには以下の条件を満たさなくてはならない。

#### 【 0 0 2 8 】

メモリセルはQSのゲートにVDDあるいは0Vの2値情報を記憶し、その記憶情報はワード線へ読み出しパルスを印加したときにQSがオンか、オフかで弁別されるものとする。VDLの読み出しパルスを印加してQRを導通させるためには、QRの閾値電圧をV<sub>tr</sub>とすると、以下の関係式を満たす必要がある。40

#### 【 0 0 2 9 】

$$VDL > V_{tr} \dots (1)$$

このときQSのゲートの記憶情報が、QWに読み出しパルスが印加されても破壊されないためには、以下の条件が必要である。すなわちQSのゲート電圧がVDDの場合には、QSのゲートに蓄えられていた電荷がQWを通してローカルデータ線DLB1に消失してしまわぬように、QWが非導通になる条件を求めればよい。VDD/2にプリチャージされているデータ線がQWのソースになるから、この条件はQWの閾値電圧をV<sub>tw</sub>とすると、以下の通りである。

#### 【 0 0 3 0 】

$$VDL < VDD/2 + V_{tw} \dots (2)$$

10

20

30

40

50

一方、QSのゲート電圧が0Vの場合には、QWが導通してQSのゲートが充電されて0Vから昇圧しても、その昇圧電圧がQSの閾値電圧 $V_{ts}$ よりも低ければQSは非導通のままである。この条件は、以下の通りである。

【0031】

$$VDL < V_{ts} + V_{tw} \dots\dots (3)$$

ここで、QSのゲートに蓄えられている電荷を長時間（例えば2ms～64ms）の間ローカルデータ線へ消失させないためには、閾値電圧 $V_{tw}$ は高くしたい。一方、高速読出しのためには $V_{ts}$ と $V_{tr}$ はできるだけ低くしたい。したがって、3者の閾値電圧は、上述した式を満足する範囲で自由に選べる。ただし、 $V_{tr}$ は $V_{ts}$ ほどには低くできない。不安定動作の原因となるからである。なぜなら、同じローカルデータ線に多数接続されている他の非選択メモリセル内のトランジスタQRにリーク電流（いわゆるサブスレッショルド電流）が流れて、ローカルデータ線のプリチャージ電圧が低下してしまうためである。例えば、 $VDD=1V$ 、 $V_{tw}=1V$ 、 $V_{ts}=0V$ 、 $V_{tr}=0.5V$ などとすると、QWによって記憶情報が破壊されない $VDL$ の範囲は、式(1)～(3)より以下の通りとなる。

【0032】

$$1.5V > VDL > 0.5V$$

このように $VDL$ を設定すれば、 $VDD$ と $VDD/2$ にプリチャージされていた $DL1$ 及び $DLB1$ は次のように変化する。QSのゲート（記憶ノードN1）が $VDD$ なら $DL1$ は0Vに放電し（図6においてN1で表示）、QWTがオフなので $DLB1$ はプリチャージレベル $VDD/2$ のままに維持される。一方、QSのゲート（記憶ノードN1）の電位が0Vである場合は、QSがオフなので、 $DL1$ はプリチャージレベルを保持し（図6においてN1'で表記）、 $DLB1$ はQWTがオフなので、プリチャージレベル $VDD/2$ のままに維持される。なお、実施例1でも述べたが、高速読出しのためにはワード線の行非選択レベルを負の電圧に設定し、 $V_{tr}$ を0Vのような低い値に設定すると効果的である。

【0033】

さて記憶情報がローカルデータ線 $DL1$ に読み出された後に、制御信号 $RWC1$ をハイレベルにして $QRT$ と $QWT$ をオンすると、 $DL1$ と $GDL1$ 、あるいは $DLB1$ と $GDLB1$ とがそれぞれ接続される。このとき $DLB1$ と $GDLB1$ は同じ電位レベル（プリチャージレベル）にあるため、電位変化はない。しかし $GDL1$ には以下のように寄生容量に応じた電荷配分により読出し信号（ $vs$ ）が現れる。

【0034】

ローカルデータ線 $DL1$ が放電されて0Vにある場合には、グローバルデータ線 $GDL1$ のレベルは $VDD/2$ に対して $vs$ だけ低下し、 $DL1$ も同じ値 $VDD/2 - vs$ レベルとなる。一方、読出し用データ線 $DL1$ がプリチャージレベル $VDD$ のままの場合には、 $GDL1$ はそのプリチャージ電圧 $VDD/2$ に対して微小電圧だけ上昇（ $+vs$ ）し、 $DL1$ も同じ値 $VDD/2 + vs$ レベルとなる。この状況は図6の $DL1$ 、 $DLB1$ 、 $GDL1$ 、 $GDLB1$ の波形図において点線で記述し、ダッシュ付記号 $DL1'$ 、 $DLB1'$ 、 $GDL1'$ 、 $GDLB1'$ で示した。このように、グローバルデータ線 $GDL1$ にはメモリセルの記憶ノードに保持された2値情報（あるいは0）に応じて、 $VDD/2$ に対して $-vs$ あるいは $+vs$ の微小な読出し信号が現れる。したがって他方のグローバルデータ線 $GDLB1$ のプリチャージ電圧 $VDD/2$ を基準にして、センスアンプにて弁別・增幅ができる。ここでは、図2(a)に示したようなセンスアンプを用いた場合で説明する。この増幅は、共通ソース線SAPを $VDD$ のような高電圧に、共通ソース線SANを $VSS$ のような低電圧にすることによって行われる。その結果、グローバルデータ線 $GDL$ はロウレベル（ $VSS$ ）に、 $GDL1$ と相補を成す他方のグローバルデータ線 $GDLB1$ はハイレベル（ $VDD$ ）になる。このように、本発明では、メモリ記憶情報の増幅に際して、従来必須であったダミーセルが不用となる特長がある。なお、制御信号 $RWC1$ はプリチャージ信号PCがロウレベルになると同時にハイレベルにしてもよい。その場合は、制御すべきタイミングが少なくなるので、設計が容易になる効果がある。

【0035】

センスアンプで増幅された後、メモリセルに書込むために共通データ対線（I0、I0B）に印加された $VDD$ と $VSS$ の差動電圧は、列選択線YS1を選択的にハイレベルにすることでグ

10

20

30

40

50

ローバルデータ対線（GDL1、GDLB1）とローカルデータ対線（DL1、DLB1）に送られる。（図中点線で示したDL1'の動きは、蓄積MOSFET QSのゲートにOVが記憶されている場合である。）その後ワード線レベルは書き込みレベルVDHにされる。これにより、書き込みデータ線DLB1の電圧がメモリセルMC11内のQSのゲートに伝えられて書き込みが完了する。同じワード線上の他の列非選択メモリセルには、増幅された記憶電圧が再書き込みされる。

#### 【0036】

上記のように列選択されたメモリセルへの書き込み動作、列非選択メモリセルへの再書き込み動作が終了すると、ワード線WL1ならびにYS1はロウレベルにされ、上記QY1及びQY2はオフ状態になる。さらに、プリチャージ信号PCをハイレベル（VDH）にすることで、各ローカルデータ対線とグローバルデータ対線はプリチャージされ、次のメモリアクセスに備えることができる。10

#### 【0037】

##### (2) 読出し動作

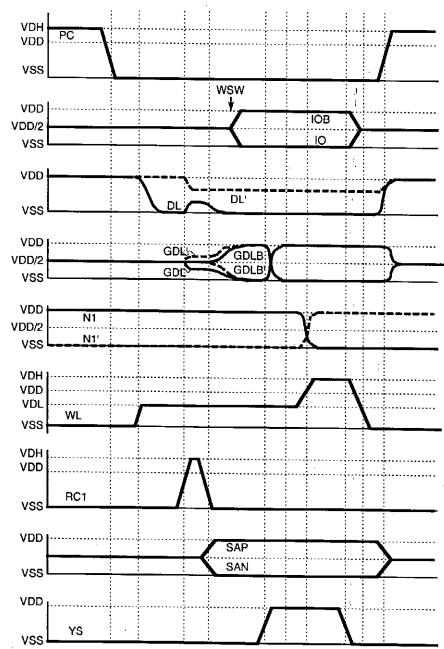

図7は読み出し動作を示す波形図を記した。読み出し動作では前記のような書き込み動作において、行及び列選択されたメモリセルの読み出し信号をセンスアンプSAにより増幅し、共通データ対線に出力し、データアウトプット端子D0より外部に取り出せばよい。ワード線の行選択レベルを高電圧VDHにすれば、列選択セル及び列非選択セルのすべてに対して、読み出し情報に対応した電圧が再書き込みされる。

#### 【0038】

##### (3) リフレッシュ動作

リフレッシュ動作は、前記図7において列選択線YSを非選択にしたまま、ワード線の全てのメモリセルに対する読み出し・再書き込み動作を、すべてのワード線に対して行えばよい。20

#### 【0039】

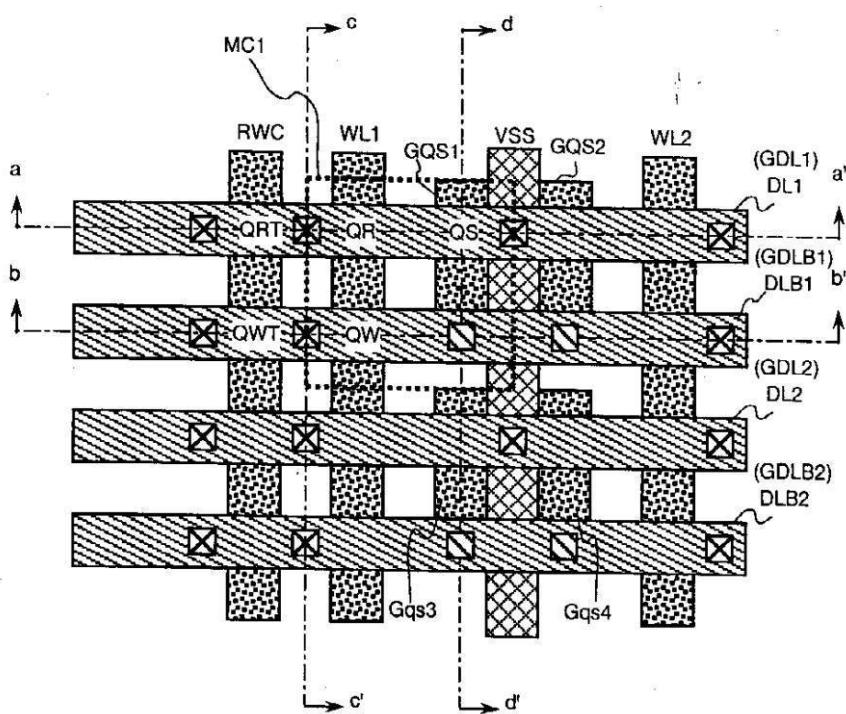

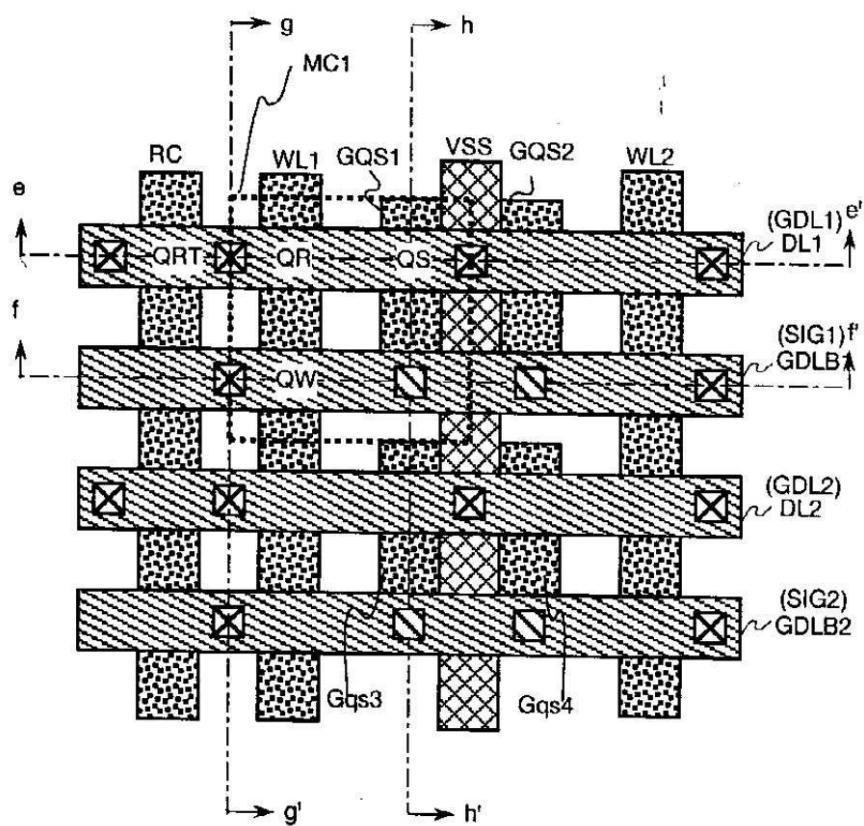

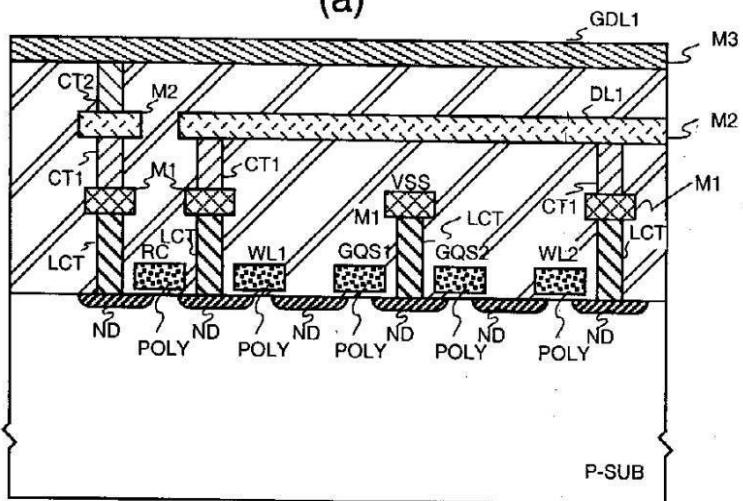

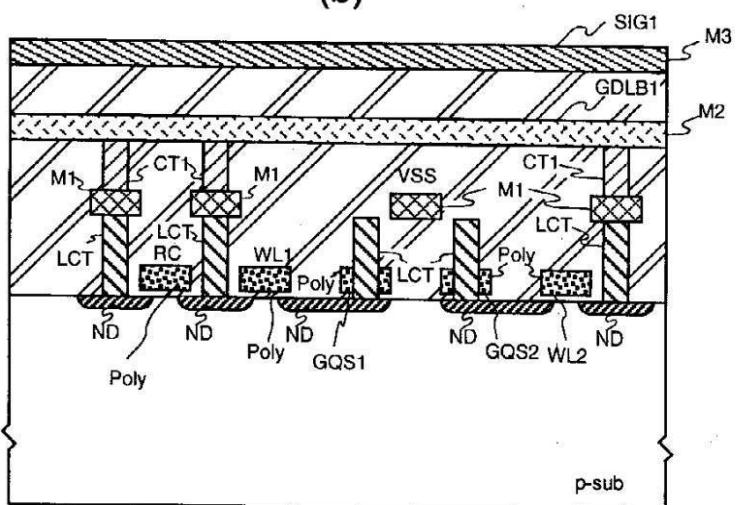

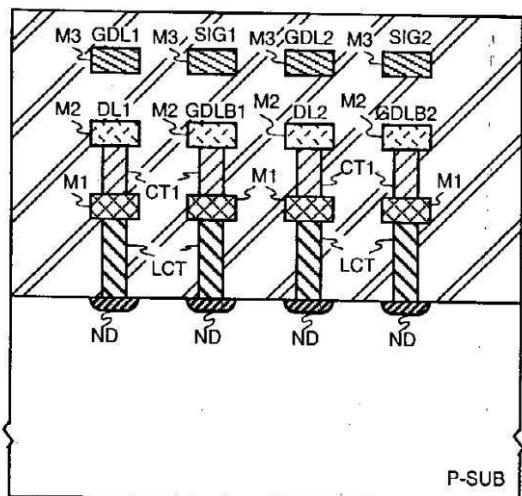

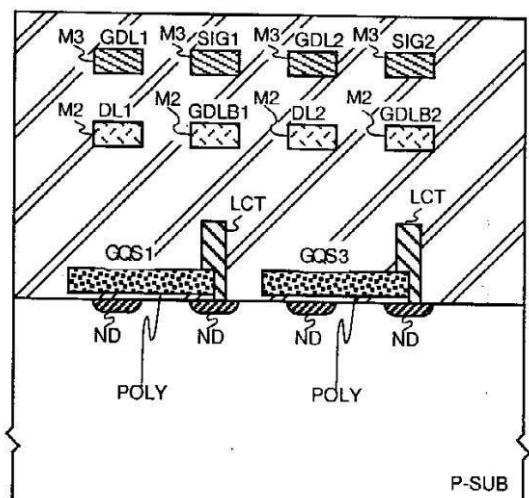

図8は、本発明のメモリセル関連のレイアウト図である。この図には、図5に示したメモリセルが4個と、QRTと、QWTとが示されている。ポリシリコン層(POLY)等で作られるワード線WL1の一部がメモリセルMC11のQRとQWのゲートを形成し、同じ層のポリシリコン層がQSのゲート(GQS)を形成する。ローカルデータ線(DL1とDLB1など)は同じ層(M2)のメタルで形成され、グローバルデータ対線(GDL1とGDL1B)は他の層(M3)のメタルで形成される。図中に示したコンタクトLCTは、拡散層とゲートを直接接続する。また、QSのソースにはVSSが印加されるが、これはメタル1層(M1)でレイアウトされ、小型化のために隣接するメモリセルと共有する。このため2つのメモリセルは鏡像関係にレイアウトされる。両対線の接続は、ポリシリコン等の配線の一部をゲートとするMOSFET(QRT、QWT)にて行われる。30

#### 【0040】

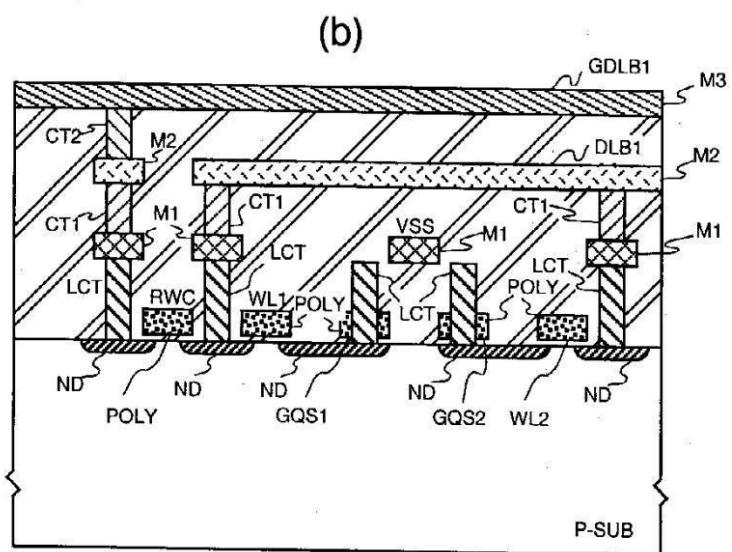

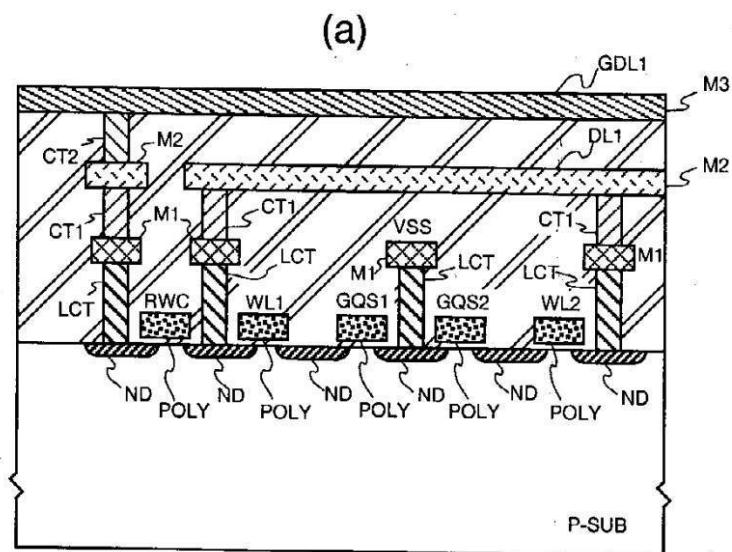

各層間の関係を明らかにするため、図8のa-a'断面及びb-b'断面を図9(a)及び(b)に示した。図9(a)はa-a'断面であり、ローカルデータ線DL1とグローバルデータ線GDL1を通る断面を示している。図9(b)はb-b'断面でありローカルデータ線DLB1とグローバルデータ線GDLB1を通る断面を示した。この図では、2個のコンタクトLCTが記されている。さらにa-a'断面b-b'断面と直角の方向の断面c-c'及びd-d'断面を図10(a)及び(d)に示した。(b)には2個のコンタクトLCTが記されている。40

#### 【0041】

##### <実施例3>

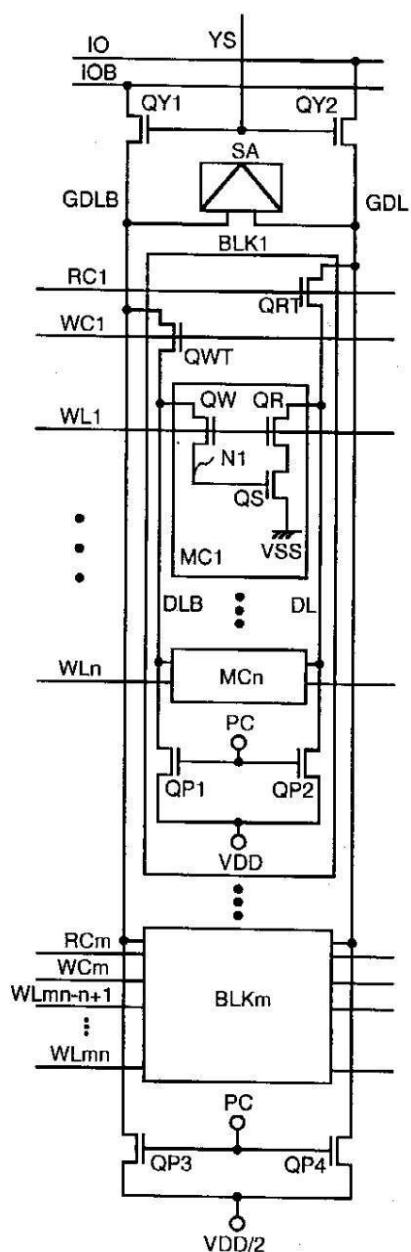

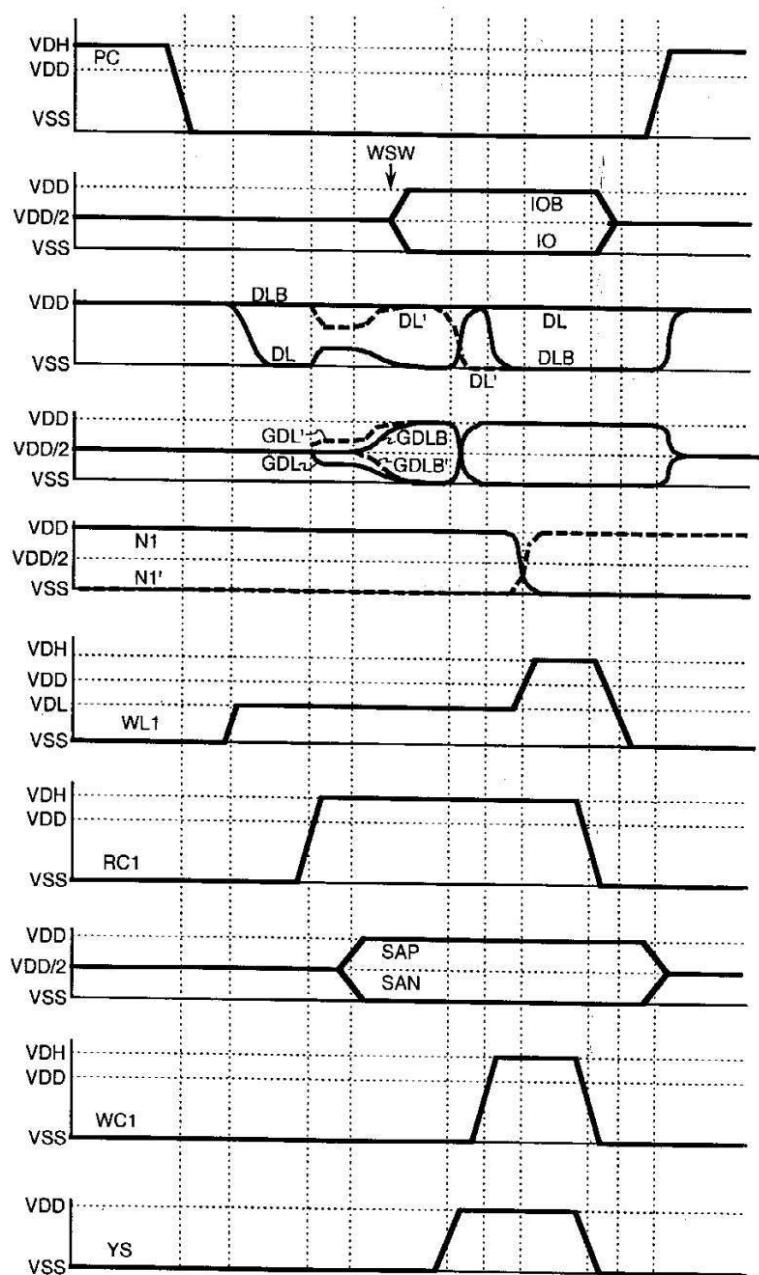

上記第2の実施例は、読み出し転送用MOSFET QRTと書き込み転送用MOSFET QWTの制御を一つの信号RWCで制御するため、タイミングマージンに余裕があり、またセンスアンプからみたデータ対線の電気的平衡度も良好なので、その分だけ高速安定動作が可能である。しかし、ブロックBLKごとにVSSとVDD/2の電源線を配線する必要があるため、場合によつては面積が増加する懸念がある。

#### 【0042】

図11は、ローカルデータ線DL及びDLBのプリチャージ用電源をVDDのみとし、読みしブロ50

ックの選択用MOSFET QRTの制御には読み出し信号RCを使用し、書き込みブロックの選択用MOSFET QWTの制御には書き込み制御信号WCを使用するという具合に、制御信号を読み出しと書き込みで独立化したことである。本実施例は、第2の実施例と比較して、RC、WCの制御を独立化することによって、動作速度が遅くなる可能性があるが、メモリアレー内に配線するブロックごとのプリチャージ用の電源配線を半数とすることができますため、面積を小さくできる効果がある。

#### 【0043】

図12は、図11に示した実施例の動作波形図である。ここでは図11中のブロックBLK1のメモリセルMC1が選択された場合を代表して説明する。書き込みは図6とほぼ同様であるが、グローバルデータ対線とローカルデータ対線の接続方法が異なる。図6において書き込み転送用MOSFET QWTと読み出し転送用MOSFET QRTは同じ制御信号RWCを用いて同時にオン・オフ制御されていたが、本実施例ではローカルデータ線DLの電位がVSS(記憶ノードN1の電位がVDDの場合)か、あるいはプリチャージレベルVDD(記憶ノードN1の電位が0Vの場合)になった後に、QRTのみ制御信号RC1を用いてDLとGDLを接続する。その結果、DLとGDLは図6で説明したように、記憶ノードN1がVDDの場合にはVDD/2 - vsのレベルに、記憶ノードN1が0Vの場合にはVDD/2 + vsレベルになる。グローバルデータ線GDLの電位がこのように確定した後に、センスアンプを活性化するとグローバルデータ対線の電位は増幅される。センスアンプにて増幅された後に、図6で説明したように、外部から書き込みデータが伝達されると、制御信号WC1をVDHレベルにすることでQWTがオンし、ローカルデータ線DLBに書き込みデータが伝達される。ローカルデータ線DLBに書き込みデータが伝達された後に、ワード線の電位を書き込み電位VDHにすることで、メモリセルの記憶ノードN1に書き込みデータが書き込まれる。読み出し時にはQRTとQWTを同時にオンにすることはできない。なぜなら、ローカルデータ線DLBのプリチャージレベルはVDDであるため、読み出し時にQWTをオンすると、VDD/2にプリチャージされているグローバルデータ線GDLBに正の微小信号が伝達されてしまい、正確な参照電位が得られなくなってしまうからである。特に記憶ノードN1がVDDの場合にはグローバルデータ線GDLに出現する上述した正の微小信号+vsとの大小関係で、正確な増幅動作ができなくなってしまう恐れがある。

#### 【0044】

読み出し動作では、選択されたメモリセルの読み出し信号をセンスアンプSAにより増幅し、共通データ対線に出力し、データアウトプット端子D0から外部に取り出せばよい。ワード線の選択レベルを高電圧VDHにすれば、列選択セル及び列非選択セルのすべてに対して、読み出し情報に対応した電圧が再書き込みされる。

#### 【0045】

リフレッシュ動作は、列選択線YSを非選択にしたまま、ワード線上のすべてのメモリセルに対する読み出し・再書き込み動作を、すべてのワード線に対して行えばよい。

#### 【0046】

<実施例4>

これまで述べた実施例は、センスアンプにて増幅する際に、グローバルデータ対線に接続されるローカルデータ対線が選択ブロックのみとなるものである。このような構成は、グローバルデータ対線に接続されるMOSFETの数を少なくできるため、負荷容量が少なく高速な増幅動作が可能である。一般に、メタル配線の寄生容量は、多数のMOSFETが接続されることで生じる寄生容量に比べて小さいからである。しかし、高速増幅動作よりも配線数を節約することが望まれる場合もある。以下で配線数の少ないメモリアレイの実施例について述べる。

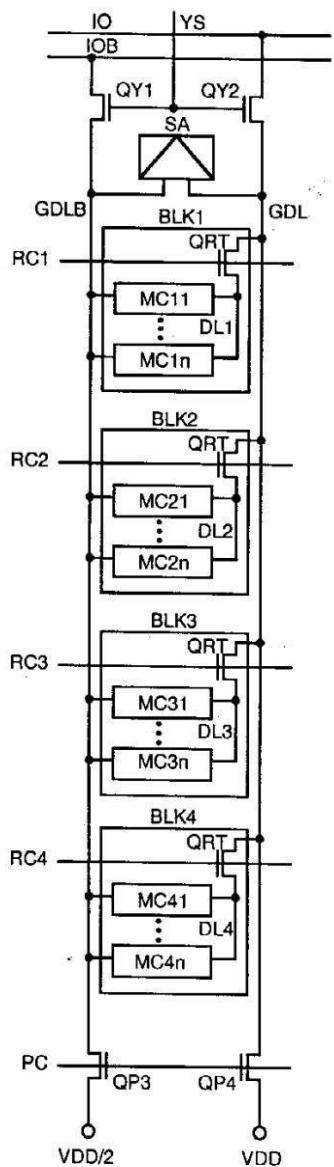

#### 【0047】

図13は、本発明に係る他のメモリ回路の実施例である。この実施例の特長は、書き込み用ローカルデータ線(DLB)をグローバルデータ線GDLBと共に接続して配線数を削減し、実施例2で必要であったQWTを不用としたことである。したがって、図5のQWはグローバルデータ線GDLBに直接接続されている。このため、後述するように、メモリアレイ上にデータ線以外の信号線が、配線層を付加せずに設置することができるとなり、限られた配線層を有

10

20

30

40

50

効に利用できる効果がある。

#### 【0048】

図14は、上記図13に示したメモリ回路の書き込み動作の波形図である。図6での説明と同様に、プリチャージ信号PCをロウレベルした後にメモリの読み出し・書き込みが行われる。この実施例においても書き込み動作に先行して読み出し動作が行なわれる。図6と唯一異なるのは、DLBが無いことである。前述したようにメモリセルMC1の記憶情報は、グローバルデータ線GDL1に極性の異なる信号として読み出され、その情報は対をなす他方のグローバルデータ線GDLB1の電圧(VDD/2)を基準にしてセンスアンプで増幅・弁別される。その後に、前述したように、上述した増幅電圧を外部からの書き込みデータの電圧で置き換えてメモリセルMC1に書き込む。このときは、他のメモリセルには、もとの記憶電圧が再書き込みされる。読み出しならびにリフレッシュ動作も前述したように行われる。10

#### 【0049】

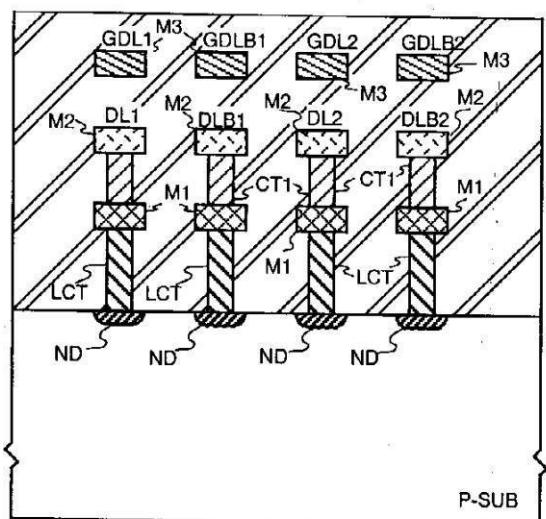

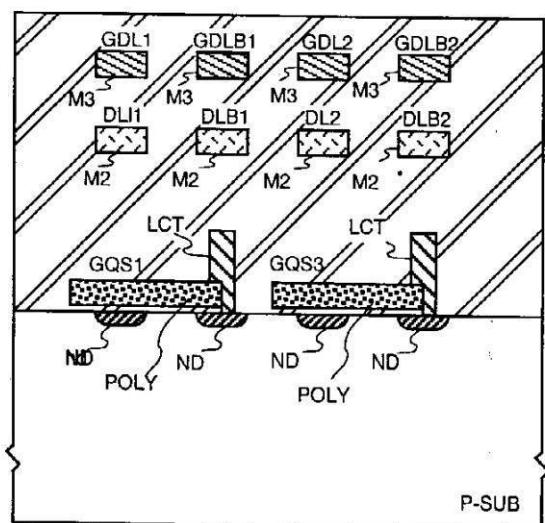

図15は、本発明のメモリセル周辺のレイアウト図である。この図には図13に示した4個のメモリセルと、QRTと、QWTとが示されている。メモリセルMC1はポリシリコン層等で作られるワード線WL1の一部がQRとQWのゲートを形成し、同じ層のポリシリコン層がQSのゲートを形成する。ローカルデータ線DL及びグローバルデータ線GDLBは同じ層(M2)のメタルで配線され、グローバルデータ線GDL及び列選択線のような信号線(SIG1、SIG2等)は他の層(M3)のメタルで形成される。図中に示したコンタクトLCTは、拡散層とゲートを直接接続する。また、QSのソースには電源VSSが印加されるが、これはメタル1層でレイアウトされ、小型化のために隣接するメモリセルと共有する。このため2つのメモリセルは鏡像関係にレイアウトされる。DLとGDLの接続は、ポリシリコン等の配線の一部をゲートとするMOSFET QRTにて行われる。各層間の関係を明らかにするため、図15のe-e'断面及びf-f'断面を図16(a)及び(b)に示した。図16(a)はe-e'断面であり、読み出しデータ線DL1とグローバルデータ線GDL1を通る断面を示している。図16(b)はf-f'断面でありグローバルデータ線GDLB1と信号線を通る断面を示した。この図では、2個のコンタクトLCTが記されている。さらにe-e'断面とf-f'断面と直角の方向の断面g-g'及びh-h'断面を図17(a)及び(b)に示した。(b)には2個のコンタクトLCTが記されている。20

#### 【0050】

##### <実施例5>

図18は、アレイ内のプリチャージ用の電源配線数を削減し、更なる省面積化を図る実施例であり、(a)はセンスアンプとして、例えば図2(b)を用いる場合であり、図18(b)はセンスアンプとして、例えば図2(a)を用いる場合である。この実施例は、図5でロックBLKごとに必要としていたローカルデータ対線のプリチャージ用の電源配線を廃し、プリチャージ電源をグローバルデータ対線と共通化していることを特徴とする。図18(a)及び(b)ではロックBLKが4つの例を示したが、本発明はロック数を4つに限定すること無く実施できる。ここではまず図18(a)を説明する。同図においてグローバルデータ線GDLとローカルデータ線DL(DL1～DL4)はプリチャージ期間に電源電圧VDDにプリチャージされ、グローバルデータ線GDLBとローカルデータ線DLB(DLB1～DLB4)はプリチャージ期間にハーフプリチャージレベルVDD/2にプリチャージされる。このためには、プリチャージ期間にすべての制御信号RWC(RWC1～RWC4)をハイレベル(オン)にすることが必要である。プリチャージ期間には貫通電流をなくすために、センスアンプ起動信号SPEはハイレベルに、SNEはロウレベルにされる。ここで問題とするプリチャージ期間の貫通電流は、GDL及びGDLBのプリチャージ電圧がそれぞれVDDとVDD/2と等しくないため生じてしまう。例えば図2(a)のセンスアンプを用いると、トランジスタQ4がプリチャージ期間に半オンとなってしまうため、GDLから共通ソース線SANへ電流が流れてしまう。3040

#### 【0051】

ここで図19をもちいて、図18(a)実施例の書き込み動作を説明する。本実施例も書き込み動作に先行して読み出し動作が行われる。ここではロックBLK1のメモリセルMC1を例に読み出し動作を説明する。この図では各メモリセルへ接続されるワード線は省略してある。データ線のプリチャージは、プリチャージ信号(PC)がハイレベルの時に行われる。このとき50

、グローバルデータ対線GDL、GDLBはそれぞれVDD、VDD/2にプリチャージされる。同時にローカルデータ対線DL1とDLB1をプリチャージするために、制御信号RWC1をハイレベルにしてローカルデータ対線をグローバルデータ対線に接続する。その結果、ローカルデータ対線DL1及びDLB1はそれぞれVDD、VDD/2にプリチャージされる。読み出し動作に入るためには、プリチャージを停止する必要があり、これはPCをローレベルにすることで行う。PCがローレベルにあるとき、ワード線の電位を読み出しレベルVDLとして、行選択されたメモリセルからの読み出しが開始される。このとき、非選択ロックの制御信号RWC2～4は図19にてRWC'で記したように、ロウレベルにすることが望ましい。このようにすることで、グローバルデータ対線への負荷容量を小さくすることができる。なぜなら、非選択ロックのメモリセルトランジスタがグローバルデータ対線と電気的に非接続となるため、これら非接続のMOSFETによる寄生容量の分だけ負荷容量が削減できるからである。ローカルデータ線DL1及びグローバルデータ線GDLへの読み出し電位がVDD/2より低下するまで待った後、センスアンプ起動信号SPEをロウレベルに、SNEをハイレベルにしてセンスアンプを起動し、読み出し信号を0、1へ正確に増幅する。

#### 【0052】

メモリセルへの書き込みは、まず、列選択スイッチQY1とQY2をオンすることで共通データ対線に伝達されている書き込み信号電圧をグローバルデータ対線へ伝達する。その後、ワード線を書き込みレベルVDHとしてメモリセルの記憶ノードn1に書き込み信号を伝達し、ワード線を列非選択レベル0Vにして記憶ノードをローカルデータ線から隔離する。その後、プリチャージ状態へ戻るが、これは図2での説明と同じである。

#### 【0053】

次に図18(b)について述べる。これは、図18(a)で説明した実施例の変形例であり、センスアンプの構成が異なる。この例では、図2(a)に示したような、センスアンプにつながるデータ対線のプリチャージレベルが等しいセンスアンプを用いている。図18(b)のグローバルデータ対線GDLとGDLBはプリチャージレベルがそれぞれVDDとVDD/2であるため、両グローバルデータ対線のプリチャージレベルが等しくない。そこで、隔離用MOSFET Qi1とQi2で分離された、プリチャージレベルとしてVDD/2レベルをもつメインデータ対線MGDL、MGDLBを新たに設け、このMGDLとMGDLBをセンスアンプに接続して読み出し信号を増幅する。

#### 【0054】

ここで図20をもちいて、図18(b)実施例の書き込み動作を説明する。この場合も書き込み動作に先行して読み出し動作が行われる。ここではロックBLK1を例に読み出し動作を説明する。この図では各メモリセルへ接続されるワード線は省略してある。データ線のプリチャージは、プリチャージ信号(PC)がハイレベルの時に行われる。このとき、メインデータ対線MGDLとMGDLBはそれぞれVDD/2レベルにプリチャージされ、グローバルデータ対線GDL、GDLBはそれぞれVDD、VDD/2にプリチャージされる。同時にローカルデータ対線DL1とDLB1をプリチャージするために、制御信号RWC1～4をハイレベルにしてローカルデータ対線をグローバルデータ対線に接続する。その結果、ローカルデータ対線DL1及びDLB1はそれぞれVDD、VDD/2にプリチャージされる。読み出し動作に入るためには、プリチャージを停止する必要があり、これはPCをローレベルにすることで行う。PCがローレベルにあるとき、ワード線の電位を読み出しレベルVDLとして、行選択されたメモリセルからの読み出しが開始される。このとき、非選択ロックの制御信号RWC2～4は図20にてRWC'で記したように、ロウレベルにすることが望ましい。このようにすることで、グローバルデータ対線への負荷容量を小さくすることができる。ローカルデータ線DL1及びグローバルデータ線GDLへの読み出しが完了したら、制御信号ICをハイレベルにしてグローバルデータ線へ伝達された読み出し信号電圧をメインデータ線MGDLへ伝達する。その結果、各データ線の寄生容量に応じた電荷配分により、記憶ノードの情報電圧に応じた極性の異なる読み出し信号(±vs)がメインデータ線MGDLに現れる。このときGDLBとMGDLBは同じ電位レベル(プリチャージレベル)にあるため、電位変化はない。したがって図6の説明で述べたように、MGDLへはメモリセルからの読み出し信号に応じてVDD/2+vsあるいはVDD/2-vsの読み出し信号が伝達される

10

20

30

40

50

。MGDLへ読み出し信号が伝達された後、制御信号ICをローレベルにし、メインデータ対線MGDL、MGDLBとグローバルデータ対線GDL、GDLBを隔離する。このように、増幅時にグローバルデータ線を隔離すると、メインデータ線MGDLとMGDLBの寄生容量が少なくなるので、高速に増幅することができる。その後、メインデータ線につながるセンスアンプによって、読み出し信号を0、1へ正確に増幅する。

#### 【0055】

メモリセルへの書き込みは、まず、列選択スイッチQY1とQY2をオンすることで共通データ対線に伝達されている書き込み信号電圧をメインデータ対線MGDL、MGDLBへ伝達し、制御信号ICをハイレベルにしてスイッチQI1とQI2をオンしグローバルデータ対線へ伝達する。その後、ワード線を書き込みレベルVDHにすることでメモリセルの記憶ノードN1に書き込み信号を伝達し、ワード線を非選択レベル0Vにして記憶ノードをローカルデータ線から隔離する。その後、プリチャージ状態へ戻るが、これは図6での説明と同じである。なお、プリチャージ用MOSFETQP1と隔離用MOSFETQI1は、MGDLBとGDLBのプリチャージ電圧が等しいため、原理的には不要である。しかし、これらのMOSFETを設ける利点は、メインデータ対線MGDLとMGDLBが電気的に平衡するため、安定した増幅動作が実現できることである。10

#### 【0056】

##### <実施例6>

図21はプリチャージ用電源をローカルデータ対線とグローバルデータ対線とで共有する別の実施例である。これは、図13に示した実施例のメモリアレイ構成において、プリチャージ用電源配線をローカルデータ対線とグローバルデータ対線で共有するようにしたものである。図13と異なるのは、グローバルデータ線GDLのプリチャージレベルがVDDであることである。なお、図21にはブロック数が4の場合について記してあるが、本発明はブロック数を4つに限定することなく実施することができる。20

#### 【0057】

書き込み動作及び読み出し動作は図14の説明に準じるが、グローバルデータ線への書き込み・読み出し等の制御は図19の説明に準じる。すなわち、図19でRWC及びRWC'の動作をRC及びRC'の動作に置き換え、DLB1の動作を不用とした動作波形図にしたがって制御すればよい。

#### 【0058】

##### <実施例7>

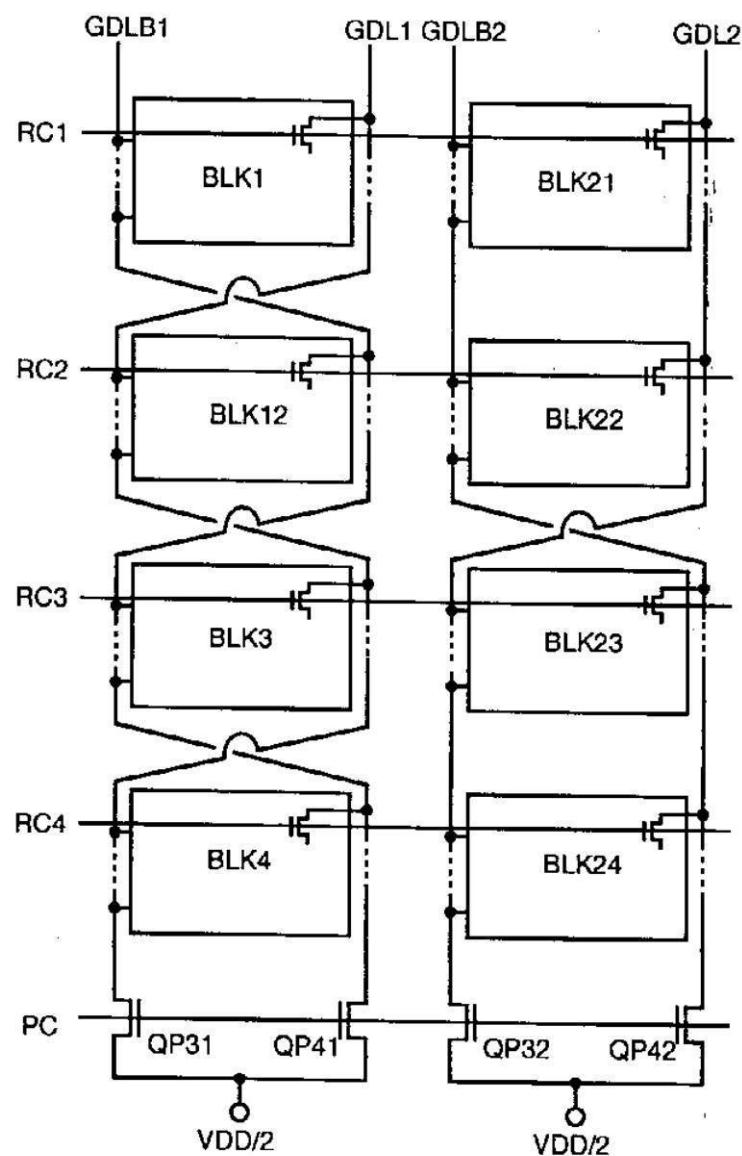

図5、図10及び図13のメモリアレイ構成では、グローバルデータ対線GDLとGDLBに接続されるMOSFETの数が不均等であるため、GDLとGDLBとで寄生容量が異なる。このため、センスアンプから見ると実効雑音に作用したり、低速動作となってしまうおそれもある。図22は寄生容量の不均等を少なくする対線構成を図13に適用した実施例である。この実施例は、グローバルデータ対線をメモリセル上で交差させ、両対線の容量不均衡を解消する効果がある。また、この図に示すように、隣りあうグローバルデータ対線ごとに、交差方法を変えれば、GDL及びGDLBに出現する雑音をうまく相殺することが可能となる。30

#### 【0059】

まず、寄生容量の平衡化について述べる。ここでは便宜的に隣り合うグローバルデータ対線（GDL1とGDLB1ならびにGDL2とGDLB2）に着目して説明する。これらのグローバルデータ対線には、MC1からMC1nまでのn個のメモリセルで構成されるブロックが4つづつ接続されているものとする。ブロックBLK11が選択されており、制御信号RCがハイレベルにある場合を考える。このときGDL1につながるMOSFETはBLK11のQRTとそれにつながる読み出し用MOSFETがあわせてn+1個、BLK12の書き込み用MOSFETがn個、BLK13の読み出し転送用MOSFETが1個、BLK14の書き込み用MOSFETがn個の、計3n+2個であり、GDLB1につながるMOSFETの数は、BLK11の書き込み用MOSFETがn個、BLK13の読み出し転送用MOSFETが1個、BLK13の書き込み用MOSFETがn個、BLK14の読み出し転送用MOSFETが1個の、計2n+2個である。ここでグローバルデータ線を交差させなかった場合、GDLにつながるMOSFETの数はBLK11のQRTとそれにつながる読み出し用MOSFET n個、BLK12の読み出し転送用MOSFET、BLK13の読み出し転送用MOSFET、BLK14の読み出し転送用MOSFETの、計n+4個であり、GDLBには、BLK11の書き込み用MOSFET n個、BLK13の書き込み用MOSFET n個、BLK14の書き込み用MOSFET n個。40

50

個の、計 $4n$ 個である。したがって、グローバルデータ対線につながるMOSFETの数の不均衡は大幅に改善されているといえる。同様に、グローバルデータ対線をGDL2とGDLB2のように配置しても、ブロックBLKの読み出し側と書き込み側の接続数が等しくなるため、接続MOSFETの数の不均衡が改善されていることは明らかである。

#### 【0060】

つぎに、GDL及びGDLBに出現する雑音の低減化について述べる。メモリの読み出し及び書き込み動作時にGDLとGDLBがプリチャージレベルからVDDあるいはVSSに変化するが、このとき、隣り合うグローバルデータ線に容量結合による雑音が発生することが知られている。図22のようにGDLとGDLBを配線すれば、例えば、GDL1に着目した場合に、グローバルデータ対線（GDL2、GDLB2）が等しい長さでGDL1の隣に配置されるため、同じ雑音がGDL2とGDLB2に等しく現れるようになる。したがってGDL2とGDLB2に生じる雑音は同一となるので、センサーアンプによる増幅時に誤動作のおそれがなくなる効果がある。10

#### 【0061】

なお、この図には一対のグローバルデータ線に4つのブロックが接続される例が示されているが、本発明はその接続されるブロック数を4つに限定することなく実施できる。

#### 【0062】

##### <実施例8>

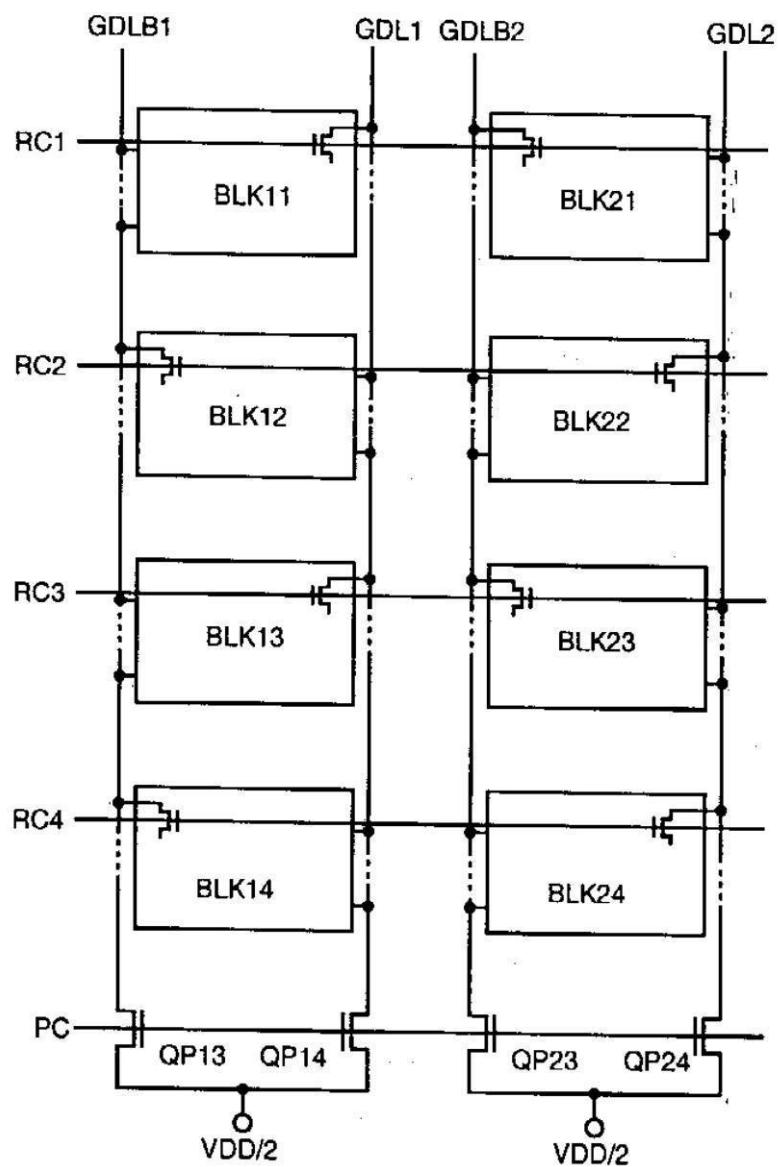

図23はグローバルデータ対線の寄生容量を平衡するための他の実施例である。これはグローバルデータ対線に接続される半数のブロック（例えば、BLK11及びBLK13）についてはGDL1に読み出し転送用MOSFETを接続し、GDLB1に書き込み用MOSFETを接続させ、残りの半数のブロック（例えば、BLK12とBLK14）についてはGDL1に書き込み用MOSFETを接続し、GDLB1に読み出し転送用MOSFETを接続している。これにより、BLK11が選択されている場合には、GDL1につながるMOSFETは $3n+2$ 個、GDLB1につながるMOSFETは $2n+2$ 個となる。これは容量の不均衡を解消するために、グローバルデータ対線を交差させない構造を用いたものである。配線の交差は、通常2層以上のメタル配線層を用いるため、本発明は使用する配線層を削減できる。したがって、限られた配線層を他の信号線及び電源線に割り当てられることによる省面積化の効果がある。なお、この図には、隣り合うグローバルデータ対線に接続されるブロックの構成が、例えばBLK11とBLK21はグローバルデータ線に関して鏡像関係に配置されているが、鏡像関係に配置しなくてもよい。ブロックの配置方法は、レイアウトのしやすさ等で決めればよい。20

#### 【0063】

##### <実施例9>

図24は、上述したメモリセルにおいて、さらにGDL及びGDLBに生じる寄生容量を平衡するための別の実施例を説明するための動作波形図である。ここでは図13の実施例に記載した例を用いて説明する。この実施例は、メモリセルの記憶情報をグローバルデータ線に伝達するための制御信号の制御方法にかかるものである。この実施例では、制御信号RC1により読み出し転送用MOSFETをオンしてグローバルデータ線GDLに読み出しデータを転送した後、センサーアンプにて増幅する前に読み出し転送用MOSFETをオフにすることを特長とする。これにより選択されたブロックの $n$ 個のQRが電気的にGDLと遮断されるため、この容量がセンサス時に負荷容量として寄与しない。したがって、GDL及びGDLBに接続されるMOSFETの数は、それぞれ $2n+2$ 個となり、寄生容量の不均衡がさらに無くなるという効果がある。30

#### 【0064】

本発明により、ゲインセルを用いたDRAM回路において従来必須であったダミーセルが必要となるため、面積が小さくなり製造コストが安くなる効果がある。また、階層データ線構造とすることで、高速動作が可能となる効果がある。

#### 【図面の簡単な説明】

#### 【0065】

【図1】(a)は本発明の最も基本的な構成を示す1実施例であり、(b)、(c)はその動作波形図。

【図2】(a)はCMOSラッチ回路により構成される説明図であり、(b)は電源にスイッチ

10

20

30

40

50

のあるCMOSラッチ型センスアンプの説明図。

【図3】(a)は読み出し用と書き込み用ワード線が同じ3トランジスタDRAMの回路図であり、(b)はそのワード線駆動の波形図。

【図4】(a)は読み出し用と書き込み用ワード線が分離された3トランジスタDRAMの回路図であり、(b)はそのワード線駆動の波形図。

【図5】この発明にかかる半導体集積回路に構成されるメモリ回路の1実施例を示す要部回路。

【図6】図5のメモリ回路の書き込み動作の一例を説明するための波形図。

【図7】図5のメモリ回路の読み出し動作の一例を説明するための波形図。

【図8】図5のメモリセル周りのレイアウトの1実施例を示す図。 10

【図9】(a)は図8のa-a'断面の断面図、(b)は図8のb-b'断面の断面図。

【図10】(a)は図8のc-c'断面の断面図、及び、(b)は図8のd-d'断面の断面図。

【図11】この発明にかかる半導体集積回路に構成されるメモリ回路の別の実施例を示す要部回路。

【図12】第10図のメモリ回路の書き込み動作の一例を説明するための波形図。

【図13】この発明にかかる半導体集積回路に構成されるメモリ回路の別の実施例を示す要部回路。

【図14】図13のメモリ回路の書き込み動作の一例を説明するための波形図。

【図15】図13の実施例におけるメモリセル周りのレイアウトの1実施例を示す図。 20

【図16】(a)は図15のe-e'断面の断面図、(b)は図14のf-f'断面の断面図。

【図17】(a)は図15のg-g'断面の断面図、及び(b)は図14のh-h'断面の断面図。

【図18】本発明のさらに別の実施例。(a)は図2(b)のようなセンスアンプを用いた例を示す図であり、(b)は図2の(a)のようなセンスアンプを用いた例を示す図。

【図19】図17(a)の書き込み動作を示す動作波形図である。

【図20】図17(b)の書き込み動作を示す動作波形図である。

【図21】本発明のさらに別の実施例。

【図22】グローバルデータ線の配置方法の1実施例。

【図23】ブロックとグローバルデータ線の結線方法を示す1実施例。

【図24】グローバルデータ線の電気的平衡を実現する1実施例。

【符号の説明】 30

【0066】

VDD...低圧電源、VSS...VDDの接地電位、VDL...読み出し時のワード線電位、VDH...書き込み時ワード線電位、WLR on...読み出し開始、SA on...センスアンプ起動、WLW on...書き込み開始、...センスアンプの感度、BLK...ブロック、n...蓄積ノード、MC...メモリセル、QR...読み出し用MOSFET、QW...書き込み用MOSFET、QS...蓄積MOSFET、QP...プリチャージ用MOSFET、QY...列選択スイッチ用MOSFET、QRT...読み出し転送用MOSFET、QWT...書き込み転送用MOSFET、DL...読み出しはうせんデータ線、DLB...書き込みデータ線、GDL...グローバルデータ線、GDLB...グローバルデータ線(GDLの相補信号用)、SA...センスアンプ、IO...共通IO線、IOB...共通IO線(IOの相補信号用)、WL...ワード線、PC...プリチャージ信号、YS...列選択信号、RWC...ブロック選択信号、W...書き込み制御信号、RC...読み出し制御信号、XDEC...行系デコーダ、XDRV...ワードドライバ、YDEC...列系デコーダ、YDRV...ドライバ、MA...メインアンプ、DIB...データインプットバッファ、DOB...データアウトプットバッファ、VGC...電源発生回路、RSW...読み出しスイッチ、WSW...書き込みスイッチ、SAP...センスアンプ起動信号(P型MOSFETのソース側)、SAN...センスアンプ起動信号(N型MOSFETのソース側)、SPE...センスアンプ起動信号(P側)、SNE...センスアンプ起動信号(N側)、M1~M3...メタル配線層、ND...MOSFET拡散層、LCT...ローカルコンタクト、CT1~2メタル層間コンタクト、P-SUB...P型シリコン基板、MGDL...メインデータ線、MGDLB...メインデータ線(MGDLの相補信号用)Qi...メインデータ線とグローバルデータ線の隔絶用MOSFET、IC...メインデータ線とグローバルデータ線の隔絶制御信号、DRAMC...DRAMコア回路。 40

【図2】

図 2

【図3】

図 3

【図7】

図 7

【図4】

図 4

【図19】

図 19

【図 24】

図 24

【図1】

図 1

(a)

(b)

(c)

【図5】

図 5

【図6】

6

【図8】

図 8

【図9】

四 9

【図 10】

図 10

(a)

(b)

【図 11】

図 11

【図 1 2】

図 1 2

【図 13】

図 13

【図 14】

図 14

【図15】

図 15

【図16】

図 16

(a)

(b)

【図17】

図 17

(a)

(b)

【図18】

図 18

【図20】

図 20

【図21】

図 21

【図22】

図 22

【図 23】

図 23

---

フロントページの続き

(56)参考文献 特開昭63-000894(JP,A)

特開昭62-226494(JP,A)

特開2000-036194(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 40