### (12) STANDARD PATENT

(11) Application No. AU 2012294932 B2

## (19) AUSTRALIAN PATENT OFFICE

(54) Title

High-efficiency solar photovoltaic cells and modules using thin crystalline semiconductor absorbers

(51) International Patent Classification(s)

**H01L 31/042** (2006.01)

H01L 31/18 (2006.01)

(21) Application No: 2012294932 (22) Date of Filing: 2012.08.09

(87) WIPO No: WO13/022479

(30) Priority Data

(31) Number (32) Date (33) Country 61/521,743 2011.08.09 US 61/521,754 2011.08.09 US

(43) Publication Date: 2013.02.14(44) Accepted Journal Date: 2016.08.11

(71) Applicant(s) Solexel, Inc.

(72) Inventor(s)

Moslehi, Mehrdad M.;Kapur, Pawan;Kramer, K-Josef;Rana, Virendra V.;Seutter, Sean;Deshpande, Anand;Calcaterra, Anthony;Olsen, Gerry;Manteghi, Kamran;Stalcup, Thom;Kamian, George D.;Wang, David xuan-Qi;Su, Yen-Sheng;Wingert, Michael

(74) Agent / Attorney

Freehills Patent Attorneys, Level 43 101 Collins Street, Melbourne, VIC, 3000

(56) Related Art

WO 2011/072161

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2013/022479 A3

(43) International Publication Date 14 February 2013 (14.02.2013)

H01L 31/042 (2006.01) H01L 31/18 (2006.01)(21) International Application Number:

(51) International Patent Classification:

PCT/US2012/000348

(22) International Filing Date:

9 August 2012 (09.08.2012)

(25) Filing Language:

English

(26) Publication Language:

pitas, CA 95035-7405 (US).

English

(30) Priority Data:

61/521,754 9 August 2011 (09.08.2011) US 61/521,743 9 August 2011 (09.08.2011) US

61/521,743 9 August 2011 (09.08.2011) US

(71) Applicant (for all designated States except US):

SOLEXEL, INC. [US/US]; 1530 McCarthy Blvd., Mil-

(72) Inventors; and

(75) Inventors/Applicants (for US only): MOSLEHI, Mehrdad, M. [US/US]; 956 Stanley Ave., Los Alto, CA 94024 (US). KAPUR, Pawan [US/US]; 565 Matadero Ave., Palo Alto, CA 94306 (US). KRAMER, K.-Josef [US/US]; 824 Riverside Dr., San Jose, CA 95125 (US). RANA, Virendra, V. [US/US]; 101 Andre Court, Los Gatos, CA 95032 (US). SEUTTER, Sean [US/US]; 629 Har-

risburg Place, San Jose, CA 95133 (US). **DESHPANDE**, **Anand** [US/US]; 4691 Albany Circle, Unit 127, San Jose, CA 95129 (US). **CALCATERRA**, **Anthony** [US/US]; 1775 Momong. Dr. R108, Milpitas, CA 95035 (US). **OLSEN**, **Gerry** [US/US]; 263 Wabash Ave., San Jose, CA 95128 (US). **MANTEGHI**, **Kamran** [US/US]; 508 Verano Ct., San Jose, CA 95111 (US). **STALCUP**, **Thom** [US/US]; 1530 McCarthy Blvd., Milpitas, CA 95035 (US). **KAMIAN**, **George**, **D**. [US/US]; 425 Silverwood Drive, Scotts Valley, CA 95066 (US). **WANG**, **David**, **Xuan-Qi** [US/US]; 91831 Via San Miguel, Fremont, CA 94539 (US). **SU**, **Yen-Sheng** [US/US]; 1530 McCarthy Blvd., Milpitas, CA 95035 (US). **WINGERT**, **Michael** [US/US]; 140 Wilder Ave., Los Gatos, CA 95030 (US).

- (74) Agent: WOOD, John; Hulsey, P.C. Intellectual Property Lawyers, 919 Congress Ave., Suite 919, Austin, TX 78701 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI,

[Continued on next page]

(54) Title: HIGH-EFFICIENCY SOLAR PHOTOVOLTAIC CELLS AND MODULES USING THIN CRYSTALLINE SEMICONDUCTOR ABSORBERS

(57) Abstract: Fabrication methods and structures relating to backplanes for back contact solar cells that provide for solar cell substrate reinforcement and electrical interconnects as well as Fabrication methods and structures for forming thin film back contact solar cells are described.

#

- NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### Published:

- with international search report (Art. 21(3))

- (88) Date of publication of the international search report: 16 May 2013

# HIGH-EFFICIENCY SOLAR PHOTOVOLTAIC CELLS AND MODULES USING THIN CRYSTALLINE SEMICONDUCTOR ABSORBERS

### **CROSS-REFERENCE TO RELATED APPLICATIONS**

This application claims priority to U.S. Provisional Patent Application Serial No. 61/521,754 and 61/521,743 both filed August 9, 2011, which are hereby incorporated by reference in its entirety.

#### **FIELD**

The present disclosure relates in general to the fields of photovoltaics and semiconductor microelectronics. More particularly, the present disclosure relates to the methods, architectures, and apparatus related to high-efficiency back-contact crystalline silicon photovoltaic solar cells.

#### **BACKGROUND**

Currently, crystalline silicon (both multi-crystalline and mono-crystalline silicon) has the largest market share in the photovoltaics (PV) industry, currently accounting for about 85% of the overall global PV market share. Although moving to thinner crystalline silicon solar cells is long understood to be one of the most potent and effective methods for PV cost reduction (because of the relatively high material cost of crystalline silicon wafers used in solar cells as a fraction of the total PV module cost), utilizing thinner crystalline wafers is hampered by the problem of thin wafers being extremely fragile, mechanical breakage during wafer handling and cell processing, and the resulting production yield losses caused by thin and fragile silicon wafers. Other problems include inadequate light trapping in the thin cell structure because silicon is an indirect bandgap semiconductor material and absorption of longer wavelength red and infrared photons (particularly those in the wavelength range of about 900 nm to 1150 nm) requires relatively long optical path lengths - often much larger than the wafer thickness itself. Further, using known designs and manufacturing technologies it is often difficult to balance the requirement of high mechanical yield and reduced wafer breakage rate with high manufacturing yields in PV factories in a cost effective manner.

Relating to substrate (semiconductor absorber) thickness, for current crystalline silicon wafer solar cells, moving even slightly thinner than the current thickness range of 140  $\mu m$  to 200

μm starts to severely compromise mechanical yield during cell and module manufacturing. This is particularly a big challenge for larger cell sizes such as 156 mm x 156 mm and 210 mm x 210 mm cells (compared to the smaller 125 mm x 125 mm cells). Thus, manufacturable solutions directed to process very thin solar cell structures, such as with cell semiconductor absorbers thinner than about 100 μm down to micron-size-scale and submicron thickness, often must utilize a cell process during which the cell is fully supported by a either a temporary and/or a permanent host carrier throughout the process flow, or a cell process which utilizes a novel self-supporting, stand-alone, substrate with an accompanying structural innovation. This structural innovation must allow the cell substrate to be extremely robust against breakage in high throughput solar cell and module factories. Examples of the latter are the novel 3-Dimensional honeycomb and pyramidal structures formed with crystalline silicon thin films.

On the cell architecture side, back-junction/back contacted monocrystalline semiconductor (such as monocrystalline silicon) solar cells are conducive to very high efficiency. This is primarily because there is no metal shading associated losses on the front side as well as no emitter on the front which helps result in a high blue response. Moreover, the use of n-type base enables much higher minority carrier lifetime compared to p-type base, as well as no Light-Induced Degradation (LID). In addition, the back-contact/back-junction cell with n-type base may use well-established silicon nitride frontside passivation and anti-reflection coating layer with positive fixed charges in the passivation layer (or layer stack) comprising silicon nitride providing for improved frontside surface passivation with reduced Frontside Surface Recombination Velocity (FSRV) enabled by field-assisted passivation. Further, backside metal may be made thicker and with a higher area coverage (e.g., well over 90%) to ensure very low series resistance (or very high metal interconnect electrical conductivity) without worrying about the trade-off with shading that is often a consideration for front contacted cells. Back contacted/back junctions cells are, in particular, highly conducive to being combined with very thin (e.g., solar cell substrates for at least two distinct reasons. Firstly, high-efficiency back contacted/back junction cells have a stringent requirement of having minority carrier diffusion length (known as Leff) at least 5x (by a factor of at least approximately 5) the thickness of the substrate (or the active crystalline semiconductor absorber). A very thin (e.g., with crystalline semiconductor layer thickness less than about 80 microns and more preferably less than about 50 microns) solar cell substrate enables this requirement without demanding a very high bulk

substrate lifetime or a very high quality material, thus, can be done in practice on a cheaper starting material having eliminated the most stringent substrate quality requirements. This indirectly gives a further cost advantage: the quality of the material can be relaxed in addition to it being thinner. A second reason is related to the process flow which enables fabrication of the back contact/back junction cells (will be discussed further in the following sections). Because back contacted cell architecture and related process flow may be catered to have all high temperature process steps (i.e., any cell process steps with process temperatures in the range of approximately 400°C to ~1150°C) on one side of the cell, the requirement for a carrier of the thin substrate when it is going through processing on the other sides are considerably eased. Thus, using a very thin substrate (e.g., with crystalline semiconductor layer thickness less than about 80 microns and more preferably less than about 50 microns) in conjunction with a back-contacted/back-junction architecture may represent an ideal solar cell combination.

In the past, there have been attempts in solar PV R&D to use carriers such as glass for thin substrates; however, these carriers have suffered from serious limitations including relatively low maximum processing temperatures in the case of soda lime glass (or most other non-silicon foreign materials), with the processing temperatures being limited to well below approximately 400°C - which potentially may compromise the solar cell efficiency. There have also been attempts to make small area (for example, cell areas well below 10 cm<sup>2</sup>) thin cells which do not have serious breakage concerns (while they still suffer from the thermal processing limitations, including limitation of process temperatures to well below approximately 400°C); however, large cell areas (areas well above 100 cm<sup>2</sup>) are often required for commercial viability through cost-effective manufacturing.

#### **BRIEF SUMMARY**

Therefore, a need has arisen for fabrication methods and designs relating to a back contact solar cells. In accordance with the disclosed subject matter, methods, structures, and apparatus for fabricating back-contact solar cells are herein disclosed. These innovations substantially reduce or eliminate disadvantages and problems associated with previously developed back contact solar cells.

According to one aspect of the disclosed subject matter, fabrication methods and structures relating to backplanes for back contact solar cells that provide for solar cell substrate reinforcement and electrical interconnects are described. In one embodiment, the back contact back junction solar cell comprises a substrate having a light capturing frontside surface, a doped base region, and a doped backside emitter region with a polarity opposite the doped base region. A metallization pattern is positioned on the backside of the solar cell and a permanent reinforcement provides support to the cell.

In one embodiment, a back contact back junction thin solar cell is provided comprising:

- a deposited semiconductor layer, comprising:

- a light capturing frontside surface with a passivation layer,

- a doped base region, and

- a doped backside emitter region with a polarity opposite said doped base

region;

a backside passivation dielectric layer and patterned reflective layer on said backside emitter region;

backside emitter contacts and backside base contacts connected to metal interconnects forming a first level interdigitated metallization pattern on the backside of said back contact back junction thin solar cell; and

at least one permanent support reinforcement positioned on the backside of said back contact back junction thin solar cell, where said permanent reinforcement structure contains prepreg material; and

a second metal layer which is separated from the first layer by said permanent backside support reinforcement structure, said second layer contacting to said first level metallization pattern locally through an interdigitated pattern of holes in said permanent backside support reinforcement structure.

In one embodiment, a back contact back junction thin solar cell is provided, comprising:

- a deposited semiconductor layer, comprising:

- a light capturing frontside surface with a passivation layer,

- a doped base region, and

- a doped backside emitter region with a polarity opposite said doped base

region;

a backside passivation dielectric layer and patterned reflective layer on said backside emitter region;

backside emitter contacts and backside base contacts connected to metal interconnects forming a first level interdigitated metallization pattern on the backside of said back contact back junction thin solar cell; and

at least one permanent support reinforcement positioned on the backside of said back contact back junction thin solar cell; and

a second metal layer which is separated from the first layer by said permanent backside support reinforcement structure, said second layer contacting to said first level metallization pattern locally through an interdigitated pattern of holes in said permanent backside support reinforcement structure, said second metal layer comprising at least one bus bar per polarity, wherein said first level interdigitated metallization pattern is positioned under said bus bars thereby reducing electrical shading.

In one embodiment, a back contact back junction thin solar cell is provided, comprising:

- a deposited semiconductor layer, comprising:

- a light capturing frontside surface with a passivation layer,

- a doped base region, and

- a doped backside emitter region with a polarity opposite said doped base

region;

a backside passivation dielectric layer and patterned reflective layer on said backside emitter region;

backside emitter contacts and backside base contacts connected to metal interconnects forming a first level interdigitated metallization pattern on the backside of said back contact back junction thin solar cell, wherein said emitter region is comprised of at least two regions of different dopant concentration and regions in the vicinity of said emitter contact have higher dopant concentration than regions away from said emitter contact regions; and

at least one permanent support reinforcement positioned on the backside of said back contact back junction thin solar cell; and

a second metal layer which is separated from the first layer by said permanent backside support reinforcement structure, said second layer contacting to said first level metallization pattern locally through an interdigitated pattern of holes in said permanent backside support reinforcement structure.

In one embodiment, a back contact back junction thin solar cell is provided, comprising:

a deposited semiconductor layer, comprising:

a light capturing frontside surface with a passivation layer,

a doped base region, and

a doped backside emitter region with a polarity opposite said doped base

region;

a backside passivation dielectric layer and patterned reflective layer on said backside emitter region, wherein said emitter region is comprised of a very thin layer of p+ doped amorphous silicon on top of intrinsic amorphous silicon, said emitter region backed by polycrystalline silicon germanium alloy or a conductive oxide;

backside emitter contacts and backside base contacts connected to metal interconnects forming a first level interdigitated metallization pattern on the backside of said back contact back junction thin solar cell; and

at least one permanent support reinforcement positioned on the backside of said back contact back junction thin solar cell; and

a second metal layer which is separated from the first layer by said permanent backside support reinforcement structure, said second layer contacting to said first level metallization pattern locally through an interdigitated pattern of holes in said permanent backside support reinforcement structure.

As used herein, except where the context requires otherwise, the term "comprise" and variations of the term, such as "comprising", "comprises" and "comprised", are not intended to exclude other additives, components, integers or steps.

These and other advantages of the disclosed subject matter, as well as additional novel features, will be apparent from the description provided herein. The intent of this summary is not to be a comprehensive description of the subject matter, but rather to provide a short overview of some of the subject matter's functionality. Other systems, methods, features and advantages here provided will become apparent to one with skill in the art upon examination of the following FIGURES and detailed description. It is intended that all such additional systems, methods, features and advantages included within this description be within the scope of the claims.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

The features, nature, and advantages of the disclosed subject matter may become more apparent from the detailed description set forth below when taken in conjunction with the drawings in which like reference numerals indicate like features and wherein:

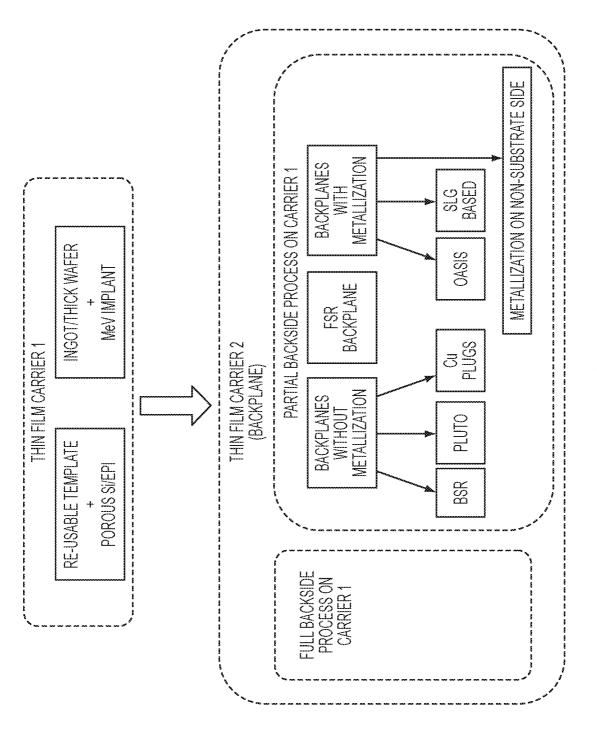

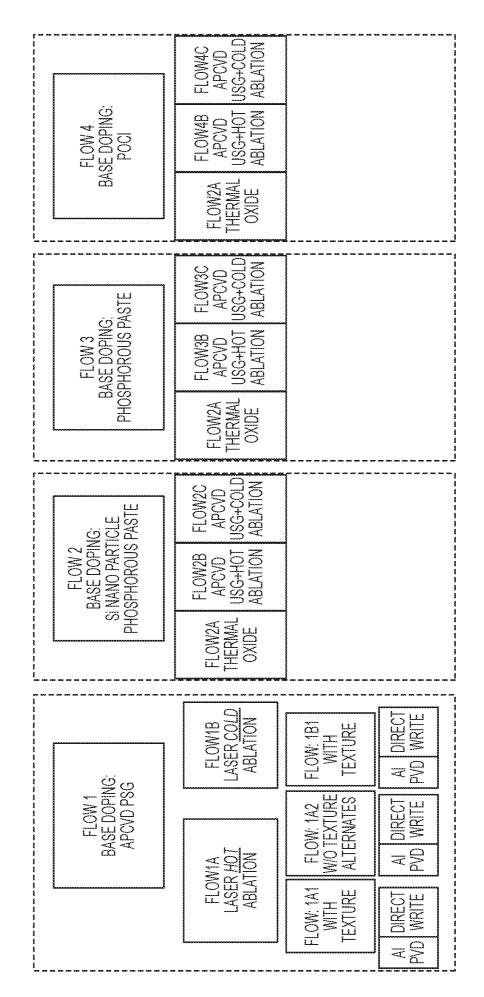

- Fig. 1 is a diagram illustrating solar cell processing carrier combinations;

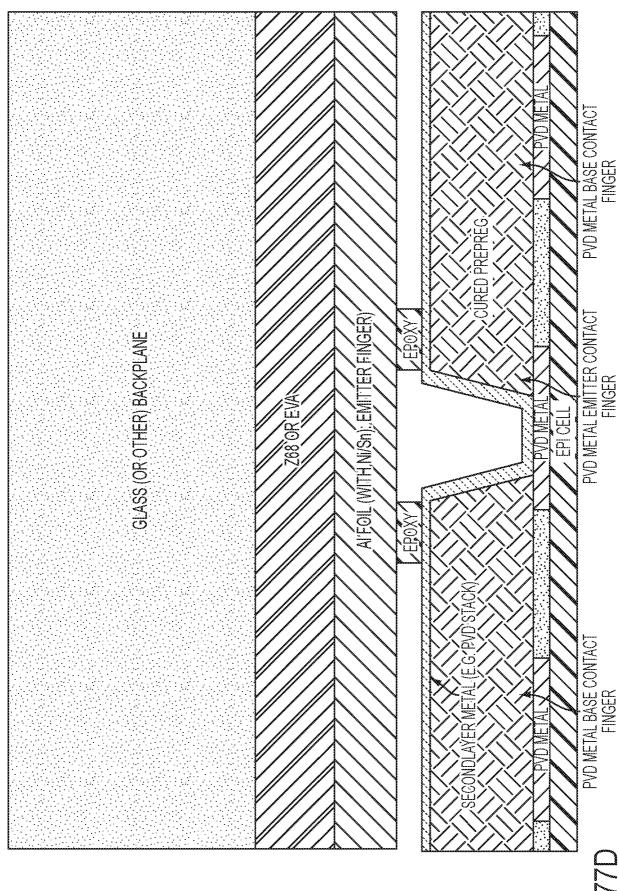

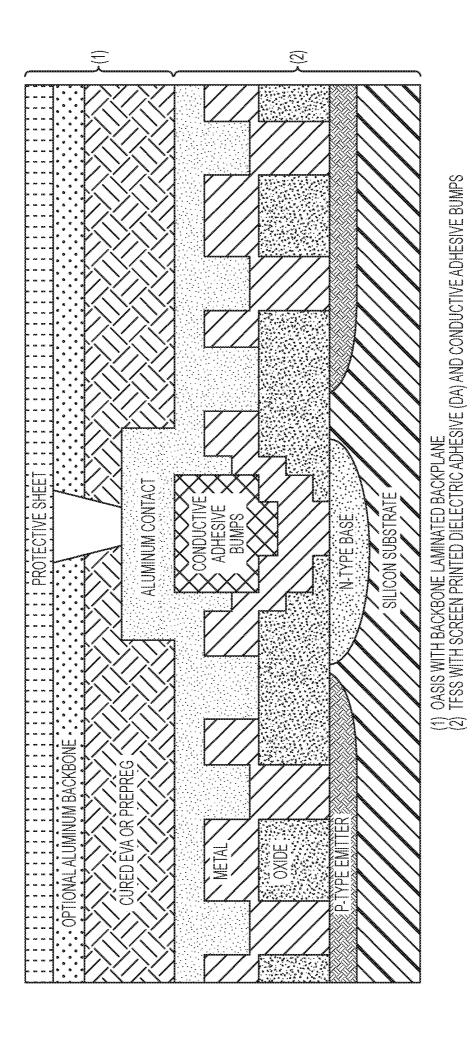

- Fig. 2 is a cross-sectional diagram of a back contact solar cell embodiment;

- Fig. 3 is a diagram illustrating ex-situ emitter process flow embodiments;

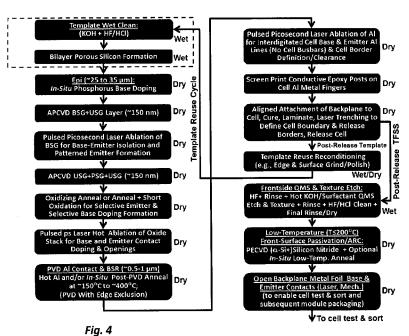

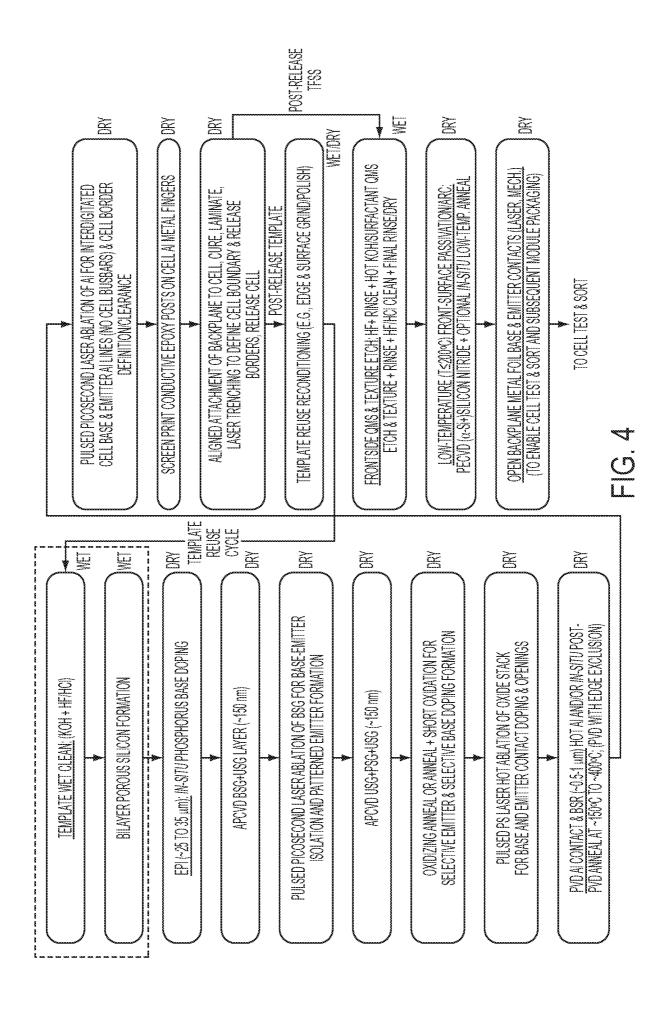

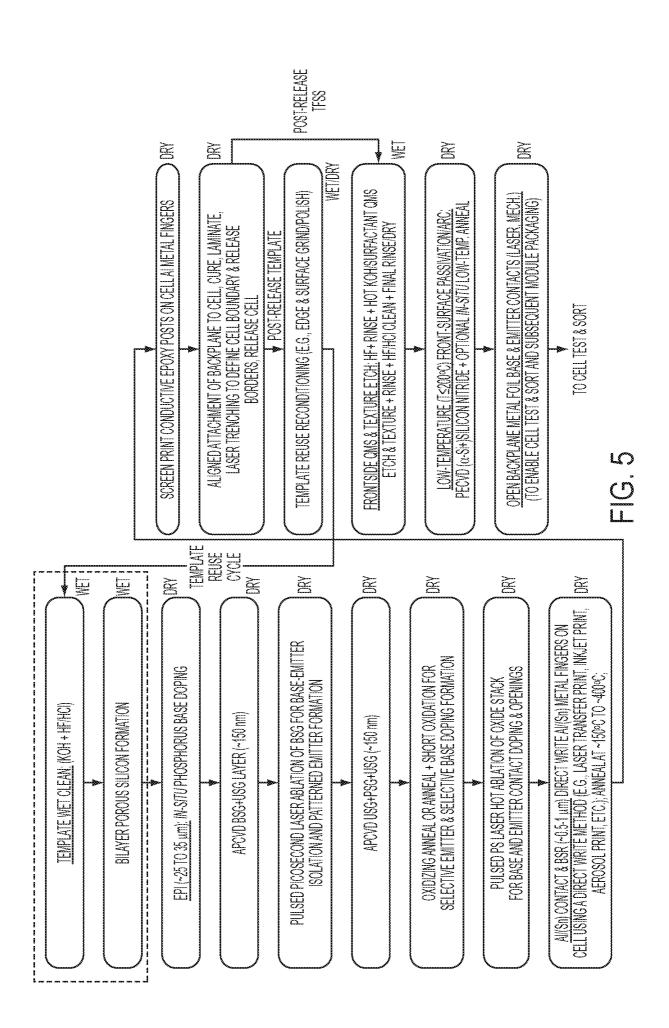

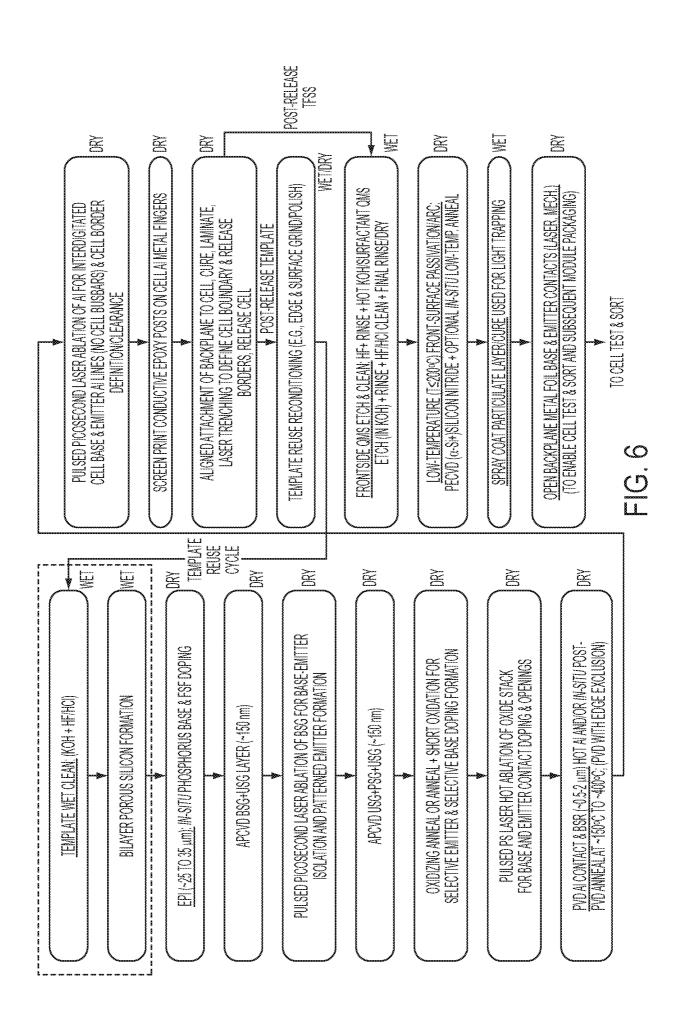

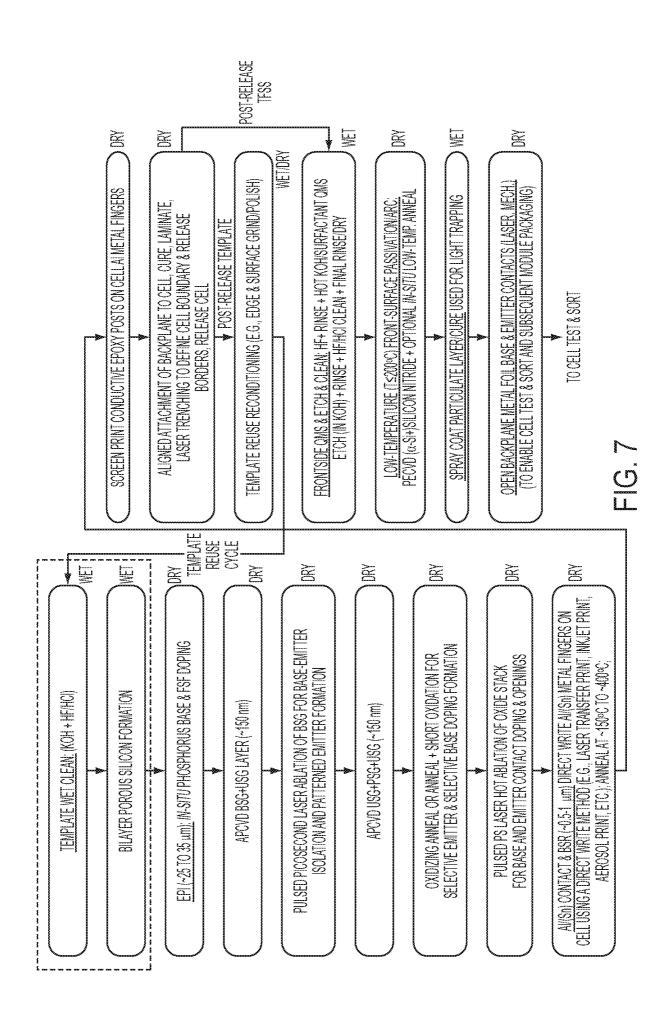

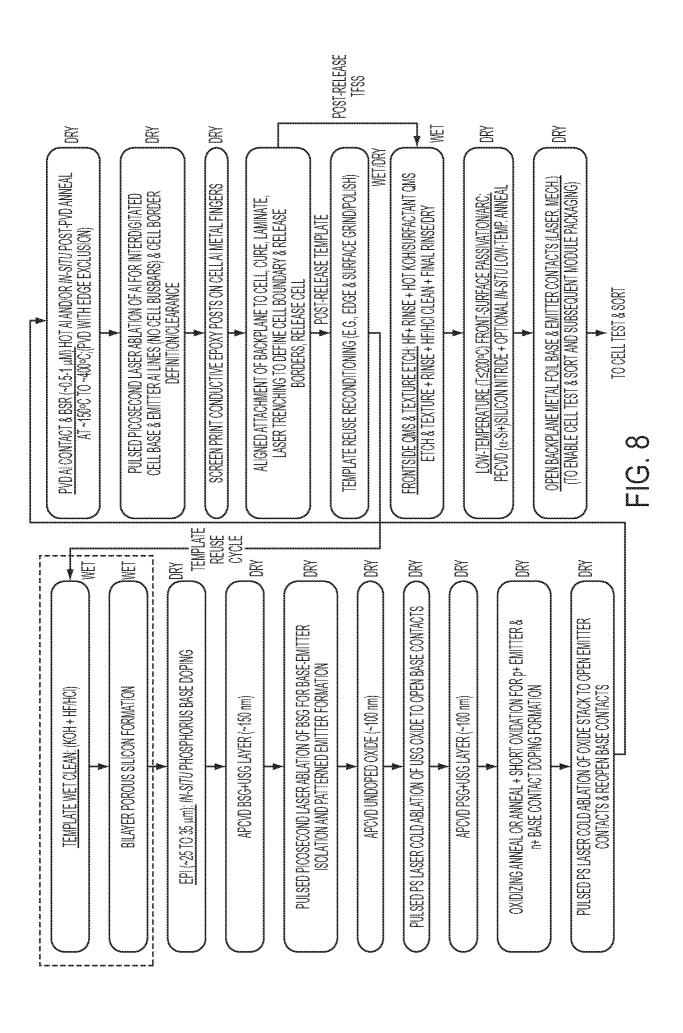

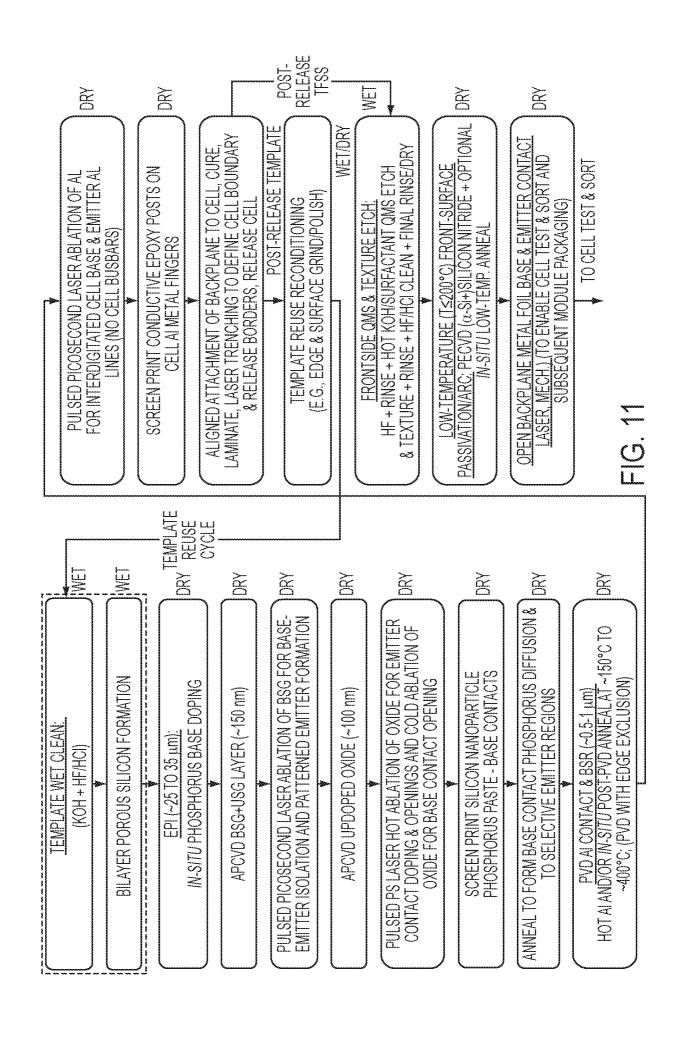

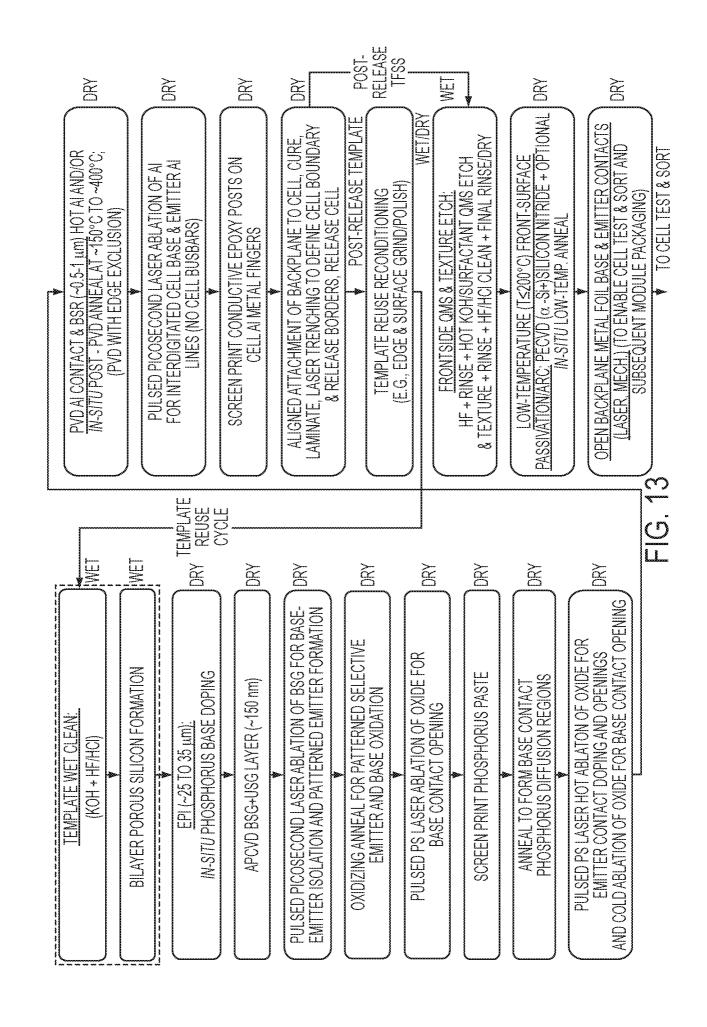

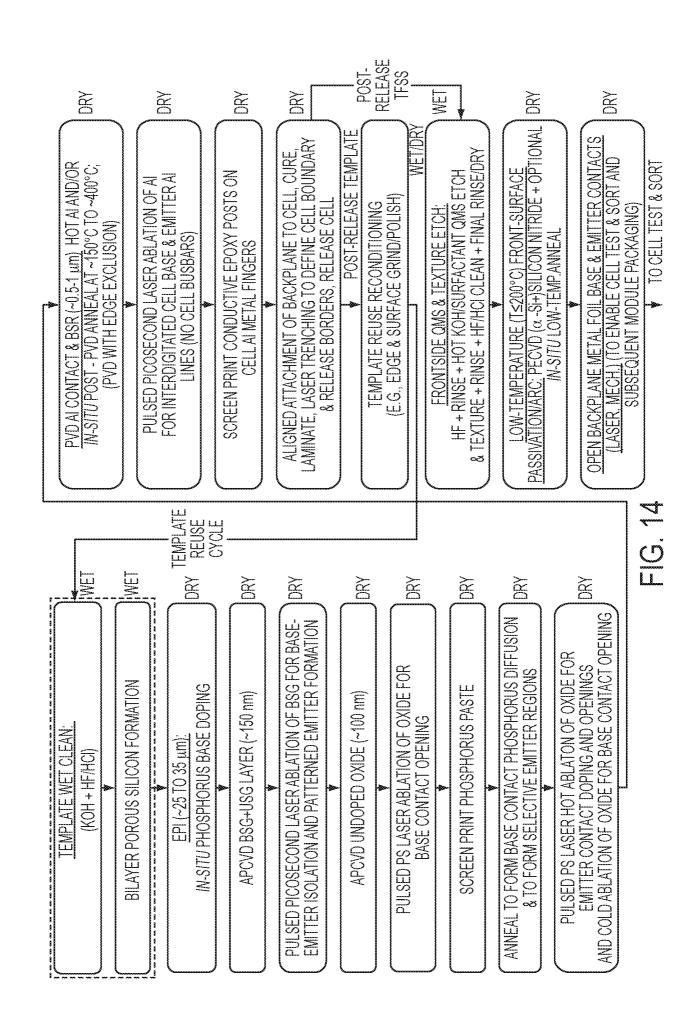

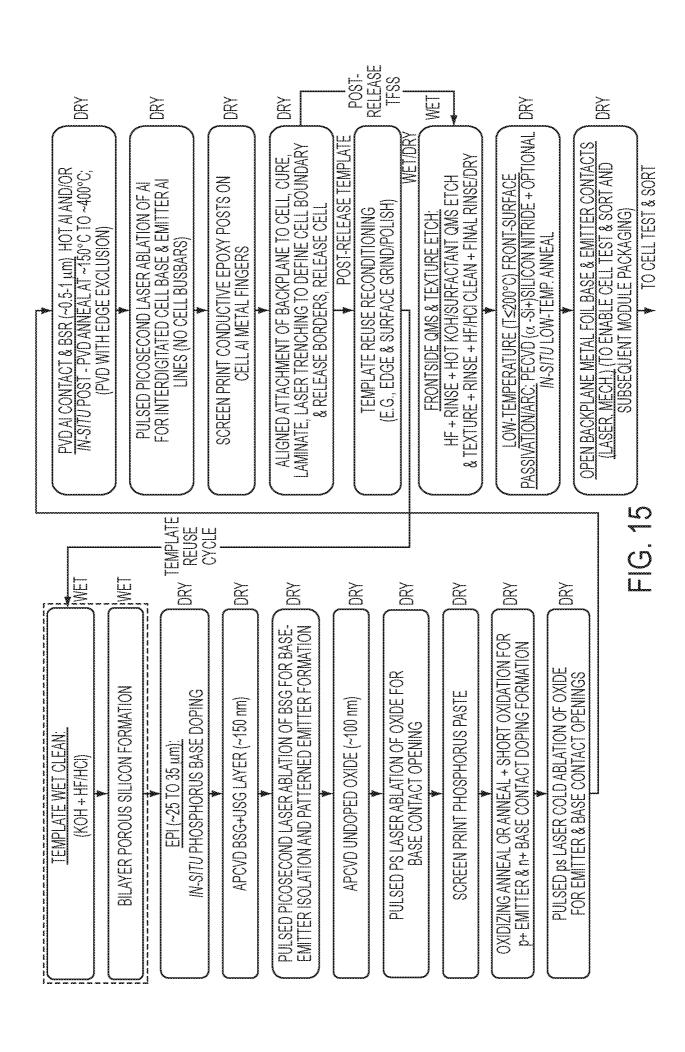

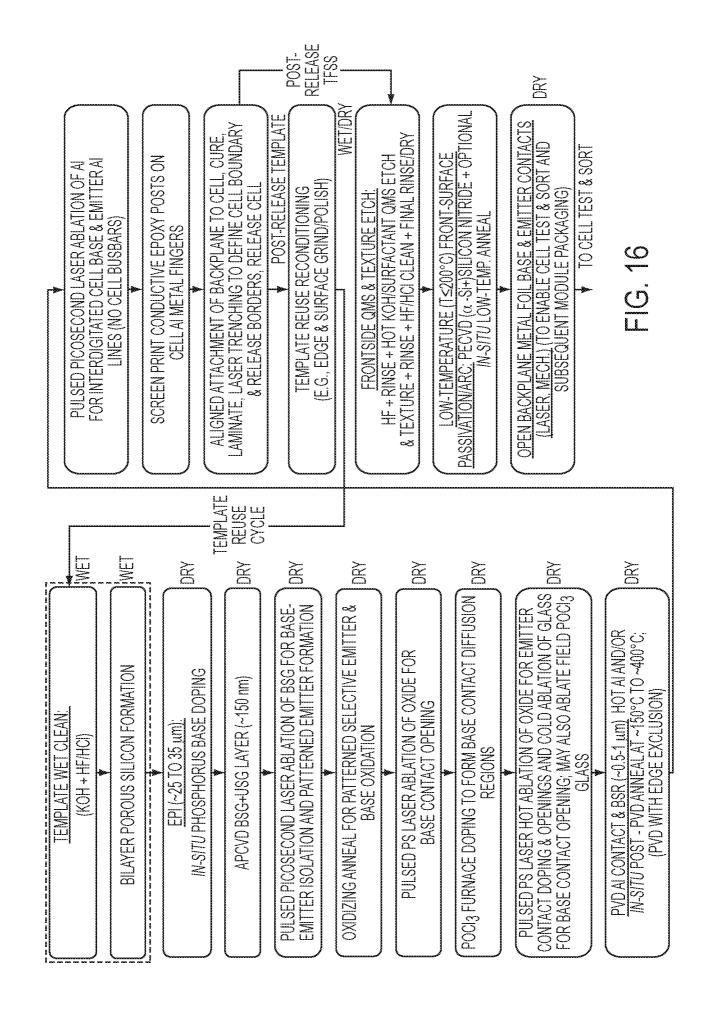

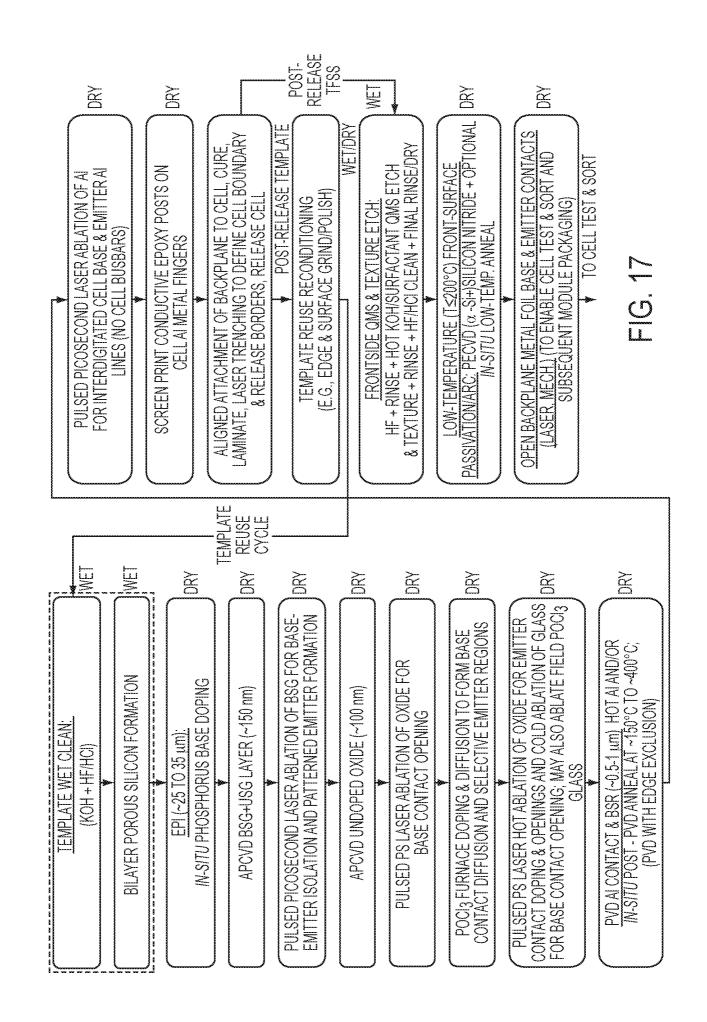

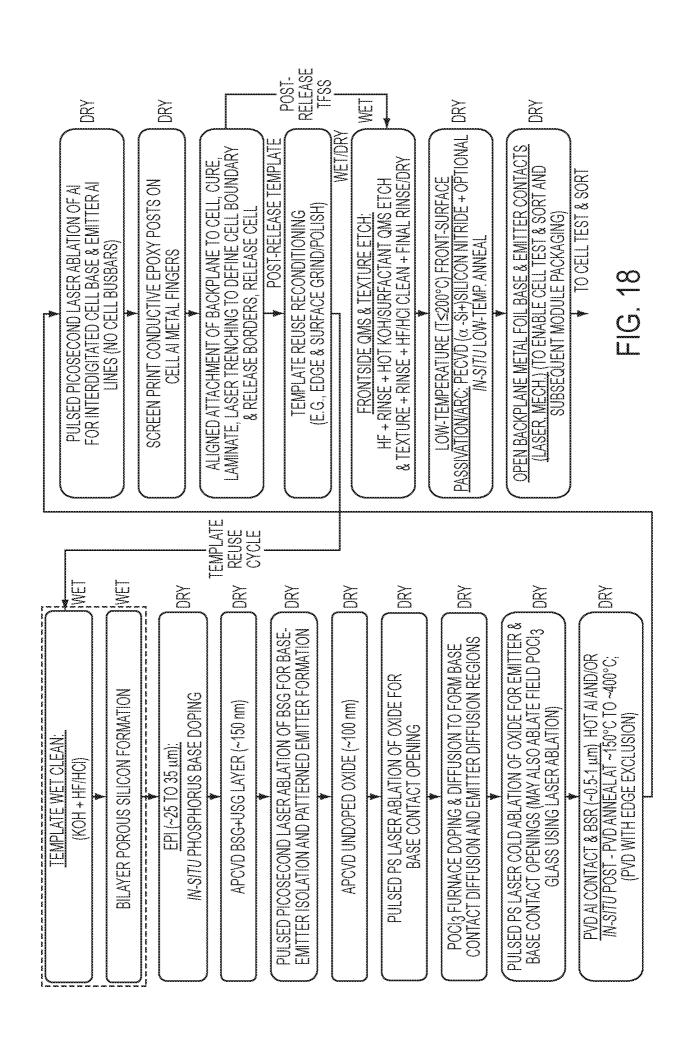

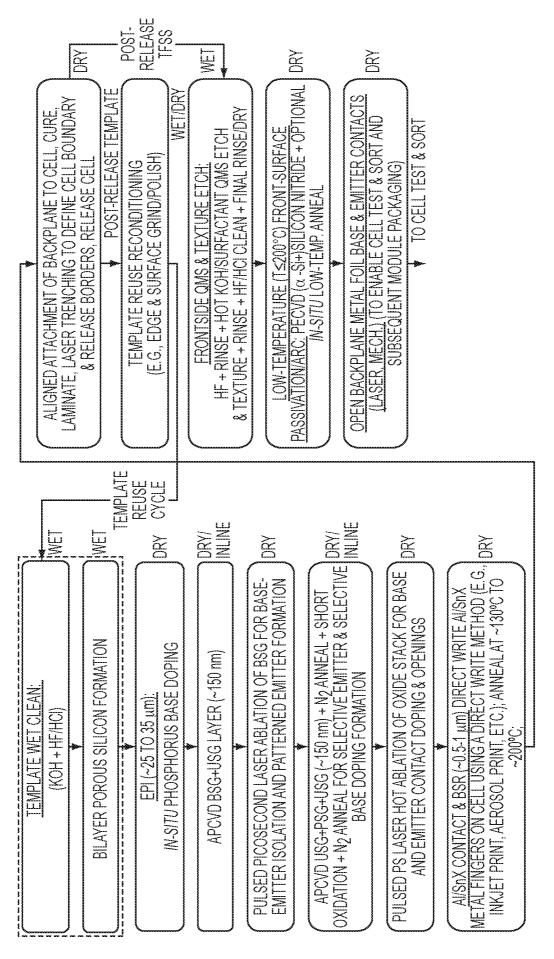

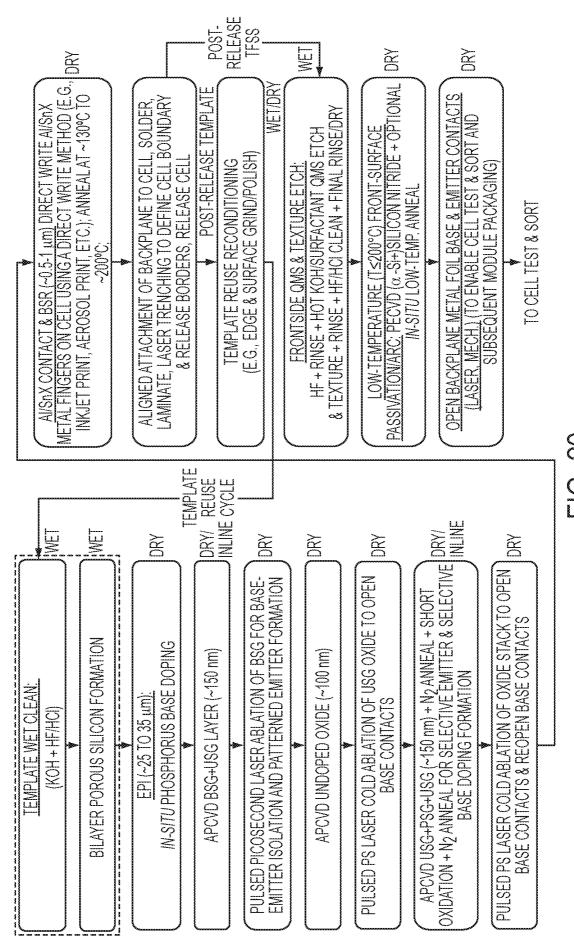

- Fig. 4 through 8 are back contact solar cell manufacturing process flows using an epitaxial substrate;

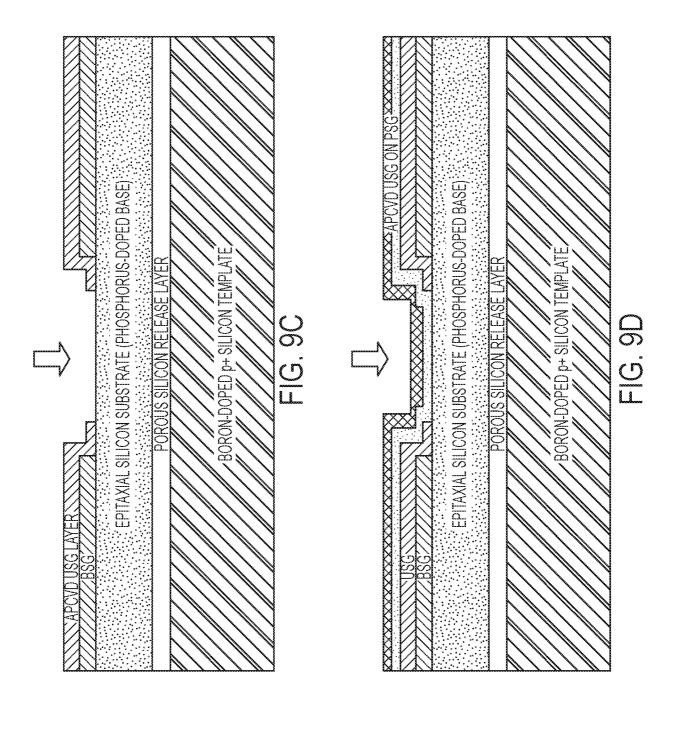

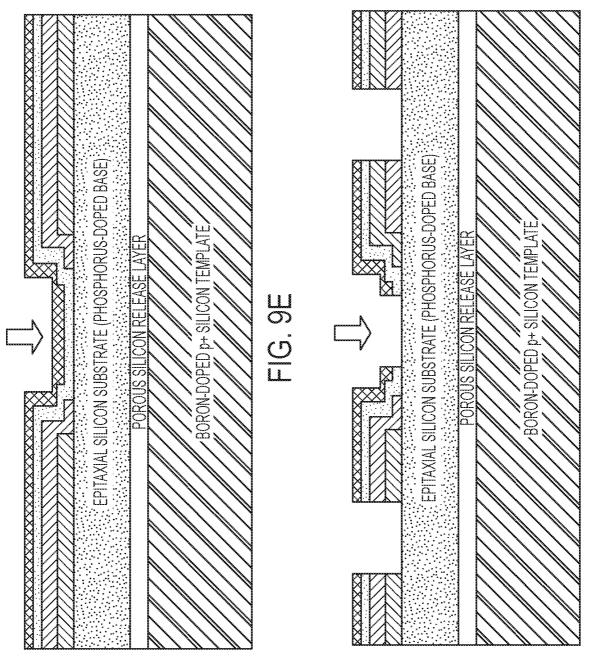

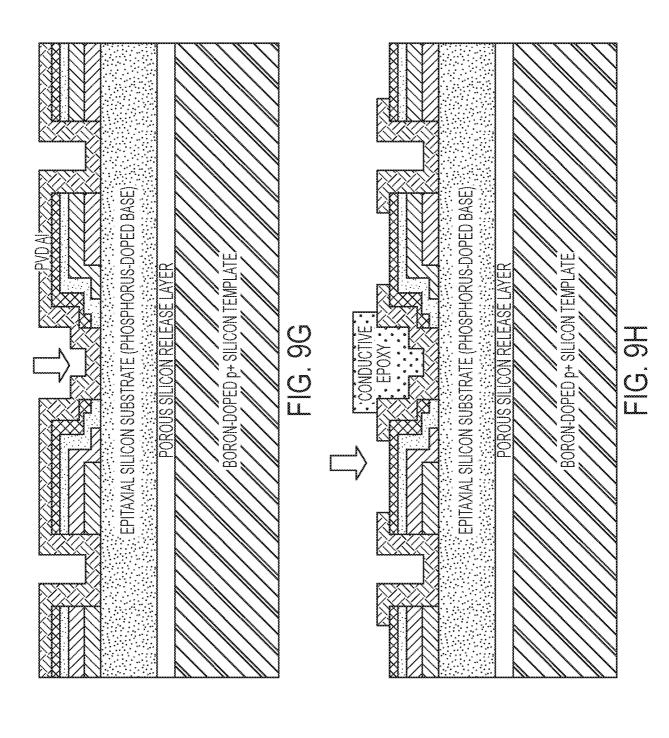

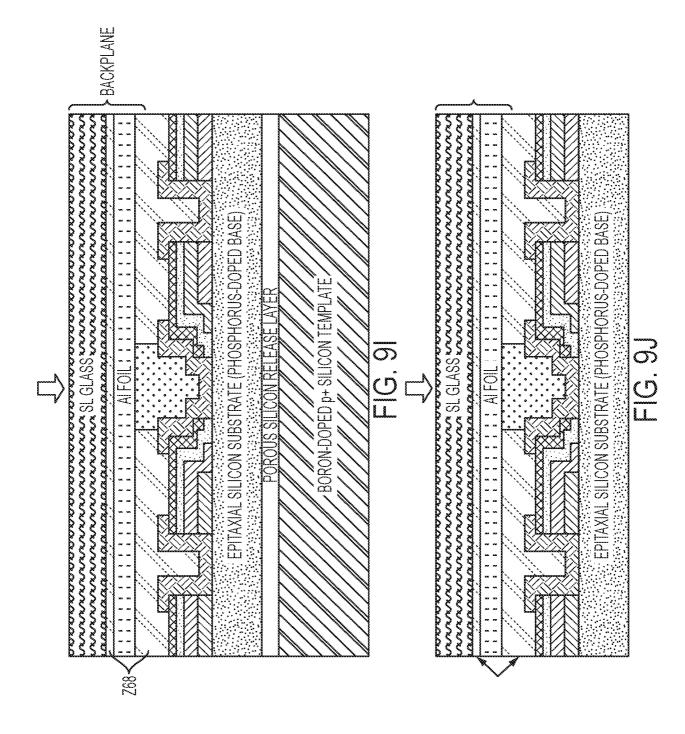

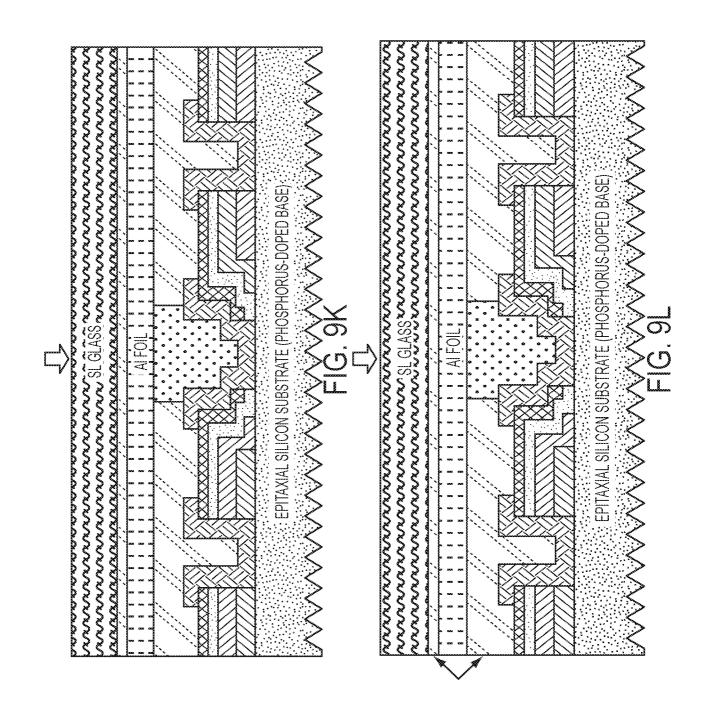

- Figs. 9A through L are cross-sectional diagrams after processing steps of a back contact solar cell;

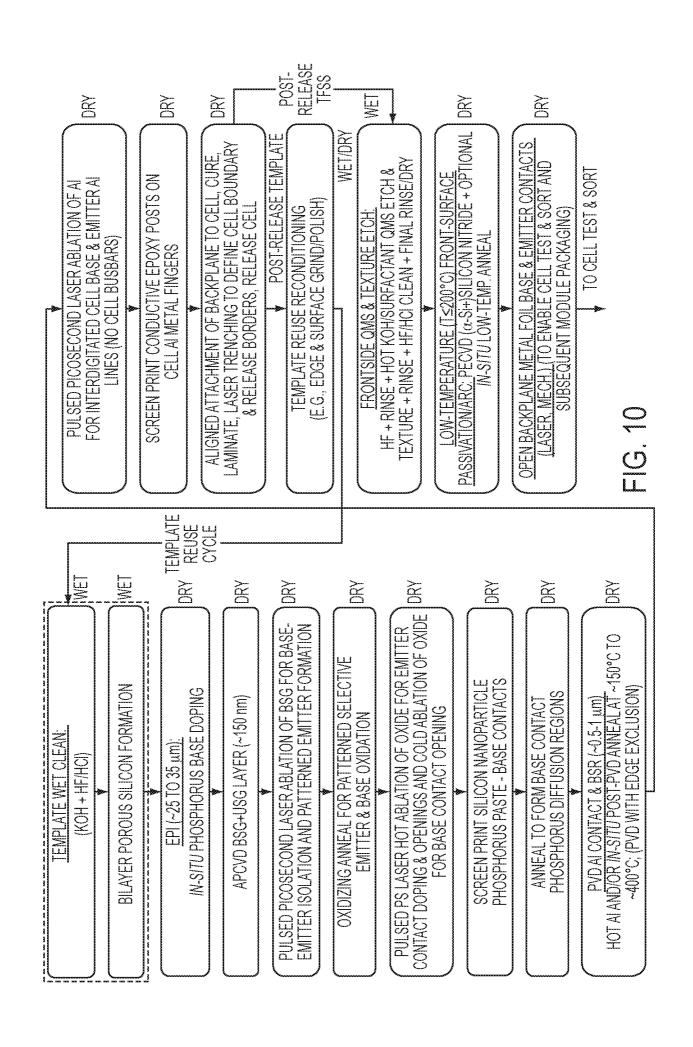

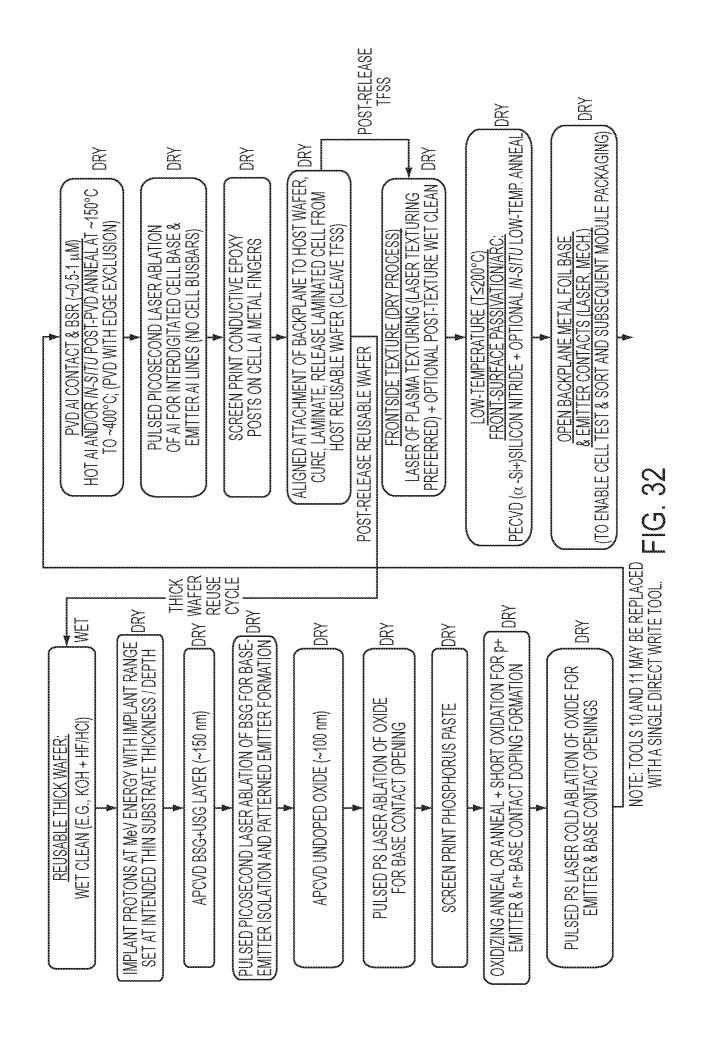

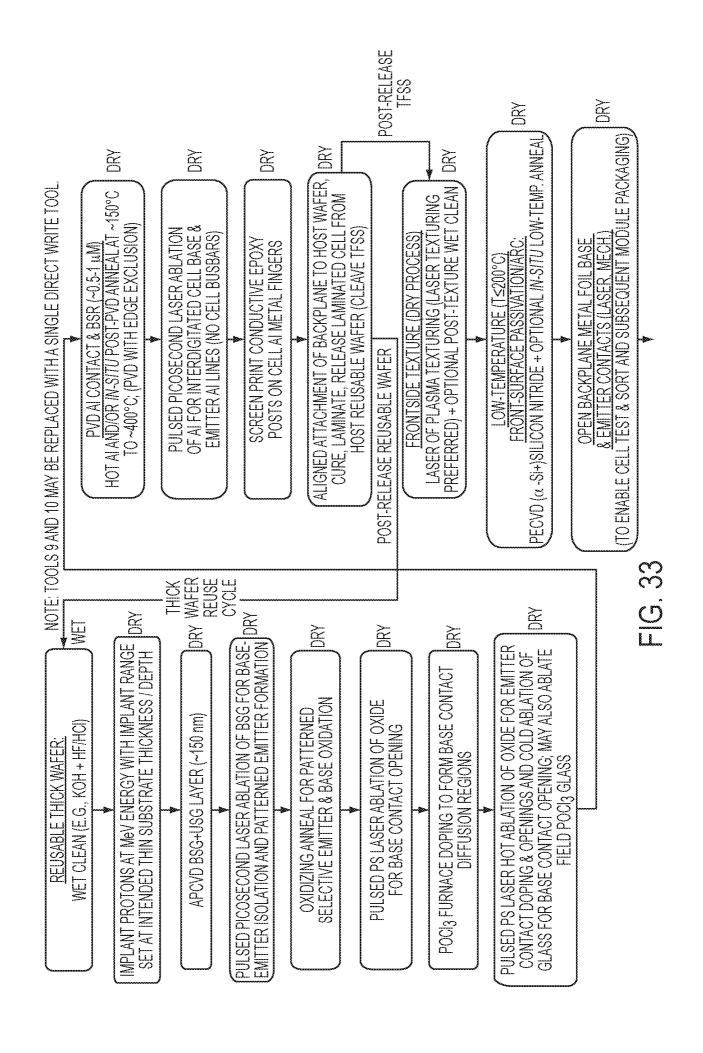

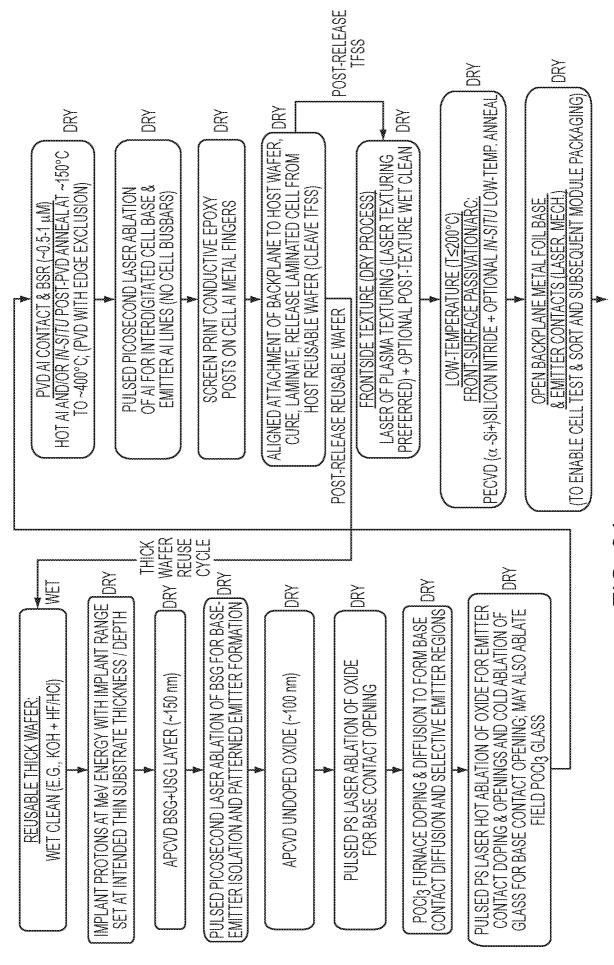

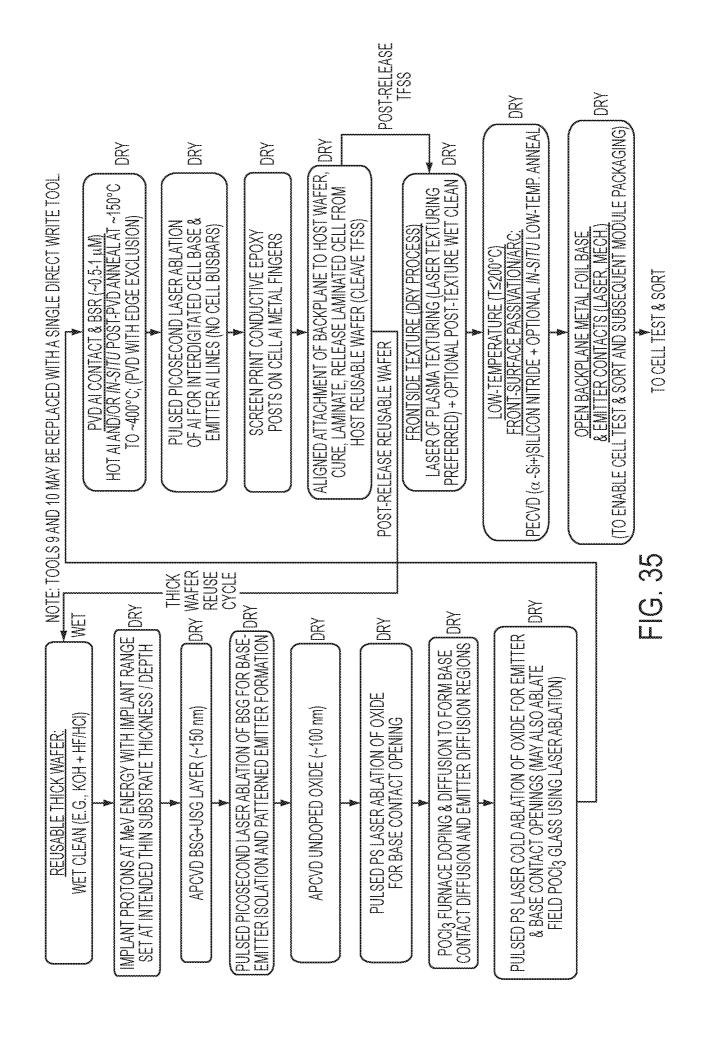

- **Figs. 10** through **21** are back contact solar cell manufacturing process flows using epitaxial substrate:

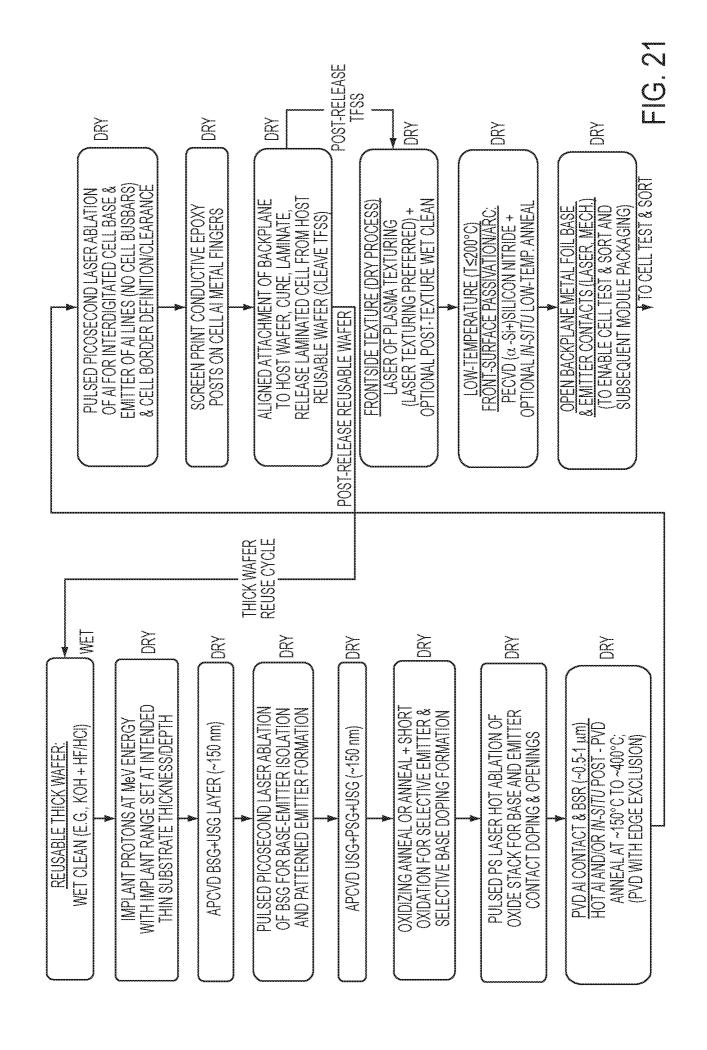

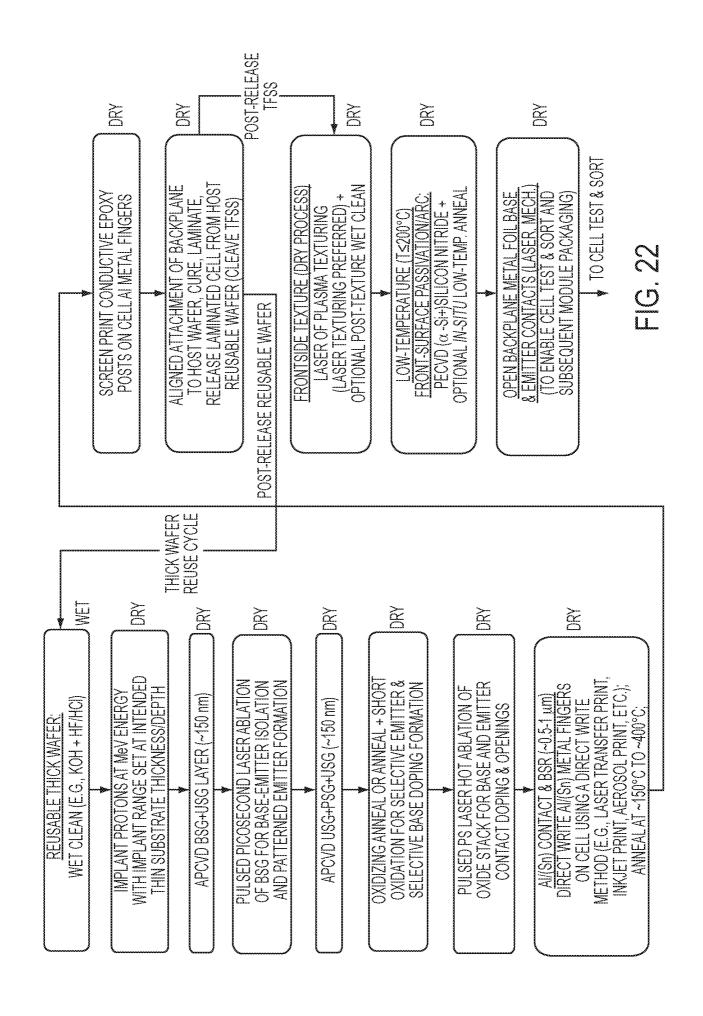

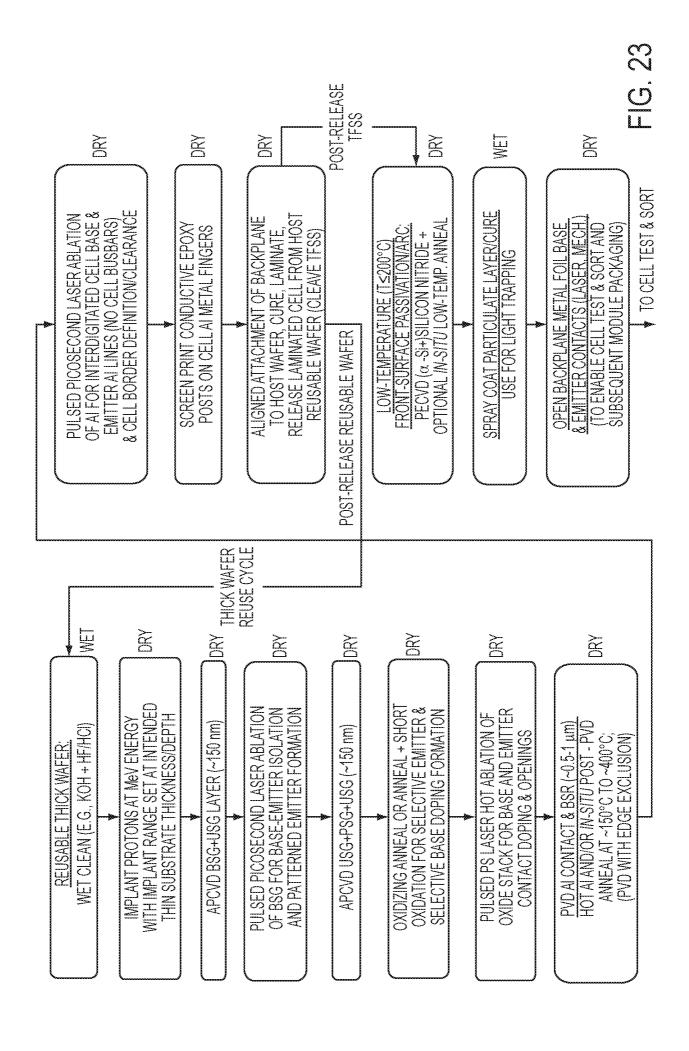

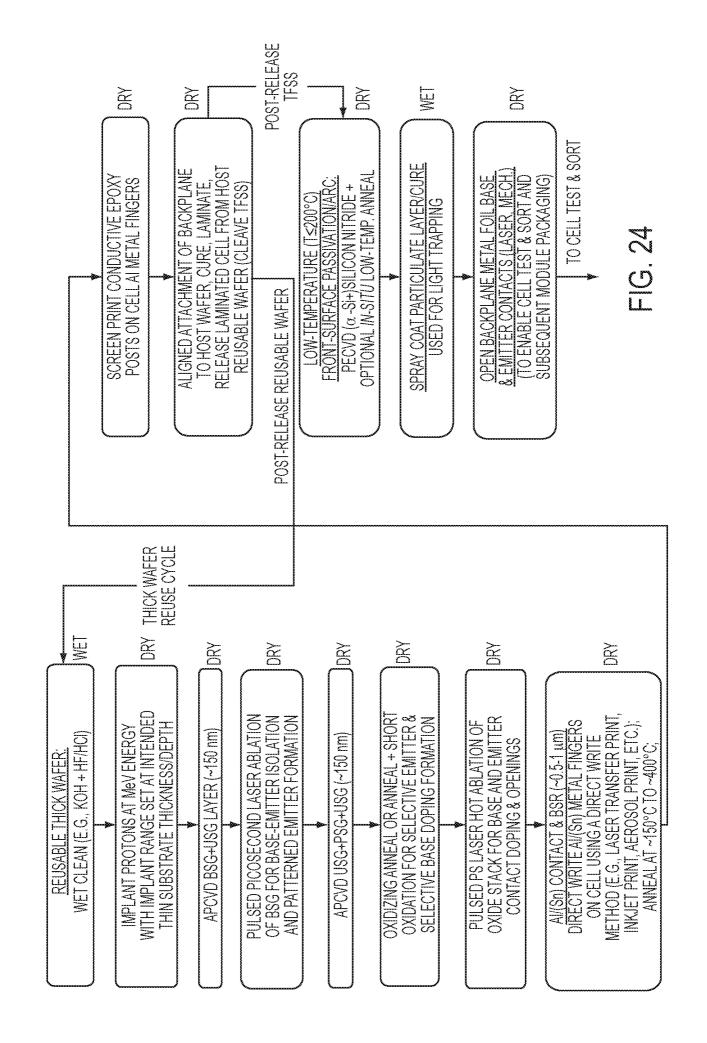

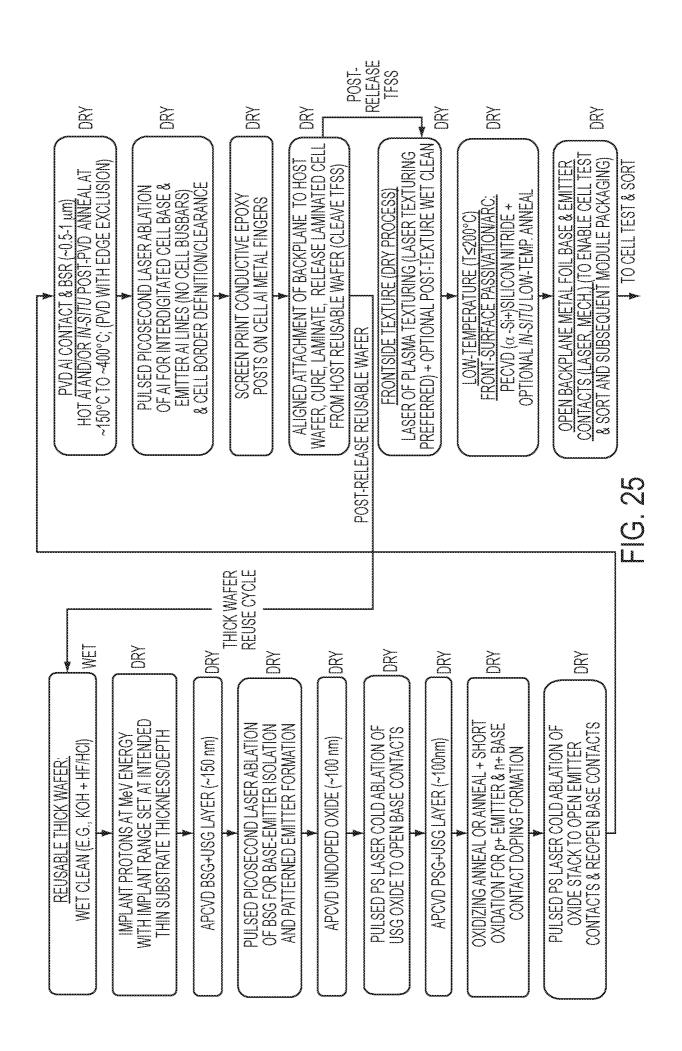

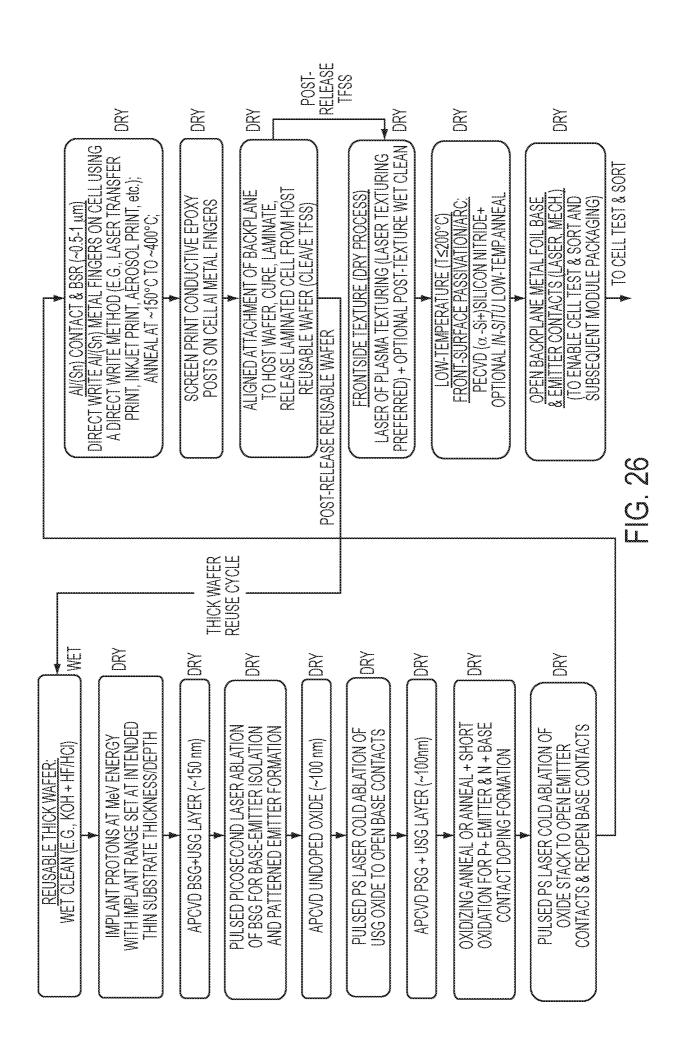

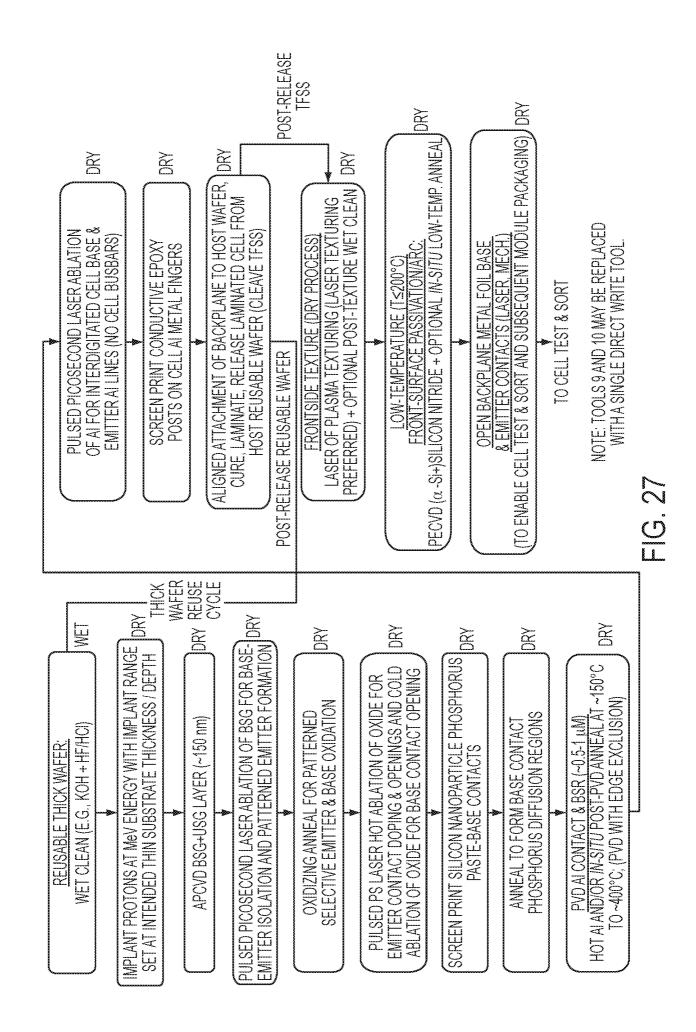

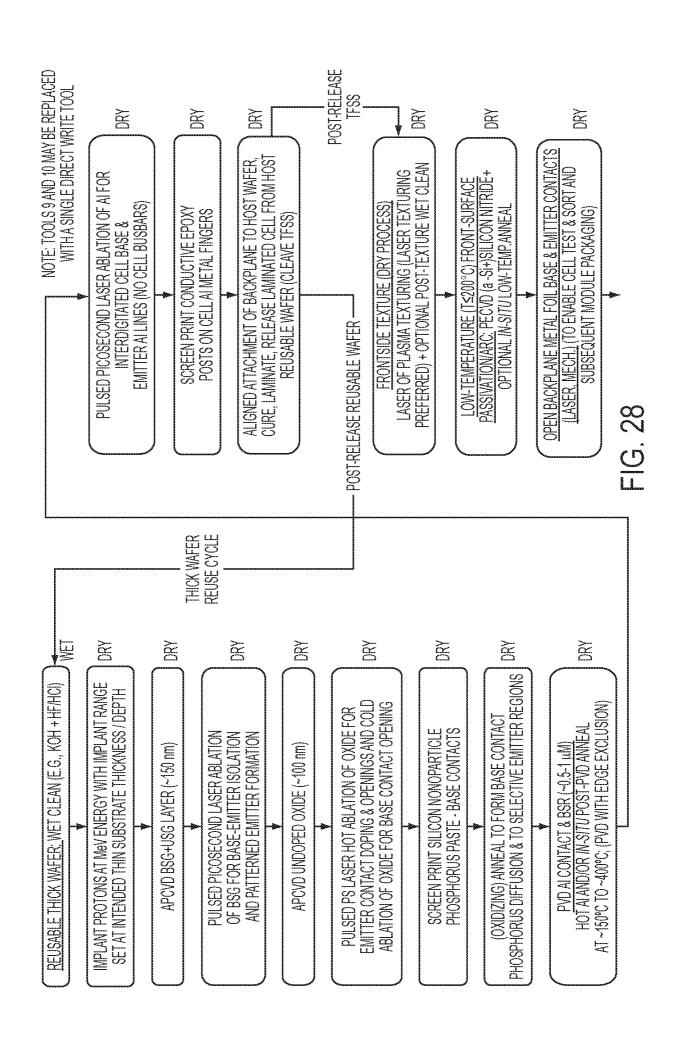

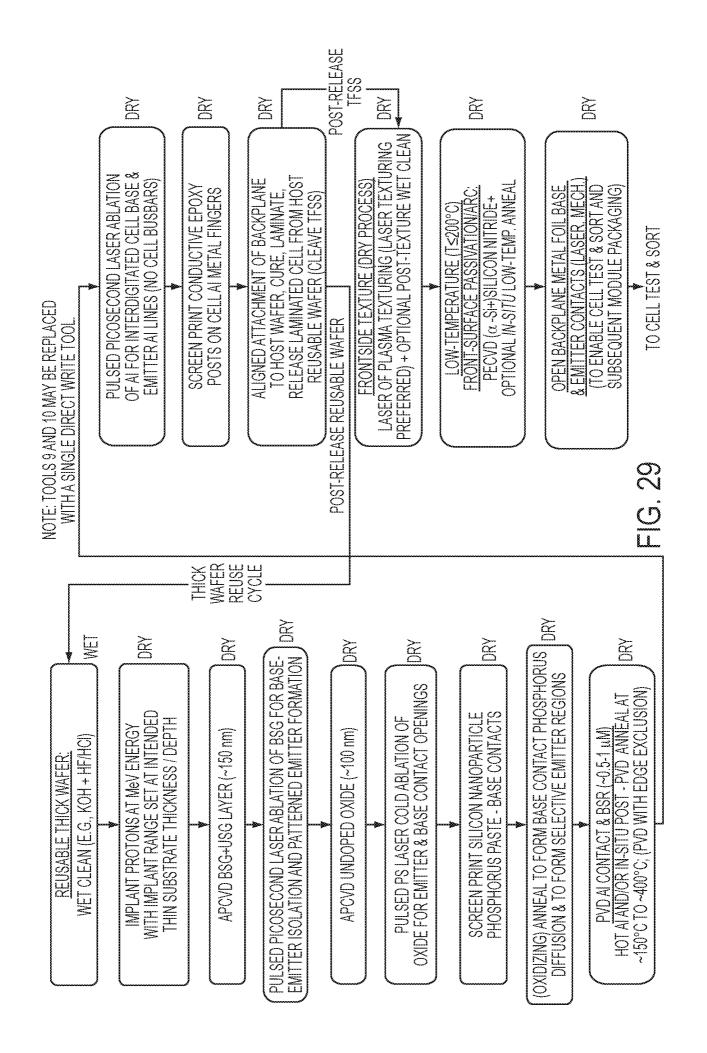

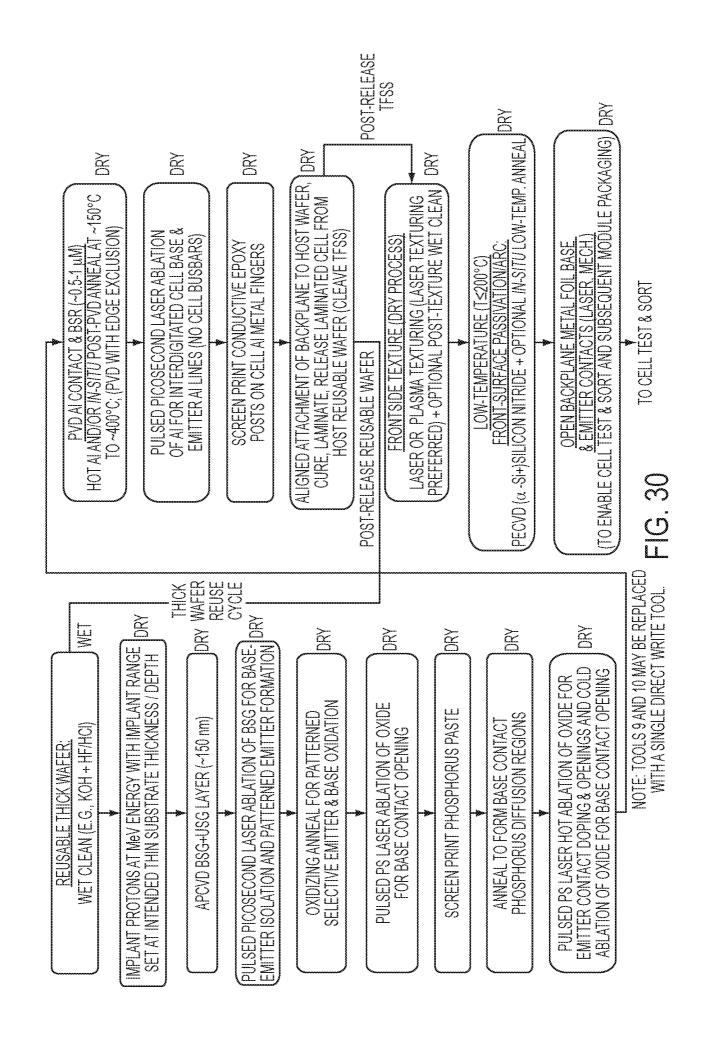

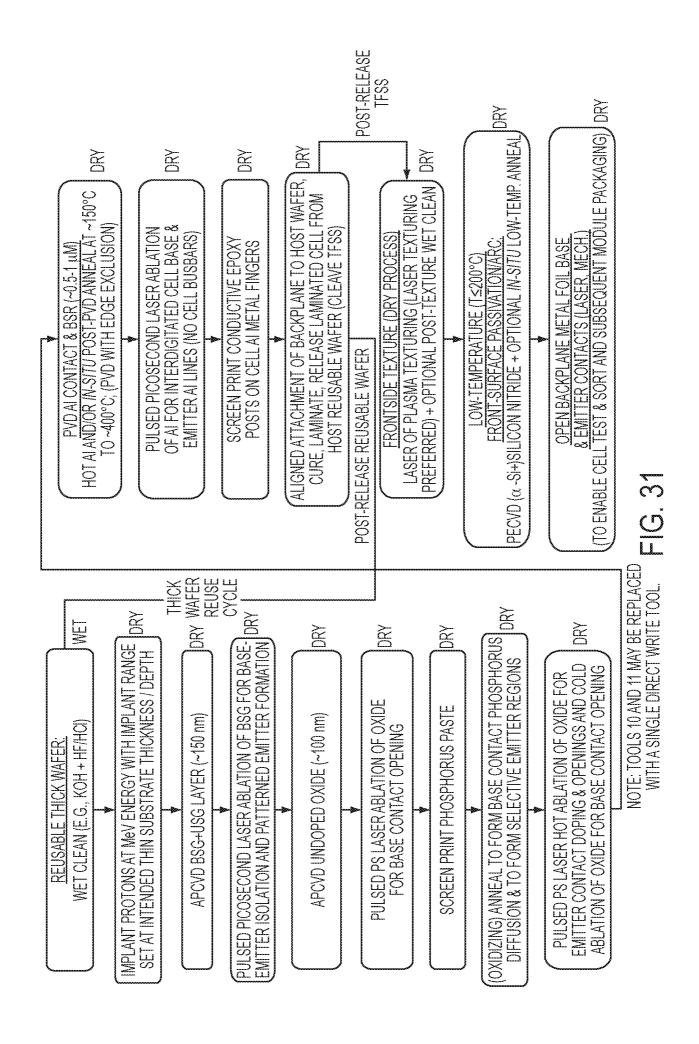

- Figs. 22 through 35 are back contact solar cell manufacturing process flows using a cleaved substrate;

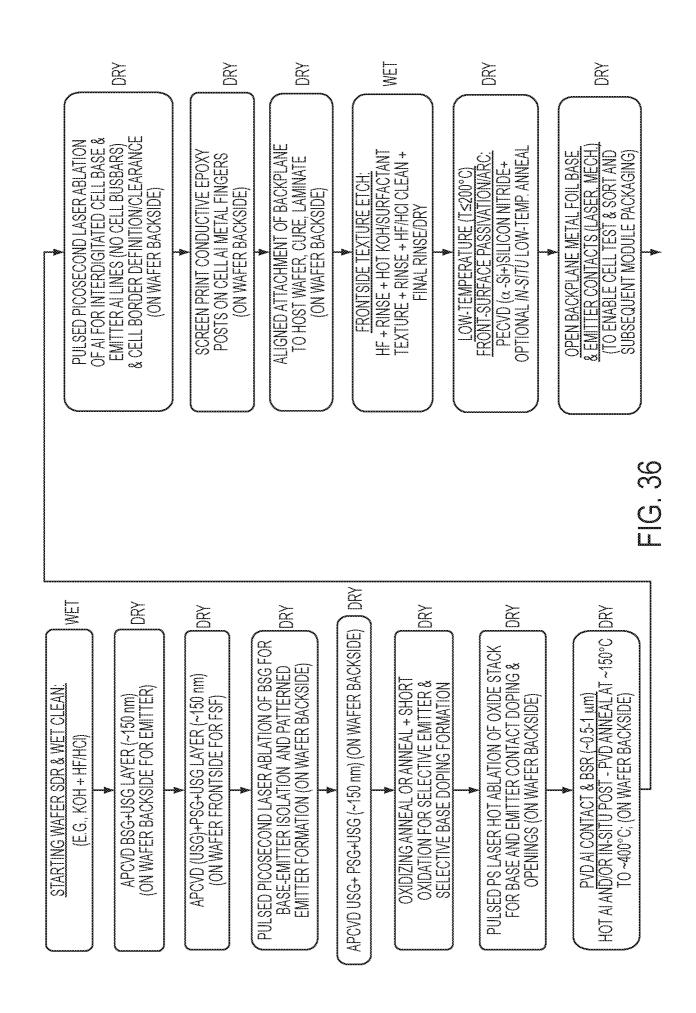

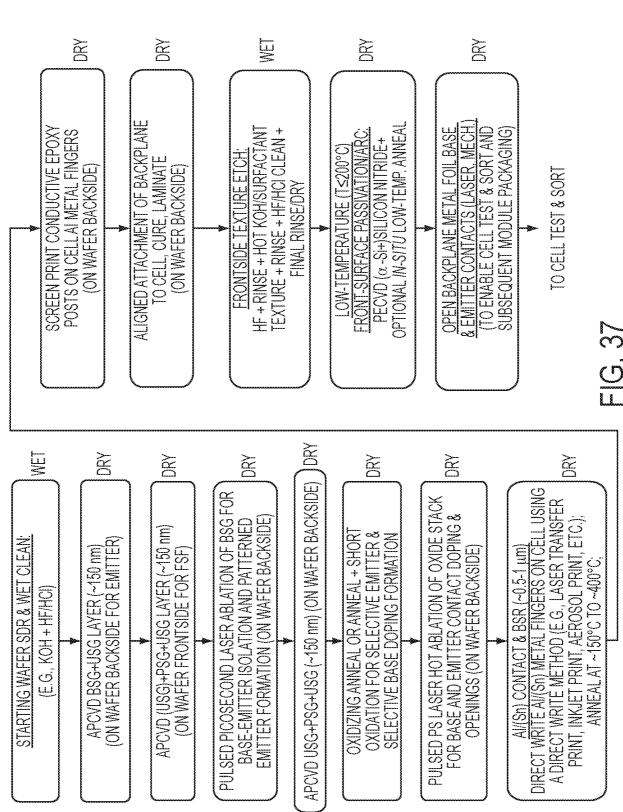

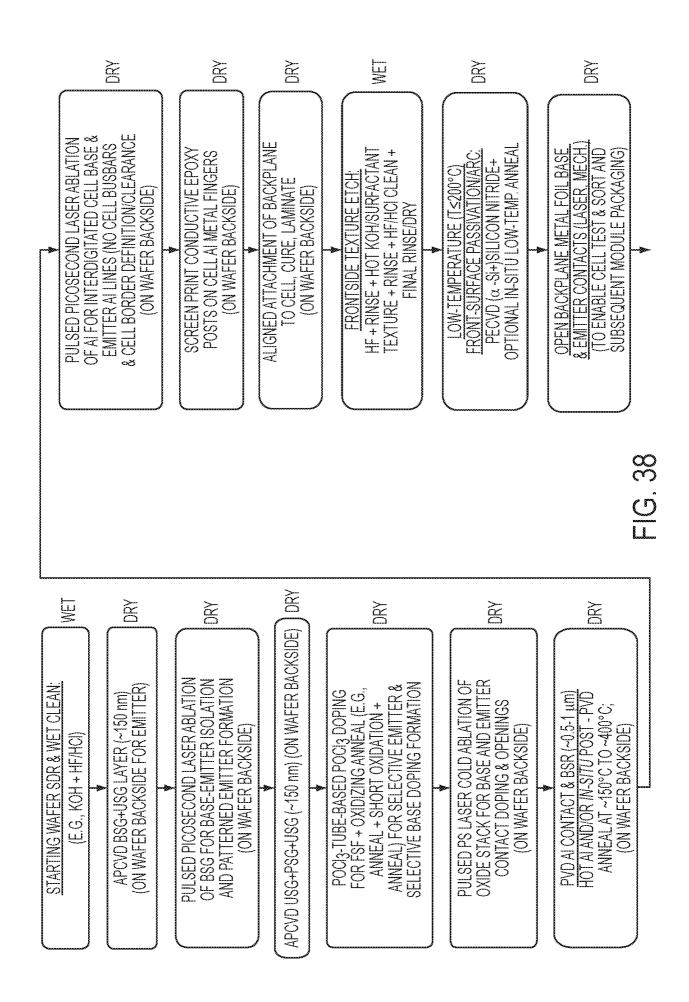

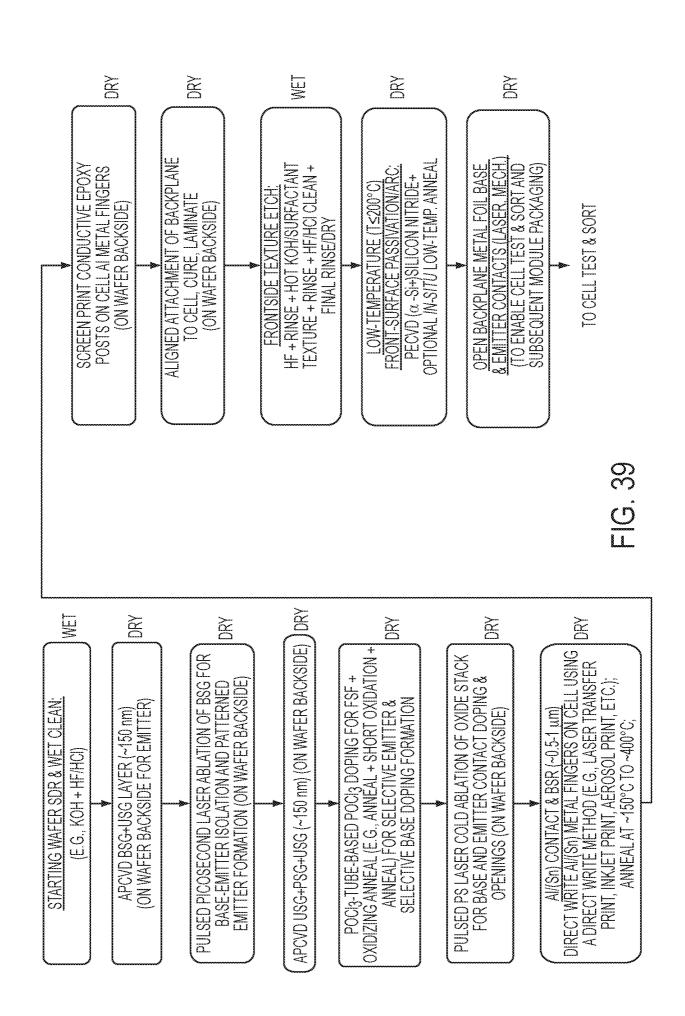

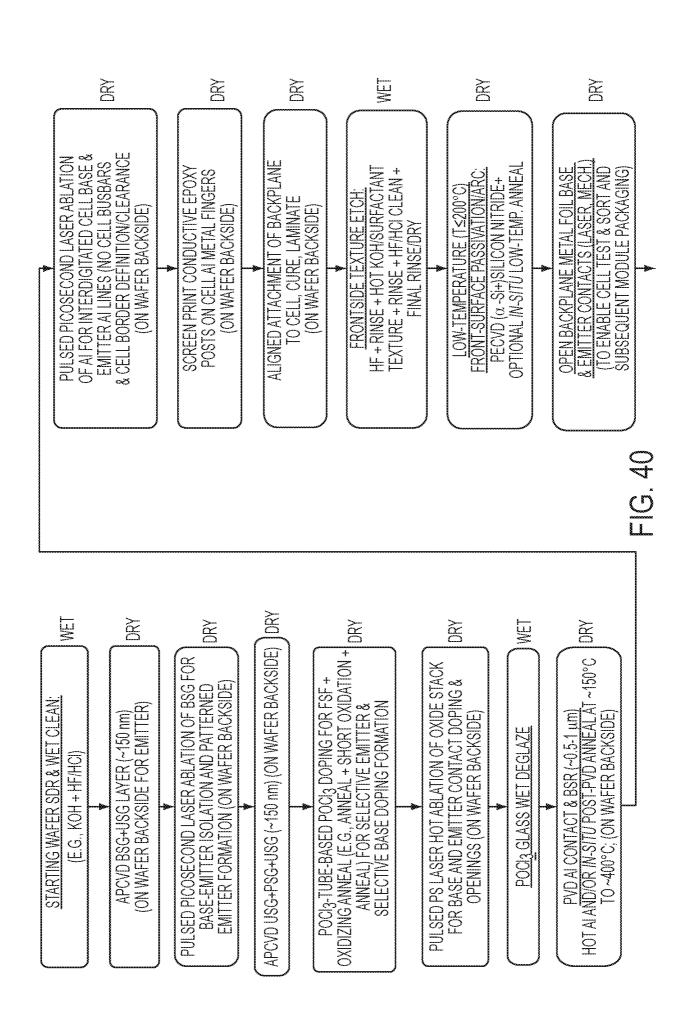

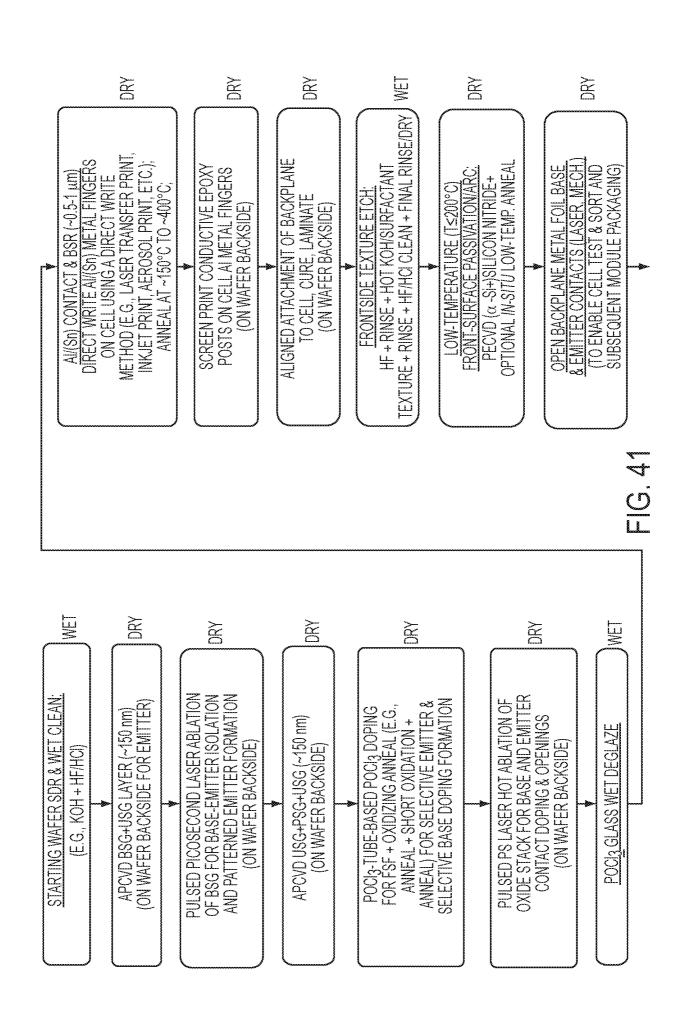

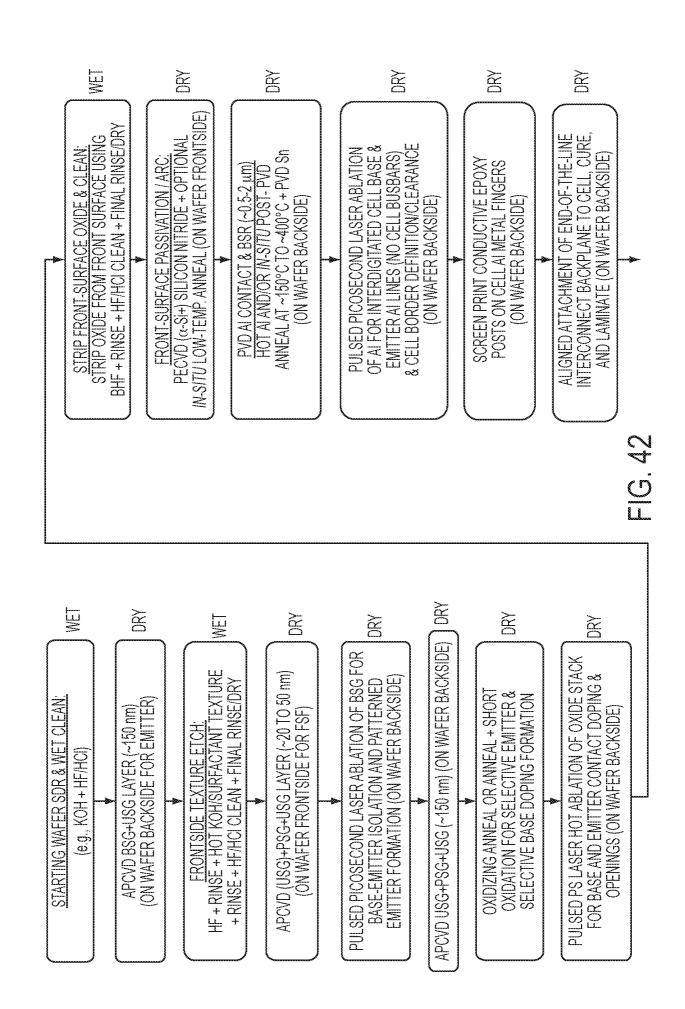

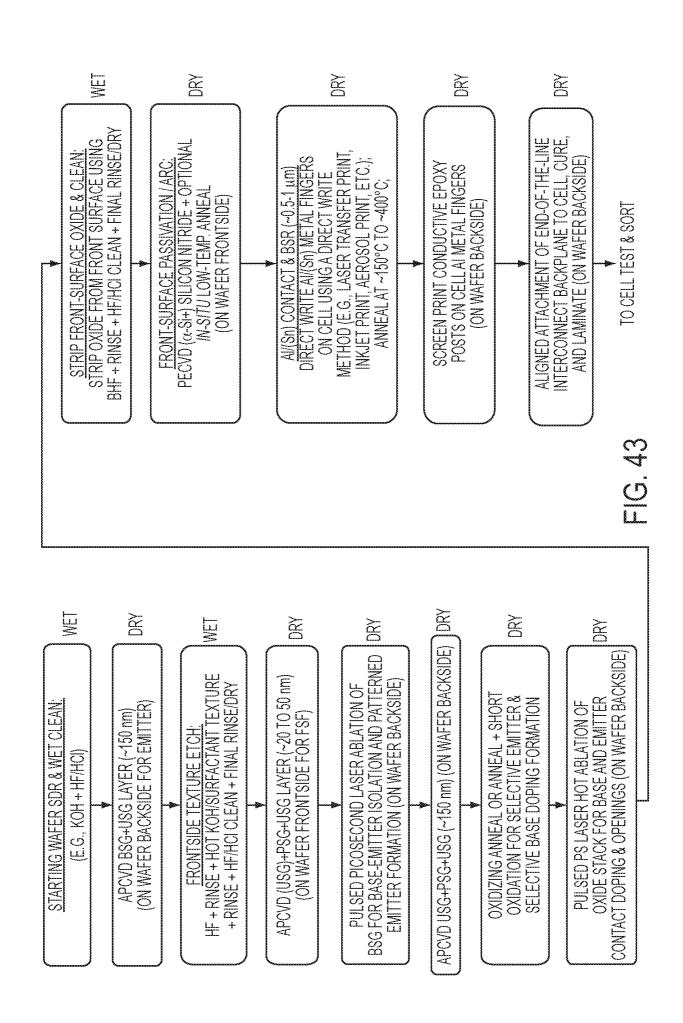

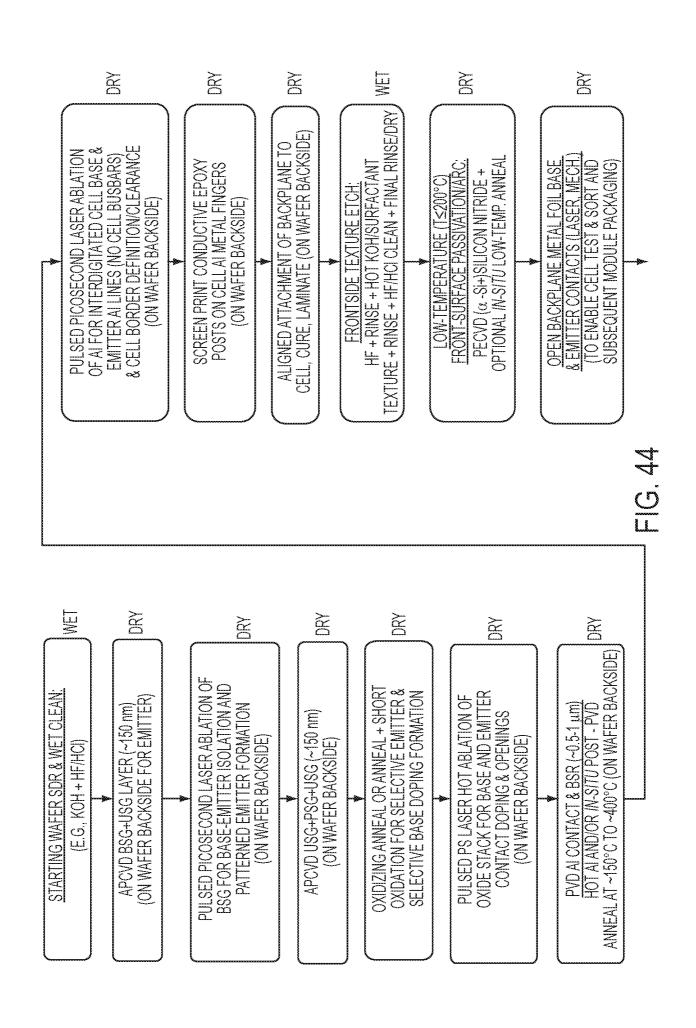

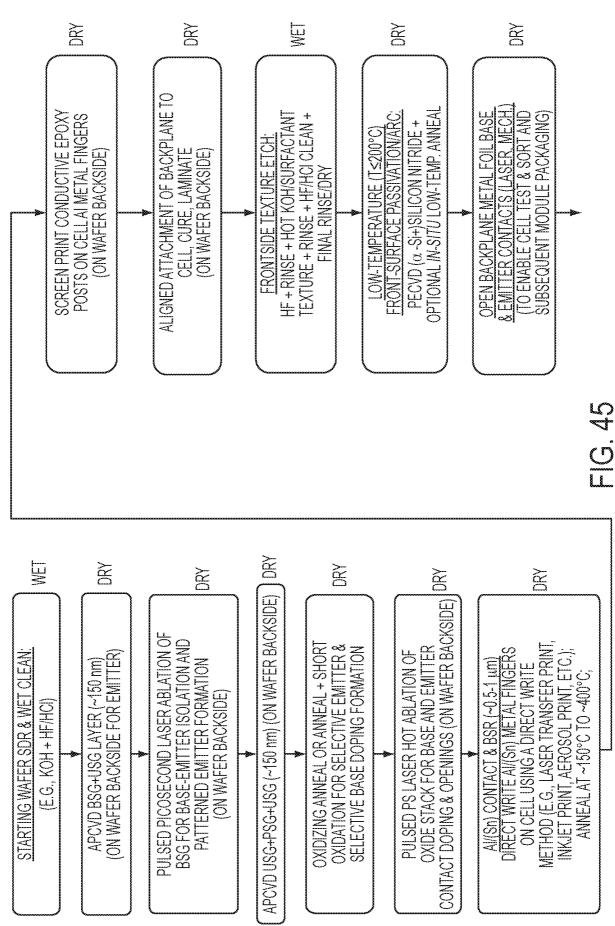

- Figs. 36 through 45 are back contact solar cell manufacturing process flows using a bulk wafer;

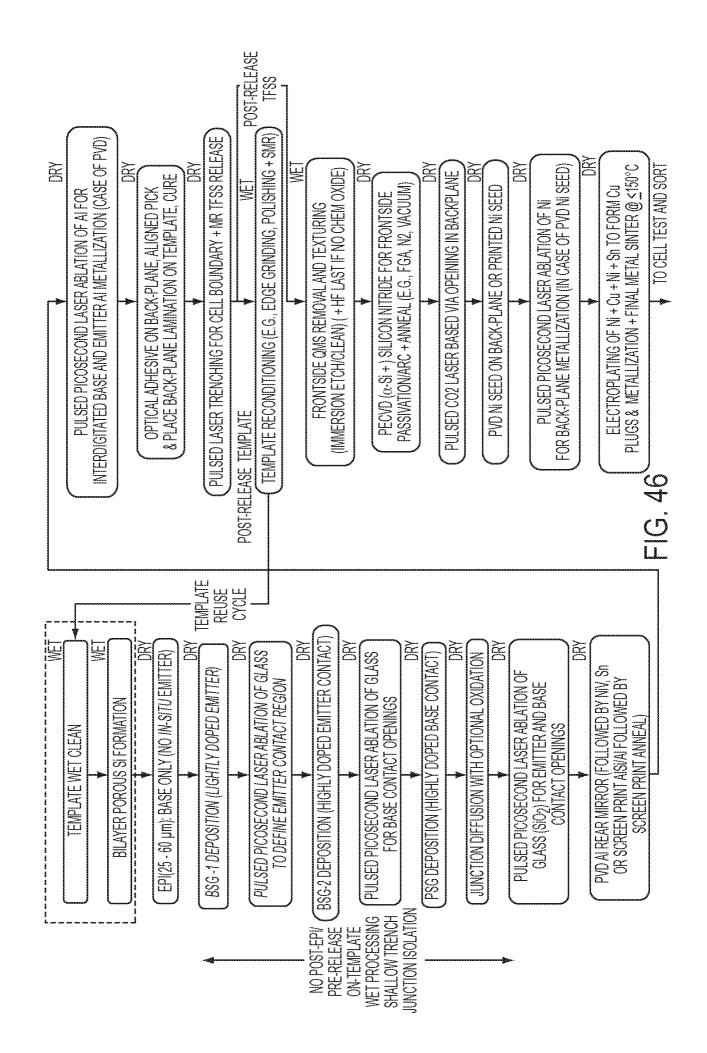

- Fig. 46 is a back contact solar cell manufacturing process flow for a selective emitter;

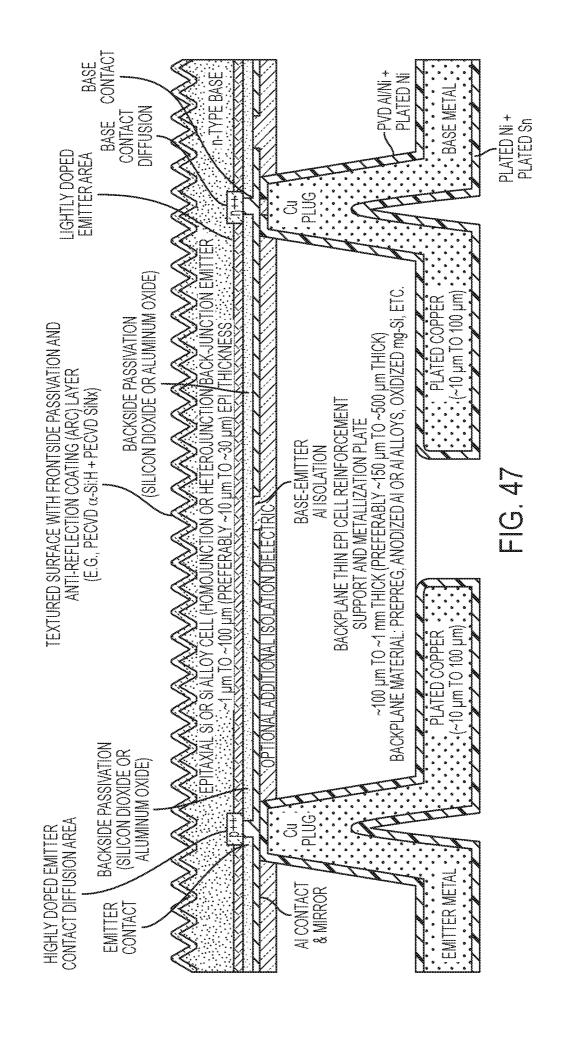

- Fig. 47 is a cross-sectional diagram of a cell resulting from the flow of Fig. 46;

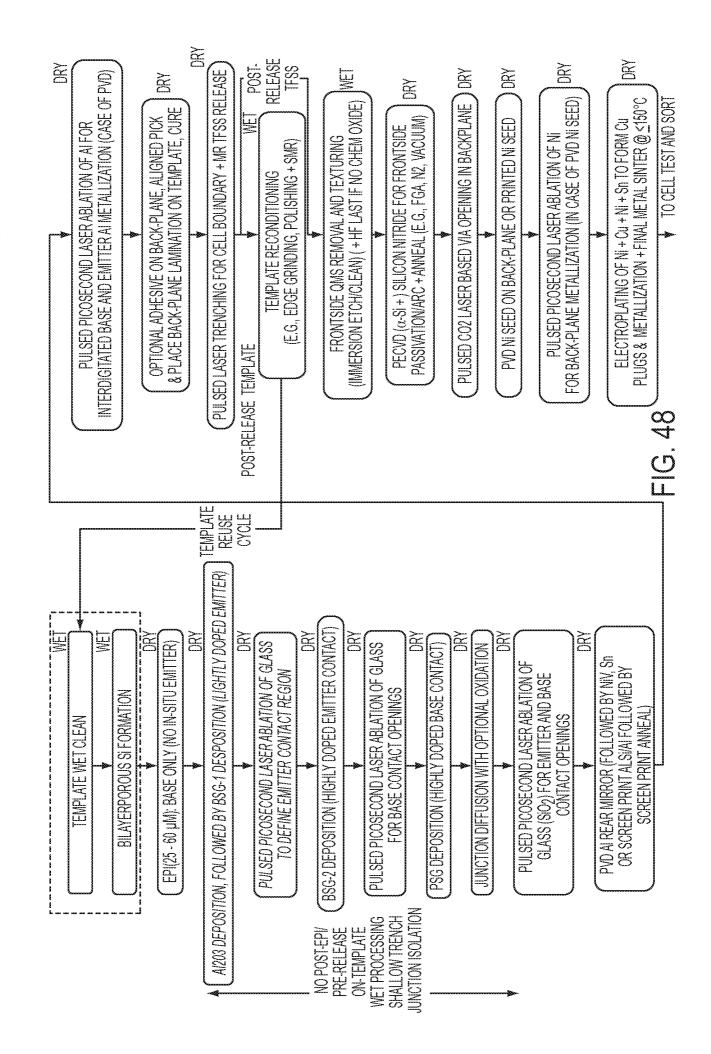

- Fig. 48 is a back contact solar cell manufacturing process flow;

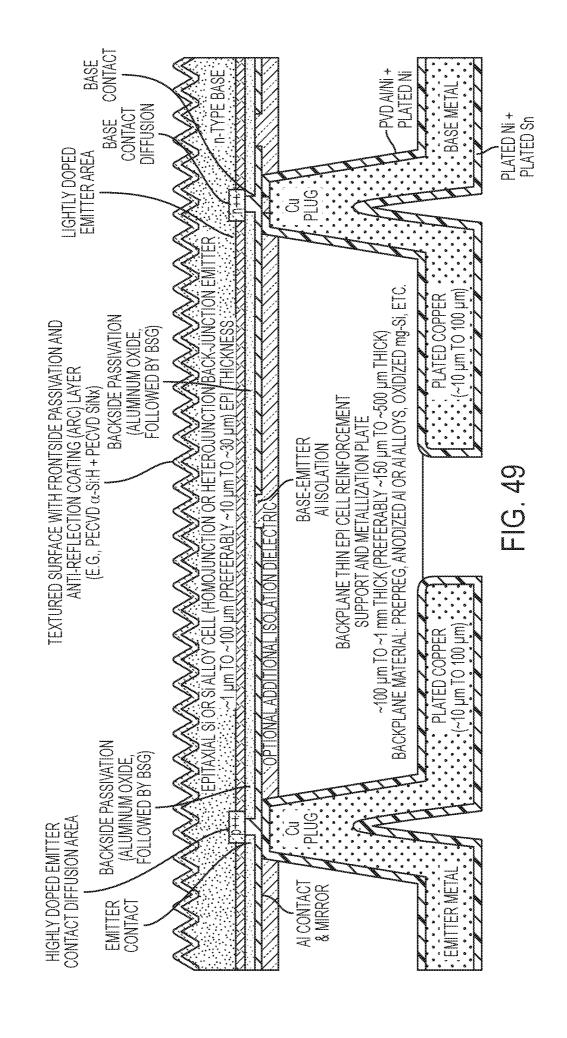

- Fig. 49 is a cross-sectional diagram of a cell resulting from the flow of Fig. 48;

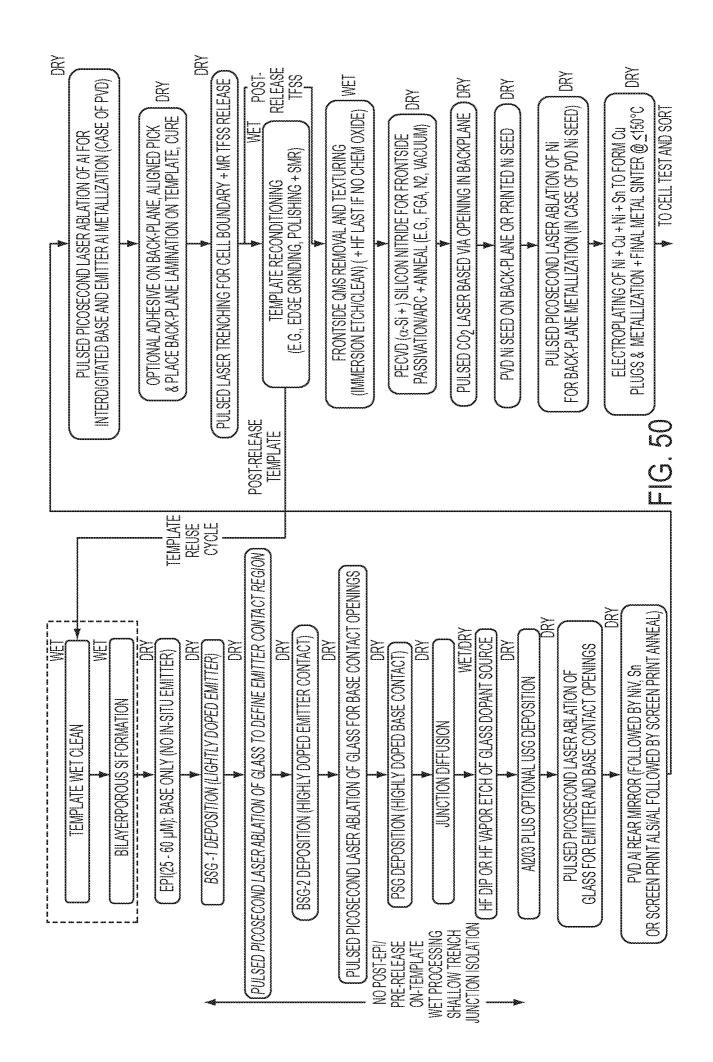

- Fig. 50 is a back contact solar cell manufacturing process flow;

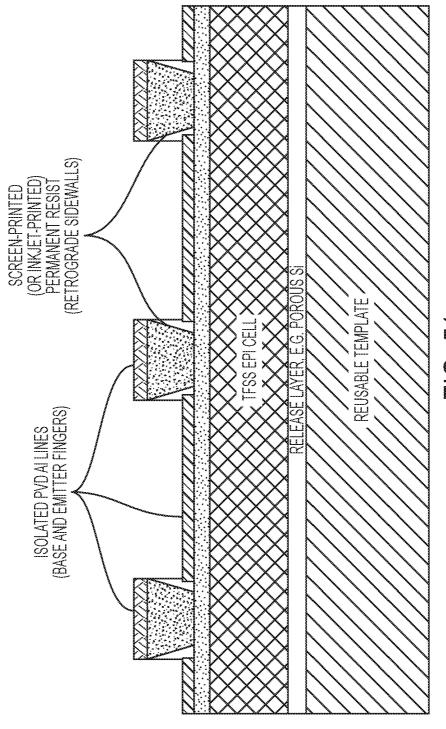

- Fig. 51 is a cross-sectional diagram of a structure with retrograde resist sidewalls;

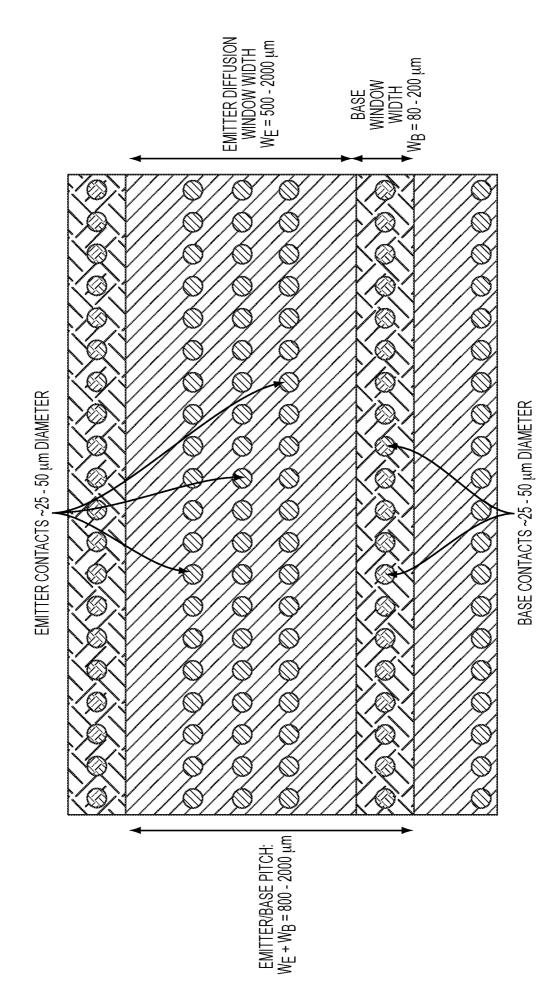

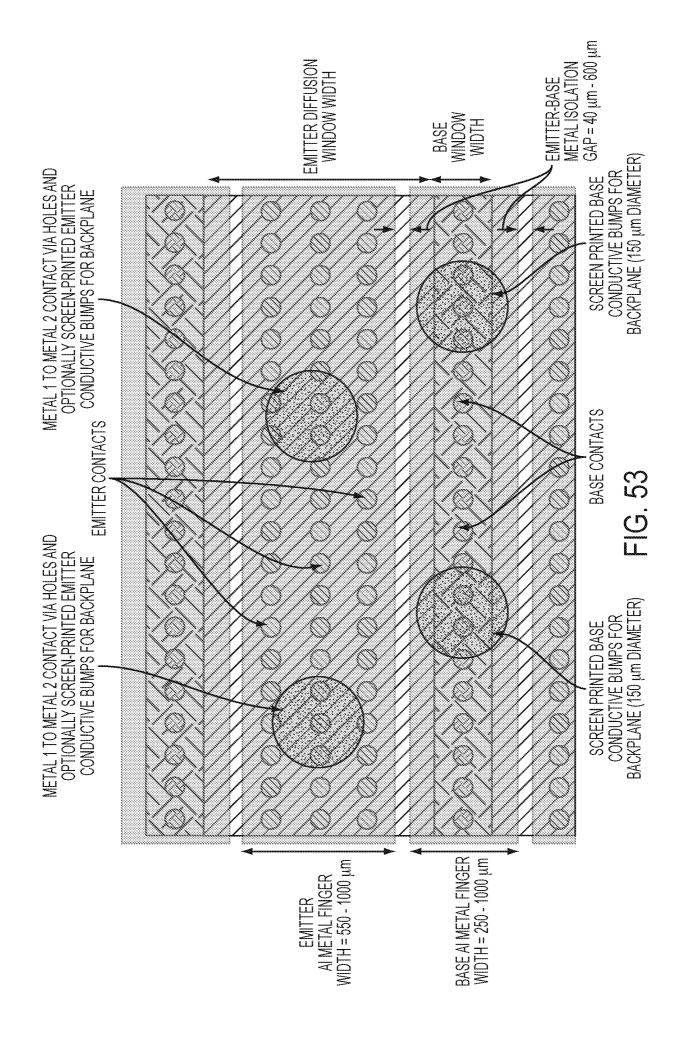

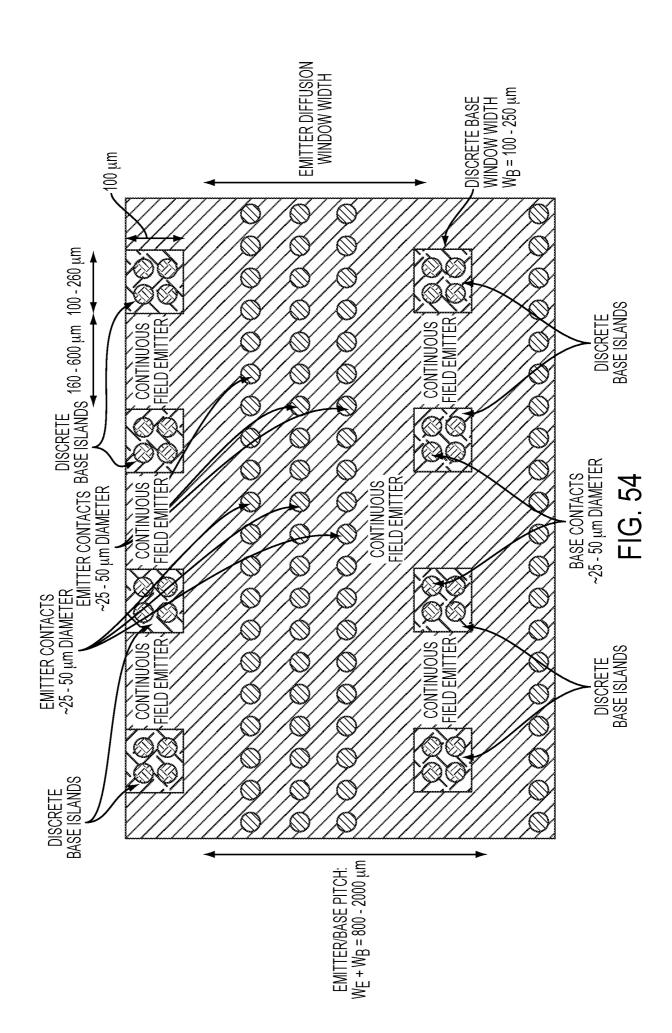

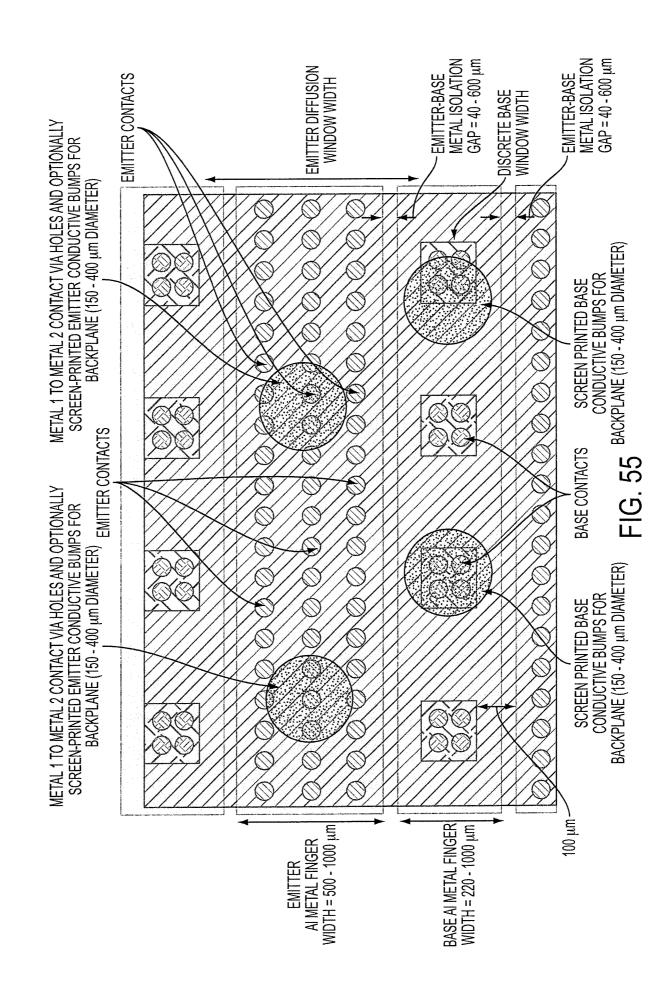

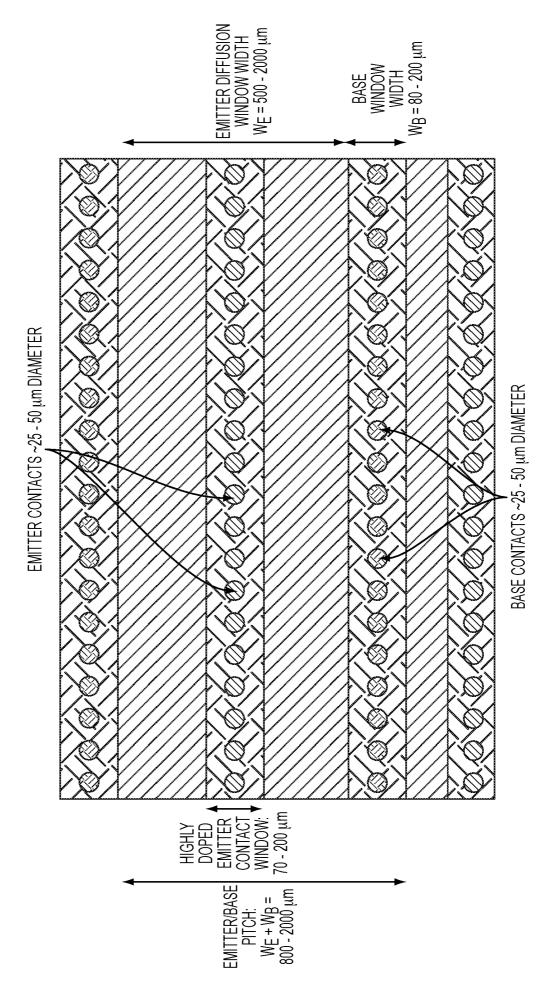

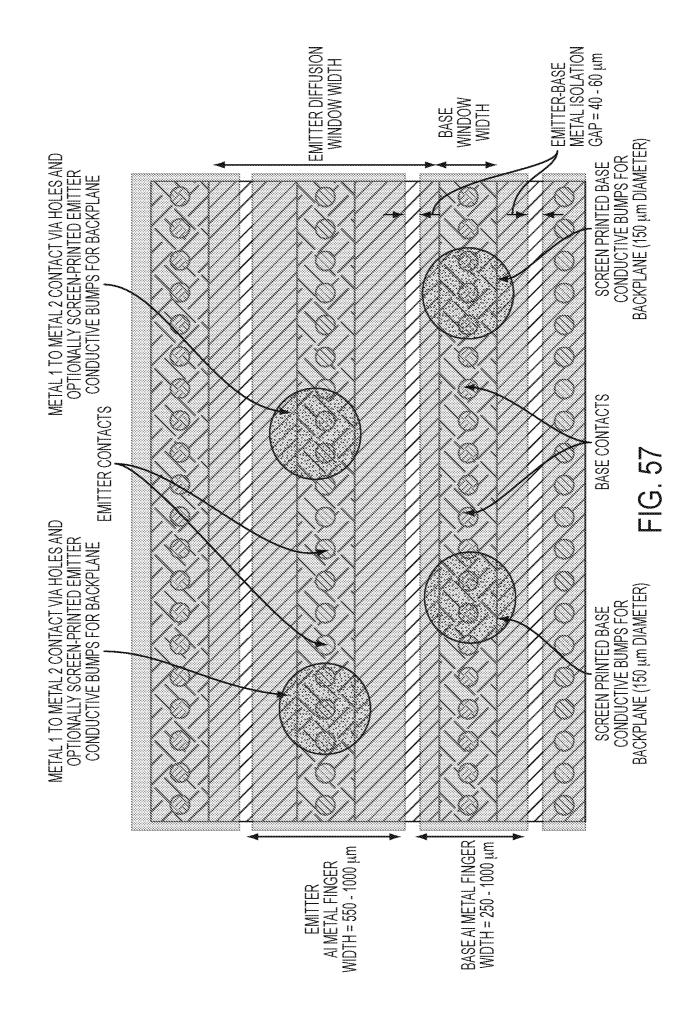

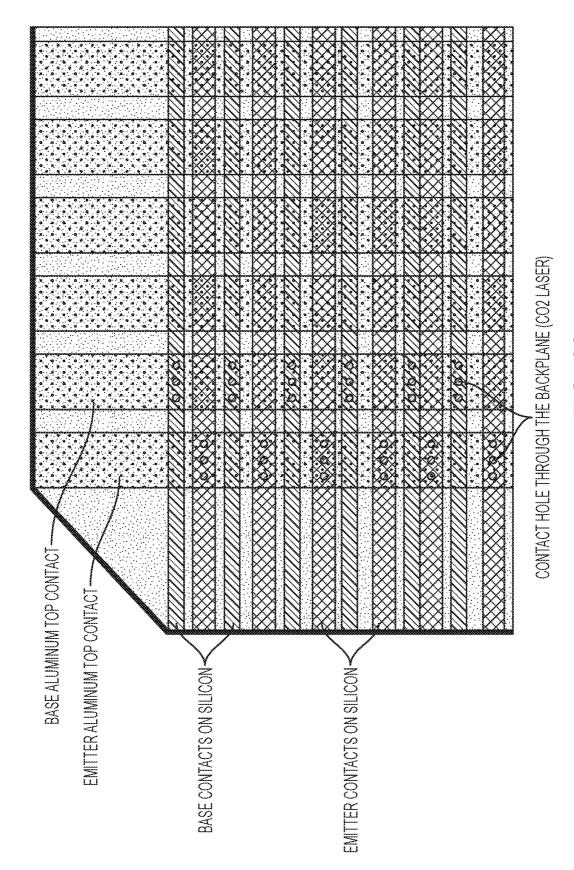

- **Figs. 52** through **57** are top views of solar cell backplane embodiments after various processing steps;

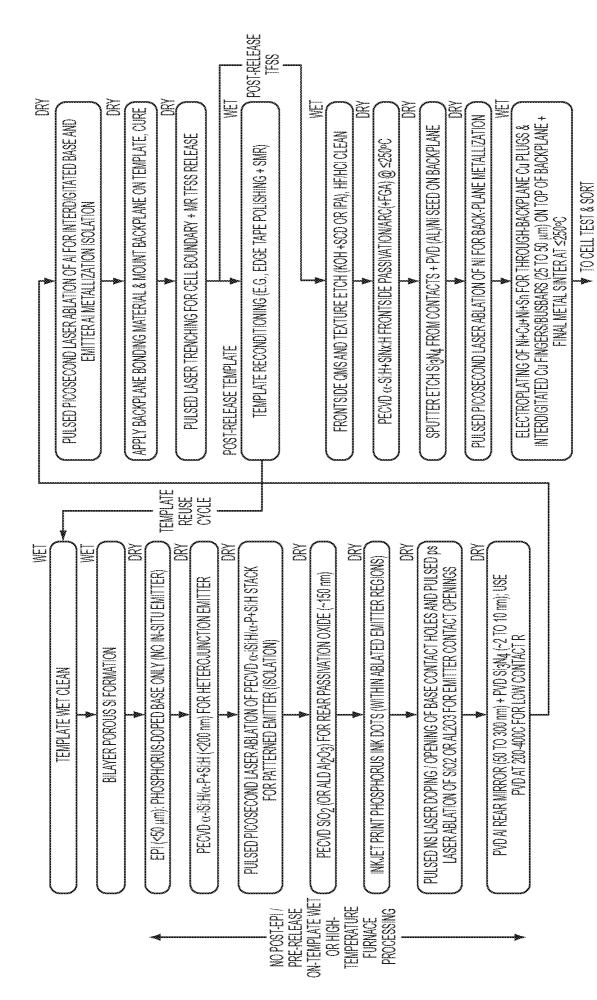

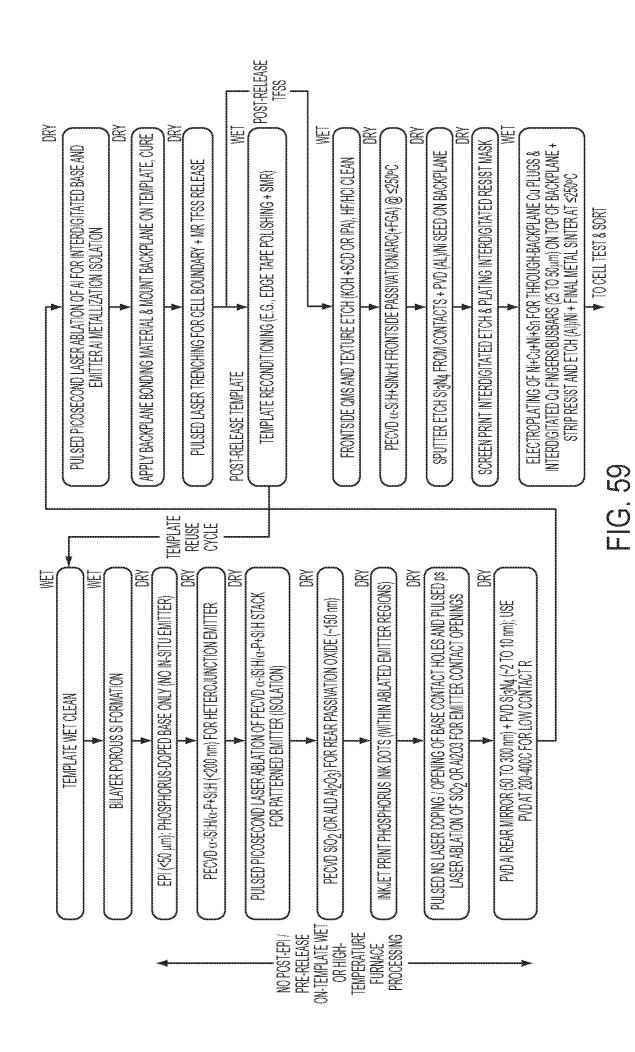

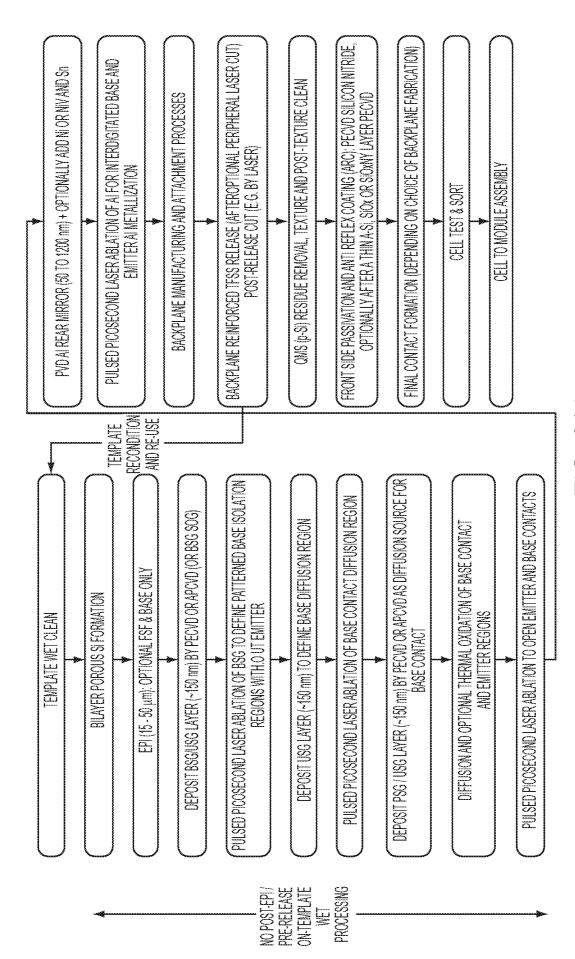

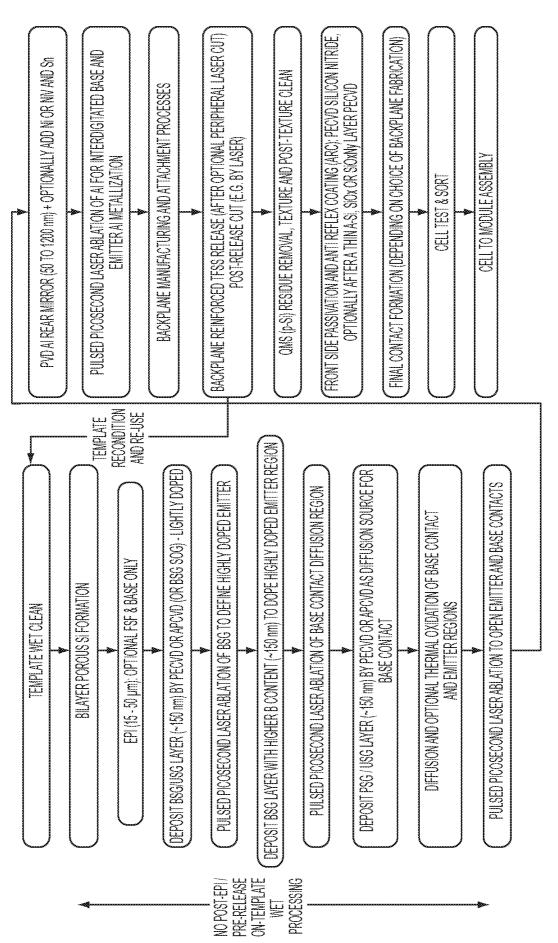

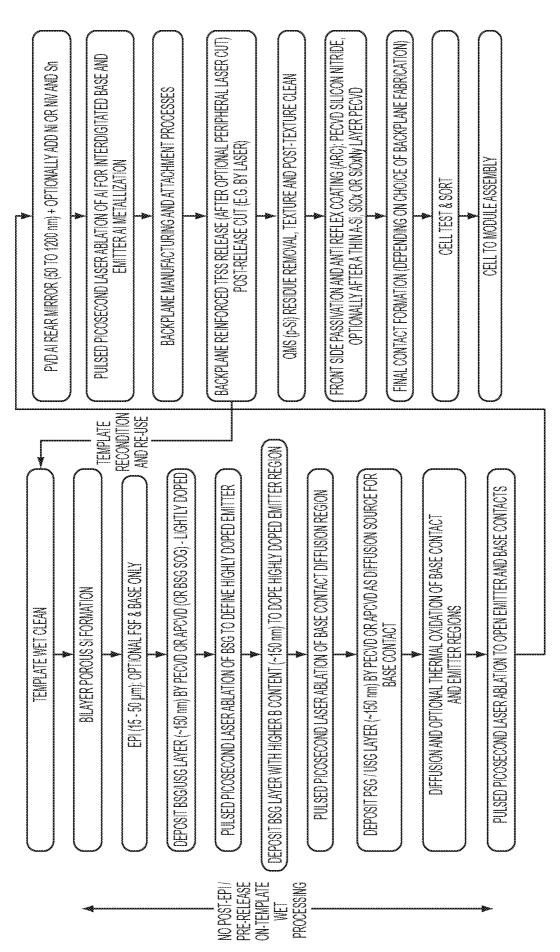

- Figs. 58 and 59 are back contact solar cell manufacturing process flows for heterojunction cells;

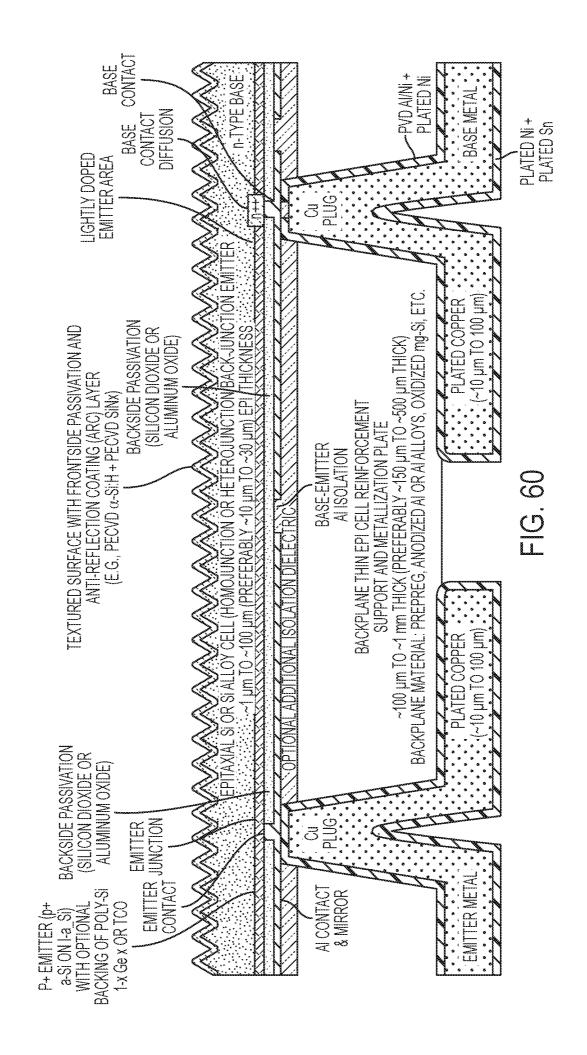

- Fig. 60 is a cross-sectional diagram of a solar cell with a heterojunction architecture;

- Figs. 61A through C are back contact solar cell manufacturing process flows using an epitaxial substrate:

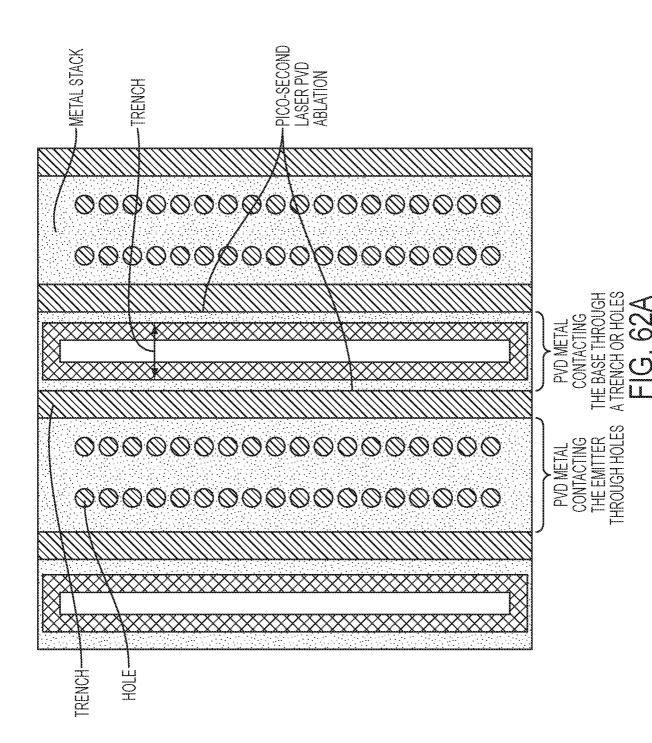

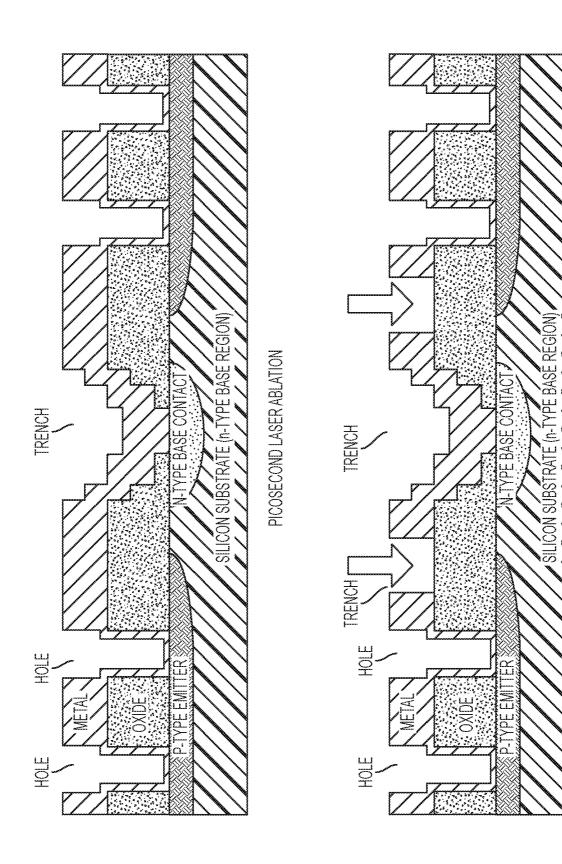

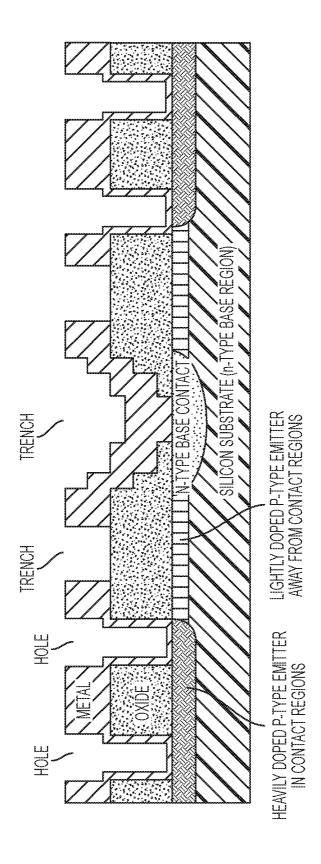

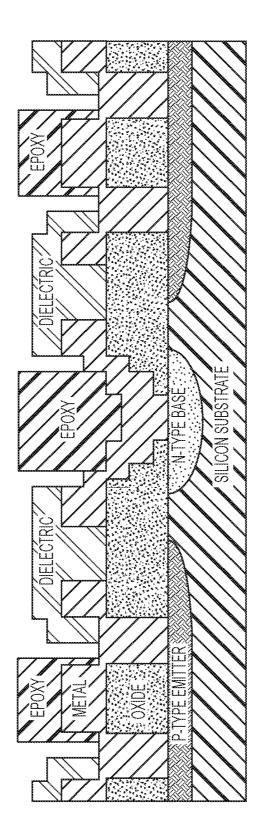

- **Figs. 62A** through **G** are top view and cross-sectional views of a back contact solar cells after backplane processing steps;

**Figs. 63A** through **D** are cross sectional diagrams of a pluto structure after certain processing steps;

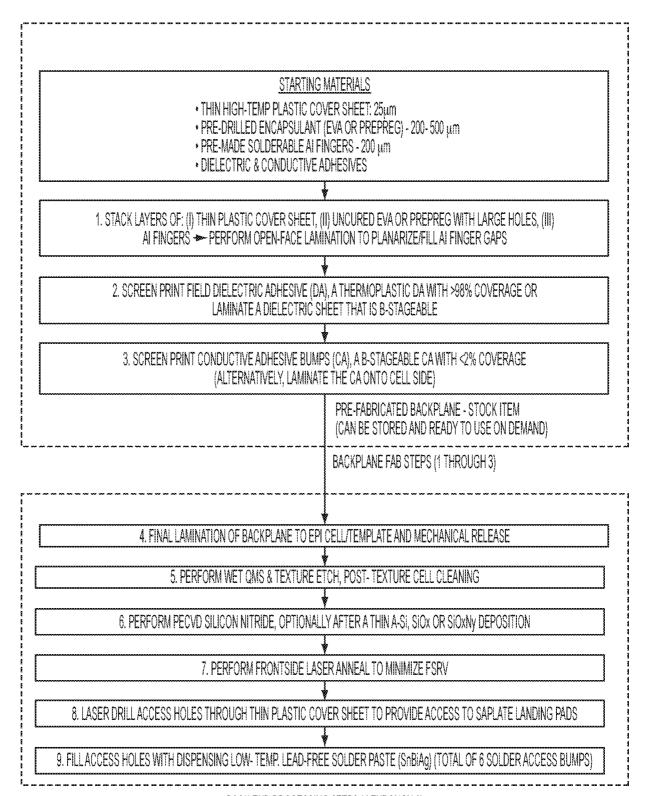

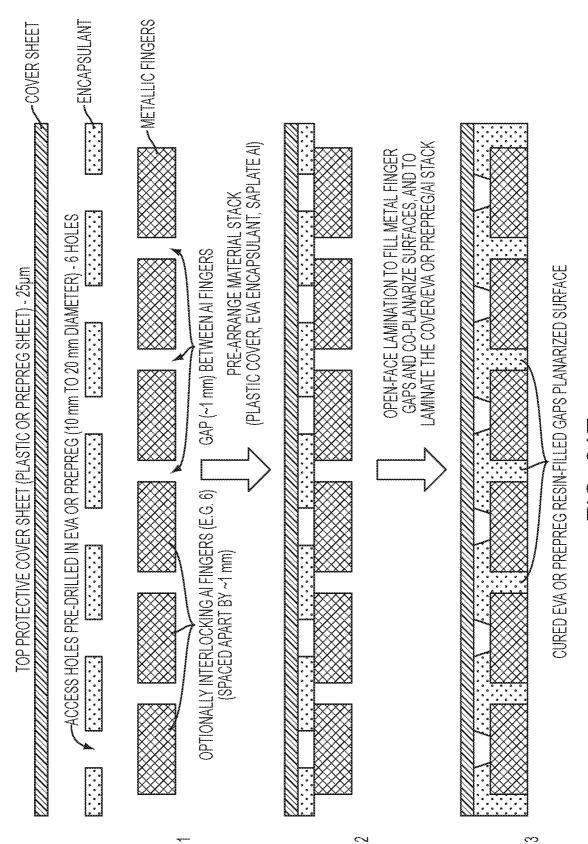

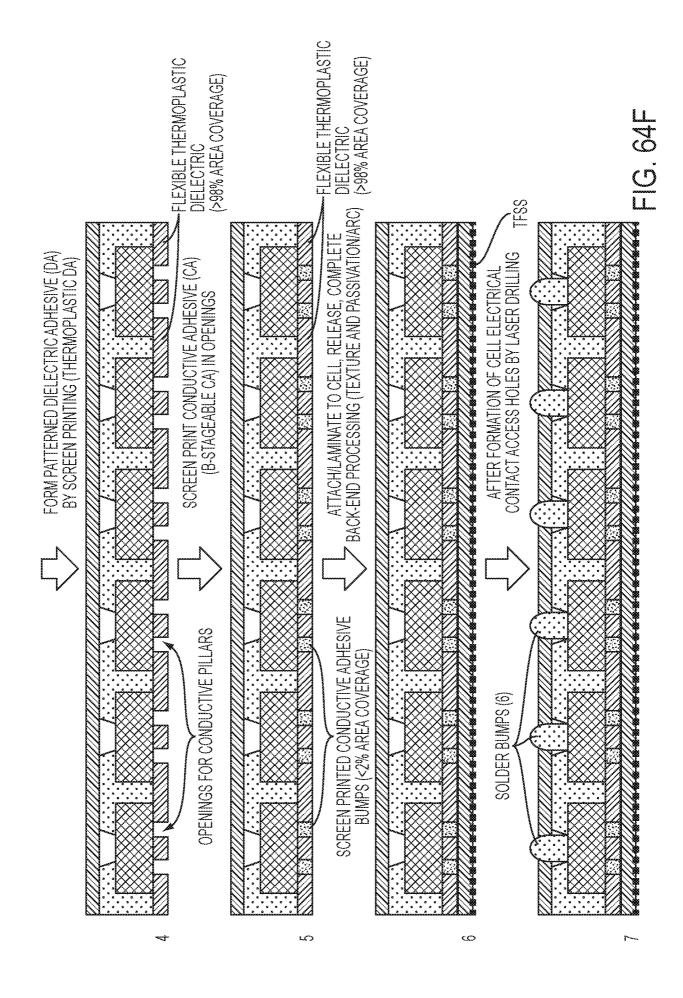

**Figs. 64A** through **F** show various aspects, cross-sectional and top views and process flows, of a four-layer backplane oasis structure;

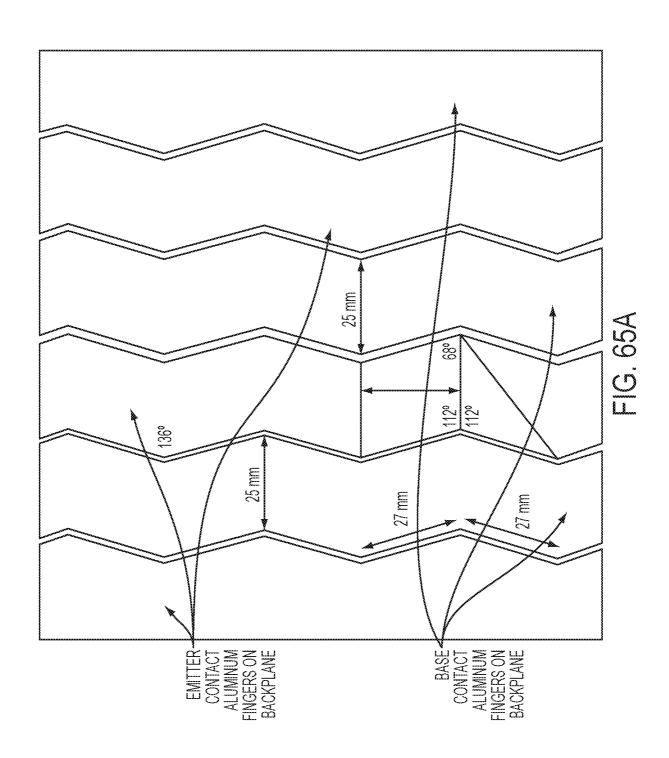

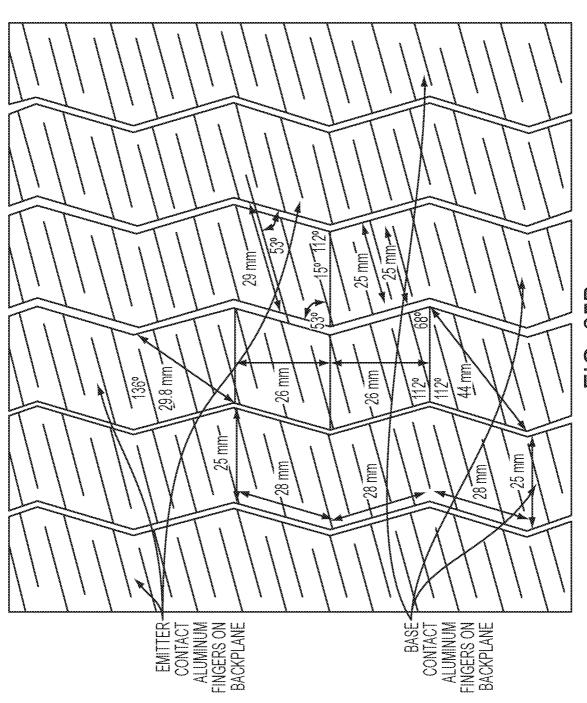

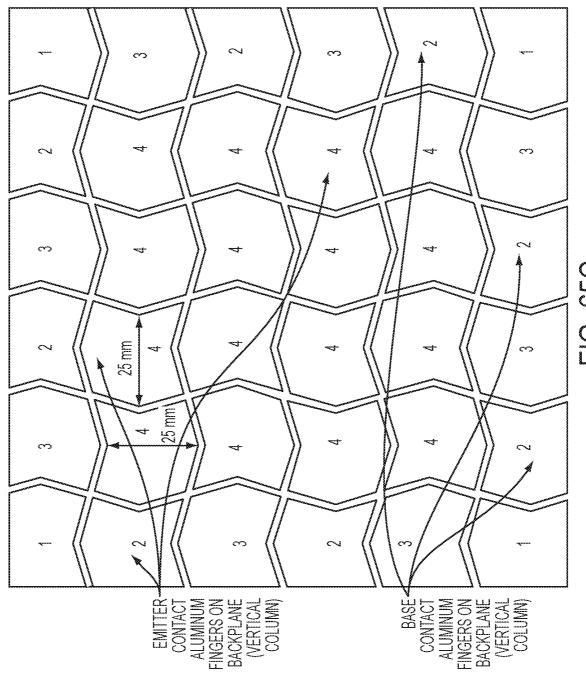

Figs. 65A through D are top views of various cell backplane metal finger designs;

Fig. 66 is a top view of backplane embodiment;

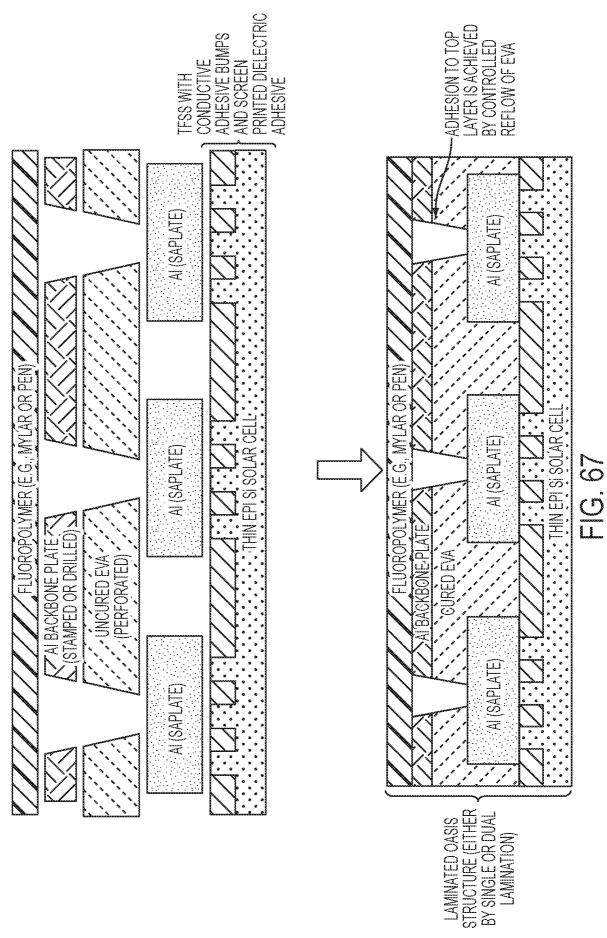

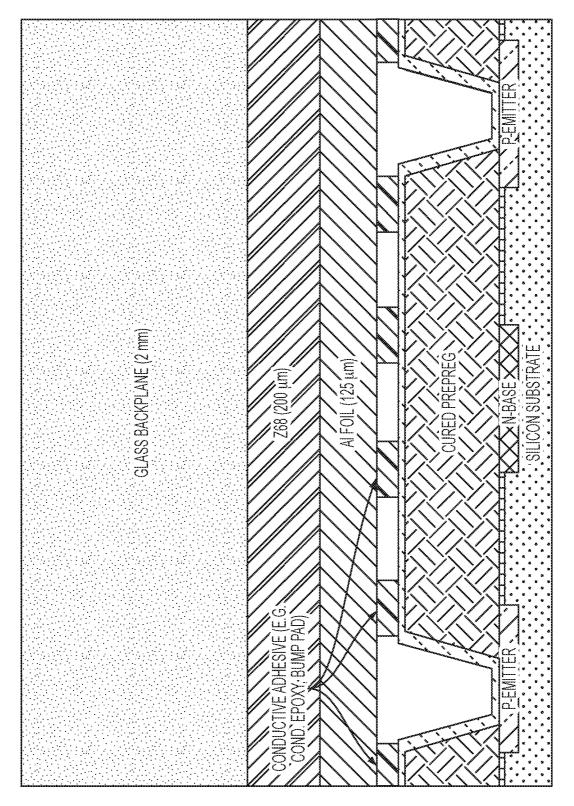

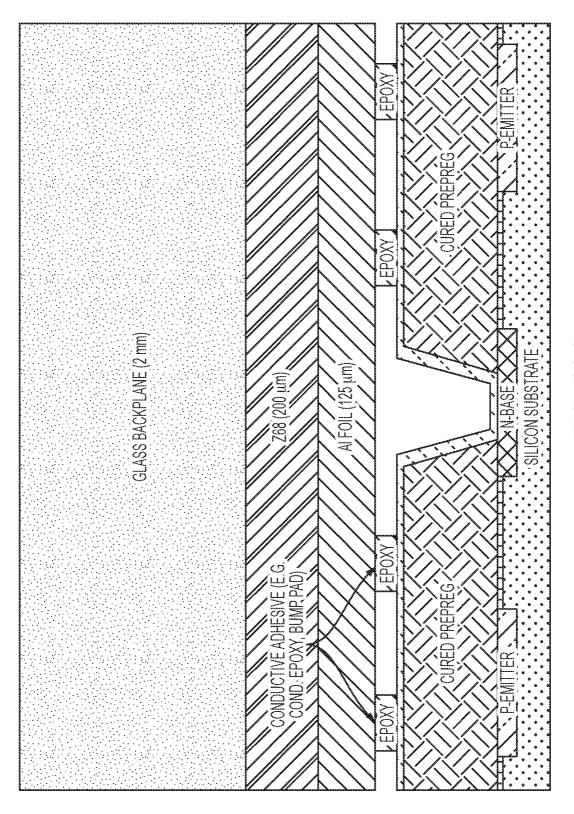

Fig. 67 show cross-sectional diagrams of an oasis structure;

Figs. 68A through C are cross-sectional diagrams of a hybrid structure;

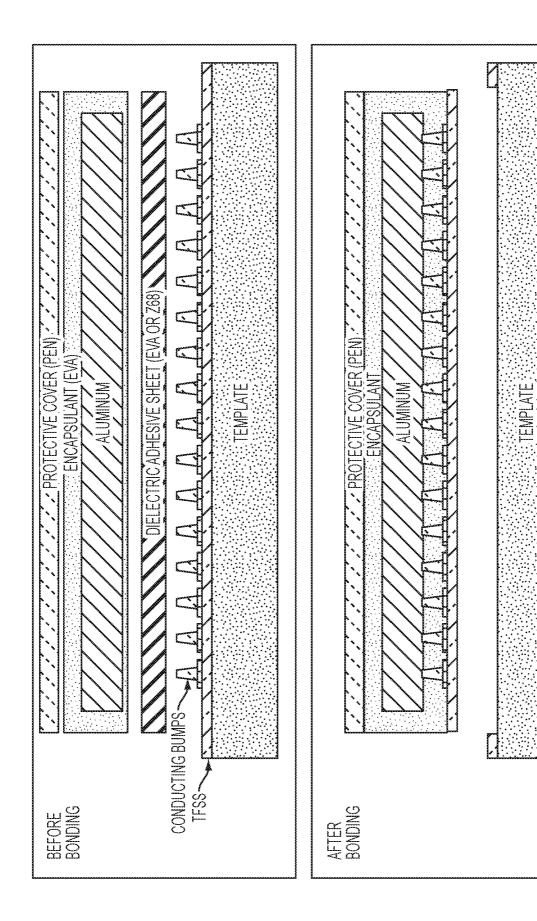

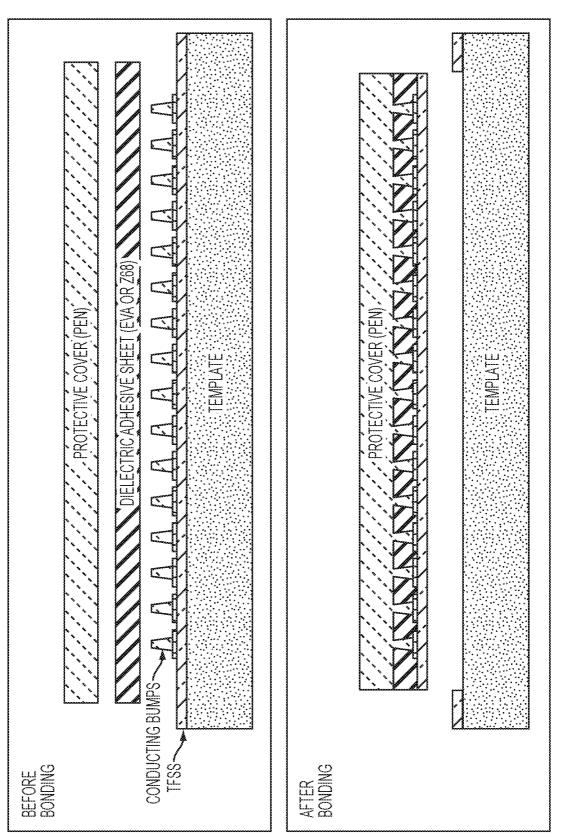

**Figs. 69** and **70** show cross-sectional diagrams of a immersion contact bonding structure embodiments;

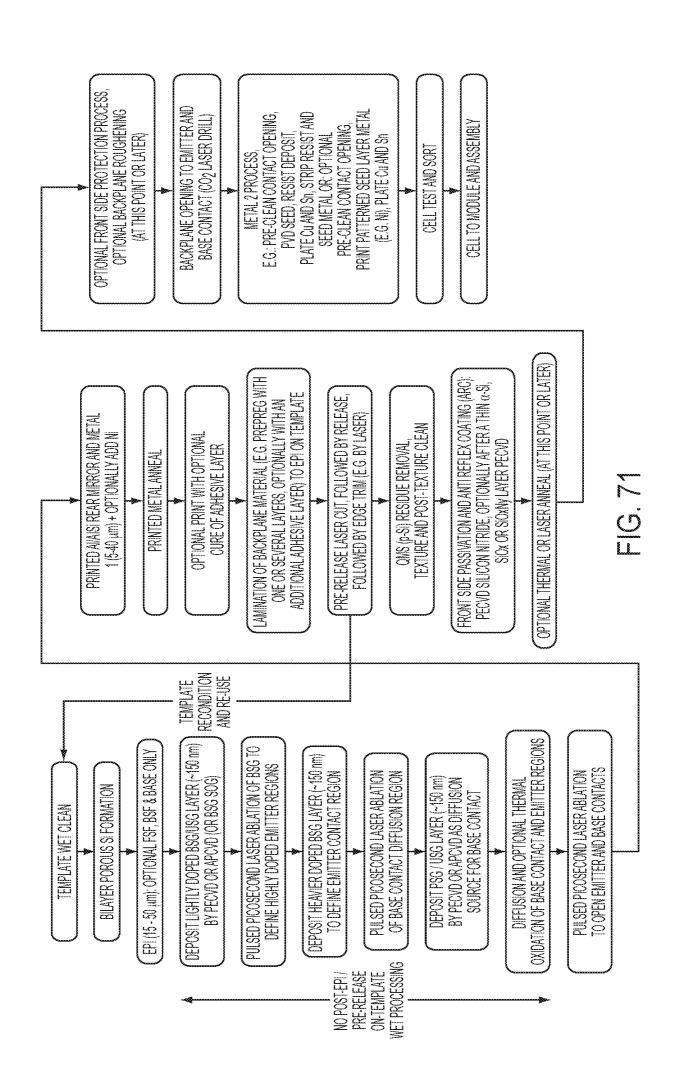

Fig. 71 is a back contact solar cell manufacturing process flow;

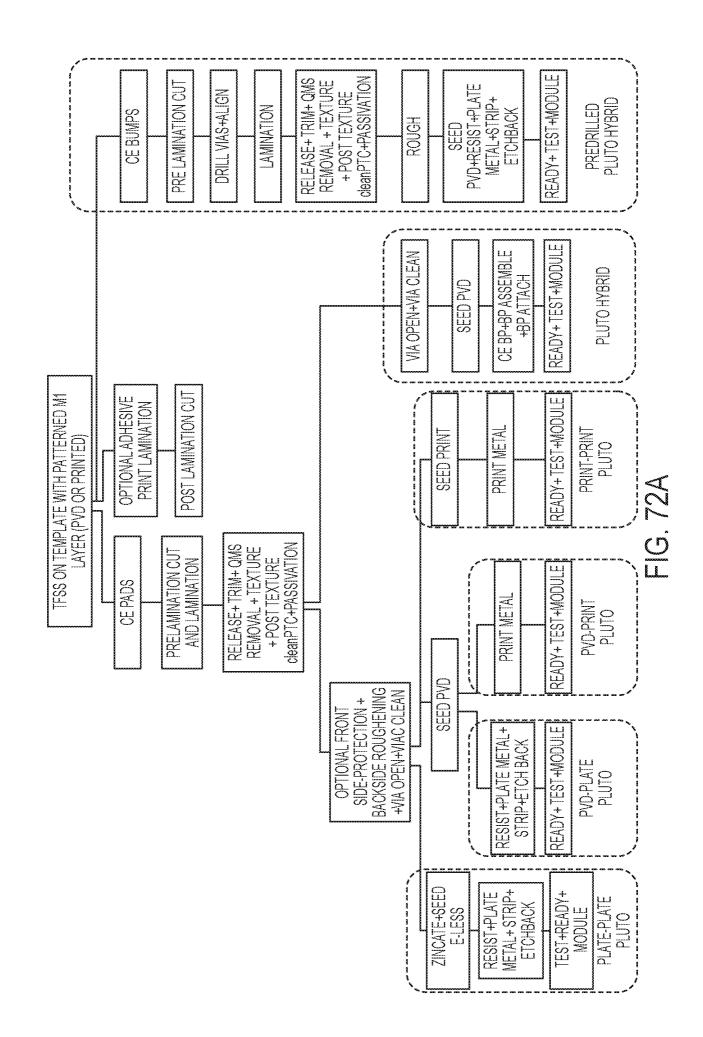

Figs. 72A shows process flows for manufacturing pluto backplane structures;

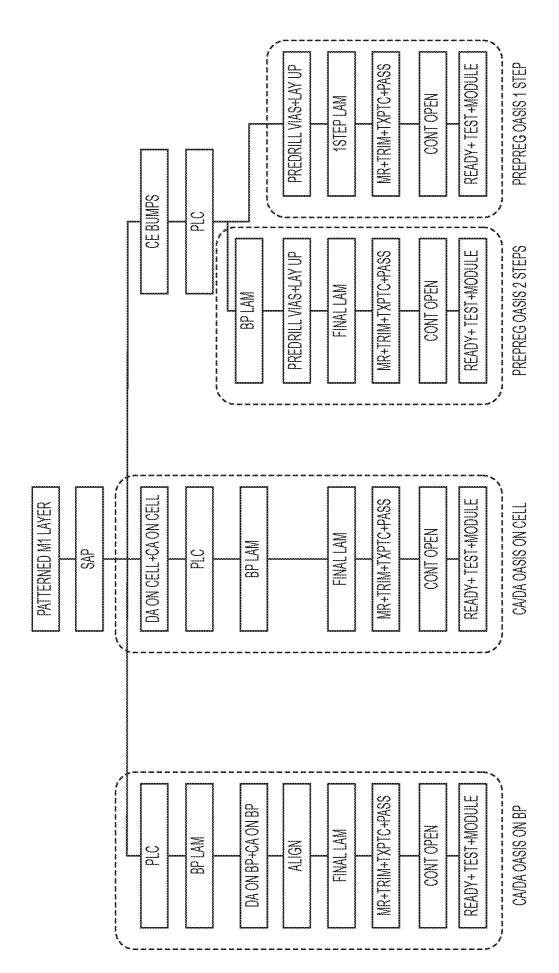

Figs. 72B shows process flows for manufacturing oasis backplane structures;

Figs. 73A through J show cross-sectional diagrams of a cell during fabrication steps of a pluto embodiment of back contact solar cell process flow;

**Figs. 74A** through **D** show a top view (**Fig. 74A**) and cross-sectional diagrams of a cell during fabrication steps of a oasis embodiment of back contact solar cell process flow;

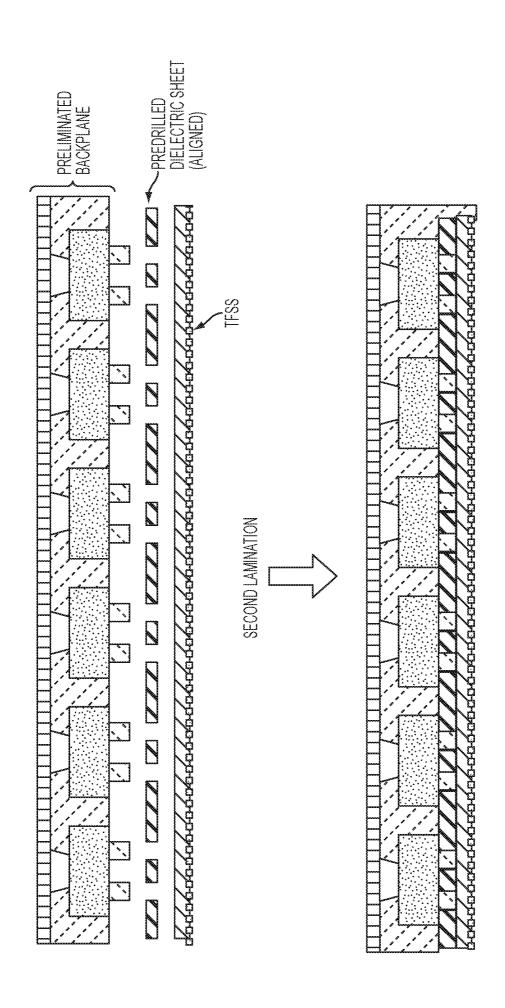

**Fig. 75** shows cross-sectional diagrams of an oasis structure two step lamination using a predrilled dielectric sheet;

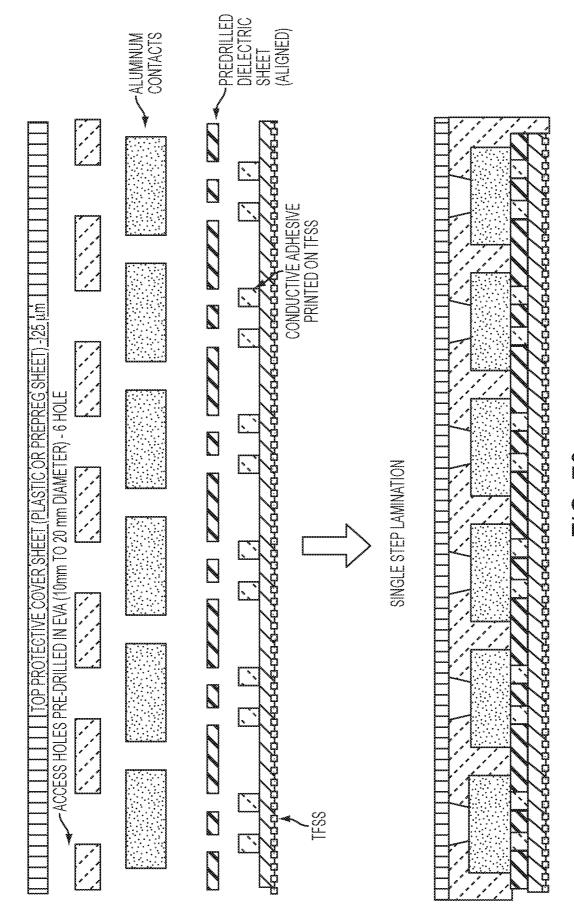

**Fig. 76** shows cross-sectional diagrams of an oasis structure single step lamination using a predrilled dielectric sheet; and

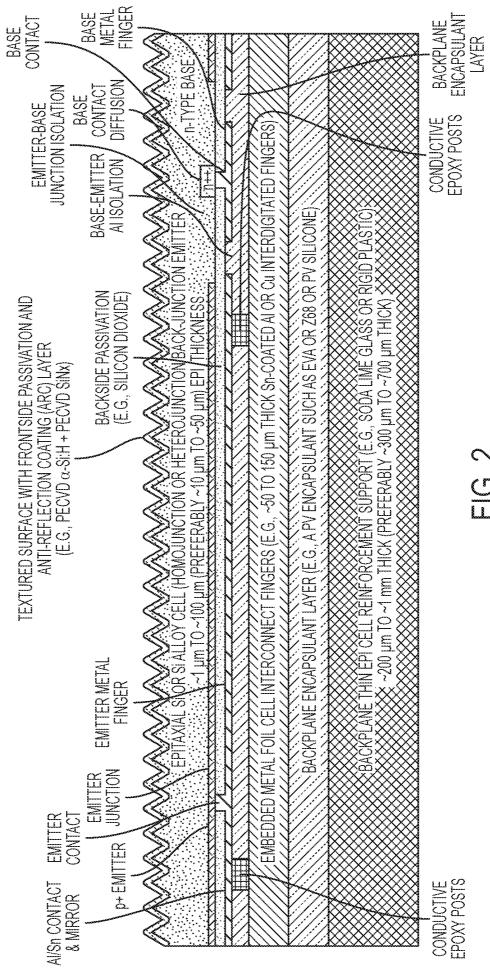

**Figs. 77A** through **D** are cross-sectional diagrams of a pluto-hybrid structure during back contact solar cell formation.

#### **DETAILED DESCRIPTION**

The following description is not to be taken in a limiting sense, but is made for the purpose of describing the general principles of the present disclosure. The scope of the present disclosure should be determined with reference to the claims. Exemplary embodiments of the present disclosure are illustrated in the drawings, like numbers being used to refer to like and corresponding parts of the various drawings.

And although the present disclosure is described with reference to specific embodiments, such as crystalline silicon and other fabrication materials, one skilled in the art could apply the principles discussed herein to other materials, technical areas, and/or embodiments without undue experimentation.

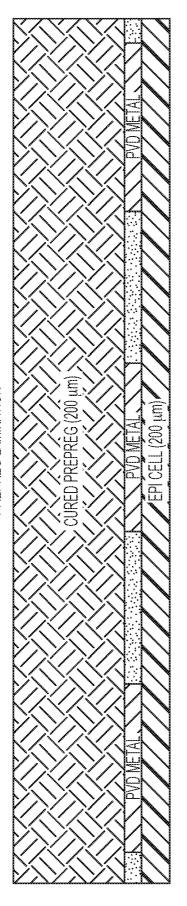

The disclosed subject matter provides various structures and manufacturing methods for high-efficiency back- junction/back contacted solar cells specifically using thin crystalline semiconductor absorbers such as monocrystalline silicon with the cell absorber layer (or substrate), preferably ranging in thickness from about less than one micron (1 µm) up to about one hundred microns (100 µm), and even more particularly ranging in thickness from about one micron (1 µm) to about fifty microns (50 µm). The cell structures and manufacturing methods provided also apply to thicker crystalline semiconductor substrates or absorbers, ranging in thickness from about 100 µm to about 200 µm (which also includes the thickness range for more conventional CZ or FZ wafer thicknesses). The crystalline solar cell substrates may be formed either using chemical-vapor-deposition (CVD) methods including epitaxial growth (such as atmospheric-pressure epitaxy) or other crystalline silicon material formation techniques (including but not limited to the so-called kerfless slicing or exfoliation methods utilization proton implantation, metal-stress-induced exfoliation, or laser). Various embodiments of manufacturing methods as it pertains to all aspects of processing very thin crystalline semiconductor solar cell substrates may be extended to other types of materials and to wafer based approaches, including kerfless cleavage methods such as the implantation-assisted wafer cleavage methods. Key attributes of various cell embodiments provided include substantially reduced semiconductor (e.g., silicon) material consumption, very low manufacturing cost, high cell efficiency, and relatively high energy yield, thus, improved solar photovoltaic module performance. Specifically, this stems from the combinations of the unique cell design architectures and manufacturing methods of this invention, which entail manufacturing back

junction/back contacted solar cells using thin crystalline semiconductor layers, yielding very high conversion efficiency on thin crystalline semiconductor substrates, yielding very low cost. While the variety of disclosed embodiments may be applied to various crystalline semiconductor materials (such as silicon, gallium arsenide, germanium, etc.), preferred embodiments for monocrystalline silicon are provided (which also apply to the other monocrystalline semiconductors including gallium arsenide, germanium, gallium nitride, etc.).

The disclosed subject matter provides innovations particularly pertaining to very thin crystalline solar cells (from about 1 micron up to 150 microns, and more preferably cell absorbers in the thickness range of about 1 micron to about 50 microns) with the back junction/back contact architecture. First, novel very thin (thickness range of 1 micron to 150 microns) back contacted/back junction crystalline silicon cell structures are provided. Secondly, methods for manufacturing back contacted/back junction crystalline silicon cell structures are provided. Thirdly, methods for supporting thin substrates (using *Carriers*) while they have being processed through the line and while they are deployed in the field are provided. Various combinations of these three categories create a myriad set of structures, process flows, and thin cell support carriers. Fig. 1 is a graphical flowchart showing the various thin film carrier combinations, comprising temporary Thin-Film Carrier 1 and permanent Thin-Film Carrier 2, disclosed herein. Fig. 1 shows the two classes of carriers whose varied combination constitute the novel structures and methods for manufacturing very thin back contacted/back junction crystalline semiconductor solar cells and specific embodiments which are disclosed herein. The two classes of carriers comprise first carrier and second carrier. Options for different cell fabrication process flows once the carriers 1 and 2 are established are also provided herein, including in Fig. 3. Note that, it is possible to have any of the process flows paired with most carrier 1 and carrier 2 combinations

The final structures obtained using these unique combinations are back-contact solar cells. Importantly, although this disclosure provides many unique sets of set of structures, process flows, and thin cell support carriers, it is understood that not all sets of possible process flows based are explicitly covered by this document, and the ones which are not covered are implied based on the cell design and process flow architectures disclosed herein. Several process

flows and alternative embodiments are provided with detail herein allowing one with skill in art to combine various disclosed aspects.

This disclosure provides various host carrier methods and structures used for supporting the thin semiconductor (such as thin monocrystalline silicon) cell. We start by first addressing the category pertaining to handling and supporting thin film silicon substrate (henceforth, TFSS) through its manufacturing and permanently reinforcing it - this is shown as Thin Carrier 1 and Thin Film carrier 2 in **Fig. 1**.

High manufacturing yield is a pre-requisite for commercially viable thin silicon solar technology. Very thin solar cells (from about 1 micron up to 150 microns, and more preferably cell absorbers in the thickness range of about 5 microns to about 60 microns) discussed in this document are fully and continually supported throughout the cell handling and processing to maintain high manufacturing yield and for commercial viability. This means that thin cells are never processed or handled without either temporary or permanent support attachments (also called substrate carriers). These thin semiconductor cells are also permanently supported (and reinforced) once assembled in the photovoltaic modules for installation and operation in the field maintain mechanical resilience, reliability, and high yield during module lamination/packaging, field installation, and field operation. Because both sides of the solar cell need to be accessed and processed (to complete the cell backside and sunnyside), in general, two carriers are required for TFSS (in order to always support the thin semiconductor substrate throughout handling, processing, and final module packaging): one for processing each face of the solar cell. The carriers must satisfy several important criteria: firstly, they should be costeffective (i.e., very low cost per cell or very low cost per peak watt). Their combined amortized cost should be less than the cost of the silicon in the thin cell that they save (compared to the traditional wafer-based solar cells). Secondly, at least one of the carriers should be able to withstand relatively high temperature processing (particularly at temperatures in the range of approximately 300°C up to as much as 1150°C) required in manufacturing of high-efficiency solar cells, without any complications due to mismatch in coefficienct of thermal expansion (CTE) and/or due to undesirable impurities being introduced into the cell. In addition, if only one of the carriers is able to support high temperature cell processing (i.e., high-temperature processing to form the cell substrate itself using CVD epitaxy as well as to complete the cell

backside device structure as required), the process flow should be such that all the necessary high temperature processing steps are on this high-temperature-capable carrier (which will serve as temporary reusable carrier). As mentioned before these particular criteria are highly favorable to back contacted/back junction cell, hence, truly enabling high efficiency back-contact, backjunction thin cells. Thirdly, at least one of the carriers should preferably be able to withstand wet processing and final cell metallization required for manufacturing solar cells. An example of a key wet processing step includes silicon front surface random pyramid texturing etch in diluted and heated alkaline (comprising KOH and/or NaOH and/or TMAH) solutions. Fourthly, once the first side (preferably the cell backside for the back-contact / back-junction cell processing) is partially or fully processed, the carrier (which serves as temporary reusable carrier) should be such that the thin cell (Thin Film Semiconductor Substrate: TFSS) may be easily detached or lifted off from the carrier on demand with high yield and with the TFSS layer transferred to the other carrier in conjunction with the lift-off detachment process (attached on the side which was processed first, preferably the cell backside for back-contact cell) for processing of the second side. Subsequently, in the case, where the first side (preferably the cell backside) was only partially processed, the remaining process steps (for instance, such as completion of the final cell metallization) can be completed using, for example, various embodiments detailed below. Preferably within the embodiments of this invention, the high-temperature-capable temporary carrier and the high-temperature processing steps precede the permanent carrier as well as the wet processing and final cell metallization steps. Moreover, starting with the formation of the thin-silicon substrate using CVD epitaxy till the pre-lift-off attachment of the permanent carrier to the TFSS layer, all the process steps performed on the TFSS while on the temporary carrier are preferably dry processing steps (no wet processing on the temporary carrier other than a wet porous silicon process step prior to the formation of the TFSS layer by CVD epitaxy). Furthermore, the cell contact metallization is preferably performed after formation of the cell contacts and prior to the attachment of the permanent carrier and prior to the lift-off separation of the TFSS layer from the temporary reuable carrier or template.

Supporting Carrier # 1 (i.e., reusable template) for TFSS. For the combination of TFSS with back contact/back junction architecture two choices for the first carrier are disclosed, henceforth <u>carrier 1</u>. These options are shown in **Fig. 1** under carrier 1. In the remaining

document Sunnyside of the Back contact/back junction cell will be interchangeably referred to as the cell "frontside", while the non-sunny side will be interchangeably called the cell "backside".

1. The first disclosed option for carrier 1 is a relatively thick (preferably in the thickness range of about 0.2 mm to 2 mm) semiconductor (e.g., preferably mono-crystalline silicon for highefficiency mono-crystalline silicon solar cells) wafer (with wafer area in the range of 150 cm<sup>2</sup> up to over 2,000 cm<sup>2</sup>), which may also serve as a reusable template (hence amortizing cost over many template reuse cycles). Large area thin solar cell substrates, with desirable cell areas, for instance, square-shaped cell dimensions of 156 mm x 156 mm (this size may be scaled up to at least 210 mm x 210 mm or even larger sizes up to 300 mm x 300 mm and 450 mm x 450 mm), are first manufactured using epitaxial semiconductor (epitaxial silicon) growth on top of a reusable crystalline semiconductor template, and are subsequently dislodged. The reusable template can be substantially planar or in a different embodiment have pre-structured 3-dimensional pre-pattern. This document focuses on the substantially planar template, although various embodiments can be applied to the pre-structured templates with random structure or patterned regular structure 3D features. It may be reused several times (preferably at least 10's of times) for epi (epitaxial silicon) growth, which amortizes its cost over the reuse cycles. After its useful reuse life, the reusable template can be ultimately recycled to make new templates through CZ crystal growth and wafer slicing. The TFSS is released from the reusable template using a sacrificial release layer which in one preferred embodiment may be a porous silicon layer, preferably with at least with two different porosities (a higher porosity buried release layer and a lower porosity seed layer) or a graded porosity. The reusable template, since it is preferably a relatively thick (preferably in the range of about 0.2 mm to 2 mm) silicon wafer, is capable of withstanding relatively high processing temperatures (e.g., up to about 1150°C or even higher) without any CTE mismatch issues with the subsequent TFSS and without any contamination concerns, satisfying one of the key criteria for carrier 1, outlined above. The template can be in various sizes such as 156 mm, 165 mm, 200mm, 300mm or 450 mm (or any diametric or side dimensions in the range of about 100 mm to several hundred mm, at least up to 450 mm), shapes, such as round or square or polygon, and thicknesses capable of going through full or partial solar cell process without cracks or breakage, with template thickness of about at least 200 µm (and as thick as about 2 mm or even thicker). The second criterion for carrier 1,

related to cost effectiveness is accomplished by reusing and amortizing the template cost over a plurality of TFSS fabrication cycles (as well as by using unpolished templates if necessary or desired). Finally, this carrier also satisfies the aforementioned carrier criteria of being conducive to the high-yield detachment of the TFSS with high repeatability and consistency. This is accomplished by preceding the epitaxial growth of TFSS with formation of a porous silicon layer (serving as an epitaxial seed layer and subsequent release layer) between the template and the TFSS, preferably using a wet electrochemical etch process in a liquid comprising HF and IPA (or HF and acetic acid, or HF mixed with another suitable material). The porosity of the porous silicon layer is catered and spatially adjusted in depth (by using a lower porosity top layer and a higher porosity buried bottom layer) to accomplish the dual purpose of i) transferring the crystallinity of template with high fidelity during the epitaxial process, and ii) yet be able to provide very high yield detachment and release on demand from the template. The cell release may be accomplished using processes such as mechanical release (MR) or sonicated mechanical release in a liquid (SMR), or another suitable method, resulting in lift-off detachment of the TFSS layer after its attachment or lamination to the permanent carrier 2.

2. The second disclosed option for carrier 1 can be a reusable thick wafer or an ingot. The detachment of the TFSS may be accomplished using a high-implantation-energy such as an MeV (mega-electron volt) proton (hydrogen ion) implant and separating thin slices from the host wafer or ingot.

When the porous silicon/epi technique on the host carrier is compared with the thick wafer/ingot and implant induced separation technique several trade-offs can be identified. The wafer/ingot with implant has the advantage of not needing porous silicon and epitaxial growth and the accompanying reactors (however, it has dependency on polysilicon feedstock and ingot growth). On the other hand it needs rather expensive MeV proton implantation capital equipment and high energy consumption to operate the implanters. The quality of silicon can be high depending on the cost of the ingot and it can potentially also allow wet processing. A downside is that because the ingot may have <111> orientation in order to eliminate the need for excessively high proton implanation doses, the wafer may rely on more-expensive and damage-producing dry texturing as opposed to the standard wet texturing. The porous silicon/epi combination has the advantage that it is compatible with standard alkaline wet texturing and the

substrate doping can be modulated/graded to whatever is conducive for high efficiency requirements. Also, very thin silicon cell substrates (down to about one micron) are possible using a porous silicon/epi manufacturing method and the doping profile can be engineered and adjusted during the epitaxial growth process (not possible for the thin silicon layers produced by proton implantation).

Supporting Carrier # 2 for TFSS: Backplane. The second carrier, in the specific context of back contacted/ back junction cells should preferably satisfy several criteria. An obvious one is that it must support the TFSS through the remaining process steps. Secondly, it should protect the prior processing on the side where it is attached (backside for our specific architecture), while the other side (frontside) is being processed. This requires that the second carrier preferably be relatively immune or resistant to the wet chemistry that is used during processing of the frontside (particularly and primarily the wet chemistry used to clean and texture the TFSS sunnyside). Thirdly, it may or may not have high-conductivity metallization layer (preferably comprising aluminum and/or copper) as its integral part. For the case where it does have metallization, in addition to being a carrier (preferably a very low cost permanently attached carrier), it provides metallization which seamlessly attaches to the metal on the cell with low resistance. Finally, though not as high a priority, it should have thermal processing capability sufficient for acheiving excellent frontside passivation (therefore, preferably at least up to a temperature of about 180°C and more preferably at least up to a temperature of about 250°C or even 300°C) without producing cracks in TFSS due to any CTE mismatch with silicon and without degradation of the carrier material. This second carrier attached to the solar cell backside henceforth, will be identified as the solar cell "Backplane."

Several backplanes embodiments are disclosed herein and outlined in **Fig. 1** under the Thin Film Carrier 2 heading. It is important to note that any of the several options outlined for carrier 2 in **Fig.1** may be used in conjunction with either of the two carrier 1 options, which are discussed above, that is, any carrier 2 embodiment be used with either the Reusable template/epi/porous silicon option or with the Ingot (or thick wafer)/Implant option.

Carrier 2 (the backplane) may be divided into two broad classes (**Fig. 1**): The first category, "Full Backside Process on Carrier 1" is where carrier 2 is attached only after all the required processing on the side where it attaches (backside) is completed on carrier 1. In a back

contact/back junction cell this might entail finishing all non-sunny side (backside) processing steps including patterned dopant diffusions, contact opens, and full backside contact metallization. No further processing is required on this side, except in some cases, where electrical access to the final cell metallization is required. The second category, "Partial Backside Process on Carrier 2" is where carrier 2 is attached after only partial processing on the backside is finished. Although, this document focuses on the latter category with partial processing and discusses several sub-groups that are possible within this paradigm, it is understood that a variation entailing full processing per the first category is implicit and within the scope of this invention.

One of the driving forces behind the partial processing paradigm on the non-sunny side (i.e., cell backside) is to ensure that if potentially deleterious materials (including lifetime degrading materials), such as copper, are part of the backside processing, they do not contaminate carrier 1, which can be reused for carrying other TFSS (hence, preventing the risk of metallic cross contamination in the production line). This prevents cross contamination in the manufacturing line and the resulting efficiency degradation (hence enabling high-yield template reuse without the risk of cross contamination to the cells). Thus, an idea behind partial processing on the non-sunny side is to introduce the potentially lifetime-degrading materials and processes (such as high-conductivity copper plating metalliation) after the TFSS is detached and released from carrier 1, hence, eliminating the risk of cross contamination.

Three sub-categories of backplanes within the partial processing paradigm are shown in **Fig.**1. In the first case, referred to as front surface reinforcement, "FSR", the TFSS is released from the template using a temporary carrier attached on the partially processed backside. Subsequently, the frontside cell processes such as texture and passivation are carried out with the temporary backside carrier supporting the TFSS. The temporary carrier is choose by the ease of release of the TFSS and may utilize known methods, such as electricity (ex. Mobile electrostatic chuck, MESC), mobile vacuum chuck, MOVAC, or a temporary adhesive which is released upon heating or upon UV exposure. The remaining backside steps (for example, copper metallization) are performed by transferring the TFSS from the temporary backside support to the optically transparent permanent front side reinforcement (for example, a low-cost EVA encapsulant/glass combination), thus freeing up the backside for remaining processing (for

example remaining metallization steps). A specific requirement of the front side reinforcement being that it does not degrade light transmission and coupling beyond the degradation usually incurred due to module level packaging. Thus, EVA/glass based reinforcement or the like is preferred, although, other material sets are also possible (such as EVA with a clear front fluropolymer sheet made of ETFE).

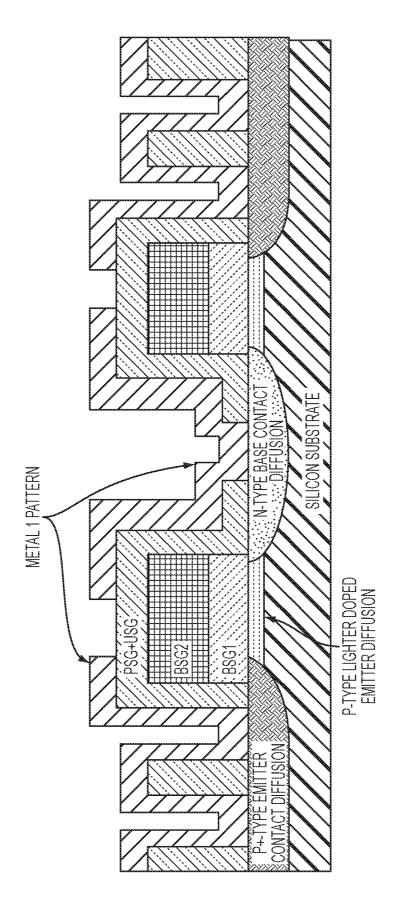

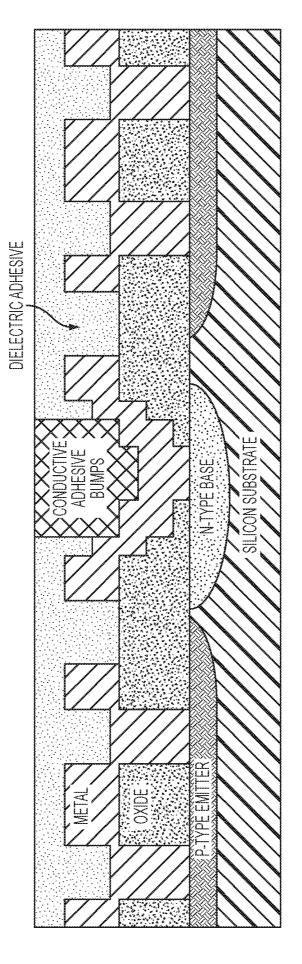

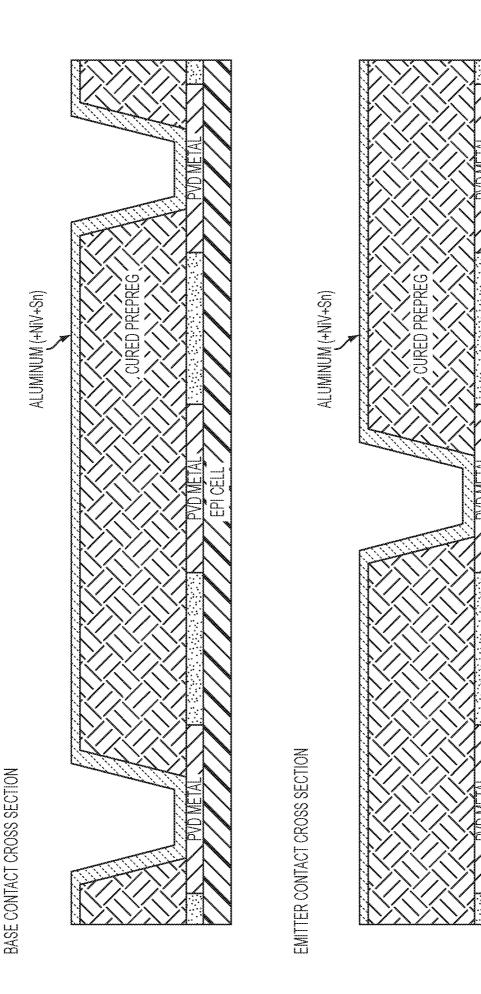

The second and third subcategories, "Backplanes without Metallization" and "Backplanes with Metallization," of backplanes with partial backside processing are characterized by backplanes which are permanent (in contrast with aforementioned FSR). A difference between these two categories is that the "Backplanes without Metallization" do not have thick metallization integrated or embedded in their structure; rather, this metallization is put on toward the back-end after the frontside (sunny-side) is processed. Whereas, "Backplanes with Metallization" have a thick second level of metallization (for instance, a patterned metal foil) integrated into the backplane. The thick metallization layer on the backplane connects to the thin metallization layer on the TFSS, forming the second layer of interconnects, and may also contain busbars. This thick high-electrical-conductivity metallization layer (preferably made of aluminum and/or copper) decreases resistance for back-contacted cells.

This disclosure details three particular embodiments within the "Backplanes without Metallization" subcategory of backplanes. Importantly, this should not be construed as limitation of this paradigm to these three embodiments. The first case is called Back Surface Reinforcement or "BSR." In this process flow, the TFSS is released from the template (the first carrier) using a permanent backside reinforcement. The permanent backside reinforcement only partially covers the backside, thus allowing processing on the backside through the open areas, after front side processes are completed also with the BSR support. A structural example of this is a backplane made in a grid pattern with a substantially large open area between the grids providing access to the backside for last several processing steps on the non-sunny backside.

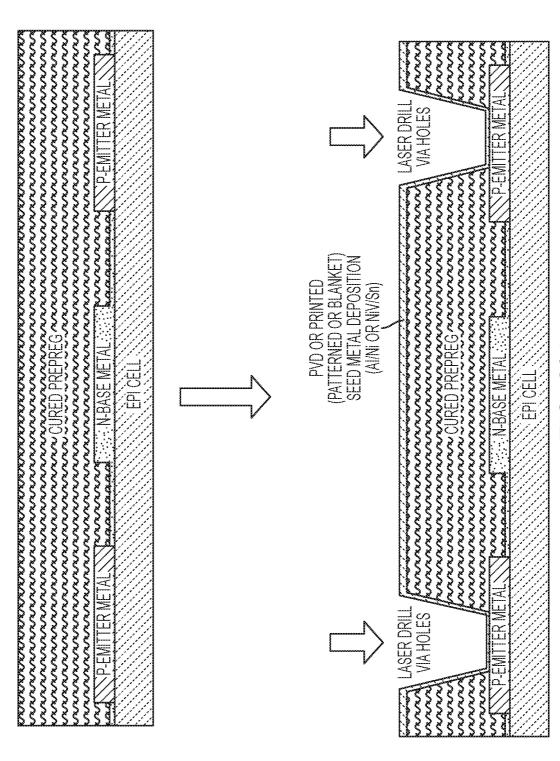

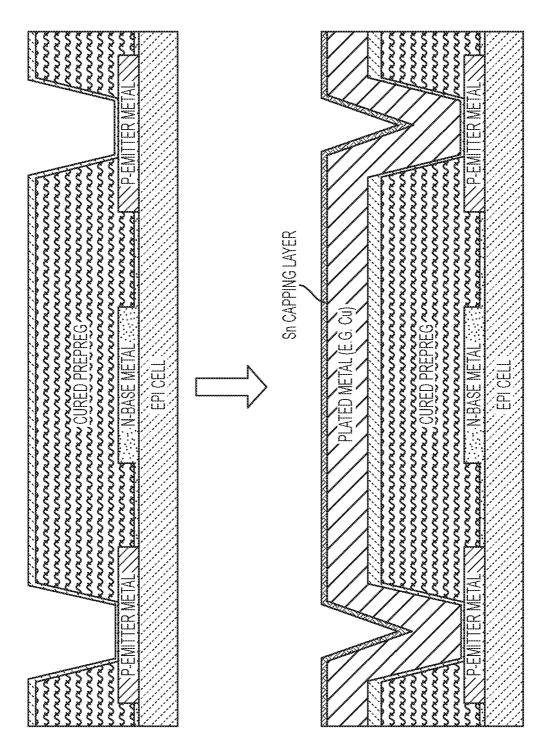

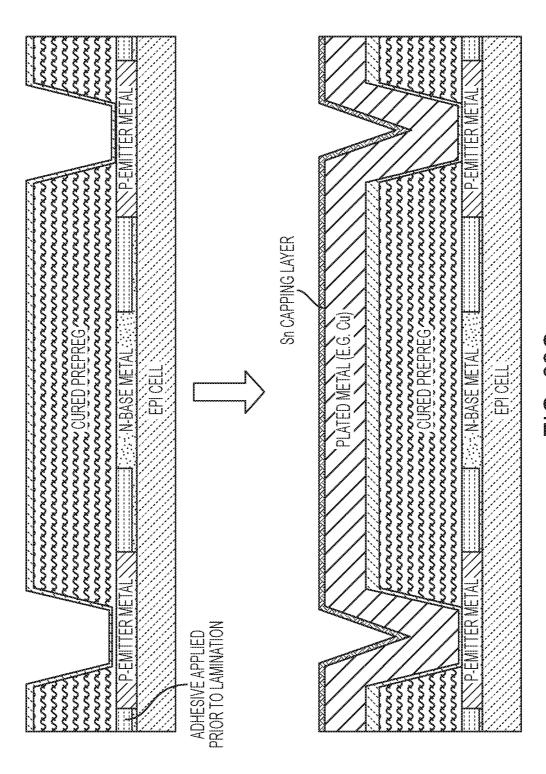

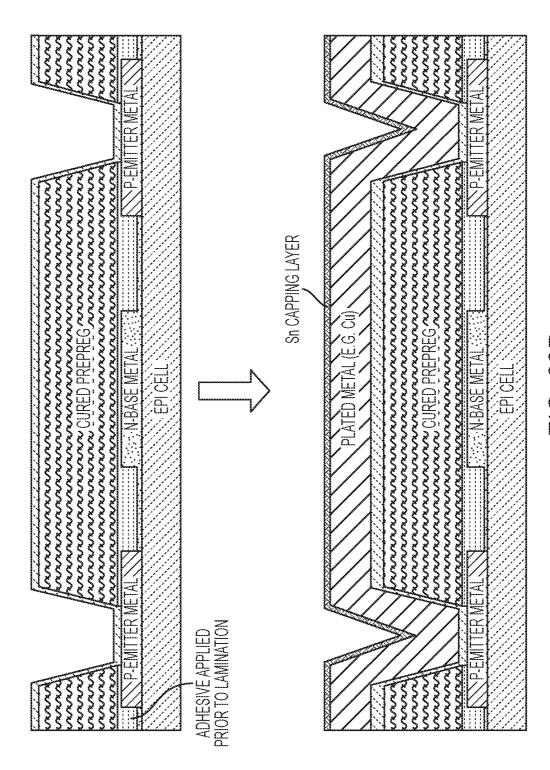

The second embodiment of a permanent "Backplanes without Metallization" is a design known as acronym "PLUTO." In this process flow, a simple and cheap backplane material (e.g., a relatively low-CTE Pre-preg material comprising a mixture of resin and fibers) is attached to the TFSS, while it is attached to the first carrier. The backplane attachment may be a direct bonding/lamination (if material has adhesive in it) or use an intermediate adhesive layer, for

example a dielectric adhesive (DA) which may be printed using means such as screen printing (or applied using a spray coater or a roller coater). The pre-preg assembly/material choices should be such that they meet the following criteria:

- a. The released TFSS/Pre-preg assembly should be relatively stress and crack-free with very little bow.

- b. The backplane should maintain crack-free properties and should not induce stress cracks in the TFSS, while going through subsequent processing steps such as frontside texturing (e.g., using hot KOH) and PECVD passivation processes.

- c. The backplane should be relatively resistant to the chemicals used during frontside processing such as texturing and post-texture surface cleaning (and any possible pretexture silicon etch).

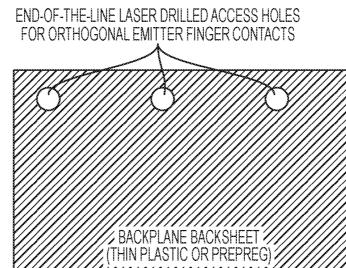

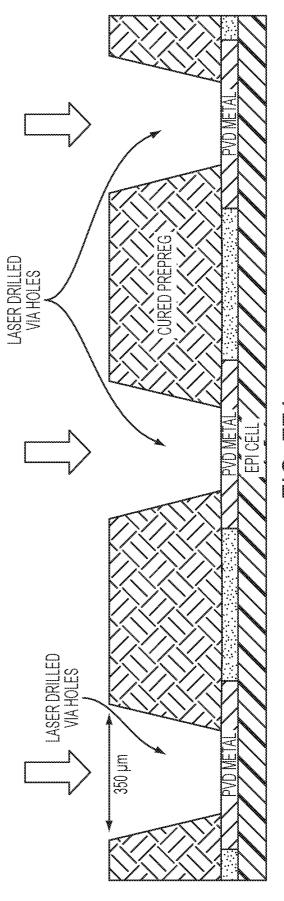

After all frontside processing is completed using the PLUTO backplane, access holes (100's to 1000's of holes) are drilled, preferably using a high-productivity laser drilling tool, through the backplane (such as a pre-preg material) and remaining cell metallization is finished, preferably either by plating or using a combination of screen printing of a patterned electrically conductive seed paste and attachment of a pre-patterned metal foil layer (comprising aluminum and/or copper). These holes provide access to the underlying on-cell patterned metal which was formed while the TFSS was on the template (specific examples will be illustrated during the subsequent discussion on process flows). The drilling of holes may be accomplished using a myriad of laser and mechanical methods, in a specific example this can be accomplished using a fast throughput CO2 laser. Requirements for the drilling technique include fast throughput, no damage to the TFSS or the underlying metal on the TFSS, a reliable way to clean the laser opened contacts (if necessary) to have low resistance electrical access to the underlying metal on the TFSS, and proper alignment of the holes to the underlying metal. Subsequent to the laser drilling the rest of the metallization (comprising a second level of metal) may be finished using several method including plating (both electroless and/or electroplating), direct thick metal write techniques such as flame spray, attaching a cheap bread-board with metallization to the backplane, attaching metal foil fingers after screen printing of a patterned conductive seed paste, or having the metallization as part of the module assembly in approaches such as monolithic module assembly (MMA). A slight modification process includes an embodiment in which the pre-preg has pre-

drilled holes prior to its attachment / lamination to the TFSS (to eliminate the risk of laser-drilling-induced damage to the TFSS) and is protected by another easily removable cheap thin material layer or sheet (such as a thin Mylar sheet or another suitable material). In this embodiment, the removable protective sheet will be preferably removed after completion of the sunnyside cell processing (including at the wet texture and PECVD passivation processes), and prior to completion of the final cell metallization (or prior to module assembly in the case of MMA).

The third embodiment, "Cu Plugs," of a permanent "Backplanes without Metallization" of Fig. 1 is a design with a slight modification of the aforementioned so-called PLUTO embodiment. And although, specifically identified with a metal as a naming convention, this approach should not be construed to be limited to copper as the electrically conductive material. In this case, the backplane has an additional layer backing compared to PLUTO. For example, the backplane may consists of glass or other harder solid backsheet materials (e.g., anodized Al) with a pliant attachment material such as an encapsulant PV-FS Z68 (from DNP Solar), also called Z68 in short, or Ethylene Vinyl Acetate (EVA). The backsheet may have pre-drilled holes, but the underlying attachment material serves as a sealant to protect the TFSS metal from being chemically attacked during frontside processing (such as during fronside wet alkaline texturing). After texture and passivation processes, the sealant material is opened up through the pre-drilled holes in the backsheet (for example soda lime glass, SLG). This may be performed using a myriad of methods such as laser drilling or mechanical punching. Once these holes are opened, a continuous seed metal layer is deposited either using a direct write scheme such as metal ink/paste printing (using s stencil printer, screen printer, inkjet printer, or aerosol jet printer), or PVD (e.g., plasma sputtering), or electroless plating. The metal is then thickened by plating and isolated between p and n type diffusion contact metals on top of the backsheet. Various known plating and isolation processes may be used including, for example a screen print resist, then blanket plating of metal, then etch back the resist and use the plated metal as the mask to etch the underlying thin seed metal layer. Alternatively and preferably in our embodiments, a patterned electrically conductive paste is formed by direct write on the backplane, such as with screen printing of a suitable paste (e.g., paste containing copper or nickel or another suitable conductor). Then, the final metallization is completed using direct plating

(e.g., such as copper plating) on the patterned plating seed (hence, eliminating the need for sacrificial resist and resist strip and seed etch-back processes).

Another embodiment uses a single sided or a dry frontside texturing process so that the need to protect the partially processed backside is obviated and all access points can be preopened (using laser drilling or mechanical drilling or punching) either before attachment of the backplane or before processing the frontside.

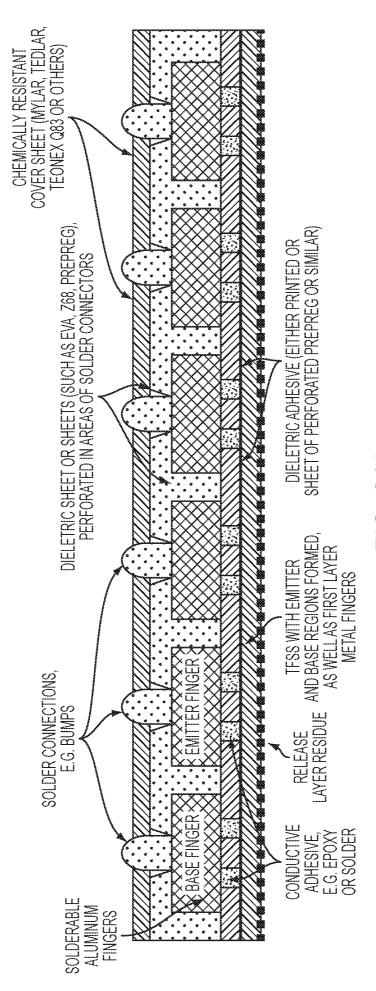

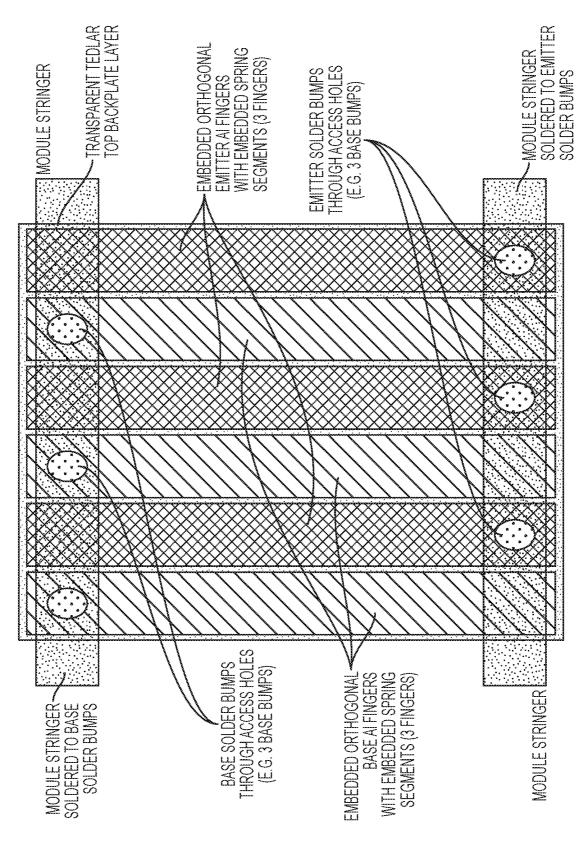

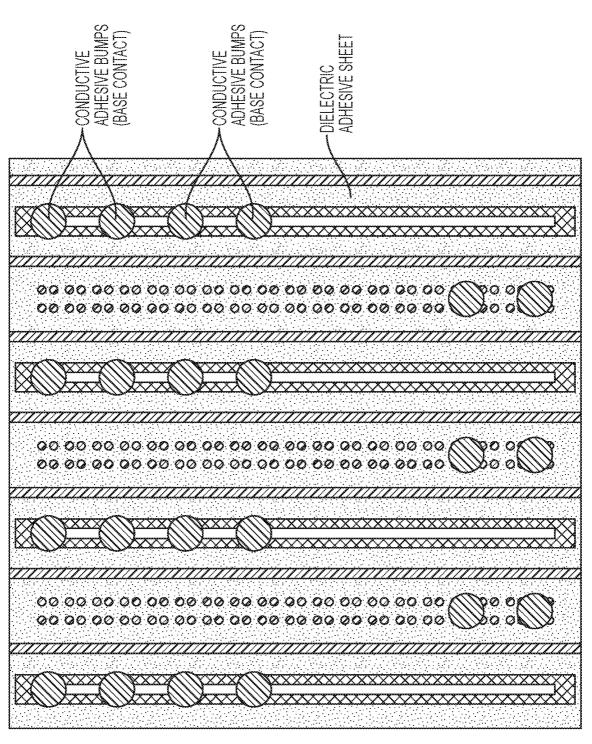

The "Backplanes with Metallization" subcategory of backplanes, as shown in **Fig. 1** with partial backside processing, are characterized by backplanes which are permanent and have integrated metallization. Three embodiments of the "Backplanes with Metallization" are disclosed in detail in **Fig. 1**: Ahown with acronyms OASIS, SLG-based (soda lime glass), and "Metallization on non substrate side" (backplanes with metallization facing away from the TFSS). In two embodiments, OASIS and SLG-based, the backplane-integrated metal faces the TFSS during its lamination/bonding to the TFSS, while in the third embodiment, "Metallization on non substrate side," the metallization of the backplane faces away from the TFSS.

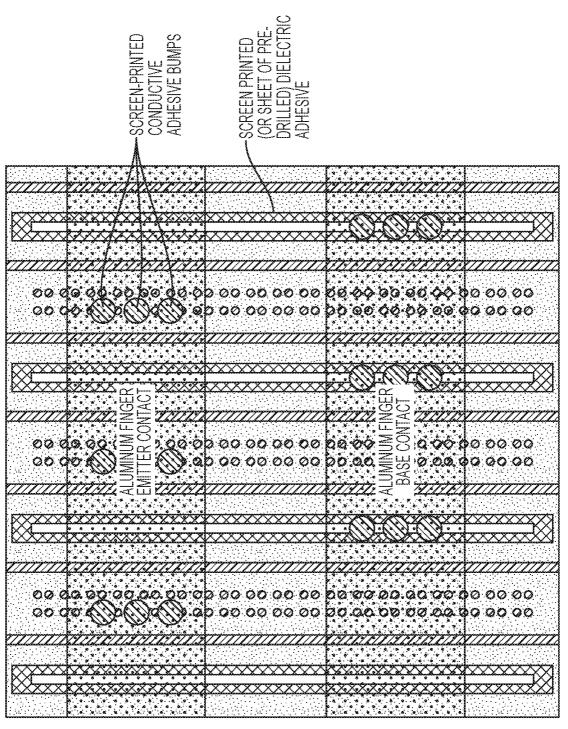

The OASIS backplane embodiment has several components. First, it consists of a metallic backplate which may or may not also serve as the metallization layer. This metallization layer, which in a particular embodiment is patterned into inter-digitated fingers with busbars, may be made, for example, from Al foils or solderable aluminum foils. The Al foils may be precoated or pre-plated with nickel and Sn (or a Sn solder alloy) to provide better adhesion of the conductive vias which connect the second level of interconnects to the first level of interconnects on the TFSS. The backplate may be protected from chemical attack on the top by a suitable protective layer such as Z68, EVA or prepreg or another suitable polymeric / plastic cover sheet. These layers are ultimately opened up to provide access for the testing and module connections from the top. During lamination of the patterned metal to the EVA or Z68 like material, substantial planarity must be accomplished by exploiting the flow of the attachment material such that the final assembly should be substantially planar from both top and bottom. At the planar bottom of this assembly, the connection of the Al foil metal to the underlying TFSS metal is made using selective conductive posts or vias in the dielectric layer which has gaps to accommodate the electrically conductive vias. The conductive vias (henceforth conductive epoxy or CE) and the dielectric material (henceforth dielectric epoxy or DE) in the preferred

embodiment are screen printed on either the TFSS or on the backplane. CE material requirements include cost effectiveness, highly conductive, it may be screen printable in a preferred embodiment, and that it attaches with low contact resistance to both the overlying backplane metal and the underlying TFSS metal. DE material requirements include cost effectiveness, that it is a non-electrically-conductive dielectric, it may be screen printable in a preferred embodiment, and it adheres well to both the overlying backplane material (both metal and the EVA orZ68 dielectric encapsulant) and the underlying TFSS materials consisting of both TFSS metal and dielectric. For example, the OASIS backplane may have a myriad of variations based on choices in the following categories:

- a. Backplate material in the backplane: examples include aluminum foils, Al foils coated with Sn, or glass (different kinds of glasses including the soda lime glass), or other polymeric materials. The requirement is that the backplate material should give the strength and rigidity to the backplane to carry the TFSS. It should also be such that during subsequent thermal processes, it does not induce cracks in the TFSS because of thermal expansion coefficient mismatch.

- b. Patterned Metallization material: examples include Al foils which may be coated with other metals to make them conducive for low contact resistance attachment to the electrically conductive vias. In another example, these may be pre-coated Al foils. In one embodiment the metallization material may be the same as the backplate material or it could be attached to the backplate material using adhesive. The thickness of the metallization is dictated by strength requirement if it is the same as the backplate and the resistance requirements.

- c. Pattern Design of the metallization: Options primarily consist of the number and hence the width of inter-digitated fingers that are used. The widest width and the least number of fingers that is used may be determined by the largest tolerable resistance (without degrading Fill Factor) on the TFSS metal line between conductive via posts. A second consideration which falls under pattern design is whether the metal foils have additional functionality. For example, they can be designed to give a partial spring-like action, which may be accomplished, for example, either by having them physically separated within each finger or by partially cutting them in a snake-like pattern; however, various designs are possible. The spring-like functionality is geared toward providing the metal

foils to expand and contract freely such that they do not rupture the CE or the TFSS due to thermal expansion coefficient mismatch.

- d. The choice of the dielectric and the conductive connection material: criteria for selection of these materials are already discussed above.

- e. Method of depositing the CE and the DE materials: in one preferred embodiment these are screen printed. This print can be either on the TFSS or on the backplane.

- f. Orthogonal vs. Parallel Design: Whether the backplane metallization (second level metal or M2) is parallel or orthogonal to the on-cell TFSS metallization (first level metal or M1) is dictated by several considerations. The orthogonal backplane (M2 fingers orthogonal or cross-cut or perpendicular to M1) has an advantage that the width of the lines on the backplane (or the width of M2 fingers) can be independent, in general, and specifically, much wider than the M1 fingers. This helps in making this metallization much coarser and with less strongent alignment requirements than M1. However, precaution needs to be taken to ensure that orthogonal lines do not short. Thus, the dielectric material has to have good coverage. Parallel design restricts the pitch and dimensions of the backplane metal (M2) to be the same as the on-cell TFSS metal (M1) design. This design on the cell is in general fairly tight and, in turn, is dictated by several device considerations including reduced base resistance, reduced electrical shading, etc.

- g. Access scheme of the foil busbars for the module connections: For example, this may be through through-holes through the protective layer or may be a wrap around where the Al foils are wrapped around to the top of the backplane, and protected for example by a laminated polymer during processing of the frontside and contact access to the foils is enabled at the end of the process.

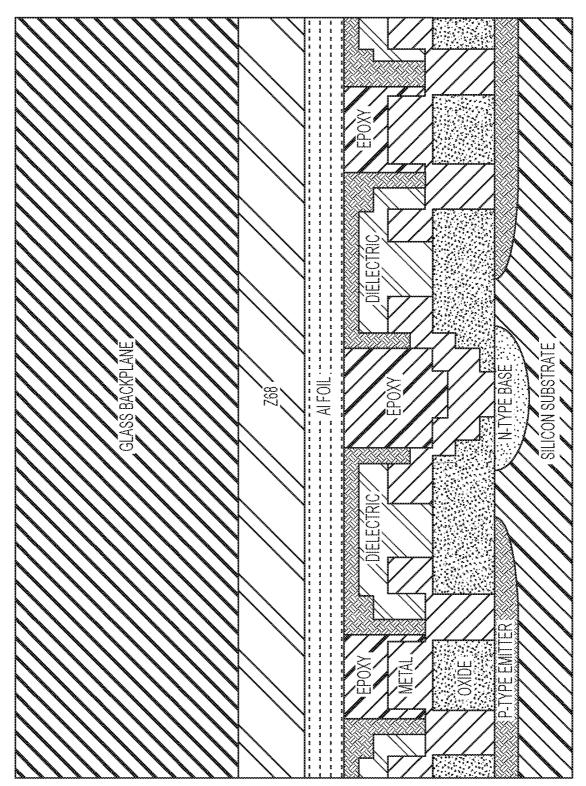

- Fig. 2 is a diagram of a cross section of an SLG-based back contact solar cell embodiment. The soda-lime glass or SLG based embodiment as disclosed herein is a subcategory of the so-called OASIS backplane, where the backplate material is a soda lime glass sheet as shown in Fig. 2. This is attached to the Sn-coated (or solder alloy coated) Al foil metallization using Z68 (or another suitable encapsulant) material. The Al foils wrapped around the glass to have the busbars on top of the glass backplane, and thus are sealed with the protective z68 on the sides as well. The "Metallization on non substrate side" back contact solar cell embodiment has the integrated metallization of the backplane on the side facing away from the TFSS.

Specific examples in which these backplanes may be fit into process flows for forming back contact solar cells are outlined in the manufacturing methods below.

# General Structures and Methods for TFSS-based Back Junction/Back Contacted Solar Cells

The above discussion pertained to the choices and combinations pertaining to first and second (backplane) carriers for ensuring high processing/manufacturable yield for TFSS back junction/back contacted solar cells. The following section deals with manufacturing methods and process flows for an entire TFSS based solar cell with these carriers. While depicting process flows, in several cases, the backplane is abstracted. This abstraction may be replaced by any of the several backplane options that were discussed in the above sections. In addition, the combination of the backplane with specific flows may either be used with the template/Porous Silicon (PS) based carrier 1 or the Ingot (or Thick Wafer)/implant based carrier 1. Specific flows pertaining to these two cases will be shown. Fig. 1 shows process flow options and their relations to carrier 1 and carrier 2; however again it should be noted that the process flows in Fig. 1 or the following process flows are descriptive examples and should not be used in a restricted sense. Further, these exemplary process flow embodiments should be interpreted as being able to be used with the myriad backplane options as well as any of the two carrier 1 options. A noted exception to this is that in-situ emitter based process flows may not be used with Ingot (or Thick Wafer)/implant carrier 1 option.

Ex-situ vs. In-situ Emitter. The process flows shown Fig. 1 may be further categorized into two broad categories of process flows: Ex-situ emitter where the emitter is not formed as an integral part of the epitaxial growth process and is produced after the TFSS is manufactured using techniques such as atmospheric pressure chemical vapor deposition (APCVD) epitaxial growth. And in-situ emitter which is appropriate for the carrier 1 template/porous silicon option and is grown as part of the silicon epitaxial growth of the TFSS (hence, eliminating the need for subsequent formation of emitter). This disclosure focuses on the embodiments with ex-situ emitter formation; however, in-situ emitter based flows may also be applicable in some instances by one skilled in the art. With respect to the aforementioned options of ex-situ and in-situ emitter, the following considerations should be noted.

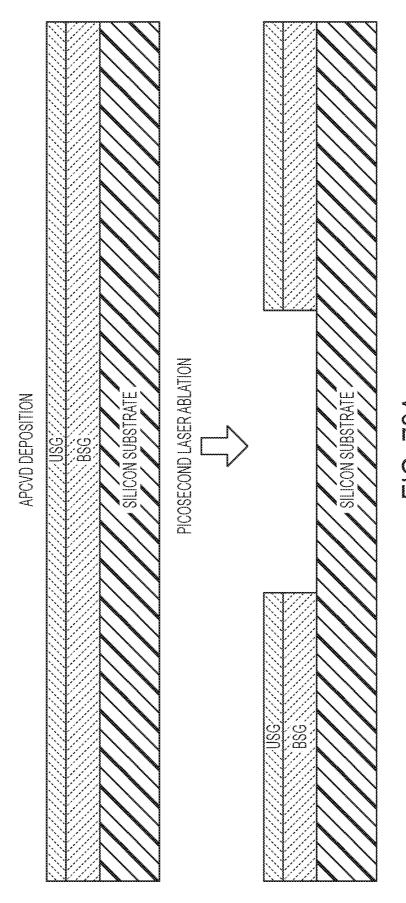

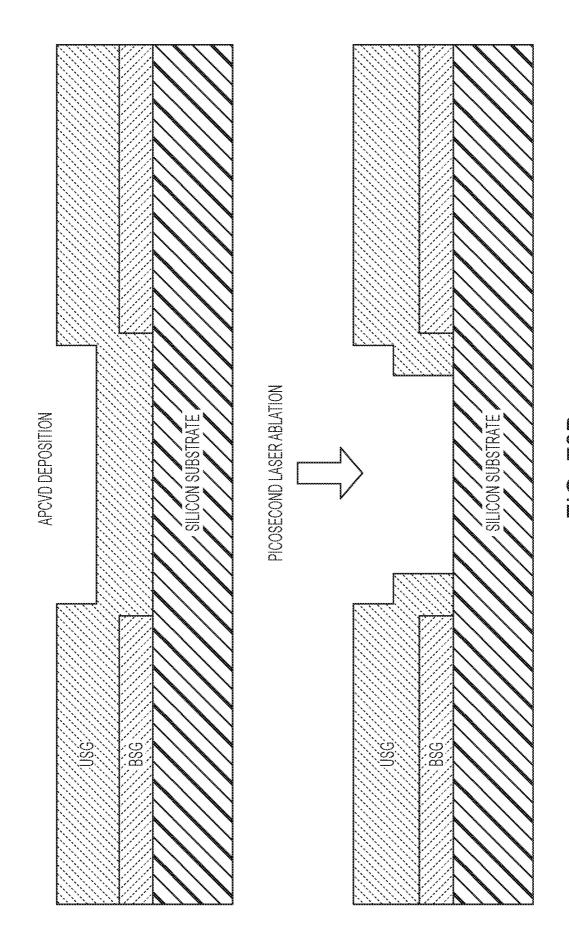

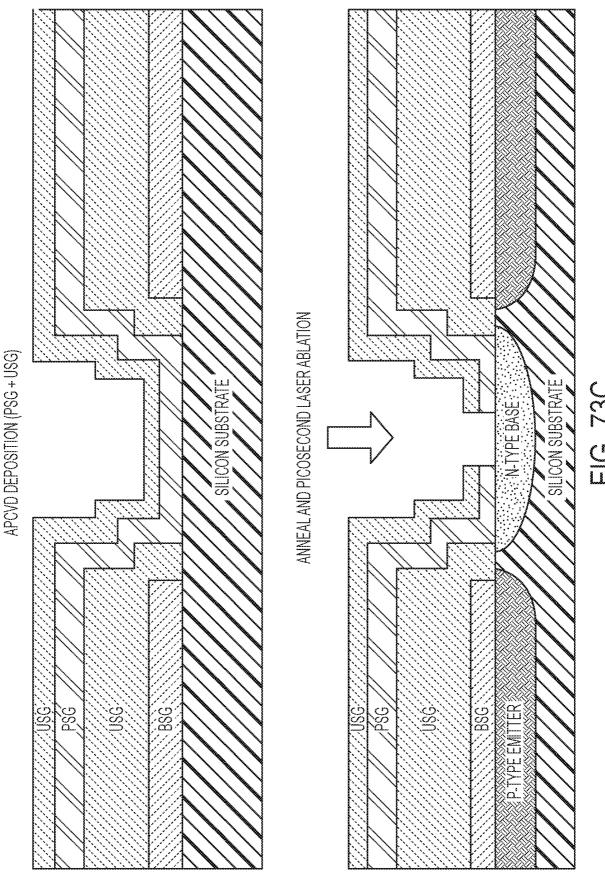

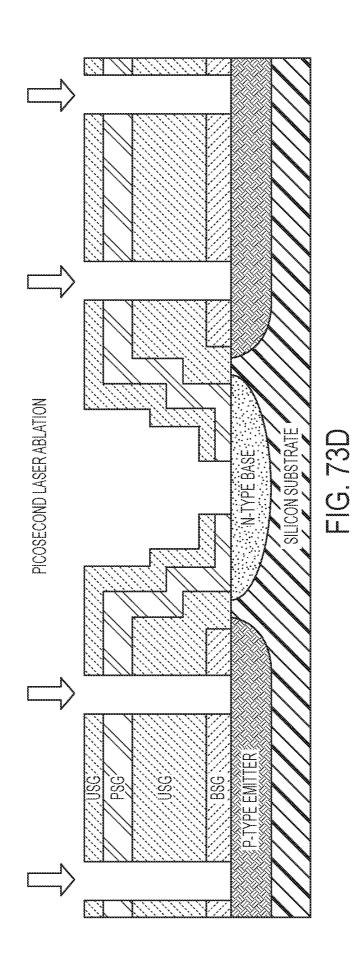

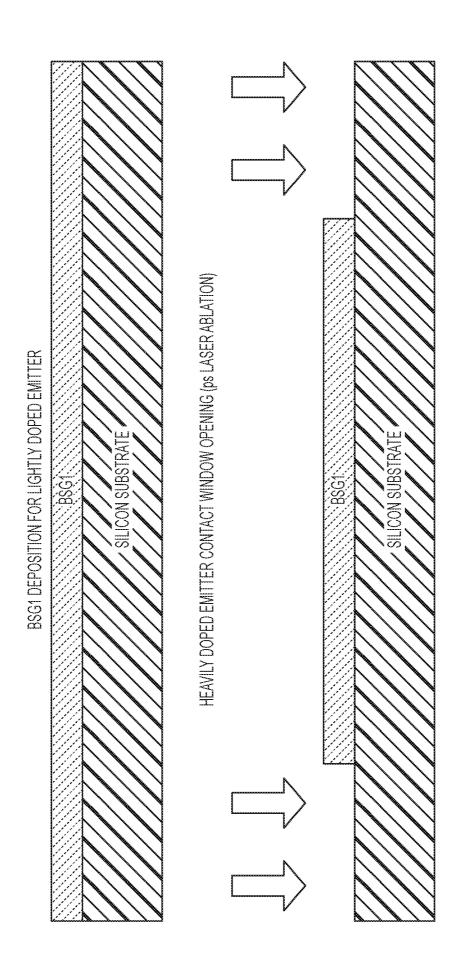

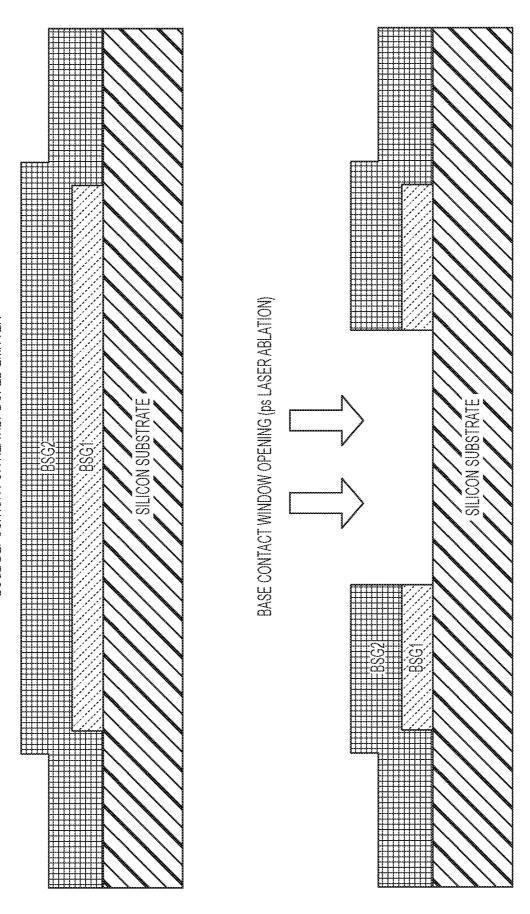

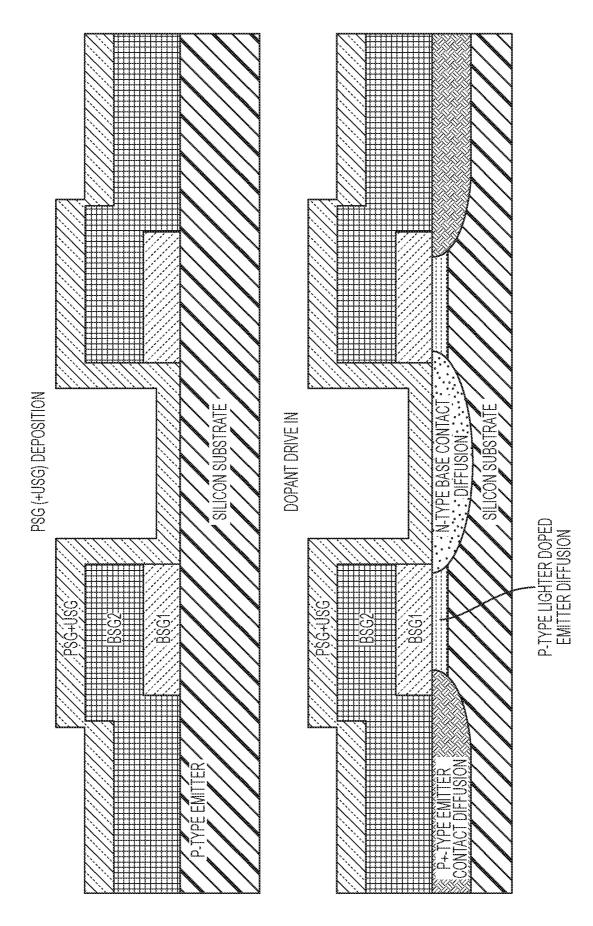

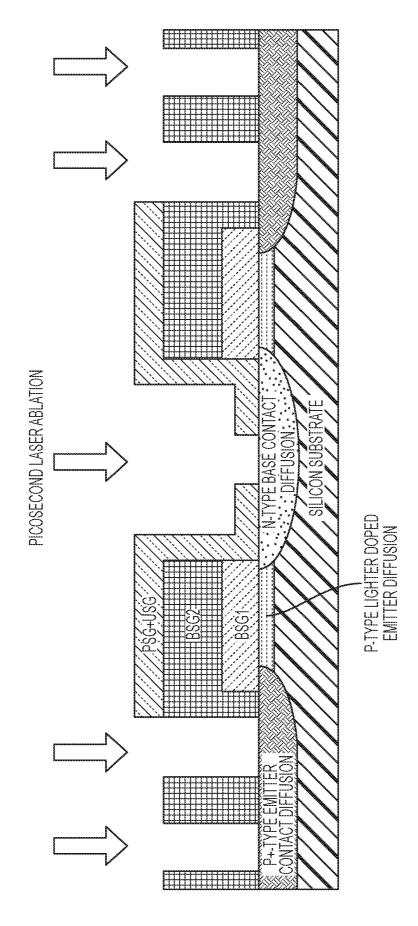

1. The ex-situ boron doped p+ emitter is formed after the in-situ phosphorous based n-type epitaxial substrate is grown using epitaxy. The patterned ex-situ emitter is formed preferably using the combination of APCVD BSG (glass doped heavily with boron), laser ablation of BSG, followed by drive-in of the emitter.

- 2. The ex-situ emitter eliminates the risk of epitaxial auto-doping during high-volume manufacturing of solar cells, which is present in the case of in-situ emitter.

- 3. The ex-situ emitter eliminates the need for pulsed picoseconds laser ablation of silicon to isolate base with the emitter (or to form the patterned emitter and base regions).

General Structural and Manufacturing Method attributes shared by the process flows. Specific examples of a class of final back junction/back contacted solar cell structure and methods for manufacturing are detailed below. Note, that the structures and methods are not limited to these specific examples. A wider range of examples may be derived using the aforementioned general carrier methods by those skilled in the related art. For those specific structure and methods detailed herein, identified common attributes include:

- 1. Common <u>Structural</u> attributes in the disclosed process embodiments:

- a. About 25μm (microns) to 50 μm epi thickness. More generally, this range can be 5 μm to conventional thicknesses of around 200 μm.

- b. Phosphorous based n-type base doping. In general, this can be other n-type dopant material (for instance, arsenic or antimony or indium) as well as a p-type base such as, but not limited to that formed by boron or gallium doping.

- 2. Common *Manufacturing Method* attributes in the disclosed process embodiments:

- a. The processes on carrier 1 (either template of thick wafer/ingot) include:

- APCVD-based processes are preferably used in conjunction with furnace anneal to form the ex-situ emitter. APCVD, in general, has both boron silicate glass (BSG) and phosphorous silicate glass (PSG). However, other substitutes for APCVD PSG are also possible and discussed.

- ii. As mentioned above, in another embodiment relevant to the template/porous silicon (PS) first carrier, the ex-situ APCVD emitter may be replaced by epitaxial-based in-situ emitter followed by laser based silicon ablation to isolate the base from the emitter area.

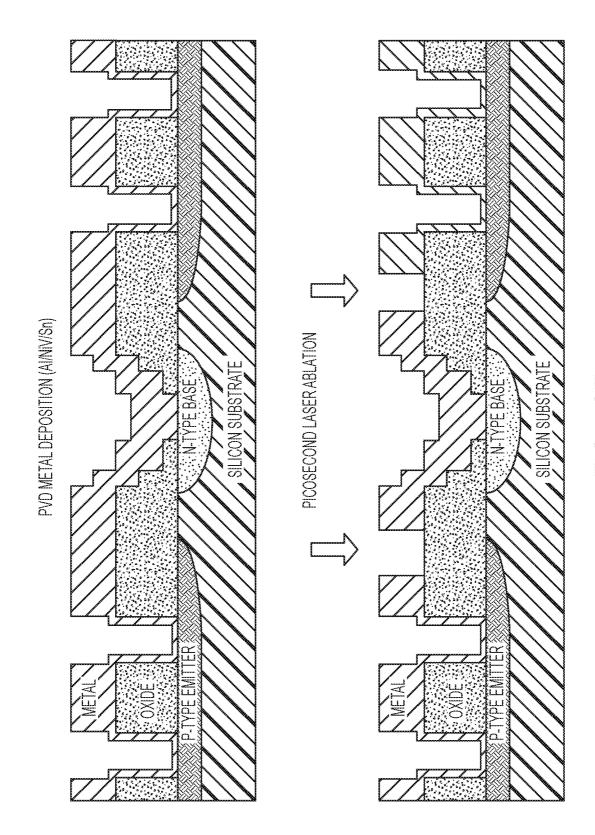

iii. Pulsed pico-second based laser ablation pattern for emitter-base isolation, emitter and base contacts, and busbarless Al fingers on the cells. In a generic case, the pattern may be defined by other lasers such as nanosecond (ns) laser. In addition, the Al (or aluminum alloy such as Al-Si) fingers on the cell may be of ar bitrary design conducive for better cell performance. This includes, but is not limited to, several mini-cells (on a single substrate) with their own busbars connected at a level above the on-cell metallization levels, such as at the backplane.

- iv. An anneal step with optional oxidation, which takes care of both driving and activation of the BSG dopant (and PSG, if present), as well as creating the thermal oxide based back surface passivation. In a preferred embodiment this is done in the same step, however, if need be, in general may be broken down into separate steps. In addition, this may be done either in a tube based or an in-line thermal processing furnace.

- v. A metal 1 deposition step, which may be a vacuum based deposition such as physical vapor deposition (PVD) such as plasma sputtering or evaporation or ion beam deposition, which is then followed by a laser ablation, such as a pulsed picosecond laser ablation step, for patterning said metal 1 layer. Alternatively, the metal 1 (M1) deposition step may entail the direct-write printing, using for instance ink jet, screen printing, stencil printing, or aerosol jet printing to deposit directly a patterned metal ink or paste on the processed TFSS backside.

- vi. If the carrier 1 is a template/Porous Silicon (PS), a preferred process method embodiment is to not use wet processing on it after (between epitaxial growth till completion of the lift-off separation of TFSS attached to carrier 2) because of the risk of TFSS lifting or bubbling prematurely. However, this should not be interpreted in the limiting sense. The disclosed subject matter includes the general case where it is possible to do wet processing or semi-wet processing, for instance, through the use of etching vapors such as HF vapors to remove dielectric films such as the silicate glasses.

vii. On carrier-1 lamination of backplane and the release of the TFSS from carrier-1 while attached to carrier-2.

- b. The processes on carrier 2 (Backplane)

- i. Post-release wet etch for removing quasi mono-crystalline silicon (QMS) layer arising from the processed porous silicon layer. This also includes using wet processing to texture the front surface. In a preferred embodiment, these wet steps are performed in a single step using KOH-based (or NAOH-based) etch chemistry. However, if needed, in general they can be broken down in two separate steps with both steps using KOH based chemistry or the QMS removal step using TMAH-based or a separate KOH-based (or NAOH-based) chemistry. There is also the possibility of just doing QMS removal without texture with either KOH or TMAH (KOH may be advantageous for lower cost reasons). And instead of wet texture either use dry texture based on laser or plasma processing, or no texture and use other means to effectively couple-in broad-band sunlight these "other" means may rely on dispersed nanoparticles such as dielectric particles, or silver or gold particles.

- ii. If texturing is involved, a post texture surface cleaning process is a critical step for back junction/back contacted cell. This cleaning step enables formation of a high quality front-surface passivation layer following the cleaning process. A specific cleaning chemistry for this purpose may be based on HF/HCl chemistry and/or ozonated HF chemistry, although more expensive alternates such as the so-called RCA clean can also be used. Performing a diluted HF dip post texture clean and just before passivation is also critical to get lower front surface recombination velocities (hence, higher quality passivation). For the case of an organic backplane material such as prepreg or prepreg with an underlying additional adhesive layer and with a marginal integrity of the backplane during the texture and post texture clean processes, an additional process step prior to the deposition of the passivation layer or layers such as a-Si or a-SiOx (amorphous silicon oxide) plus Silicon nitride is disclosed which is to use a reduced pressure or atmospheric pressure plasma or a stream of radicals (such as hydrogen radicals and/or ions) to

remove both organic residue redeposited from the backplane material as well as native oxide. Such processes may be preferably integrated in the initial stage of the passivation tool (such as the PECVD passivation) or alternatively be performed off-line.

- c. Low temperature front surface passivation and ARC layer that meets the required device specifications. In general, this includes a passivation layer which is deposited at a temperature which can accommodate processing with the chosen backplane is adequate. The allowable maximum temperature of passivation is dependent on the ability of backplane to withstand this without cracking TFSS, without degradation of the backplane material, and/or compromising the solar cell fill factor and other reliability related parameters. A good passivation is expected at temperatures in the range at or above about 150°C for PECVD SiN. One example is to use PECVD of thin amorphous silicon (deposited using PECVD at a substrate temperature in the range of about 150°C to 200°C) followed by a low temperature SiN deposition (preferably at the same temperature as amorphous silicon or amorphous silicon oxide). More generally, a good passivation must have a very low interface trap density with silicon and the polarity of charge which repels the minority carriers away from the front surface. For the n-type material, this embedded charge needs to be a stable positive charge. A subsequent thermal anneal either in a forming gas, a neutral, or vacuum or other suitable ambient at a suitable time after the passivation may be beneficial for improving the passivation quality. Such thermal anneal may be performed at a temperature equal to or higher than the PECVD passivation temperature (up to about 300°C depending on the thermal stability and CTE-match of the backplane material).

- d. Access to backplane metal and its busbars. The specifics of this depends on the type of the backplane. If the backplane is the kind (discussed above) which has integrated or embedded metal foil metallization then the choices are either a pre-made through hole (which would be covered during wet processing) or a wrap around bus bar opening (which would be covered during wet processing). For the backplanes where the backplane metallization is a final processing step, access is not an issue.

**Fig. 3** is a diagram showing for ex-situ emitter process flow embodiments in accordance with the disclosed subject matter. The process flows are divided into four categories Flow 1 through 4 which are distinguished by the differences in the way the base contact is made. All the flows shown in **Fig. 3** may be used with either the template/porous silicon carrier 1 or with the bulk wafer Ingot/implant Carrier 1, and with any backplane option outlined in this diclosure.

Flow Option 1: This process flow uses APCVD PSG to make the base doping. PSG layer is deposited and phosphorus is driven in either using a batch furnace anneal or using pulsed nanosecond laser hot ablation of the PSG layer (in the latter case, to dope the underlying TFSS and to ablate the PSG layer for base contact opening).

<u>Flow Option 2:</u> This process uses screen printed (or stencil printed) silicon nanoparticle phosphorous or silicon nanoparticle phosphorous ink applied by inkjet (or aerosol jet) printing. This will be followed by a thermal anneal.

<u>Flow Option 3:</u> This option uses screen printing of the phosphorous paste or phosphorous ink applied by inkjet printing. This is followed by thermal anneal in a batch furnace equipment to drive in the dopant.

<u>Flow Option 4:</u> This process uses Phosphorous Oxychloride POC13 as the starting phosphorous dopant material (process is preferably performed in a POC13 tube furnace). It requires post diffusion phosphorus glass wet etch or HF vapor etch.

Sub-categories of the four flow option categories of Fig. 3 are detailed below.

Flow Option 1: APCVD PSG based base doping. There are two sub-categories in this class: a) Hot ablation using pulsed ns laser processing to drive base and emitter contact using laser (and to concurrently open the base and emitter contact holes), b) Cold ablation (preferably using pulsed ps laser processing) where furnace anneal makes the base contact diffusion regions. Fig. 4 is a process flow using hot laser ablation (preferably using pulsed ns laser processing) with selective emitters for manufacturing thin back junction/back contacted solar cells with two carriers (corresponding to flow option 1A1 in Fig. 3). The process starts with cleaning of a mother template crystalline silicon wafer. In one example this could be a 200mm diameter, 200 μm to 1.2 mm thick semiconductor standard wafer. In another example, this can be a 165mm side full

square, 200 µm to 1.2 mm thick crystalline silicon wafer. The template is cleaned using, for example, chemistries such as KOH, and acids such as HF, HCl or combinations thereof (HF/HCl), and/or a chemistry comprising ozonated HF. The cleaning can also be performed using any other chemical cleans known for cleaning metallic and organic impurities. Another example is RCA clean; however, RCA clean is more expensive for solar cell manufacturing purposes. The cleaning is followed by bilayer or multi-layer (at least two different porosities) porous silicon formation using electrochemical etching (preferably in HF/IPA). The first layer (or the top layer) formed is a low porosity layer (for example, this can be a layer with a porosity in the range of, but not limited to, 15-40%). This is followed by the second layer (buried layer) with a higher porosity (for example, this can be a layer with a porosity in the range of, but not limited to, 45-70% porosity) which is formed underneath so that it is closer to the template and separates the lower porosity layer from the template. Other configurations such as monolayer or trilayer or graded-porosity porous silicon are also possible, in general, as long as the layers facilitate several key requirements including: an excellent top epitaxial seed layer to enable formation of a good quality epitaxial silicon layer on top of the low porosity porous silicon layer, a reliable and high release yield due to on-demand breaking of the high porosity layer for TFSS lift-off separation from the template, and no premature release or bubbling of the TFSS from the template carrier during the on-template processing steps (preferably but not limited to the all-dry on-template processing steps after formation of TFSS till lift-off separation). The porous silicon formation process is followed by a drying step and then hydrogen pre-bake and epitaxial silicon growth, preferably in the thickness range of about 5 µm to about 50 µm. Both the hydrogen prebake and epitaxial growth process are preferably performed in the same An integral part of the growth process is the selection of the pre-bake condition. During the hydrogen pre-bake process step (preferably in-situ prebake in the epitaxial growth reactor), not only the pre-bake removes the native oxide and other potential surface contaminants, is also causes a reflow and solid phase diffusion of silicon such that the surface pores of the porous silicon seal at the surface of the low porosity layer (due to the driving force caused by reduction of the surface energy of low-porosity porous silicon), hence, producing an excellent epitaxial seed layer for subsequent epitaxial growth of a high quality TFSS layer. This, in turn, facilitates better epitaxial growth and formation of high-quality in-situ-doped TFSS layer with high minority carrier lifetimes. The epitaxial growth process is then followed by BSG deposition, preferably using an