(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5637384号

(P5637384)

(45) 発行日 平成26年12月10日(2014.12.10)

(24) 登録日 平成26年10月31日(2014.10.31)

(51) Int.Cl.

F 1

H04N 5/374 (2011.01)

H04N 5/335 74 O

H01L 27/146 (2006.01)

H01L 27/14 A

H04N 5/357 (2011.01)

H04N 5/335 57 O

請求項の数 10 (全 22 頁)

(21) 出願番号

特願2010-279508 (P2010-279508)

(22) 出願日

平成22年12月15日 (2010.12.15)

(65) 公開番号

特開2012-129798 (P2012-129798A)

(43) 公開日

平成24年7月5日 (2012.7.5)

審査請求日

平成25年11月20日 (2013.11.20)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 大池 祐輔

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 町田 貴志

東京都港区港南1丁目7番1号 ソニー株

式会社内

審査官 木方 庸輔

最終頁に続く

(54) 【発明の名称】 固体撮像素子および駆動方法、並びに電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部と、前記光電変換部により生成された電荷を所定の領域に転送する転送手段と、前記所定の領域に転送された電荷を読み出す読み出し手段と、前記所定の領域の電荷を排出する排出手段とを少なくとも備える複数の単位画素と、

前記単位画素における配線層より下層に形成され、前記光電変換部の受光部を除く前記複数の単位画素の略全ての表面を遮光する遮光膜と、

前記遮光膜に印加する電圧を制御する電圧制御手段と

を備え、

前記電圧制御手段は、前記排出手段による電荷排出から前記転送手段による電荷転送までの期間、前記遮光膜に印加する電圧を第1の電圧とし、電荷転送後、前記読み出し手段による電荷読み出しまでの期間、前記遮光膜に印加する電圧を前記第1の電圧より低い第2の電圧とし、前記読み出し手段による電荷読み出し時に、前記遮光膜に印加する電圧を前記第1の電圧とする

固体撮像素子。

## 【請求項 2】

前記複数の単位画素が配列される画素アレイ部において、前記排出手段による電荷排出、前記転送手段による電荷転送、および、電荷排出から電荷読み出しまでの期間における前記電圧制御手段による前記遮光膜の電圧制御は、複数行一括で行われる

請求項1に記載の固体撮像素子。

10

20

**【請求項 3】**

前記第2の電圧は、負電圧である

請求項1に記載の固体撮像素子。

**【請求項 4】**

前記複数の単位画素が配列される画素アレイ部において、前記遮光膜は、1行または複数行単位で分離されて形成される

請求項1に記載の固体撮像素子。

**【請求項 5】**

前記遮光膜は、前記受光部の開口部を、1行または複数行単位の境界の一部として分離されて形成される

請求項4に記載の固体撮像素子。

**【請求項 6】**

前記読み出し手段による電荷読み出しが行われる画素を選択する選択手段をさらに備え

、

1行または複数行単位で分離されて形成される前記遮光膜に電圧を印加する駆動回路は

、前記選択手段の駆動回路と共有される

請求項4に記載の固体撮像素子。

**【請求項 7】**

前記所定の領域は、フローティングディフュージョンであり、

前記転送手段は、前記光電変換部から前記フローティングディフュージョンに電荷を転送する

請求項1に記載の固体撮像素子。

**【請求項 8】**

前記所定の領域は、フローティングディフュージョンであり、

前記転送手段は、前記フローティングディフュージョンとは別に設けられた電荷保持部から、前記フローティングディフュージョンに電荷を転送する

請求項1に記載の固体撮像素子。

**【請求項 9】**

光電変換部と、前記光電変換部により生成された電荷を所定の領域に転送する転送手段と、前記所定の領域に転送された電荷を読み出す読み出し手段と、前記所定の領域の電荷を排出する排出手段とを少なくとも備える複数の単位画素と、

前記単位画素における配線層より下層に形成され、前記光電変換部の受光部を除く前記複数の単位画素の略全ての表面を遮光する遮光膜と、

前記遮光膜に印加する電圧を制御する電圧制御手段と

を備える固体撮像素子の駆動方法であって、

前記排出手段による電荷排出から前記転送手段による電荷転送までの期間、前記遮光膜に印加する電圧を第1の電圧とし、電荷転送後、前記読み出し手段による電荷読み出しまでの期間、前記遮光膜に印加する電圧を前記第1の電圧より低い第2の電圧とし、前記読み出し手段による電荷読み出し時に、前記遮光膜に印加する電圧を前記第1の電圧とするステップ

を含む駆動方法。

**【請求項 10】**

光電変換部と、前記光電変換部により生成された電荷を所定の領域に転送する転送手段と、前記所定の領域に転送された電荷を読み出す読み出し手段と、前記所定の領域の電荷を排出する排出手段とを少なくとも備える複数の単位画素と、

前記単位画素における配線層より下層に形成され、前記光電変換部の受光部を除く前記複数の単位画素の略全ての表面を遮光する遮光膜と、

前記遮光膜に印加する電圧を制御する電圧制御手段と

を備え、

前記電圧制御手段が、前記排出手段による電荷排出から前記転送手段による電荷転送ま

10

20

30

40

50

での期間、前記遮光膜に印加する電圧を第1の電圧とし、電荷転送後、前記読み出し手段による電荷読み出しまでの期間、前記遮光膜に印加する電圧を前記第1の電圧より低い第2の電圧とし、前記読み出し手段による電荷読み出し時に、前記遮光膜に印加する電圧を前記第1の電圧とする固体撮像素子

を備える電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固体撮像素子および駆動方法、並びに電子機器に関し、特に、撮像画像の高画質化を図ることができるようとする固体撮像素子および駆動方法、並びに電子機器に関する。 10

【背景技術】

【0002】

受光部で蓄積された電荷をMOSトランジスタを介して読み出すイメージセンサにおいては、蓄積電荷を全て読み出すために、受光部が完全空乏状態となるように電荷電圧変換部（いわゆるフローティングディフュージョン。以下、FDともいう）へ電荷を転送することが望ましい。

【0003】

しかしながら、例えば省電力化を目的として電源電圧を低下させた場合、その低下分に応じて、FDをリセットしたときのFDの電圧（リセット電圧）が低下するため、受光部を完全空乏状態とし、蓄積電荷を完全転送することが難しくなる。FDのリセット電圧が低下しても蓄積電荷を完全転送するには、受光部のポテンシャルを浅く設計する必要があるが、これにより飽和電荷量が低減してしまう。 20

【0004】

そこで、FDを所定電圧にリセットした後、受光部の蓄積電荷を転送する際に、画素の電源線または垂直信号線により高い電圧を印加することで、画素の電源線または垂直信号線とFDとの寄生容量のカップリングによって、フローティング状態のFDの電圧を高くして、受光部の蓄積電荷を容易に完全転送するようにしたものがある（例えば、特許文献1，2参照）。

【0005】

また、FDを所定電圧にリセットした後に、選択トランジスタに入力される選択信号をアクティブにする（Highレベルにする）ことで、選択信号を入力する選択信号線とFDとの寄生容量のカップリングによって、フローティング状態のFDの電圧を高くして、受光部の蓄積電荷を容易に完全転送するようにしたものがある（例えば、特許文献3，4参照）。 30

【0006】

このように、画素の電源線、垂直信号線、または選択信号線等の既存信号線により高い電圧を印加することで、FDの電圧を高くして、受光部の蓄積電荷を容易に完全転送することがなされている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2005-86225号公報

【特許文献2】特開2005-192191号公報

【特許文献3】特開2009-26892号公報

【特許文献4】特開2009-130679号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところで、受光部で蓄積された電荷を画素内で一時的に保持する動作を行うイメージセンサにおいては、電荷を保持する領域（以下、電荷保持領域という）に光が入射すること 50

で、保持されている電荷に対応する信号に残像のような信号が加わってしまうことを避けるために、その電荷保持領域を、配線層に対してできるだけ下層で遮光する必要がある。具体的には、例えば、最下層のメタル配線の下に、タンゲステン（元素記号：W）からなる遮光膜が、電荷保持領域の全部または一部を覆うように形成される。

#### 【0009】

上述したようなイメージセンサにおいては、この電荷保持領域を、受光部とFDとの間に設けたり、FDそのものを電荷保持領域として用いるようにすることがなされているが、遮光膜が配線層より下層に形成されることで、既存信号線と電荷保持領域との寄生容量は、電荷保持領域の総容量に対して小さくなってしまう。これにより、電荷保持領域における十分な変調効果が得られず、受光部の蓄積電荷を完全転送することができなくなってしまい、ひいては、撮像画像の画質が低下する恐れがあった。10

#### 【0010】

本発明は、このような状況に鑑みてなされたものであり、撮像画像の高画質化を図ることができるようにするものである。

#### 【課題を解決するための手段】

#### 【0021】

本発明の一側面の固体撮像素子は、光電変換部と、前記光電変換部により生成された電荷を所定の領域に転送する転送手段と、前記所定の領域に転送された電荷を読み出す読み出し手段と、前記所定の領域の電荷を排出する排出手段とを少なくとも備える複数の単位画素と、前記単位画素における配線層より下層に形成され、前記光電変換部の受光部を除く前記複数の単位画素の略全ての表面を遮光する遮光膜と、前記遮光膜に印加する電圧を制御する電圧制御手段とを備え、前記電圧制御手段は、前記排出手段による電荷排出から前記転送手段による電荷転送までの期間、前記遮光膜に印加する電圧を第1の電圧とし、電荷転送後、前記読み出し手段による電荷読み出しまでの期間、前記遮光膜に印加する電圧を前記第1の電圧より低い第2の電圧とし、前記読み出し手段による電荷読み出しひに、前記遮光膜に印加する電圧を前記第1の電圧とする。20

#### 【0022】

前記複数の単位画素が配列される画素アレイ部において、前記排出手段による電荷排出、前記転送手段による電荷転送、および、電荷排出から電荷読み出しまでの期間における前記電圧制御手段による前記遮光膜の電圧制御は、複数行一括で行われるようにすることができる。30

#### 【0023】

前記第2の電圧は、負電圧とすることができます。

#### 【0024】

前記複数の単位画素が配列される画素アレイ部において、前記遮光膜は、1行または複数行単位で分離されて形成されるようにすることができます。

#### 【0025】

前記遮光膜は、前記受光部の開口部を、1行または複数行単位の境界の一部として分離されて形成されるようにすることができます。

#### 【0026】

前記読み出し手段による電荷読み出しが行われる画素を選択する選択手段をさらに備え、1行または複数行単位で分離されて形成される前記遮光膜に電圧を印加する駆動回路は、前記選択手段の駆動回路と共有されるようにすることができます。40

#### 【0027】

前記所定の領域は、フローティングディフュージョンとし、前記転送手段には、前記光電変換部から前記フローティングディフュージョンに電荷を転送させることができる。

#### 【0028】

前記所定の領域は、フローティングディフュージョンとし、前記転送手段には、前記フローティングディフュージョンとは別に設けられた電荷保持部から、前記フローティングディフュージョンに電荷を転送させることができます。50

**【0029】**

本発明の一側面の駆動方法は、光電変換部と、前記光電変換部により生成された電荷を所定の領域に転送する転送手段と、前記所定の領域に転送された電荷を読み出す読み出し手段と、前記所定の領域の電荷を排出する排出手段とを少なくとも備える複数の単位画素と、前記単位画素における配線層より下層に形成され、前記光電変換部の受光部を除く前記複数の単位画素の略全ての表面を遮光する遮光膜と、前記遮光膜に印加する電圧を制御する電圧制御手段とを備える固体撮像素子の駆動方法であって、前記排出手段による電荷排出から前記転送手段による電荷転送までの期間、前記遮光膜に印加する電圧を第1の電圧とし、電荷転送後、前記読み出し手段による電荷読み出しまでの期間、前記遮光膜に印加する電圧を前記第1の電圧より低い第2の電圧とし、前記読み出し手段による電荷読み出しへに、前記遮光膜に印加する電圧を前記第1の電圧とするステップを含む。10

**【0030】**

本発明の一側面の電子機器は、光電変換部と、前記光電変換部により生成された電荷を所定の領域に転送する転送手段と、前記所定の領域に転送された電荷を読み出す読み出し手段と、前記所定の領域の電荷を排出する排出手段とを少なくとも備える複数の単位画素と、前記単位画素における配線層より下層に形成され、前記光電変換部の受光部を除く前記複数の単位画素の略全ての表面を遮光する遮光膜と、前記遮光膜に印加する電圧を制御する電圧制御手段とを備え、前記電圧制御手段が、前記排出手段による電荷排出から前記転送手段による電荷転送までの期間、前記遮光膜に印加する電圧を第1の電圧とし、電荷転送後、前記読み出し手段による電荷読み出しまでの期間、前記遮光膜に印加する電圧を前記第1の電圧より低い第2の電圧とし、前記読み出し手段による電荷読み出しへに、前記遮光膜に印加する電圧を前記第1の電圧とする固体撮像素子を備える。20

**【0032】**

本発明の一側面においては、排出手段による電荷排出から転送手段による電荷転送までの期間、遮光膜に印加する電圧が第1の電圧とされ、電荷転送後、読み出し手段による電荷読み出しまでの期間、遮光膜に印加する電圧が第1の電圧より低い第2の電圧とされ、読み出し手段による電荷読み出しへに、遮光膜に印加する電圧が第1の電圧とされる。

**【発明の効果】****【0033】**

本発明の一側面によれば、撮像画像の高画質化を図ることが可能となる。30

**【図面の簡単な説明】****【0034】**

【図1】本発明を適用した固体撮像素子の一実施の形態の構成例を示す図である。

【図2】単位画素の構成例を示す図である。

【図3】単位画素の回路構成例を示す図である。

【図4】単位画素の第1の動作例を説明する図である。

【図5】単位画素の第1の動作例を説明する図である。

【図6】単位画素の第2の動作例を説明する図である。

【図7】単位画素の第2の動作例を説明する図である。

【図8】単位画素のその他の第1の構成例を示す図である。40

【図9】単位画素のその他の第2の構成例を示す図である。

【図10】単位画素のその他の第3の構成例を示す図である。

【図11】単位画素のその他の第4の構成例を示す図である。

【図12】単位画素の構成例を示す平面図である。

【図13】単位画素の構成例を示す平面図である。

【図14】本発明を適用した電子機器の一実施の形態の構成例を示す図である。

**【発明を実施するための形態】****【0035】**

以下、本発明の実施の形態について図を参照して説明する。

**【0036】**

**[ 固体撮像素子の構成 ]**

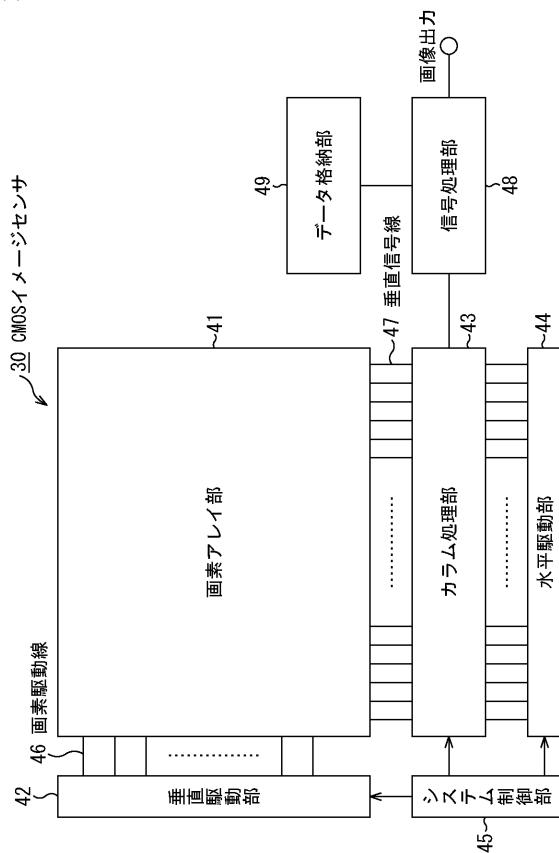

図1は、本発明が適用される固体撮像素子としてのCMOS(Complementary Metal Oxide Semiconductor)イメージセンサの構成例を示すブロック図である。

**【 0 0 3 7 】**

CMOSイメージセンサ30は、画素アレイ部41、垂直駆動部42、カラム処理部43、水平駆動部44、およびシステム制御部45を含んで構成される。画素アレイ部41、垂直駆動部42、カラム処理部43、水平駆動部44、およびシステム制御部45は、図示せぬ半導体基板(チップ)上に形成されている。

**【 0 0 3 8 】**

画素アレイ部41には、入射光量に応じた電荷量の光電荷を発生して内部に蓄積する光電変換素子を有する単位画素(図2,3の単位画素50)が行列状に2次元配置されている。なお、以下では、入射光量に応じた電荷量の光電荷を、単に「電荷」と記述し、単位画素を、単に「画素」と記述する場合もある。

10

**【 0 0 3 9 】**

画素アレイ部41にはさらに、行列状の画素配列に対して行ごとに画素駆動線46が図の左右方向(画素行の画素の配列方向)に沿って形成され、列ごとに垂直信号線47が図の上下方向(画素列の画素の配列方向)に沿って形成されている。画素駆動線46の一端は、垂直駆動部42の各行に対応した出力端に接続されている。

**【 0 0 4 0 】**

CMOSイメージセンサ30はさらに、信号処理部48およびデータ格納部49を備えている。信号処理部48およびデータ格納部49については、CMOSイメージセンサ30とは別の基板に設けられる外部信号処理部、例えばDSP(Digital Signal Processor)やソフトウェアによる処理でも構わないし、CMOSイメージセンサ30と同じ基板上に搭載しても構わない。

20

**【 0 0 4 1 】**

垂直駆動部42は、シフトレジスタやアドレスデコーダなどによって構成され、画素アレイ部41の各画素を、全画素同時あるいは行単位等で駆動する画素駆動部である。この垂直駆動部42は、その具体的な構成については図示を省略するが、読み出し走査系と、書き出し走査系あるいは、一括書き出し、一括転送を有する構成となっている。

**【 0 0 4 2 】**

30

読み出し走査系は、単位画素から信号を読み出すために、画素アレイ部41の単位画素を行単位で順に選択走査する。行駆動(ローリングシャッタ動作)の場合、書き出しについては、読み出し走査系によって読み出し走査が行われる読み出し行に対して、その読み出し走査よりもシャッタスピードの時間分だけ先行して書き出し走査が行なわれる。また、グローバル露光(グローバルシャッタ動作)の場合は、一括転送よりもシャッタスピードの時間分先行して一括書き出しが行なわれる。

**【 0 0 4 3 】**

この書き出しにより、読み出し行の単位画素の光電変換素子から不要な電荷が書き出される(リセットされる)。そして、不要電荷の書き出し(リセット)により、いわゆる電子シャッタ動作が行われる。ここで、電子シャッタ動作とは、光電変換素子の光電荷を捨てて、新たに露光を開始する(光電荷の蓄積を開始する)動作のことを言う。

40

**【 0 0 4 4 】**

読み出し走査系による読み出し動作によって読み出される信号は、その直前の読み出し動作または電子シャッタ動作以降に入射した光量に対応するものである。行駆動の場合は、直前の読み出し動作による読み出しタイミングまたは電子シャッタ動作による掃出しタイミングから、今回の読み出し動作による読み出しタイミングまでの期間が、単位画素における光電荷の蓄積時間(露光時間)となる。グローバル露光の場合は、一括書き出しから一括転送までの時間が蓄積時間(露光時間)となる。

**【 0 0 4 5 】**

垂直駆動部42によって選択走査された画素行の各単位画素から出力される画素信号は

50

、垂直信号線 4 7 の各々を通してカラム処理部 4 3 に供給される。カラム処理部 4 3 は、画素アレイ部 4 1 の画素列ごとに、選択行の各単位画素から垂直信号線 4 7 を通して出力される画素信号に対して所定の信号処理を行うとともに、信号処理後の画素信号を一時的に保持する。

#### 【 0 0 4 6 】

具体的には、カラム処理部 4 3 は、信号処理として少なくとも、ノイズ除去処理、例えばCDS(Correlated Double Sampling; 相関二重サンプリング)処理を行う。このカラム処理部 4 3 による相関二重サンプリングにより、リセットノイズや増幅トランジスタの閾値ばらつき等の画素固有の固定パターンノイズが除去される。なお、カラム処理部 4 3 にノイズ除去処理以外に、例えば、AD(アナログ - デジタル)変換機能を持たせ、信号レベルをデジタル信号で出力することも可能である。10

#### 【 0 0 4 7 】

水平駆動部 4 4 は、シフトレジスタやアドレスデコーダなどによって構成され、カラム処理部 4 3 の画素列に対応する単位回路を順番に選択する。この水平駆動部 4 4 による選択走査により、カラム処理部 4 3 で信号処理された画素信号が順番に信号処理部 4 8 に出力される。

#### 【 0 0 4 8 】

システム制御部 4 5 は、各種のタイミング信号を生成するタイミングジェネレータ等によって構成され、タイミングジェネレータで生成された各種のタイミング信号を基に垂直駆動部 4 2 、カラム処理部 4 3 、および水平駆動部 4 4 などの駆動制御を行う。20

#### 【 0 0 4 9 】

信号処理部 4 8 は、少なくとも加算処理機能を有し、カラム処理部 4 3 から出力される画素信号に対して加算処理等の種々の信号処理を行う。データ格納部 4 9 は、信号処理部 4 8 での信号処理に当たって、その処理に必要なデータを一時的に格納する。

#### 【 0 0 5 0 】

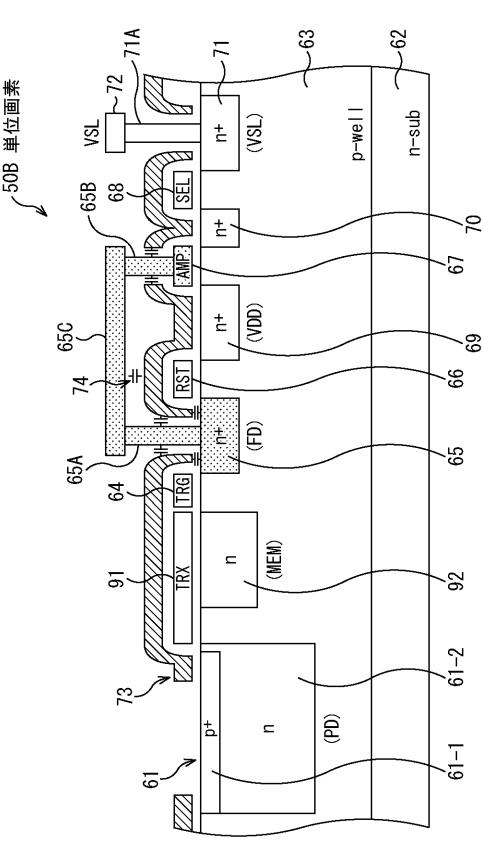

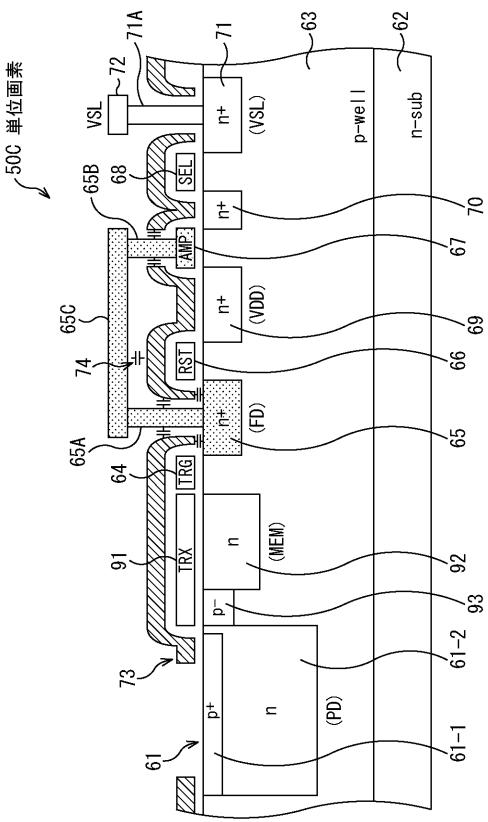

##### [ 単位画素の構造 ]

次に、図 1 の画素アレイ部 4 1 に行列状に配置されている単位画素 5 0 の具体的な構造について説明する。

#### 【 0 0 5 1 】

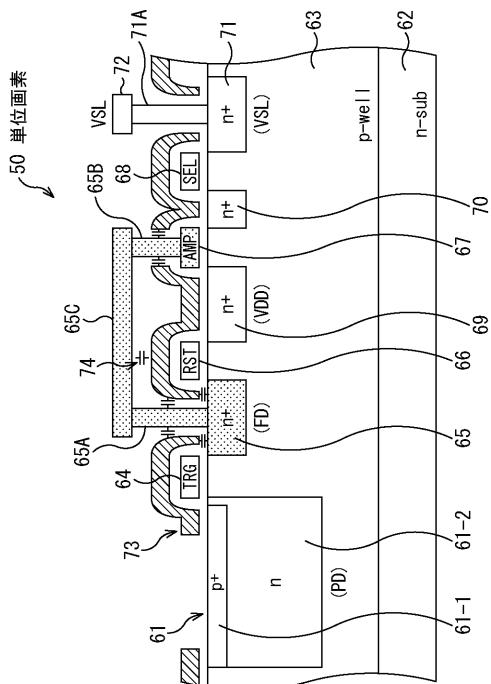

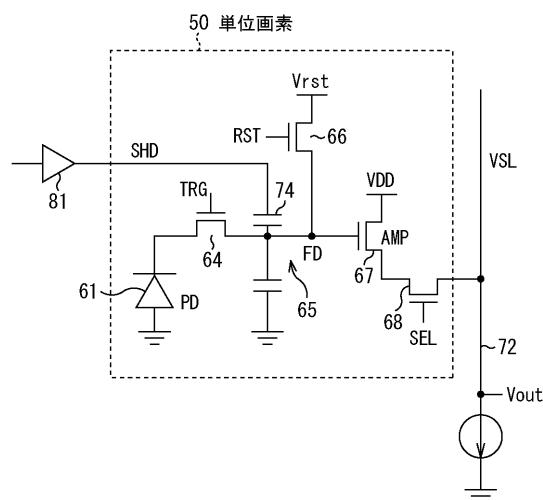

図 2 は、単位画素 5 0 の断面の構成例を示しており、図 3 は、単位画素 5 0 の回路構成例を示している。30

#### 【 0 0 5 2 】

単位画素 5 0 は、光電変換素子として、例えばフォトダイオード(PD) 6 1 を有している。フォトダイオード 6 1 は、例えば、n 型基板 6 2 上に形成された p 型ウェル層 6 3 に対して、p 型層 6 1 - 1 を基板表面側に形成して n 型埋め込み層 6 1 - 2 を埋め込むことによって形成される埋め込み型フォトダイオードである。なお、p 型層 6 1 - 1 および n 型埋め込み層 6 1 - 2 は、電荷排出時に空乏状態となる不純物濃度とされる。

#### 【 0 0 5 3 】

単位画素 5 0 は、フォトダイオード 6 1 に加えて、転送ゲート 6 4 および浮遊拡散領域(FD: Floating Diffusion) 6 5 を有する。40

#### 【 0 0 5 4 】

転送ゲート 6 4 は、フォトダイオード 6 1 で光電変換され、フォトダイオード 6 1 の内部に蓄積された電荷を、転送ゲート 6 4 のゲート電極に駆動信号TRGが印加されることによって、浮遊拡散領域 6 5 に転送する。

#### 【 0 0 5 5 】

浮遊拡散領域 6 5 は、n 型層からなる電荷電圧変換部であり、転送ゲート 6 4 によってフォトダイオード 6 1 から転送された電荷を電圧に変換する。浮遊拡散領域 6 5 の上部には、配線用のコンタクト 6 5 A (図 2) が接続されている。また、コンタクト 6 5 A は、配線 6 5 C に接続されている。

#### 【 0 0 5 6 】

10

20

30

40

50

単位画素 50 はさらに、リセットトランジスタ 66、増幅トランジスタ 67、および選択トランジスタ 68 を有している。なお、図 2 では、リセットトランジスタ 66、増幅トランジスタ 67、および選択トランジスタ 68 に、n チャネルの MOSトランジスタを用いた例を示している。しかし、リセットトランジスタ 66、増幅トランジスタ 67、および選択トランジスタ 68 の導電型の組み合わせは、これらの組み合わせに限られるものではない。

#### 【 0 0 5 7 】

リセットトランジスタ 66 のドレイン電極は、電源 Vrst に接続され、ソース電極は、浮遊拡散領域 65 に接続されている。また、リセットトランジスタ 66 のゲート電極に駆動信号 RST が印加され、リセットトランジスタ 66 がオンされることにより、浮遊拡散領域 65 がリセットされ、浮遊拡散領域 65 から電荷が排出される。10

#### 【 0 0 5 8 】

増幅トランジスタ 67 のドレイン電極は、図示せぬコンタクトを介して電源 69 (VDD) に接続され、ゲート電極は、コンタクト 65B、配線 65C、およびコンタクト 65A (図 2) を介して浮遊拡散領域 65 に接続されている。選択トランジスタ 68 のドレイン電極は、n 型層 70 を介して増幅トランジスタ 67 のソース電極に接続され、ソース電極は、n 型層 71 およびコンタクト 71A を介して垂直信号線 72 に接続されている。また、選択トランジスタ 68 のゲート電極に駆動信号 SEL が印加され、選択トランジスタ 68 がオンされることにより、画素信号を読み出す対象となる単位画素 50 が選択される。すなわち、増幅トランジスタ 67 は、選択トランジスタ 68 がオンされているとき、浮遊拡散領域 65 の電圧を示す画素信号を、n 型層 70、選択トランジスタ 68、n 型層 71、コンタクト 71A、および垂直信号線 72 を介して、カラム処理部 43 に供給する。ここで、垂直信号線 72 は、図 1 の垂直信号線 47 と同一であり、ソースフォロア回路の一定電流源に接続されている (図 2)。20

#### 【 0 0 5 9 】

なお、選択トランジスタ 68 を、電源 69 (VDD) と増幅トランジスタ 67 のドレイン電極との間に接続することも可能である。また、リセットトランジスタ 66、増幅トランジスタ 67、および選択トランジスタ 68 については、その一つあるいは複数を画素信号の読み出し方法によって省略したり、複数の画素間で共有したりすることも可能である。30

#### 【 0 0 6 0 】

また、単位画素 50 の上面であって、Al や Cu 等で形成される、配線 65C および垂直信号線 72 等からなる配線層より下層には、タングステンなどの金属からなる遮光膜 73 が形成されている。詳細は後述するが、遮光膜 73 は、フォトダイオード 61 の受光部とコンタクト 65A, 65B, 71A 等が形成されている部分のみ開口されている。

#### 【 0 0 6 1 】

フォトダイオード 61 の受光部に対する遮光膜 73 の開口部は、フォトダイオード 61 の光学感度と、浮遊拡散領域 65 で発生するノイズとのトレードオフにより、最適な大きさおよび位置に設定される。なお、ここでいう浮遊拡散領域 65 で発生するノイズとは、CCDイメージセンサのスミアと同じ原理で発生するノイズである。具体的には、例えば、このノイズは、遮光膜 73 の開口から光が、浮遊拡散領域 65 やその近傍に入射し、浮遊拡散領域 65 内で電荷が発生したり、外部で発生した電荷が拡散して浮遊拡散領域 65 に流入したりすることにより発生するノイズである。40

#### 【 0 0 6 2 】

また、コンタクト 65A, 65B, 71A 等に対する遮光膜 73 の開口部は、各コンタクトと遮光膜 73 との間の短絡を防ぐために、各コンタクトの断面より一回り大きく開口され、両者の間に所定の間隔が確保される。ただし、各コンタクトと遮光膜 73 の間隔が狭すぎると、短絡が発生しやすくなる。また、各コンタクトと遮光膜 73 の間隔が広すぎると、開口部から迷い光が入射し、この迷い光により、上述したスミアと同じ原理で発生するノイズが増加する。従って、各コンタクトに対する開口部も、この 2 つの特性のトレ50

ードオフにより、最適な大きさに設定される。

**【0063】**

さらに、遮光膜73には、駆動回路81(図3)が接続され、システム制御部45の制御に基づいて、駆動回路81から、複数の電圧値をとる遮光膜電圧SHDが印加されることにより、遮光膜73は、浮遊拡散領域65の表面、コンタクト65A, 65B、および配線65Cとの間で容量結合する。このようにして発生する寄生容量74は、浮遊拡散領域65の総容量に対して支配的な要素となる。なお、図2においては、寄生容量74は、遮光膜73と配線65Cとの間に図示されている図形と同様の、遮光膜73と、浮遊拡散領域65、コンタクト65A, 65Bそれぞれとの間に図示されている図形も含む。

**【0064】**

**[単位画素の第1の動作例1]**

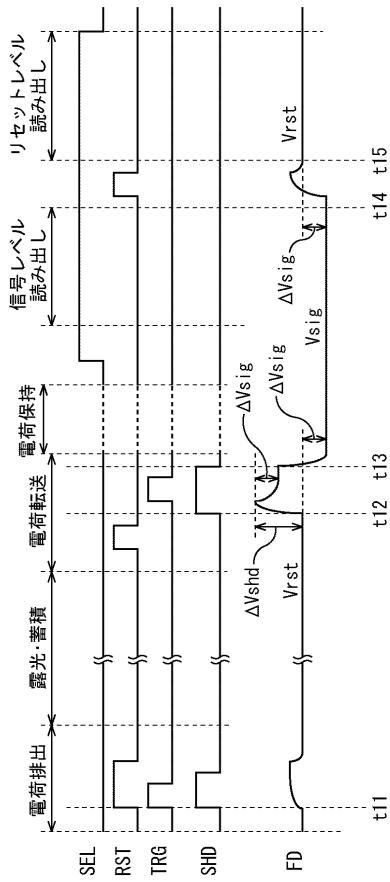

次に、図4のタイミングチャートを参照して、単位画素50において、フォトダイオード61の電荷が読み出される際の、単位画素50の動作(駆動方法)について説明する。

**【0065】**

まず、駆動信号SELがH(High)レベルになった状態で、時刻t1において駆動信号RSTがパルス状に印加されると、浮遊拡散領域65に蓄積されている電荷がリセットトランジスタ66によってリセット(排出)され、浮遊拡散領域65の電圧FDはVrstとなる。このリセット状態は、駆動信号TRGがHレベルになるまで続き、その間、リセットレベルの電圧が読み出される。

**【0066】**

その後、駆動信号TRGがHレベルになると、フォトダイオード61に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送され、時刻t4において駆動信号SELがL(Low)レベルになるまで、信号レベルの電圧が読み出される。

**【0067】**

このようにして、読み出されたリセットレベルと信号レベルとの差分をとることでノイズを除去する、いわゆるCDS処理を行うことで、ノイズが除去された画素信号を読み出すことができる。

**【0068】**

ここで、フォトダイオード61に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送されるとき、すなわち、時刻t2乃至t3において、遮光膜電圧SHDは、それまで印加されていたLレベルからHレベルとされる。これにより、遮光膜73は高い電圧に設定され、遮光膜73と浮遊拡散領域65との間の寄生容量74によって、浮遊拡散領域65の電圧FDはVshd分変調される。そして、フォトダイオード61から浮遊拡散領域65に電荷が転送されると、浮遊拡散領域65の電圧FDは、その電荷に対応するVsigt分だけ降下する。

**【0069】**

時刻t3において、遮光膜電圧SHDがHレベルからLレベルとされると、遮光膜73は低い電圧に設定され、浮遊拡散領域65の電圧FDは-Vshd分変調される。これにより、信号レベルの読み出し期間においては、浮遊拡散領域65の電圧FDは、リセットトランジスタ66により設定された電圧Vrstより-Vsig分低い電圧Vsigtに保持される。

**【0070】**

以上の動作によれば、フォトダイオード61に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送されるときに、浮遊拡散領域65の電圧FDはVshd分変調され、受光部(フォトダイオード61)とのポテンシャルの差を大きくすることができるので、受光部の蓄積電荷を残留させることなく完全転送することができるようになるので、撮像画像の高画質化を図ることが可能となる。

**【0071】**

なお、遮光膜73の低い方の電圧(Lレベルの遮光膜電圧SHD)は、負電圧に設定されるようにできる。これにより、浮遊拡散領域65のSi表面に反転層を形成し、Si表面の結

10

20

30

40

50

晶欠陥から発生する暗電流や点欠陥の発生を抑制することが可能となる。

#### 【0072】

また、上述で説明した動作は、CMOSイメージセンサ30において浮遊拡散領域65を電荷保持領域として用いたグローバルシャッタ動作に適用するよう也能する。

#### 【0073】

##### [ 単位画素の第1の動作例2 ]

ここで、図5のタイミングチャートを参照して、グローバルシャッタ動作を行うCMOSイメージセンサ30における単位画素50の動作（駆動方法）について説明する。

#### 【0074】

CMOSイメージセンサ30においては、図5のタイミングチャートに示される、電荷排出期間における電荷排出、露光・蓄積期間における露光・蓄積、および電荷転送期間における電荷転送は全画素一括で行われる。また、電荷保持期間における電荷保持、信号レベル読み出し期間における信号レベル読み出し、およびリセットレベル読み出し期間におけるリセットレベル読み出しは、行単位で行われる。10

#### 【0075】

まず、電荷排出期間の時刻t11において、全単位画素50について、駆動信号RST, TRG、および遮光膜電圧SHDがパルス状に印加されると、フォトダイオード61および浮遊拡散領域65に蓄積されている電荷がリセットされ、浮遊拡散領域65の電圧FDはVrstとなる。

#### 【0076】

これにより、これまでフォトダイオード61に蓄積されていた電荷が掃き出され、露光・蓄積期間においては、新たに被写体からの光から得られた電荷がフォトダイオード61に蓄積されることになる。20

#### 【0077】

露光・蓄積期間の後、電荷転送期間において、全単位画素50について、駆動信号RSTがパルス状に印加され、浮遊拡散領域65に蓄積されている電荷が再度リセットされた後、フォトダイオード61に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送されるとき、すなわち、駆動信号TRGがLレベルからHレベルとされる時刻t12乃至t13において、遮光膜電圧SHDがLレベルからHレベルとされる。これにより、遮光膜73は高い電圧に設定され、遮光膜73と浮遊拡散領域65との間の寄生容量74によって、浮遊拡散領域65の電圧FDはVshd分変調される。そして、フォトダイオード61から浮遊拡散領域65に電荷が転送されると、浮遊拡散領域65の電圧FDは、その電荷に対応するVsigtだけ降下する。30

#### 【0078】

時刻t13において、遮光膜電圧SHDがHレベルからLレベルとされると、遮光膜73は低い電圧に設定され、浮遊拡散領域65の電圧FDは-Vshd分変調される。これにより、電荷保持期間においては、浮遊拡散領域65の電圧FDは、リセットトランジスタ66により設定された電圧VrstよりVsigt分低い電圧Vsigtに保持される。

#### 【0079】

電荷保持期間の後、行毎の単位画素50について、駆動信号SELがLレベルからHレベルとされると、時刻t14において駆動信号RSTがHレベルとされるまで、浮遊拡散領域65に蓄積されている電荷に対応する電圧、すなわち、信号レベルの電圧が読み出される。40

#### 【0080】

時刻t14乃至t15において駆動信号RSTがHレベルとされると、浮遊拡散領域65に蓄積されている電荷がリセットトランジスタ66によってリセット（排出）され、浮遊拡散領域65の電圧FDはVrstとなる。このリセット状態は、駆動信号SELがLレベルになるまで続き、その間、リセットレベルの電圧が読み出される。このようにして、読み出されたりセットレベルと信号レベルとの差分をとることでノイズを除去するCDS処理を行うことで、ノイズが除去された画素信号が読み出される。

#### 【0081】

以上の動作によれば、全単位画素 50について、フォトダイオード 61に蓄積された電荷が転送ゲート 64によって浮遊拡散領域 65に転送されるときに、浮遊拡散領域 65の電圧FDは  $V_{shd}$  分変調され、受光部（フォトダイオード 61）とのポテンシャルの差を大きくすることができるので、グローバルシャッタ動作を行うCMOSイメージセンサ 30においても、受光部の蓄積電荷を残留させることなく完全転送することが可能となる。これにより、飽和電荷量を拡大することができるとともに、残像を低減することができるようになるので、撮像画像の高画質化を図ることが可能となる。

#### 【0082】

なお、以上の動作においても、遮光膜 73の低い方の電圧（L レベルの遮光膜電圧SHD）は、負電圧に設定されるようにできる。これにより、浮遊拡散領域 65のSi表面に反転層を形成し、Si表面の結晶欠陥から発生する暗電流や点欠陥の発生を抑制することが可能となる。10

#### 【0083】

また、CMOSイメージセンサ 30において、遮光膜 73を、1行または複数行単位で、駆動走査方向に分離されて形成されるようにし、行単位で駆動させるようにすることで、遮光膜 73に接続されている駆動回路 81を、転送ゲート 64のゲート電極に駆動信号TRGを印加する図示せぬ駆動回路と共有するようにしてもよい。これにより、駆動回路 81を設ける必要がなくなるので、CMOSイメージセンサ 30に設ける駆動回路を削減することができ、消費電力を低減することができるとともに、遮光膜 73に遮光膜電圧SHDが印加される際の負荷抵抗（配線抵抗）を低減することが可能となる。20

#### 【0084】

以上においては、電荷転送期間において、フォトダイオード 61に蓄積された電荷が浮遊拡散領域 65に転送されるときに、遮光膜 73の電圧を高くする動作について説明した。。

#### 【0085】

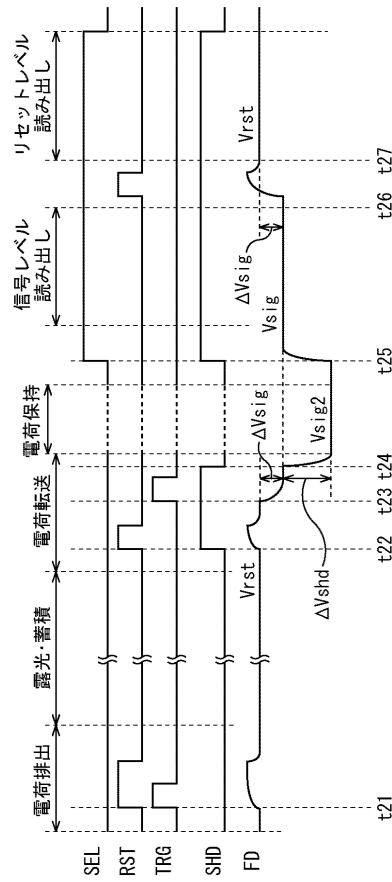

##### [ 単位画素の第 2 の動作例 ]

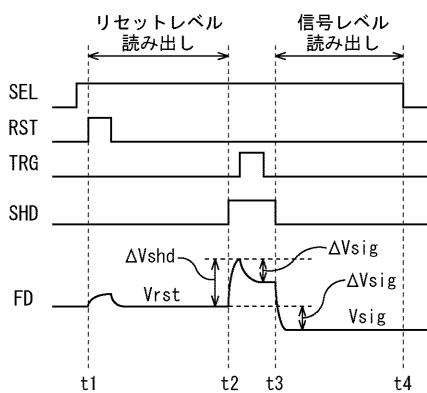

ここで、図 6 のタイミングチャートを参照して、グローバルシャッタ動作を行うCMOSイメージセンサ 30における単位画素 50の第 2 の動作（駆動方法）について説明する。

#### 【0086】

以下で説明する動作を行うCMOSイメージセンサ 30においても、図 6 のタイミングチャートに示される、電荷排出期間における電荷排出、露光・蓄積期間における露光・蓄積、および電荷転送期間における電荷転送は全画素一括で行われる。また、電荷保持期間における電荷保持、信号レベル読み出し期間における信号レベル読み出し、およびリセットレベル読み出し期間におけるリセットレベル読み出しへは、行単位で行われる。30

#### 【0087】

まず、電荷排出期間の時刻  $t_{21}$ において、全単位画素 50について、駆動信号RST, TRGがパルス状に印加されると、フォトダイオード 61および浮遊拡散領域 65に蓄積されている電荷がリセットされ、浮遊拡散領域 65の電圧FDは  $V_{rst}$  となる。

#### 【0088】

これにより、これまでフォトダイオード 61に蓄積されていた電荷が掃き出され、露光・蓄積期間においては、新たに被写体からの光から得られた電荷がフォトダイオード 61に蓄積されることになる。40

#### 【0089】

露光・蓄積期間の後、電荷転送期間の時刻  $t_{22}$ において、全単位画素 50について、駆動信号RSTがパルス状に印加され、浮遊拡散領域 65に蓄積されている電荷がリセットされたとき、遮光膜電圧SHDが L レベルから H レベルとされる。これにより、遮光膜 73は高い電圧に設定されるが、浮遊拡散領域 65の電圧FDは、一旦立ち上がり再び  $V_{rst}$  となる。。

#### 【0090】

時刻  $t_{23}$ において、駆動信号TRGが L レベルから H レベルとされ、フォトダイオード 61

50

に蓄積された電荷が転送ゲート 6 4 によって浮遊拡散領域 6 5 に転送されると、浮遊拡散領域 6 5 の電圧FDは、その電荷に対応する Vsig 分だけ低い電圧Vsigに保持される。

#### 【 0 0 9 1 】

そして、時刻t24において、遮光膜電圧SHDがH レベルからL レベルとされると、遮光膜7 3 は低い電圧に設定され、遮光膜7 3 と浮遊拡散領域6 5との間の寄生容量7 4 によって、浮遊拡散領域6 5 の電圧FDは - Vshd分変調される。これにより、電荷保持期間においては、浮遊拡散領域6 5 の電圧FDは、リセットトランジスタ6 6 により設定された電圧Vrstより ( $Vsig + Vshd$ ) 分低い電圧Vsig2に保持される。

#### 【 0 0 9 2 】

電荷保持期間の後、時刻t25において、行毎の単位画素5 0について、駆動信号SELがL レベルからH レベルとされるとともに、遮光膜電圧SHDがL レベルからH レベルとされると、浮遊拡散領域6 5 に蓄積されている電荷に対応する電圧、すなわち、信号レベルの電圧が読み出されるとともに、遮光膜7 3 は高い電圧に設定される。これにより、信号レベル読み出し期間においては、浮遊拡散領域6 5 の電圧FDは、Vshd分変調され、リセットトランジスタ6 6 により設定された電圧Vrstより Vsig分低い電圧Vsigに保持される。

#### 【 0 0 9 3 】

このように、浮遊拡散領域6 5 の電圧FDは、電荷保持期間においては、電圧Vsigよりも低い電圧Vsig2に保持されるが、信号レベル読み出し期間においては、電圧Vsigに戻るため、信号レベルの読み出しに必要な電圧範囲は、従来の動作におけるそれと同様とすることができる。

#### 【 0 0 9 4 】

時刻t26乃至t27において駆動信号RSTがH レベルとされると、浮遊拡散領域6 5 に蓄積されている電荷がリセットトランジスタ6 6 によってリセットされ、浮遊拡散領域6 5 の電圧FDはVrstとなる。このリセット状態は、駆動信号SELがL レベルになるまで続き、その間、リセットレベルの電圧が読み出される。このようにして、読み出されたリセットレベルと信号レベルとの差分をとることでノイズを除去するCDS処理を行うことで、ノイズが除去された画素信号が読み出される。なお、遮光膜電圧SHDは、駆動信号SELがL レベルにされるとともに、H レベルからL レベルとされる。

#### 【 0 0 9 5 】

以上の動作によれば、全単位画素5 0について、フォトダイオード6 1に蓄積された電荷が転送ゲート6 4 によって浮遊拡散領域6 5 に転送された後に、浮遊拡散領域6 5 の電圧FDは - Vshd分変調され、電荷保持期間における浮遊拡散領域6 5 の電圧FDをより一層低い電圧に保持することができるようになる。これにより、浮遊拡散領域6 5 にかかる電界の強さが緩和され、暗電流や点欠陥の発生を抑制することが可能となり、ひいては、撮像画像の高画質化を図ることが可能となる。

#### 【 0 0 9 6 】

なお、以上の動作においても、遮光膜7 3 の低い方の電圧 (L レベルの遮光膜電圧SHD) は、負電圧に設定されるようにできる。これにより、浮遊拡散領域6 5 のSi表面に反転層を形成し、Si表面の結晶欠陥から発生する暗電流や点欠陥をさらに抑制することが可能となる。

#### 【 0 0 9 7 】

また、CMOSイメージセンサ3 0において、遮光膜7 3 を、1行または複数行単位で、駆動走査方向に分離されて形成されるようにし、行単位で駆動させることで、行毎の順次読み出しにおいて読み出される行に応じた電荷保持期間だけ、浮遊拡散領域6 5 の電圧FDをより一層低い電圧に保持することができる。

#### 【 0 0 9 8 】

さらに、遮光膜7 3 を、駆動走査方向に分離されて形成されるようにし、行単位で駆動させるようにした場合、上述した第2の動作を行うCMOSイメージセンサ3 0において、遮光膜7 3 に接続されている駆動回路8 1を、選択トランジスタ6 8 のゲート電極に駆動信号SELを印加する図示せぬ駆動回路と共有するようにしてもよい。

10

20

30

40

50

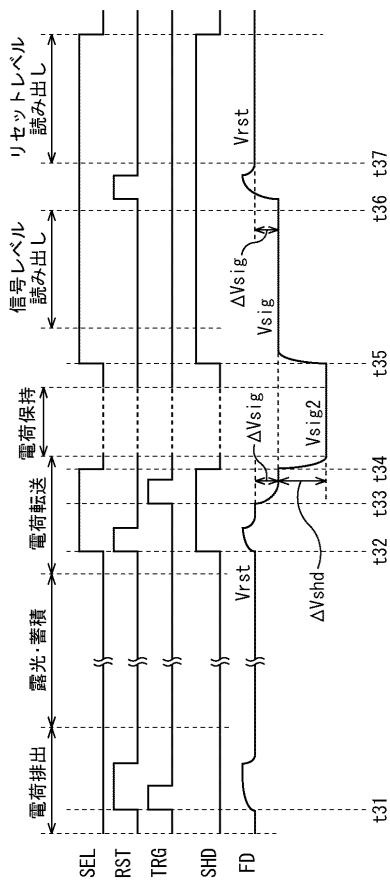

**【 0 0 9 9 】**

図7は、遮光膜73に接続されている駆動回路81を、選択トランジスタ68のゲート電極に駆動信号SELを印加する駆動回路と共有するようにしたCMOSイメージセンサ30における単位画素50の動作(駆動方法)を説明するタイミングチャートである。

**【 0 1 0 0 】**

駆動回路81を選択トランジスタ68の駆動回路と共有することで、図7のタイミングチャートに示されるように、駆動信号SELと遮光膜電圧SHDとが同一のタイミングで印加されるようになる。

**【 0 1 0 1 】**

このとき、CMOSイメージセンサ30において、電荷転送期間では、選択トランジスタ68、および駆動走査方向に分離され形成された遮光膜73の駆動は全画素一括で行われ、信号レベル読み出し期間およびリセットレベル読み出し期間では、選択トランジスタ68、および駆動走査方向に分離され形成された遮光膜73の駆動は行単位で行われるようになる。 10

**【 0 1 0 2 】**

このように、駆動回路81を選択トランジスタ68の駆動回路と共有することで、駆動回路81を設ける必要がなくなるので、CMOSイメージセンサ30に設ける駆動回路を削減することができ、消費電力を低減することができるとともに、遮光膜73に遮光膜電圧SHDが印加される際の負荷抵抗(配線抵抗)を低減することが可能となる。

**【 0 1 0 3 】**

ところで、本発明は、上述した実施の形態で説明した単位画素以外の構造にも採用することができる。以下、本発明が適用可能なその他の単位画素の構造について説明する。また、以下の図において、図2と対応する部分には同一符号を付してあり、その説明は適宜省略する。 20

**【 0 1 0 4 】****[ 単位画素のその他の第1の構成例 ]**

図8は、単位画素50のその他の第1の構成例を示す図である。

**【 0 1 0 5 】**

図8の単位画素50Bでは、図2の構成に加えて、フォトダイオード61と転送ゲート64との間に、転送ゲート91とメモリ部92が設けられている。 30

**【 0 1 0 6 】**

転送ゲート91は、フォトダイオード61で光電変換され、フォトダイオード61の内部に蓄積された電荷を、転送ゲート91のゲート電極に駆動信号TRXが印加されることによって転送する。メモリ部92は、遮光されており、転送ゲート91の下に形成されたn型の埋め込みチャネルによって形成され、転送ゲート91によってフォトダイオード61から転送された電荷を蓄積する。メモリ部92が埋め込みチャネルによって形成されていることで、Si-SiO<sub>2</sub>界面での暗電流の発生を抑えることができるため画質の向上に寄与できる。

**【 0 1 0 7 】**

このメモリ部92において、その上部に転送ゲート91のゲート電極を配置し、そのゲート電極に駆動信号TRXを印加することでメモリ部92に変調をかけることができる。すなわち、転送ゲート91のゲート電極に駆動信号TRXが印加されることで、メモリ部92のポテンシャルが深くなる。これにより、メモリ部92の飽和電荷量を、変調を掛けない場合よりも増やすことができる。 40

**【 0 1 0 8 】**

また、図8の単位画素50Bにおいて、転送ゲート64は、その図示せぬゲート電極に駆動信号TRGが印加されると、メモリ部92に蓄積された電荷を、浮遊拡散領域65に転送する。

**【 0 1 0 9 】**

すなわち、図8の単位画素50Bにおいては、第1の動作を行う場合には、メモリ部9 50

2に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送されるときに、浮遊拡散領域65の電圧FDが変調され、第2の動作を行う場合には、メモリ部92に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送された後に、浮遊拡散領域65の電圧FDが変調されるようになる。なお、図8の単位画素50Bにおいては、メモリ部92とは異なるその他の電荷保持領域をさらに設けるようにしてもよい。

#### 【0110】

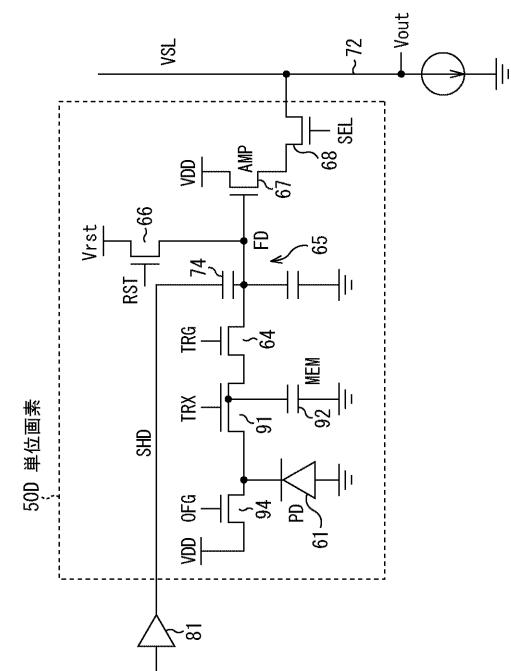

##### [単位画素のその他の第2の構成例]

図9は、単位画素50のその他の第2の構成例である単位画素50Cの構造を示す図である。

#### 【0111】

図9の単位画素50Cでは、転送ゲート91のゲート電極の下で、かつ、フォトダイオード61とメモリ部92との境界部分に、p-の不純物拡散領域を設けることによりオーバーフローパス93を形成した点が図8の単位画素50Bと異なる。

#### 【0112】

単位画素50Cにおいては、低照度での発生電荷を優先的にフォトダイオード61で蓄積する手段として、オーバーフローパス93が用いられる。

#### 【0113】

フォトダイオード61とメモリ部92との境界部分に、p-の不純物拡散領域を設けることで境界部分のポテンシャルが下がる。このポテンシャルが下がった部分がオーバーフローパス93となる。そして、フォトダイオード61で発生し、オーバーフローパス93のポテンシャルを超えた電荷は、自動的にメモリ部92に漏れて、蓄積される。換言すれば、オーバーフローパス93のポテンシャル以下の発生電荷はフォトダイオード61に蓄積される。

#### 【0114】

また、オーバーフローパス93は中間電荷転送部としての機能を持つ。すなわち、中間電荷転送部としてのオーバーフローパス93は、複数の単位画素の全てが同時に撮像動作を行う露光期間において、フォトダイオード61での光電変換によって発生し、オーバーフローパス93のポテンシャルで決まる所定電荷量を超える電荷を信号電荷としてメモリ部92へ転送する。

#### 【0115】

そして、図9の単位画素50Cにおいても、転送ゲート64は、その図示せぬゲート電極に駆動信号TRGが印加されると、メモリ部92に蓄積された電荷が、浮遊拡散領域65に転送される。

#### 【0116】

すなわち、図9の単位画素50Cにおいてもまた、図8の単位画素50Bと同様にして、第1の動作を行う場合には、メモリ部92に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送されるときに、浮遊拡散領域65の電圧FDが変調され、第2の動作を行う場合には、メモリ部92に蓄積された電荷が転送ゲート64によって浮遊拡散領域65に転送された後に、浮遊拡散領域65の電圧FDが変調されるようになる。

#### 【0117】

なお、図9の例では、p-の不純物拡散領域を設けることによりオーバーフローパス93を形成した構造が採用されている。しかし、p-の不純物拡散領域を設ける代わりに、n-の不純物拡散領域を設けることによりオーバーフローパス93を形成した構造をとることも可能である。

#### 【0118】

##### [単位画素のその他の第3の構成例]

また、図9で説明した単位画素50Cに、ブルーミング防止用のオーバーフローゲートが設けられるようにしてもよい。そのような場合、単位画素50Cの回路構成は、例えば、図10に示すように構成される。なお、図10において、図9における場合と対応する部分には、同一の符号を付してあり、その説明は適宜省略する。

10

20

30

40

50

## 【0119】

図10に示す単位画素50Dには、図9に示した単位画素50Cに加えて、さらにトランジスタなどからなるオーバーフローゲート94が設けられている。図10では、オーバーフローゲート94は、電源VDDとフォトダイオード61との間に接続されている。オーバーフローゲート94は、垂直駆動部42から画素駆動線46を介して、制御信号OFGが供給されると、フォトダイオード61をリセットする。すなわち、オーバーフローゲート94は、フォトダイオード61に蓄積されている電荷を排出する。

## 【0120】

なお、図10に示す単位画素50Dに設けられたオーバーフローゲート94は、図2で説明した単位画素50、および、図8で説明した単位画素50Bに設けられるようにしてももちろんよい。

10

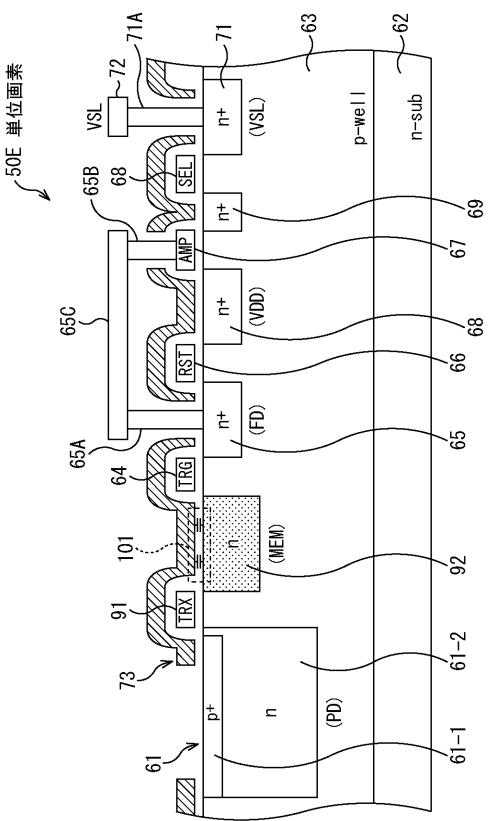

## 【0121】

## [単位画素のその他の第4の構成例]

図11は、単位画素50のその他の第4の構成例である単位画素50Eの構造を示す図である。

## 【0122】

単位画素50Eでは、遮光膜73が、メモリ部92のSi表面との間で容量結合している点で、図8の単位画素50Bと異なる。このようにして発生する寄生容量101は、メモリ部92の総容量に対して支配的な要素となる。

## 【0123】

20

図11の単位画素50Eにおいては、第1の動作を行う場合には、フォトダイオード61に蓄積された電荷が転送ゲート91によってメモリ部92に転送されるときに、メモリ部92の電圧が変調され、第2の動作を行う場合には、フォトダイオード61に蓄積された電荷が転送ゲート91によってメモリ部92に転送された後に、メモリ部92の電圧が変調されるようになる。

## 【0124】

なお、図8乃至11を参照して説明した単位画素50B乃至50Eにおいても、遮光膜73の低い方の電圧(Lレベルの遮光膜電圧SHD)は、負電圧に設定されるようにできる。これにより、浮遊拡散領域65やメモリ部92のSi表面に反転層を形成し、Si表面の結晶欠陥から発生する暗電流や点欠陥の発生を抑制することが可能となる。

30

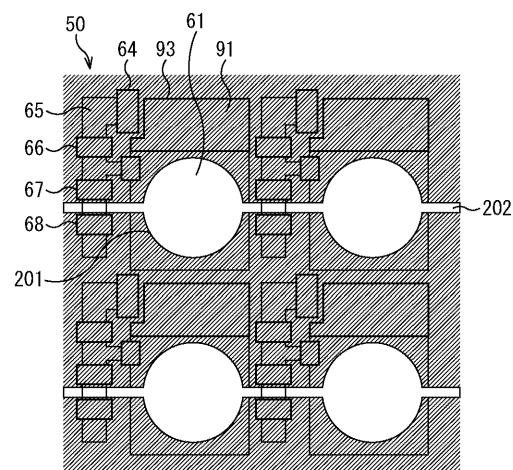

## 【0125】

## [単位画素の平面の構成]

次に、本発明を適用したCMOSイメージセンサ30の画素アレイ部41を構成する単位画素の平面の構成について説明する。

## 【0126】

図12は、単位画素の構成例を示す平面図である。図12においては、4つの単位画素が示されている。なお、図12に示される単位画素のそれぞれは、具体的には、転送ゲート91およびメモリ部92を有する単位画素50B乃至50E(図8乃至11)に対応するが、図2の単位画素50にも対応するものとする。また、図12において、図2、8乃至11に示される構成と対応する部分には、同一の符号を付してあり、その説明は適宜省略する。

40

## 【0127】

すなわち、図12に示されるように、単位画素50の上面を覆うように形成される遮光膜73におけるフォトダイオード61の受光部に対応する部分に、開口部201が設けられている。

## 【0128】

開口部201は、上述したように、フォトダイオード61の光学感度と、浮遊拡散領域65で発生するノイズとのトレードオフにより、最適な大きさおよび位置に設定されている。なお、図12においては、コンタクト65A、65B、71A等に対応する部分に設けられる開口部は図示されないものとする。

50

**【 0 1 2 9 】**

このように、CMOSイメージセンサ30の画素アレイ部41においては、その画素アレイ部41を構成する各単位画素50のフォトダイオード61の受光部に対応する部分に開口部201が設けられた遮光膜73が形成される。

**【 0 1 3 0 】**

なお、図12においては、1枚の遮光膜73が画素アレイ部41を構成する各単位画素50の上面に形成されるものとしたが、上述したように、1枚の遮光膜73を、1行または複数行単位で、駆動走査方向に分離されて形成されるようにすることもできる。

**【 0 1 3 1 】**

例えば、図12において左右方向に配列される単位画素50を、駆動走査方向の単位画素50とした場合、図12に示される4個の単位画素50を、上下2個ずつに分ける境界部分で、遮光膜73を駆動走査方向に分離されるように形成することができる。10

**【 0 1 3 2 】**

これにより、遮光膜73は、行単位で駆動されるようになるので、第2の動作において、行毎の順次読み出しにおいて読み出される行に応じた電荷保持期間だけ、浮遊拡散領域65の電圧FDをより一層低い電圧に保持することができるようになる。

**【 0 1 3 3 】**

また、図13に示されるように、開口部201を、遮光膜73を分離する境界202の一部として、遮光膜73が駆動走査方向に分離されるようにしてもよい。これにより、開口部201を、遮光膜73を分離する境界の一部としない場合と比較して、単位画素50の上面における非遮光領域を小さくすることができる。特に、開口部201が円形に形成されている場合、その直径を通るように境界202を形成することで、単位画素50の上面における非遮光領域を最小にすることことができ、浮遊拡散領域65で発生するノイズをより低減することが可能となる。20

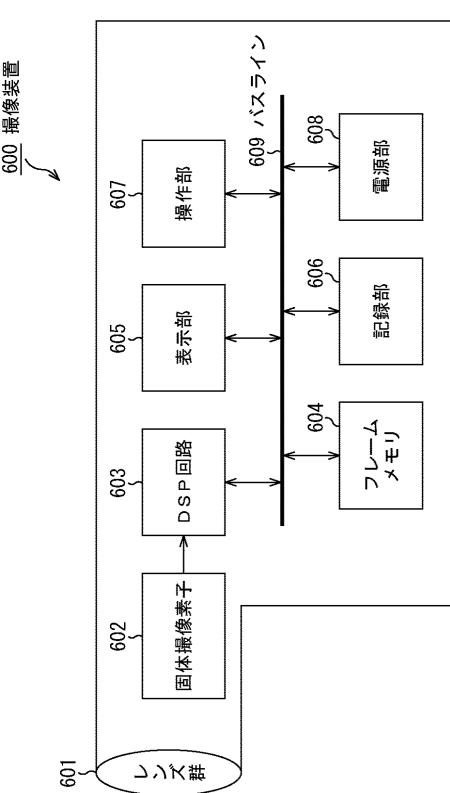

**【 0 1 3 4 】****[ 本発明を適用した電子機器の構成例 ]**

なお、本発明は、固体撮像素子への適用に限られるものではない。即ち、本発明は、デジタルスチルカメラやビデオカメラ等の撮像装置や、撮像機能を有する携帯端末装置や、画像読取部に固体撮像素子を用いる複写機など、画像取込部（光電変換部）に固体撮像素子を用いる電子機器全般に対して適用可能である。固体撮像素子は、ワンチップとして形成された形態であってもよいし、撮像部と信号処理部および光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。30

**【 0 1 3 5 】**

図14は、本発明を適用した電子機器としての、撮像装置の構成例を示すブロック図である。

**【 0 1 3 6 】**

図14の撮像装置600は、レンズ群などからなる光学部601、上述した単位画素50の各構成が採用される固体撮像素子（撮像デバイス）602、およびカメラ信号処理回路であるDSP回路603を備える。また、撮像装置600は、フレームメモリ604、表示部605、記録部606、操作部607、および電源部608も備える。DSP回路603、フレームメモリ604、表示部605、記録部606、操作部607および電源部608は、バスライン609を介して相互に接続されている。40

**【 0 1 3 7 】**

光学部601は、被写体からの入射光（像光）を取り込んで固体撮像素子602の撮像面上に結像する。固体撮像素子602は、光学部601によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この固体撮像素子602として、上述した実施の形態に係るCMOSイメージセンサ30等の固体撮像素子、即ちグローバル露光によって歪みのない撮像を実現できる固体撮像素子を用いることができる。

**【 0 1 3 8 】**

10

20

30

40

50

表示部 605 は、例えば、液晶パネルや有機EL(Electro Luminescence)パネル等のパネル型表示装置からなり、固体撮像素子 602 で撮像された動画または静止画を表示する。記録部 606 は、固体撮像素子 602 で撮像された動画または静止画を、ビデオテープやDVD(Digital Versatile Disk)等の記録媒体に記録する。

#### 【0139】

操作部 607 は、ユーザによる操作の下に、撮像装置 600 が持つ様々な機能について操作指令を発する。電源部 608 は、DSP回路 603、フレームメモリ 604、表示部 605、記録部 606 および操作部 607 の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

#### 【0140】

上述したように、固体撮像素子 602 として、上述した実施の形態に係るCMOSイメージセンサ 30 を用いることで、電荷保持領域の電圧を十分大きく変調することができる。従って、飽和電荷量を拡大することができるとともに、残像を低減することができるようになったり、暗電流や点欠陥の発生を抑制することができるようになるので、ビデオカメラやデジタルスチルカメラ、さらには携帯電話機等のモバイル機器向けカメラモジュールなどの撮像装置 600 において、撮像画像の高画質化を図ることができる。

#### 【0141】

また、上述した実施形態においては、可視光の光量に応じた信号電荷を物理量として検知する単位画素が行列状に配置されてなるCMOSイメージセンサに適用した場合を例に挙げて説明した。しかしながら、本発明はCMOSイメージセンサへの適用に限られるものではなく、画素アレイ部の画素列ごとにカラム処理部を配置してなるカラム方式の固体撮像素子全般に対して適用可能である。

#### 【0142】

また、本発明は、可視光の入射光量の分布を検知して画像として撮像する固体撮像素子への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像素子や、広義の意味として、圧力や静電容量など、他の物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像素子（物理量分布検知装置）全般に対して適用可能である。

#### 【0143】

なお、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

#### 【符号の説明】

#### 【0144】

30 CMOSイメージセンサ， 41 画素アレイ部， 42 垂直駆動部， 43 カラム処理部， 45 システム制御部， 47 垂直信号線， 50 単位画素， 61 フォトダイオード， 64 転送ゲート， 65 浮遊拡散領域， 66 リセットトランジスタ， 68 選択トランジスタ， 73 遮光膜， 74 寄生容量， 81 駆動回路

10

20

30

【図1】

図1【図2】

図2【図3】

図3【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9【図10】

図10【図11】

図11【図12】

図12

【図13】

図13

【図14】

図14

---

フロントページの続き

(56)参考文献 特開2005-101442(JP,A)

特開2003-258234(JP,A)

特開2000-077642(JP,A)

特開2007-115803(JP,A)

特開平10-313426(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378 ,

H04N 5/222 - 5/257 ,

H01L 21/339 ,

H01L 27/14 - 27/148 ,

H01L 29/762