(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5160856号

(P5160856)

(45) 発行日 平成25年3月13日(2013.3.13)

(24) 登録日 平成24年12月21日(2012.12.21)

(51) Int.Cl.

F 1

**G 11 C 11/401 (2006.01)**

**G 11 C 11/407 (2006.01)**

**G 06 F 12/00 (2006.01)**

G 11 C 11/34 362 Z

G 11 C 11/34 362 T

G 06 F 12/00 597 D

G 06 F 12/00 550 E

G 06 F 12/00 564 C

請求項の数 4 (全 17 頁)

(21) 出願番号

特願2007-276184 (P2007-276184)

(22) 出願日

平成19年10月24日 (2007.10.24)

(65) 公開番号

特開2009-104721 (P2009-104721A)

(43) 公開日

平成21年5月14日 (2009.5.14)

審査請求日

平成22年5月17日 (2010.5.17)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100102864

弁理士 工藤 実

(72) 発明者 杉下 恭輔

神奈川県川崎市中原区下沼部 1753 番地

NECエレクトロニクス株式会社内

審査官 堀田 和義

最終頁に続く

(54) 【発明の名称】 DDRメモリコントローラ及び半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

マスター-DLLにより決定されたディレイコードに基づき、DDRメモリからのストローブ信号をスレーブディレイにて遅延させ、前記DDRメモリからのデータ信号に対するストローブ信号とするDDRメモリコントローラであって、

周波数の異なる複数のクロック信号から周波数選択信号に応じて選択されたクロック信号を前記DDRメモリに出力するクロック制御回路を備え、

前記クロック制御回路は、

入力された基準クロック信号から前記複数のクロック信号のそれぞれを生成する複数の分周回路と、

前記周波数選択信号を前記複数のクロック信号のそれぞれに同期化させる同期化回路と、

前記同期化回路から出力される前記周波数選択信号に応じたクロック信号を前記複数のクロック信号から選択する選択回路と

を有し、

前記マスター-DLLには、前記複数のクロック信号のうち最大周波数のクロック信号がリファレンスクロックとして入力されることを特徴とするDDRメモリコントローラ。

## 【請求項 2】

請求項1に記載のDDRメモリコントローラであって、

前記クロック制御回路は、前記基準クロック信号の周波数を遙倍するPLL回路を有し

、前記複数のクロック信号は、遅倍後の前記基準クロック信号から生成されることを特徴とするDDRメモリコントローラ。

**【請求項3】**

請求項1又は2に記載のDDRメモリコントローラであって、

前記ディレイコードは、初期化時に決定され、前記DDRメモリに対して出力されるクロック信号が変わっても変化しないことを特徴とするDDRメモリコントローラ。

**【請求項4】**

請求項1乃至3のいずれかに記載のDDRメモリコントローラを備えることを特徴とする半導体集積回路。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は、DDRメモリ用のDDRメモリコントローラ、及びそのDDRメモリコントローラが搭載された半導体装置に関する。

**【背景技術】**

**【0002】**

SDRAM (Synchronous Dynamic Random Access Memory) の一種として、高速データ転送が可能なDDR (Double Data Rate) - SDRAMが知られている。DDR - SDRAMは、以下「DDRメモリ」と参照される。また、DDRメモリ用のメモリコントローラは、以下「DDRメモリコントローラ」と参照される。

20

**【0003】**

DDRメモリとDDRメモリコントローラとの間の高速データ転送においては、「ストローブ信号」と呼ばれる専用の信号が用いられる。具体的には、データ送出側は、データ信号と共にストローブ信号を出力する。そのストローブ信号は、データ信号の出力タイミング毎にH/Lのトグル動作を繰り返すが、クロック信号とは別の信号である。データ受取側は、クロック信号ではなく受け取ったストローブ信号を参照して、データ信号の取り込みを行う。

**【0004】**

例えばデータ読み出し時、DDRメモリは、読み出しデータを示すデータ信号に加えてストローブ信号を出力する。DDRメモリコントローラは、受け取ったストローブ信号を参照して、ストローブ信号の立ち上がりエッジ及び立ち下がりエッジのタイミングで、受け取ったデータ信号をラッチする。この時、データ信号が安定した状態でラッチを行うために、DDRメモリコントローラは、受け取ったストローブ信号を遅延させ、遅延したストローブ信号を参照してデータ信号をラッチする。ストローブ信号を遅延させる手法として、DLL (Delay Locked Loop) 回路及びディレイ回路を用いる手法が知られている(特許文献1、非特許文献1参照)。

30

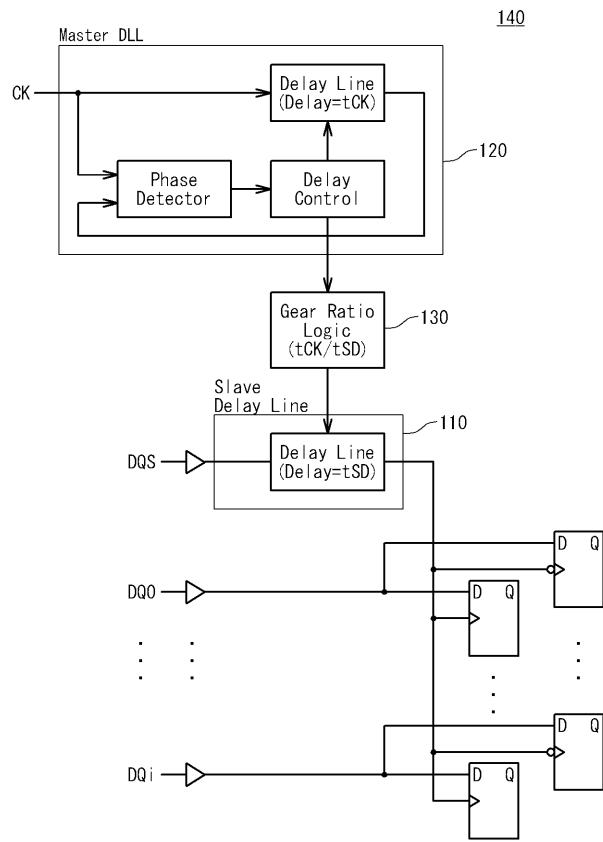

**【0005】**

図1は、非特許文献1のFig.30に記載されたDDRメモリコントローラ140を示している。このDDRメモリコントローラ140は、DDRメモリから出力されるデータ信号DQ及びストローブ信号DQSを受け取る。データ信号DQは、例えば8ビットの信号(DQ0~DQ7)である。図1に示されるように、DDRメモリコントローラは、スレーブディレイ回路110、マスターDLL回路120、及びギア比論理回路130を備えている。

40

**【0006】**

スレーブディレイ回路110は、DDRメモリから受け取ったストローブ信号DQSを遅延させる回路である。具体的には、スレーブディレイ回路110は、ディレイコードに応じて遅延段数が変化する可変遅延回路を有しており、その遅延段数に応じた遅延時間tSdだけストローブ信号DQSを遅延させる。このスレーブディレイ回路110から出力されるストローブ信号DQSの立ち上がりエッジ及び立ち下がりエッジを参照して、フリップフロップ群はデータ信号DQをラッチする。データ信号DQが安定状態でラッチされ

50

るためには、典型的には、ストローブ信号DQSの位相が約90度シフトするように遅延段数(遅延時間tSD)が設定される。言い換れば、ストローブ信号DQSの位相が約90度シフトするように、ディレイコードが決定される。

#### 【0007】

ここで、遅延回路を構成する遅延素子の特性は、温度や製造ばらつきに依存して変化することに注意する必要がある。つまり、ディレイコード(遅延段数)が同じ場合であっても、温度や製造ばらつきに依存して遅延時間tSDがばらつく可能性がある。半導体チップ毎に遅延時間tSDを揃えるためには、半導体チップ毎にディレイコードを調整(トリミング)する必要がある。そのようなディレイコードのトリミングを行うための構成が、マスターDLL回路120及びギア比論理回路130である。

10

#### 【0008】

マスターDLL回路120は、DDRメモリの動作クロックCKをリファレンスクロックとして受け取り、そのリファレンスクロックCKの位相が360度(1周期)シフトするような遅延段数を求める。具体的には、マスターDLL回路120は、可変遅延回路、位相検出器、及び遅延コントローラを有している。可変遅延回路は、上述のスレーブディレイ回路110と同じ構成を有しており、遅延コントローラから出力される制御信号に応じて遅延段数が変化する。この可変遅延回路は、リファレンスクロックCKを受け取り、設定された遅延段数に応じた遅延時間tCKだけリファレンスクロックCKを遅延させる。位相検出器には、遅延していないリファレンスクロックCKと、可変遅延回路から出力される遅延後のリファレンスクロックCKが入力される。そして、位相検出器は、それら2つのリファレンスクロックCKの位相を比較し、比較結果を遅延コントローラに出力する。遅延コントローラは、比較結果に基づいて制御信号を変更し、可変遅延回路における遅延段数を変化させる。このような構成により、リファレンスクロックCKが1周期遅延するような遅延段数を決定することが可能となる。

20

#### 【0009】

ギア比論理回路130は、リファレンスクロックCKが1周期遅延するような遅延段数を“4”で割る。その結果、リファレンスクロックCKの位相が90度シフトするような遅延段数が算出される。その算出された遅延段数を示す信号が、本半導体チップにおけるディレイコードである。スレーブディレイ回路110は、決定されたディレイコードに基づいて遅延段数を設定し、ストローブ信号DQSを遅延時間tSDだけ遅延させる。

30

#### 【0010】

このようにして、マスターDLL回路120及びギア比論理回路130により、ディレイコードのトリミングが半導体チップ毎に実施される。その結果、スレーブディレイ回路110におけるストローブ信号DQSの遅延時間tSDが、半導体チップ毎に揃うことになる。すなわち、動作環境の温度や製造ばらつきに対処することが可能となる。

#### 【0011】

【特許文献1】特開2004-220643号公報

【非特許文献1】Design Line, Volume 8, Issue 3, 3Q99,

Micron Technology Inc.

#### 【発明の開示】

40

#### 【発明が解決しようとする課題】

#### 【0012】

近年、DDRメモリを様々な動作周波数で動作させたいという要望がある。例えば、データがあまり読み出されないときには、消費電力を抑制するために、DDRメモリの動作周波数を低下させたいという要望がある。図1で示された構成によれば、DDRメモリの動作クロックCKが変更されると、それに応じて上述のディレイコードも適切な値に再度設定される。これにより、DDRメモリの動作周波数の変更後でも、DDRメモリコントローラはデータ信号DQを安定的に取り込むことができる。

#### 【0013】

しかしながら、ディレイコードの再設定(再トリミング)には、ある程度の時間が必要

50

である。従って、ディレイコードの再設定の間は、DDRメモリを待機状態にする必要があり、スループットが低下する。すなわち、DDRメモリの動作周波数の変更に伴うディレイコードの再設定による時間的なオーバーヘッドは、スループットの低下を招く。

**【課題を解決するための手段】**

**【0014】**

以下に、[発明を実施するための最良の形態]で使用される番号・符号を用いて、[課題を解決するための手段]を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

10

**【0015】**

本発明の第1の観点において、マスターDLL(50)により決定されたディレイコード(DCODE)に基づき、DDRメモリ(1)からのストローブ信号(DQS)をスレーブディレイ(40)にて遅延させ、DDRメモリ(1)からのデータ信号(DQ)に対するストローブ信号(DQS')とするDDRメモリコントローラ(10)が提供される。そのDDRメモリコントローラ(10)は、周波数の異なる複数のクロック信号(CLK1～CLKn)から周波数選択信号(SEL)に応じて選択されたクロック信号(SCLK)をDDRメモリ(1)に出力するクロック制御回路(20)を備える。マスターDLL(50)には、上記複数のクロック信号(CLK1～CLKn)のうち最大周波数のクロック信号(CLK1)がリファレンスクロック(REF)として入力される。

20

**【0016】**

本発明の第2の観点において、DDRメモリコントローラ(10)は、クロック制御回路(20)とストローブ遅延回路(40)とを備える。クロック制御回路(20)は、周波数の異なる複数のクロック信号(CLK1～CLKn)のうちいずれか1つをDDRメモリ(1)の動作クロック信号(SCLK)として出力する。ストローブ遅延回路(40)は、DDRメモリ(1)から出力されるストローブ信号(DQS)を、所定の遅延時間(tSD)だけ遅延させる。その遅延時間(tSD)は、上記複数のクロック信号(CLK1～CLKn)のうち最大周波数のクロック信号(CLK1)の位相が所定の角度だけシフトする量に調整される。

30

**【0017】**

本発明の第3の観点において、上記DDRメモリコントローラ(10)が搭載された半導体装置が提供される。

**【0018】**

本発明によれば、クロック制御回路(20)によって、DDRメモリ(1)の動作クロック信号(SCLK)を変更したいという要求は満たされる。一方で、ディレイコード(DCODE)は、DDRメモリ(1)の動作クロック信号(SCLK)となり得る複数のクロック信号(CLK1～CLKn)のうち、最大周波数のクロック信号(CLK1)を基準として用いることにより決定される。つまり、ストローブ信号(DQS)の遅延時間(tSD)は、DDRメモリ(1)の動作クロック信号(SCLK)にかかわらず、最大周波数のクロック信号(CLK1)の位相が所定の角度だけシフトする量に調整される。

40

**【0019】**

DDRメモリ(1)の動作クロック信号(SCLK)が、最大周波数のクロック信号(CLK1)から、それ以外のもの(CLK2～CLKn)に変更される場合を考える。この時、データ信号(DQ)のストローブ信号(DQS')に対するセットアップバージェットは変わらず、これは動作上問題ない。また、データ信号(DQ)のストローブ信号(DQS')に対するホールドバージェットは必然的に大きくなり、これも動作上問題ない。すなわち、DDRメモリ(1)の動作クロック信号(SCLK)としていかなるクロック信号が選択されても、DDRメモリコントローラ(10)は、データ信号(DQ)を安定的に取り込むことが可能である。言い換えれば、DDRメモリ(1)の動作クロック信号(SCLK)が変更されても、ディレイコード(DCODE)を再度トリミングする必

50

要はない。

#### 【0020】

以上に説明されたように、ディレイコード（D C O D E）のトリミング時に基準となるクロック信号（R E F）は、D D Rメモリ（1）の動作クロック信号（S C L K）となり得る複数のクロック信号（C L K 1 ~ C L K n）のうち最大周波数のクロック信号（C L K 1）に固定される。この場合、D D Rメモリ（1）の動作クロック信号（S C L K）が変更されても、ディレイコード（D C O D E）を再度トリミングする必要はない。従って、動作クロック信号（S C L K）の変更に伴う時間的なオーバーヘッドが短縮される。結果として、スループットの低下が防止され、動作速度が全体として向上する。

#### 【発明の効果】

10

#### 【0021】

本発明によれば、D D Rメモリの動作周波数の変更に伴う時間的なオーバーヘッドが短縮される。その結果、スループットの低下が防止され、動作速度が全体として向上する。

#### 【発明を実施するための最良の形態】

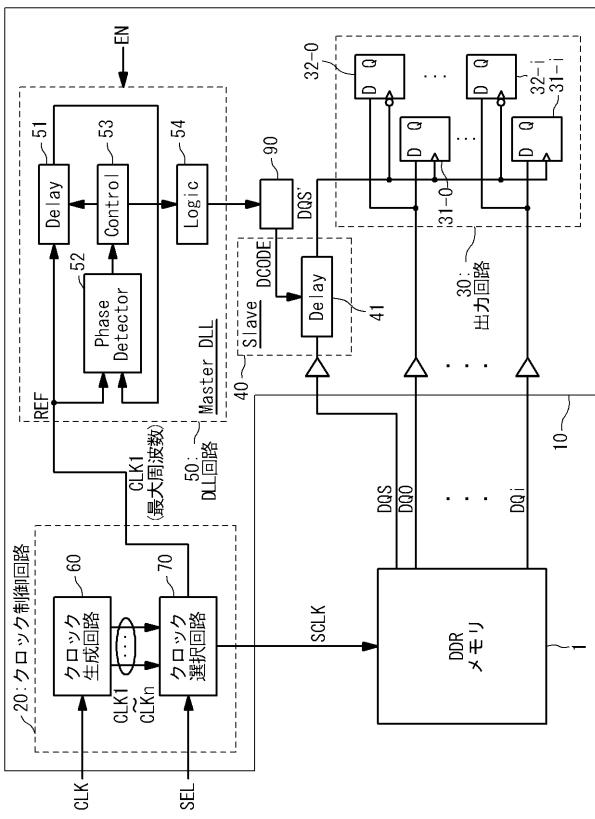

#### 【0022】

添付図面を参照して、本発明の実施の形態に係るD D Rメモリコントローラ及び半導体装置を説明する。

#### 【0023】

##### 1. 第1の実施の形態

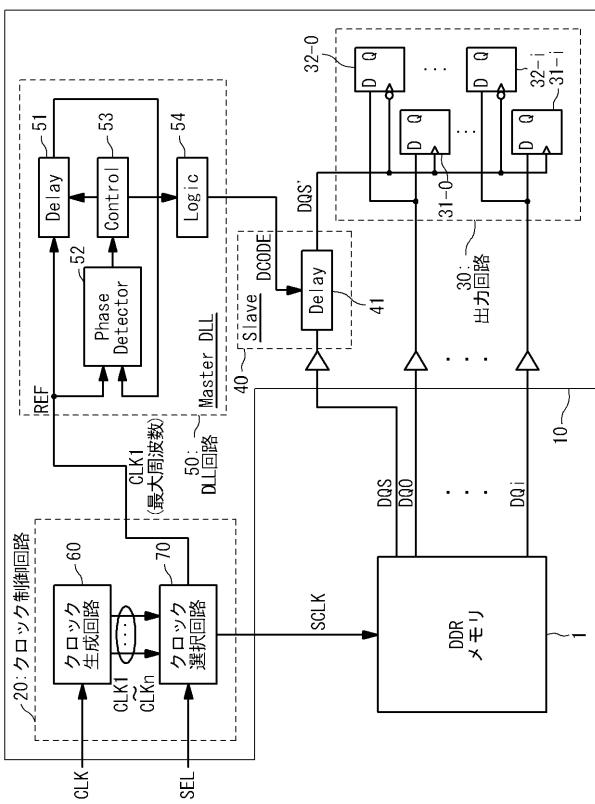

###### 1 - 1. 全体構成

20

図2は、本発明の第1の実施の形態に係るD D Rメモリコントローラ及び半導体装置の構成を示すブロック図である。半導体装置は、D D Rメモリ（D D R - S D R A M）1及びD D Rメモリコントローラ10を備えている。例えば、D D Rメモリ1とD D Rメモリコントローラ10とは、それぞれ別々の半導体チップとして構成される。また、D D Rメモリコントローラ10は論理半導体チップなどに搭載されていてもよい。つまり、D D Rメモリコントローラ10が搭載された半導体集積回路が提供されてもよい。さらにまた、D D Rメモリ1とD D Rメモリコントローラ10とが1つの半導体チップに構成されているてもよい。

#### 【0024】

30

D D Rメモリ1は、動作クロック信号S C L Kに基づいて動作する。また、データ読み出し時、D D Rメモリ1は、読み出しデータを示すデータ信号D Q（D Q 0 ~ D Q i）に加えて、そのデータ信号D Qに対応するストローブ信号D Q Sを出力する。

#### 【0025】

D D Rメモリコントローラ10は、動作クロック信号S C L KをD D Rメモリ1に出力し、また、動作クロック信号S C L Kを切り換える機能を有している。更に、D D Rメモリコントローラ10は、D D Rメモリ1からデータ信号D Q及びストローブ信号D Q S信号を受け取り、ストローブ信号D Q Sに基づいてデータ信号D Qを外部に出力する機能を有している。これら機能を実現するために、D D Rメモリコントローラ10は、クロック制御回路20、出力回路30、ストローブ遅延回路40、及びD L L回路50を有している。以下、各構成を詳しく説明する。

40

#### 【0026】

###### 1 - 2. クロック制御回路

近年、D D Rメモリ1を状況に応じて様々な動作周波数で動作させたいという要望がある。つまり、D D Rメモリ1の動作クロック信号S C L Kを動的に変更したいという要望がある。そのような要望に応えるための構成が、クロック制御回路20である。

#### 【0027】

クロック制御回路20は、D D Rメモリコントローラ10の外部から基準クロック信号C L Kを受け取る。典型的には、基準クロック信号C L Kは、システムクロック信号である。クロック制御回路20は、受け取った基準クロック信号C L Kに基づいて、互いに周波数の異なる複数のクロック信号C L K 1 ~ C L K nを生成する（nは2以上の整数）。

50

更に、クロック制御回路20は、生成された複数のクロック信号CCLK1～CCLKnのうちいずれか1つを、DDRメモリ1の動作クロック信号SCLKとしてDDRメモリ1に出力する。

#### 【0028】

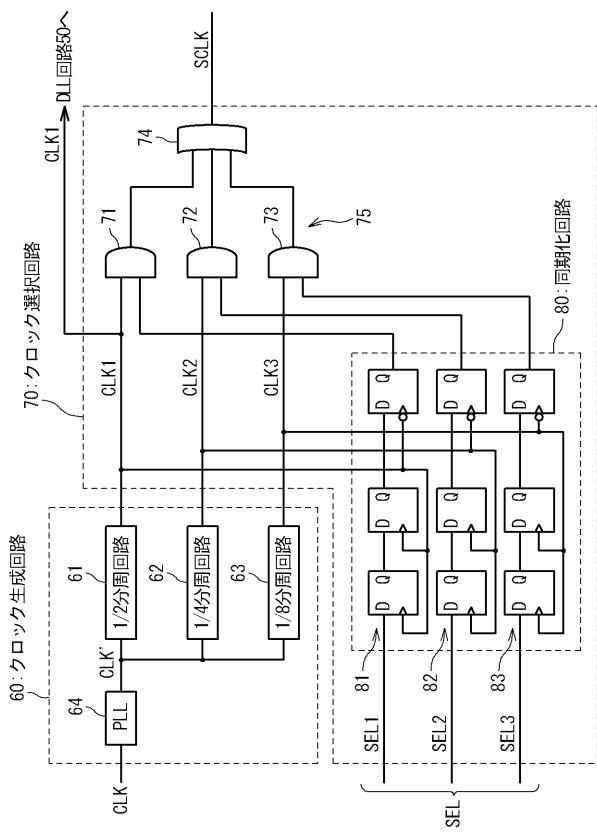

より詳細には、図2に示されるように、クロック制御回路20は、クロック生成回路60及びクロック選択回路70を有している。クロック生成回路60は、基準クロック信号CCLKから、互いに周波数の異なる複数のクロック信号CCLK1～CCLKnを生成する。一方、クロック選択回路70は、複数のクロック信号CCLK1～CCLKnに加えて周波数選択信号SELを受け取る。周波数選択信号SELは、DDRメモリ1の動作クロック信号SCLKを指定する信号であり、例えばCPUによって発行される。クロック選択回路70は、周波数選択信号SELに応答して、複数のクロック信号CCLK1～CCLKnから1つの動作クロック信号SCLKを選択し、選択された動作クロック信号SCLKをDDRメモリ1に出力する。10

#### 【0029】

このように、クロック制御回路20は、複数のクロック信号CCLK1～CCLKnを生成し、そのうち周波数選択信号SELに応じて選択された動作クロック信号SCLKをDDRメモリ1に出力する。DDRメモリ1は、選択された動作クロック信号SCLKに基づいて動作する、すなわち、複数のクロック信号CCLK1～CCLKnのいずれかに基づいて動作する。クロック制御回路20によって生成される複数のクロック信号CCLK1～CCLKnは、DDRメモリ1の動作クロック信号SCLKとなり得る候補である。20

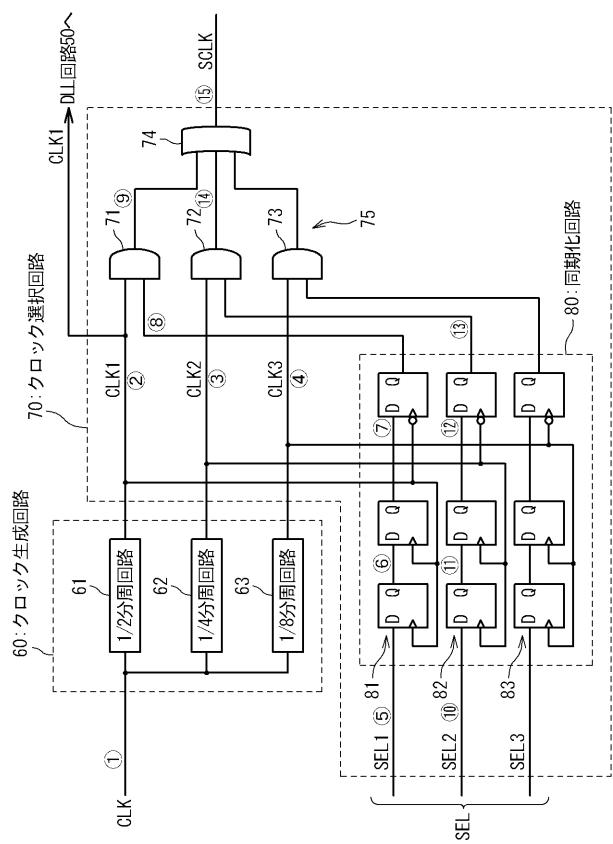

#### 【0030】

図3は、クロック制御回路20の回路構成の一例を示している。図3において、クロック生成回路60は、複数の分周回路61、62及び63を有している。分周回路61、62及び63のそれぞれは、基準クロック信号CCLKから、互いに周波数の異なるクロック信号CCLK1、CCLK2及びCCLK3を生成する。例えば、分周回路61、62及び63は、それぞれ1/2分周回路、1/4分周回路、及び1/8分周回路である。この場合、分周回路61によって生成されるクロック信号CCLK1の周波数が最大となり、分周回路63によって生成されるクロック信号CCLK3の周波数が最小となる。尚、クロック生成回路60の別の形態として、分周回路61、62、63の他に入力クロック(CCLK)をスルーするバッファを有する構成も可能である。30

#### 【0031】

クロック選択回路70は、クロック信号CCLK1～CCLK3と周波数選択信号SELを受け取る。周波数選択信号SELは、クロック信号CCLK1の選択/非選択を示す選択信号SEL1と、クロック信号CCLK2の選択/非選択を示す選択信号SEL2と、クロック信号CCLK3の選択/非選択を示す選択信号SEL3からなる。いずれの選択信号に関しても、Hレベルが「選択」を意味し、Lレベルが「非選択」を意味するとする。ここでは、複数のクロック信号(CCLK1～CCLK3)から1つのクロック信号が選択されるように、選択信号SEL1、SEL2、SEL3は排他的に設定される。

#### 【0032】

図3において、クロック選択回路70は、選択回路75と同期化回路80を有している。同期化回路80は、周波数選択信号SELをクロック信号CCLK1～CCLK3のそれぞれに同期化させるための回路であり、フリップフロップ群81～83を有している。具体的には、フリップフロップ群81は、多段に接続されたフリップフロップを含んでおり、クロック信号CCLK1を利用して選択信号SEL1の同期化を行う。同様に、フリップフロップ群82は、クロック信号CCLK2を利用して選択信号SEL2の同期化を行い、フリップフロップ群83は、クロック信号CCLK3を利用して選択信号SEL3の同期化を行う。尚、選択信号SEL(SEL1～SEL3)としてデコード済みの信号が入力される例をここでは示したが、クロック選択回路70は、選択情報をデコードして選択信号SEL(SEL1～SEL3)を出力するデコード回路を有していてもよい。40

#### 【0033】

選択回路 75 は、同期化回路 80 から出力される周波数選択信号 S E L ( S E L 1 ~ S E L 3 ) に応じたクロック信号を、クロック信号 C L K 1 ~ C L K 3 の中から選択し出力する。例えば図 3 に示されるように、選択回路 75 は、AND 回路 71 ~ 73 及び OR 回路 74 を有している。AND 回路 71 には、クロック信号 C L K 1 と同期化回路 80 から出力される選択信号 S E L 1 が入力される。AND 回路 72 には、クロック信号 C L K 2 と同期化回路 80 から出力される選択信号 S E L 2 が入力される。AND 回路 73 には、クロック信号 C L K 3 と同期化回路 80 から出力される選択信号 S E L 3 が入力される。AND 回路 71 ~ 73 のそれぞれの出力は、OR 回路 74 に入力される。OR 回路 74 から出力される信号が、DDR メモリ 1 の動作クロック信号 S C L K である。

## 【 0 0 3 4 】

10

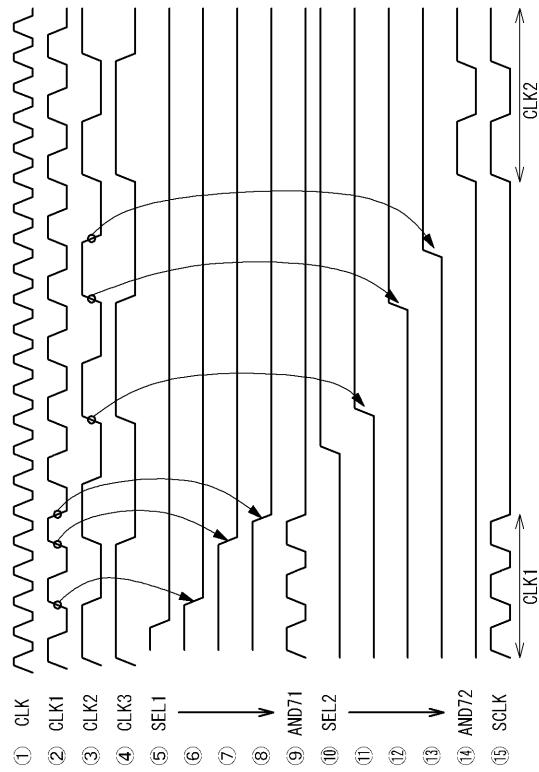

図 4 は、図 3 で示されたクロック制御回路 20 の動作の一例を示すタイミングチャートである。図 4 には、基準クロック信号 C L K 、クロック信号 C L K 1 ~ C L K 3 、選択信号 S E L 1 、AND 回路 71 の出力、選択信号 S E L 2 、AND 回路 72 の出力、及び選択された動作クロック信号 S C L K が示されている。尚、図 4 中の各段に付されている数字は、図 3 中の対応する数字で示される位置での信号をそれぞれ意味している。

## 【 0 0 3 5 】

図 4 で示される例では、最初、選択信号 S E L 1 だけが H レベルであり、その他の選択信号は L レベルである。その結果、クロック制御回路 20 からは、クロック信号 C L K 1 ~ C L K 3 のうち最大周波数のクロック信号 C L K 1 が、選択的に動作クロック信号 S C L K として出力される。その後、選択信号 S E L 1 が L レベルに変更される。続いて、選択信号 S E L 2 が L レベルから H レベルに変更される。その結果、クロック制御回路 20 からは、クロック信号 C L K 1 ~ C L K 3 のうちクロック信号 C L K 2 が、選択的に動作クロック信号 S C L K として出力される。このように、動作クロック信号 S C L K が、最大周波数のクロック信号 C L K 1 から、それより低い周波数のクロック信号 C L K 2 に切り換える。

20

## 【 0 0 3 6 】

図 5 は、クロック制御回路 20 の回路構成の他の例を示している。図 5 において、クロック選択回路 70 の構成は、図 3 で示されたものと同じである。一方、クロック生成回路 60 は、分周回路 61 ~ 63 に加えて PLL 回路 64 を更に有している。PLL 回路 64 は、基準クロック信号 C L K の周波数を遙倍する機能を有している。この場合、分周回路 61 ~ 63 のそれぞれは、遙倍後の基準クロック信号 C L K ' からクロック信号 C L K 1 ~ C L K 3 を生成する。このように、クロック制御回路 20 は、基準クロック信号 C L K を遙倍した後に、複数のクロック信号 C L K 1 ~ C L K 3 を生成してもよい。この場合でも、クロック制御回路 20 が果たす役割は同じである。

30

## 【 0 0 3 7 】

## 1 - 3 . 出力回路及びストローブ遅延回路

再度図 2 を参照して、DDR メモリコントローラ 10 の出力回路 30 及びストローブ遅延回路 40 (スレーブディレイ回路) を説明する。

## 【 0 0 3 8 】

DDR メモリ 1 から出力されるストローブ信号 D Q S は、まず、ストローブ遅延回路 40 に入力される。このストローブ遅延回路 40 は、DDR メモリ 1 から受け取ったストローブ信号 D Q S を、所定の遅延時間 ( t S D ) だけ遅延させる回路である。具体的には、スレーブディレイ回路 40 は、多段の遅延素子から構成される可変遅延回路 41 を含んでいる。その遅延素子の段数、すなわち、遅延時間 ( t S D ) は、後述される「ディレイコード D C O D E 」に応じて変化する。つまり、ストローブ遅延回路 40 は、ディレイコード D C O D E に応じた遅延時間 ( t S D ) だけ、ストローブ信号 D Q S を遅延させる。遅延後のストローブ信号 D Q S は、以下「ストローブ信号 D Q S ' 」と参照される。そのストローブ信号 D Q S ' は、出力回路 30 に供給される。

40

## 【 0 0 3 9 】

出力回路 30 は、DDR メモリ 1 から出力されるデータ信号 D Q ( D Q 0 ~ D Q i ) を

50

受け取る。データ信号 D Q は、例えば 8 ビットの信号 (D Q 0 ~ D Q 7) である。また、出力回路 3 0 は、ストローブ遅延回路 4 0 を通して、ストローブ信号 D Q S' を受け取る。そして、出力回路 3 0 は、受け取ったストローブ信号 D Q S' を参照し、そのストローブ信号 D Q S' の立ち上がりエッジ及び立ち下がりエッジのタイミングでデータ信号 D Q を取り込む。

#### 【 0 0 4 0 】

具体的には、図 2 に示されるように、出力回路 3 0 は、フリップフロップ 3 1 - 0 ~ 3 1 - i 及びフリップフロップ 3 2 - 0 ~ 3 2 - i を有している。フリップフロップ 3 1 - 0 ~ 3 1 - i には、ストローブ信号 D Q S' が入力される。そして、フリップフロップ 3 1 - 0 ~ 3 1 - i のそれぞれは、ストローブ信号 D Q S' の立ち上がりエッジのタイミングで、データ信号 D Q 0 ~ D Q i をラッチする。一方、フリップフロップ 3 2 - 0 ~ 3 2 - i には、ストローブ信号 D Q S' の反転信号が入力される。そして、フリップフロップ 3 2 - 0 ~ 3 2 - i のそれぞれは、ストローブ信号 D Q S' の立ち下がりエッジのタイミングで、データ信号 D Q 0 ~ D Q i をラッチする。そして、出力回路 3 0 は、データ信号 D Q 0 ~ D Q i を、DDR メモリコントローラ 1 0 の外部に出力する。

10

#### 【 0 0 4 1 】

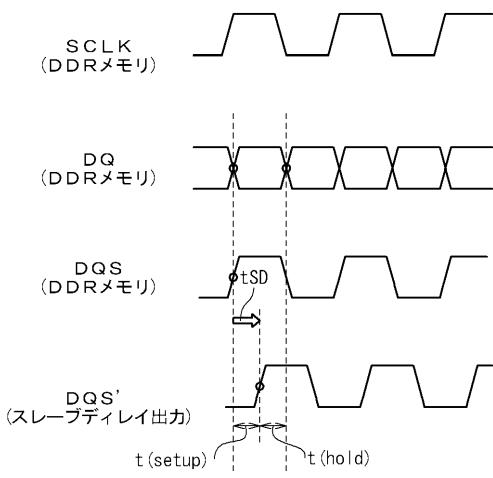

図 6 は、データ信号 D Q とストローブ信号 D Q S、D Q S' の関係を示すタイミングチャートである。DDR メモリ 1 は、上述の動作クロック信号 S C L K に基づいて動作し、データ信号 D Q とストローブ信号 D Q S を出力する。この時、ストローブ信号 D Q S は、データ信号 D Q の出力タイミング毎に H / L のトグル動作を繰り返す。

20

#### 【 0 0 4 2 】

DDR メモリコントローラ 1 0 内で、ストローブ遅延回路 4 0 は、ストローブ信号 D Q S を所定の遅延時間 t S D だけ遅延させる。その結果、ストローブ遅延回路 4 0 から出力されるストローブ信号 D Q S' の立ち上がりエッジ及び立ち下がりエッジのタイミングは、データ信号 D Q が安定期間間に含まれることになる。つまり、データ信号 D Q に関して十分なセットアップ時間 t (s e t u p) とホールド時間 t (h o l d) が確保されることになる。結果として、出力回路 3 0 は、データ信号 D Q が安定している期間に、そのデータ信号 D Q をラッチすることが可能となる。尚、図 6 では、データ信号 D Q 及びストローブ信号 D Q S の各エッジにおいて位相差 (スキー) が無いものとして記載している。しかしながら実際には、後述のように (例えば図 8) 、各データ信号 D Q 及びストローブ信号 D Q S 間にはスキーが生じてしまう。

30

#### 【 0 0 4 3 】

このように、ストローブ遅延回路 4 0 がストローブ信号 D Q S を遅延時間 t S D だけ遅延させることにより、DDR メモリコントローラ 1 0 はデータ信号 D Q を安定状態でラッチすることが可能となる。逆に言えば、データ信号 D Q が安定状態でラッチされるよう、遅延時間 t S D は設定される。その遅延時間 t S D は、可変遅延回路 4 1 を構成する遅延素子の段数によって決まり、その段数はディレイコード D C O D E に応じて設定される。

。

#### 【 0 0 4 4 】

ここで、遅延素子の特性は、温度や製造ばらつきに依存して変化することに注意する必要がある。つまり、ディレイコード D C O D E (遅延段数) が同じ場合であっても、温度や製造ばらつきに依存して遅延時間 t S D がばらつく可能性がある。半導体チップ毎に遅延時間 t S D を揃えるためには、半導体チップ毎にディレイコード D C O D E を調整 (トリミング) する必要がある。そのようなディレイコード D C O D E のトリミングを行うための構成が、次に説明される D L L 回路 5 0 である。

40

#### 【 0 0 4 5 】

##### 1 - 4 . D L L 回路

再度図 2 を参照して、D L L 回路 5 0 (マスター D L L 回路) を説明する。D L L 回路 5 0 は、ストローブ遅延回路 4 0 (スレーブディレイ回路) における遅延時間 t S D を指定するディレイコード D C O D E のトリミングを行い、適切なディレイコード D C O D E

50

を決定する。

**【0046】**

ディレイコード D C O D E の決定に際し、本実施の形態に係る D L L 回路 5 0 は、上述のクロック制御回路 2 0 によって生成された複数のクロック信号 C L K 1 ~ C L K n のうち「最大周波数のクロック信号 C L K 1」をリファレンスクロック R E F として利用する。つまり、D D R メモリ 1 の動作クロック信号 S C L K にかかわらず、D L L 回路 5 0 は、最大周波数のクロック信号 C L K 1 を利用してディレイコード D C O D E を決定する。そのために、D L L 回路 5 0 はクロック制御回路 2 0 から、最大周波数のクロック信号 C L K 1 をリファレンスクロック R E F として受け取る（図 2、図 3、図 5 参照）。

**【0047】**

図 2 に示されるように、D L L 回路 5 0 は、可変遅延回路 5 1、位相検出器 5 2、遅延コントローラ 5 3、及びコード生成論理回路 5 4 を有している。可変遅延回路 5 1 は、ストローブ遅延回路 4 0 に含まれる可変遅延回路 4 1 のレプリカであり、多段の遅延素子を有している。その遅延素子の段数（遅延段数）は、遅延コントローラ 5 3 から出力される制御信号に応じて変化する。可変遅延回路 5 1 は、リファレンスクロック R E F を受け取り、設定された遅延段数に応じた遅延時間だけリファレンスクロック R E F を遅延させる。

10

**【0048】**

位相検出器 5 2 には、遅延していないリファレンスクロック R E F と、可変遅延回路 5 1 から出力される遅延後のリファレンスクロック R E F が入力される。そして、位相検出器 5 2 は、それら 2 つのリファレンスクロック R E F の位相を比較し、比較結果を遅延コントローラ 5 3 に出力する。遅延コントローラ 5 3 は、比較結果に基づいて制御信号を変更し、可変遅延回路 5 1 における遅延段数を変化させる。

20

**【0049】**

以上に説明された可変遅延回路 5 1、位相検出器 5 2、及び遅延コントローラ 5 3 によって、リファレンスクロック R E F の位相が 360 度（1 周期）シフトするような遅延段数を決定することが可能である。コード生成論理回路 5 4 は、リファレンスクロック R E F の位相が 360 度シフトするような遅延段数を、所定の数で割る割算回路である。例えば、コード生成論理回路 5 4 は、上記遅延段数を“4”で割る。その結果、リファレンスクロック R E F の位相が 90 度シフトするような遅延段数が算出される。言い換えれば、最大周波数のクロック信号 C L K 1 の位相が 90 度シフトするような遅延段数が算出される。

30

**【0050】**

このようにして算出された遅延段数を示す信号が、ディレイコード D C O D E である。本実施の形態に係る D L L 回路 5 0 は、最大周波数のクロック信号 C L K 1 の位相が所定の角度（例えば 90 度）だけシフトするようにディレイコード D C O D E を決定する。上述のストローブ遅延回路 4 0 は、決定されたディレイコード D C O D E に基づいて、遅延段数を設定し、ストローブ信号 D Q S を遅延時間 t S D だけ遅延させる。すなわち、ストローブ信号 D Q S の遅延時間 t S D は、最大周波数のクロック信号 C L K 1 の位相が所定の角度（例えば 90 度）だけシフトする量に調整（トリミング）される。

40

**【0051】**

以上に説明されたように、本実施の形態によれば、D L L 回路 5 0 に入力されるリファレンスクロック R E F は、D D R メモリ 1 の動作クロック信号 S C L K にかかわらず、最大周波数のクロック信号 C L K 1 に固定される。言い換えれば、ディレイコード D C O D E は、動作クロック信号 S C L K となり得るクロック信号 C L K 1 ~ C L K n のうち、最大周波数のクロック信号 C L K 1 を基準として用いることにより決定される。結果として、ストローブ信号 D Q S の遅延時間 t S D は、動作クロック信号 S C L K に依存することなく、最大周波数のクロック信号 C L K 1 の位相が所定の角度だけシフトする量に調整されることになる。D D R メモリ 1 の動作クロック信号 S C L K が変更されたとしても、ディレイコード D C O D E や遅延時間 t S D は変わらないことに留意されたい。

50

## 【0052】

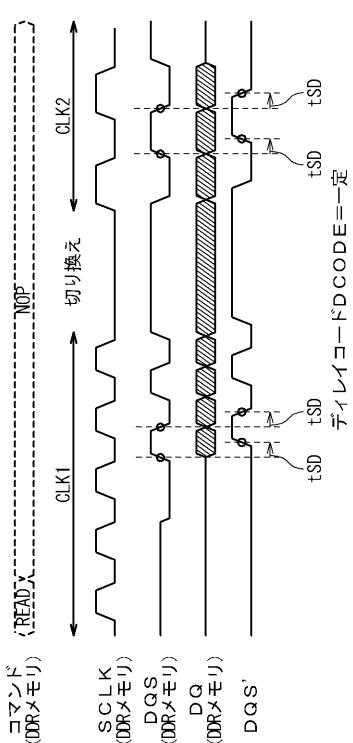

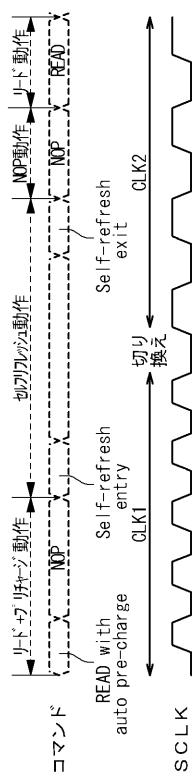

## 1 - 5 . DDR メモリの動作クロック信号の切り換え

次に、DDR メモリ 1 の動作クロック信号 SCLK の切り換え時における DDR メモリコントローラ 10 の動作を説明する。図 7 は、動作クロック信号 SCLK の切り換え処理の一例を示すタイミングチャートである。図 7 には、DDR メモリ 1 に対するコマンド、動作クロック信号 SCLK 、 DDR メモリ 1 から出力されるストローブ信号 DQS とデータ信号 DQ 、及びストローブ遅延回路 40 から出力されるストローブ信号 DQS' が示されている。

## 【0053】

図 7 で示される例において、DDR メモリ 1 にはリードコマンド (READ) が入力され、その後、ノーオペレーションコマンド (NOP) が入力される。リードコマンド (READ) に応答して、DDR メモリ 1 は、データを読み出す。このとき、バースト長は 8 であるとする。10

## 【0054】

最初、DDR メモリ 1 の動作クロック信号 SCLK は、最大周波数のクロック信号 CLK1 である。DDR メモリ 1 は、最大周波数のクロック信号 CLK1 に基づいて、ストローブ信号 DQS 及びデータ信号 DQ を出力する。ストローブ信号 DQS 及びデータ信号 DQ は、 NOP コマンドの期間に出力されている。DDR メモリコントローラ 10 において、ストローブ遅延回路 40 は、ストローブ信号 DQS を所定の遅延時間 tSD だけ遅延させる。その遅延時間 tSD は、最大周波数のクロック信号 CLK1 の位相が所定の角度だけシフトする量に設定されている。20

## 【0055】

NOP コマンドの期間中のあるタイミングにおいて、周波数選択信号 SEL が変更され、動作クロック信号 SCLK が切り換えられる。例えば、動作クロック信号 SCLK は、最大周波数のクロック信号 CLK1 から、それより低いクロック信号 CLK2 に切り換えられる（既出の図 4 参照）。図 4 及び図 7 に示されるように、動作クロック信号 SCLK は、クロック信号 CLK1 から多少の間をあいてクロック信号 CLK2 に変わる。その後、DDR メモリ 1 は、クロック信号 CLK2 に基づいて、ストローブ信号 DQS 及びデータ信号 DQ を出力する。30

## 【0056】

ここで注意すべきことは、DLL 回路 50 に入力されるリファレンスクロック REF は、最大周波数のクロック信号 CLK1 のまま変わらないことである。すなわち、DLL 回路 50 においてディレイコード DCODE の再トリミングは実施されず、ディレイコード DCODE は変わらず一定である。従って、ストローブ遅延回路 40 によるストローブ信号 DQS の遅延時間 tSD も変わらない。遅延時間 tSD は、最大周波数のクロック信号 CLK1 の位相が所定の角度だけシフトする量のままである。40

## 【0057】

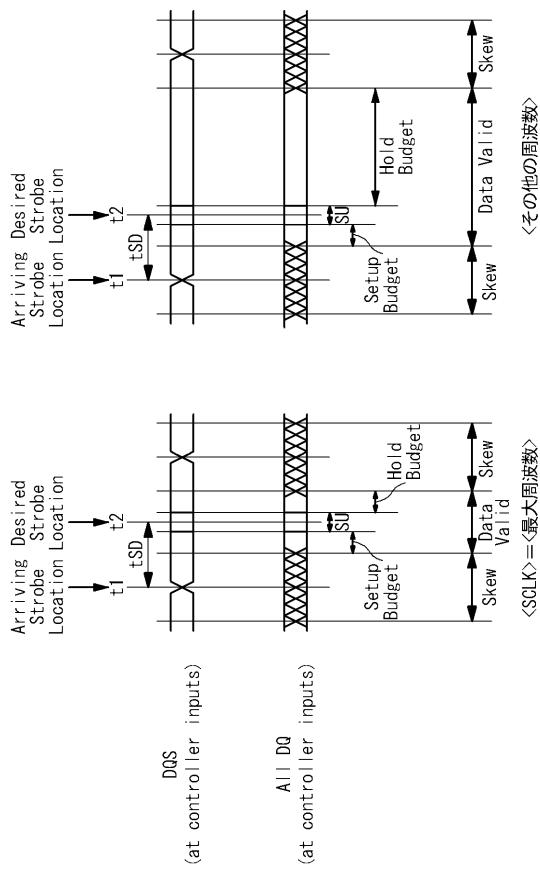

図 8 は、DDR メモリ 1 の動作周波数が最大周波数の場合とその他の場合とのタイミングバジェットを概念的に示している。より詳細には、図 8 には、DDR メモリコントローラ 10 に入力されるストローブ信号 DQS とデータ信号 DQ が示されている。ストローブ信号 DQS は、時刻 t1 において DDR メモリコントローラ 10 に到達するとする。また、スキュー (Skew) を考慮すると、データ信号 DQ が安定する期間は、図中の “Data Valid” で示される期間となる。そのデータ信号 DQ の安定期間内の時刻 t2 に、ストローブ信号 DQS' のエッジのタイミングが位置することが望ましい。その時刻 t2 と上記時刻 t1 の差が、望ましい遅延時間 tSD である。但し、実際の遅延回路では、遅延時間 tSD に誤差が生じる可能性がある。そのような不確定性 (SU: Strobe Uncertainty) も考慮すると、図 8 に示されるように、セットアップバジェット (Setup Budget) とホールドバジェット (Hold Budget) が定義され得る。40

## 【0058】

上述の通り、本実施の形態によれば、ディレイコード DCODE は、最大周波数のクロ50

ック信号 C L K 1 を利用することによりトリミングされている。つまり、遅延時間  $t_{SD}$  は、DDRメモリ1の動作周波数が最大の場合でもセットアップ／ホールド制約が満たされるように設定されている。

#### 【 0 0 5 9 】

次に、動作周波数が最大周波数以外の場合を考える。この場合も、ディレイコード D C O D E 、すなわち遅延時間  $t_{SD}$  は、最大周波数の場合と同じである。そのため、セットアップバジェットは最大周波数の場合と変わらないが、これは動作上問題ない。一方、ホールドバジェットは、図8に示されるように、最大周波数の場合よりも必然的に大きくなる。これも当然、動作上問題ない。すなわち、最大周波数の場合と少なくとも同等のタイミングバジェットが確保されるため、正常動作が保障される。

10

#### 【 0 0 6 0 】

このように、DDRメモリ1の動作クロック信号 S C L K としていかなるクロック信号が選択されても、十分なタイミングバジェットが確保されるため、DDRメモリコントローラ10は、データ信号 D Q を安定的に取り込むことが可能である。言い換えれば、十分なタイミングバジェットが保障されているため、動作クロック信号 S C L K が変更されても、ディレイコード D C O D E を再度トリミングする必要はない。

#### 【 0 0 6 1 】

以上に説明されたように、ディレイコード D C O D E は、DDRメモリ1の動作クロック信号 S C L K となり得る候補のうち最大周波数のクロック信号 C L K 1 を利用することにより決定される。その場合、DDRメモリ1の動作クロック信号 S C L K が変更されても、ディレイコード D C O D E を再度トリミングする必要はない。従って、DDRメモリコントローラ10におけるディレイコード D C O D E の再トリミング処理の間に、DDRメモリ1を待機状態にする必要もない。周波数選択信号 S E L が切り換えられたとき、DDRメモリ1は、コントローラ側の再トリミング処理を待つことなく、すぐに動作することが可能である。このように、動作クロック信号 S C L K の動的な変更に伴う時間的なオーバーヘッドが短縮される。結果として、スループットの低下が防止され、動作速度が全体として向上する。

20

#### 【 0 0 6 2 】

尚、動作クロック信号 S C L K の切り換えタイミングは、図7で示された例に限られない。動作クロック信号 S C L K の切り換えタイミングは、DDRメモリ1側の仕様に応じて適宜決定されるとよい。例えば、DDRメモリ1の仕様が、セルフリフレッシュ動作中の動作クロック信号 S C L K の切り換えを許可する場合を考える。その場合は、図9に示されるように、セルフリフレッシュ動作の最中に、動作クロック信号 S C L K が切り換えられるとよい。図9で示される例の場合でも、DDRコントローラ10側の処理は同じである。つまり、本実施の形態に係るDDRコントローラ10は、DDRメモリ1側の仕様によらず、汎用的に適用可能である。

30

#### 【 0 0 6 3 】

##### 1 - 6 . 効果

本実施の形態によれば、DDRメモリ1の動作クロック信号 S C L K を動的に変更したいという要求は、クロック制御回路20によって満たされる。

40

#### 【 0 0 6 4 】

また、ディレイコード D C O D E のトリミング時に用いられるリファレンスクロック R E F は、DDRメモリ1の動作クロック信号 S C L K となり得る複数のクロック信号 C L K 1 ~ C L K n のうち最大周波数のクロック信号 C L K 1 に固定される。この場合、DDRメモリ1の動作クロック信号 S C L K が変更されても、ディレイコード D C O D E を再度トリミングする必要はない。従って、動作クロック信号 S C L K の動的な変更に伴う時間的なオーバーヘッドが短縮される。結果として、スループットの低下が防止され、動作速度が全体として向上する。

#### 【 0 0 6 5 】

##### 2 . 第2の実施の形態

50

図10は、本発明の第2の実施の形態に係るDDRメモリコントローラ及び半導体装置の構成を示すブロック図である。半導体装置は、DDRメモリ1及びDDRメモリコントローラ10を備えている。本実施の形態において、DDRメモリコントローラ10は、図2で示された構成に加えて保持回路90を有している。その他の構成は第1の実施の形態と同様であり、重複する説明は適宜省略される。

#### 【0066】

保持回路90は、ディレイコードDCODEを保持する記憶回路であり、DLL回路50とストローブ遅延回路40に接続されている。 DLL回路50は、決定したディレイコードDCODEを保持回路90に出力し、保持回路90は、 DLL回路50によって決定されたディレイコードDCODEを保持する。そのディレイコードDCODEは、保持回路90からストローブ遅延回路40に出力される。ストローブ遅延回路40は、保持回路90によって保持されているディレイコードDCODEに基づいて、ストローブ信号DQSを遅延させる。

10

#### 【0067】

第1の実施の形態で説明されたように、DDRメモリ1の動作クロックSCLKが変更されたとしても、ディレイコードDCODEの再トリミングを実施する必要はない。従って、ディレイコードDCODEが一旦決定された後は、DLL回路50の動作を停止させることが可能である。これにより、消費電力が低減される。

#### 【0068】

例えば、DDRメモリコントローラ10の初期化時に、イネーブル信号ENがHレベルに設定され、DLL回路50はディレイコードDCODEを決定する。ディレイコードDCODEの決定後は、イネーブル信号ENはLレベルに設定され、DLL回路50はスタンバイ状態に設定される。これにより、DLL回路50におけるリファレンスクロックREFのトグル動作がなくなり、消費電力が大幅に削減される。 DLL回路50がスタンバイ状態となつても、保持回路90からストローブ遅延回路40にディレイコードDCODEが出力されるため、ストローブ遅延回路40はストローブ信号DQSを遅延させることができる。

20

#### 【0069】

##### 3. その他の例

本発明は、上述のいずれの実施の形態の記載にのみ限定されるものではない。たとえば、上述の可変遅延回路41、51はともに段数が固定の多段の遅延素子を有し、その遅延素子の動作電圧（電源電圧）を、遅延コントローラ53から出力される制御信号に応じて変化する構成としてもよい。たとえば可変遅延回路51を4段の遅延素子で構成すれば、遅延素子が1段ごとに位相を90度ずつシフトすることが可能である。

30

#### 【0070】

また、上述のいずれの実施の形態においてもクロック生成回路60を備える構成として示した。別途周波数の異なる複数のクロックを本発明のDDRコントローラのために準備できる場合は、単に周波数の異なる複数のクロック信号を直接クロック選択回路70に入力する構成をとってもよいことはもちろんである。

#### 【0071】

さらにまた、上述のDDRメモリ1及びDDRコントローラ10が備えられた半導体装置は、単にプリント板（PCB）にそれぞれ独立した半導体集積回路（半導体チップ）として搭載された構成でもよい。あるいは、SIP（System In Package）として、DDRメモリチップとDDRコントローラ10が搭載された半導体チップとが1つの半導体パッケージ基板に収められてもよい。 DDRメモリチップやDDRコントローラ10が搭載された半導体チップは、所望の数（1つまたは複数）を搭載してよい。

40

#### 【図面の簡単な説明】

#### 【0072】

【図1】図1は、従来技術におけるDDRメモリコントローラの構成を示すブロック図である。

50

【図2】図2は、本発明の第1の実施の形態に係るDDRメモリコントローラ及び半導体装置の構成を示すブロック図である。

【図3】図3は、クロック制御回路の構成の一例を示す回路図である。

【図4】図4は、クロック制御回路の動作の一例を示すタイミングチャートである。

【図5】図5は、クロック制御回路の構成の他の例を示す回路図である。

【図6】図6は、データ信号DQとストローブ信号DQS、DQS'の関係を示すタイミングチャートである。

【図7】図7は、DDRメモリの動作クロック信号の切り換え処理の一例を示すタイミングチャートである。

【図8】図8は、最高周波数の場合とその他の周波数の場合とのタイミングバジェットの比較を示す概念図である。 10

【図9】図9は、DDRメモリの動作クロック信号の切り換え処理の他の例を示すタイミングチャートである。

【図10】図10は、本発明の第2の実施の形態に係るDDRメモリコントローラ及び半導体装置の構成を示すブロック図である。

#### 【符号の説明】

##### 【0073】

|               |              |    |

|---------------|--------------|----|

| 1             | DDRメモリ       |    |

| 10            | DDRメモリコントローラ |    |

| 20            | クロック制御回路     | 20 |

| 30            | 出力回路         |    |

| 40            | ストローブ遅延回路    |    |

| 41            | 可変遅延回路       |    |

| 50            | DLL回路        |    |

| 51            | 可変遅延回路       |    |

| 52            | 位相検出器        |    |

| 53            | 遅延コントローラ     |    |

| 54            | コード生成論理回路    |    |

| 60            | クロック生成回路     |    |

| 61 ~ 63       | 分周回路         | 30 |

| 64            | PLL回路        |    |

| 70            | クロック選択回路     |    |

| 75            | 選択回路         |    |

| 80            | 同期化回路        |    |

| 90            | 保持回路         |    |

| CCLK          | 基準クロック信号     |    |

| CCLK1 ~ CCLKn | クロック信号       |    |

| SCLK          | 動作クロック信号     |    |

| DQ            | データ信号        |    |

| DQS, DQS'     | ストローブ信号      | 40 |

| REF           | リファレンスクロック   |    |

| SEL           | 周波数選択信号      |    |

| CODE          | ディレイコード      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 図 9 】

【 図 1 0 】

---

フロントページの続き

(56)参考文献 特開2005-78547(JP,A)

特開2007-109203(JP,A)

特開2006-13990(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 401

G 06 F 12 / 00