(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7030817号**

**(P7030817)**

(45)発行日 令和4年3月7日(2022.3.7)

(24)登録日 令和4年2月25日(2022.2.25)

(51)国際特許分類

|         |                |     |         |      |         |

|---------|----------------|-----|---------|------|---------|

| G 0 9 G | 3/20 (2006.01) | F I | G 0 9 G | 3/20 | 6 7 0 D |

| G 0 9 G | 3/36 (2006.01) |     | G 0 9 G | 3/20 | 6 1 2 G |

|         |                |     | G 0 9 G | 3/36 |         |

請求項の数 4 (全14頁)

(21)出願番号 特願2019-537080(P2019-537080)

(86)(22)出願日 平成30年5月24日(2018.5.24)

(65)公表番号 特表2020-503567(P2020-503567

A)

(43)公表日 令和2年1月30日(2020.1.30)

(86)国際出願番号 PCT/CN2018/088248

(87)国際公開番号 WO2019/011064

(87)国際公開日 平成31年1月17日(2019.1.17)

審査請求日 令和1年7月8日(2019.7.8)

(31)優先権主張番号 201710571690.X

(32)優先日 平成29年7月13日(2017.7.13)

(33)優先権主張国・地域又は機関

中国(CN)

(73)特許権者 516189213

クンシャン ゴー - ビシオノクス オプト

- エレクトロニクス カンパニー リミテ

ッド

Kunshan Go - Visionox

Opto - Electronics C

o., Ltd.

中華人民共和国 215300 ジアンス

- クンシャン ディベロブメント ゾーン

ロントン ロード ナンバー 1 ビルディ

ング 4

Building 4, No. 1, L

ongteng Road, Devel

opment Zone, Kunsha

n, Jiangsu 215300,

最終頁に続く

(54)【発明の名称】 ディスプレイ電源制御方法、装置、記録媒体及び電子機器

**(57)【特許請求の範囲】****【請求項 1】**

駆動チップとスクリーンを含むTFT型ディスプレイに応用されるディスプレイ電源制御方法であって、

前記駆動チップが適当な画像を表示させるよう前記スクリーンを制御するとともに、前記スクリーンが薄膜トランジスタによって画素を制御され、

当該ディスプレイ電源制御方法において、

パワーアップ制御モジュールが起動信号を受信した後、前記駆動チップの出力電圧が異常となる可能性を下げるよう予め規定された規則に従って前記駆動チップの電源をパワーアップさせるように前記パワーアップ制御モジュールが前記駆動チップに含まれる電源管理モジュールへの供給電圧を制御するステップと、

前記駆動チップに含まれる電源管理モジュールへの供給電圧を制御するステップの後、前記駆動チップに対して連続給電するステップと、を含み、

前記駆動チップに含まれる電源管理モジュールへの供給電圧を制御するステップは、前記パワーアップ制御モジュールが起動信号を受信した後、前記駆動チップから出力されるゲート駆動負電圧が異常となる可能性を下げるよう予め規定された規則に従って、第一の期間において、前記駆動チップの電源をパワーアップさせるように前記電源管理モジュールへの供給電圧を第一レベルまで制御するステップと、

前記第一の期間が経過した後の第二の期間において、前記電源管理モジュールへの供給電圧が第一レベルより低い第二レベルまで降下するように前記電源管理モジュールへの供

給電圧を制御するステップと、

前記第二の期間を経過した後、前記電源管理モジュールへの供給電圧が再び第一レベルまで上昇するように前記電源管理モジュールへの供給電圧を制御するステップと、を含むディスプレイ電源制御方法。

**【請求項 2】**

駆動チップとスクリーンを含むTFT型ディスプレイに応用されるディスプレイ電源制御装置であり、前記駆動チップが適当な画像を表示させるよう前記スクリーンを制御するとともに、前記スクリーンが薄膜トランジスタによって画素を制御され、当該ディスプレイ電源制御装置において、

起動信号を受信した後、前記駆動チップの出力電圧が異常となる可能性を下げるよう予め規定された規則に従って前記駆動チップの電源をパワーアップさせるように前記駆動チップに含まれる電源管理モジュールへの供給電圧を制御するパワーアップ制御モジュールと、前記駆動チップに対して連続給電する正常給電モジュールと、を含み、

前記駆動チップは、デジタル回路を含み、

前記電源管理モジュールへの供給電圧を段階的に降下させた後、前記デジタル回路への供給電圧を制御して前記駆動チップをパワーアップさせるディスプレイ電源制御装置。

**【請求項 3】**

電源チップ、前記駆動チップと前記スクリーンを含む電子機器であって、

前記電源チップは、メモリとプロセッサを含み、前記メモリにプログラムが蓄積され、前記プログラムが前記プロセッサで実行されると、請求項1に記載の方法を実行させる電子機器。

**【請求項 4】**

電源チップ、前記駆動チップと前記スクリーンを含むTFT型ディスプレイに応用される記録媒体であって、

前記電源チップに内蔵されたプロセッサにより実行されるプログラムを蓄積し、

当該プログラムは、プロセッサで実行されると、請求項1に記載の方法を実行させるプログラムである記録媒体。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、ディスプレイ技術分野に関し、特にディスプレイ電源の制御方法、装置、記録媒体及び電子機器に関する。

**【背景技術】****【0002】**

TFT (Thin Film Transistor、薄膜トランジスタ)型ディスプレイは、あらゆるノートパソコンやデスクトップパソコンに設置された主な表示装置である。当該型において、それぞれの各画素点が画素点の後に集積された薄膜トランジスタにより駆動されるようになる。TFT型ディスプレイは、一般的に駆動チップ及びスクリーンを含む。さらに、駆動チップが、薄膜トランジスタの動作状態を制御することによりスクリーンに適当な画像を表示させるように作動している。従来のTFT型ディスプレイは、再起動またはスリープ喚起時に画面が真っ暗になってしまう可能性があり、また駆動チップの性能がスクリーンの表示効果に直接に影響するため、駆動チップの性能を改善することは早急に解決すべき問題である。

**【発明の概要】****【発明が解決しようとする課題】****【0003】**

これに鑑みて、TFT型ディスプレイの駆動チップの性能を改善するという課題に対し、ディスプレイ電源の制御方法、装置、記録媒体及び電子機器を提供する必要がある。

**【課題を解決するための手段】****【0004】**

10

20

30

40

50

本願は、駆動チップとスクリーンを含む TFT 型ディスプレイに応用されるディスプレイ電源制御方法を提供する。前記駆動チップが適当な画像を表示させるよう前記スクリーンを制御とともに、前記スクリーンが薄膜トランジスタによって画素を制御され、当該ディスプレイ電源制御方法において、起動信号を受信した後、前記駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御するステップと、前記駆動チップに正常で連続給電するステップと、を含む。

#### 【 0 0 0 5 】

一実施例において、前記駆動チップは電源管理モジュールを含み、さらに、前記起動信号を受信した後前記駆動チップの出力電圧が異常発生される可能性を下げるよう前記駆動チップの電源に予め規定された規則に従ってパワーアップさせるように制御するステップが、起動信号を受信した後、前記駆動チップに出力されたゲート駆動負電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記電源管理モジュールの供給電圧を制御するというステップである。

10

#### 【 0 0 0 6 】

一実施例において、起動信号を受信した後、前記駆動チップに出力されたゲート駆動負電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記電源管理モジュールの供給電圧を制御するステップが、起動信号を受信した後、正常に第一レベルまでにパワーアップさせるように前記電源管理モジュールの供給電圧を制御するステップと、第一の期間を経過した後、電圧が第一レベルより低い第二レベルまで降下するように前記電源管理モジュールの供給電圧を制御するステップと、第二の期間を経過した後、電圧が再び第一レベルまで上昇するように前記電源管理モジュールの供給電圧を制御するステップと、を含む。

20

#### 【 0 0 0 7 】

一実施例において、前記第一レベルは 2 . 5 V ~ 4 . 8 V である。好ましくは、前記第一の期間は 8 ms ~ 12 ms であり、さらに好ましくは、前記第一の期間は 10 ms である。好ましくは、前記第二の期間は 8 ms ~ 12 ms であり、さらに好ましくは、前記第二の期間は 10 ms である。

#### 【 0 0 0 8 】

一実施例において、前記第二レベルは 1 V ~ 2 . 2 V である。

30

#### 【 0 0 0 9 】

一実施例において、前記駆動チップは電源管理モジュールと、デジタル回路とを含み、さらに、前記起動信号を受信した後前記駆動チップの出力電圧が異常発生される可能性を下げるよう前記駆動チップの電源に予め規定された規則に従ってパワーアップさせるように制御するステップが、起動信号を受信した後、前記電源管理モジュールの供給電圧を制御してパワーアップされるステップと、第三の期間を経過した後、前記デジタル回路の供給電圧を制御してパワーアップされるステップと、を含む。

#### 【 0 0 1 0 】

好ましくは、前記第三の期間は 90 ms ~ 110 ms であり、さらに好ましくは、前記第三の期間は 100 ms である。

40

#### 【 0 0 1 1 】

一実施例において、前記第三の期間を経過した後前記デジタル回路の供給電圧を制御してパワーアップされるステップが、前記駆動チップで前記電源管理モジュールの供給電圧を段階的に降下させた後、前記デジタル回路の供給電圧を制御してパワーアップされるというステップである。

#### 【 0 0 1 2 】

好ましくは、前記駆動チップで前記電源管理モジュールの供給電圧を段階的に降下させた後前記デジタル回路の供給電圧を制御してパワーアップされるステップが、前記駆動チップで前記電源管理モジュールの供給電圧を第一電圧まで降下させ、さらに第二電圧まで降下させた後、前記デジタル回路の供給電圧を制御してパワーアップされるというステップ

50

である。ここで、前記第二電圧は電源管理モジュールに用いる基準電圧であり、好ましくは、前記第一電圧は前記電源管理モジュールのチャージポンプにより生成された電圧である。

#### 【0013】

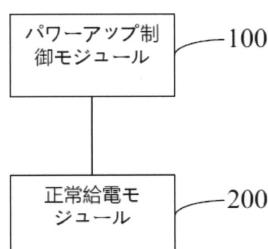

もう一つの発明は、駆動チップとスクリーンを含むTFT型ディスプレイに応用されるディスプレイ電源制御装置であり、前記駆動チップが適当な画像を表示させるよう前記スクリーンを制御とともに、前記スクリーンが薄膜トランジスタによって画素を制御され、当該ディスプレイ電源制御装置において、起動信号を受信した後、前記駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御するパワーアップ制御モジュールと、前記駆動チップに正常で連続給電する正常給電モジュールと、を含む。

10

#### 【0014】

もう一つの発明は、電源チップ、駆動チップとスクリーンを含むTFT型ディスプレイに応用される記録媒体であり、前記記録媒体は前記電源チップ内に設置されて、電源チップに内蔵されたプロセッサにより実行されるプログラムを蓄積し、当該プログラムは、プロセッサで実行されて、起動信号を受信した後、前記駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御するステップと、前記駆動チップに正常で連続給電するステップとを実現させるようプログラムである。

20

#### 【0015】

もう一つの発明は、電源チップ、駆動チップとスクリーンを含む電子機器であって、前記電源チップは、メモリとプロセッサを含み、前記メモリにプログラムが蓄積され、前記プログラムが前記プロセッサで実行されると、起動信号を受信した後、前記駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御するステップと、前記駆動チップに正常で連続給電するステップとを実行させる。

30

#### 【発明の効果】

#### 【0016】

上記ディスプレイ電源制御方法、装置、記録媒体及び電子機器によれば、起動信号を受信した後、駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御する。駆動チップの電源が、駆動チップからスクリーンに出力する電圧の性能を直接に決定するため、さらに電源がパワーアップの際の短時間内に電圧変動がよく発生するから、本願によれば、駆動チップのパワーアップ状況を改善することにより、駆動チップの出力電圧の品質を向上させることができ、よってディスプレイ画面が真っ暗になる可能性を低減しディスプレイの表示性能が向上できる。

40

#### 【図面の簡単な説明】

#### 【0017】

本発明の実施例または従来技術による技術的解決手段をより明らかに説明するために、以下は、実施例または従来技術を記述するのに必要な図面を簡単に説明する。下記の図面は本発明の実施例に過ぎず、当該図面に基づいて他の実施例の図面を得られることは、当業者にとって創造的な労働をしなくてもできる。

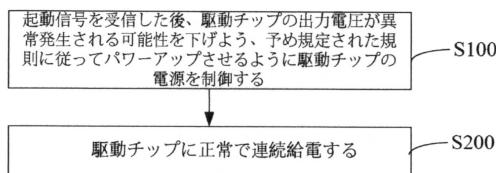

【図1】一実施形態に係るディスプレイ電源制御方法のフローチャートである。

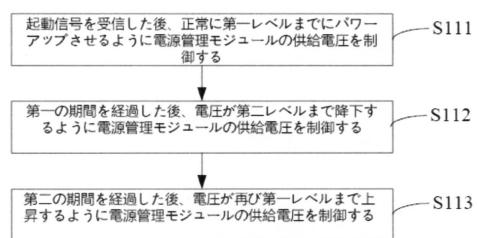

【図2】図1に示す実施形態におけるディスプレイ電源制御方法のステップS100の一つの実施例のフローチャートである。

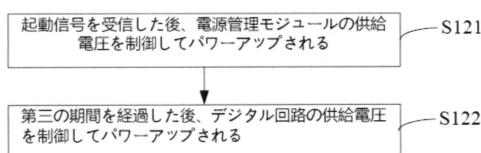

【図3】図1に示す実施形態におけるディスプレイ電源制御方法のステップS100のさらなる実施例のフローチャートである。

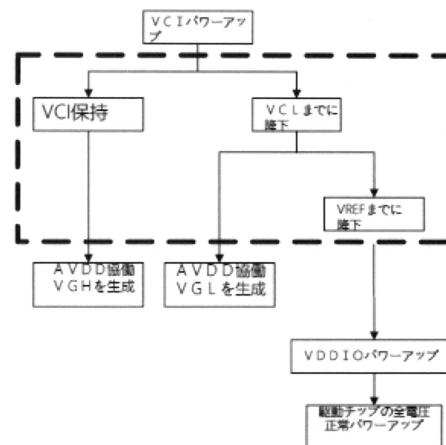

【図4】図3に示す実施例のディスプレイ電源制御方法における駆動チップの具体的なパワーアップ方式のフローチャートである。

【図5】もう一つ実施形態に係るディスプレイ電源制御装置のブロック図である。

50

【図6】図5に示す実施形態におけるディスプレイ電源制御装置のパワーアップ制御モジュールの一つの実施例のブロック図である。

【図7】図5に示す実施形態におけるディスプレイ電源制御装置のパワーアップ制御モジュールのさらなる実施例のブロック図である。

**【発明を実施するための形態】**

**【0018】**

以下、本発明を容易に理解するために、図面を参照しながら本発明をさらに詳しく説明する。図面には、本発明の最適な実施例が示されている。しかし、本発明は様々な形で実現でき、本明細書で記述される実施例に限らない。その一方で、これらの実施例を挙げる目的は、本発明の開示をさらに徹底的かつ完全に理解することである。

10

**【0019】**

特に定義しない限り、本明細書中にて使用されるすべての技術用語および科学用語は、本考案の技術分野の当業者一般に理解されている意味とする。本明細書で使用される用語は、具体的な実施形態を説明するためのものであり、本発明を限定するものではない。本明細書で使用された用語「及び／又は」は、挙げられた一或いは複数の関連項目の任意な、あらゆる組み合わせを含む。

**【0020】**

本発明の実施形態は、TFT型ディスプレイに応用されるディスプレイ電源制御方法を提供する。TFT型ディスプレイは電源チップ、駆動チップ及びスクリーンを含む。スクリーンは薄膜トランジスタによって画素を制御される。スクリーンは、例えば画素マトリクス、水平駆動回路、及び垂直駆動回路を含む。画素マトリクスは、複数の画素及び複数の画素駆動回路を含み、各画素がそれぞれ対応する一つの画素駆動回路によって制御される。水平駆動回路は、水平（走査）アドレスバスを介して各画素駆動回路に走査信号を送信する。垂直駆動回路は、垂直（データ）アドレスバスを介して各画素駆動回路にデータ信号を送信する。駆動チップは適当な画像を表示させるようスクリーンを制御する。駆動チップは水平駆動回路、垂直駆動回路をそれぞれに電気接続され、ディスプレイ全体のデータ処理、転送、及び制御信号の発信などの機能を有する。駆動チップは、例えばMCU（あるいはFPGA）及び周辺回路によって構成される。電源チップ（Power I C）は駆動チップに給電することに用いられる。本実施形態に係るディスプレイ電源制御方法は電源チップで実行してもよい。

20

**【0021】**

図1に示すように、本実施形態に係るディスプレイ電源制御方法は以下のステップを含む。

**【0022】**

ステップS100において、起動信号を受信した後、駆動チップの出力電圧が異常発生される可能性を下げるよう、予め規定された規則に従ってパワーアップさせるように駆動チップの電源を制御する。

**【0023】**

ここで、起動信号というのは、例えばパソコンの起動またはスリープ喚起際に生成された信号である。駆動チップの電源とは、電源チップから駆動チップに入力される電力ソースである。駆動チップが出力する電圧は、例えばゲート駆動正電圧VGH、ゲート駆動負電圧VGLなどを含む。駆動チップの出力電圧に異常が発生すると、スクリーンの薄膜トランジスタが動作異常されるまで引き起こされて、スクリーン画面が真っ暗になってしまう。

30

**【0024】**

駆動チップは、例えばデジタル回路及びアナログ回路を含む。

**【0025】**

ここで、デジタル回路は例えば入出力インターフェース及びタイミング制御モジュール（即ち、TCONモジュール）を含む。入出力インターフェースは高速パラレルバスインターフェース及びシリアル・ペリフェラル・インタフェースを有する。タイミング制御モジュールは、例えば、SPIインターフェース及びRGBインターフェースからのデータを処

40

50

理するとともに、駆動チップにおいて一部モジュールのタイミング制御を行うなどの機能を備える。

#### 【 0 0 2 6 】

アナログ回路は、例えば電源管理モジュール及び画素駆動モジュールを含む。ここで、電源管理モジュールが駆動チップにおける部件及びディスプレイの走査信号に電力を提供し、電源管理モジュールが例えば基準電圧源、チャージポンプ、LDO ( low drop out regulator、低損失レギュレータ ) を含む。画素駆動モジュールは例えばソース駆動モジュール、ゲート駆動モジュール及びガンマ補正モジュールを含む。ここで、ソース駆動モジュールがスクリーンの垂直駆動回路に階調電圧を出力する。ゲート駆動モジュールが水平駆動回路に走査信号（例えばゲート駆動正電圧 VGH、ゲート駆動負電圧 VGL など）を出力する。ガンマ補正モジュールがソース駆動モジュールに階調電圧を提供し、ガンマ曲線を調整することによりバイナリコードと階調電圧との対応関係を変化できる。

#### 【 0 0 2 7 】

駆動チップにおいて、駆動チップの電源が、例えば上記電源管理モジュールの供給電圧 VCI 及びデジタル回路の供給電圧を含む。パワーアップの際に電圧がバラツキしやすいため、駆動チップの出力電圧が異常発生され、ディスプレイ画面が真っ暗になる可能性がある。そのため、駆動チップの電源パワーアップ方式を改善することで、スクリーン画面が真っ暗になる可能性が低減させられる。

#### 【 0 0 2 8 】

ステップ S200 において、駆動チップに正常で連続給電する。

10

#### 【 0 0 2 9 】

ステップ S100 が実行された後、電源チップは通常の需要に応じて駆動チップに給電し、TFT 型ディスプレイを正常に動作させる。

#### 【 0 0 3 0 】

以上説明したように、上記実施形態に係るディスプレイ電源制御方法において、駆動チップの電源が、駆動チップからスクリーンに出力する電圧の性能を直接に決定するため、さらにパワーアップ際の短時間内に電圧変動がよく発生するから、本願によれば、駆動チップのパワーアップ状況を改善することにより、駆動チップの出力電圧の品質を向上させることができ、よってディスプレイ画面が真っ暗になる可能性を低減しディスプレイの表示性能が向上できる。

30

#### 【 0 0 3 1 】

一実施例において、上記駆動チップは電源管理モジュールを含む。さらに、上記ステップ S100 が、起動信号を受信した後、駆動チップに出力されたゲート駆動負電圧 VGL が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように電源管理モジュールの供給電圧を制御するというステップである。

#### 【 0 0 3 2 】

ここで、ゲート駆動負電圧 VGL が電源管理モジュールの供給電圧 VCI は降下されることにより得られる。ゲート駆動負電圧 VGL が異常上昇するとは、ゲート駆動負電圧 VGL が正常な電圧範囲より高いことを意味する。例えば、正常にゲート駆動負電圧 VGL の範囲が ( -7V, 0V ) である場合、ゲート駆動負電圧 VGL が 0.6V まで上昇されたと、異常上昇であると考えられる。

40

#### 【 0 0 3 3 】

従来の TFT 型ディスプレイにおいて、パワーアップの際に、電源管理モジュールの供給電圧 VCI は正常範囲を超えた電圧変動が発生される可能性があり、よってゲート駆動負電圧 VGL が異常上昇される場合がある。この時、駆動チップに Latch-up 現象（即ち、駆動チップの出力電圧が高すぎて薄膜トランジスタの動作が異常になる）が発生される。ゲート駆動負電圧 VGL は薄膜トランジスタの動作を直接的に制御するため、ゲート駆動負電圧 VGL に異常が発生すると、薄膜トランジスタが導通できず、画面が真っ暗になってしまう。本実施例において、電源管理モジュールの供給電圧 VCI のパワーアッ

50

の状況を改善する（例えば、バラツキ電流を低減する）ことにより、ゲート駆動負電圧  $V_{GL}$  の値を低下させることができ、ゲート駆動負電圧  $V_{GL}$  が高すぎる可能性を低減できる。

#### 【0034】

具体的には、ステップ S100 の上記具体的な実施形態は、図 2 に示すように、以下のステップを含むことができる。

#### 【0035】

ステップ S111において、起動信号を受信した後、正常に第一レベルまでにパワーアップさせるように電源管理モジュールの供給電圧  $V_{CI}$  を制御する。

#### 【0036】

ここで、第一レベルは電源管理モジュールの正常な供給電圧であってもよく、例えば 2.5 V ~ 4.8 V である。好適には、第一レベルは 3.3 V である。

#### 【0037】

ステップ S112において、第一の期間を経過した後、電圧が第一レベルより低い第二レベルまで降下するように電源管理モジュールの供給電圧  $V_{CI}$  を制御する。

#### 【0038】

ここで、第一の期間が電源チップの Transient Response (過渡応答) の特性とかかる。Transient Response の時間が短いほど、第一の期間は長くなる。好ましくは、第一の期間は 8 ms ~ 12 ms であり、例えば 10 ms である。第二レベルとは、少なくともスクリーン画面が真っ暗にならないゲート駆動負電圧  $V_{GL}$  を保証できる大きさである。第二レベルは例えば 1 V ~ 2.2 V である。好適には、第二レベルは例えば 1.8 V である。この場合に、対応するゲート駆動負電圧  $V_{GL}$  は 0.4 V 以下になる。

#### 【0039】

具体的には、電源チップはチャージポンプや他の電圧降下機能を有する回路により第一レベルが第二レベルまでに降下させて、ステップ S112 で電源管理モジュールに第二レベルを提供することができる。

#### 【0040】

ステップ S113において、第二の期間を経過した後、電圧が再び第一レベルまで上昇するように電源管理モジュールの供給電圧  $V_{CI}$  を制御する。

#### 【0041】

ここで、第二の期間が電源チップの Transient Response (過渡応答) の特性とかかる。Transient Response の時間が短いほど、第二の期間は長くなる。好ましくは、第二の期間は 8 ms ~ 12 ms であり、例えば 10 ms である。

#### 【0042】

具体的には、同じく、電源チップはチャージポンプや他の電圧降下機能を有する回路により第二レベルが第一レベルまでに上昇させて、ステップ S113 で電源管理モジュールに第一レベルを提供することができる。

#### 【0043】

図 2 に示す上記具体的な実施形態において、正常にパワーアップされた後に、電源管理モジュールの供給電圧  $V_{CI}$  を降下させて Latch-up 電流を降下させるより、電源管理モジュールの供給電圧  $V_{CI}$  が第二レベルまで降下され、Latch-up 現象を解除する。その後、電源管理モジュールの供給電圧  $V_{CI}$  を第一レベルまで上昇させば、駆動チップを正常に動作させることができる。

#### 【0044】

よって、上記具体的な実現形態は電源管理モジュールの供給電圧  $V_{CI}$  のパワーアップ方式を最適化する（即ち、ハイレベル - ローレベル - ハイレベルというパターンを採用する）ことにより、スクリーン画面が真っ暗になる可能性が低減させられる。

#### 【0045】

10

20

30

40

50

別の実施例において、上記ステップ S 1 0 0 が別の方に変えられて駆動チップの出力電圧が異常発生される可能性を下げられる。上記駆動チップは上記電源管理モジュール及び上記デジタル回路を含む。また、上記ステップ S 1 0 0 は、図 3 に示すように、具体的に以下のステップを含む。

#### 【 0 0 4 6 】

ステップ S 1 2 1 において、起動信号を受信した後、電源管理モジュールの供給電圧 V C I を制御してパワーアップされる。

#### 【 0 0 4 7 】

ステップ S 1 2 2 において、第三の期間を経過した後、デジタル回路の供給電圧を制御してパワーアップされる。

#### 【 0 0 4 8 】

この実施例において、電源管理モジュールの供給電圧 V C I 及びデジタル回路の供給電圧のパワーアップ順番を、まず電源管理モジュールの供給電圧 V C I を制御してパワーアップされた後、第三の期間を経過してデジタル回路の供給電圧を制御してパワーアップされようとして調整した。これにより、デジタル回路は V C I 回路（例えば電源管理モジュール内の電圧上昇・降下回路）より干渉（例えば電磁気干渉）されることを避けられ、デジタル回路の正常動作を保証できる。デジタル回路は駆動チップの主な制御回路であるため、駆動チップの動作の信頼性を向上させ、駆動チップの出力電圧が異常発生される可能性を下げられ、ディスプレイ画面が真っ暗になる可能性を低減される。具体的には、第三の期間は 9 0 m s ~ 1 1 0 m s であり、例えば 1 0 0 m s である。

#### 【 0 0 4 9 】

具体的には、デジタル回路の供給電圧は、例えば入出力インターフェースの電圧 V D D I O である。また、タイミング制御モジュールの供給電圧 D V D D は、入出力インターフェースの電圧 V D D I O を降下させて得る。この場合、入出力インターフェースの電圧 V D D I O が後でパワーアップされる。干渉がない場合、タイミング制御モジュールの供給電圧が所定の電圧閾値（例えば 1 . 4 V ）以下になることが確保でき、タイミング制御モジュールの正常動作が確保される。

#### 【 0 0 5 0 】

具体的には、上記ステップ S 1 2 2 が、駆動チップで電源管理モジュールの供給電圧 V C I を段階的に降下させた後、デジタル回路の供給電圧を制御してパワーアップされるというステップである。

#### 【 0 0 5 1 】

ここで、電源管理モジュールの供給電圧 V C I を段階的に降下させると、電源管理モジュールの供給電圧 V C I を順次で段階的に一つまたは一つ以上の電圧に降下させることである。また、電源管理モジュールの供給電圧 V C I の電圧降下過程全体にかかる時間が上記第三の期間に達した後、デジタル回路の供給電圧を制御してパワーアップされる。具体的には、電源管理モジュールの供給電圧の電圧降下はチャージポンプまたは他の電圧降下機能を有する回路で実現ができる。

#### 【 0 0 5 2 】

具体的には、駆動チップで電源管理モジュールの供給電圧 V C I を段階的に降下させた後デジタル回路の供給電圧を制御してパワーアップされる上記ステップが、駆動チップで電源管理モジュールの供給電圧 V C I を第一電圧まで降下させ、さらに第二電圧まで降下させた後、デジタル回路の供給電圧を制御してパワーアップされるというステップである。ここで、第二電圧は、例えば電源管理モジュールに用いる基準電圧 V R E F である。

#### 【 0 0 5 3 】

ここで、電源管理モジュールの供給電圧 V C I を第一電圧まで降下させてさらに第二電圧まで降下させる過程にかかる時間は、上記第三の期間である。例えば、駆動チップ内のチャージポンプの立ち上がりエッジ、立ち下がりエッジの持続期間、あるいはタイミング制御モジュールが同時に実行する指令数を調整するなどにより、電源管理モジュールの供給電圧 V C I を第一電圧まで降下させてさらに第一電圧を第二電圧まで降下させる過程にか

10

20

30

40

50

かる時間が上記第三の期間になるように制御する。

#### 【0054】

具体的には、第一電圧はVCL、即ち電源管理モジュールにおいてチャージポンプが生成された電圧である。好適には、電源管理モジュールの供給電圧VC1がチャージポンプで第一電圧まで降下させ、さらに第二電圧まで降下させることができる。

#### 【0055】

さらに、図3に示す実施例による駆動チップにおける各電圧のパワーアップ状況は図4に示される。ここで、電源管理モジュールの供給電圧VC1がパワーアップされた後、電源管理モジュールの供給電圧VC1が自身の電圧を保持するとともに、電圧AVDD（即ち、ガンマ補正モジュールと電源管理モジュールにおける電圧上昇・降下回路の供給電圧）と協働し、チャージポンプや他の電圧降下機能を有する回路で昇圧させ、ゲート駆動正電圧VGHを生成する。VGHは、例えばAVDD+VC1、2AVDD、2AVDD+VC1または3AVDDである。一方、電源管理モジュールの供給電圧VC1が、チャージポンプやその他の電圧降下機能を有する回路により第一電圧VCLまでに降下される。ここで、電源管理モジュールの供給電圧VC1が自身の電圧を保持するという手順と、電源管理モジュールの供給電圧VC1が第一電圧まで降下されるという手順が同時に行われてもよい。電源管理モジュールの供給電圧VC1を第一電圧まで降下させた後、第一電圧が、電圧AVDDの協働でゲート駆動負電圧VGLを生成するように電圧降下される一方、さらに降下されて第二電圧（例えば上記VREF）が得られる。図4において、破線ブロック内に示されたように、VC1パワーアップされるからVREFまでに降下するという期間は、上述した第三の期間である。VREFまでに降下した後（即ち、第三の期間を経過した後）、デジタル回路の供給電圧がパワーアップされる。

10

20

30

#### 【0056】

なお、図1～図3は本発明の実施例に係る方法のフローチャートである。理解できるように、図1～図3のフローチャートにおける各ステップは、矢印の方向に従って順次示されているが、必ずしも矢印の示す順番で実行されなくてもよい。本明細書において明示的な説明がない限り、これらのステップが厳密な順番に限定されず、他の順番で実行されることができる。また、図1～図3における少なくとも一部のステップは複数のサブステップまたは複数の段階を含んでもよく、これらのサブステップまたは段階は同じ時点で実行されなくともよく、異なる時点で実行されてもよい。また、図1～図3における少なくとも一部のステップは、順次実行されなくともよく、他のステップまたは他のステップのサブステップまたは段階の少なくとも一部と順番または交互に実行されてもよい。

#### 【0057】

本発明の他の実施形態は、TFT型ディスプレイに応用されるディスプレイ電源制御装置を提供する。前記TFT型ディスプレイは駆動チップ及びスクリーンを含む。前記駆動チップが適当な画像を表示させるよう前記スクリーンを制御するとともに、前記スクリーンが薄膜トランジスタによって画素を制御される。ディスプレイ電源制御装置は、図5に示すように以下部品を含む。

#### 【0058】

起動信号を受信した後、前記駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御するパワーアップ制御モジュール100。

40

#### 【0059】

前記駆動チップに正常で連続給電する正常給電モジュール200。

#### 【0060】

一実施例において、前記駆動チップは電源管理モジュールを含む。また、起動信号を受信した後、パワーアップ制御モジュール100は、前記駆動チップに出力されたゲート駆動負電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記電源管理モジュールの供給電圧を制御する。

#### 【0061】

50

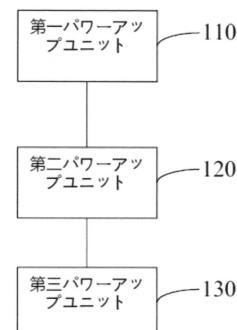

一実施例において、パワーアップ制御モジュール 100 は、図 6 に示すように、以下部品を含む。

**【 0 0 6 2 】**

起動信号を受信した後、正常に第一レベルまでにパワーアップさせるように前記電源管理モジュールの供給電圧を制御する第一パワーアップユニット 110。

**【 0 0 6 3 】**

第一の期間を経過した後、電圧が第一レベルより低い第二レベルまで降下するように前記電源管理モジュールの供給電圧を制御する第二パワーアップユニット 120。

**【 0 0 6 4 】**

第二の期間を経過した後、電圧が再び第一レベルまで上昇するように前記電源管理モジュールの供給電圧を制御する第三パワーアップユニット 130。 10

**【 0 0 6 5 】**

一実施例において、前記第一レベルは 2.5V ~ 4.8V である。好ましくは、前記第一の期間は 8ms ~ 12ms であり、さらに好ましくは、前記第一の期間は 10ms である。好ましくは、前記第二の期間は 8ms ~ 12ms であり、さらに好ましくは、前記第二の期間は 10ms である。一実施例において、前記第二レベルは 1V ~ 2.2V である。

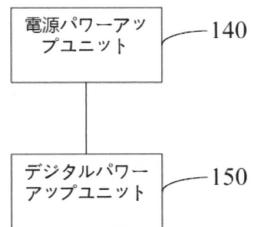

**【 0 0 6 6 】**

一実施例において、前記駆動チップは電源管理モジュール及びデジタル回路を含む。また、パワーアップ制御モジュール 100 は、図 7 に示すように、以下部品を含む。

**【 0 0 6 7 】**

起動信号を受信した後、前記電源管理モジュールの供給電圧を制御してパワーアップされる電源パワーアップユニット 140。 20

**【 0 0 6 8 】**

第三の期間を経過した後、前記デジタル回路の供給電圧を制御してパワーアップされるデジタルパワーアップユニット 150。前記第三の期間は 90ms ~ 110ms である。好ましくは、前記第三の期間は 100ms である。

**【 0 0 6 9 】**

一実施例において、デジタルパワーアップユニット 150 は、前記駆動チップで前記電源管理モジュールの供給電圧を段階的に降下させた後、前記デジタル回路の供給電圧を制御してパワーアップされる。好ましくは、デジタルパワーアップユニット 150 は、前記駆動チップで前記電源管理モジュールの供給電圧を第一電圧まで降下させ、さらに第二電圧まで降下させた後、前記デジタル回路の供給電圧を制御してパワーアップされる。ここで、前記第二電圧は前記電源管理モジュールに用いる基準電圧である。好ましくは、前記第一電圧は前記電源管理モジュールのチャージポンプにより生成された電圧である。 30

**【 0 0 7 0 】**

なお、本実施形態に係るディスプレイ電源制御装置は上記実施形態におけるディスプレイ電源制御方法に対応するため、ここでは余計な説明を省略する。

**【 0 0 7 1 】**

さらに一つの実施形態は記録媒体を提供する。記録媒体は磁気ディスク、光ディスク、読み出し専用メモリ (Read-Only Memory、ROM) 等である。当該記録媒体は、TFT 型ディスプレイに応用される。前記 TFT 型ディスプレイは電源チップ、駆動チップ及びスクリーンを含む。前記記録媒体は前記電源チップ内に設置されて、電源チップに内蔵されたプロセッサにより実行されるプログラムを蓄積し、当該プログラムは、プロセッサで実行されて、起動信号を受信した後、前記駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御するステップと、前記駆動チップに正常で連続給電するステップとを実現させるようプログラムである。 40

**【 0 0 7 2 】**

なお、本実施形態においてプロセッサで実行される手順は上記実施形態におけるディスプレイ電源制御方法に対応するため、ここでは余計な説明を省略する。

10

20

30

40

50

**【 0 0 7 3 】**

もう一つの実施形態は電子機器（例えば、携帯電話、コンピュータなど）を提供する。該電子機器は電源チップ、駆動チップ及びスクリーンを含む。前記電源チップは、メモリとプロセッサを含み、前記メモリにプログラムが蓄積され、前記プログラムが前記プロセッサで実行されると、起動信号を受信した後、前記駆動チップの出力電圧が異常発生される可能性を下げるよう予め規定された規則に従ってパワーアップさせるように前記駆動チップの電源を制御するステップと、前記駆動チップに正常で連続給電するステップとを実行させる。

**【 0 0 7 4 】**

なお、本実施形態においてプロセッサで実行される手順は上記実施形態におけるディスプレイ電源制御方法に対応するため、ここでは余計な説明を省略する。

10

**【 0 0 7 5 】**

上述した実施例の各技術的特徴は任意に組み合わせができる。記述の簡潔化のために、上述した実施例における各技術的特徴のあらゆる組合せについて説明していないが、これらの技術的特徴の組合せは矛盾しない限り、本明細書に記述されている範囲内であると考えられるべきである。

**【 0 0 7 6 】**

上述した実施例は、本発明のいくつかの実施形態を示したものにすぎず、その記述が具体的かつ詳細であるが、本発明の範囲を限定するものと解釈されるべきではない。なお、当業者にとって、本発明の趣旨から逸脱しないかぎり、若干の変形および改良を行うことができ、これらもすべて本発明の保護範囲内にある。本発明の保護範囲は、特許請求の範囲に準ずるべきである。

20

30

40

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

20

【図 5】

【図 6】

30

40

50

【図7】

10

20

30

40

50

---

フロントページの続き

C h i n a

(74)代理人 110001210

特許業務法人 Y K I 国際特許事務所

(72)発明者 ワン ユキン

中華人民共和国 ジアンスー クンシャン ディベロプメント ゾーン ロントン ロード ナンバー

1 ビルディング 4

(72)発明者 ワン ジエン

中華人民共和国 ジアンスー クンシャン ディベロプメント ゾーン ロントン ロード ナンバー

1 ビルディング 4

(72)発明者 ジヤン シャオバオ

中華人民共和国 ジアンスー クンシャン ディベロプメント ゾーン ロントン ロード ナンバー

1 ビルディング 4

(72)発明者 ゲ ミンウェイ

中華人民共和国 ジアンスー クンシャン ディベロプメント ゾーン ロントン ロード ナンバー

1 ビルディング 4

審査官 斎藤 厚志

(56)参考文献 米国特許出願公開第 2008 / 0094386 ( U S , A 1 )

特開 2005 - 091636 ( J P , A )

特開 2000 - 122028 ( J P , A )

中国特許出願公開第 106847215 ( C N , A )

特開 2005 - 062618 ( J P , A )

(58)調査した分野 (Int.Cl., DB名)

G 09 G 3 / 20

G 09 G 3 / 36