(12) 发明专利申请

(10) 申请公布号 CN 118016687 A

(43) 申请公布日 2024.05.10

(21) 申请号 202311456805.2

(22) 申请日 2023.11.03

(30) 优先权数据

2022-179333 2022.11.09 JP

(71) 申请人 三菱电机株式会社

地址 日本东京

(72) 发明人 西康一 新田哲也

(74) 专利代理机构 北京天昊联合知识产权代理

有限公司 11112

专利代理人 何立波 张天舒

(51) Int.CI.

H01L 29/06 (2006.01)

H01L 29/36 (2006.01)

权利要求书1页 说明书6页 附图6页

(54) 发明名称

半导体装置

(57) 摘要

一边将在VLD构造的电场缓和层之上配置的电极的宽度保持得宽一边提高半导体装置的耐压。在构成半导体装置的半导体基板(50)形成有第1导电型的漂移层(1),在末端区域(20)的半导体基板的表层部形成有杂质浓度朝向半导体基板的外侧减少的第2导电型的阱层(2)和作为沟道截断层的第1导电型的发射极层(3)。末端区域具有:缓和区域(21),阱层形成得深;RESURF区域(22),其位于缓和区域的外侧,阱层形成得浅;沟道截断区域(23),其形成有沟道截断层。在缓和区域之上形成栅极配线电极(11),在沟道截断区域之上形成沟道截断电极(13)。栅极配线电极及沟道截断电极被将它们之间电连接的半绝缘膜(14)覆盖。

## 1. 一种半导体装置,其具有:

半导体基板,其形成有第1导电型的漂移层;

有源区域,其在所述半导体基板形成有半导体元件;

末端区域,其是所述半导体基板的所述有源区域的外侧的区域;

第2导电型的阱层,其形成于所述末端区域的所述半导体基板的表层部,第2导电型的杂质浓度朝向所述半导体基板的外侧而减少;以及

第1导电型的沟道截断层,其形成于比所述阱层更靠外侧的所述半导体基板的表层部,

所述末端区域具有:

缓和区域,其与所述有源区域相邻,形成有所述阱层;

RESURF区域,其位于所述缓和区域的外侧,在该RESURF区域,所述阱层形成得比所述缓和区域浅,其中,RESURF是指降低表面场;

沟道截断区域,其位于所述RESURF区域的外侧,形成有所述沟道截断层;

电极,其隔着层间绝缘膜而形成于所述缓和区域之上;

沟道截断电极,其与所述沟道截断层连接;以及

半绝缘膜,其将所述电极及所述沟道截断电极覆盖,将所述电极与所述沟道截断电极之间电连接。

## 2. 根据权利要求1所述的半导体装置,其中,

所述末端区域还具有在所述RESURF区域之上隔着所述层间绝缘膜而形成的至少1个场板电极,

所述半绝缘膜将所述电极、所述场板电极及所述沟道截断电极覆盖,将所述电极、所述场板电极及所述沟道截断电极之间电连接。

## 3. 根据权利要求2所述的半导体装置,其中,

所述电极、所述场板电极及所述沟道截断电极的间隔是均一的。

## 4. 根据权利要求2或3所述的半导体装置,其中,

所述场板电极为多个,多个所述场板电极的宽度是均一的。

## 5. 根据权利要求2至4中任一项所述的半导体装置,其中,

所述电极、所述场板电极及所述沟道截断电极由相同的导电体材料形成。

## 6. 根据权利要求1至5中任一项所述的半导体装置,其中,

所述电极的外端部伸出至所述RESURF区域,

所述电极向所述RESURF区域伸出的长度大于或等于0μm且小于或等于30μm。

## 7. 根据权利要求1至6中任一项所述的半导体装置,其中,

所述沟道截断电极的内端部伸出至所述RESURF区域,

所述沟道截断电极向所述RESURF区域伸出的长度大于或等于0μm且小于或等于30μm。

## 8. 根据权利要求1至7中任一项所述的半导体装置,其中,

所述半绝缘膜的电阻率小于或等于 $1 \times 10^{12} \Omega \cdot \text{cm}$ 。

## 9. 根据权利要求1至8中任一项所述的半导体装置,其中,

还具有在所述半绝缘膜之上形成的绝缘膜。

## 10. 根据权利要求1至9中任一项所述的半导体装置,其中,

还具有以将所述半绝缘膜的上表面的凹凸填埋的方式覆盖所述半绝缘膜的表面保护膜。

## 半导体装置

### 技术领域

[0001] 本发明涉及半导体装置。

### 背景技术

[0002] 作为纵型半导体元件的末端构造,已知使电场缓和层的杂质浓度朝向半导体基板的外侧而减少的VLD(Variation of Lateral Doping)构造(例如下述的专利文献1)。

[0003] 专利文献1:国际公开第2015/104900号

[0004] 在专利文献1中,提出了在VLD构造之上设置场板电极,使场板电极的宽度(W)与间隔(D)的比率(W/D)朝向半导体基板的外侧而减少。该构造能够使场板电极的电位分布接近电场缓和层的电位分布,提高半导体装置的耐压。但是,在该构造中,在半导体基板的周缘部,场板电极宽度变窄,因此容易产生由应力导致的场板电极的滑动等,成为导致可靠性下降的要因。

### 发明内容

[0005] 本发明就是为了解决以上这样的课题而提出的,其目的在于,一边将在VLD构造的电场缓和层之上配置的电极的宽度保持得宽,一边提高半导体装置的耐压。

[0006] 本发明涉及的半导体装置具有:半导体基板,其形成有第1导电型的漂移层;有源区域,其在所述半导体基板形成有半导体元件;末端区域,其是所述半导体基板的所述有源区域的外侧的区域;第2导电型的阱层,其形成于所述末端区域的所述半导体基板的表层部,第2导电型的杂质浓度朝向所述半导体基板的外侧而减少;以及第1导电型的沟道截断层,其形成于比所述阱层更靠外侧的所述半导体基板的表层部,所述末端区域具有:缓和区域,其与所述有源区域相邻,形成有所述阱层;RESURF区域,其位于所述缓和区域的外侧,在该RESURF区域,所述阱层形成得比所述缓和区域浅,其中,RESURF是指降低表面场;沟道截断区域,其位于所述RESURF区域的外侧,形成有所述沟道截断层;电极,其隔着层间绝缘膜而形成于所述缓和区域之上;沟道截断电极,其与所述沟道截断层连接;以及半绝缘膜,其将所述电极及所述沟道截断电极覆盖,将所述电极与所述沟道截断电极之间电连接。

[0007] 发明的效果

[0008] 根据本发明,配线电极与沟道截断电极之间通过半绝缘膜而电连接,由此,配线电极与沟道截断电极之间的电位分布接近阱层的电位分布,半导体装置的耐压提高。另外,由于不需要在阱层之上设置宽度小的电极,因此,能够抑制由应力导致的电极的滑动等的产生,还能够有助于可靠性的提高。

### 附图说明

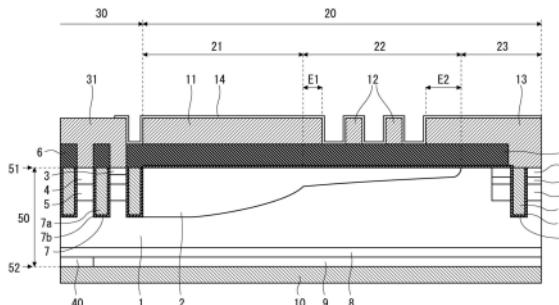

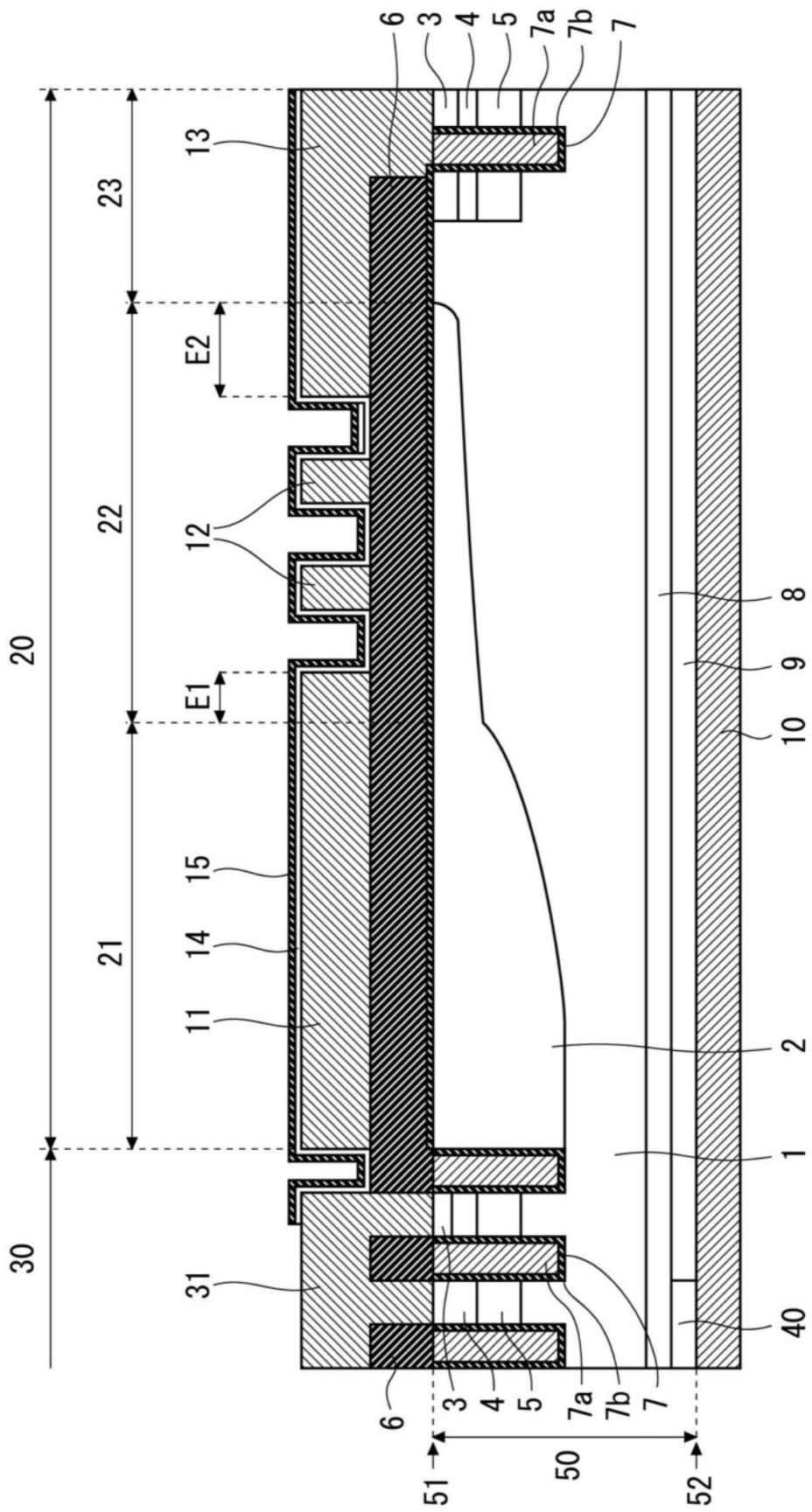

[0009] 图1是实施方式1涉及的半导体装置的剖视图。

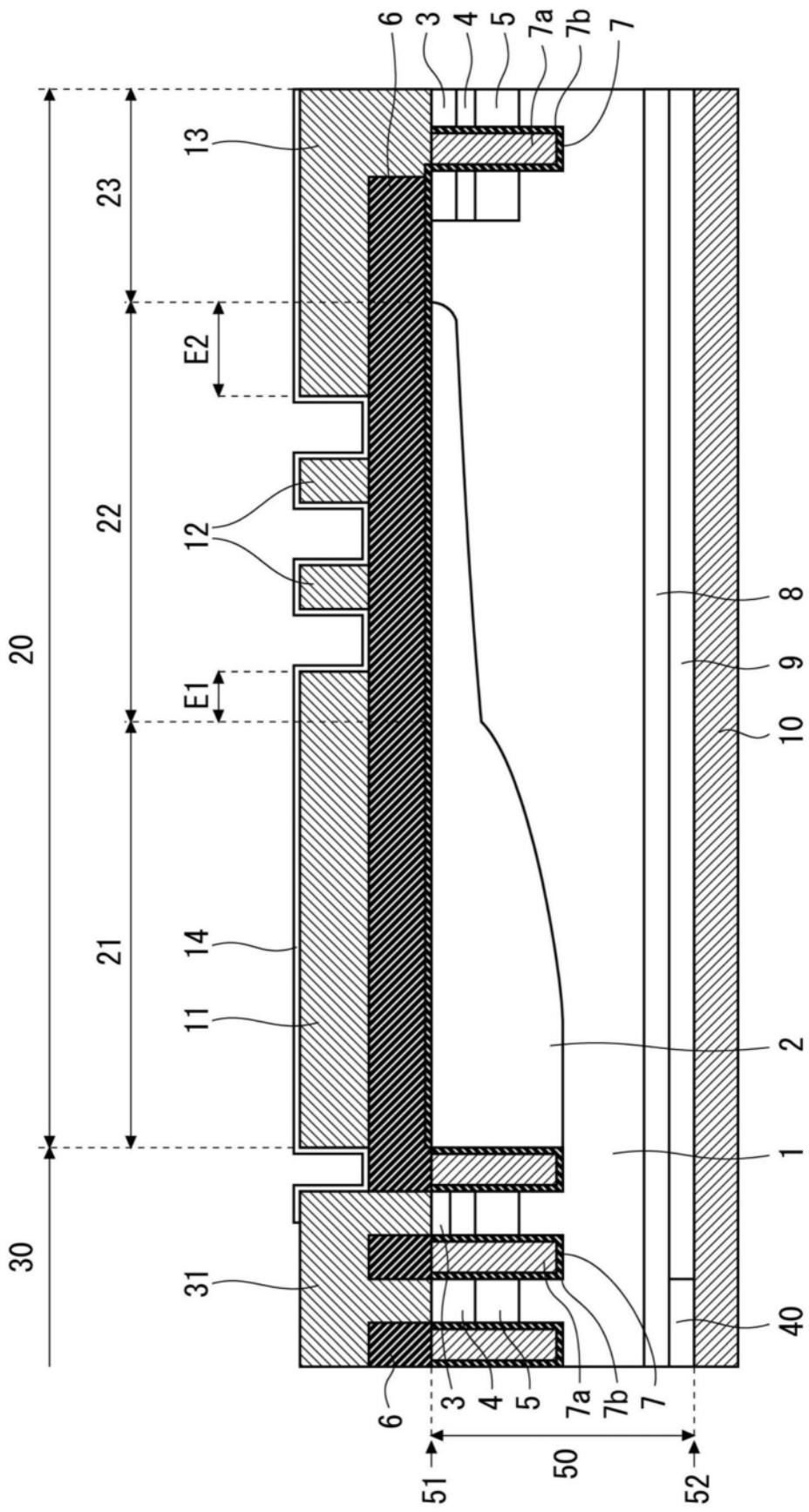

[0010] 图2是表示栅极配线向RESURF(降低表面场)区域伸出的长度(E1)与半导体装置的耐压之间的关系的曲线。

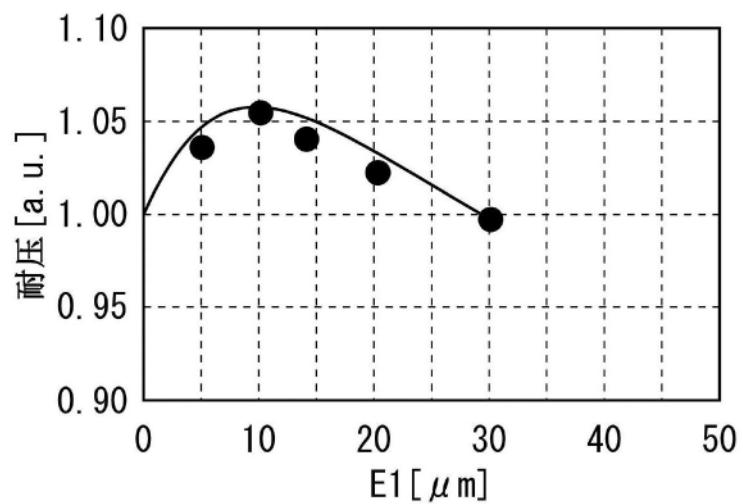

[0011] 图3是表示沟道截断电极向RESURF区域伸出的长度(E2)与半导体装置的耐压之间的关系的曲线。

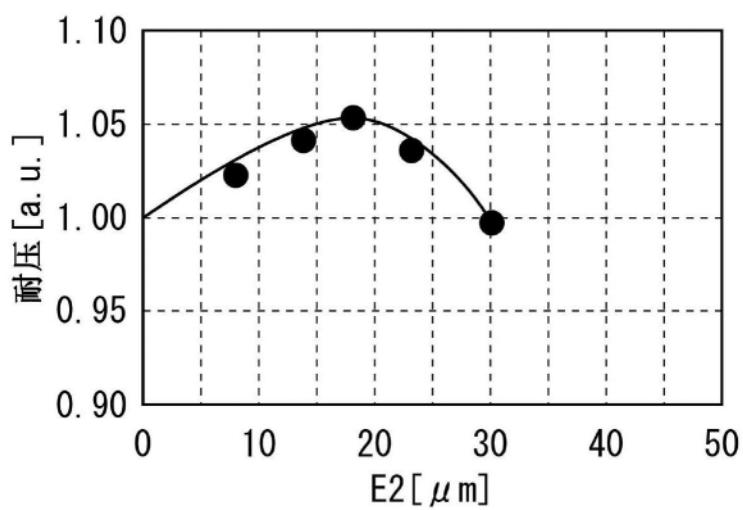

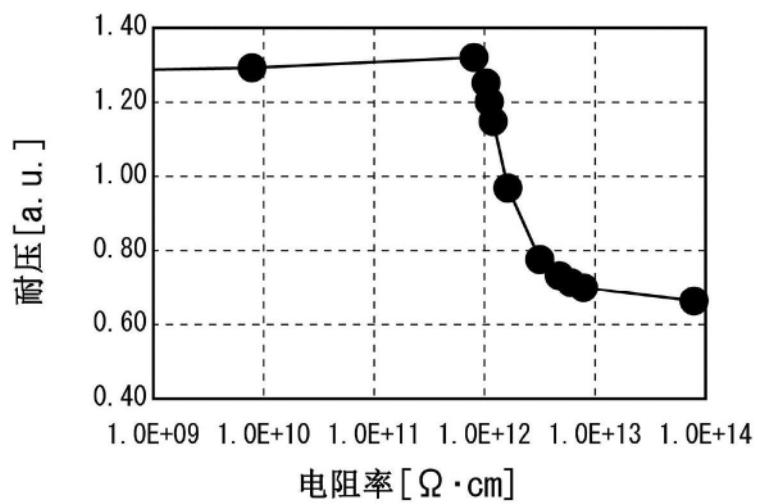

[0012] 图4是表示半绝缘膜的电阻率与半导体装置的耐压之间的关系的曲线。

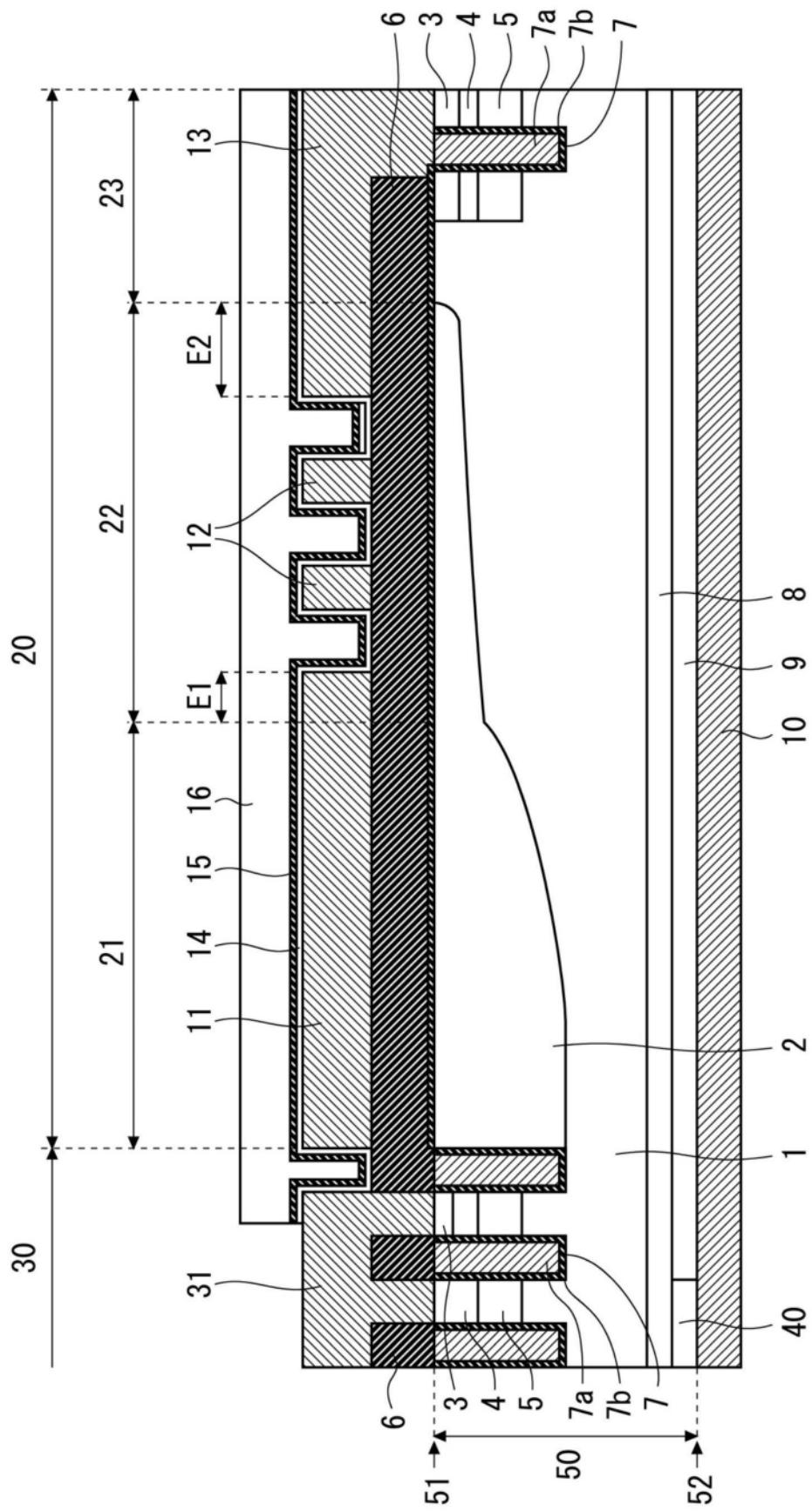

[0013] 图5是实施方式5涉及的半导体装置的剖视图。

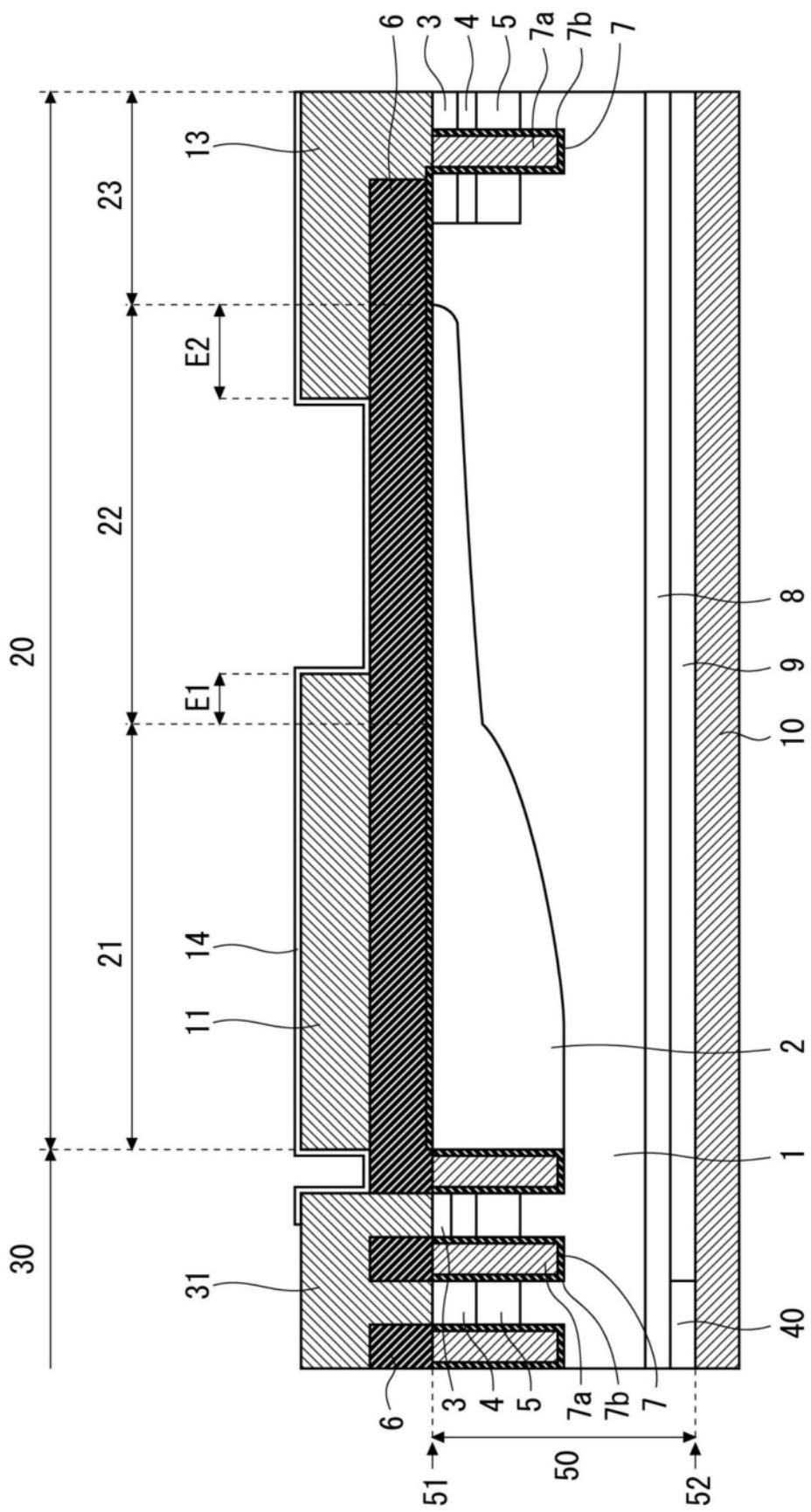

[0014] 图6是实施方式6涉及的半导体装置的剖视图。

[0015] 图7是实施方式7涉及的半导体装置的剖视图。

## 具体实施方式

[0016] <实施方式1>

[0017] 图1是表示实施方式1涉及的半导体装置的剖视图。在本实施方式中,作为半导体装置,示出由1个芯片构成了IGBT(Insulated Gate Bipolar Transistor)和FWD(Free Wheeling Diode)的RC-IGBT(Reverse Conducting IGBT),但半导体装置例如也可以是MOSFET(Metal Oxide Semiconductor Field Effect Transistor)、SBD(Schottky Barrier Diode)等。另外,在以下的说明中,将第1导电型设为N型、将第2导电型设为P型而进行说明,但也可以相反地,将第1导电型设为P型、将第2导电型设为N型。

[0018] 如图1所示,实施方式1涉及的半导体装置是使用半导体基板50而形成的。这里,将图1中的半导体基板50的上侧的主面定义为第1主面51,将半导体基板50的下侧的主面定义为第2主面52。

[0019] 半导体基板50的材料除了硅(Si)以外,也可以是碳化硅(SiC)、氮化镓(GaN)、金刚石等宽带隙半导体。在使用了宽带隙半导体作为半导体基板50的材料的情况下,与使用了硅的半导体装置相比,得到高电压、大电流、高温下的动作优异的特性。另外,半导体基板50可以是通过FZ(Floating Zone)法形成的FZ基板、通过MCZ(Magnetic field applied Czochralski)形成的基板、通过外延生长法形成的外延基板的任意者。

[0020] 在半导体基板50的第1主面51与第2主面52之间形成有第1导电型的漂移层1。另外,在半导体基板50规定了形成有作为半导体元件的RC-IGBT的有源区域30和将有源区域30包围的末端区域20。

[0021] 首先,对有源区域30的结构进行说明。

[0022] 在有源区域30,在半导体基板50的第1主面51侧的表层部形成有第2导电型的基极层4,在基极层4的表层部选择性地形成有发射极层3。另外,在本实施方式中,在基极层4与漂移层1之间形成有与漂移层1相比杂质的峰值浓度高的第1导电型的载流子积蓄层5。

[0023] 在半导体基板50的第1主面51形成有与发射极层3相邻、将基极层4及载流子积蓄层5贯通而到达漂移层1的沟槽7。在沟槽7的侧面及底面形成有栅极绝缘膜7b。另外,以被埋入至沟槽7内的方式,栅极电极7a形成于栅极绝缘膜7b之上。

[0024] 在半导体基板50的第1主面51之上以将栅极电极7a覆盖的方式形成有层间绝缘膜6。在层间绝缘膜6之上形成有发射极电极31。发射极电极31经由在层间绝缘膜6形成的接触孔与发射极层3及基极层4电连接。

[0025] 在半导体基板50的第2主面52侧的表层部分别选择性地形成有第2导电型的集电极层9和第1导电型的阴极层40。另外,在本实施方式中,在集电极层9及阴极层40与漂移层1之间形成有与漂移层1相比杂质的峰值浓度高的第1导电型的缓冲层8。在半导体基板50的

第2主面52之上形成有与集电极层9及阴极层40电连接的集电极 (collector) 电极 (electrode) 10。

[0026] 接下来,对末端区域20的结构进行说明。

[0027] 如图1所示,上述漂移层1、缓冲层8、集电极层9、集电极电极10及层间绝缘膜6不仅形成于有源区域30,也形成于末端区域20。

[0028] 在末端区域20,在半导体基板50的第1主面51侧的表层部形成有第2导电型的阱层2作为电场缓和层。末端区域20从半导体基板50的内侧起依次被划分为:缓和区域21,其与有源区域30相邻,在该缓和区域21,阱层2形成得较深;RESURF区域22,其位于缓和区域21的外侧,在该RESURF区域22,与缓和区域21相比阱层2形成得浅;以及沟道截断区域23,其位于比RESURF区域22更靠外侧处。在本实施方式中,通过将缓和区域21的阱层2中的第2导电型的杂质浓度的峰值的位置设为比RESURF区域22的阱层2中的第2导电型的杂质浓度的峰值的位置深的位置(距离第1主面51远的位置),从而使缓和区域21的阱层2比RESURF区域22的阱层2深。但是,由于阱层2的深度也能够通过杂质浓度进行调整,因此,例如能够通过使RESURF区域22的阱层2中的第2导电型的杂质浓度低于缓和区域21的阱层2中的第2导电型的杂质浓度而使RESURF区域22的阱层2比缓和区域21的阱层2浅。因此,缓和区域21的阱层2中的第2导电型的杂质浓度的峰值的位置与RESURF区域22的阱层2中的第2导电型的杂质浓度的峰值的位置也可以是相同深度。

[0029] 阈层2是第2导电型的杂质浓度朝向半导体基板50的外侧而减少的所谓的VLD构造的杂质区域。即,在缓和区域21,阱层2的第2导电型的杂质浓度从有源区域30的外周部朝向缓和区域21的外周部而减少。另外,在RESURF区域22,阱层2的第2导电型的杂质浓度从缓和区域21的外周部朝向RESURF区域22的外周部而减少。

[0030] 在沟道截断区域23,与有源区域30同样地,在半导体基板50的第1主面51侧的表层部形成有第1导电型的发射极层3,该发射极层3作为沟道截断层起作用。另外,在本实施方式中,如图1所示,基极层4、载流子积蓄层5、沟槽7、栅极电极7a及栅极绝缘膜7b也设置于沟道截断区域23。但是,也可以省略它们。

[0031] 在末端区域20的层间绝缘膜6之上形成有栅极配线电极11、场板电极12及沟道截断电极13。栅极配线电极11在未图示的区域与栅极电极7a连接,形成于缓和区域21,并且,其外端部伸出至RESURF区域22。场板电极12在RESURF区域22形成有大于或等于1个(在图1中为2个)。沟道截断电极13形成于沟道截断区域23,并且,其内端部伸出至RESURF区域22。另外,沟道截断电极13通过在层间绝缘膜6形成的接触孔与作为沟道截断层的沟道截断区域23的发射极层3电连接。

[0032] 栅极配线电极11、场板电极12及沟道截断电极13被半绝缘膜14覆盖。因此,栅极配线电极11、场板电极12及沟道截断电极13彼此分离,但通过半绝缘膜14而电连接。通过该结构,能够一边将场板电极12的宽度保持得宽,一边使场板电极12的电位分布接近作为电场缓和层的阱层2的电位分布,能够提高半导体装置的耐压。另外,通过将场板电极12的宽度保持得宽,从而防止由于来自将半导体装置的芯片封装的封装材料(例如树脂等)的应力而产生场板电极12的滑动,半导体装置的可靠性提高。场板电极12的长宽比(高度/宽度)优选小于或等于1。

[0033] 并且,通过上述的结构,从而能够将场板电极12设为单层,能够降低与末端构造的

形成相关的制造成本。此外,栅极配线电极11、场板电极12及沟道截断电极13能够由与发射极电极31相同的导电体材料形成,由此,能够有助于制造成本的降低。

[0034] 优选栅极配线电极11、场板电极12及沟道截断电极13的各电极的间隔是均一的。由此,半导体装置的耐压稳定化。另外,在设置多个场板电极12的情况下,优选多个场板电极12的宽度是均一的。由此,能够防止场板电极12的滑动的产生。

[0035] <实施方式2>

[0036] 图2示出实施方式1涉及的半导体装置(图1)的栅极配线电极11向RESURF区域22伸出的长度即从缓和区域21与RESURF区域22之间的边界起至栅极配线电极11的外端为止的长度(E1)与半导体装置的耐压之间的关系。此外,在栅极配线电极11的外端位于比缓和区域21与RESURF区域22之间的边界更靠内侧处的情况下,E1成为负值。

[0037] 如图2所示,半导体装置的耐压相对于E1而具有极大值。其原因是,如果将E1设定得小,则在缓和区域21与RESURF区域22之间的边界处电场集中,耐压下降,如果将E1设定得大,则能够配置于RESURF区域22之上的场板电极12的个数变少,耐压下降。因此,在实施方式2中,通过将E1设为大于或等于0μm且小于或等于30μm,从而提高半导体装置的耐压。

[0038] <实施方式3>

[0039] 图3示出实施方式1涉及的半导体装置(图1)的沟道截断电极13向RESURF区域22伸出的长度即从RESURF区域22与沟道截断区域23之间的边界起至沟道截断电极13的外端为止的长度(E2)与半导体装置的耐压之间的关系。此外,在沟道截断电极13的内端位于比RESURF区域22与沟道截断区域23之间的边界更靠外侧处的情况下,E2成为负值。

[0040] 如图3所示,半导体装置的耐压相对于E2而具有极大值。其原因是,如果将E2设定得小,则在RESURF区域22与沟道截断区域23之间的边界处电场集中,耐压下降,如果将E2设定得大,则能够配置于RESURF区域22之上的场板电极12的个数变少,耐压下降。因此,在实施方式2中,通过将E2设为大于或等于0μm且小于或等于30μm,从而提高半导体装置的耐压。

[0041] <实施方式4>

[0042] 图4示出实施方式1涉及的半导体装置(图1)的半绝缘膜14的电阻率与半导体装置的耐压之间的关系。

[0043] 如图4所示,如果半绝缘膜14的电阻率超过一定值,则半导体装置的耐压下降。其原因是,如果将半绝缘膜14的电阻率设定得高,则栅极配线电极11、场板电极12及沟道截断电极13各电极间的电位分布变得不稳定,耐压下降。因此,在实施方式4中,通过将半绝缘膜14的电阻率设为小于或等于 $1 \times 10^{12} \Omega \cdot \text{cm}$ ,从而提高半导体装置的耐压。

[0044] <实施方式5>

[0045] 图5是实施方式5涉及的半导体装置的剖视图。相对于图1的结构,图5的结构在半绝缘膜14之上设置有绝缘膜15。绝缘膜15能够相对于半绝缘膜14的形成工序之后的制造工艺、将半导体装置的芯片封装的封装材料对半绝缘膜14进行保护,提高半导体装置的可靠性。

[0046] <实施方式6>

[0047] 图6是实施方式6涉及的半导体装置的剖视图。相对于图5的结构,图6的结构在绝缘膜15之上设置有表面保护膜16。此外,表面保护膜16也可以是针对图1的结构而设置的。即,表面保护膜16也可以设置于半绝缘膜14之上。

[0048] 就实施方式6涉及的半导体装置而言,与栅极配线电极11、场板电极12、沟道截断电极13的形状对应地在半绝缘膜14的上表面产生的凹凸被表面保护膜16填埋。因此,栅极配线电极11、场板电极12、沟道截断电极13各电极之间被表面保护膜16填埋。表面保护膜16能够缓和从将半导体装置的芯片封装的封装材料施加至场板电极12的应力,提高半导体装置的可靠性。

[0049] <实施方式7>

[0050] 图7是实施方式7涉及的半导体装置的剖视图。图7的结构是从图1的结构将场板电极12省略后的结构。因此,在本实施方式中,半绝缘膜14将栅极配线电极11及沟道截断电极13覆盖,将栅极配线电极11与沟道截断电极13之间电连接。此外,也可以从图5或图6的结构将场板电极12省略。

[0051] 就实施方式7涉及的半导体装置而言,末端区域20的栅极配线电极11与沟道截断电极13之间通过连续地配置的半绝缘膜14而电连接,而不经由离散地配置的场板电极12。因此,半导体装置栅极配线电极11与沟道截断电极13之间的电位分布变得顺滑,能够有助于半导体装置的耐压的提高。

[0052] 此外,能够对各实施方式自由地进行组合,对各实施方式适当地进行变形、省略。

[0053] <附记>

[0054] 以下,将本发明的各方案作为附记而汇总地进行记载。

[0055] (附记1)

[0056] 一种半导体装置,其具有:

[0057] 半导体基板,其形成有第1导电型的漂移层;

[0058] 有源区域,其在所述半导体基板形成有半导体元件;

[0059] 末端区域,其是所述半导体基板的所述有源区域的外侧的区域;

[0060] 第2导电型的阱层,其形成于所述末端区域的所述半导体基板的表层部,第2导电型的杂质浓度朝向所述半导体基板的外侧而减少;以及

[0061] 第1导电型的沟道截断层,其形成于比所述阱层更靠外侧的所述半导体基板的表层部,

[0062] 所述末端区域具有:

[0063] 缓和区域,其与所述有源区域相邻,形成有所述阱层;

[0064] RESURF区域,其位于所述缓和区域的外侧,在该RESURF区域,所述阱层形成得比所述缓和区域浅,其中,RESURF是指降低表面场;

[0065] 沟道截断区域,其位于所述RESURF区域的外侧,形成有所述沟道截断层;

[0066] 电极,其隔着层间绝缘膜而形成于所述缓和区域之上;

[0067] 沟道截断电极,其与所述沟道截断层连接;以及

[0068] 半绝缘膜,其将所述电极及所述沟道截断电极覆盖,将所述电极与所述沟道截断电极之间电连接。

[0069] (附记2)

[0070] 根据附记1所记载的半导体装置,其中,

[0071] 所述末端区域还具有在所述RESURF区域之上隔着所述层间绝缘膜而形成的至少1个场板电极,

- [0072] 所述半绝缘膜将所述电极、所述场板电极及所述沟道截断电极覆盖,将所述电极、所述场板电极及所述沟道截断电极之间电连接。

- [0073] (附记3)

- [0074] 根据附记2所记载的半导体装置,其中,

- [0075] 所述半绝缘膜构成为,所述电极、所述场板电极及所述沟道截断电极的间隔是均一的。

- [0076] (附记4)

- [0077] 根据附记2或3所记载的半导体装置,其中,

- [0078] 所述场板电极为多个,多个所述场板电极的宽度是均一的。

- [0079] (附记5)

- [0080] 根据附记2至4中任一项所记载的半导体装置,其中,

- [0081] 所述电极、所述场板电极及所述沟道截断电极由相同的导电体材料形成。

- [0082] (附记6)

- [0083] 根据附记1至5中任一项所记载的半导体装置,其中,

- [0084] 所述电极的外端部伸出至所述RESURF区域,

- [0085] 所述电极向所述RESURF区域伸出的长度大于或等于0μm且小于或等于30μm。

- [0086] (附记7)

- [0087] 根据附记1至6中任一项所记载的半导体装置,其中,

- [0088] 所述沟道截断电极的内端部伸出至所述RESURF区域,

- [0089] 所述沟道截断电极向所述RESURF区域伸出的长度大于或等于0μm且小于或等于30μm。

- [0090] (附记8)

- [0091] 根据附记1至7中任一项所记载的半导体装置,其中,

- [0092] 所述半绝缘膜的电阻率小于或等于 $1 \times 10^{12} \Omega \cdot \text{cm}$ 。

- [0093] (附记9)

- [0094] 根据附记1至8中任一项所记载的半导体装置,其中,

- [0095] 还具有在所述半绝缘膜之上形成的绝缘膜。

- [0096] (附记10)

- [0097] 根据附记1至9中任一项所记载的半导体装置,其中,

- [0098] 还具有以将所述半绝缘膜的上表面的凹凸填埋的方式覆盖所述半绝缘膜的表面保护膜。

- [0099] 标号的说明

- [0100] 1漂移层,2阱层,3发射极层,4基极层,5载流子积蓄层,6层间绝缘膜,7沟槽,7a栅极电极,7b栅极绝缘膜,8缓冲层,9集电极层,10集电极电极,11栅极配线电极,12场板电极,13沟道截断电极,14半绝缘膜,15绝缘膜,16表面保护膜,20末端区域,21缓和区域,22RESURF区域,23沟道截断区域,30有源区域,31发射极电极,40阴极层,50半导体基板,51第1主面,52第2主面。

图1

图2

图3

图5

图6

图7