(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3889402号

(P3889402)

(45) 発行日 平成19年3月7日(2007.3.7)

(24) 登録日 平成18年12月8日(2006.12.8)

(51) Int.C1.

F 1

|             |              |                  |      |      |      |

|-------------|--------------|------------------|------|------|------|

| <b>G05F</b> | <b>1/56</b>  | <b>(2006.01)</b> | G05F | 1/56 | 320C |

| <b>G05F</b> | <b>1/10</b>  | <b>(2006.01)</b> | G05F | 1/56 | 310D |

| <b>H02H</b> | <b>3/087</b> | <b>(2006.01)</b> | G05F | 1/10 | 304M |

HO2H 3/087

請求項の数 3 (全 11 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-14988 (P2004-14988)    |

| (22) 出願日  | 平成16年1月22日 (2004.1.22)        |

| (65) 公開番号 | 特開2005-208949 (P2005-208949A) |

| (43) 公開日  | 平成17年8月4日 (2005.8.4)          |

| 審査請求日     | 平成16年11月12日 (2004.11.12)      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000116024<br>ローム株式会社<br>京都府京都市右京区西院溝崎町21番地 |

| (74) 代理人  | 100121337<br>弁理士 藤河 恒生                     |

| (72) 発明者  | 北條 喜之<br>京都市右京区西院溝崎町21番地 ローム<br>株式会社内      |

| 審査官       | 櫻田 正紀                                      |

最終頁に続く

(54) 【発明の名称】過電流検出回路及びそれを備えたレギュレータ

## (57) 【特許請求の範囲】

## 【請求項1】

電源電圧が入力端に、制御電圧が制御端に入力されて出力端から出力電流を出力する出力トランジスタに過電流が流れたときそれを検出する過電流検出回路であって、

出力トランジスタの制御端及び出力端にそれぞれ制御端及び出力端が接続されるモニタ用トランジスタと、

電源電圧が入力端に、検出用バイアス電圧が制御端に入力され、出力端がモニタ用トランジスタの入力端に接続される出力電流検出用トランジスタと、

基準電流を生成する定電流源と、

電源電圧が入力端に、検出用バイアス電圧が制御端に入力されて出力端から前記定電流源に前記基準電流を流し込むリファレンス用トランジスタと、

出力電流検出用トランジスタの出力端の電圧とリファレンス用トランジスタの出力端の電圧を比較することにより、出力トランジスタに過電流が流れたときそれを検出して過電流検出信号を出力する比較回路と、

を備えてなることを特徴とする過電流検出回路。

## 【請求項2】

請求項1に記載の過電流検出回路において、

前記比較回路は、前記定電流源とリファレンス用トランジスタの間に介装されたダイオード接続の第1の比較用トランジスタと、前記定電流源が生成する基準電流の所定倍の電流を生成する第2の定電流源と、第2の定電流源と出力電流検出用トランジスタの間に介

装され、第1の比較用トランジスタの制御端に制御端が接続された第2の比較用トランジスタと、を備えてなることを特徴とする過電流検出回路。

### 【請求項3】

請求項1又は2に記載の過電流検出回路を備えたレギュレータであって、

電源電圧と所定のDC電圧を出力する出力端子との間に出力トランジスタを設け、出力端子の電圧をフィードバック入力して所定のDC電圧を維持すべく出力トランジスタを制御するとともに、過電流検出回路の過電流検出信号が入力されると、出力トランジスタをオフする制御回路を設けてなることを特徴とするレギュレータ。

### 【発明の詳細な説明】

#### 【技術分野】

10

#### 【0001】

本発明は、例えば電源電圧を所定のDC電圧に変換するレギュレータにおいて負荷に電流を出力する構成要素としての出力トランジスタに過電流が流れた場合に、これを検出して保護する過電流検出回路及びその過電流検出回路を備えたレギュレータに関する。

#### 【背景技術】

#### 【0002】

スイッチングレギュレータやシリーズレギュレータなどのレギュレータは、入力する電源電圧と負荷に接続され所定のDC電圧を出力する端子の間に出力トランジスタを設け、その出力トランジスタを制御することにより所定のDC電圧を維持する。そして、負荷が短絡した場合などの異常時に、出力トランジスタが過電流により破壊するのを防止するために、過電流を検出して保護する回路が設けられる（例えば特許文献1）。

20

#### 【0003】

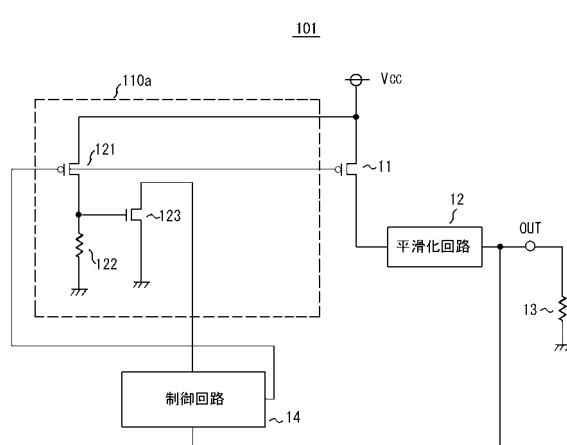

図4に従来の過電流検出回路及びそれを備えたレギュレータを示す。このレギュレータ101は、P型MOSトランジスタである出力トランジスタ11と、出力トランジスタ11の出力を平滑化する平滑化回路12と、平滑化した所定のDC電圧を出力する出力端子OUTと、出力端子OUTの電圧をフィードバック入力して出力トランジスタ11を制御する制御回路14と、出力トランジスタ11の過電流を検出して保護する過電流検出回路110aと、から構成される。出力端子OUTには負荷13が接続される。

#### 【0004】

過電流検出回路110aは、電源電圧V<sub>CC</sub>にソースが、出力トランジスタ11のゲートにゲートが接続されたP型MOSトランジスタであるモニタ用トランジスタ121と、モニタ用トランジスタ121のドレインに接続され他端が接地された出力電流検出用抵抗122と、モニタ用トランジスタ121のドレインと出力電流検出用抵抗122の接続点にゲートが、制御回路14にドレインが接続され、ソースが接地されたN型MOSトランジスタである過電流検出トランジスタ123と、から構成される。ここで、モニタ用トランジスタ121のサイズは出力トランジスタ11の1/Nに設定されている。そして、モニタ用トランジスタ121に流れる電流は過電流検出にだけ用いられるので、電力損失を大きくしないため、その電流値を小さくするようNは大きな値の自然数とされる。

30

#### 【0005】

今、出力トランジスタ11に出力電流I<sub>o</sub>が流れると、モニタ用トランジスタ121にはほぼI<sub>o</sub>/Nの電流が流れ、それに応じた電圧が接地電位を基準にして出力電流検出用抵抗122に生じる。そして、出力電流I<sub>o</sub>が過電流となり、この電圧が過電流検出出力トランジスタ123のしきい値(V<sub>th</sub>)を超えると過電流検出トランジスタ123がローレベルを出力する。これにより、制御回路14は、出力トランジスタ11の出力電流が過電流検出レベルを超えたとして（過電流が流れていると判断して）出力トランジスタ11をオフする。ここで、過電流検出レベルは、モニタ用トランジスタ121のサイズと出力電流検出用抵抗122の抵抗値によって調整することができる。

40

#### 【0006】

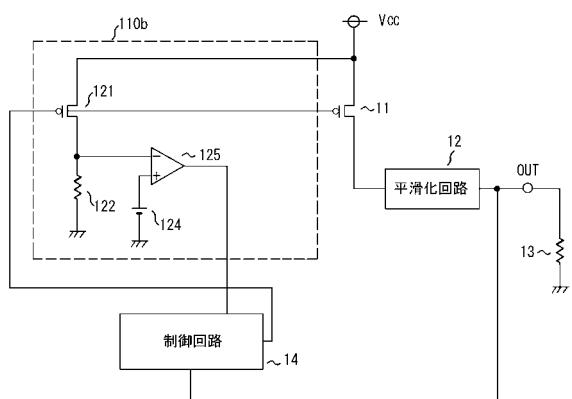

次に、従来の別の過電流検出回路及びそれを備えたレギュレータを図5に示す。このレギュレータ102は、過電流検出回路110b以外は上述のレギュレータ101と実質的

50

に同じ構成であり、過電流検出回路 110b も、上述の過電流検出回路 110a と同様に、モニタ用トランジスタ 121 と、出力電流検出用抵抗 122 と、を有している。そして、過電流検出回路 110b は、過電流検出出力トランジスタ 123 の代わりに、過電流検出出力用コンパレータ 125 を有している。この過電流検出出力用コンパレータ 125 は、モニタ用トランジスタ 121 と出力電流検出用抵抗 122 の接続点に反転入力端子が、過電流検出用基準電圧 124 に非反転入力端子が、制御回路 14 に出力端子が、それぞれ接続されている。

#### 【0007】

このものも、出力トランジスタ 11 に出力電流  $I_o$  が流れると、モニタ用トランジスタ 121 にはほぼ  $I_o / N$  の電流が流れ、それに応じた電圧が接地電位を基準にして出力電流検出用抵抗 122 に生じる。そして、出力電流  $I_o$  が過電流となり、この電圧が過電流検出用基準電圧 124 を超えると過電流検出出力用コンパレータ 125 がローレベルを出力する。これにより、制御回路 14 は、出力トランジスタ 11 の出力電流が過電流検出レベルを超えたとして出力トランジスタ 11 をオフする。ここで、過電流検出レベルは、モニタ用トランジスタ 121 のサイズ、出力電流検出用抵抗 122 の抵抗値及び過電流検出用基準電圧 124 の値によって調整することができる。

#### 【0008】

【特許文献 1】特開平 8 - 331757 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

このように、過電流検出回路 110a 及び 110b は、出力トランジスタ 11 に流れる過電流を検出することができる。ところで、過電流検出回路の過電流検出レベルのより高精度化を研究している本願発明者は、これら過電流検出回路 110a 及び 110b においては、出力電流検出用抵抗 122 に生じる電圧、すなわち、モニタ用トランジスタ 121 のドレイン電圧は接地電位を基準にしており、出力トランジスタ 11 のドレイン電圧は接地電位を基準にしていないことに着目した。すなわちこれにより、モニタ用トランジスタ 121 のドレインの電圧は出力トランジスタ 11 のドレインの電圧と異なり、その結果、モニタ用トランジスタ 121 の電流は、 $I_o / N$  の値からずれてくることを想定したのである。

#### 【0010】

従って、このずれを予め算出し、出力電流検出用抵抗 122 の抵抗値を変えて過電流検出レベルを調整することも考えられるものの、入力する電源電圧  $V_{cc}$  が変動した場合にはずれの程度も変化するので、この対策は効果的ではない。

#### 【0011】

また、本願発明者は、温度が変動したとき、モニタ用トランジスタ 121 及び出力トランジスタ 11 と出力電流検出用抵抗 122 とは温度特性が異なることによる過電流検出レベルへの影響にも着目した。また、過電流検出回路 110a においては、過電流検出出力トランジスタ 123 の特性も変動するため、更に過電流検出レベルは変動すると想定したのである。

#### 【0012】

本発明は、以上の事由に鑑みてなされたもので、その目的とするところは、入力する電源電圧や温度が変動した場合の過電流検出レベルの変動を抑制することができる過電流検出回路及びそれを備えたレギュレータを提供することにある。

#### 【課題を解決するための手段】

#### 【0013】

上記の課題を解決するために、請求項 1 に係る過電流検出回路は、電源電圧が入力端に、制御電圧が制御端に入力されて出力端から出力電流を出力する出力トランジスタに過電流が流れたときそれを検出する過電流検出回路であって、出力トランジスタの制御端及び出力端にそれぞれ制御端及び出力端が接続されるモニタ用トランジスタと、電源電圧が入

10

20

30

40

50

力端に、検出用バイアス電圧が制御端に入力され、出力端がモニタ用トランジスタの入力端に接続される出力電流検出用トランジスタと、基準電流を生成する定電流源と、電源電圧が入力端に、検出用バイアス電圧が制御端に入力されて出力端から前記定電流源に前記基準電流を流し込むリファレンス用トランジスタと、出力電流検出用トランジスタの出力端の電圧とリファレンス用トランジスタの出力端の電圧を比較することにより、出力トランジスタに過電流が流れたときそれを検出して過電流検出信号を出力する比較回路と、を備えてなることを特徴とする。

#### 【0014】

請求項2に係る過電流検出回路は、請求項1に記載の過電流検出回路において、前記比較回路は、前記定電流源とリファレンス用トランジスタの間に介装されたダイオード接続の第1の比較用トランジスタと、前記定電流源が生成する基準電流の所定倍の電流を生成する第2の定電流源と、第2の定電流源と出力電流検出用トランジスタの間に介装され、第1の比較用トランジスタの制御端に制御端が接続された第2の比較用トランジスタと、を備えてなることを特徴とする。10

#### 【0015】

請求項3に係るレギュレータは、請求項1又は2に記載の過電流検出回路を備えたレギュレータであって、電源電圧と所定のDC電圧を出力する出力端子との間に出力トランジスタを設け、出力端子の電圧をフィードバック入力して所定のDC電圧を維持すべく出力トランジスタを制御するとともに、過電流検出回路の過電流検出信号が入力されると、出力トランジスタをオフする制御回路を設けてなることを特徴とする。20

#### 【発明の効果】

#### 【0016】

本発明の過電流検出回路は、モニタ用トランジスタと出力電流検出用トランジスタの直列体を出力トランジスタと並列に設け、かつリファレンス用トランジスタを出力電流検出用トランジスタと並列に設け、出力電流検出用トランジスタの出力をリファレンス用トランジスタの出力と比較することで過電流を検出しているので、入力する電源電圧や温度が変動しても、それらのトランジスタの特性は相対的には余り変動しないので、過電流検出レベルの変動を抑制することができる。また、それを備えたレギュレータは、過電流検出レベルが安定するので、信頼性を向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0017】

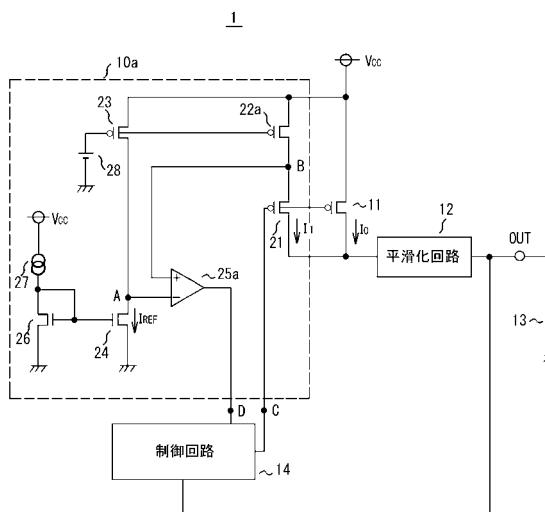

以下、本発明の最良の実施形態を図面を参照しながら説明する。図1は本発明の実施形態である過電流検出回路とそれを備えるレギュレータの回路図である。このレギュレータ1は、電源電圧 $V_{CC}$ と出力端子OUTの間にP型MOSトランジスタである出力トランジスタ11を設け、出力トランジスタ11を制御することにより出力端子OUTを所定のDC電圧に維持するとともに、出力トランジスタ11に過電流が流れた場合には過電流検出回路10aがそれを検出して出力トランジスタ11をオフするものである。更に詳しく説明すると、このレギュレータ1は、電源電圧 $V_{CC}$ を入力端(ソース)に入力し、制御電圧を制御端(ゲート)に入力し、出力電流 $I_o$ を出力端(ドレイン)から出力する出力トランジスタ11と、出力トランジスタ11の出力端に生じる電圧を平滑化する平滑化回路12と、平滑化した所定のDC電圧を出力する出力端子OUTと、出力端子OUTの電圧をフィードバック入力して所定のDC電圧を維持すべく図1における節点Cから出力トランジスタ11を制御するとともに、過電流検出回路10aの過電流検出信号が節点Dから入力されると、出力トランジスタ11をオフすべく節点Cの制御電圧を電源電圧 $V_{CC}$ レベルにする制御回路14と、出力トランジスタ11に過電流が流れた場合にそれを検出し、その過電流検出信号を節点Dから制御回路14に出力する過電流検出回路10aと、を備える。出力端子OUTには負荷13が接続される。40

#### 【0018】

過電流検出回路10aは、出力トランジスタ11の制御端(ゲート)及び出力端(ドレイン)にそれぞれ制御端(ゲート)及び出力端(ドレイン)が接続されるP型MOSトランジスタ。50

ンジスタであるモニタ用トランジスタ21と、電源電圧 $V_{CC}$ が入力端(ソース)に、検出用バイアス電圧28が制御端(ゲート)に入力され、出力端(ドレイン)がモニタ用トランジスタ21の入力端(ソース)に接続されるP型MOSトランジスタである出力電流検出用トランジスタ22aと、基準電流 $I_{REF}$ (例えば $10\mu A$ )を生成するN型MOSトランジスタである定電流源24と、電源電圧 $V_{CC}$ が入力端(ソース)に、検出用バイアス電圧28が制御端(ゲート)に入力されて出力端(ドレイン)から定電流源24に基準電流 $I_{REF}$ を流し込むP型MOSトランジスタであるリファレンス用トランジスタ23と、出力電流検出用トランジスタ22aの出力端(ドレイン)の電圧(すなわち図1における節点Bの電圧)とリファレンス用トランジスタ23の出力端(ドレイン)の電圧(すなわち図1における節点Aの電圧)を比較して検出信号を節点Dに出力するコンパレータからなる比較回路25aと、を備える。この比較回路25aは、さらに具体的には、出力トランジスタ11に過電流が流れていないとときはハイレベルの検出信号を出力し、過電流が流れたときそれを検出してローレベルの過電流検出信号を出力する。つまり、過電流検出回路10aは、モニタ用トランジスタ21と出力電流検出用トランジスタ22aの直列体を出力トランジスタ11と並列に設け、かつリファレンス用トランジスタ23を出力電流検出用トランジスタ22aと並列に設け、出力電流検出用トランジスタ22aの出力をリファレンス用トランジスタ23の出力と比較することで過電流を検出しているのである。また、モニタ用トランジスタ21、出力電流検出用トランジスタ22a及びリファレンス用トランジスタ23のサイズは等しく、そして出力トランジスタ11のサイズの1/N(例えば1/50000)に設定されている。なお、過電流検出回路10aは、更にN型MOSトランジスタ26及び定電流源27を備え、それらは、定電流源24の電流値を決めるものである。

10

20

## 【0019】

また、出力電流検出用トランジスタ22aとリファレンス用トランジスタ23の制御端に共通に入力される検出用バイアス電圧28は、モニタ用トランジスタ21の制御端(ゲート)の電圧にほぼ一致させることが望ましい。例えば、レギュレータ1がスイッチングレギュレータの場合は、検出用バイアス電圧28を接地電圧レベルにするのが望ましい。

## 【0020】

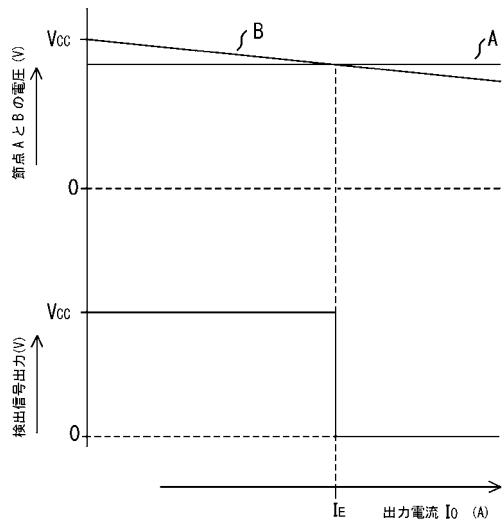

次に、過電流検出回路10aの動作を図2の動作波形図に基づいて説明する。この動作波形図は、節点A及びBの動作波形(曲線Aと曲線B)、すなわち出力電流 $I_0$ に対する節点A及びBの電圧の変化と、比較回路25aの動作波形、すなわち検出信号出力(節点Dの電圧)の変化を示している。モニタ用トランジスタ21と出力電流検出用トランジスタ22aのサイズは出力トランジスタ11の1/Nに設定されているので、出力トランジスタ11に出力電流 $I_0$ が流れると、直列接続された(直列体の)モニタ用トランジスタ21及び出力電流検出用トランジスタ22aに流れる電流 $I_1$ はほぼ $I_0/2N$ となる。すなわち、モニタ用トランジスタ21と出力電流検出用トランジスタ22aの等価抵抗の値をRとすると、出力トランジスタ11の等価抵抗の値は $R/N$ であるから、以下の式が成立する。

30

$$R I_1 + R I_1 = R I_0 / N \quad \dots (1)$$

よって、

$$I_1 = I_0 / 2N \quad \dots (2)$$

となる。

## 【0021】

そして、節点Bには、出力電流検出用トランジスタ22aに $I_0/2N$ の電流を流すために必要な電圧が電源電圧 $V_{CC}$ を基準にして生じている。節点Bの電圧は、出力トランジスタ11の出力電流 $I_0$ が増加すると直線的に下降する。一方、節点Aには、リファレンス用トランジスタ23に基準電流 $I_{REF}$ を流すために必要な電圧が電源電圧 $V_{CC}$ を基準にして生じている。従って、出力トランジスタ11の出力電流 $I_0$ が増加し、モニタ用トランジスタ21及び出力電流検出用トランジスタ22aに流れる電流 $I_0/2N$ が基準電流 $I_{REF}$ の値を超えると、すなわち、節点Bの電圧が節点Aの電圧以下に下降する

40

50

と、比較回路 25a の出力である節点 D の検出信号はハイレベルからローレベル（過電流検出信号）に変化する。具体的には、N を 50000 に、基準電流  $I_{REF}$  を  $10 \mu A$  に、それぞれ設定すると、出力トランジスタ 11 の電流  $I_o$  がほぼ 1A (アンペア) 以上で、節点 D の検出信号はローレベルになる。その結果、制御回路 14 は、出力トランジスタ 11 の出力電流  $I_o$  が過電流検出レベル  $I_E$  を超えたとして（過電流が流れていると判断して）出力トランジスタ 11 をオフする。

#### 【0022】

ここで、直列体のモニタ用トランジスタ 21 及び出力電流検出用トランジスタ 22a、さらにはリファレンス用トランジスタ 23 の各出力端（ドレイン）の電圧は、出力トランジスタ 11 と同様に、流れる電流の値に応じて電源電圧  $V_{CC}$  を基準に生じている。従って、これらトランジスタの出力端（ドレイン）の電圧が他の素子の影響を受けて流れる電流の比率がサイズの比率からずれることが抑制される。そして、電源電圧  $V_{CC}$  が変動した場合でも、これらのトランジスタの出力端（ドレイン）の電圧は、電源電圧  $V_{CC}$  を基準に生じているので、その影響を受けず、過電流検出レベル  $I_E$  の変動はほとんど起こらないのである。10

#### 【0023】

また、出力トランジスタ 11、モニタ用トランジスタ 21、出力電流検出用トランジスタ 22a 及びリファレンス用トランジスタ 23 は、全て P 型 MOS トランジスタであるので、同じ温度特性を有する。従って、モニタ用トランジスタ 21、出力電流検出用トランジスタ 22a 及びリファレンス用トランジスタ 23 の特性は、温度が変動しても出力トランジスタ 11 と同じように変化することとなり、温度の変動によって生じる過電流検出レベル  $I_E$  の変動を抑制することができる。20

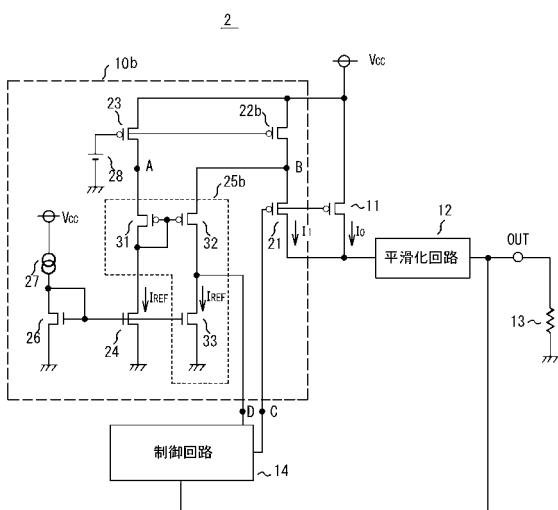

#### 【0024】

次に、本発明の他の実施形態である過電流検出回路とそれを備えるレギュレータを、図 3 に基づいて説明する。このレギュレータ 2 は、過電流検出回路 10b 以外は、上述のレギュレータ 1 と実質的に同じ構成であるので、過電流検出回路 10b について以下説明を行う。

#### 【0025】

過電流検出回路 10b は、過電流検出回路 10a と同様に、モニタ用トランジスタ 21 と、出力電流検出用トランジスタ 22b と、リファレンス用トランジスタ 23 と、基準電流  $I_{REF}$  を生成する定電流源 24 と、を備える。ただし、モニタ用トランジスタ 21 及びリファレンス用トランジスタ 23 のサイズは過電流検出回路 10a と同様に設定されているが、出力電流検出用トランジスタ 22b のサイズは、モニタ用トランジスタ 21 及びリファレンス用トランジスタ 23 の 2 倍に設定されている。30

#### 【0026】

そして、過電流検出回路 10b は、先の実施形態におけるコンパレータからなる比較回路 25a を、別の回路構成を有する比較回路 25b に替えている。比較回路 25b は、定電流源 24 とリファレンス用トランジスタ 23 の間に介装されたダイオード接続の（出力端（ドレイン）と制御端（ゲート）が接続された）P 型 MOS トランジスタである第 1 の比較用トランジスタ 31 と、定電流源（N 型 MOS トランジスタ）24 とゲート電圧を共通にすることで定電流源 24 が生成する基準電流  $I_{REF}$  の所定倍（ここでは 1 倍）の電流を生成する第 2 の定電流源 33 と、第 2 の定電流源 33 と出力電流検出用トランジスタ 22b の間に介装され、第 1 の比較用トランジスタ 31 の制御端（ゲート）に制御端（ゲート）が接続された P 型 MOS トランジスタである第 2 の比較用トランジスタ 32 と、を備える。従って、第 2 の比較用トランジスタ 32 の入力端（ソース）の電位が第 1 の比較用トランジスタ 31 の入力端（ソース）よりも降下すると、第 2 の比較用トランジスタ 32 には電流は流れなくなる（オフする）。40

#### 【0027】

次に、過電流検出回路 10b の動作を説明する。モニタ用トランジスタ 21 とリファレンス用トランジスタ 23 の等価抵抗の値を R とすると、出力電流検出用トランジスタ 2

2 b の等価抵抗の値は  $R / 2$  であり、出力トランジスタ 1 1 の等価抵抗の値は  $R / N$  である。出力電流検出用トランジスタ 2 2 b に流れる電流は、モニタ用トランジスタ 2 1 に流れる電流  $I_1$  と第 2 の定電流源 3 3 に流れ込む電流  $I_{REF}$  とに分岐する。従って、節点 B には、出力電流検出用トランジスタ 2 2 b に電流  $I_{REF} + I_1$  を流すために必要な電圧  $R(I_{REF} + I_1) / 2$  が電源電圧  $V_{CC}$  を基準にして生じる。そして、

$$R(I_{REF} + I_1) / 2 + R I_1 = R I_0 / N \quad \dots (3)$$

が成立し、この式を満たすようモニタ用トランジスタ 2 1 に電流  $I_1$  が流れることになる。

### 【0028】

一方、節点 A には、リファレンス用トランジスタ 2 3 に基準電流  $I_{REF}$  を流すために必要な電圧  $R I_{REF}$  が電源電圧  $V_{CC}$  を基準にして生じている。節点 B の電圧が節点 A の電圧と等しくなると、

$$R(I_{REF} + I_1) / 2 = R I_{REF} \quad \dots (4)$$

が成立する。これを解くと、

$$I_1 = I_{REF} \quad \dots (5)$$

となる。そして、(5) 式を (3) 式に代入すると、

$$I_1 = I_{REF} = I_0 / 2N \quad \dots (6)$$

となる。そして、モニタ用トランジスタ 2 1 に流れる電流  $I_1$  が電流  $I_{REF}$  を超えると、節点 B の電圧は節点 A よりも降下するので、第 2 の比較用トランジスタ 3 2 はオフし、比較回路 2 5 b の出力、すなわち節点 D の検出信号はハイレベルからローレベル（過電流検出信号）に変化する。具体的には、N を 5 0 0 0 0 と、基準電流  $I_{REF}$  を  $10 \mu A$  と、それぞれ設定すると、出力トランジスタ 1 1 の出力電流  $I_0$  が  $1 A$  以上で、節点 D の検出信号はローレベルになる。

### 【0029】

このように、過電流検出回路 1 0 b は、過電流検出回路 1 0 a と同様に、出力トランジスタ 1 1 に過電流が流れた場合、それを検出して過電流検出信号を節点 D から制御回路 1 4 に出力することができる。加えて、この過電流検出回路 1 0 b の比較回路 2 5 b は、過電流検出回路 1 0 a の比較回路 2 5 a のようなコンパレータを用いていないので、回路を構成する素子数を削減することができ、占有面積及び消費電力を減少させることができる。

### 【0030】

なお、過電流検出回路 1 0 a 又は 1 0 b において、過電流検出レベル  $I_E$  を調整するには基準電流  $I_{REF}$  を変えればよい。また、過電流検出回路 1 0 b において、定電流源 (N 型 MOS トランジスタ) 2 4 に対して第 2 の定電流源 (N 型 MOS トランジスタ) 3 3 のサイズを変えて流れる電流値の所定の倍率を変えることによって、過電流検出レベル  $I_E$  を調整することも可能である。例えば、第 2 の定電流源 (N 型 MOS トランジスタ) 3 3 のサイズを  $1 / 2$  にすると、

$$I_{REF} = 2 I_0 / 5N \quad \dots (7)$$

で、節点 B の電圧が節点 A の電圧と等しくなる。従って、N を 5 0 0 0 0 と、基準電流  $I_{REF}$  を  $10 \mu A$  と、それぞれ設定すると、過電流検出レベル  $I_E$  は  $1.25 A$  となる。

### 【0031】

また、モニタ用トランジスタ 2 1 及び出力電流検出用トランジスタ 2 2 a (2 2 b) に対してリファレンス用トランジスタ 2 3 のサイズ比を変えることによって、過電流検出レベル  $I_E$  を調整することも可能である。例えば、過電流検出回路 1 0 a において、リファレンス用トランジスタ 2 3 のサイズをモニタ用トランジスタ 2 1 及び出力電流検出用トランジスタ 2 2 a の  $1 / 2$  とすると、上記条件 (N が 5 0 0 0 0、基準電流  $I_{REF}$  が  $10 \mu A$ ) で、過電流検出レベル  $I_E$  は  $2 A$  となる。また、過電流検出回路 1 0 b において、リファレンス用トランジスタ 2 3 のサイズをモニタ用トランジスタ 2 1 の  $1 / 2$  とすると、

$$I_{REF} = I_0 / 5N \quad \dots (8)$$

10

20

20

30

40

50

で、節点Bの電圧が節点Aの電圧と等しくなる。従って、上記条件（Nが50000、基準電流 $I_{REF}$ が $10\mu A$ ）で、過電流検出レベル $I_E$ は $2.5A$ となる。

### 【0032】

また、以上説明した実施形態では、レギュレータの出力トランジスタ11をP型MOSトランジスタとし、過電流検出回路のモニタ用トランジスタ21、出力電流検出用トランジスタ22a(22b)及びリファレンス用トランジスタ23は全てP型MOSトランジスタにしたもので説明したが、出力トランジスタ11をN型MOSトランジスタ、PNP型バイポーラトランジスタあるいはNPN型バイポーラトランジスタにすることも可能であり、その場合、モニタ用トランジスタ21、出力電流検出用トランジスタ22a(22b)及びリファレンス用トランジスタ23をそれらの型に合わせて過電流検出回路を構成すればよいことは勿論のことである。10

### 【図面の簡単な説明】

#### 【0033】

【図1】本発明の実施形態に係る過電流検出回路とそれを備えるレギュレータの回路図。

【図2】同上の動作波形図。

【図3】本発明の別の実施形態に係る過電流検出回路とそれを備えるレギュレータの回路図。

【図4】背景技術の過電流検出回路とそれを備えるレギュレータの回路図。

【図5】背景技術の別の過電流検出回路とそれを備えるレギュレータの回路図。

### 【符号の説明】

#### 【0034】

|         |               |    |

|---------|---------------|----|

| 1、2     | レギュレータ        | 20 |

| 10a、10b | 過電流検出回路       |    |

| 11      | 出力トランジスタ      |    |

| 13      | 負荷            |    |

| 21      | モニタ用トランジスタ    |    |

| 22a、22b | 出力電流検出用トランジスタ |    |

| 23      | リファレンス用トランジスタ |    |

| 24      | 定電流源          |    |

| 25a、25b | 比較回路          |    |

| 28      | 検出用バイアス電圧     |    |

|    |              |

|----|--------------|

| 31 | 第1の比較用トランジスタ |

| 32 | 第2の比較用トランジスタ |

| 33 | 第2の定電流源      |

|          |             |

|----------|-------------|

| $V_{CC}$ | 入力する電源電圧    |

| OUT      | レギュレータの出力端子 |

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

102

---

フロントページの続き

(56)参考文献 特開平05-076133(JP,A)

特開2003-173211(JP,A)

特開平08-331757(JP,A)

特開平10-322185(JP,A)

特開平05-026912(JP,A)

特開平10-332751(JP,A)

(58)調査した分野(Int.Cl., DB名)

G05F 1/00 - 1/70

G05F 3/00 - 3/30

H02H 3/00 - 3/52