(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5759704号

(P5759704)

(45) 発行日 平成27年8月5日(2015.8.5)

(24) 登録日 平成27年6月12日(2015.6.12)

(51) Int.Cl.

F 1

G02F 1/1343 (2006.01)

G02F 1/1343

G02F 1/1368 (2006.01)

G02F 1/1368

請求項の数 10 (全 76 頁)

(21) 出願番号 特願2010-261887 (P2010-261887)

(22) 出願日 平成22年11月25日 (2010.11.25)

(65) 公開番号 特開2011-133876 (P2011-133876A)

(43) 公開日 平成23年7月7日 (2011.7.7)

審査請求日 平成25年10月18日 (2013.10.18)

(31) 優先権主張番号 特願2009-270055 (P2009-270055)

(32) 優先日 平成21年11月27日 (2009.11.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 久保田 大介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 石谷 哲二

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山下 晃央

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 田村 智宏

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板と第2の基板との間に、液晶材料を含む液晶層を有し、

前記第1の基板の前記液晶層側の面から前記液晶層中に突出するリブ状の第1の構造体と、

前記リブ状の第1の構造体の間に設けられ、前記第1の基板の前記液晶層側の面から前記液晶層中に突出するリブ状の第2の構造体と、

前記リブ状の第1の構造体の上面及び側面を覆う第1の電極層と、

前記リブ状の第2の構造体の上面及び側面を覆う第2の電極層と、を有し、

前記リブ状の第1の構造体と、前記リブ状の第2の構造体とは、連続膜からなる構造体であり、

前記リブ状の第1の構造体の前記上面はドーム状であり、

前記リブ状の第1の構造体の前記側面は、直線に沿う形状を有し、

前記リブ状の第1の構造体の断面の端部は、曲率を有し、

前記リブ状の第2の構造体の前記上面はドーム状であり、

前記リブ状の第2の構造体の前記側面は、直線に沿う形状を有し、

前記リブ状の第2の構造体の断面の端部は、曲率を有することを特徴とする液晶表示装置。

## 【請求項 2】

請求項1において、

10

20

前記第1の電極層、及び前記第2の電極層は前記液晶層に接していることを特徴とする液晶表示装置。

【請求項3】

請求項1又は請求項2において、

前記第1の電極層、及び前記第2の電極層は櫛歯状であることを特徴とする液晶表示装置。

【請求項4】

第1の基板と第2の基板との間に、液晶材料を含む液晶層を有し、

前記第1の基板の前記液晶層側の面から前記液晶層中に突出するリブ状の第1の構造体と、

前記リブ状の第1の構造体の間に設けられ、前記第1の基板の前記液晶層側の面から前記液晶層中に突出するリブ状の第2の構造体と、

前記リブ状の第1の構造体の上面及び側面を覆う第1の電極層と、

前記リブ状の第2の構造体の上面及び側面を覆う第2の電極層と、

前記第2の基板の前記液晶層側の面に設けられた第3の電極層と、を有し、

前記第3の電極層は、開口パターンを有し、

前記第3の電極層は、前記第2の電極層と重畠し、

前記リブ状の第1の構造体と、前記リブ状の第2の構造体とは、連続膜からなる構造体であり、

前記リブ状の第1の構造体の前記上面はドーム状であり、

前記リブ状の第1の構造体の前記側面は、直線に沿う形状を有し、

前記リブ状の第1の構造体の断面の端部は、曲率を有し、

前記リブ状の第2の構造体の前記上面はドーム状であり、

前記リブ状の第2の構造体の前記側面は、直線に沿う形状を有し、

前記リブ状の第2の構造体の断面の端部は、曲率を有することを特徴とする液晶表示装置。

【請求項5】

請求項4において、

前記第1の電極層、前記第2の電極層、及び前記第3の電極層は前記液晶層に接していることを特徴とする液晶表示装置。

【請求項6】

請求項4又は請求項5において、

前記第1の電極層、前記第2の電極層、及び前記第3の電極層は櫛歯状であることを特徴とする液晶表示装置。

【請求項7】

請求項1乃至6のいずれか一項において、

前記液晶層は、カイラル剤を含むことを特徴とする液晶表示装置。

【請求項8】

請求項1乃至7のいずれか一項において、

前記液晶層は、光硬化樹脂及び光重合開始剤を有することを特徴とする液晶表示装置。

【請求項9】

請求項1乃至8のいずれか一項において、

前記第1の基板と、前記第1の電極層及び前記第2の電極層との間にトランジスタが設けられ、

前記第1の電極層は、前記トランジスタと電気的に接続していることを特徴とする液晶表示装置。

【請求項10】

請求項9において、

前記トランジスタは、Inと、Gaと、Znを含むことを特徴とする液晶表示装置。

【発明の詳細な説明】

10

20

30

40

50

**【技術分野】****【0001】**

液晶表示装置及びその作製方法に関する。

**【背景技術】****【0002】**

薄型、軽量化を図った表示装置（所謂フラットパネルディスプレイ）には液晶素子を有する液晶表示装置、自発光素子を有する発光装置、フィールドエミッഷンディスプレイ（FED）などが競合し、開発されている。

**【0003】**

液晶表示装置においては、液晶分子の応答速度の高速化が求められている。液晶の表示モードは種々あるが、中でも高速応答可能な液晶モードとしてFLC（Ferroelectric Liquid Crystal）モード、OCB（Optical Compensated Birefringence）モード、ブルー相を示す液晶を用いるモードがあげられる。

**【0004】**

特にブルー相を示す液晶を使用するモードは配向膜が不要であり、かつ広視野角化が得られるので、実用化に向けてより研究が行われている（例えば特許文献1参照。）。特許文献1は、ブルー相の出現する温度範囲を広げるために、液晶に高分子安定化処理を行う報告である。

**【先行技術文献】**

10

**【特許文献】****【0005】****【特許文献1】国際公開第05/090520号パンフレット**

20

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

液晶表示装置における問題として高いコントラストを実現するためには、白透過率（白表示時の光の透過率）が大きいことが必要である。

**【0007】**

従って、より高コントラスト化に向けて、ブルー相を示す液晶を用いた液晶表示モードに適した液晶表示装置を提供することを目的のーとする。

30

**【0008】**

また、ブルー相を示す液晶を用いた液晶表示装置において、より低消費電力化を達成することを目的のーとする。

**【課題を解決するための手段】****【0009】**

第1の基板と第2の基板とでブルー相を示す液晶層を挟持する液晶表示装置において、第1の基板と液晶層との間に設けられる開口パターン（スリット）を有する画素電極層（第1の電極層）及び開口パターン（スリット）を有する共通電極層（第2の電極層）を重ならないように配置する。画素電極層は第1の基板の液晶層側の面（液晶層に面している方の面）から液晶層に突出して設けられたリブ状の第1の構造体の上面側面を覆って形成され、共通電極層は第1の基板の液晶層側の面から液晶層に突出して設けられたリブ状の第2の構造体の上面側面を覆って形成される。

40

**【0010】**

共通電極層は、対向基板（第2の基板）側にも一対の共通電極層が対向するように設けてもよく、この場合液晶層を間に挟んで第1の基板側の第1の共通電極層と、第2の基板側に第2の共通電極層（第3の電極層）とがお互いに重畳するように配置される。

**【0011】**

第1の基板に形成された画素電極層及び第1の共通電極層と、第2の基板に形成された第2の共通電極層は液晶層を間に挟んでシール材によって固持されている。画素電極層、第

50

1の共通電極層及び第2の共通電極層は平板状でなく、様々な開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。また、第2の共通電極層を形成する場合、第1の共通電極層及び第2の共通電極層は少なくとも画素領域において、平面図でみるとほぼ同形状であり液晶層を介して重畠するように配置される。第1の共通電極層及び第2の共通電極層は少なくとも一部重なって（重畠して）いればよい。

【0012】

第1の構造体及び第2の構造体はリブ状である。リブ状の第1の構造体及び第2の構造体は、該上面及び側面に形成される画素電極層、又は共通電極層の形状を反映し、開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。

【0013】

第1の構造体の上面及び側面を覆うように画素電極層を設け、第2の構造体の上面及び側面を覆うように共通電極層を設けることで、画素電極層及び共通電極層の形成面積を液晶層の膜厚方向に（3次元的に）も拡大できる。よって、画素電極層及び共通電極層間に電圧を印加した時、画素電極層と、共通電極層との間に広く電界を形成することができる。

【0014】

また、第2の基板側に第2の共通電極層を設けると、画素電極層と第2の共通電極層との間に液晶に対して斜め方向（基板に対して斜めの方向）の電界も加えることができるため、より効率よく液晶分子を制御できる。

【0015】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率（黒表示時の光の透過率）との比であるコントラスト比も高くすることができる。また、粘度の高いブルー相を示す液晶材料（液晶混合物）であっても、効果的に電界を印加することができるため、低消費電力化も達成できる。

【0016】

構造体は絶縁性材料（有機材料及び無機材料）を用いた絶縁体、及び導電性材料（有機材料及び無機材料）を用いた導電体で形成することができる。代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。例えば、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。また、導電性樹脂や金属材料で形成してもよい。なお、構造体は複数の薄膜の積層構造であってもよい。

【0017】

構造体の形状は、柱状、錐形の先端が平面である断面が台形の形状、錐形の先端が丸いドーム状などを用いることができる。本明細書において画素電極層及び共通電極層（第1の共通電極層）は構造体の表面（上面及び側面）を覆うように形成されるため、構造体は画素電極層及び共通電極層（第1の共通電極層）の被覆性が良好なように表面に段差が少なく曲面を有するような形状が好ましい。また、構造体は可視光の光に対して透光性を有する材料を用いると開口率や白透過率を低下させないために好ましい。

【0018】

また、構造体は基板の液晶層側の面から液晶層中に突出する部分であればよいので、層間膜を加工して液晶層側の表面を凹凸形状とし、突出する構造体としてもよい。よって、構造体は複数の突出した凸部を有する連続膜であってもよく、第1の構造体と第2の構造体が連続膜であってもよい。

【0019】

本明細書において、第1の電極層（画素電極層）及び第2の電極層（共通電極層）（又は第3の電極層（第2の共通電極層））が有する形状としては、閉空間を形成せず開かれた櫛歯状のようなパターンを用いる。第1の電極層と第2の電極層とは接せず、互いの櫛歯状のパターンがかみ合うように同一の絶縁表面（例えば同一基板や同一絶縁膜）に設けられる。

【0020】

本明細書では、半導体素子（例えばトランジスタ）、画素電極層、第1の共通電極層及び層間膜が形成されている基板を素子基板（第1の基板）といい、該素子基板と液晶層を介

10

20

30

40

50

して対向する基板を対向基板（第2の基板）という。対向基板（第2の基板）と液晶層との間に第1の共通電極層と重疊する第2の共通電極層が形成されてもよい。

#### 【0021】

液晶層には、ブルー相を示す液晶材料を用いる。なお、液晶材料とは、液晶層に用いる液晶を含む混合物をさす。ブルー相を示す液晶材料は、応答速度が1msec以下と短く高速応答が可能であるため、液晶表示装置の高性能化が可能になる。

#### 【0022】

ブルー相を示す液晶材料として液晶及びカイラル剤を含む。カイラル剤は、液晶を螺旋構造に配向させ、ブルー相を発現させるために用いる。例えば、5重量%以上のカイラル剤を混合させた液晶材料を液晶層に用いればよい。

10

#### 【0023】

液晶は、サーモトロピック液晶、低分子液晶、高分子液晶、強誘電液晶、反強誘電液晶等を用いる。

#### 【0024】

カイラル剤は、液晶に対する相溶性が良く、かつ捩れ力の強い材料を用いる。また、R体、S体のどちらか片方の材料が良く、R体とS体の割合が50:50のラセミ体は使用しない。

#### 【0025】

上記液晶材料は、条件により、コレステリック相、コレステリックブルー相、スマクチック相、スマクチックブルー相、キュービック相、カイラルネマチック相、等方相等を示す。

20

#### 【0026】

ブルー相であるコレステリックブルー相及びスマクチックブルー相は、螺旋ピッチが500nm以下とピッチの比較的短いコレステリック相またはスマクチック相を有する液晶材料にみられる。液晶材料の配向は二重ねじれ構造を有する。可視光の波長以下の秩序を有しているため、透明であり、電圧印加によって配向秩序が変化して光学的変調作用が生じる。ブルー相は光学的に等方であるため視野角依存性がなく、配向膜を形成しなくとも良いため、表示画像の質の向上及びコスト削減が可能である。

#### 【0027】

また、ブルー相は狭い温度範囲でしか発現が難しく、温度範囲を広く改善するために液晶材料に、光硬化樹脂及び光重合開始剤を添加し、高分子安定化処理を行うことが好ましい。高分子安定化処理は、液晶、カイラル剤、光硬化樹脂、及び光重合開始剤を含む液晶材料に、光硬化樹脂、及び光重合開始剤が反応する波長の光を照射して行う。この高分子安定化処理は、温度制御を行い、等方相を示した状態で光照射して行っても良いし、ブルー相を示した状態で光照射して行ってもよい。

30

#### 【0028】

例えば、液晶層の温度を制御し、ブルー相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行う。但し、これに限定されず、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内の等方相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行ってもよい。ブルー相と等方相間の相転移温度とは、昇温時にブルー相から等方相に転移する温度又は降温時に等方相からブルー相に相転移する温度をいう。高分子安定化処理の一例としては、液晶層を等方相まで加熱した後、徐々に降温させてブルー相にまで相転移させ、ブルー相が発現する温度を保持した状態で光を照射することができる。他にも、液晶層を徐々に加熱して等方相に相転移させた後、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内状態（等方相を発現した状態）で光を照射することができる。また、液晶材料に含まれる光硬化樹脂として、紫外線硬化樹脂（UV硬化樹脂）を用いる場合、液晶層に紫外線を照射すればよい。なお、ブルー相を発現させなくとも、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内状態（等方相を発現した状態）で光を照射して高分子安定化処理を行えば、応答速度が1msec以下と短く高速応答が可能である。

40

50

## 【0029】

本明細書で開示する発明の構成の一形態は、ブルー相を示す液晶材料を含む液晶層を挟持する第1の基板及び第2の基板と、第1の基板の液晶層側の面から液晶層中に突出するリブ状の第1の構造体と、リブ状の第1の構造体の間に設けられ、第1の基板の液晶層側の面から液晶層中に突出するリブ状の第2の構造体と、リブ状の第1の構造体の上面及び側面を覆う第1の電極層と、リブ状の第2の構造体の上面及び側面を覆う第2の電極層とを有する液晶表示装置である。

## 【0030】

本明細書で開示する発明の構成の他の一形態は、ブルー相を示す液晶材料を含む液晶層を挟持する第1の基板及び第2の基板と、第1の基板の液晶層側の面から液晶層中に突出するリブ状の第1の構造体と、リブ状の第1の構造体の間に設けられ、第1の基板の液晶層側の面から液晶層中に突出するリブ状の第2の構造体と、リブ状の第1の構造体の上面及び側面を覆う第1の電極層と、リブ状の第2の構造体の上面及び側面を覆う第2の電極層と、第2の電極層と重畠し第2の基板と液晶層との間に設けられた開口パターンを有する第3の電極層とを有する液晶表示装置である。

10

## 【0031】

ブルー相を示す液晶層を用いるため、配向膜を形成する必要がないため、画素電極層（第1の電極層）と液晶層、及び第2の電極層（第1の共通電極層）と液晶層とは接する構成となる。なお、第3の電極層（第2の共通電極層）を設ける場合、第3の電極層（第2の共通電極層）も液晶層と接する構成となる。

20

## 【0032】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

## 【0033】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

## 【発明の効果】

## 【0034】

リブ状の第1の構造体の上面及び側面を覆うように画素電極層を設け、リブ状の第2の構造体の上面及び側面を覆うように共通電極層を設けることで、画素電極層及び共通電極層の形成面積を液晶層の膜厚方向に（3次元的に）も拡大できる。よって、画素電極層及び共通電極層間に電圧を印加した時、画素電極層と、共通電極層との間に広く電界を形成することができ、その電界を用いて液晶分子を制御できる。

30

## 【0035】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上し、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

## 【0036】

また、粘度の高いブルー相を示す液晶層であっても、効果的に電界を印加することができるため、液晶表示装置の低消費電力化も達成できる。

40

## 【図面の簡単な説明】

## 【0037】

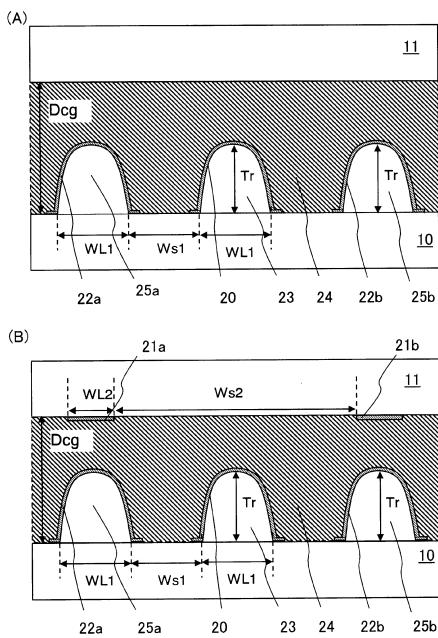

【図1】液晶表示装置の電界モードを説明する図。

【図2】液晶表示装置の電界モードを説明する図。

【図3】液晶表示装置を説明する図。

【図4】液晶表示装置を説明する図。

【図5】液晶表示装置を説明する図。

【図6】液晶表示装置を説明する図。

【図7】液晶表示装置の作製方法を説明する図。

50

- 【図 8】液晶表示装置の電極層を説明する図。

- 【図 9】液晶表示装置を説明する図。

- 【図 10】液晶表示装置を説明する図。

- 【図 11】液晶表示装置に適用できるトランジスタを説明する図。

- 【図 12】液晶表示装置を説明する図。

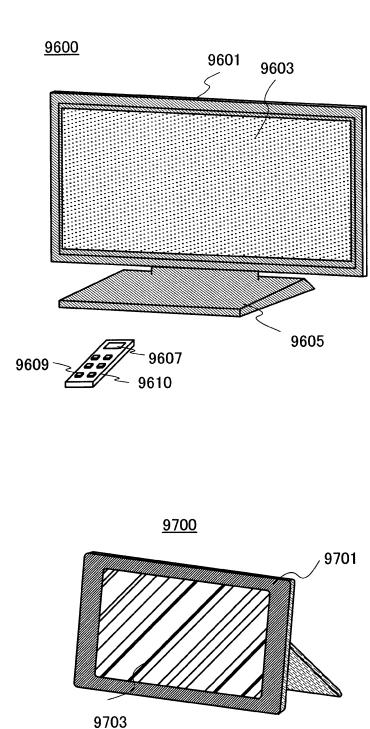

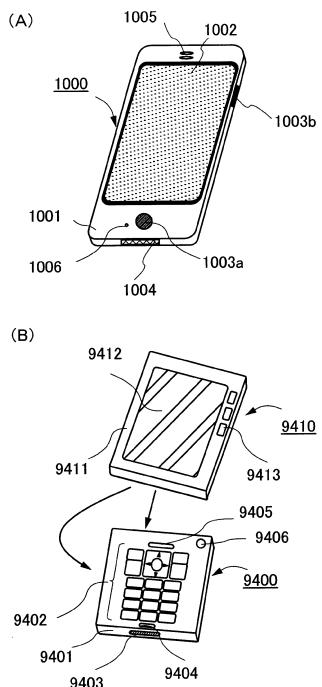

- 【図 13】テレビジョン装置およびデジタルフォトフレームの例を示す外観図。

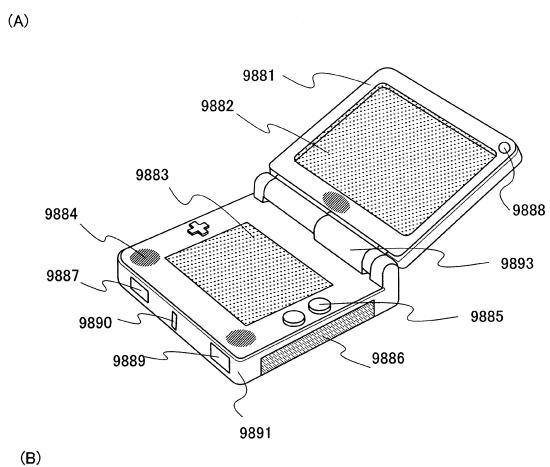

- 【図 14】遊技機の例を示す外観図。

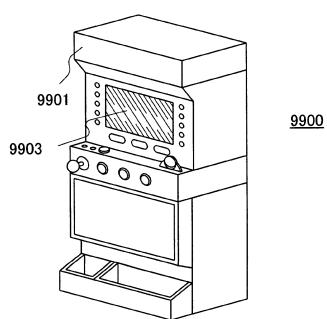

- 【図 15】携帯電話機の一例を示す外観図。

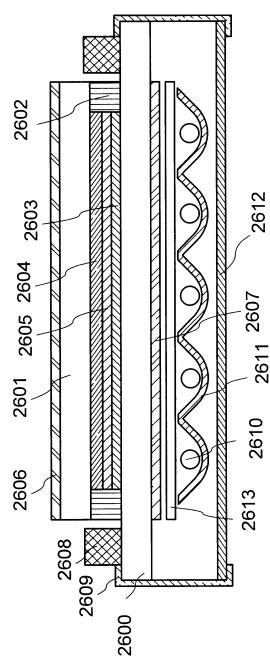

- 【図 16】液晶表示モジュールを説明する図。

- 【図 17】液晶表示装置の作製方法を説明する図。 10

- 【図 18】液晶表示装置の作製方法を説明する図。

- 【図 19】液晶表示装置を説明する図。

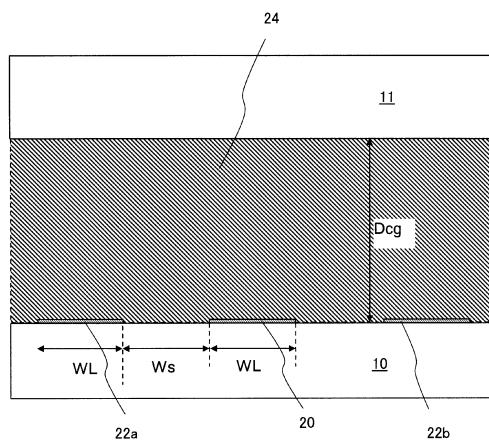

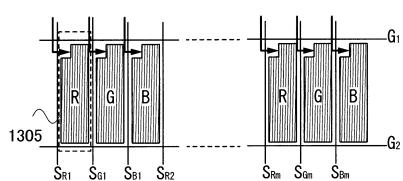

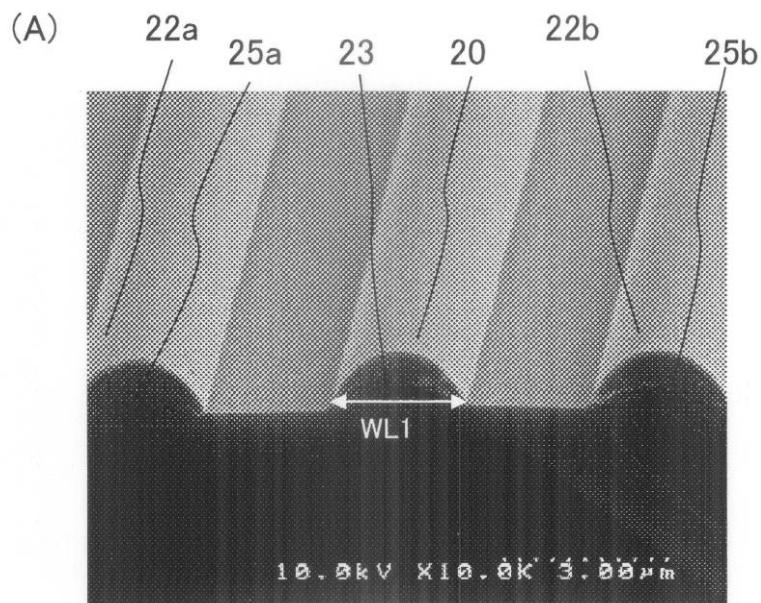

- 【図 20】実施例 1 の試料 1 及び試料 2 の構造を示す図。

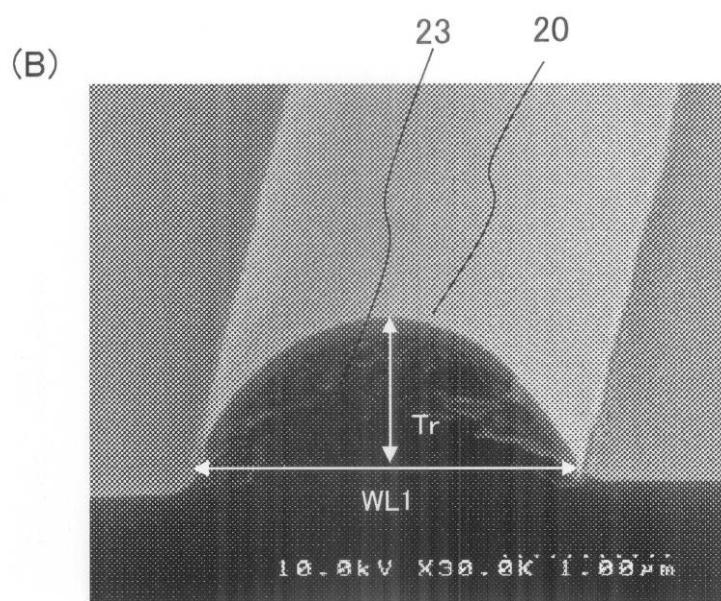

- 【図 21】試料 1 の S E M 像を示す図。

- 【図 22】比較試料の構造を示す図。

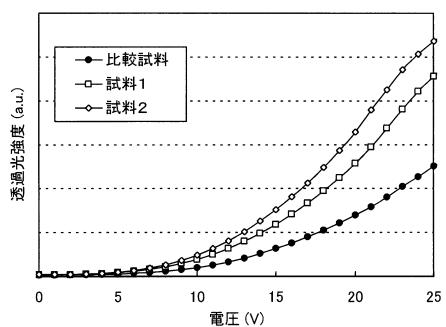

- 【図 23】印加電圧と透過光強度の関係を示す図。

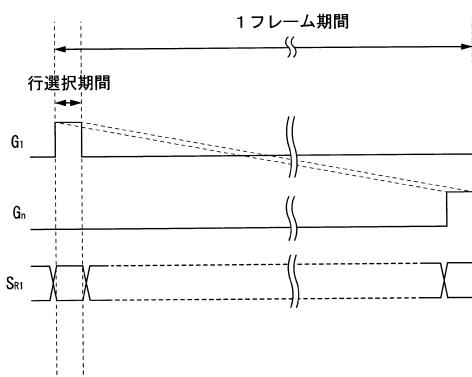

- 【図 24】液晶表示装置を説明するタイミングチャート。

- 【図 25】液晶表示装置に適用できるトランジスタ及びトランジスタの作製方法を説明する図。

- 【図 26】液晶表示装置に適用できるトランジスタ及びトランジスタの作製方法を説明する図。 20

- 【図 27】液晶表示装置に適用できるトランジスタ及びトランジスタの作製方法を説明する図。

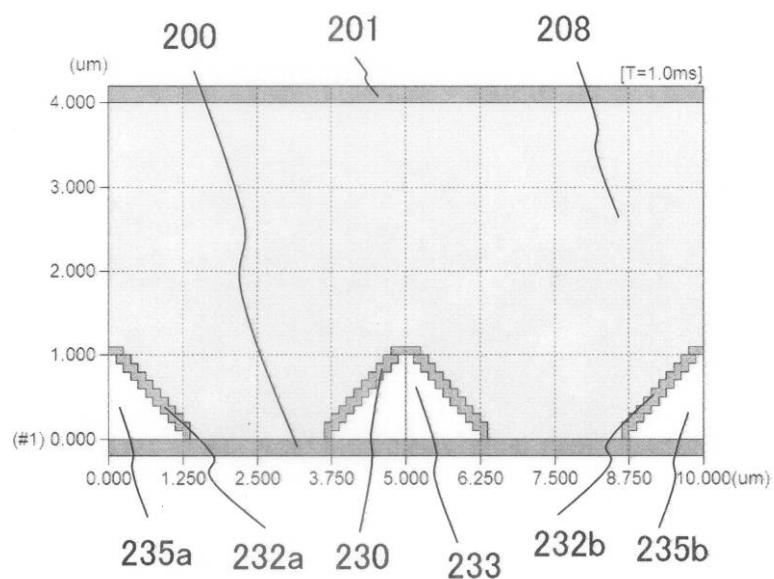

- 【図 28】液晶表示装置の電界モードの計算結果を説明する図。

- 【図 29】液晶表示装置の電界モードの計算結果を説明する図。

- 【図 30】液晶表示装置の電界モードの計算結果を説明する図。

- 【図 31】液晶表示装置の電界モードの計算結果を説明する図。

- 【図 32】液晶表示装置の電界モードの計算結果を説明する図。

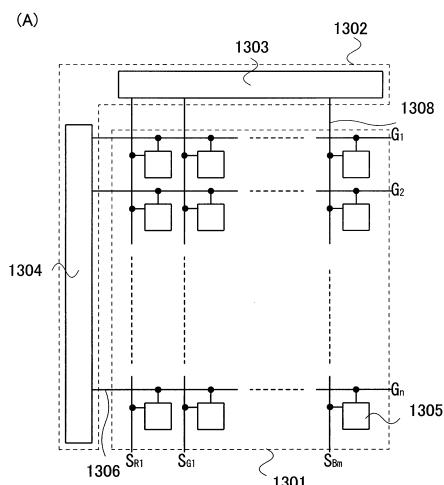

- 【図 33】液晶表示装置を説明するブロック図。

- 【発明を実施するための形態】 30

- 【0038】

- 実施の形態について、図面を用いて詳細に説明する。但し、以下の説明に限定されず、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

- 【0039】

- (実施の形態 1)

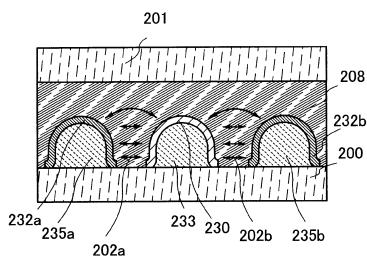

- 本明細書で開示する発明の構成の一形態である液晶表示装置を、図 1 を用いて説明する。

- 図 1 は液晶表示装置の断面図である。 40

- 【0040】

- ブルー相を示す液晶層を含む液晶表示装置において、基板に概略平行（すなわち水平な方向）な電界を生じさせて、基板と平行な面内で液晶分子を動かして、階調を制御する方式を用いることができる。このような方式として、IPS (In-Plane-Switching) モードで用いる電極構成が適用できる。

- 【0041】

- IPS モードなどに示される横電界モードは、液晶層の下方に開口パターンを有する第 1 の電極層（例えば各画素別に電圧が制御される画素電極層）及び第 2 の電極層（例えば全画素に共通の電圧が供給される共通電極層）を配置する。第 1 の電極層及び第 2 の電極層は、平面形状でなく、様々な開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む。 50

第1の電極層及び第2の電極層はその電極間に電界を発生させるため、同形状で重ならない配置とする。

【0042】

画素電極層と共通電極層との間に電界を加えることで、液晶を制御する。液晶には水平方向の電界が加わるため、その電界を用いて液晶分子を制御できる。つまり、基板と平行に配向している液晶分子を、基板と平行な方向で制御できるため、視野角が広くなる。

【0043】

図1は、第1の基板200と第2の基板201とが、ブルー相を示す液晶材料を用いた液晶層208を間に挟持して対向するように配置された液晶表示装置である。第1の基板200と液晶層208との間には第1の構造体233、画素電極層230、第2の構造体235a、235b、及び共通電極層232a、232bが設けられている。第1の構造体233、第2の構造体235a、235bは第1の基板200の液晶層208側の面から液晶層208中に突出して設けられている。

10

【0044】

画素電極層230は第1の基板200の液晶層208側の面（液晶層208に面している方の面）から液晶層208に突出して設けられた第1の構造体233の上面側面を覆って形成され、共通電極層232a、232bは第1の基板200の液晶層208側の面から液晶層208に突出して設けられた第2の構造体235a、235bの上面側面を覆って形成される。

【0045】

20

第1の構造体及び第2の構造体はリブ状である。リブ状の第1の構造体及び第2の構造体は、該上面及び側面に形成される画素電極層、又は共通電極層の形状を反映し、開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。

【0046】

第1の構造体233、第2の構造体235a、235bは断面が半円に近い先端が丸いドーム形状の構造体である。このように構造体表面が曲面を有していると上に積層する画素電極層、共通電極層が被覆性よく良好な形状で形成することができる。

【0047】

画素電極層230、共通電極層232a、232bは平板状ではなく、開口パターンを有する形状であるために、断面図においては分断された複数の電極層として示される。

30

【0048】

画素領域における画素電極層230及び共通電極層232a、232bが有する形状としては、閉空間を形成せず開かれた櫛歯状のようなパターンが好ましい。画素電極層230及び共通電極層232a、232bとは接せず、互いの櫛歯状のパターンがかみ合うように同一の絶縁表面である第1の基板200上に設けられている。

【0049】

図1の液晶表示装置において、第1の構造体233の上面及び側面を覆うように画素電極層230を設け、第2の構造体235a、235bの上面及び側面を覆うように共通電極層232a、232bを設けることで、画素電極層230及び共通電極層232a、232bの形成面積を液晶層208の膜厚方向に（3次元的に）も拡大できる。よって、図1に示すように、画素電極層230と共に電極層232aとの間に矢印202aに示す電界が、画素電極層230と共に電極層232bとの間に矢印202bに示す電界がそれぞれ液晶層の膜厚方向にわたって広範囲に加わる。なお、矢印202a、202bに示すように、画素電極層230と共に電極層232a、232bとの上面（上方領域）では電位線は円状に回り込むように形成される。

40

【0050】

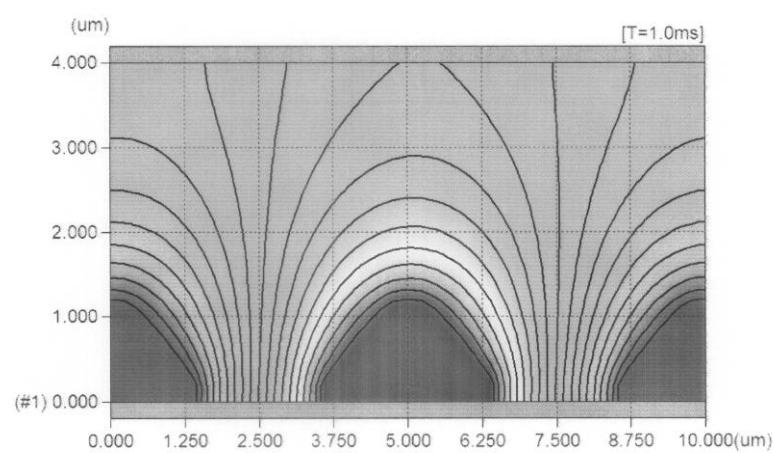

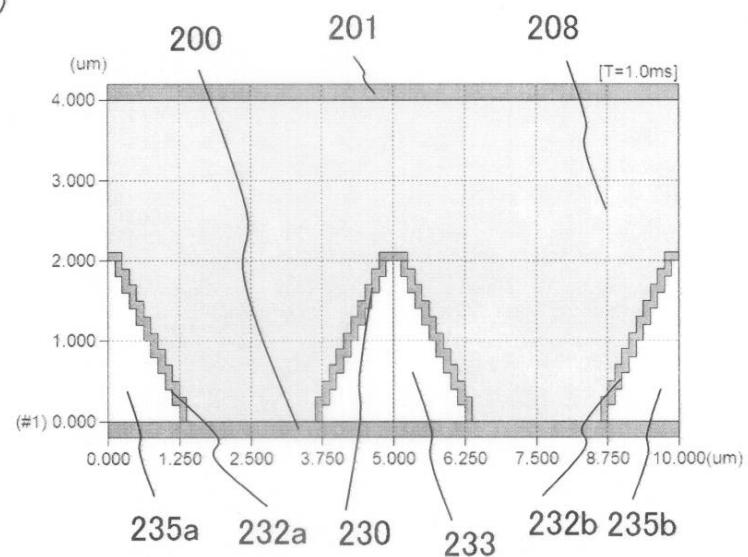

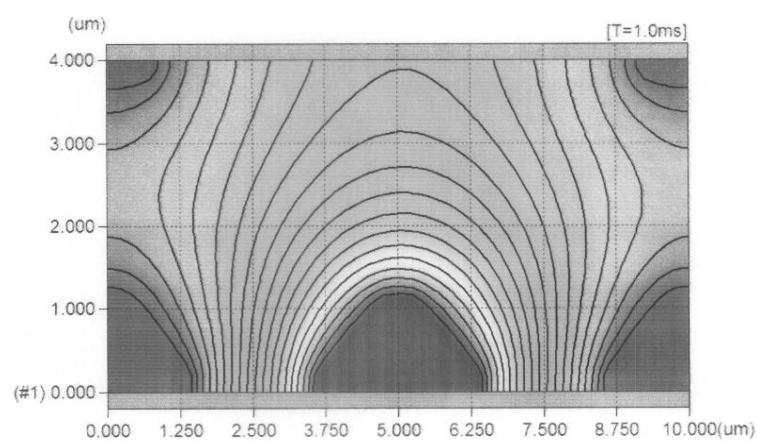

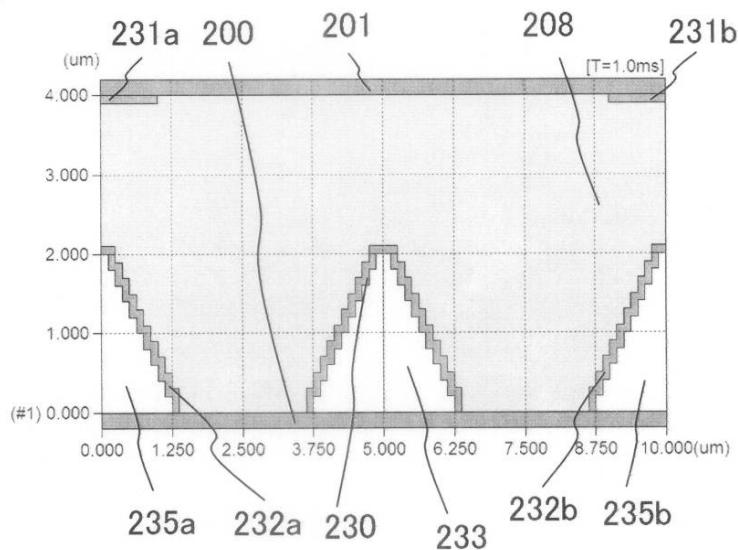

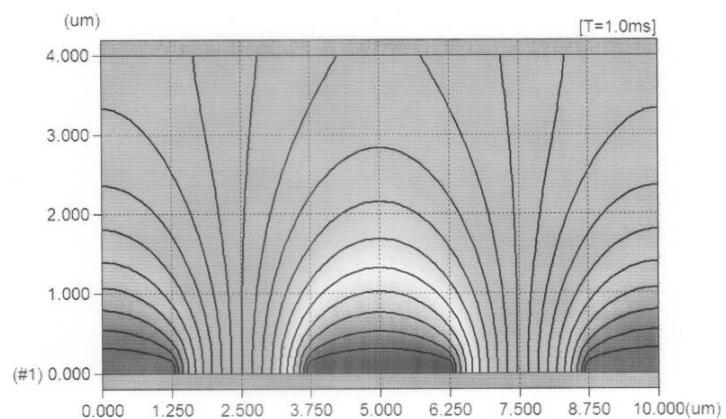

液晶表示装置における電界の印加状態を計算した結果を、図28（B）、図29（B）、及び図32（B）に示す。図28（A）、図29（A）、及び図32（A）は計算した液晶表示装置の構成を示す図である。計算は、シンテック社製、LCD Master、2s Benchを用いて行い、構造体（第1の構造体233、第2の構造体235a、2

50

35b)としては誘電率4の絶縁体を用い、断面の幅は2.5μmとした。図28(A)(B)においては第1の構造体233、第2の構造体235a、235bの膜厚(高さ)は1μm、図29(A)(B)においては第1の構造体233、第2の構造体235a、235bの膜厚(高さ)は2μmである。なお、ここでいう第1の構造体233、第2の構造体235a、235bの膜厚(高さ)は底面からの最大値である。

【0051】

図28(A)(B)及び図29(A)(B)において、画素電極層230は第1の構造体233の上面及び側面を覆うように形成され、同様に共通電極層232a、232bもそれぞれ第2の構造体235a、235bの上面及び側面を覆うように形成されている。画素電極層230、共通電極層232a、232bの膜厚は0.1μm、第1の構造体233と第2の構造体235a、235bとの間の距離は2.5μmである。セルギャップ(液晶層の最大膜厚)に相当する第1の基板200から第2の基板201まで距離は4μmである。

10

【0052】

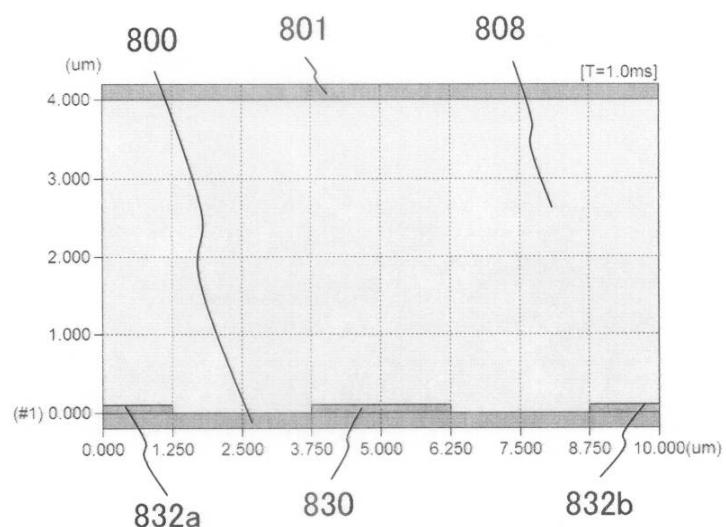

また、図32(A)(B)は比較例であり、第1の基板800と液晶層808との間に互い違いに共通電極層832a、832bと画素電極層830が設けられ、第2の基板801によって封止される例である。比較例断面における画素電極層830、共通電極層832a、832bの幅は2.5μm、厚さは0.1μm、セルギャップ(液晶層の最大膜厚)に相当する第1の基板800から第2の基板801まで距離は4μmである。

20

【0053】

図28(A)、図29(A)、及び図32(A)の構造に対して、共通電極層を0V、画素電極層は10Vの設定として計算した計算結果を図28(B)、図29(B)、及び図32(B)に示す。

【0054】

図28(B)、図29(B)、及び図32(B)において、実線は等電位線を示しており、円状に広がる等電位線の中心に画素電極層又は共通電極層が配置されている。

【0055】

電界は等電位線と垂直に発現するので、図28(B)、図29(B)に示すように、第1の構造体233表面を覆うように設けられた画素電極層230と、第2の構造体235a、235b表面を覆うように設けられた共通電極層232a、232bとの間にそれぞれ横方向の電界が加わっていることが確認できる。

30

【0056】

特に、膜厚の大きな第1の構造体233、及び第2の構造体235a、235bが設けられた図29においては、より広く液晶層に電界が形成されており、液晶層全体に広がって電界が形成することができる。

【0057】

一方、図32(B)においては、第1の基板上に互い違いに画素電極層830、共通電極層832a、832bが形成された第1の基板800近くの液晶層808には等電位線が見られ電界が形成されているが、第2の基板801に近づくにつれ電位線は分布せず電位差も生じていない。よって第2の基板801近くの液晶層808には電界が形成されず、図32の構成では、液晶層の全ての液晶分子を応答させることができることが確認できる。

40

【0058】

第1の構造体の上面及び側面を覆うように画素電極層を設け、第2の構造体の上面及び側面を覆うように共通電極層を設けることで、画素電極層及び共通電極層の形成面積を液晶層の膜厚方向に(3次元的に)も拡大できる。よって、画素電極層及び共通電極層間に電圧を印加した時、画素電極層と、共通電極層との間に広く電界を形成することができる。

【0059】

よって、画素電極層230及び共通電極層232a、232b間に電圧を印加した時、液晶層208において画素電極層230と、共通電極層232a、232bとの間に広く電

50

界を形成することができ、その電界を用いて液晶分子を制御できる。

【0060】

従って、膜厚方向も含め液晶層208全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率（黒表示時の光の透過率）との比であるコントラスト比も高くすることができる。また、粘度の高いブルー相を示す液晶材料（液晶混合物）であっても、効果的に電界を印加することができるため、低消費電力化も達成できる。

【0061】

構造体（第1の構造体、第2の構造体）は絶縁性材料（有機材料及び無機材料）を用いた絶縁体、及び導電性材料（有機材料及び無機材料）を用いた導電体で形成することができる。代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。例えば、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。また、導電性樹脂や金属材料で形成してもよい。なお、構造体は複数の薄膜の積層構造であってもよい。

10

【0062】

構造体の形状は、柱状、錐形の先端が平面である断面が台形の形状、錐形の先端が丸いドーム状などを用いることができる。本明細書において画素電極層及び共通電極層（第1の共通電極層）は構造体の表面（上面及び側面）を覆うように形成されるため、構造体は画素電極層及び共通電極層（第1の共通電極層）の被覆性が良好なように表面に段差が少なく曲面を有するような形状が好ましい。また、構造体は可視光の光に対して透光性を有する材料を用いると開口率や白透過率を低下させないために好ましい。

20

【0063】

また、構造体は基板の液晶層側の面から液晶層中に突出する部分であればよいので、層間膜を加工して液晶層側の表面を凹凸形状とし、突出する構造体としてもよい。よって、構造体は複数の突出した凸部を有する連続膜であってもよく、第1の構造体と第2の構造体が連続膜であってもよい。

【0064】

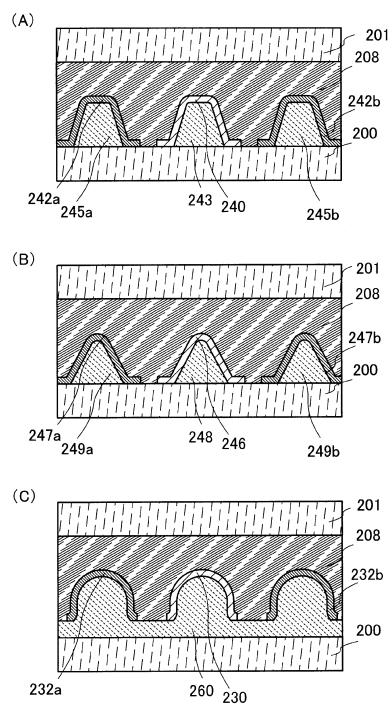

なお、構造体上に形成される画素電極層、共通電極層の形状は、該構造体の形状が反映され、またエッティング加工方法にも影響をうける。構造体及び該構造体上に形成される画素電極層、共通電極層の形状例を図19（A）（B）（C）に示す。

30

【0065】

図19（A）は、第1の構造体243上に画素電極層240が、第2の構造体245a、245b上に共通電極層242a、242bがそれぞれ形成される例である。第1の構造体243、第2の構造体245a、245bは錐形の先端が平面である断面が台形の形状であり、覆って形成されている画素電極層240、共通電極層242a、242bも該形状を反映している。また、画素電極層240、共通電極層242a、242bは第1の基板200に接するように形成されているが、その第1の基板200上に接して形成される面積は、画素電極層240、共通電極層242a、242bとが接しなければ適宜設定することができる。

40

【0066】

図19（B）は、第1の構造体248上に画素電極層246が、第2の構造体249a、249b上に共通電極層247a、247bがそれぞれ形成される例である。第1の構造体248、第2の構造体249a、249bは錐形の先端が丸い形状であり、覆って形成されている画素電極層246、共通電極層247a、247bも該形状を反映している。このように錐形の形状の場合、錐形の頂点付近で画素電極層246、共通電極層247a、247bが一部不連続になる場合（例えば膜に開口（穴）が形成されるなど）もありうるが、画素電極層246、共通電極層247a、247bとして電圧が印加できれば問題ない。

【0067】

図19（C）は、凹凸形状を有する構造体260の凸部に画素電極層230、共通電極層

50

232a、232bがそれぞれ形成される例である。凹凸形状を有する構造体260は絶縁層を加工して液晶層側の表面を凹凸形状とし、複数の突出した凸部を有する連続膜からなる構造体とした例である。よって、画素電極層230、共通電極層232a、232bは第1の構造体、第2の構造体に対応した突出した凸部にそれぞれ形成される。

【0068】

本明細書における図面においては、図1のように、画素電極層230と共通電極層232a、232bとを判別しやすいように異なるハッチで示している。これは機能が異なる電極層ということを明確に示すためであり、画素電極層230と共通電極層232a、232bとは同工程及び同材料によって形成することができる。図18に本実施の形態における液晶表示装置の作製方法の例を説明する。

10

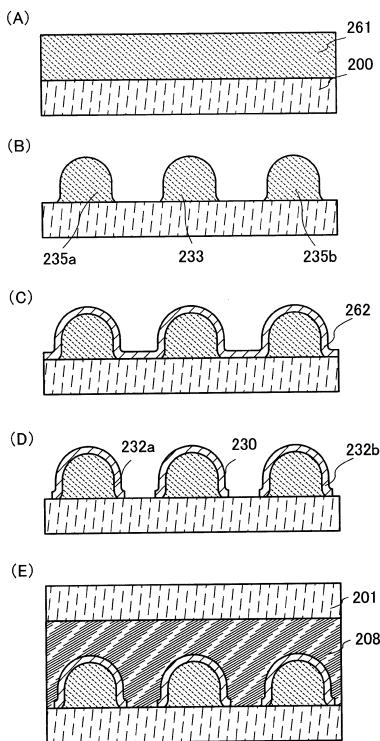

【0069】

第1の基板200上に構造体となる膜261を形成する(図18(A)参照。)。本実施の形態では、膜261として樹脂絶縁層を形成する。

【0070】

膜261を、フォトリソグラフィ工程を用いたエッチングにより加工し、第1の構造体233、第2の構造体235a、235bを形成する(図18(B)参照。)。なお、第1の構造体233、第2の構造体235a、235bをインクジェット法などの印刷法で形成してもよい。インクジェット法などの印刷法で形成するとフォトリソグラフィ工程を用いないため、工程が簡略化し、製造コストを低減できる。

20

【0071】

次に、第1の構造体233、第2の構造体235a、235b上に導電膜262を形成する(図18(C)参照。)。

【0072】

導電膜262を、フォトリソグラフィ工程を用いたエッチングにより加工し、画素電極層230、共通電極層232a、232bを形成する(図18(D)参照。)。

【0073】

第1の構造体233、第2の構造体235a、235b、画素電極層230、共通電極層232a、232bが形成された第1の基板200と対向基板となる第2の基板201を液晶層208を挟持するように固着し、液晶表示装置を作製する(図18(E)参照。)。

30

【0074】

以上のように、第1の構造体233、及び第2の構造体235a、235bを同工程同材料で形成し、また画素電極層230、及び共通電極層232a、232bを同工程同材料で形成することができる。図18(E)においては、同工程同材料で形成されたことが明確に分かりやすいように画素電極層230、及び共通電極層232a、232bは同じハッチで示している。もちろん、第1の構造体233、及び第2の構造体235a、235bを異なる工程や材料で形成すること、また画素電極層230、及び共通電極層232a、232bを異なる工程や材料で形成することも適宜組み合わせて液晶表示装置を作製することができる。

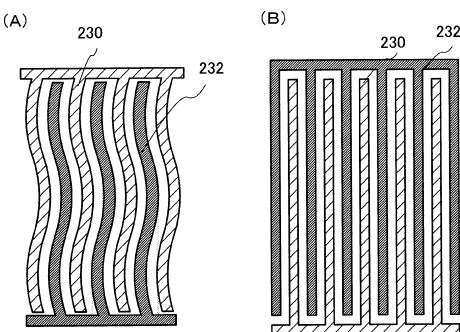

【0075】

図8(A)(B)に画素電極層230、共通電極層232(232a、232b)に適用できる例を示す。図8(A)(B)は画素電極層230と共通電極層232の平面図である。画素電極層230と共通電極層232は櫛歯形状の電極層であり、櫛歯が互いにかみ合うように設けられており、図8(A)はうねりを有する波状形状である。また、第1の構造体及び第2の構造体は画素電極層及び共通電極層下に選択的に設けられてもよい。画素電極層230及び共通電極層232の形状が複雑な場合、第1の構造体233及び第2の構造体235a、235bを選択的に設けることで、液晶材料の注入、充填工程が容易になり工程時間も短くてすむ。

40

【0076】

液晶層208を形成する方法として、ディスペンサ法(滴下法)や、第1の基板200と

50

第2の基板201とを貼り合わせてから毛細管現象等を用いて液晶を注入する注入法を用いることができる。

#### 【0077】

液晶層208には、ブルー相を示す液晶材料を用いる。ブルー相を示す液晶材料は、応答速度が1msec以下と短く高速応答が可能であるため、液晶表示装置の高性能化が可能になる。

#### 【0078】

例えば、高速応答が可能であるため、バックライト装置にRGBの発光ダイオード(LED)等を配置し、時分割によりカラー表示する継時加法混色法(フィールドシーケンシャル法)や、時分割により左目用、右目用の映像を交互に見るシャッター眼鏡方式による3次元表示方式に好適に採用できる。

10

#### 【0079】

ブルー相を示す液晶材料として液晶及びカイラル剤を含む。カイラル剤は、液晶を螺旋構造に配向させ、ブルー相を発現させるために用いる。例えば、5重量%以上のカイラル剤を混合させた液晶材料を液晶層に用いればよい。

#### 【0080】

液晶は、サーモトロピック液晶、低分子液晶、高分子液晶、強誘電液晶、反強誘電液晶等を用いる。

#### 【0081】

カイラル剤は、液晶に対する相溶性が良く、かつ捩れ力の強い材料を用いる。また、R体、S体のどちらか片方の材料が良く、R体とS体の割合が50:50のラセミ体は使用しない。

20

#### 【0082】

上記液晶材料は、条件により、コレステリック相、コレステリックブルー相、スマクチック相、スマクチックブルー相、キューピック相、カイラルネマチック相、等方相等を示す。

#### 【0083】

ブルー相であるコレステリックブルー相及びスマクチックブルー相は、螺旋ピッチが500nm以下とピッチの比較的短いコレステリック相またはスマクチック相を有する液晶材料にみられる。液晶材料の配向は二重ねじれ構造を有する。可視光の波長以下の秩序を有しているため、透明であり、電圧印加によって配向秩序が変化して光学的変調作用が生じる。ブルー相は光学的に等方であるため視野角依存性がなく、配向膜を形成しなくとも良いため、表示画像の質の向上及びコスト削減が可能である。

30

#### 【0084】

また、ブルー相は狭い温度範囲でしか発現が難しく、温度範囲を広く改善するために液晶材料に、光硬化樹脂及び光重合開始剤を添加し、高分子安定化処理を行うことが好ましい。高分子安定化処理は、液晶、カイラル剤、光硬化樹脂、及び光重合開始剤を含む液晶材料に、光硬化樹脂、及び光重合開始剤が反応する波長の光を照射して行う。この高分子安定化処理は、温度制御を行い、等方相を示した状態で光照射して行っても良いし、ブルー相を示した状態で光照射して行ってもよい。

40

#### 【0085】

例えば、液晶層の温度を制御し、ブルー相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行う。但し、これに限定されず、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内の等方相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行ってもよい。ブルー相と等方相間の相転移温度とは、昇温時にブルー相から等方相に転移する温度又は降温時に等方相からブルー相に相転移する温度をいう。高分子安定化処理の一例としては、液晶層を等方相まで加熱した後、徐々に降温させてブルー相にまで相転移させ、ブルー相が発現する温度を保持した状態で光を照射することができる。他にも、液晶層を徐々に加熱して等方相に相転移させた後、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内状態(等方相を

50

発現した状態)で光を照射することができる。また、液晶材料に含まれる光硬化樹脂として、紫外線硬化樹脂(UV硬化樹脂)を用いる場合、液晶層に紫外線を照射すればよい。なお、ブルー相を発現させなくとも、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内状態(等方相を発現した状態)で光を照射して高分子安定化処理を行えば、応答速度が1msec以下と短く高速応答が可能である。

【0086】

光硬化樹脂は、アクリレート、メタクリレートなどの単官能モノマーでもよく、ジアクリレート、トリアクリレート、ジメタクリレート、トリメタクリレートなどの多官能モノマーでもよく、これらを混合させたものでもよい。また、液晶性のものでも非液晶性のものでもよく、両者を混合させてよい。光硬化樹脂は、用いる光重合開始剤の反応する波長の光で硬化する樹脂を選択すれば良く、代表的には紫外線硬化樹脂を用いることができる。

10

【0087】

光重合開始剤は、光照射によってラジカルを発生させるラジカル重合開始剤でもよく、酸を発生させる酸発生剤でもよく、塩基を発生させる塩基発生剤でもよい。

【0088】

具体的には、液晶材料として、JC-1041XX(チッソ株式会社製)と4-シアノ-4'-ペンチルビフェニルの混合物を用いることができ、カイラル剤としては、ZLI-4572(メルク株式会社製)を用いることができ、光硬化樹脂は、2-エチルヘキシリアクリレート、RM257(メルク株式会社製)、トリメチロールプロパントリアクリレートを用いることができ、光重合開始剤としては2,2-ジメトキシ-2-フェニルアセトフェノンを用いることができる。

20

【0089】

また、図1では図示しないが、偏光板、位相差板、反射防止膜などの光学フィルムなどは適宜設ける。例えば、偏光板及び位相差板による円偏光を用いてよい。また、光源としてバックライトなどを用いることができる。

【0090】

本明細書において、液晶表示装置は光源の光を透過することによって表示を行う透過型の液晶表示装置である(又は半透過型の液晶表示装置)場合、少なくとも画素領域において光を透過させる必要がある。よって光が透過する画素領域に存在する第1の基板、第2の基板、他絶縁膜、導電膜などの薄膜はすべて可視光の波長領域の光に対して透光性とする。

30

【0091】

画素電極層、共通電極層においては透光性が好ましいが、開口パターンを有するために形状によっては金属膜などの非透光性材料を用いてよい。

【0092】

画素電極層、共通電極層は、インジウム錫酸化物(ITO)、酸化インジウムに酸化亜鉛(ZnO)を混合したIZO(indium zinc oxide)、酸化インジウムに酸化珪素(SiO<sub>2</sub>)を混合した導電材料、有機インジウム、有機スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、またはタンゲステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

40

【0093】

第1の基板200、第2の基板201にはバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、石英基板、プラスチック基板などを用いることができる。

【0094】

50

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

【0095】

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

【0096】

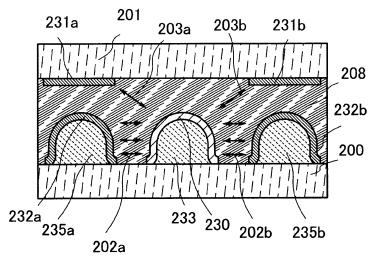

(実施の形態2)

本明細書で開示する発明の構成の他の一形態である液晶表示装置を、図2を用いて説明する。図2は液晶表示装置の断面図であり、実施の形態1で示す液晶表示装置において、対向基板(第2の基板)側にも共通電極層を設ける構成である。なお、実施の形態1と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

10

【0097】

図2は、第1の基板200と第2の基板201とが、ブルー相を示す液晶材料を用いた液晶層208を間に挟持して対向するように配置された液晶表示装置である。第1の基板200と液晶層208との間には第1の構造体233、画素電極層230、第2の構造体235a、235b、及び共通電極層232a、232bが設けられている。第1の構造体233、第2の構造体235a、235bは第1の基板200の液晶層208側の面から液晶層208中に突出して設けられている。

20

【0098】

共通電極層は、対向基板(第2の基板)側にも一対の共通電極層が対向するように設けてもよく、図2のように液晶層208を間に挟んで第1の基板200側の共通電極層(第1の共通電極層ともいう)232a、232bと、第2の基板側に共通電極層(第3の電極層、第2の共通電極層ともいう)231a、231bとがお互いに重畳するように配置される。

【0099】

画素電極層230、共通電極層232a、232b、及び共通電極層231a、231bは平板状でなく、様々な開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。また、共通電極層231a、231bを形成する場合、共通電極層232a、232b及び共通電極層231a、231bは少なくとも画素領域において、平面図でみるとほぼ同形状であり液晶層を介して重畳するように配置される。なお、図2の断面図では、共通電極層232a、232bの端部と共通電極層231a、231bの端部とは一致する例を示しているが、少なくとも一部重なって(重畳して)いれば端部が揃っていないてもよい(例えば、共通電極層232a、232bの端部が共通電極層231a、231bの端部より、外側に位置している、又は逆に内側に位置しているなど)。

30

【0100】

画素電極層230は第1の基板200の液晶層208側の面(液晶層208に面している方の面)から液晶層208に突出して設けられた第1の構造体233の上面側面を覆って形成され、共通電極層232a、232bは第1の基板200の液晶層208側の面から液晶層208に突出して設けられた第2の構造体235a、235bの上面側面を覆って形成される。

40

【0101】

画素電極層230及び共通電極層232a、232bが有する形状としては、閉空間を形成せず開かれた櫛歯状のようなパターンが好ましい。画素電極層230及び共通電極層232a、232bとは接せず、互いの櫛歯状のパターンがかみ合うように同一の絶縁表面である第1の基板200上に設けられている。

【0102】

図2の液晶表示装置において、第1の構造体233の上面及び側面を覆うように画素電極層230を設け、第2の構造体235a、235bの上面及び側面を覆うように共通電極層232a、232bを設けることで、画素電極層230及び共通電極層232a、232bを設けること

50

2 b の形成面積を液晶層 2 0 8 の膜厚方向に(3次元的に)も拡大できる。よって、図2に示すように、画素電極層 2 3 0 と共に電極層 2 3 2 a との間に矢印 2 0 2 a に示す電界が、画素電極層 2 3 0 と共に電極層 2 3 2 b との間に矢印 2 0 2 b に示す電界がそれぞれ液晶層の膜厚方向にわたって広範囲に加わる。

【0103】

さらに、本実施の形態のように、第2の基板 2 0 1 側に第2の共通電極層として共通電極層 2 3 1 a、2 3 1 b を設けると、画素電極層 2 3 0 と共に電極層 2 3 1 a、2 3 1 b との間に液晶に対して斜め方向(基板に対して斜めの方向)の電界も加えることができるため、より効率よく液晶分子を制御できる。

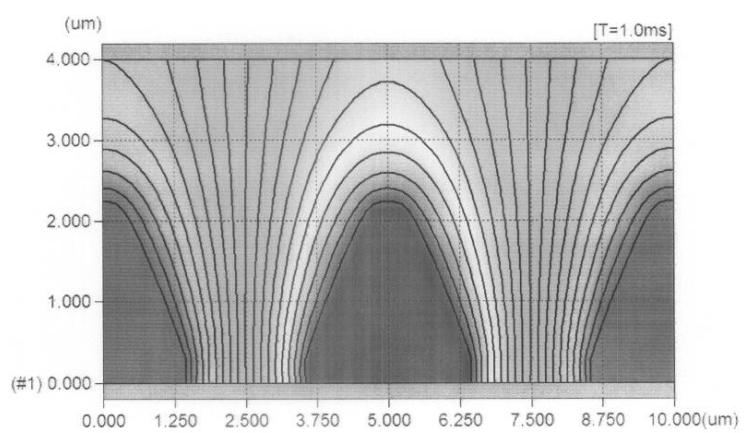

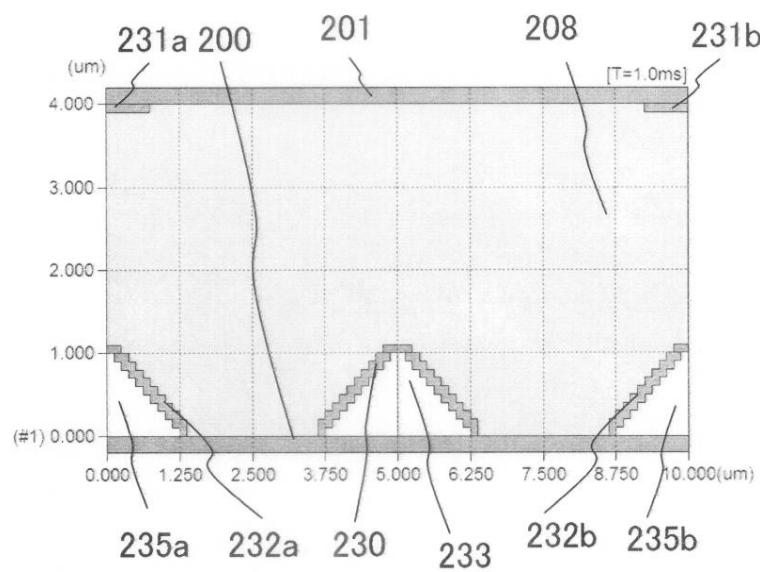

【0104】

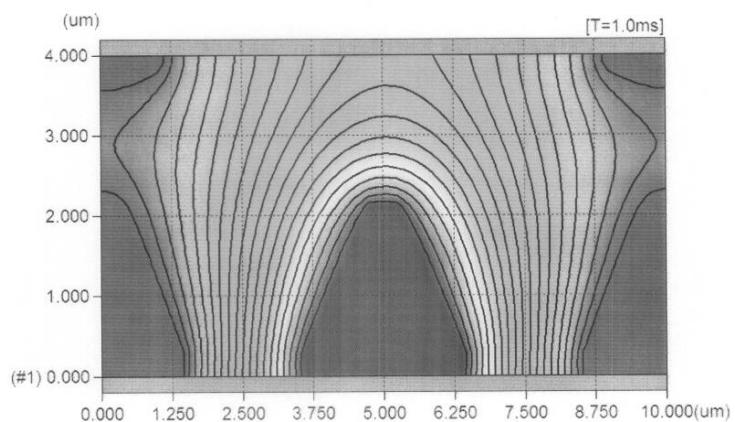

液晶表示装置における電界の印加状態を計算した結果を、図30(B)、図31(B)、及び図32(B)に示す。図30(A)、図31(A)、及び図32(A)は計算した液晶表示装置の構成を示す図である。計算は、シンテック社製、LCD Master、2s Benchを用いて行い、構造体(第1の構造体 2 3 3、第2の構造体 2 3 5 a、2 3 5 b)としては誘電率4の絶縁体を用い、断面の幅は2.5 μmとした。図30(A)(B)においては第1の構造体 2 3 3、第2の構造体 2 3 5 a、2 3 5 b の膜厚(高さ)は1 μm、図31(A)(B)においては第1の構造体 2 3 3、第2の構造体 2 3 5 a、2 3 5 b の膜厚(高さ)は2 μmである。なお、ここでいう第1の構造体 2 3 3、第2の構造体 2 3 5 a、2 3 5 b の膜厚(高さ)は底面からの最大値である。また、図30(A)(B)、図31(A)(B)において第2の基板 2 0 1 と液晶層 2 0 8 との間に共通電極層 2 3 2 a、2 3 2 b と重なるように共通電極層 2 3 1 a、2 3 1 b が設けられている。

【0105】

図30(A)(B)及び図31(A)(B)において、画素電極層 2 3 0 は第1の構造体 2 3 3 の上面及び側面を覆うように形成され、同様に共通電極層 2 3 2 a、2 3 2 b もそれぞれ第2の構造体 2 3 5 a、2 3 5 b の上面及び側面を覆うように形成されている。画素電極層 2 3 0 、共通電極層 2 3 2 a、2 3 2 b 、共通電極層 2 3 1 a、2 3 1 b の膜厚は0.1 μm、第1の構造体 2 3 3 と第2の構造体 2 3 5 a、2 3 5 b との間の距離は2.5 μmである。セルギャップ(液晶層の最大膜厚)に相当する第1の基板 2 0 0 から第2の基板 2 0 1 まで距離は4 μmである。なお、共通電極層 2 3 1 a と共通電極層 2 3 1 b との距離は8 μm、共通電極層 2 3 1 a、2 3 1 b の幅は1 μmである。

【0106】

また、図32(A)(B)は比較例であり、第1の基板 8 0 0 と液晶層 8 0 8 との間に互い違いに共通電極層 8 3 2 a、8 3 2 b と画素電極層 8 3 0 が設けられ、第2の基板 8 0 1 によって封止される例である。比較例断面における画素電極層 8 3 0 、共通電極層 8 3 2 a、8 3 2 b の幅は2.5 μm、厚さは0.1 μm、セルギャップ(液晶層の最大膜厚)に相当する第1の基板 8 0 0 から第2の基板 8 0 1 まで距離は4 μmである。

【0107】

図30(A)、図31(A)、及び図32(A)の構造に対して、共通電極層を0V、画素電極層は10Vの設定として計算した計算結果を図30(B)、図31(B)、及び図32(B)に示す。

【0108】

図30(B)、図31(B)、及び図32(B)において、実線は等電位線を示しており、円状に広がる等電位線の中心に画素電極層又は共通電極層が配置されている。

【0109】

電界は等電位線と垂直に発現するので、図30(B)、図31(B)に示すように、第1の構造体 2 3 3 表面を覆うように設けられた画素電極層 2 3 0 と、第2の構造体 2 3 5 a、2 3 5 b 表面を覆うように設けられた共通電極層 2 3 2 a、2 3 2 b との間にそれぞれ横方向の電界が加わっていることが確認できる。

【0110】

10

20

30

40

50

さらに、画素電極層 230 と、共通電極層 231a、231bとの間に斜め方向にも電界を形成することができる。よって、液晶層 208 全体に広く電界を形成することが可能となる。

【0111】

特に、膜厚の大きな第1の構造体 233、及び第2の構造体 235a、235b が設けられた図31においては、より広く液晶層に電界が形成されており、液晶層全体に広がって電界を形成することができる。

【0112】

一方、図32(B)においては、第1の基板上に互い違いに画素電極層 830、共通電極層 832a、832b が形成された第1の基板 800 近くの液晶層 808 には等電位線が見られ電界が形成されているが、第2の基板 801 に近づくにつれ電位線は分布せず電位差も生じていない。よって第2の基板 801 近くの液晶層 808 には電界が形成されず、図32の構成では、液晶層の全ての液晶分子を応答させることが難しいことが確認できる。

10

【0113】

第1の構造体の上面及び側面を覆うように画素電極層を設け、第2の構造体の上面及び側面を覆うように第1の共通電極層を設けることで、画素電極層及び第1の共通電極層の形成面積を液晶層の膜厚方向に(3次元的に)も拡大できる。さらに第2の基板側において画素電極層と重ならない位置に第2の共通電極層を設けることによって、画素電極層と第2の共通電極層との間に斜め電界が形成できる。従って、画素電極層と、及び第1の共通電極層、及び第2の共通電極層間に電圧を印加した時、画素電極層と、及び第1の共通電極層、及び第2の共通電極層との間に広く電界を形成することができる。

20

【0114】

よって、画素電極層 230 と、共通電極層 232a、232b、共通電極層 231a、231bとの間に電圧を印加した時、液晶層 208 において広く電界を形成することができ、その電界を用いて液晶分子を制御できる。

【0115】

従って、膜厚方向も含め液晶層 208 全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率(黒表示時の光の透過率)との比であるコントラスト比も高くすることができる。また、粘度の高いブルー相を示す液晶材料(液晶混合物)であっても、効果的に電界を印加することができるため、低消費電力化も達成できる。

30

【0116】

第2の共通電極層である共通電極層 231a、231b は実施の形態1で示した共通電極層 232a、232b と同様な材料及び方法で形成することができる。

【0117】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

【0118】

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

40

【0119】

(実施の形態3)

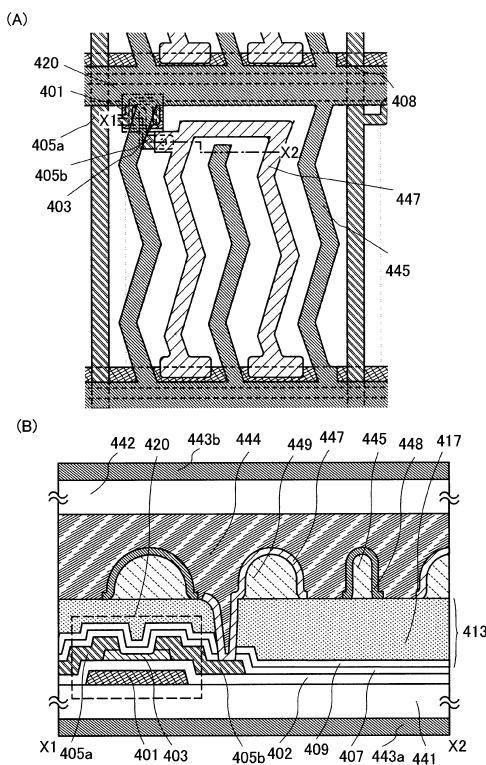

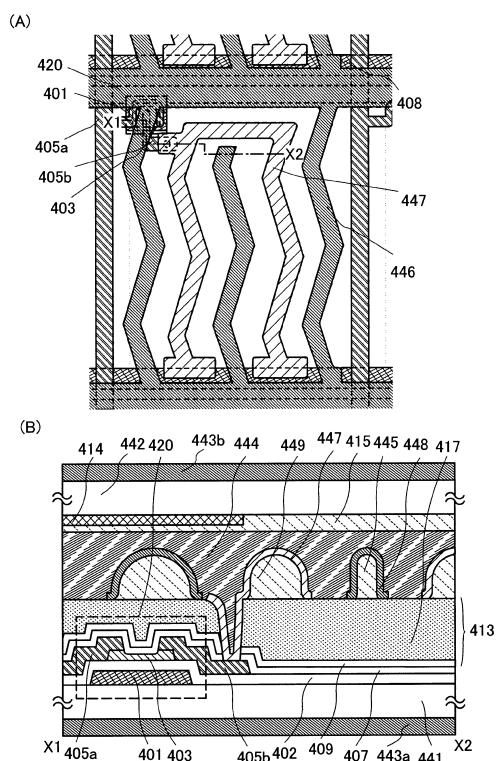

本明細書に開示する発明を適用したアクティブマトリクス型の液晶表示装置の例を、図3を用いて説明する。

【0120】

図3(A)は液晶表示装置の平面図であり1画素分の画素を示している。図3(B)は図3(A)の線X1-X2における断面図である。

【0121】

図3(A)において、複数のソース配線層(配線層 405a を含む)が互いに平行(図中

50

上下方向に延伸)かつ互いに離間した状態で配置されている。複数のゲート配線層(ゲート電極層401を含む)は、ソース配線層に略直交する方向(図中左右方向)に延伸し、かつ互いに離間するように配置されている。容量配線層408は、複数のゲート配線層それぞれに隣接する位置に配置されており、ゲート配線層に概略平行な方向、つまり、ソース配線層に概略直交する方向(図中左右方向)に延伸している。ソース配線層と、容量配線層408及びゲート配線層とによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極層、共通電極層が液晶層444を介して配置されている。画素電極層を駆動するトランジスタ420は、図中左上の角に配置されている。画素電極層及びトランジスタは、マトリクス状に複数配置されている。

【0122】

10

図3(B)の液晶表示装置において、トランジスタ420に電気的に接続する第1の電極層447が画素電極層として機能し、第2の電極層448が共通電極層として機能する。なお、第1の電極層447と容量配線層408によって容量が形成されている。共通電極層とはフローティング状態(電気的に孤立した状態)として動作させることも可能だが、固定電位、好ましくはコモン電位(データとして送られる画像信号の中間電位)近傍でフリッカーの生じないレベルに設定してもよい。なお、共通電極層を実施の形態2のように第1の共通電極層及び第2の共通電極層と2種類設ける場合は等電位が好ましい。

【0123】

画素電極層である第1の電極層447は第1の基板441(素子基板ともいう)上の層間膜413の液晶層444側の面から液晶層444に突出して設けられた第1の構造体449の上面側面を覆って形成され、第2の電極層448は第1の基板441上の層間膜413の液晶層444側の面から液晶層444に突出して設けられた第2の構造体445の上面側面を覆って形成される。

20

【0124】

また、図3の断面図において、第1の電極層447と、第2の電極層448とは重疊せず互い違いに設けられている。

【0125】

第1の電極層447、及び第2の電極層448は平板状ではなく、様々な開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。

【0126】

30

第1の構造体449及び第2の構造体445はリブ状である。リブ状の第1の構造体449及び第2の構造体445は、該上面及び側面に形成される第1の電極層447、又は第2の電極層448の形状を反映し、開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。

【0127】

第1の構造体449の上面及び側面を覆うように第1の電極層447を設け、第2の構造体445の上面及び側面を覆うように第2の電極層448を設けることで、第1の電極層447及び第2の電極層448の形成面積を液晶層444の膜厚方向に(3次元的に)も拡大できる。よって、第1の電極層447及び第2の電極層448間に電圧を印加した時、第1の電極層447と、第2の電極層448との間に広く電界を形成することができる。

40

【0128】

なお、実施の形態2のように、共通電極層は、対向基板(第2の基板)側にも一対の共通電極層が対向するように設けてもよく、この場合液晶層を間に挟んで第1の基板側の第1の共通電極層と、第2の基板側に第2の共通電極層(第3の電極層)とがお互いに重疊するように配置される。

【0129】

また、第2の基板側に第2の共通電極層を設けると、画素電極層と第2の共通電極層との間に液晶に対して斜め方向(基板に対して斜めの方向)の電界も加えることができるため、より効率よく液晶分子を制御できる。

50

## 【0130】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率（黒表示時の光の透過率）との比であるコントラスト比も高くすることができる。

## 【0131】

構造体は絶縁性材料（有機材料及び無機材料）を用いた絶縁体、及び導電性材料（有機材料及び無機材料）を用いた導電体で形成することができる。代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。例えば、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。また、導電性樹脂や金属材料で形成してもよい。なお、構造体は複数の薄膜の積層構造であってもよい。

10

## 【0132】

構造体の形状は、柱状、錐形の先端が平面である断面が台形の形状、錐形の先端が丸いドーム状などを用いることができる。本明細書において画素電極層及び共通電極層（第1の共通電極層）は構造体の表面（上面及び側面）を覆うように形成されるため、構造体は画素電極層及び共通電極層（第1の共通電極層）の被覆性が良好なように表面に段差が少なく曲面を有するような形状が好ましい。また、構造体は可視光の光に対して透光性を有する材料を用いると開口率や白透過率を低下させないために好ましい。

## 【0133】

また、構造体は第1の基板の液晶層側の面から液晶層中に突出する部分であればよいので、層間膜を加工して液晶層側の表面を凹凸形状とし、突出する構造体としてもよい。よって、構造体は複数の突出した凸部を有する連続膜であってもよく、第1の構造体と第2の構造体が連続膜であってもよい。

20

## 【0134】

構造体の形成方法は特に限定されず、材料に応じて、蒸着法、スパッタ法、CVD法などの乾式法、又はスピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法）、ナノインプリント、各種印刷法（スクリーン印刷、オフセット印刷）等などの湿式法を用い、必要に応じてエッチング法（ドライエッチング又はウェットエッチング）により所望のパターンに加工すればよい。

## 【0135】

図3（B）のように、第1の電極層447が形成される第1の構造体449、第2の構造体445は、端部に曲率を有するテーパー形状であると第1の電極層447、第2の電極層448の被膜性が向上するために好ましい。本実施の形態では、第1の電極層447はトランジスタ420の配線層405bと接し、第1の構造体449上にまで連続的に成膜される例であるが、配線層405bと接する電極層を形成し、その電極層を介して第1の電極層447と配線層405bが電気的に接続されるように第1の電極層447を形成してもよい。

30

## 【0136】

また、トランジスタを覆って層間膜を形成し、層間膜上に構造体を形成する場合、構造体をエッチング加工によって形成した後、層間膜にトランジスタに接続するためのコンタクトホールを開口してもよい。なお図3は、層間膜及び構造体となる絶縁膜にコンタクトホールを形成した後、絶縁膜をエッチング加工して構造体を形成する例である。

40

## 【0137】

トランジスタ420は逆スタガ型の薄膜トランジスタであり、絶縁表面を有する基板である第1の基板441上に、ゲート電極層401、ゲート絶縁層402、半導体層403、ソース電極層又はドレイン電極層として機能する配線層405a、405bを含む。

## 【0138】

トランジスタ420を覆い、半導体層403に接する絶縁膜407、絶縁層409が設けられ、絶縁層409上に層間膜413が積層されている。

## 【0139】

液晶表示装置にカラーフィルタ層として機能する着色層を設けることができる。カラーフ

50

イルタ層は、第1の基板441及び第2の基板442より外側（液晶層444と反対側）に設けてもよいし、第1の基板441及び第2の基板442より内側に設けてもよい。

【0140】

カラーフィルタは、液晶表示装置をフルカラー表示とする場合、赤色（R）、緑色（G）、青色（B）を呈する材料から形成すればよく、モノカラー表示とする場合、着色層を無くす、もしくは少なくとも一つの色を呈する材料から形成すればよい。なお、バックライト装置にRGBの発光ダイオード（LED）等を配置し、時分割によりカラー表示する緒時加法混色法（フィールドシーケンシャル法）を採用するときには、カラーフィルタを設けない場合もある。

【0141】

図3の液晶表示装置は、層間膜413に、カラーフィルタ層として機能する有彩色の透光性樹脂層417を用いる例である。

【0142】

カラーフィルタ層を対向基板側に設ける場合、トランジスタが形成される素子基板との、正確な画素領域の位置合わせが難しく画質を損なう恐れがあるが、層間膜をカラーフィルタ層として直接素子基板側に形成するのでより精密な形成領域の制御ができ、微細なパターンの画素にも対応することができる。また、層間膜とカラーフィルタ層を同一の絶縁層で兼ねるので、工程が簡略化し、より低コストで液晶表示装置が作製可能となる。

【0143】

有彩色の透光性樹脂としては、感光性、非感光性の有機樹脂を用いることができる。感光性の有機樹脂層を用いるとレジストマスク数を削減することができるため、工程が簡略化し好ましい。また、層間膜に形成するコンタクトホールも曲率を有する開口形状となるために、コンタクトホールに形成される電極層などの膜の被覆性も向上させることができる。

【0144】

有彩色は、黒、灰、白などの無彩色を除く色であり、着色層はカラーフィルタとして機能させるため、その着色された有彩色の光のみを透過する材料で形成される。有彩色としては、赤色、緑色、青色などを用いることができる。また、シアン、マゼンダ、イエロー（黄）などを用いてもよい。着色された有彩色の光のみを透過するとは、着色層において透過する光は、その有彩色の光の波長にピークを有するということである。

【0145】

有彩色の透光性樹脂層417は、着色層（カラーフィルタ）として機能させるため、含ませる着色材料の濃度と光の透過率の関係に考慮して、最適な膜厚を適宜制御するとよい。層間膜413を複数の薄膜で積層する場合、少なくとも一層が有彩色の透光性樹脂層であれば、カラーフィルタとして機能させることができる。

【0146】

有彩色の色によって有彩色の透光性樹脂層の膜厚が異なる場合や、遮光層、トランジスタに起因する凹凸を有する場合は、可視光領域の波長の光を透過する（いわゆる無色透明）絶縁層を積層し、層間膜表面を平坦化してもよい。層間膜の平坦性を高めるとその上に形成される画素電極層や第1の共通電極層の被覆性もよく、かつ液晶層のギャップ（膜厚）を均一にすることができるため、より液晶表示装置の視認性を向上させ、高画質化が可能になる。

【0147】

層間膜413（有彩色の透光性樹脂層417）の形成法は、特に限定されず、その材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）等の方法、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等のツール（設備）を用いることができる。

【0148】

第1の電極層447及び第2の電極層448上には液晶層444が設けられ、対向基板である第2の基板442で封止されている。

10

20

30

40

50

## 【0149】

第1の基板441及び第2の基板442は透光性基板であり、それぞれ外側（液晶層444と反対側）に偏光板443a、443bが設けられている。

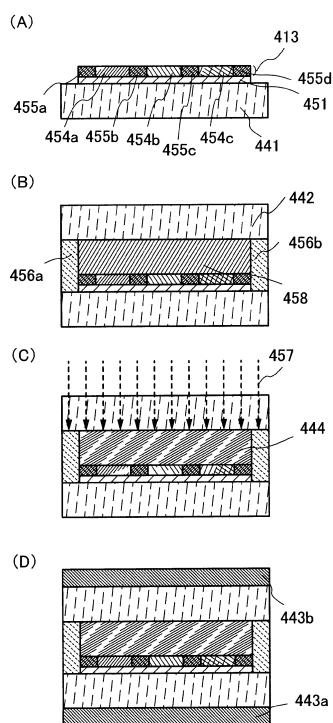

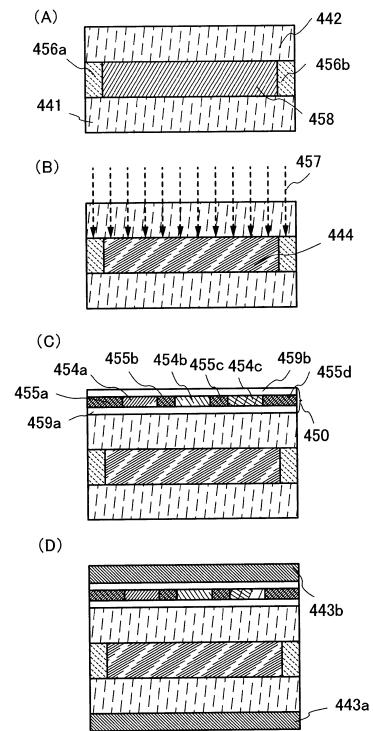

## 【0150】

図7（A）乃至（D）を用いて図3に示す液晶表示装置の作製工程を説明する。図7（A）乃至（D）は液晶表示装置の作製工程の断面図である。なお、図7（A）乃至（D）では含まれる画素電極層、第1の共通電極層及び第2の共通電極層は省略している。画素電極層、共通電極層は図3の構造を用いることができ、液晶層において画素電極層及び共通電極層がそれぞれ構造体上面及び側面を覆うように配置されており、高範囲な電界を形成することができる。

10

## 【0151】

図7（A）において、素子基板である第1の基板441上に素子層451が形成され、素子層451上に層間膜413が形成されている。

## 【0152】

層間膜413は、有彩色の透光性樹脂層454a、454b、454c及び遮光層455a、455b、455c、455dを含み、有彩色の透光性樹脂層454a、454b、454cが遮光層455a、455b、455c、455dの間にそれぞれ形成される構成である。なお、図7（A）乃至（D）では含まれる画素電極層、共通電極層は省略している。

20

## 【0153】

図7（B）に示すように、第1の基板441と対向基板である第2の基板442とを、液晶層458を間に挟持させてシール材456a、456bで固着する。液晶層458を形成する方法として、ディスペンサ法（滴下法）や、第1の基板441と第2の基板442とを貼り合わせてから毛細管現象等を用いて液晶を注入する注入法を用いることができる。

## 【0154】

液晶層458には、ブルー相を示す液晶材料を用いることができる。液晶層458は、液晶、カイラル剤、光硬化樹脂、及び光重合開始剤を含む液晶材料を用いて形成する。

## 【0155】

シール材456a、456bとしては、代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。代表的には、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。また、光（代表的には紫外線）重合開始剤、熱硬化剤、フィラー、カップリング剤を含んでもよい。

30

## 【0156】

図7（C）に示すように、液晶層458に、光457を照射して高分子安定化処理を行い、液晶層444を形成する。光457は、液晶層458に含まれる光硬化樹脂、及び光重合開始剤が反応する波長の光とする。この光照射による高分子安定化処理により、液晶層444がブルー相を示す温度範囲を広く改善することができる。

## 【0157】

シール材に紫外線などの光硬化樹脂を用い、滴下法で液晶層を形成する場合など、高分子安定化処理の光照射工程によってシール材の硬化も行ってよい。

40

## 【0158】

図7のように、素子基板上にカラーフィルタ層及び遮光層を作り込む液晶表示装置の構成であると、カラーフィルタ層及び遮光層によって対向基板側から照射される光が吸収、遮断されないようにするために、液晶層全体に均一に照射することができる。よって、光重合の不均一による液晶の配向乱れやそれに伴う表示ムラなどを防止することができる。また、遮光層によってトランジスタも遮光でき、光照射における電気特性の不良を防止することができる。

## 【0159】

図7（D）に示すように、第1の基板441の外側（液晶層444と反対側）に偏光板4

50

43aを、第2の基板442の外側（液晶層444と反対側）に偏光板443bを設ける。また、偏光板の他、位相差板、反射防止膜などの光学フィルムなどを設けてよい。例えば、偏光板及び位相差板による円偏光を用いてよい。以上の工程で、液晶表示装置を完成させることができる。

【0160】

また、大型の基板を用いて複数の液晶表示装置を作製する場合（所謂多面取り）、その分断工程は、高分子安定化処理の前か、偏光板を設ける前に行うことができる。分断工程による液晶層への影響（分断工程時にかかる力などによる配向乱れなど）を考慮すると、第1の基板と第2の基板とを貼り合わせた後、高分子安定化処理の前が好ましい。

【0161】

図示しないが、光源としてバックライト、サイドライトなどを用いればよい。光源からの光は素子基板である第1の基板441側から、視認側である第2の基板442へと透過するように照射される。

【0162】

第1の電極層447、及び第2の電極層448は、酸化タンクス滕を含むインジウム酸化物、酸化タンクス滕を含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（ITO）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

【0163】

また、第1の電極層447、及び第2の電極層448はタンクス滕（W）、モリブデン（Mo）、ジルコニウム（Zr）、ハフニウム（Hf）、バナジウム（V）、ニオブ（Nb）、タンタル（Ta）、クロム（Cr）、コバルト（Co）、ニッケル（Ni）、チタン（Ti）、白金（Pt）、アルミニウム（Al）、銅（Cu）、銀（Ag）等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

【0164】

また、第1の電極層447、及び第2の電極層448として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 / 以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

【0165】

導電性高分子としては、いわゆる電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

【0166】

下地膜となる絶縁膜を第1の基板441とゲート電極層401の間に設けてよい。下地膜は、第1の基板441からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜から選ばれた一又は複数の膜による積層構造により形成することができる。ゲート電極層401の材料は、モリブデン、チタン、クロム、タンタル、タンクス滕、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層又は積層して形成することができる。ゲート電極層401に遮光性を有する導電膜を用いることで、バックライトからの光（第1の基板441から入射する光）が、半導体層403へ入射することを防止することができる。

【0167】

例えば、ゲート電極層401の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、または銅層上にモリブデン層を積層した2層構造、または銅層上に窒化チタン層若しくは窒化タンタル層を積層した2層構造、窒化チタン層とモ

10

20

30

40

50

リブデン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タンゲステン層または窒化タンゲステンと、アルミニウムとシリコンの合金層またはアルミニウムとチタンの合金層と、窒化チタン層またはチタン層とを積層した積層構造とすることが好ましい。

【0168】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層又は窒化酸化シリコン層を単層で又は積層して形成することができる。また、ゲート絶縁層402として、有機シランガスを用いたCVD法により酸化シリコン層を形成することも可能である。有機シランガスとしては、珪酸エチル(TEOS:化学式Si(OCH<sub>3</sub>)<sub>4</sub>)、テトラメチルシラン(TMS:化学式Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>3</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。

【0169】

半導体層、配線層の作製工程において、薄膜を所望の形状に加工するためにエッティング工程を用いる。エッティング工程は、ドライエッティングやウェットエッティングを用いることができる。

【0170】

ドライエッティングに用いるエッティング装置としては、反応性イオンエッティング法(RIE法)を用いたエッティング装置や、ECR(Electron Cyclotron Resonance)やICP(Inductively Coupled Plasma)などの高密度プラズマ源を用いたドライエッティング装置を用いることができる。また、ICPエッティング装置と比べて広い面積に渡って一様な放電が得られやすいドライエッティング装置としては、上部電極を接地させ、下部電極に13.56MHzの第1の高周波電源を接続し、さらに下部電極に第1の高周波電源の周波数よりも低い3.2MHzの第2の高周波電源を接続したECCP(Enhanced Capacitively Coupled Plasma)モードのエッティング装置がある。このECCPモードのエッティング装置であれば、例えば基板として、第10世代の3mを超えるサイズの基板を用いる場合にも対応することができる。

【0171】

エッティング装置としてICPドライエッティング装置を用いる場合、薄膜を所望の加工形状にエッティングできるように、エッティング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

【0172】

薄膜を所望の加工形状にエッティングできるように、材料に合わせてエッティング条件(エッティング液、エッティング時間、温度等)を適宜調節する。

【0173】

配線層405a、405bの材料としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に持たせることが好ましい。例えば、Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。Alと組み合わせる耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

【0174】

ゲート絶縁層402、半導体層403、配線層405a、405bを大気に触れさせることなく連続的に形成してもよい。大気に触れさせることなく連続成膜することで、大気成

10

20

30

40

50

分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができるので、トランジスタ特性のばらつきを低減することができる。

【0175】

なお、半導体層403は一部のみがエッティングされ、溝部（凹部）を有する半導体層である。

【0176】

トランジスタ420を覆う絶縁膜407、絶縁層409は、乾式法や湿式法で形成される無機絶縁膜、有機絶縁膜を用いることができる。例えば、CVD法やスパッタ法などを用いて得られる窒化シリコン膜、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化タンタル膜などを用いることができる。また、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。

10

【0177】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。シロキサン系樹脂は塗布法により成膜し、焼成することによって絶縁膜407として用いることができる。

【0178】

20

なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁膜407、絶縁層409を形成してもよい。例えば、無機絶縁膜上に有機樹脂膜を積層する構造としてもよい。

【0179】

また、多階調マスクにより形成した複数（代表的には二種類）の厚さの領域を有するレジストマスクを用いると、レジストマスクの数を減らすことができるため、工程簡略化、低コスト化が図れる。

【0180】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

30

【0181】

また、より低電圧で高い白透過率を得るために、液晶表示装置の低消費電力化も達成できる。

【0182】

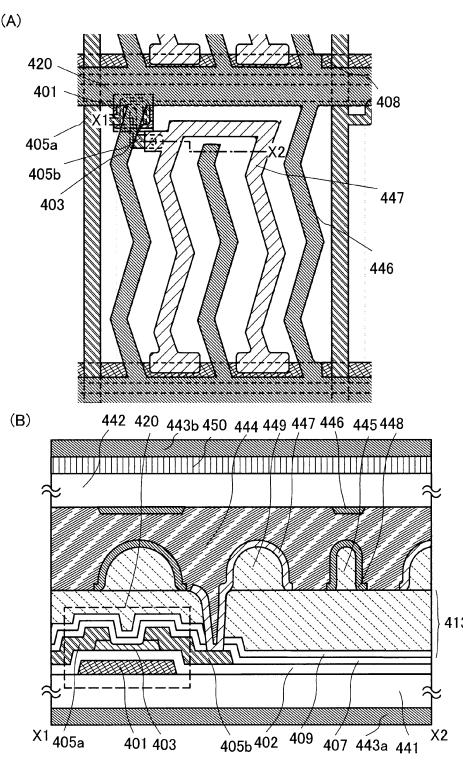

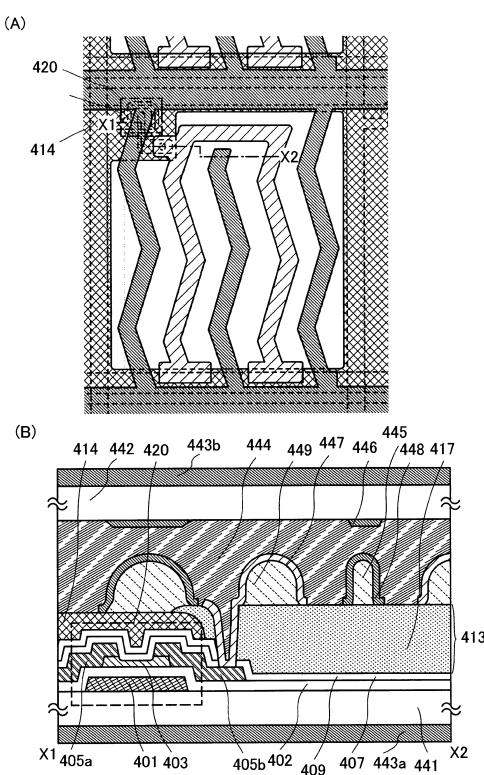

（実施の形態4）

実施の形態3において、カラーフィルタを液晶層を挟持する基板の外側に設ける例を図4に示す。なお、実施の形態1乃至3と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

【0183】

図4（A）は液晶表示装置の平面図であり1画素分の画素を示している。図4（B）は、図4（A）の線X1-X2における断面図である。

40

【0184】

図4（A）の平面図においては、実施の形態2と同様に、複数のソース配線層（配線層405aを含む）が互いに平行（図中上下方向に延伸）かつ互いに離間した状態で配置されている。複数のゲート配線層（ゲート電極層401を含む）は、ソース配線層に略直交する方向（図中左右方向）に延伸し、かつ互いに離間するように配置されている。容量配線層408は、複数のゲート配線層それぞれに隣接する位置に配置されており、ゲート配線層に概略平行な方向、つまり、ソース配線層に概略直交する方向（図中左右方向）に延伸している。ソース配線層と、容量配線層408及びゲート配線層とによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極層（第1の電極層447）及

50

び第1の共通電極層（第2の電極層448）と、第2の共通電極層（第3の電極層446）が液晶層444を介して配置されている。画素電極層を駆動するトランジスタ420は、図中左上の角に配置されている。画素電極層及びトランジスタは、マトリクス状に複数配置されている。

【0185】

図4においては、トランジスタ420を覆って層間膜413を形成し、層間膜413上に第1の構造体449を形成する際、第1の構造体449をエッティング加工によって形成した後、層間膜413にトランジスタ420に接続するためのコンタクトホールを開口する例である。画素電極層である第1の電極層447は、層間膜413に形成したコンタクトホール及び第1の構造体449を覆って連続的に形成されている。

10

【0186】

画素電極層である第1の電極層447は第1の基板441上の層間膜413の液晶層444側の面から液晶層444に突出して設けられた第1の構造体449の上面側面を覆って形成され、第2の電極層448は第1の基板441上の層間膜413の液晶層444側の面から液晶層444に突出して設けられた第2の構造体445の上面側面を覆って形成される。

【0187】

本実施の形態では、実施の形態2のように、液晶層444を間に挟んで第1の基板441側の第1の共通電極層である第2の電極層448と、第2の基板442側に第2の共通電極層である第3の電極層446とがお互いに重畠するように配置される。図4（B）の断面図において、第1の電極層447と、第2の電極層448及び第3の電極層446とは重畠せず互い違いに設けられている。

20

【0188】

第1の構造体449の上面及び側面を覆うように第1の電極層447を設け、第2の構造体445の上面及び側面を覆うように第2の電極層448を設けることで、第1の電極層447及び第2の電極層448の形成面積を液晶層444の膜厚方向に（3次元的に）も拡大できる。よって、第1の電極層447及び第2の電極層448間に電圧を印加した時、第1の電極層447と、第2の電極層448との間に広く電界を形成することができる。

【0189】

30

また、第2の基板442側に第2の共通電極層として第3の電極層446を設けると、画素電極層である第1の電極層447と第3の電極層446との間に液晶に対して斜め方向（基板に対して斜めの方向）の電界も加えることができるため、より効率よく液晶分子を制御できる。

【0190】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率（黒表示時の光の透過率）との比であるコントラスト比も高くすることができる。

【0191】

第3の電極層446は第1の電極層447、第2の電極層448と同様に形成することができ、同様な材料及び方法を用いることができる。

40

【0192】

図4の液晶表示装置は、カラーフィルタ450が第2の基板442と偏光板443bの間に設けられている。このように、液晶層444を挟持する第1の基板441及び第2の基板442の外側にカラーフィルタ450を設けてもよい。

【0193】

図4の液晶表示装置の作製工程を図17（A）乃至（D）に示す。

【0194】

なお、図17（A）乃至（D）では含まれる画素電極層、第1の共通電極層、第2の共通電極層、第1の構造体、及び第2の構造体は省略している。例えば、画素電極層、第1の

50

共通電極層、第2の共通電極層、第1の構造体、及び第2の構造体は実施の形態1又は実施の形態2の構造を用いることができる。

【0195】

図17(A)に示すように、第1の基板441と対向基板である第2の基板442とを、液晶層458を間に挟持させてシール材456a、456bで固着する。液晶層458を形成する方法として、ディスペンサ法(滴下法)や、第1の基板441と第2の基板442とを貼り合わせてから毛細管現象を用いて液晶を注入する注入法を用いることができる。

【0196】

液晶層458には、ブルー相を示す液晶材料を用いる。液晶層458は、液晶、カイラル剤、光硬化樹脂、及び光重合開始剤を含む液晶材料を用いて形成する。

【0197】

図17(B)に示すように、液晶層458に、光457を照射して高分子安定化処理を行い、液晶層444を形成する。光457は、液晶層458に含まれる光硬化樹脂、及び光重合開始剤が反応する波長の光とする。この光照射による高分子安定化処理により、液晶層458がブルー相を示す温度範囲を広く改善することができる。

【0198】

シール材に紫外線などの光硬化樹脂を用い、滴下法で液晶層を形成する場合など、高分子安定化処理の光照射工程によってシール材の硬化も行ってもよい。

【0199】

次に図17(C)に示すように、視認側である第2の基板442側にカラーフィルタ450を設ける。カラーフィルタ450は、一対の基板459a及び基板459bの間に、カラーフィルタ層として機能する有彩色の透光性樹脂層454a、454b、454c及びブラックマトリクス層として機能する遮光層455a、455b、455c、455dを含み、有彩色の透光性樹脂層454a、454b、454cが遮光層455a、455b、455c、455dの間にそれぞれ形成される構成である。

【0200】

図17(D)に示すように、第1の基板441の外側(液晶層444と反対側)に偏光板443aを、カラーフィルタ450の外側(液晶層444と反対側)に偏光板443bを設ける。また、偏光板の他、位相差板、反射防止膜などの光学フィルムなどを設けてもよい。例えば、偏光板及び位相差板による円偏光を用いてもよい。以上の工程で、液晶表示装置を完成させることができる。

【0201】

また、大型の基板を用いて複数の液晶表示装置を作製する場合(所謂多面取り)、その分断工程は、高分子安定化処理の前か、偏光板を設ける前に行うことができる。分断工程による液晶層への影響(分断工程時にかかる力などによる配向乱れなど)を考慮すると、第1の基板と第2の基板とを貼り合わせた後、高分子安定化処理の前が好ましい。

【0202】

図示しないが、光源としてバックライト、サイドライトなどを用いればよい。光源からの光は素子基板である第1の基板441側から、視認側である第2の基板442へと透過するように照射される。

【0203】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

【0204】

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

【0205】

(実施の形態5)

遮光層(ブラックマトリクス)を有する液晶表示装置を、図5を用いて説明する。

10

20

30

40

50

## 【0206】

図5に示す液晶表示装置は、実施の形態3の図3(A)(B)で示す液晶表示装置において、対向基板である第2の基板442側にさらに遮光層414を形成する例である。よって、実施の形態3と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

## 【0207】

図5(A)は液晶表示装置の平面図であり、図5(B)は図5(A)の線X1-X2の断面図である。なお、図5(A)の平面図では素子基板側のみ図示しており、対向基板側の記載は省略している。

## 【0208】

第2の基板442の液晶層444側に、遮光層414が形成され、平坦化膜として絶縁層415が形成されている。遮光層414は、液晶層444を介してトランジスタ420と対応する領域(トランジスタの半導体層と重畳する領域)に形成することが好ましい。遮光層414がトランジスタ420の少なくとも半導体層403上方を覆うように配置されるように、第1の基板441及び第2の基板442は液晶層444を挟持して固着される。

## 【0209】

図5において、遮光層414は第1の電極層447と配線層405bとが接続するコンタクトホール上を覆うように形成されている。よって、コンタクトホール上に発生しやすい液晶の配向欠陥による光漏れ等の表示むらを隠すことができるため、コントラストの低下を抑制することができる。

## 【0210】

遮光層414は、光を反射、又は吸収し、遮光性を有する材料を用いる。例えば、黒色の有機樹脂を用いることができ、感光性又は非感光性のポリイミドなどの樹脂材料に、顔料系の黒色樹脂やカーボンブラック、チタンブラック等を混合させて形成すればよい。また、遮光性の金属膜を用いることもでき、例えばクロム、モリブデン、ニッケル、チタン、コバルト、銅、タンゲステン、又はアルミニウムなどを用いればよい。

## 【0211】

遮光層414の形成方法は特に限定されず、材料に応じて、蒸着法、スパッタ法、CVD法などの乾式法、又はスピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)などの湿式法を用い、必要に応じてエッチング法(ドライエッチング又はウェットエッチング)により所望のパターンに加工すればよい。

## 【0212】

絶縁層415もアクリルやポリイミドなどの有機樹脂などを用いて、スピンドルコートや各種印刷法などの塗布法で形成すればよい。

## 【0213】

このようにさらに対向基板側に遮光層414を設けると、よりコントラスト向上やトランジスタの安定化の効果を高めることができる。遮光層414はトランジスタ420の半導体層403への光の入射を遮断することができるため、半導体の光感度によるトランジスタ420の電気特性の変動を防止しより安定化させる。また、遮光層414は隣り合う画素への光漏れを防止することもできるため、より高コントラスト及び高精細な表示を行うことが可能になる。よって、液晶表示装置の高精細、高信頼性を達成することができる。

## 【0214】

第1の構造体449の上面及び側面を覆うように第1の電極層447を設け、第2の構造体445の上面及び側面を覆うように第2の電極層448を設けることで、第1の電極層447及び第2の電極層448の形成面積を液晶層444の膜厚方向に(3次元的に)も拡大できる。よって、第1の電極層447及び第2の電極層448間に電圧を印加した時、第1の電極層447と、第2の電極層448との間に広く電界を形成することができる。

10

20

30

40

50

**【 0 2 1 5 】**

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率との比であるコントラスト比も高くすることができる。

**【 0 2 1 6 】**

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

**【 0 2 1 7 】**

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

10

**【 0 2 1 8 】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

**【 0 2 1 9 】****( 実施の形態 6 )**

遮光層（ブラックマトリクス）を有する液晶表示装置を、図6を用いて説明する。

**【 0 2 2 0 】**

図6に示す液晶表示装置は、実施の形態3の図3（A）（B）で示す液晶表示装置において、素子基板である第1の基板441側に層間膜413の一部として遮光層414を形成する例である。よって、実施の形態3と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

20

**【 0 2 2 1 】**

図6（A）は液晶表示装置の平面図であり、図6（B）は図6（A）の線X1-X2の断面図である。

**【 0 2 2 2 】**

層間膜413は遮光層414及び有彩色の透光性樹脂層417を含む。遮光層414は、素子基板である第1の基板441側に設けられており、トランジスタ420上（少なくともトランジスタの半導体層と覆う領域）に絶縁膜407、絶縁層409を介して形成され、半導体層に対する遮光層として機能する。一方、有彩色の透光性樹脂層417は、第1の電極層447、第2の電極層448及び第3の電極層446に重なる領域に形成され、カラーフィルタ層として機能する。図6（B）の液晶表示装置において、第2の電極層448の一部は、遮光層414上に形成され、その上に液晶層444が設けられている。

30

**【 0 2 2 3 】**

遮光層414を層間膜として用いるため、黒色の有機樹脂を用いることが好ましい。例えば、感光性又は非感光性のポリイミドなどの樹脂材料に、顔料系の黒色樹脂やカーボンブラック、チタンブラック等を混合させて形成すればよい。遮光層414の形成方法は材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）などの湿式法を用い、必要に応じてエッチング法（ドライエッティング又はウェットエッティング）により所望のパターンに加工すればよい。

**【 0 2 2 4 】**

40

このように遮光層414を設けると、遮光層414は、画素の開口率を低下させることなくトランジスタ420の半導体層403への光の入射を遮断することができ、トランジスタ420の電気特性の変動を防止し安定化する効果を得られる。また、遮光層414は隣り合う画素への光漏れを防止することもできるため、より高コントラスト及び高精細な表示を行うことができる。よって、液晶表示装置の高精細、高信頼性を達成することができる。

**【 0 2 2 5 】**

また、有彩色の透光性樹脂層417は、カラーフィルタ層として機能させることができる。カラーフィルタ層を対向基板側に設ける場合、トランジスタが形成される素子基板との、正確な画素領域の位置合わせが難しく画質を損なう恐れがあるが、層間膜に含まれる有

50

彩色の透光性樹脂層 417 をカラーフィルタ層として直接素子基板側に形成するのでより精密な形成領域の制御ができ、微細なパターンの画素にも対応することができる。また、層間膜とカラーフィルタ層を同一の絶縁層で兼ねるので、工程が簡略化しより低コストで液晶表示装置を作製可能となる。

【 0 2 2 6 】

第 1 の構造体 449 の上面及び側面を覆うように第 1 の電極層 447 を設け、第 2 の構造体 445 の上面及び側面を覆うように第 2 の電極層 448 を設けることで、第 1 の電極層 447 及び第 2 の電極層 448 の形成面積を液晶層 444 の膜厚方向に（3 次元的に）も拡大できる。よって、第 1 の電極層 447 及び第 2 の電極層 448 間に電圧を印加した時、第 1 の電極層 447 と、第 2 の電極層 448 との間に広く電界を形成することができる。

。

10

【 0 2 2 7 】

また、第 2 の基板 442 側に第 2 の共通電極層として第 3 の電極層 446 を設けると、画素電極層である第 1 の電極層 447 と第 3 の電極層 446 との間に液晶に対して斜め方向（基板に対して斜めの方向）の電界も加えることができるため、より効率よく液晶分子を制御できる。

【 0 2 2 8 】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率（黒表示時の光の透過率）との比であるコントラスト比も高くすることができる。

。

20

【 0 2 2 9 】

また、より低電圧で高い白透過率を得ることができると、液晶表示装置の低消費電力化も達成できる。

【 0 2 3 0 】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【 0 2 3 1 】

（実施の形態 7 ）

実施の形態 1 乃至 6 において、液晶表示装置に適用できるトランジスタの他の例を示す。なお、実施の形態 1 乃至 6 と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

。

30

【 0 2 3 2 】

図 10 ( A ) は液晶表示装置の平面図であり 1 画素分の画素を示している。図 10 ( B ) は、図 10 ( A ) の線 V1 - V2 における断面図である。

【 0 2 3 3 】

図 10 ( A ) の平面図においては、実施の形態 2 と同様に、複数のソース配線層（配線層 405a を含む）が互いに平行（図中上下方向に延伸）かつ互いに離間した状態で配置されている。複数のゲート配線層（ゲート電極層 401 を含む）は、ソース配線層に略直交する方向（図中左右方向）に延伸し、かつ互いに離間するように配置されている。容量配線層 408 は、複数のゲート配線層それぞれに隣接する位置に配置されており、ゲート配線層に概略平行な方向、つまり、ソース配線層に概略直交する方向（図中左右方向）に延伸している。ソース配線層と、容量配線層 408 及びゲート配線層とによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極層、共通電極層が配置されている。画素電極層を駆動するトランジスタ 422 は、図中左上の角に配置されている。画素電極層及びトランジスタは、マトリクス状に複数配置されている。

。

40

【 0 2 3 4 】

トランジスタ 422 、有彩色の透光性樹脂層である層間膜 413 、第 1 の構造体 449 、第 1 の電極層 447 、第 2 の構造体 445 、第 2 の電極層 448 が設けられた第 1 の基板 441 と、第 2 の基板 442 とは液晶層 444 を間に挟持して固着されている。

【 0 2 3 5 】

50

図10における構造において、半導体層403とソース電極層の間にソース領域（一導電型を有する半導体層、バッファ層ともいう）を、半導体層403とドレイン電極層との間にドレイン領域（一導電型を有する半導体層、バッファ層ともいう）を有する例を示す。例えば、ソース領域及びドレイン領域に、n型の導電型を示す半導体層を用いる。

【0236】

また、トランジスタ422のソース領域またはドレイン領域404a、404bとして、半導体層を用いる場合は、チャネル形成領域として用いる半導体層403の膜厚よりも薄く、且つ、より高い導電率（電気伝導度）を有するのが好ましい。

【0237】

第1の構造体449の上面及び側面を覆うように第1の電極層447を設け、第2の構造体445の上面及び側面を覆うように第2の電極層448を設けることで、第1の電極層447及び第2の電極層448の形成面積を液晶層444の膜厚方向に（3次元的に）も拡大できる。よって、第1の電極層447及び第2の電極層448間に電圧を印加した時、第1の電極層447と、第2の電極層448との間に広く電界を形成することができる。

【0238】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率との比であるコントラスト比も高くすることができる。

【0239】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

【0240】

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

【0241】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0242】

（実施の形態8）

実施の形態1乃至6において、液晶表示装置に適用できるトランジスタの他の例を、図9を用いて説明する。

【0243】

図9（A）は液晶表示装置の平面図であり1画素分の画素を示している。図9（B）は、図9（A）の線Z1-Z2における断面図である。

【0244】

図9（A）の平面図においては、実施の形態2と同様に、複数のソース配線層（配線層405aを含む）が互いに平行（図中上下方向に延伸）かつ互いに離間した状態で配置されている。複数のゲート配線層（ゲート電極層401を含む）は、ソース配線層に略直交する方向（図中左右方向）に延伸し、かつ互いに離間するように配置されている。容量配線層408は、複数のゲート配線層それぞれに隣接する位置に配置されており、ゲート配線層に概略平行な方向、つまり、ソース配線層に概略直交する方向（図中左右方向）に延伸している。ソース配線層と、容量配線層408及びゲート配線層とによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極層、共通電極層が配置されている。画素電極層を駆動するトランジスタ421は、図中左上の角に配置されている。画素電極層及びトランジスタは、マトリクス状に複数配置されている。

【0245】

トランジスタ421、有彩色の透光性樹脂層である層間膜413、第1の構造体449、第1の電極層447、第2の構造体445、第2の電極層448が設けられた第1の基板441と、第2の基板442とは液晶層444を間に挟持して固着されている。

10

20

30

40

50

## 【0246】

トランジスタ421はボトムゲート型の薄膜トランジスタであり、絶縁表面を有する基板である第1の基板441上に、ゲート電極層401、ゲート絶縁層402、ソース電極層又はドレイン電極層として機能する配線層405a、405b、及び半導体層403を含む。また、トランジスタ421を覆い、半導体層403に接する絶縁膜407が設けられている。

## 【0247】

なお、実施の形態7で示したようにバッファ層を、半導体層403と配線層405a、405bの間に設ける構造としてもよい。また、バッファ層をゲート絶縁層及び配線層の間と、配線層と半導体層の間と両方に設ける構造としてもよい。

10

## 【0248】

トランジスタ421は、トランジスタ421を含む領域全てにおいてゲート絶縁層402が存在し、ゲート絶縁層402と絶縁表面を有する基板である第1の基板441の間にゲート電極層401が設けられている。ゲート絶縁層402上には配線層405a、405bが設けられている。そして、ゲート絶縁層402、配線層405a、405b上に半導体層403が設けられている。なお、ゲート絶縁層402上の配線層405a、405bは半導体層403の外周部より外側に延在している。

## 【0249】

第1の構造体449の上面及び側面を覆うように第1の電極層447を設け、第2の構造体445の上面及び側面を覆うように第2の電極層448を設けることで、第1の電極層447及び第2の電極層448の形成面積を液晶層444の膜厚方向に(3次元的に)も拡大できる。よって、第1の電極層447及び第2の電極層448間に電圧を印加した時、第1の電極層447と、第2の電極層448との間に広く電界を形成することができる。

20

## 【0250】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率との比であるコントラスト比も高くすることができる。

## 【0251】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

30

## 【0252】

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

## 【0253】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

## 【0254】

## (実施の形態9)

上記実施の形態3乃至8において、トランジスタ420、421、422の半導体層に用いることのできる材料として酸化物半導体を説明する。具体的には、半導体層として酸化物半導体層を用いたトランジスタ1420、1450を説明する。

40

## 【0255】

図11(A)に示すトランジスタ1450はボトムゲート型の薄膜トランジスタであり、絶縁表面を有する基板1400上に、ゲート電極層1401、ゲート絶縁層1402、酸化物半導体層1403、ソース電極層1405a、及びドレイン電極層1405bを含む。また、トランジスタ1450を覆い、酸化物半導体層1403に積層する酸化物絶縁層1407が設けられている。酸化物絶縁層1407上にはさらに窒化物絶縁層を用いた保護絶縁層1409が形成されている。

## 【0256】

50

酸化物半導体層を用いるトランジスタの電気的特性変動を抑止するため、変動要因となる水素、水分、水酸基又は水素化物（水素化合物ともいう）などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料の1つである酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型（真性）化する。

## 【0257】

よって酸化物半導体中の水素は少なければ少ないほどよく、酸化物半導体に含まれる水素が好ましくは $1 \times 10^{-6}$  / cm<sup>3</sup>未満として、酸化物半導体に含まれる水素をゼロに近いほど極力除去する。

## 【0258】

また、高純度化された酸化物半導体中にはキャリアが極めて少なく（ゼロに近い）、キャリア濃度は $1 \times 10^{-4}$  / cm<sup>3</sup>未満、好ましくは $1 \times 10^{-2}$  / cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{-1}$  / cm<sup>3</sup>未満である。酸化物半導体中にキャリアが極めて少ないため、トランジスタのオフ電流を少なくすることができる。オフ電流は少なければ少いほど好ましい。オフ電流（リーク電流ともいう）とは、-1V~-10Vの間のいずれかのゲート電圧を印加した場合のトランジスタのソース、ドレイン間を流れる電流のことであり、本明細書に開示する酸化物半導体を用いたトランジスタは、チャネル幅（w）が1μmあたりの電流値が100aA / μm以下、好ましくは10aA / μm以下、さらに好ましくは1aA / μm以下である。さらに、pn接合がなく、ホットキャリア劣化がないため、これらにトランジスタの電気的特性が影響を受けない。

## 【0259】

上記水素の濃度範囲は、二次イオン質量分析（SIMS: Secondary Ion Mass Spectrometry）で得られたもの、またはそのデータに基づいて得られる。また、キャリア濃度はホール効果測定により求めることができる。ホール効果測定器の例として、比抵抗/ホール測定システムResiTest 8310（東陽テクニカ製）を挙げることができる。比抵抗/ホール測定システムResiTest 8310は、磁場の向きと大きさを一定の周期で変化させ、それと同期してサンプルに現れるホール起電圧のみを検出するAC（交流）ホール測定が可能であり、移動度が小さくて抵抗率の高い材料についても、ホール起電圧を検出できる。

## 【0260】

また、酸化物半導体膜中だけでなく、ゲート絶縁層内に存在する水分などの不純物を低減し、上下に接して設けられる膜と酸化物半導体膜の界面に存在する水分などの不純物も低減する。

## 【0261】

酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより、トランジスタの動作を良好なものとすることができます。

## 【0262】

酸化物半導体膜としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O膜や、三元系金属酸化物であるIn-Ga-Zn-O膜、In-Sn-Zn-O膜、In-Al-Zn-O膜、Sn-Ga-Zn-O膜、Al-Ga-Zn-O膜、Sn-Al-Zn-O膜や、二元系金属酸化物であるIn-Zn-O膜、Sn-Zn-O膜、Al-Zn-O膜、Zn-Mg-O膜、Sn-Mg-O膜、In-Mg-O膜や、In-O膜、Sn-O膜、Zn-O膜などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜にSiO<sub>2</sub>を含んでもよい。

## 【0263】

また、酸化物半導体膜は、InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される構造の酸化物半導体膜のうち、MとしてGaを含む構造の酸化物半導体を、上記したIn-Ga-Zn-O酸化

10

20

30

40

50

物半導体とよび、その薄膜を In - Ga - Zn - O 非単結晶膜ともよぶこととする。

【0264】

また、トランジスタ 1420、1450 はボトムゲート構造の逆スタガ型薄膜トランジスタの例を示すが、本明細書に開示する液晶表示装置に適用できる酸化物半導体層を有するトランジスタは、酸化物半導体層上にチャネル保護層を設けたチャネル保護型のトランジスタでも、トップゲート構造のトランジスタであってもよい。

【0265】

また、トランジスタ 1420、1450 はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造のトランジスタも形成することができる。

10

【0266】

図 11 (B) では、断面から見て酸化物半導体層を窒化物絶縁層で囲む例を示す。

【0267】

図 11 (B) に示すトランジスタ 1420 はボトムゲート型の薄膜トランジスタであり、絶縁表面を有する基板 1400 上に、ゲート電極層 1401、窒化物絶縁層を用いたゲート絶縁層 1432a、酸化物絶縁層を用いたゲート絶縁層 1432b、酸化物半導体層 1403、ソース電極層 1405a、及びドレイン電極層 1405b を含む。また、トランジスタ 1420 を覆い、酸化物半導体層 1403 に積層する酸化物絶縁層 1437 が設けられている。酸化物絶縁層 1437 上にはさらに窒化物絶縁層を用いた保護絶縁層 1439 が形成されている。保護絶縁層 1439 は窒化物絶縁層であるゲート絶縁層 1432a と接する構成とする。

20

【0268】

本実施の形態では、トランジスタ 1420 においてゲート絶縁層をゲート電極層側から窒化物絶縁層と酸化物絶縁層との積層構造とする。また、窒化物絶縁層である保護絶縁層 1439 の形成前に、酸化物絶縁層 1437 と、ゲート絶縁層 1432b を選択的に除去し、窒化物絶縁層であるゲート絶縁層 1432a が露出するように加工する。

【0269】

少なくとも酸化物絶縁層 1437、ゲート絶縁層 1432b の上面形状は、酸化物半導体層 1403 の上面形状よりも広く、トランジスタ 1420 を覆う上面形状とすることが好みしい。

30

【0270】

さらに酸化物絶縁層 1437 の上面と、酸化物絶縁層 1437 及びゲート絶縁層 1432b の側面とを覆い、かつ窒化物絶縁層であるゲート絶縁層 1432a に接して、窒化物絶縁層である保護絶縁層 1439 を形成する。

【0271】

窒化物絶縁層からなる保護絶縁層 1439 及びゲート絶縁層 1432a は、スパッタ法やプラズマ CVD 法で得られる窒化シリコン膜、酸化窒化シリコン膜、窒化アルミニウム膜、酸化窒化アルミニウム膜などの水分、水素イオン、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用いる。

40

【0272】

本実施の形態では、窒化物絶縁層からなる保護絶縁層 1439 として、酸化物半導体層 1403 の下面、上面、及び側面を囲むように RF スパッタ法を用い、膜厚 100 nm の窒化シリコン層を設ける。

【0273】

図 11 (B) に示す構造とすることで、酸化物半導体層は、接して囲う様に設けられるゲート絶縁層 1432b 及び酸化物絶縁層 1437 によって、水素、水分、水酸基又は水素化物などの不純物は低減され、かつ窒化物絶縁層であるゲート絶縁層 1432a 及び保護絶縁層 1439 によってさらに外部を覆うように囲まれているので、保護絶縁層 1439 の形成後の製造プロセスにおいて、外部からの水分の侵入を防ぐことができる。また、液晶表示装置としてデバイスが完成した後にも長期的に、外部からの水分の侵入を防ぐこと

50

ができるデバイスの長期信頼性を向上することができる。

【0274】

また、本実施の形態では一つのトランジスタを窒化物絶縁層で囲む構成を示したが特に限

定されず、複数のトランジスタを窒化物絶縁層で囲む構成としてもよいし、画素部の複数

のトランジスタをまとめて窒化物絶縁層で囲む構成としてもよい。少なくともアクティブ

マトリクス基板の画素部の周縁を囲むように保護絶縁層1439とゲート絶縁層1432

aとが接する領域を設ける構成とすればよい。

【0275】

後工程は、実施の形態3と同様に、トランジスタ1420、又はトランジスタ1450に接続する画素電極層を、絶縁表面（絶縁層）上において液晶層に突出する第1の構造体の表面を覆うように形成し、同一絶縁表面（絶縁層）において液晶層に突出するように設けられた第2の構造体の表面を覆うように共通電極層を形成し、液晶層を挟持して第2の基板で固着すればよい。

10

【0276】

第1の構造体の上面及び側面を覆うように設けられた画素電極層と、第2の構造体の上面及び側面を覆うように設けられた共通電極層によって、液晶層において、画素電極層と、共通電極層との間に広く電界を形成することができる。

【0277】

また、実施の形態2のように、第2の基板側に第2の共通電極層を設けると、画素電極層と第2の共通電極層との間に液晶に対して斜め方向（基板に対して斜めの方向）の電界も加えることができるため、より効率よく液晶分子を制御できる。

20

【0278】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率との比であるコントラスト比も高くすることができる。

【0279】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

【0280】

また、より低電圧で高い白透過率を得るために、液晶表示装置の低消費電力化も達成できる。

30

【0281】

ブルー相の液晶材料を用いると、配向膜へのラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって液晶表示装置の生産性を向上させることができるとなる。特に、酸化物半導体層を用いるトランジスタは、静電気の影響によりトランジスタの電気的な特性が著しく変動して設計範囲を逸脱する恐れがある。

【0282】

ブルー相の液晶材料の応答速度が従来液晶材料よりも一桁以上速いため、酸化物半導体層を用いるトランジスタの様な倍速（高速）駆動が可能なデバイスと組み合わせることによって、液晶表示装置の高機能化及び高速応答化が実現できる。

40

【0283】

酸化物半導体を用いたトランジスタは、オフ電流が非常に小さいため、保持容量は非常に小さくてよく、また設けなくてもよいので、開口率を大きくすることができ、またブルー相の液晶材料を用いることによる容量増加が生じても、寄生容量を低減することができるため消費電力を低く抑えることができる。

【0284】

以上のことから、本実施の形態のように酸化物半導体層を用いるトランジスタを有する液晶表示装置にブルー相の液晶材料を用いることはより効果的である。

【0285】

50

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0286】

(実施の形態10)

本実施の形態は、実施の形態9で示した酸化物半導体層を含むトランジスタ、及び作製方法の一例を図25を用いて詳細に説明する。本実施の形態で示すトランジスタ390は、上記実施の形態における、チャネル形成領域を含む酸化物半導体層を用いるトランジスタ1420、1450として適用することができる。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

10

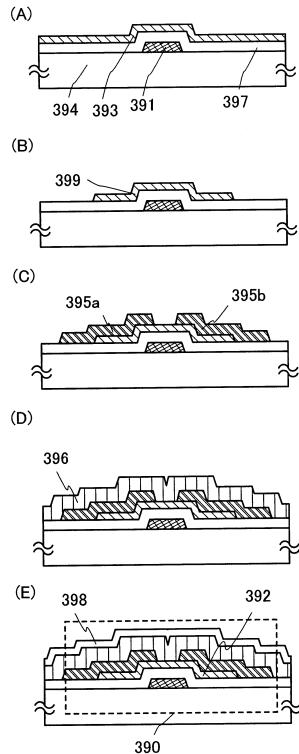

【0287】

図25(A)乃至(E)にトランジスタの断面構造の一例を示す。図25(A)乃至(E)に示すトランジスタ390は、ボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

【0288】

また、トランジスタ390はシングルゲート構造のトランジスタを用いて説明するが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造のトランジスタも形成することができる。

【0289】

以下、図25(A)乃至(E)を用い、基板394上にトランジスタ390を作製する工程を説明する。

20

【0290】

まず、絶縁表面を有する基板394上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層391を形成する。形成されたゲート電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0291】

絶縁表面を有する基板394に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板を用いることができる。

30

【0292】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。また、ガラス基板には、例えば、アルミニシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。また、実用的な耐熱ガラスが得られるため、B<sub>2</sub>O<sub>3</sub>よりBaOを多く含むガラス基板を用いることは好ましい。

【0293】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いても良い。他にも、結晶化ガラス基板などを用いることができる。また、プラスチック基板等も適宜用いることができる。

40

【0294】

下地膜となる絶縁膜を基板394とゲート電極層391との間に設けてもよい。下地膜は、基板394からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

【0295】

また、ゲート電極層391の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

50

## 【0296】

例えば、ゲート電極層391の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、銅層上にモリブデン層を積層した2層構造、銅層上に窒化チタン層若しくは窒化タンタルを積層した2層構造、窒化チタン層とモリブデン層とを積層した2層構造、又は窒化タンゲステン層とタンゲステン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タンゲステン層または窒化タンゲステン層と、アルミニウムとシリコンの合金層またはアルミニウムとチタンの合金層と、窒化チタン層またはチタン層とを積層した積層とすることが好ましい。なお、透光性を有する導電膜を用いてゲート電極層を形成することもできる。透光性を有する導電膜としては、透光性導電性酸化物等をその例に挙げることができる。

10

## 【0297】

次いで、ゲート電極層391上にゲート絶縁層397を形成する。

## 【0298】

ゲート絶縁層397は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

20

## 【0299】

ここで、不純物を除去することによりi型化又は実質的にi型化された酸化物半導体（高純度化された酸化物半導体）は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層（G1）は、高品質化が要求される。

## 【0300】

例えば、μ波（2.45GHz）を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

30

## 【0301】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

## 【0302】

さらに、 $85$ 、 $2 \times 10^6$  V/cm、12時間のゲートバイアス・熱ストレス試験（BT試験）においては、不純物が酸化物半導体に添加されていると、不純物と酸化物半導体の主成分との結合手が、強電界（B：バイアス）と高温（T：温度）により切断され、生成された未結合手がしきい値電圧（Vth）のドリフトを誘発することとなる。

40

## 【0303】

これに対して、本明細書に開示する発明は、酸化物半導体の不純物、特に水素や水等を極力除去し、上記のようにゲート絶縁層との界面特性を良好にすることにより、BT試験に対しても安定なトランジスタを得ることを可能としている。

## 【0304】

ゲート絶縁層397は、ゲート電極層391側から窒化物絶縁層と、酸化物絶縁層との積層構造とすることもできる。例えば、第1のゲート絶縁層としてスパッタリング法により膜厚50nm以上200nm以下の窒化シリコン層（SiNy（y>0））を形成し、第1のゲート絶縁層上に第2のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層（SiOx（x>0））を積層してゲート絶縁層とする。ゲート絶縁層の膜厚は

50

、トランジスタに要求される特性によって適宜設定すればよく 100 nm 程度、あるいは 350 nm 乃至 400 nm 程度でもよい。

【0305】

また、ゲート絶縁層 397、酸化物半導体膜 393 に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層 391 が形成された基板 394、又はゲート絶縁層 397 までが形成された基板 394 を予備加熱し、基板 394 に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度としては、100 以上 400 以下好ましくは 150 以上 300 以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、酸化物絶縁層 396 の成膜前に、ソース電極層 395a 及びドレイン電極層 395b まで形成した基板 394 にも同様に行ってよい。10

【0306】

次いで、ゲート絶縁層 397 上に、膜厚 2 nm 以上 200 nm 以下の酸化物半導体膜 393 を形成する（図 25（A）参照。）。

【0307】

なお、酸化物半導体膜 393 をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 397 の表面に付着しているゴミを除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に RF 電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。20

【0308】

酸化物半導体膜 393 はスパッタリング法により成膜する。酸化物半導体膜 393 は、四元系金属酸化物である In - Sn - Ga - Zn - O 膜や、三元系金属酸化物である In - Ga - Zn - O 膜、In - Sn - Zn - O 膜、In - Al - Zn - O 膜、Sn - Ga - Zn - O 膜、Al - Ga - Zn - O 膜、Sn - Al - Zn - O 膜や、二元系金属酸化物である In - Zn - O 膜、Sn - Zn - O 膜、Al - Zn - O 膜、Zn - Mg - O 膜、Sn - Mg - O 膜、In - Mg - O 膜や、In - O 膜、Sn - O 膜、Zn - O 膜などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜に SiO<sub>2</sub> を含んでもよい。本実施の形態では、酸化物半導体膜 393 を In - Ga - Zn - O 系酸化物半導体ターゲットを用いてスパッタリング法により成膜する。また、酸化物半導体膜 393 は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（代表的にはアルゴン）及び酸素雰囲気下においてスパッタリング法により形成することができる。30

【0309】

酸化物半導体膜 393 をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及び Zn を含む酸化物半導体ターゲット（組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol%]、In : Ga : Zn = 1 : 1 : 0.5 [atom%]）を用いることができる。また、In、Ga、及び Zn を含む酸化物半導体ターゲットとして、In : Ga : Zn = 1 : 1 : 1 [atom%]、又は In : Ga : Zn = 1 : 1 : 2 [atom%] の組成比を有するターゲットを用いることもできる。酸化物半導体ターゲットの充填率は 90% 以上 100% 以下、好ましくは 95% 以上 99.9% 以下である。充填率の高い酸化物半導体ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。40

【0310】

減圧状態に保持された処理室内に基板を保持し、基板を室温又は 400 未満の温度に加熱する。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板 394 上に酸化物半導体膜 393 を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ま50

しい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水( $H_2O$ )など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

### 【0311】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、ごみが軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

### 【0312】

スパッタリング法にはスパッタ用電源に高周波電源を用いるRFスパッタリング法と、DCスパッタリング法があり、さらにパルス的にバイアスを与えるパルスDCスパッタリング法もある。RFスパッタリング法は主に絶縁性ターゲットを用いて膜を成膜する場合に用いられ、DCスパッタリング法は主に金属ターゲット等の導電性ターゲットを用いて膜を成膜する場合に用いられる。

### 【0313】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

### 【0314】

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタリング法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタリング法を用いるスパッタ装置がある。

### 【0315】

また、スパッタリング法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法もある。

### 【0316】

次いで、酸化物半導体膜を第2のフォトリソグラフィ工程により島状の酸化物半導体層399に加工する(図25(B)参照。)。また、島状の酸化物半導体層399を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

### 【0317】

また、ゲート絶縁層397にコンタクトホールを形成する場合、その工程は酸化物半導体層399の形成時に行うことができる。

### 【0318】

なお、ここでの酸化物半導体膜393のエッティングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。

### 【0319】

ドライエッティングに用いるエッティングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素( $Cl_2$ )、塩化硼素( $BCl_3$ )、塩化珪素( $SiCl_4$ )、四塩化炭素( $CCl_4$ )など)が好ましい。

### 【0320】

また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素( $CF_4$ )、六弗化硫黄( $SF_6$ )、三弗化窒素( $NF_3$ )、トリフルオロメタン( $CHF_3$ )など)、臭化水素( $HBr$ )、酸素( $O_2$ )、これらのガスにヘリウム( $He$ )やアルゴン( $Ar$ )などの希ガ

10

20

30

40

50

スを添加したガス、などを用いることができる。

【0321】

ドライエッティング法としては、平行平板型 RIE (Reactive Ion Etching) 法や、ICP (Inductively Coupled Plasma: 誘導結合型プラズマ) エッティング法を用いることができる。所望の加工形状にエッティングできるように、エッティング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

【0322】

ウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液、アンモニア過水（31重量%過酸化水素水：28重量%アンモニア水：水 = 5 : 2 : 2）などを用いることができる。また、ITO 07N（関東化学社製）を用いてもよい。

10

【0323】

また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

【0324】

所望の加工形状にエッティングできるように、材料に合わせてエッティング条件（エッティング液、エッティング時間、温度等）を適宜調節する。

20

【0325】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体層 399 及びゲート絶縁層 397 の表面に付着しているレジスト残渣などを除去することが好ましい。

【0326】

次いで、ゲート絶縁層 397、及び酸化物半導体層 399 上に、導電膜を形成する。導電膜をスパッタリング法や真空蒸着法で形成すればよい。ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、W から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等が挙げられる。また、Al、Cu などの金属層の一方または双方に Cr、Ta、Ti、Mo、W などの高融点金属層を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、Y など Al 膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されている Al 材料を用いることで耐熱性を向上させることができる。

30

【0327】

また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti 膜と、その Ti 膜上に重ねてアルミニウム膜を積層し、さらにその上に Ti 膜を成膜する3層構造などが挙げられる。

【0328】

また、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム ( $In_2O_3$ )、酸化スズ ( $SnO_2$ )、酸化亜鉛 ( $ZnO$ )、酸化インジウム酸化スズ合金 ( $In_2O_3 - SnO_2$ 、ITO と略記する)、酸化インジウム酸化亜鉛合金 ( $In_2O_3 - ZnO$ ) または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

40

【0329】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッティングを行ってソース電極層 395a、ドレイン電極層 395b を形成した後、レジストマスクを除去する（図 25 (C) 参照。）。

【0330】

50

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層399上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L = 25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線(Extreme ultraviolet)を用いて第3のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。

10

### 【0331】

なお、導電膜のエッチングの際に、酸化物半導体層399は除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

### 【0332】

本実施の形態では、導電膜としてTi膜を用いて、酸化物半導体層399にはIn-Ga-Zn-O系酸化物半導体を用いて、エッチャントとして過水アンモニア水(アンモニア、水、過酸化水素水の混合液)を用いる。

### 【0333】

なお、第3のフォトリソグラフィ工程では、酸化物半導体層399は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。また、ソース電極層395a、ドレイン電極層395bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

20

### 【0334】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

30

### 【0335】

N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

### 【0336】

プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる酸化物絶縁層として酸化物絶縁層396を形成する(図25(D)参照。)。本実施の形態では、酸化物半導体層399がソース電極層395a、ドレイン電極層395bと重ならない領域において、酸化物半導体層399と酸化物絶縁層396とが接するように形成する。

40

### 【0337】

本実施の形態では、酸化物絶縁層396として、島状の酸化物半導体層399、ソース電極層395a、ドレイン電極層395bまで形成された基板394を室温又は100未満の温度に加熱し、水素及び水分が除去された高純度酸素を含むスペッタガスを導入しシリコン半導体のターゲットを用いて、欠陥を含む酸化シリコン層を成膜する。

### 【0338】

例えば、純度が6Nであり、ボロンがドープされたシリコンターゲット(抵抗値0.01cm)を用い、基板とターゲットの間との距離(T-S間距離)を89mm、圧力0.

50

4 Pa、直流(DC)電源6kW、酸素(酸素流量比率100%)雰囲気下でパルスDCスパッタリング法により酸化シリコン膜を成膜する。膜厚は300nmとする。なお、シリコンターゲットに代えて石英(好ましくは合成石英)を酸化シリコン膜を成膜するためのターゲットとして用いることができる。なお、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

## 【0339】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層396を成膜することが好ましい。酸化物半導体層399及び酸化物絶縁層396に水素、水酸基又は水分が含まれないようにするためである。

## 【0340】

10

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層396に含まれる不純物の濃度を低減できる。

## 【0341】

なお、酸化物絶縁層396として、酸化シリコン層に代えて、酸化窒化シリコン層、酸化アルミニウム層、または酸化窒化アルミニウム層などを用いることもできる。

## 【0342】

20

さらに、酸化物絶縁層396と酸化物半導体層399とを接した状態で100乃至400で加熱処理を行ってもよい。本実施の形態における酸化物絶縁層396は欠陥を多く含むため、この加熱処理によって酸化物半導体層399中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁層396に拡散させ、酸化物半導体層399中に含まれる該不純物をより低減させることができる。

## 【0343】

以上の工程で、水素、水分、水酸基又は水素化物の濃度が低減された酸化物半導体層392を有するトランジスタ390を形成することができる(図25(E)参照。)。

## 【0344】

上記のように酸化物半導体膜を成膜するに際し、反応雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

## 【0345】

酸化物絶縁層上に保護絶縁層を設けてもよい。本実施の形態では、保護絶縁層398を酸化物絶縁層396上に形成する。保護絶縁層398としては、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いる。

## 【0346】

保護絶縁層398として、酸化物絶縁層396まで形成された基板394を100~400の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜する。この場合においても、酸化物絶縁層396と同様に、処理室内の残留水分を除去しつつ保護絶縁層398を成膜することが好ましい。

## 【0347】

保護絶縁層398を形成する場合、保護絶縁層398の成膜時に100~400に基板394を加熱することで、酸化物半導体層中に含まれる水素若しくは水分を酸化物絶縁層に拡散させることができる。この場合上記酸化物絶縁層396の形成後に加熱処理を行わなくてもよい。

## 【0348】

酸化物絶縁層396として酸化シリコン層を形成し、保護絶縁層398として窒化シリコン層を積層する場合、酸化シリコン層と窒化シリコン層と同じ処理室において、共通のシ

10

20

30

40

50

リコンターゲットを用いて成膜することができる。先に酸素を含むエッチングガスを導入して、処理室内に装着されたシリコンターゲットを用いて酸化シリコン層を形成し、次にエッチングガスを窒素を含むエッチングガスに切り替えて同じシリコンターゲットを用いて窒化シリコン層を成膜する。酸化シリコン層と窒化シリコン層とを大気に曝露せずに連続して形成することができるため、酸化シリコン層表面に水素や水分などの不純物が吸着することを防止することができる。この場合、酸化物絶縁層 396 として酸化シリコン層を形成し、保護絶縁層 398 として窒化シリコン層を積層した後、酸化物半導体層中に含まれる水素若しくは水分を酸化物絶縁層に拡散させるための加熱処理（温度 100 乃至 400）を行うとよい。

## 【0349】

10

保護絶縁層の形成後、さらに大気中、100 以上 200 以下、1 時間以上 30 時間以下での加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなるトランジスタを得ることができる。よって表示パネルの信頼性を向上できる。

## 【0350】

また、ゲート絶縁層上にチャネル形成領域とする酸化物半導体層を成膜するに際し、反応雰囲気中の残留水分を除去することで、該酸化物半導体層中の水素及び水素化物の濃度を低減することができる。

20

## 【0351】

上記の工程は、液晶表示装置などのバックプレーン（トランジスタが形成された基板）の製造に用いることができる。上記の工程は、厚さが 1 mm 以下で、一辺が 1 m を超えるガラス基板を用いる製造工程にも適用することができる。

## 【0352】

後工程は、実施の形態 3 と同様に、トランジスタ 390 に接続する画素電極層を、絶縁表面（絶縁層）上において液晶層に突出する第 1 の構造体の表面を覆うように形成し、同一絶縁表面（絶縁層）において液晶層に突出するように設けられた第 2 の構造体の表面を覆うように共通電極層を形成し、液晶層を挟持して第 2 の基板で固着すればよい。

30

## 【0353】

第 1 の構造体の上面及び側面を覆うように設けられた画素電極層と、第 2 の構造体の上面及び側面を覆うように設けられた共通電極層によって、液晶層において、画素電極層と、共通電極層との間に広く電界を形成することができる。

## 【0354】

また、実施の形態 2 のように、第 2 の基板側に第 2 の共通電極層を設けると、画素電極層と第 2 の共通電極層との間に液晶に対して斜め方向（基板に対して斜めの方向）の電界も加えることができるため、より効率よく液晶分子を制御できる。

## 【0355】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率との比であるコントラスト比も高くすることができる。

40

## 【0356】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

## 【0357】

また、より低電圧で高い白透過率を得ることができため、液晶表示装置の低消費電力化も達成できる。

## 【0358】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

50

## 【0359】

## (実施の形態11)

本実施の形態は、実施の形態9で示した酸化物半導体層を含むトランジスタ、及び作製方法の一例を図26を用いて詳細に説明する。本実施の形態で示すトランジスタ310は、上記実施の形態における、チャネル形成領域を含む酸化物半導体層を用いるトランジスタ1420、1450として適用することができる。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

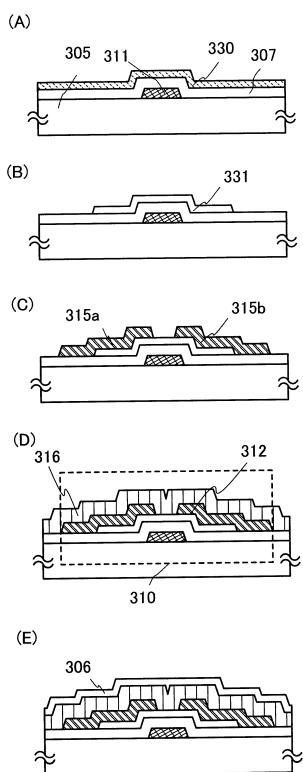

## 【0360】

図26(A)乃至(E)にトランジスタの断面構造の一例を示す。図26(A)乃至(E)に示すトランジスタ310は、ボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

10

## 【0361】

また、トランジスタ310はシングルゲート構造のトランジスタを用いて説明するが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造のトランジスタも形成することができる。

## 【0362】

以下、図26(A)乃至(E)を用い、基板305上にトランジスタ410を作製する工程を説明する。

20

## 【0363】

まず、絶縁表面を有する基板305上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層311を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0364】

絶縁表面を有する基板305に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

30

## 【0365】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、酸化ホウ素( $B_2O_3$ )と比較して酸化バリウム( $BaO$ )を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ より $BaO$ を多く含むガラス基板を用いることが好ましい

## 【0366】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いても良い。他にも、結晶化ガラスなどを用いることができる。

## 【0367】

下地膜となる絶縁膜を基板305とゲート電極層311との間に設けてもよい。下地膜は、基板305からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

40

## 【0368】

また、ゲート電極層311の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

## 【0369】

例えば、ゲート電極層311の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、銅層上にモリブデン層を積層した2層の積層構造、銅層

50

上に窒化チタン層若しくは窒化タンタル層を積層した2層の積層構造、窒化チタン層とモリブデン層とを積層した2層の積層構造、又は窒化タンゲステン層とタンゲステン層との2層の積層構造とすることが好ましい。3層の積層構造としては、タンゲステン層または窒化タンゲステン層と、アルミニウムとシリコンの合金層またはアルミニウムとチタンの合金層と、窒化チタン層またはチタン層とを積層した積層とすることが好ましい。

【0370】

次いで、ゲート電極層311上にゲート絶縁層307を形成する。

【0371】

ゲート絶縁層307は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。また、μ波(2.45GHz)を用いた高密度プラズマCVD法を用いてもよい。

10

【0372】

本実施の形態では、ゲート絶縁層307としてプラズマCVD法により膜厚100nmの酸化窒化シリコン層を形成する。

【0373】

次いで、ゲート絶縁層307上に、膜厚2nm以上200nm以下の酸化物半導体膜330を形成する。

【0374】

20

なお、酸化物半導体膜330をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層307の表面に付着しているゴミを除去することが好ましい。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

【0375】

酸化物半導体膜330は、四元系金属酸化物であるIn-Sn-Ga-Zn-O膜や、三元系金属酸化物であるIn-Ga-Zn-O膜、In-Sn-Zn-O膜、In-Al-Zn-O膜、Sn-Ga-Zn-O膜、Al-Ga-Zn-O膜、Sn-Al-Zn-O膜や、二元系金属酸化物であるIn-Zn-O膜、Sn-Zn-O膜、Al-Zn-O膜、Zn-Mg-O膜、Sn-Mg-O膜、In-Mg-O膜や、In-O膜、Sn-O膜、Zn-O膜などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜にSiO<sub>2</sub>を含んでもよい。本実施の形態では、酸化物半導体膜330としてIn-Ga-Zn-O系酸化物半導体ターゲットを用いてスパッタ法により成膜する。この段階での断面図が図26(A)に相当する。また、酸化物半導体膜330は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素雰囲気下においてスパッタ法により形成することができる。

30

【0376】

酸化物半導体膜330をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及びZnを含む酸化物半導体ターゲット(組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol比]、In : Ga : Zn = 1 : 1 : 0.5 [atom比])を用いることができる。また、In、Ga、及びZnを含む酸化物半導体ターゲットとして、In : Ga : Zn = 1 : 1 : 1 [atom比]、又はIn : Ga : Zn = 1 : 1 : 2 [atom比]の組成比を有するターゲットを用いることもできる。酸化物半導体ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い酸化物半導体ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

40

【0377】

酸化物半導体膜330を、成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用い

50

ることが好ましい。

【0378】

減圧状態に保持された処理室内に基板を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板305上に酸化物半導体膜330を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。10

【0379】

成膜条件の一例としては、基板とターゲットとの距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、ごみが軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。20

【0380】

次いで、酸化物半導体膜330を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0381】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層331を得る(図26(B)参照。)。30

【0382】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輐射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輐射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。40

【0383】

例えば、第1の加熱処理として、650~700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

【0384】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0385】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜330に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0386】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にソース電極及びドレイン電極を積層させた後、ソース電極及びドレイン電極上に保護絶縁膜を形成した後、のいずれで行っても良い。

【0387】

また、ゲート絶縁層307にコンタクトホールを形成する場合、その工程は酸化物半導体膜330に脱水化または脱水素化処理を行う前でも行った後に行ってもよい。

【0388】

なお、ここでの酸化物半導体膜のエッティングは、ウェットエッティングに限定されずドライエッティングを用いててもよい。

【0389】

所望の加工形状にエッティングできるように、材料に合わせてエッティング条件(エッティング液、エッティング時間、温度等)を適宜調節する。

【0390】

次いで、ゲート絶縁層307、及び酸化物半導体層331上に、ソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)となる導電膜を形成する。導電膜をスパッタ法や真空蒸着法で形成すればよい。ソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)となる導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等が挙げられる。また、Al、Cuなどの金属層の一方または双方にCr、Ta、Ti、Mo、Wなどの高融点金属層を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されているAl材料を用いることで耐熱性を向上させることが可能となる。

【0391】

また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。

【0392】

また、ソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ合金( $In_2O_3-SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金( $In_2O_3-ZnO$ )または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

【0393】

導電膜成膜後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

【0394】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッ

10

20

30

40

50

チングを行ってソース電極層 315a、ドレイン電極層 315b を形成した後、レジストマスクを除去する（図 26（C）参照。）。

【0395】

第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線や KrF レーザ光や ArF レーザ光を用いる。酸化物半導体層 331 上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長 L が決定される。なお、チャネル長 L = 25 nm 未満の露光を行う場合には、数 nm ~ 数 10 nm と極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長 L を 10 nm 以上 1000 nm 以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。

10

【0396】

なお、導電膜のエッティングの際に、酸化物半導体層 331 は除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。

【0397】

本実施の形態では、導電膜として Ti 膜を用いて、酸化物半導体層 331 には In-Ga-Zn-O 系酸化物半導体を用いて、エッチャントとして過水アンモニア水（アンモニア、水、過酸化水素水の混合液）を用いる。

20

【0398】

なお、第 3 のフォトリソグラフィ工程では、酸化物半導体層 331 は一部のみがエッティングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、ソース電極層 315a、ドレイン電極層 315b を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0399】

また、酸化物半導体層とソース電極層及びドレイン電極層の間に、酸化物導電層を形成してもよい。酸化物導電層とソース電極層及びドレイン電極層を形成するための金属層は、連続成膜が可能である。酸化物導電層はソース領域及びドレイン領域として機能しうる。

30

【0400】

ソース領域及びドレイン領域として、酸化物導電層を酸化物半導体層とソース電極層及びドレイン電極層との間に設けることで、ソース領域及びドレイン領域の低抵抗化を図ることができ、トランジスタの高速動作をすることができる。

【0401】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッティング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッティングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッティング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

40

【0402】

次いで、N<sub>2</sub>O、N<sub>2</sub>、または Ar などのガスを用いたプラズマ処理を行い、露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。

【0403】

プラズマ処理を行った後、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる酸化物絶縁層 316 を形成する。

【0404】

50

酸化物絶縁層316は、少なくとも1nm以上の膜厚とし、スパッタ法など、酸化物絶縁層316に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。酸化物絶縁層316に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素が酸化物半導体層中の酸素を引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化(N型化)してしまい、寄生チャネルが形成されるおそれがある。よって、酸化物絶縁層316はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

#### 【0405】

本実施の形態では、酸化物絶縁層316として膜厚200nmの酸化シリコン膜をスパッタ法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化シリコン膜のスパッタ法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下において行うことができる。また、ターゲットとして酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素、及び窒素雰囲気下でスパッタ法により酸化シリコンを形成することができる。低抵抗化した酸化物半導体層に接して形成する酸化物絶縁層316は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

#### 【0406】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層316を成膜することが好ましい。酸化物半導体層331及び酸化物絶縁層316に水素、水酸基又は水分が含まれないようにするためである。

#### 【0407】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであつてもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層316に含まれる不純物の濃度を低減できる。

#### 【0408】

酸化物絶縁層316を、成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

#### 【0409】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)が酸化物絶縁層316と接した状態で加熱される。

#### 【0410】

以上の工程を経ることによって、成膜後の酸化物半導体膜に対して脱水化または脱水素化のための加熱処理を行って水素、水分、水酸基又は水素化物(水素化合物ともいう)などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型(真性)化する。

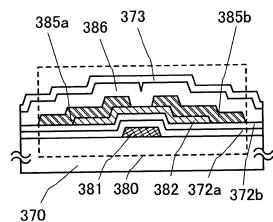

#### 【0411】