(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4836339号

(P4836339)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO1L 21/336 (2006.01) | HO1L 29/78 616A |

| HO1L 29/786 (2006.01) | HO1L 29/78 617K |

| GO9F 9/30 (2006.01)   | HO1L 29/78 617L |

| HO1L 27/32 (2006.01)  | GO9F 9/30 338   |

| HO4N 5/70 (2006.01)   | GO9F 9/30 365Z  |

請求項の数 6 (全 45 頁) 最終頁に続く

|           |                               |           |                                                |

|-----------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号 | 特願2001-59927 (P2001-59927)    | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日  | 平成13年3月5日(2001.3.5)           | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号 | 特開2001-326362 (P2001-326362A) | (72) 発明者  | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (43) 公開日  | 平成13年11月22日(2001.11.22)       | (72) 発明者  | 須沢 英臣<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査請求日     | 平成20年2月18日(2008.2.18)         | (72) 発明者  | 小野 幸治<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体表示装置及びその作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とをそれぞれ有するスイッチング用TFTおよび電流制御用TFTを有する半導体表示装置であって、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記第1のゲート電極および第2のゲート電極は、端部における断面の形状がテーパーであり、

前記スイッチング用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、前記チャネル形成領域に接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第1のLDD領域と、前記第1のLDD領域に接する第2のLDD領域と、前記第2のLDD領域に接するソース領域及びドレイン領域とを有しており、

前記電流制御用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、該チャネル形成領域と接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第3のLDD領域と、該第3のLDD領域と接するソース領域またはドレイン領域とを有することを特徴とする半導体表示装置。

## 【請求項 2】

10

20

絶縁表面上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とをそれぞれ有する第1のTFTおよび第2のTFTを有する半導体表示装置であって、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記第1のゲート電極および第2のゲート電極は、端部における断面の形状がテーパーであり、

前記第1のTFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、前記チャネル形成領域に接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第1のLDD領域と、前記第1のLDD領域に接する第2のLDD領域と、前記第2のLDD領域に接するソース領域及びドレイン領域とを有しており、

前記第2のTFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、該チャネル形成領域と接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第3のLDD領域と、該第3のLDD領域と接するソース領域またはドレイン領域とを有し、

前記第1のTFTのソースまたはドレインの一方は、前記第2のTFTのゲートに電気的に接続されていることを特徴とする半導体表示装置。

### 【請求項3】

絶縁表面上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とをそれぞれ有するスイッチング用TFT、駆動回路用TFT、および電流制御用TFTを有する半導体表示装置であって、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記第1のゲート電極および第2のゲート電極は、端部における断面の形状がテーパーであり、

前記スイッチング用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、前記チャネル形成領域に接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第1のLDD領域と、前記第1のLDD領域に接する第2のLDD領域と、前記第2のLDD領域に接するソース領域及びドレイン領域とを有しており、

前記駆動回路用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、該チャネル形成領域と接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第3のLDD領域と、該第3のLDD領域と接するソース領域またはドレイン領域とを有し、

前記電流制御用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、該チャネル形成領域と接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第4のLDD領域と、該第4のLDD領域と接するソース領域またはドレイン領域とを有することを特徴とする半導体表示装置。

### 【請求項4】

請求項3において、前記第1のLDD領域における不純物濃度は、少なくとも $1 \times 10^{17} \sim 1 \times 10^{18} / \text{cm}^3$ の範囲で濃度勾配を有する領域を有し、前記チャネル形成領域からの距離が増大するとともに不純物濃度が増加することを特徴とする半導体表示装置。

### 【請求項5】

請求項3または請求項4において、前記第3のLDD領域における不純物濃度は、少なくとも $1 \times 10^{17} \sim 1 \times 10^{18} / \text{cm}^3$ の範囲で濃度勾配を有する領域を有し、前記チャネル形成領域からの距離が増大するとともに不純物濃度が増加することを特徴とする半導体表示装置。

10

20

30

40

50

**【請求項 6】**

請求項3乃至請求項5のいずれか一項において、前記第1のLDD領域、前記第3のLDD領域、および前記第4のLDD領域は、前記第2のゲート電極をマスクとして前記半導体層に前記不純物を添加することにより、自己整合的に形成されていることを特徴とする半導体表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は半導体素子（半導体薄膜を用いた素子）を用いた半導体表示装置に関する。また該半導体表示装置を表示部に用いた電子機器に関する。

10

**【0002】****【従来の技術】**

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数nm～数百nm程度）を用いて薄膜トランジスタ（TFT）を形成する技術が注目されている。薄膜トランジスタはICや半導体表示装置のような電子デバイスに広く応用され、特に液晶表示装置、EL表示装置のスイッチング素子として開発が急がれている。

**【0003】**

EL表示装置は有機ELディスプレイ（OELD：Organic EL Display）又は有機ライトエミッティングダイオード（OLED：Organic Light Emitting Diode）とも呼ばれている。

20

**【0004】**

EL表示装置は自発光型である。EL素子は一対の電極（陽極と陰極）間に有機化合物を含む層（以下、EL層と記す）が挟まれた構造となっているが、EL層は通常積層構造となっている。代表的には、コダック・イーストマン・カンパニーのTangらが提案した「正孔輸送層／発光層／電子輸送層」という積層構造が挙げられる。この構造は非常に発光効率が高く、現在研究開発が進められているEL表示装置は殆どこの構造を採用している。

**【0005】**

EL素子は、電場を加えることで発生するルミネッセンス（Electro Luminescence）が得られると、陽極層と、EL層と、陰極層とを有する。有機化合物におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光（蛍光）と三重項励起状態から基底状態に戻る際の発光（リン光）とがあるが、本発明のEL表示装置は、どちらの発光を用いていても良い。

30

**【0006】**

また他にも、陽極上に正孔注入層／正孔輸送層／発光層／電子輸送層、または正孔注入層／正孔輸送層／発光層／電子輸送層／電子注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。

**【0007】**

本明細書において陰極と陽極の間に設けられる全ての層を総称してEL層と呼ぶ。よって上述した正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等は、全てEL層に含まれる。

40

**【0008】**

なお本明細書においてEL素子が発光することを、EL素子が駆動すると呼ぶ。また、本明細書中では、陽極、EL層及び陰極で形成される発光素子をEL素子と呼ぶ。

**【0009】**

アクティブマトリクス型EL表示装置は、画素部が有する複数の画素にそれぞれTFTとEL素子とを有している。そしてEL素子に流れる電流をTFTによって制御することで画素部に画像が表示される。

**【0010】**

特に結晶構造を有する半導体膜を活性層として用いたTFT（結晶質TFT）は高移動度が得られることから、同一基板上に機能回路を集積させて高精細な画像表示を実現するこ

50

とが可能である。

【0011】

本明細書において、前記結晶構造を有する半導体膜とは、単結晶半導体、多結晶半導体、微結晶半導体を含むものであり、さらに、特開平7-130652号公報、特開平8-78329号公報、特開平10-135468号公報、または特開平10-135469号公報で開示された半導体を含んでいる。

【0012】

アクティブマトリクス型EL表示装置を構成するためには、画素マトリクス回路（以下画素部と記す）だけでも100～200万個の結晶質TFTが必要となり、さらに周辺に設けられる機能回路を附加するとそれ以上の結晶質TFTが必要であった。EL表示装置に要求される仕様は厳しく、画像表示を安定して行うためには、個々の結晶質TFTの信頼性を確保することが必要であった。

10

【0013】

TFTの特性はオン状態とオフ状態の2つの状態に分けて考えることができる。オン状態の特性からは、オン電流、移動度、S値、しきい値などの特性を知ることができ、オフ状態の特性ではオフ電流が重視されている。

【0014】

しかし、結晶質TFTはオフ電流が高くなりやすいという問題点があった。

【0015】

また、結晶質TFTは信頼性の面で依然LSIなどに用いられるMOSトランジスタ（単結晶半導体基板上に作製されるトランジスタ）に及ばないとされている。例えば、結晶質TFTを連続駆動させると移動度やオン電流（TFTがオン状態にある時に流れる電流）の低下、オフ電流（TFTがオフ状態にある時に流れる電流）の増加といった劣化現象が観測されることがあった。この原因はホットキャリア効果であり、ドレイン近傍の高電界によって発生したホットキャリアが劣化現象を引き起こすものと考えられた。

20

【0016】

MOSトランジスタでは、オフ電流を下げ、ドレイン近傍の高電界を緩和する方法として、低濃度ドレイン（LDD：Lightly Doped Drain）構造が知られている。この構造はチャネル領域の外側に低濃度の不純物領域を設けたものであり、この低濃度不純物領域をLDD領域と呼んでいる。

30

【0017】

特にLDD領域がゲート絶縁膜を介してゲート電極と重なる構造（GOLD（Gate-drain Overlapped LDD）構造）を有している場合、ドレイン近傍の高電界を緩和してホットキャリア効果を防ぎ、信頼性を向上させることができた。なお本明細書においてLDD領域がゲート絶縁膜を介してゲート電極と重なる領域をLoV領域（第1のLDD領域）と呼ぶ。

【0018】

なおGOLD（Gate-drain Overlapped LDD）構造は、LATID（Large-tilt-angle implanted drain）構造、または、ITLD（Inverse T LDD）構造等としても知られている。そして、例えば、「Mutsuko Hatano, Hajime Akimoto and Takeshi Sakai, IE DM97 TECHNICAL DIGEST, p523-526, 1997」では、シリコンで形成したサイドウォールによるGOLD構造であるが、他の構造のTFTと比べ、きわめて優れた信頼性が得られることが確認されている。

40

【0019】

なお本明細書においてLDD領域がゲート絶縁膜を介してゲート電極と重ならない領域をLoff領域（第2のLDD領域）と呼ぶ。

【0020】

Looff領域とLoV領域を併せ持つTFTの作製方法はすでにいくつか提案されている。LoV領域とLooff領域とを形成する方法としては、マスクを用いる方法と、互いに幅の異なる2層のゲート電極及びゲート絶縁膜を用いてセルフアラインで形成する方法と

50

が挙げられる。

【0021】

しかしマスクを用いる場合、 $L_{ov}$ 領域と $L_{off}$ 領域を形成するのに2枚のマスクが必要となり、工程数が増加してしまう。一方セルフアラインによって $L_{ov}$ 領域と $L_{off}$ 領域を形成する場合、マスクの数を増やさなくても良いので、工程数を抑えることは可能である。しかしゲート電極の幅とゲート絶縁膜の厚さはそのまま $L_{ov}$ 領域と $L_{off}$ 領域の形成される位置に影響を与える。ゲート電極とゲート絶縁膜のエッチングレートは異なっており、エッチングによって、 $L_{ov}$ 領域と $L_{off}$ 領域の微妙な位置あわせを制御するのが難しい。

【0022】

10

【発明が解決しようとする課題】

本発明は上記のことと鑑み、 $L_{ov}$ 領域及び $L_{off}$ 領域を形成する際にマスクの数を抑え、また $L_{ov}$ 領域と $L_{off}$ 領域を所望の位置に容易に形成することを課題とする。またオン状態とオフ状態の両方で良好な特性が得られる結晶質TFTを実現することを課題とする。そして、そのような結晶質TFTで回路を形成した半導体回路を有する信頼性の高い半導体表示装置を実現することを課題とする。

【0023】

20

【課題を解決するための手段】

本発明は、ゲート電極を用いたセルフアラインとマスクとを用いて半導体層に不純物を添加し、 $L_{ov}$ 領域と $L_{off}$ 領域を形成した。ゲート電極は2層の導電膜から形成されており、より半導体層に近い層（第1のゲート電極）は遠い層（第2のゲート電極）よりも、チャネル長方向において長くなっている。

【0024】

なお本明細書においてチャネル長方向とは、ソース領域とドレイン領域の間をキャリアが移動する方向である。

【0025】

30

本発明では、第1のゲート電極と第2のゲート電極のチャネル長方向（キャリアが移動する方向）の長さ（以下、単にゲート電極の幅と呼ぶ）が異なっている。そのため、第1及び第2のゲート電極をマスクとしてイオン注入を行うことにより、ゲート電極の厚さが異なることによるイオンの侵入深さの違いを利用して、第2のゲート電極の下に位置する半導体層中のイオン濃度を、第2のゲート電極の下に位置せず、かつ第1のゲート電極の下に位置する半導体層中のイオン濃度より低くすることが可能である。そしてさらに、第2のゲート電極の下に位置せず、かつ第1のゲート電極の下に位置する半導体層中のイオン濃度を、第1のゲート電極の下に位置しない半導体層中のイオン濃度より低くすることが可能である。

【0026】

またマスクを用いて $L_{off}$ 領域を形成するために、エッチングで制御しなくてはならないのは第1のゲート電極と第2のゲート電極の幅のみであり、 $L_{off}$ 領域と $L_{ov}$ 領域の位置の制御が従来に比べて容易になった。よって、 $L_{ov}$ 領域と $L_{off}$ 領域の微妙な位置あわせが容易になり、所望の特性を有するTFTを作製することも容易になった。

40

【0027】

以下に本発明の構成を示す。

【0028】

本発明は、

絶縁表面上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とを有する半導体表示装置であって、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記

50

第2のゲート電極の幅より広く、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっていることを特徴とする半導体表示装置である。

【0029】

本発明は、

絶縁表面上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とを有する半導体表示装置であって、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっていることを特徴とする半導体表示装置である。

【0030】

本発明は、

絶縁表面上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極と、EL素子とを有する半導体表示装置であって、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記EL素子は陽極と、陰極と、前記陽極と前記陰極との間に設けられたEL層とを有しており、

前記ドレイン領域は、前記陽極もしくは前記陰極と電気的に接続されていることを特徴とする半導体表示装置である。

【0031】

本発明は、

絶縁表面上に形成された半導体層と、該半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とを含むTFTを有する半導体表示装置であって、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記第1のゲート電極は、端部における断面の形状がテーパーであり、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっていることを特徴とする半導体表示装置である。

【0032】

本発明は、前記LDD領域が前記第2のゲート電極をマスクとして前記半導体層に前記不純物を添加することにより、自己整合的に形成されていることを特徴としていても良い。

【0033】

本発明は、前記LDD領域における不純物濃度が、少なくとも $1 \times 10^{17} \sim 1 \times 10^{18} / \text{cm}^3$ の範囲で濃度勾配を有する領域を含んでおり、チャネル形成領域からの距離が増大

10

20

30

40

50

するとともに不純物濃度が増加することを特徴としていても良い。

【0034】

本発明は、

絶縁表面上に形成された半導体層と、該半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とをそれぞれ含むスイッチング用TFT及び駆動回路用TFTを有する半導体表示装置であって、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記スイッチング用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、前記チャネル形成領域に接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第1のLDD領域と、前記第1のLDD領域に接する第2のLDD領域と、前記第2のLDD領域に接するソース領域及びドレイン領域とを有しており、

前記駆動回路用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、該チャネル形成領域と接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第3のLDD領域と、該第3のLDD領域と接するソース領域またはドレイン領域とを含むことを特徴とする半導体表示装置である。

【0035】

本発明は、

絶縁表面上に形成された半導体層と、該半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とをそれぞれ含むスイッチング用TFT及び駆動回路用TFTを有する半導体表示装置であって、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記第1のゲート電極は、端部における断面の形状がテーパーであり、

前記スイッチング用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、前記チャネル形成領域に接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第1のLDD領域と、前記第1のLDD領域に接する第2のLDD領域と、前記第2のLDD領域に接するソース領域及びドレイン領域とを有しており、

前記駆動回路用TFTの半導体層は、前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なるチャネル形成領域と、該チャネル形成領域と接し、かつ前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なる第3のLDD領域と、該第3のLDD領域と接するソース領域またはドレイン領域とを含むことを特徴とする半導体表示装置である。

【0036】

本発明は、前記第1のLDD領域における不純物濃度が、少なくとも $1 \times 10^{17} \sim 1 \times 10^{18} / \text{cm}^3$ の範囲で濃度勾配を有する領域を含んでおり、チャネル形成領域からの距離が増大するとともに不純物濃度が増加することを特徴としていても良い。

【0037】

本発明は、前記第3のLDD領域における不純物濃度が、少なくとも $1 \times 10^{17} \sim 1 \times 10^{18} / \text{cm}^3$ の範囲で濃度勾配を有する領域を含んでおり、チャネル形成領域からの距離が増大するとともに不純物濃度が増加することを特徴としていても良い。

【0038】

本発明は、前記第1のLDD領域または前記第3のLDD領域が、前記第2のゲート電極をマスクとして前記半導体層に前記不純物を添加することにより、自己整合的に形成されていることを特徴としていても良い。

【0039】

本発明は、

10

20

30

40

50

絶縁表面上に形成された半導体層と、ゲート絶縁膜と、第1のゲート電極と、第2のゲート電極と、第1の配線と、第2の配線と、第1の層間絶縁膜と、第2の層間絶縁膜と、中間配線とを有する半導体表示装置であって、

前記ゲート絶縁膜は前記半導体層を覆って前記絶縁表面上に形成されており、

前記第1のゲート電極及び前記第1の配線は前記ゲート絶縁膜に接して形成されており、前記第2のゲート電極と前記第2の配線とは、それぞれ前記第1のゲート電極と前記第1の配線とに接して形成されており、

前記第1のゲート電極及び前記第1の配線は第1の導電膜から形成されており、

前記第2のゲート電極及び前記第2の配線は第2の導電膜から形成されており、

前記第1の層間絶縁膜は、前記第1及び第2のゲート電極と、前記第1及び第2の配線と、前記ゲート絶縁膜とを覆って形成されており、

前記第2の層間絶縁膜は、前記第1の層間絶縁膜上に形成されており、

前記中間配線は、前記第2の層間絶縁膜に設けられたコンタクトホールを介して前記第1の層間絶縁膜に接するように、前記第2の層間絶縁膜を覆って形成されており、

前記中間配線は前記コンタクトホールにおいて、前記第1の層間絶縁膜を間に介して前記第2の配線と重なっており、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

チャネル長の方向における前記第1のゲート電極の幅は、チャネル長の方向における前記第2のゲート電極の幅より広く、

前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なることを特徴とする半導体表示装置である。

#### 【0040】

本発明は、

絶縁表面上に形成された半導体層と、ゲート絶縁膜と、第1のゲート電極と、第2のゲート電極と、第1の配線と、第2の配線と、第1の層間絶縁膜と、第2の層間絶縁膜と、中間配線と、EL素子とを有する半導体表示装置であって、

前記ゲート絶縁膜は前記半導体層を覆って前記絶縁表面上に形成されており、

前記第1のゲート電極及び前記第1の配線は前記ゲート絶縁膜に接して形成されており、前記第2のゲート電極と前記第2の配線とは、それぞれ前記第1のゲート電極と前記第1の配線とに接して形成されており、

前記第1のゲート電極及び前記第1の配線は第1の導電膜から形成されており、

前記第2のゲート電極及び前記第2の配線は第2の導電膜から形成されており、

前記第1の層間絶縁膜は、前記第1及び第2のゲート電極と、前記第1及び第2の配線と、前記ゲート絶縁膜とを覆って形成されており、

前記第2の層間絶縁膜は、前記第1の層間絶縁膜上に形成されており、

前記中間配線は、前記第2の層間絶縁膜に設けられた第1のコンタクトホールを介して前記第1の層間絶縁膜に接するように、前記第2の層間絶縁膜を覆って形成されており、前記中間配線は前記第1のコンタクトホールにおいて、前記第1の層間絶縁膜を間に介して前記第2の配線と重なっており、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記中間配線は、前記ゲート絶縁膜と、前記第1の層間絶縁膜と、第2の層間絶縁膜とに設けられた第2のコンタクトホールを介して前記ソース領域に接続されており、

前記EL素子は陽極と、陰極と、前記陽極と前記陰極との間に設けられたEL層とを有し

10

20

30

40

50

ており、

前記ドレイン領域は、前記陽極もしくは前記陰極と電気的に接続されていることを特徴とする半導体表示装置である。

【0041】

本発明は、

絶縁表面上に形成された半導体層と、ゲート絶縁膜と、第1のゲート電極と、第2のゲート電極と、第1の配線と、第2の配線と、第1の層間絶縁膜と、第2の層間絶縁膜と、中間配線と、遮蔽膜とを有する半導体表示装置であって、

前記ゲート絶縁膜は前記半導体層を覆って前記絶縁表面上に形成されており、

前記第1のゲート電極及び前記第1の配線は前記ゲート絶縁膜に接して形成されており、

前記第2のゲート電極と前記第2の配線とは、それぞれ前記第1のゲート電極と前記第1の配線とに接して形成されており、

前記第1のゲート電極及び前記第1の配線は第1の導電膜から形成されており、

前記第2のゲート電極及び前記第2の配線は第2の導電膜から形成されており、

前記第1の層間絶縁膜は、前記第1及び第2のゲート電極と、前記第1及び第2の配線と、前記ゲート絶縁膜とを覆って形成されており、

前記第2の層間絶縁膜は、前記第1の層間絶縁膜上に形成されており、

前記中間配線は、前記第2の層間絶縁膜に設けられたコンタクトホールを介して前記第1の層間絶縁膜に接するように、前記第2の層間絶縁膜を覆って形成されており、

前記中間配線は前記コンタクトホールにおいて、前記第1の層間絶縁膜を間に介して前記第2の配線と重なっており、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記遮蔽膜は前記中間配線と同じ導電膜から形成されており、

前記遮蔽膜は前記チャネル形成領域と重なるように前記第2の層間絶縁膜上に形成されていることを特徴とする半導体表示装置である。

【0042】

本発明は、

絶縁表面上に形成された半導体層と、ゲート絶縁膜と、第1のゲート電極と、第2のゲート電極と、第1の配線と、第2の配線と、第1の層間絶縁膜と、第2の層間絶縁膜と、中間配線と、遮蔽膜と、EL素子とを有する半導体表示装置であって、

前記ゲート絶縁膜は前記半導体層を覆って前記絶縁表面上に形成されており、

前記第1のゲート電極及び前記第1の配線は前記ゲート絶縁膜に接して形成されており、

前記第2のゲート電極と前記第2の配線とは、それぞれ前記第1のゲート電極と前記第1の配線とに接して形成されており、

前記第1のゲート電極及び前記第1の配線は第1の導電膜から形成されており、

前記第2のゲート電極及び前記第2の配線は第2の導電膜から形成されており、

前記第1の層間絶縁膜は、前記第1及び第2のゲート電極と、前記第1及び第2の配線と、前記ゲート絶縁膜とを覆って形成されており、

前記第2の層間絶縁膜は、前記第1の層間絶縁膜上に形成されており、

前記中間配線は、前記第2の層間絶縁膜に設けられた第1のコンタクトホールを介して前記第1の層間絶縁膜に接するように、前記第2の層間絶縁膜を覆って形成されており、

前記中間配線は前記第1のコンタクトホールにおいて、前記第1の層間絶縁膜を間に介して前記第2の配線と重なっており、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、

10

20

30

40

50

前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記中間配線は、前記ゲート絶縁膜と、前記第1の層間絶縁膜と、第2の層間絶縁膜とに設けられた第2のコンタクトホールを介して前記ソース領域に接続されており、

前記遮蔽膜は前記中間配線と同じ導電膜から形成されており、

前記遮蔽膜は前記チャネル形成領域と重なるように前記第2の層間絶縁膜上に形成されており、

前記EL素子は陽極と、陰極と、前記陽極と前記陰極との間に設けられたEL層とを有しており、

前記ドレイン領域は、前記陽極もしくは前記陰極と電気的に接続されていることを特徴とする半導体表示装置である。 10

#### 【0043】

本発明は、

基板上に形成された遮蔽膜と、前記遮蔽膜を覆って前記基板上に形成された絶縁膜と、前記絶縁膜上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極とを有する半導体表示装置であって、

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、 20

前記遮蔽膜は前記絶縁膜を介して前記チャネル形成領域と重なることを特徴とする半導体表示装置である。

#### 【0044】

本発明は、

基板上に形成された遮蔽膜と、前記遮蔽膜を覆って前記基板上に形成された絶縁膜と、前記絶縁膜上に形成された半導体層と、前記半導体層に接するゲート絶縁膜と、前記ゲート絶縁膜に接する第1のゲート電極と、前記第1のゲート電極に接する第2のゲート電極と、EL素子とを有する半導体表示装置であって、 30

前記半導体層は、チャネル形成領域と、前記チャネル形成領域に接するLDD領域と、前記LDD領域に接するソース領域及びドレイン領域とを有しており、

前記LDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっており、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記遮蔽膜は前記絶縁膜を介して前記チャネル形成領域と重なっており、

前記EL素子は陽極と、陰極と、前記陽極と前記陰極との間に設けられたEL層とを有しており、

前記ドレイン領域は、前記陽極もしくは前記陰極と電気的に接続されていることを特徴とする半導体表示装置である。 40

#### 【0045】

本発明は、前記絶縁膜がCMP研磨によって平坦化されていることを特徴としていても良い。

#### 【0046】

本発明は、前記半導体表示装置を用いることを特徴とするビデオカメラ、画像再生装置、ヘッドマウントディスプレイまたはパーソナルコンピュータであっても良い。

#### 【0047】

本発明は、

絶縁表面上に半導体層を形成する工程と、

前記半導体層を覆って前記絶縁表面上にゲート絶縁膜を形成する工程と、 50

前記ゲート絶縁膜上に第1の導電膜を形成する工程と、

前記第1の導電膜上に第2の導電膜を形成する工程と、

前記第1の導電膜と前記第2の導電膜をパターニングして第1のゲート電極と第2のゲート電極とを形成する工程と、

前記半導体層の前記第1及び第2のゲート電極が形成されている方から前記半導体層に第1の不純物を添加する工程と、

前記第1のゲート電極と前記第2のゲート電極とを覆って前記半導体層上にマスクを形成し、前記半導体層の前記マスクが形成されている方から前記第1の不純物と同じ導電型を有する第2の不純物を添加することで、前記半導体層中にチャネル形成領域と、前記チャネル形成領域に接する第1のLDD領域と、前記第1のLDD領域に接する第2のLDD領域と、前記第2のLDD領域に接するソース領域及びドレイン領域とを形成する工程と、

、

を有する半導体表示装置の作製方法であって、

チャネル長方向において、前記第1のゲート電極は前記第2のゲート電極よりも長く、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記第1のLDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっていることを特徴とする半導体表示装置の作製方法が提供される。

#### 【0048】

本発明は、

絶縁表面上に半導体層を形成する工程と、

前記半導体層を覆って前記絶縁表面上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に第1の導電膜を形成する工程と、

前記第1の導電膜上に第2の導電膜を形成する工程と、

前記第1の導電膜と前記第2の導電膜をパターニングして第1のゲート電極と第2のゲート電極とを形成する工程と、

前記半導体層の前記第1及び第2のゲート電極の形成されている方から前記半導体層に第1の不純物を添加する工程と、

前記第1のゲート電極と前記第2のゲート電極とを覆って前記半導体層上にマスクを形成し、前記半導体層の前記マスクが形成されている方から前記第1の不純物と同じ導電型を有する第2の不純物を添加することで、前記半導体層中にチャネル形成領域と、前記チャネル形成領域に接する第1のLDD領域と、前記第1のLDD領域に接する第2のLDD領域と、前記第2のLDD領域に接するソース領域及びドレイン領域とを形成する工程と、

、

を有する半導体表示装置の作製方法であって、

チャネル長方向において、前記第1のゲート電極は前記第2のゲート電極よりも長く、前記チャネル形成領域は前記ゲート絶縁膜を間に挟んで前記第2のゲート電極と重なっており、

前記第1のLDD領域は前記ゲート絶縁膜を間に挟んで前記第1のゲート電極と重なっていることを特徴とする半導体表示装置の作製方法が提供される。

#### 【0049】

本発明は、

絶縁表面上に半導体層を形成する工程と、

前記半導体層上に接するようにゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜に接するように第1のゲート電極と第1の形状の第2のゲート電極を形成する工程と、

前記第1のゲート電極、前記第1の形状の第2のゲート電極をエッチングして、テーパー部を有する第1のゲート電極と、第2の形状の第2のゲート電極を形成する工程と、

前記ゲート絶縁膜を通過させて前記半導体層に一導電型を付与する不純物元素を添加し、第2のLDD領域を形成すると同時に、前記第1のゲート電極のテーパー部を通過させて

10

20

30

40

50

前記半導体層に一導電型を付与する不純物元素を添加し、前記半導体層の端部に向かって不純物濃度が増加する第1のLDD領域を形成する工程と、

前記テーパー部を有する第1のゲート電極と第2の形状の第2のゲート電極をマスクとして一導電型を付与する不純物元素を添加してソース領域またはドレイン領域を形成する工程と、

を有する半導体表示装置の作製方法が提供される。

【0050】

【発明の実施の形態】

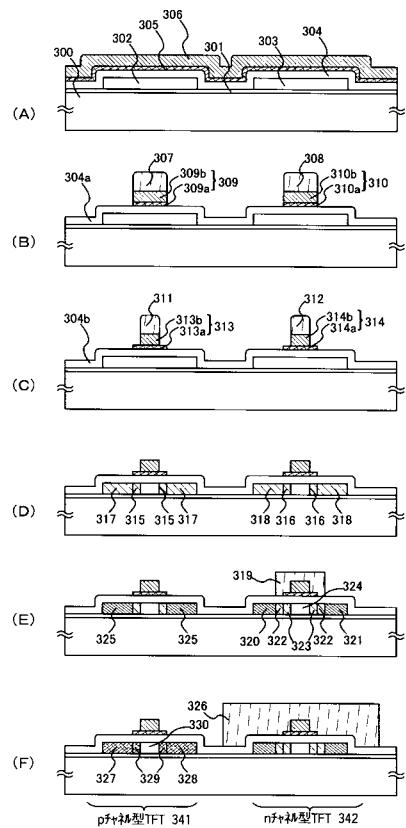

図1に本発明の薄膜トランジスタの構造およびその作製方法を示す。

【0051】

基板300上に下地膜301を形成する。下地膜301は形成しなくとも良いが、下地膜301を形成することは基板300から半導体層への不純物拡散を防ぐのに有効である。そして下地膜301上に公知の方法で形成された結晶質半導体膜からなる半導体層302、303を形成する。

【0052】

半導体層302、303を覆うようにゲート絶縁膜304を形成する。そしてゲート絶縁膜304上にゲート電極を形成するための第1の導電305と第2の導電膜306とを形成する。なお第1の導電膜305と第2の導電膜306は、エッチングで選択比の取れる導電性材料であることが必要である。(図1(A))

【0053】

次に、半導体層302、303上にレジストによるマスク307、308を形成する。そしてマスク307、308を用いて第1の導電膜305と第2の導電膜306をエッチングする(第1のエッチング処理)ことで第1の形状の導電層309、310(第1の導電層309a、310a、第2の導電層309b、310b)が形成される。(図1(B))

【0054】

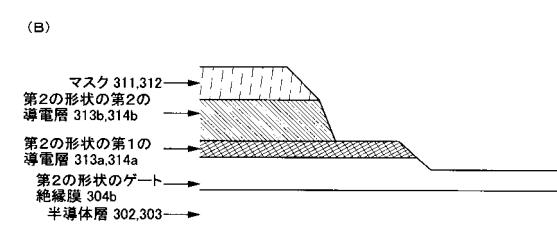

ここで図2(A)に図1(B)における第1の形状の導電層309、310の拡大図を示す。図2(A)示すように第1の導電層309a、310a及び第2の導電層309b、310bの端部はテーパーになっている。またゲート絶縁膜304は、上記エッチングによって第1の形状の導電層309、310で覆われない領域がエッチングされ薄くなり、第1の形状のゲート絶縁膜304aとなる。

【0055】

次に、図1(C)に示すように第2のエッチング処理を行う。第1の形状の第2の導電層309b、310bを異方性エッチングし、かつ、それより遅いエッチング速度で第1の導電層309a、310aを異方性エッチングし、第2の形状の導電層313、314(第1の導電層313a、314aと第2の導電層313b、314b)を形成する。

【0056】

ここで、図2(B)に図1(C)における第2の形状の導電層313、314の拡大図を示す。図2(B)示すように、第2のエッチング処理により第2の導電層313b、314bは第1の導電層313a、314aよりもよりたくさんエッチングされている。また、マスク307、308は第2のエッチング処理によってエッチングされ、マスク311、312となっている。また、第1の形状のゲート絶縁膜304aは、上記エッチングによって第2の形状の導電層313、314で覆われない領域がさらにエッチングされ薄くなり、第2の形状のゲート絶縁膜304bとなる。

【0057】

マスク311、312を除去し、図1(D)に示すように半導体層302、303に第1のドーピング処理を行い、n型を付与する不純物元素を添加する。ドーピングは、第2の形状の導電層313、314を不純物元素に対するマスクとして用い、第2の形状の第2の導電層313a、314aの下側の領域にも不純物元素が添加されるようにドーピングする。

10

20

30

40

50

## 【0058】

こうして、第2の導電層313a、314aと重なる第1の不純物領域315、316と、第1の不純物領域よりも不純物の濃度が高い第2の不純物領域317、318とが形成される。なお本実施例ではマスク311、312を除去してからn型を付与する不純物元素を添加したが、本発明はこれに限定されない。図1(D)の工程においてn型を付与する不純物元素を添加してからマスク311、312を除去しても良い。

## 【0059】

次に第2の形状の導電層314を覆うように半導体層303上にレジストからなるマスク319を形成する。マスク319は第2の形状のゲート絶縁膜304bを間に挟んで第2の不純物領域318と一部重なっている。そして第2のドーピング処理を行いn型を付与する不純物元素を添加する。この場合、第1のドーピング処理よりもドーズ量を上げて低い加速電圧の条件としてn型を付与する不純物元素をドーピングする。第2のドーピング処理によって、チャネル形成領域324及びLoV領域323の他に、自己整合的にソース領域320、ドレイン領域321、Loff領域322が半導体層303に形成される。また第2の形状の第1の導電層313aをマスクとした第2のドーピング処理によって、半導体層302に第3の不純物領域325が形成される。(図1(E))

10

## 【0060】

本発明はマスク319のサイズを制御することで、Loff領域322のサイズを自由に設定することが可能である。

20

## 【0061】

そして、図1(F)に示すように、nチャネル型TFTを形成する半導体層303はレジストマスク326で全面を被覆する。そして第2の形状の導電層313を不純物元素に対するマスクとして用いた第3のドーピング処理によって、pチャネル型TFTを形成する半導体層302にp型を付与する不純物元素を有するソース領域327、ドレイン領域328及びLoV領域329とチャネル形成領域330を自己整合的に形成する。

## 【0062】

ソース領域327、ドレイン領域328及びLoV領域329にはそれぞれ異なる濃度でn型を付与する不純物が添加されているが、p型を付与する不純物元素の濃度がn型を付与する不純物元素の濃度よりも十分に高くなるようにすることで、ソース領域327、ドレイン領域328及びLoV領域329の導電型をp型とした。

30

## 【0063】

以上までの工程でそれぞれの半導体層302、303に不純物領域(ソース領域、ドレイン領域、LoV領域、Loff領域)が形成される。半導体層302、303と重なる第2の形状の導電層313、314がゲート電極として機能する。第2の形状の第1の導電層313a、314aを第1のゲート電極、第2の形状の第2の導電層313b、314bを第2のゲート電極と呼ぶ。

## 【0064】

次に導電型の制御を目的として、それぞれの半導体層に添加された不純物元素を活性化する工程を行う。ただし、305、306に用いた導電性の材料が熱に弱い場合には、配線等を保護するため層間絶縁膜(シリコンを主成分とする)を形成した後で活性化を行うことが好ましい。なお、子の活性化は、レーザー光の照射や、赤外光の照射で行なっても良い。

40

## 【0065】

さらに、3~100%の水素を含む雰囲気中で熱処理を行い、半導体層302、303を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

## 【0066】

以上の工程が終了すると、pチャネル型TFT341、nチャネル型TFT342が完成する。

50

## 【0067】

なお図1及び図2では、チャネル長方向における第2のゲート電極313b、314bの長さと比べ、第2の形状の第1のゲート電極313a、314aのほうが長くなっている領域の表面が平坦であるように図示されているが、実際は非常に小さいテーパー角を有するテーパーとなっている。なお、エッチング条件によっては、平坦にすることも可能である。

## 【0068】

上述したように、本発明では、第1のゲート電極と第2のゲート電極のチャネル長方向(キャリアが移動する方向)の長さ(以下単にゲート電極の幅と呼ぶ)が異なっている。そのため、第1及び第2のゲート電極をマスクとしてイオン注入を行うことにより、ゲート電極の厚さが異なることによるイオンの侵入深さの違いを利用して、第2のゲート電極の下に位置する半導体層中のイオン濃度を、第2のゲート電極の下に位置せず、かつ第1のゲート電極の下に位置する半導体層中のイオン濃度より低くすることが可能である。そしてさらに、第2のゲート電極の下に位置せず、かつ第1のゲート電極の下に位置する半導体層中のイオン濃度を、第1のゲート電極の下に位置しない半導体層中のイオン濃度より低くすることが可能である。

## 【0069】

またマスクを用いてLoff領域を形成するために、エッチングで制御しなくてはならないのは第1のゲート電極と第2のゲート電極の幅のみであり、Loff領域とLov領域の位置の制御が従来に比べて容易になった。よって、Lov領域とLoft領域の微妙な位置あわせが容易になり、所望の特性を有するTFTを作製することが容易になった。

## 【0070】

なお、本発明の上記構成は、EL表示装置のみならず、液晶表示装置にも用いることが可能である。

## 【0071】

## 【実施例】

以下、本発明の実施例について説明する。

## 【0072】

## (実施例1)

本実施例では、同一基板上に画素部と、画素部の周辺に設ける駆動回路のTFT(nチャネル型TFT及びpチャネル型TFT)を同時に作製する方法について詳細に説明する。なお本明細書において駆動回路とは、ソース信号線駆動回路と、ゲート信号線駆動回路とを含む。そして本明細書において駆動回路のTFTを駆動回路用TFTと呼ぶ。

## 【0073】

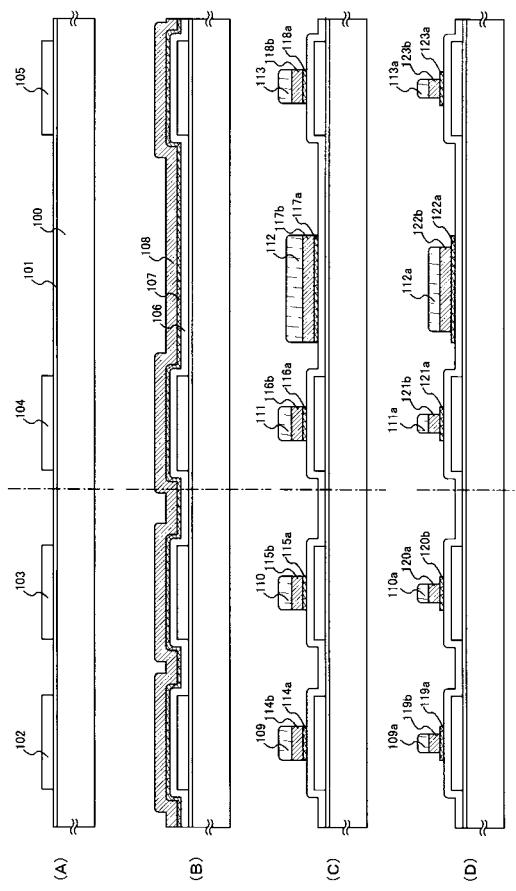

まず、図3(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、アルミノホウケイ酸ガラスなどのガラス、または石英基板から成る基板100上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜101を形成する。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜を10~200nm(好ましくは50~100nm)形成し、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化シリコン膜を50~200nm(好ましくは100~150nm)の厚さに積層形成する。なお図3(A)では1つの層で示した。本実施例では下地膜101を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させた構造として形成しても良い。

## 【0074】

半導体層102~105は、非晶質構造を有する半導体膜をレーザー結晶化法や公知の熱結晶化法を用いて作製した結晶質半導体膜で形成する。この半導体層102~105の厚さは25~80nm(好ましくは30~60nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

## 【0075】

10

20

30

40

50

公知の結晶化方法としては、電熱炉を使用した熱結晶化方法、レーザー光を用いたレーザーアニール結晶化法、赤外光を用いたランプアニール結晶化法、触媒金属を用いた結晶化法がある。

【0076】

レーザー結晶化法で結晶質半導体膜を作製するには、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宜選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数30Hzとし、レーザーエネルギー密度を100～400mJ/cm<sup>2</sup>(代表的には200～300mJ/cm<sup>2</sup>)とする。また、YAGレーザーを用いる場合にはその第2高調波を用いパルス発振周波数1～10kHzとし、レーザーエネルギー密度を300～600mJ/cm<sup>2</sup>(代表的には350～500mJ/cm<sup>2</sup>)とすると良い。そして幅100～1000μm、例えば400μmで線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を80～98%として行う。

【0077】

次いで、半導体層102～105を覆うゲート絶縁膜106を形成する。ゲート絶縁膜106はプラズマCVD法またはスパッタ法を用い、厚さを40～150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、120nmの厚さで酸化窒化シリコン膜で形成する。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。例えば、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO<sub>2</sub>とを混合し、反応圧力40Pa、基板温度300～400とし、高周波(13.56MHz)電力密度0.5～0.8W/cm<sup>2</sup>で放電させて形成することができる。このようにして作製される酸化シリコン膜は、その後400～500の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0078】

そして、ゲート絶縁膜106上にゲート電極を形成するための第1の導電膜107と第2の導電膜108とを形成する。本実施例では、第1の導電膜107をTaで50～100nmの厚さに形成し、第2の導電膜108をWで100～300nmの厚さに形成する。

【0079】

Ta膜はスパッタ法で形成し、TaのターゲットをArでスパッタする。この場合、Arに適量のXeやKrを加えると、Ta膜の内部応力を緩和して膜の剥離を防止することができる。また、Ta相のTa膜の抵抗率は20μcm程度でありゲート電極に使用することができるが、W相のTa膜の抵抗率は180μcm程度でありゲート電極とするには不向きである。Ta相のTa膜を形成するために、TaのW相に近い結晶構造をもつ窒化タンタルを10～50nm程度の厚さでTaの下地に形成しておくとTa相のTa膜を容易に得ることができる。

【0080】

W膜を形成する場合には、Wをターゲットとしたスパッタ法で形成する。その他に6フッ化タンゲステン(WF<sub>6</sub>)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999%または99.99%のWターゲットを用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9～20μcmを実現することができる。

【0081】

なお、本実施例では、第1の導電膜107をTa、第2の導電膜108をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cuから選ばれた元素、または前

10

20

30

40

50

記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。本実施例以外の他の組み合わせの一例は、第1の導電膜を窒化タンタル(TaN)で形成し、第2の導電膜をWとする組み合わせ、第1の導電膜を窒化タンタル(TaN)で形成し、第2の導電膜をAlとする組み合わせ、第1の導電膜を窒化タンタル(TaN)で形成し、第2の導電膜をCuとする組み合わせで形成することが好ましい。(図3(B))

#### 【0082】

次に、レジストによるマスク109～113を形成し、電極及び配線を形成するための第1のエッティング処理を行う。本実施例ではICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッティング法を用い、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>を混合し、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した場合にはW膜及びTaN膜とも同程度にエッティングされる。

10

#### 【0083】

なお図3(C)では図示しなかったが、上記エッティング条件では、レジストによるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパーとなる。テーパー部の角度は15～45°となる。ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10～20%程度の割合でエッティング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2～4(代表的には3)であるので、オーバーエッティング処理により、酸化窒化シリコン膜が露出した面は20～50nm程度エッティングされることになる。また図3(C)では図示しなかったが、ゲート絶縁膜106は、上記エッティングによって第1の形状の導電層114～118で覆われない領域が20～50nm程度エッティングされ薄くなつた。

20

#### 【0084】

こうして、第1のエッティング処理により第1の導電層と第2の導電層から成る第1の形状の導電層114～118(第1の導電層114a～118aと第2の導電層114b～118b)を形成する。

#### 【0085】

次に、図3(D)に示すように第2のエッティング処理を行う。同様にICPエッティング法を用い、エッティングガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>を混合して、1Paの圧力でコイル型の電極に500WのRF電力(13.56MHz)を供給し、プラズマを生成して行う。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、第1のエッティング処理に比べ低い自己バイアス電圧を印加する。このような条件によりW膜を異方性エッティングし、かつ、それより遅いエッティング速度で第1の導電層であるTaNを異方性エッティングして第2の形状の導電層119～123(第1の導電層119a～123aと第2の導電層119b～123b)を形成する。また図3(D)では図示しなかったが、ゲート絶縁膜106は、上記エッティングによって第2の形状の導電層119～123で覆われない領域がさらに20～50nm程度エッティングされ薄くなつた。また、マスク109～113は第2のエッティング処理によってエッティングされ、マスク109a～113aとなっている。

30

#### 【0086】

W膜やTaN膜のCF<sub>4</sub>とCl<sub>2</sub>の混合ガスによるエッティング反応は、生成されるラジカルまたはイオン種と反応生成物の蒸気圧から推測することができる。WとTaNのフッ化物と塩化物の蒸気圧を比較すると、Wのフッ化物であるWF<sub>6</sub>が極端に高く、その他のWC<sub>1.5</sub>、TaF<sub>5</sub>、TaCl<sub>5</sub>は同程度である。従って、CF<sub>4</sub>とCl<sub>2</sub>の混合ガスではW膜及びTaN膜共にエッティングされる。しかし、この混合ガスに適量のO<sub>2</sub>を添加するとCF<sub>4</sub>とO<sub>2</sub>が反応してCOとFになり、FラジカルまたはFイオンが多量に発生する。その結果、フッ化物の蒸気圧が高いW膜のエッティング速度が増大する。一方、TaNはFが増大しても相対的にエッティング速度の増加は少ない。また、TaNはWに比較して酸化されやすいので、O<sub>2</sub>を添加することでTaNの表面が酸化される。TaNの酸化物はフッ素や塩素と反応しない

40

50

ためさらにTa膜のエッティング速度は低下する。従って、W膜とTa膜とのエッティング速度に差を作ることが可能となりW膜のエッティング速度をTa膜よりも大きくすることが可能となる。

#### 【0087】

そして、マスク109a～マスク113aを除去し、図4(A)に示すように第1のドーピング処理を行い、n型を付与する不純物元素を添加する。例えば、加速電圧を70～120keVとし、 $1 \times 10^{13}/\text{cm}^2$ のドーズ量で行う。ドーピングは、第2の形状の導電層119～123を不純物元素に対するマスクとして用い、第2の導電層119a～123aの下側の領域にも不純物元素が添加されるようにドーピングする。こうして、第2の導電層119a～123aと重なる第1の不純物領域125～128と、第1の不純物領域よりも不純物の濃度が高い第2の不純物領域129～132とが形成される。なお本実施例ではマスク109a～マスク113aを除去してからn型を付与する不純物元素を添加したが、本発明はこれに限定されない。図4(A)の工程においてn型を付与する不純物元素を添加してからマスク109a～マスク113aを除去しても良い。

#### 【0088】

次に第2の導電層121a、121bを覆うように半導体層104上にレジストからなるマスク133を形成する。マスク133はゲート絶縁膜106を間に挟んで第2の不純物領域131と一部重なっている。そして第2のドーピング処理を行いn型を付与する不純物元素を添加する。この場合、第1のドーピング処理よりもドーズ量を上げて低い加速電圧の条件としてn型を付与する不純物元素をドーピングする。(図4(B))ドーピングの方法はイオンドープ法若しくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を $1 \times 10^{13} \sim 5 \times 10^{14} \text{atoms}/\text{cm}^2$ とし、加速電圧を60～100keVとして行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いる。この場合、第2の形状の導電層119～123がn型を付与する不純物元素に対するマスクとなり、自己整合的にソース領域134～137、ドレイン領域138～141、L<sub>o</sub>V領域142～145が形成される。またマスク133によってL<sub>o</sub>f<sub>f</sub>領域146が形成される。ソース領域134～137、ドレイン領域138～141には $1 \times 10^{20} \sim 1 \times 10^{21} \text{atomic}/\text{cm}^3$ の濃度範囲でn型を付与する不純物元素を添加する。

#### 【0089】

本発明はマスク133のサイズを制御することで、L<sub>o</sub>f<sub>f</sub>領域146の、キャリアが移動する方向における長さを自由に設定することが可能である。

#### 【0090】

n型を付与する不純物元素は、L<sub>o</sub>f<sub>f</sub>領域で $1 \times 10^{17} \sim 1 \times 10^{19} \text{atoms}/\text{cm}^3$ の濃度となるようにし、L<sub>o</sub>V領域で $1 \times 10^{16} \sim 1 \times 10^{18} \text{atoms}/\text{cm}^3$ の濃度となるようにする。

#### 【0091】

そして、図4(C)に示すように、pチャネル型TFTを形成する半導体層102、105に一導電型とは逆の導電型の不純物元素が添加されたソース領域147、148と、ドレイン領域149、150と、L<sub>o</sub>V領域151、152を形成する。第2の形状を有する第2の導電層119b、123bを不純物元素に対するマスクとして用い、自己整合的に不純物領域を形成する。このとき、nチャネル型TFTを形成する半導体層102、103はレジストマスク153で全面を被覆しておく。ソース領域147、148及びドレイン領域149、150と、L<sub>o</sub>V領域151、152とにはそれぞれ異なる濃度でリンが添加されているが、ジボラン( $\text{B}_2\text{H}_6$ )を用いたイオンドープ法で形成し、そのいずれの領域においても不純物濃度を $2 \times 10^{20} \sim 2 \times 10^{21} \text{atoms}/\text{cm}^3$ となるようにする。実際には、ソース領域147、148と、ドレイン領域149、150と、L<sub>o</sub>V領域151、152に含まれるボロンは、第2のドーピング処理と同様に半導体層上に位置する、端部の断面がテーパーとなっている導電層や絶縁膜の膜厚による影響を受け、不純物元素の濃度も変化している。

10

20

30

40

50

## 【0092】

以上までの工程でそれぞれの半導体層102～105に不純物領域（ソース領域、ドレン領域、L<sub>o</sub>v領域、L<sub>o</sub>f<sub>f</sub>領域）が形成される。半導体層と重なる第2の形状の導電層119～121、123がゲート電極として機能する。また、第2の形状の導電層122は容量配線として機能する。

## 【0093】

こうして導電型の制御を目的として、それぞれの半導体層に添加された不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法（RTA法）を適用することができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400～700、代表的には500～600で行うものであり、本実施例では500で4時間の熱処理を行う。ただし、119～123に用いた配線材料が熱に弱い場合には、配線等を保護するため層間絶縁膜（シリコンを主成分とする）を形成した後で活性化を行うことが好ましい。

10

## 【0094】

さらに、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行い、半導体層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダンギングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

20

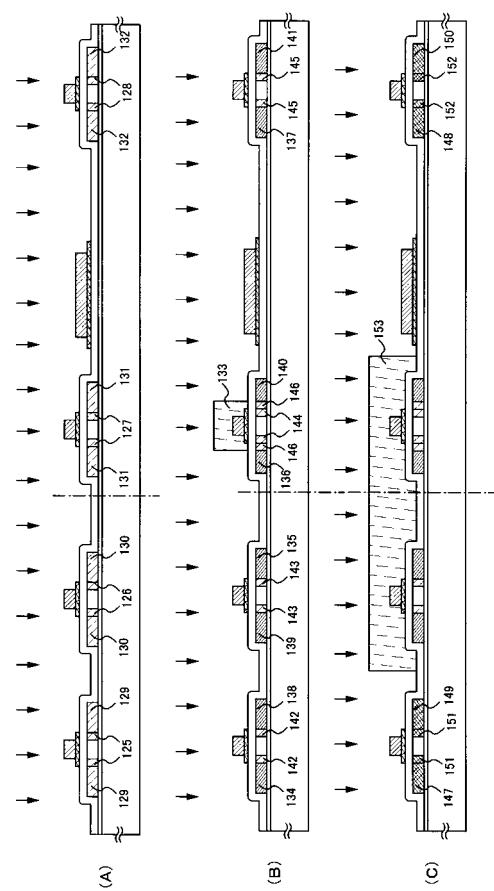

## 【0095】

次いで、第1の層間絶縁膜155は酸化窒化シリコン膜から100～200nmの厚さで形成する。その上に有機絶縁物材料から成る第2の層間絶縁膜156を形成する。

## 【0096】

そして第2の層間絶縁膜156の容量配線122上と、ソース領域148上とにコンタクトホールを形成し、前記第1の層間絶縁膜の一部を露出させる。次に中間配線（電源供給線）157を容量配線122上のコンタクトホールを介して第1の層間絶縁膜155に接するように形成した。（図5（A））

## 【0097】

次に第2の層間絶縁膜156上に、有機絶縁物材料から成る第3の層間絶縁膜158を形成する。

30

## 【0098】

そして、ゲート絶縁膜106、第1の層間絶縁膜155、第2の層間絶縁膜156にコンタクトホールを形成し、該コンタクトホールを介して、ソース領域147、135、136、148と接するようにソース配線159～162を形成した。また同様に、ドレン領域149、139、140、150と接するドレン配線163～165を形成する（図5（B））。ドレン領域140と容量配線122とは、ドレン配線164によって電気的に接続される。また電源供給線（中間配線）157とソース領域148とは、ソース配線162によって電気的に接続される。

## 【0099】

なお、ゲート絶縁膜106、第1の層間絶縁膜155、第2の層間絶縁膜156がSiO<sub>2</sub>膜またはSiON膜の場合、CF<sub>4</sub>とO<sub>2</sub>とを用いたドライエッチングでコンタクトホールを形成するのが好ましい。またゲート絶縁膜106、第1の層間絶縁膜155、第2の層間絶縁膜156が有機樹脂膜の場合、CHF<sub>3</sub>を用いたドライエッチング、またはBF<sub>3</sub>（緩衝フッ酸：HF + NH<sub>4</sub>F）でコンタクトホールを形成するのが好ましい。またゲート絶縁膜106、第1の層間絶縁膜155、第2の層間絶縁膜156が異なる材料で形成されている場合、膜ごとにエッチングの方法及び用いるエッチャントやエッチングガスの種類を変えることが好ましいが。エッチングの方法及び用いるエッチャントやエッチングガスを全て同じにしてコンタクトホールを形成しても良い。

40

## 【0100】

容量配線122と電源供給線157との間に第1の層間絶縁膜155が接して設けられて

50

いる部分に、保持容量 166 が形成される。

【0101】

次に、有機樹脂からなる第4層間絶縁膜 167 を形成する。有機樹脂としてはポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)等を使用することができる。特に、第4層間絶縁膜 167 は平坦化の意味合いが強いので、平坦性に優れたアクリルが好み。本実施例では TFT によって形成される段差を十分に平坦化しうる膜厚でアクリル膜を形成する。好ましくは 1~5 μm(さらに好ましくは 2~4 μm) とすれば良い。

【0102】

次に第4層間絶縁膜 167 に、ドレイン配線 165 に達するコンタクトホールを形成し、画素電極 168 を形成する。本実施例では酸化インジウム・スズ(ITO)膜を 110 nm の厚さに形成し、パターニングを行って画素電極 168 を形成する。また、酸化インジウムに 2~20% の酸化亜鉛(ZnO)を混合した透明導電膜を用いても良い。この画素電極 168 が EL 素子の陽極となる。(図 5(C))

【0103】

次に、樹脂材料でなる第1バンク 169 及び第2バンク 170 を形成する。第1バンク 169 及び第2バンク 170 は後に形成される EL 層及び陰極を隣り合う画素間で分離するために設けられる。よって第1バンク 169 よりも第2バンク 170 の方が横に張り出している構成にすることが望ましい。なお第1バンク 169 と第2バンク 170 とを合わせた厚さは 1~2 μm 程度であることが好ましいが、後に形成される EL 層及び陰極を隣り合う画素間で分離することができるならこの厚さに限らない。また第1バンク 169 及び第2バンク 170 は絶縁膜で形成されることが必要であり、例えば酸化物、樹脂等で形成することが可能である。そして第1バンク 169 と第2バンク 170 は互いに同じ材料で形成されていても、異なる材料で形成されていてもどちらでも良い。第1バンク 169 及び第2バンク 170 は画素と画素との間にストライプ状に形成される。第1バンク 169 及び第2バンク 170 はソース配線(ソース信号線)上に沿って形成しても良いし、ゲート配線(ゲート信号線)上に沿って形成しても良い。なお第1バンク 169 及び第2バンク 170 を樹脂に顔料等を混ぜたもので形成しても良い。(図 6(A))

【0104】

次に、EL 層 171 及び陰極(MgAg 電極) 172 を、真空蒸着法を用いて大気解放しないで連続形成する。なお、EL 層 171 の膜厚は 80~200 nm(典型的には 100~120 nm)、陰極 172 の厚さは 180~300 nm(典型的には 200~250 nm) とすれば良い。なお、本実施例では一画素しか図示されていないが、このとき同時に赤色に発光する EL 層、緑色に発光する EL 層及び青色に発光する EL 層が形成される。

【0105】

この工程では、赤色に対応する画素、緑色に対応する画素及び青色に対応する画素に対して順次 EL 層 171 を形成する。但し、EL 層 171 は溶液に対する耐性に乏しいためフォトリソグラフィ技術を用いずに各色個別に形成しなくてはならない。そこでメタルマスクを用いて所望の画素以外を隠し、必要箇所だけ選択的に EL 層 171 を形成するのが好み。

【0106】

即ち、まず赤色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて赤色発光の EL 層を選択的に形成する。次いで、緑色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて緑色発光の EL 層を選択的に形成する。次いで、同様に青色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて青色発光の EL 層を選択的に形成する。なお、ここでは全て異なるマスクを用いるように記載しているが、同じマスクを使いまわしても構わない。また、全画素に EL 層を形成するまで真空を破らずに処理することが好み。

【0107】

なお、本実施例では EL 層 171 を発光層のみからなる単層構造とするが、EL 層は発光層の他に正孔輸送層、正孔注入層、電子輸送層、電子注入層等を有していても構わない。

10

20

30

40

50

このように組み合わせは既に様々な例が報告されており、そのいずれの構成を用いても構わない。EL層171としては公知の材料を用いることができる。公知の材料としては、EL駆動電圧を考慮すると有機材料を用いるのが好ましい。

#### 【0108】

次にEL素子の陰極172を形成する、本実施例では、陰極172としてMgAg電極を用いた例を示すが、公知の他の材料を用いることが可能である。

#### 【0109】

こうして図6(B)に示すような構造のELパネルが完成する。なお、第1バンク169と第2バンク170を形成した後、陰極172を形成するまでの工程をマルチチャンバー方式(またはインライン方式)の薄膜形成装置を用いて、大気開放せずに連続的に処理することは有効である。

10

#### 【0110】

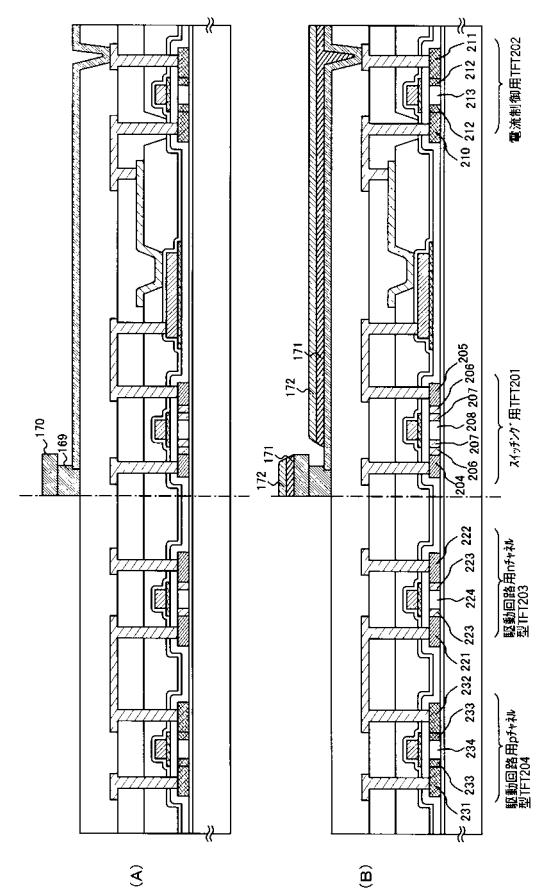

本実施例において、スイッチング用TFT201の半導体層は、ソース領域204、ドレイン領域205、Loff領域206、Lov領域207、チャネル形成領域208を含んでいる。Loff領域206はゲート絶縁膜106を介してゲート電極116と重ならないように設けられている。またLov領域207はゲート絶縁膜106を介してゲート電極121と重なるように設けられている。このような構造はオフ電流を低減する上で非常に効果的である。

#### 【0111】

また、本実施例ではスイッチング用TFT201はシングルゲート構造としているが、本発明ではスイッチング用TFTはダブルゲート構造やその他のマルチゲート構造を有していても良い。ダブルゲート構造とすることで実質的に二つのTFTが直列された構造となり、オフ電流をさらに低減することができるという利点がある。

20

#### 【0112】

また本実施例ではスイッチング用TFT201はnチャネル型TFTであるが、pチャネル型TFTであってもかまわない。

#### 【0113】

電流制御用TFT202の半導体層は、ソース領域210、ドレイン領域211、Lov領域212、チャネル形成領域213を含んでいる。Lov領域212はゲート絶縁膜106を介してゲート電極123と重なるように設けられている。なお本実施例において電流制御用TFT202はLoff領域を有していないが、Loff領域を有する構成にしても良い。

30

#### 【0114】

また本実施例では電流制御用TFT202はpチャネル型TFTであるが、nチャネル型TFTであってもかまわない。

#### 【0115】

なお、本実施例のELパネルは、画素部だけでなく駆動回路部にも最適な構造のTFTを配置することにより、非常に高い信頼性を示し、動作特性も向上しうる。

#### 【0116】

まず、極力動作速度を落とさないようにホットキャリア注入を低減させる構造を有するTFTを、駆動回路部を形成するCMOS回路のnチャネル型TFT203として用いる。なお、ここでいう駆動回路としては、シフトレジスタ、バッファ、レベルシフタ、サンプリング回路(サンプル及びホールド回路)などが含まれる。デジタル駆動を行う場合には、D/Aコンバータなどの信号変換回路も含まれ得る。

40

#### 【0117】

本実施例の場合、CMOS回路のnチャネル型TFT203の半導体層は、ソース領域221、ドレイン領域222、Lov領域223及びチャネル形成領域224を含んでいる。

#### 【0118】

また、このnチャネル型TFT203はオフ電流をあまり気にする必要はなく、それより

50

も動作速度を重視した方が良い。従って、ゲート絶縁膜 106 を介してゲート電極 120 に重なっている L<sub>o</sub>v 領域 223 を設けることは、抵抗成分を極力少なくするので動作速度を向上させるのに有効である。

【0119】

また本実施例の場合、CMOS回路のpチャネル型TFT204の半導体層は、ソース領域231、ドレイン領域232、L<sub>o</sub>v領域233及びチャネル形成領域234を含んでいる。

【0120】

なお、実際には図6(B)まで完成したら、さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)や透光性のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気(10)にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりするとEL素子の信頼性が向上する。

【0121】

また、パッケージング等の処理により気密性を高めたら、基板上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクター(フレキシブルプリントサーキット: FPC)を取り付けて製品として完成する。このような出荷できるまでした状態を本明細書中ではEL表示装置という。

【0122】

上述したように本発明では、ゲート電極の幅が異なっているため、ゲート電極をマスクとしてイオン注入を行うことにより、ゲート電極の厚さが異なることによるイオンの侵入深度の違いを利用して、第1のゲート電極の下に位置する半導体層中のイオン濃度を、第1のゲート電極の下に位置しない半導体層中のイオン濃度より低くすることが可能である。

【0123】

またマスクを用いてL<sub>o</sub>ff領域を形成するために、エッチングで制御しなくてはならないのは第1のゲート電極と第2のゲート電極の幅のみであり、L<sub>o</sub>ff領域とL<sub>o</sub>v領域の位置の制御が従来に比べて容易になった。よって、L<sub>o</sub>v領域とL<sub>o</sub>ff領域の微妙な位置あわせが容易になり、所望の特性を有するTFTを作製することも容易になった。

【0124】

また従来ゲート信号線またはソース信号線と同じ膜から形成されていた電源供給線を第2の層間絶縁膜と第3の層間絶縁膜の間に設けている。そのために電源供給線をゲート信号線と重ねて設けることができる、開口率を上げることができる。

【0125】

なお本実施例ではEL層から発せられる光が基板側に向いている例について説明したが、本発明はこれに限定されず、EL層から発せられる光が基板の上に向いているような構成であっても良い。この場合EL素子の陰極が画素電極となり、電流制御用TFTはnチャネル型TFTであることが望ましい。

【0126】

(実施例2)

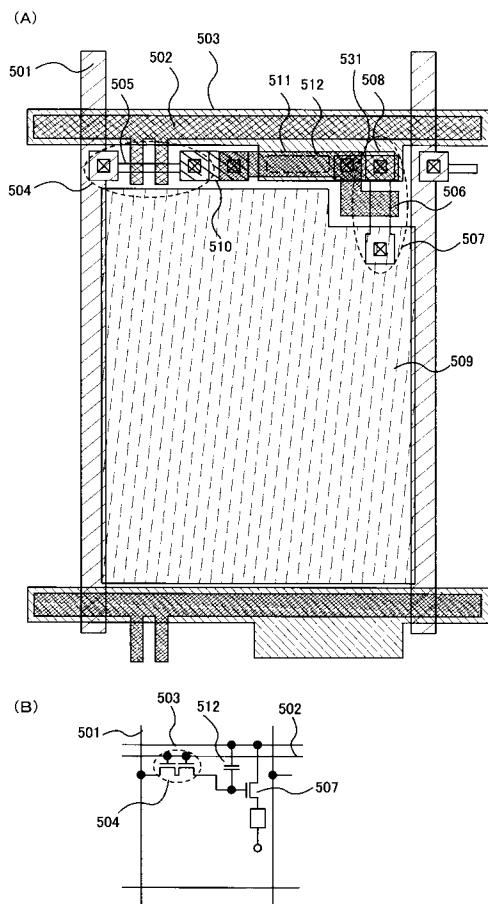

本実施例では、薄膜トランジスタを2つ有するEL表示装置の画素の上面図について説明する。

【0127】

図7(A)に本実施例のEL表示装置の上面図を示す。また図7(B)は本実施例のEL表示装置の画素の回路図である。501はソース信号線、502はゲート信号線である。ゲート信号線502上に設けられている配線503は電源供給線であり、ゲート信号線502と重なっている。

【0128】

504はスイッチング用TFTであり、半導体層505を有している。半導体層505上にゲート信号線502の一部がゲート電極として設けられている。そして半導体層505のソース領域とドレイン領域は、一方はソース信号線501に、もう一方はドレイン配線

10

20

30

40

50

510によって容量配線511に接続されている。電源供給線503は、512で示す部分で第1の層間絶縁膜(図示せず)と接しており、電源供給線503と第1の層間絶縁膜と容量配線511とで保持容量を形成している。

【0129】

容量配線511は電流制御用TFT507のゲート電極506と接続されている。電流制御用TFT507は半導体層508を有しており、半導体層508が有するソース領域はソース配線531を介して電源供給線503に接続されており、ドレイン領域は画素電極509に接続されている。

【0130】

本発明は電源供給線503を第2の層間絶縁膜と第3の層間絶縁膜の間に設けている。そのため電源供給線をゲート信号線と重ねて設けることができるので、開口率を上げることができる。

10

【0131】

(実施例3)

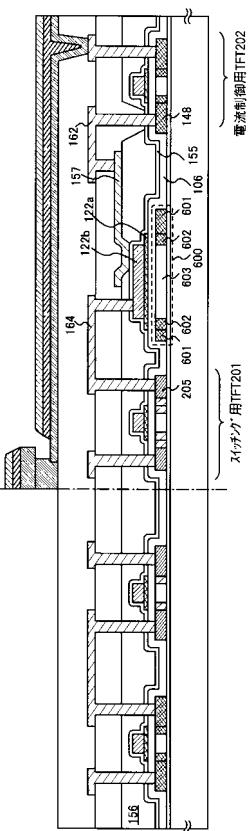

本実施例では、保持容量を、容量配線と第1の層間絶縁膜と電源供給線とで形成する構成に加え、容量配線とゲート絶縁膜と半導体層とで形成した例について説明する。なお図3～図6で示した物は同じ符号を用いる。

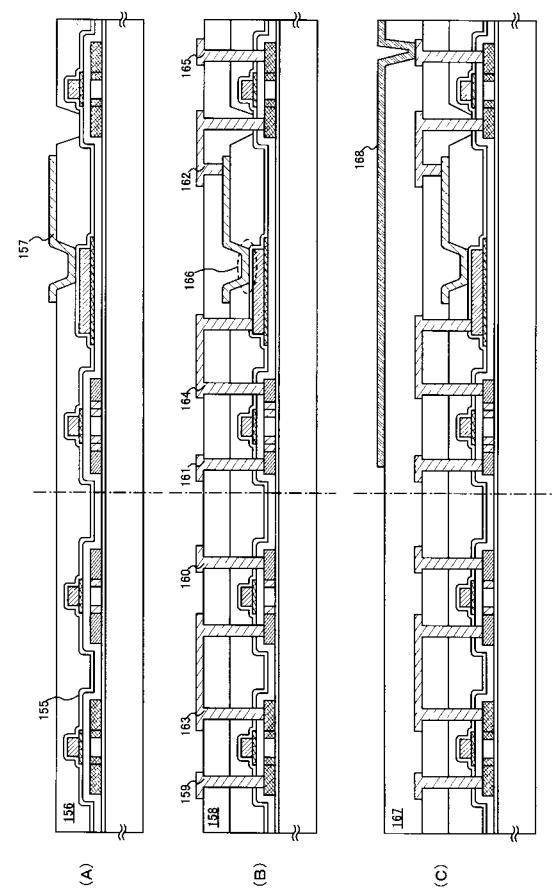

【0132】

図8に本実施例のEL表示装置の断面図を示す。本実施例のEL表示装置は図6(B)で示したEL表示装置と、半導体層600を有している点が異なっている。なおその他の構成については実施例1において既に述べているので、本実施例のEL表示装置の詳しい構成については実施例1を参照し、ここでは説明を省略する。

20

【0133】

半導体層600はゲート絶縁膜106を間に挟んで第1の容量配線122a及び第2の容量配線122bと重なっている。半導体層600はチャネル形成領域603と、チャネル形成領域603の端部に接するように設けられた第1の不純物領域602と、第1の不純物領域602に接するように設けられた第2の不純物領域601とを有している。第1の不純物領域602における不純物の濃度は第2の不純物領域601における不純物の濃度よりも低い。また第1の不純物領域602は第1の容量配線122aと、ゲート絶縁膜106を間に挟んで重なっている。

30

【0134】

なお本実施例のように電流制御用TFT202がpチャネル型TFTの場合、第1の不純物領域602と第2の不純物領域601には、p型の不純物が添加されていることが望ましい。逆に電流制御用TFT202がnチャネル型TFTの場合、第1の不純物領域602と第2の不純物領域601には、n型の不純物が添加されていることが望ましい。

【0135】

第2の容量配線122bはドレイン配線164によってスイッチング用TFT201のドレイン領域205と電気的に接続されている。また電源供給線157は第2の層間絶縁膜156に形成されたコンタクトホールを介して第2の容量配線122b上の第1の層間絶縁膜155と接している。またさらに、電源供給線157はソース配線162に接続されており、ソース配線162は、ゲート絶縁膜106と第1の層間絶縁膜155と、第2の層間絶縁膜156とに設けられたコンタクトホールを介して電流制御用TFT202のソース領域148に接続されている。

40

【0136】

本実施例の構成によって、保持容量の容量値を高くすることができる。なお本実施例の場合、EL層から発せられる光は基板側に向いているために、保持容量の面積を大きくすると開口率の低下によってEL表示装置の輝度が低くなってしまっていたが、本実施例の構成では、容量配線122とゲート絶縁膜106と半導体層600とで形成される保持容量が、電源供給線157と第1の層間絶縁膜155と容量配線122とで形成される保持容量とが重なっているために、開口率を低下させることなく保持容量の容量値を高くするこ

50

とができる。

【0137】

なお本実施例ではEL層から発せられる光が基板側に向いている例について説明したが、本発明はこれに限定されず、EL層から発せられる光が基板の上に向いているような構成であっても良い。この場合EL素子の陰極が画素電極となり、電流制御用TFTはnチャネル型TFTであることが望ましい。

【0138】

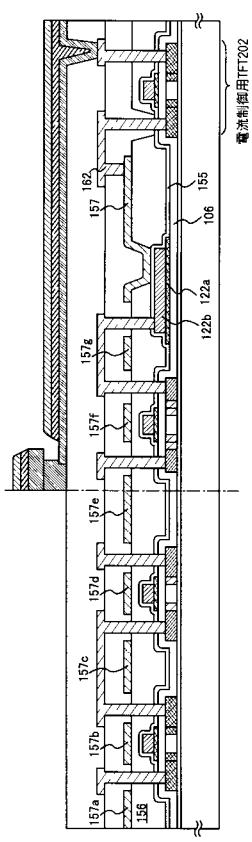

(実施例4)

本実施例では、電源供給線と遮蔽膜(ブラックマトリクス)とを同時に形成する例について説明する。なお図3～図6で示した物は同じ符号を用いる。

10

【0139】

図9に本実施例のEL表示装置の断面図を示す。本実施例のEL表示装置は図6(B)で示したEL表示装置と、遮蔽膜157a～gを有している点が異なっている。なおその他の構成については実施例1において既に述べているので、本実施例のEL表示装置の詳しい構成については実施例1を参照し、ここでは説明を省略する。

【0140】

電源供給線157は第2の層間絶縁膜156に形成されたコンタクトホールを介して第2の容量配線122b上の第1の層間絶縁膜155と接している。さらに電源供給線157はソース配線162に接続されており、ソース配線162は、ゲート絶縁膜106と第1の層間絶縁膜155と、第2の層間絶縁膜156とに設けられたコンタクトホールを介して電流制御用TFT202のソース領域148に接続されている。

20

【0141】

遮蔽膜157a～gは第2の層間絶縁膜上に電源供給線157と同時に形成される。遮蔽膜157a～gを設けることによって、EL表示装置の外部からの光とEL素子の発する光とがTFTのチャネル形成領域に入射することによってオフ電流が増加するのを防ぐことができる。

【0142】

また本実施例の遮蔽膜157a～gは電源供給線157と同時に形成することが可能であるため、工程数を増やす必要がない。

30

【0143】

なお本実施例の場合、遮蔽膜157a～gと電源供給線157とを光を透過しにくい材料で形成することが重要である。

【0144】

なお本実施例ではEL層から発せられる光が基板側に向いている例について説明したが、本発明はこれに限定されず、EL層から発せられる光が基板の上に向いているような構成であっても良い。この場合EL素子の陰極が画素電極となり、電流制御用TFTはnチャネル型TFTであることが望ましい。

【0145】

なお本実施例は実施例3と組み合わせて実施することが可能である。

40

【0146】

(実施例5)

本実施例では、遮蔽膜を基板とTFTの半導体層との間に設ける例について説明する。なお図3～図6で示した物は同じ符号を用いる。

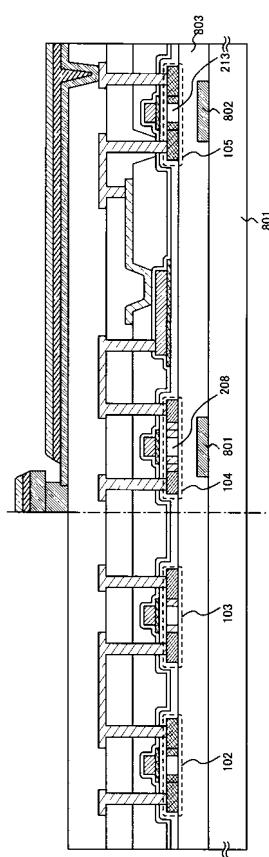

【0147】

図10に本実施例のEL表示装置の断面図を示す。本実施例のEL表示装置は図6(B)で示したEL表示装置と、遮蔽膜801、802を有している点が異なっている。なおその他の構成については実施例1において既に述べているので、本実施例のEL表示装置の詳しい構成については実施例1を参照し、ここでは説明を省略する。

【0148】

本実施例のEL表示装置は、スイッチング用TFTの半導体層104と電流制御用TFT

50

の半導体層 105 の下に遮蔽膜 801 と 802 とを設けている。遮蔽膜 801、802 は、スイッチング用 TFT の半導体層 104 のチャネル形成領域 208 と、電流制御用 TFT の半導体層 105 のチャネル形成領域 213 と絶縁膜（本実施例では酸化膜）803 を間に挟んで重なっている。

【0149】

遮蔽膜 801、802 は光を遮蔽することができ、遮蔽膜が形成された後の工程における加熱処理の温度に耐えうる材料ならば、いずれの材料でも用いることが可能であり、光を透過しにくい金属、シリコン、等を用いることが可能である。本実施例では W を用いた。なお遮蔽膜 801、802 の厚さは 0.1 μm ~ 0.5 μm 程度であることが好ましい。また酸化膜 803 の厚さは 0.5 μm ~ 1.5 μm 程度であることが好ましい。さらに遮蔽膜 801、802 と半導体層 104、105 との間の距離は 0.1 μm ~ 0.5 μm 程度であることが好ましい。

10

【0150】

なお本実施例では遮蔽膜を画素部に設けられた TFT の下側にのみ設けたが、本実施例はこれに限定されない。同様に駆動回路用の TFT の下に遮蔽膜を設けてもかまわない。

【0151】

本実施例は上記構成によって、基板の下側から入射する光がチャネル形成領域に入射することによって TFT のオフ電流が上がるのを防いでいる。

【0152】

酸化膜 803 の表面が平坦化されていないと、その上に形成された半導体層を結晶化させる際に、半導体層が均一に結晶化されないという問題が起こってしまう。よって、酸化膜 803 上には半導体層を直に形成するので、半導体層を形成する前に酸化膜 803 の表面を平坦化しておくことが好ましい。

20

【0153】

例えば、CMP（ケミカルメカニカルポリッシング）を用いて酸化膜 803 を平坦化しても良い。CMP は公知の方法を用いて行うことができる。

【0154】

本実施例ではシリカゴルと電解溶液とを混合したものを用いて研磨を行う。電解溶液中において、100 kg / cm<sup>2</sup> の圧力を研磨パッドから加えて研磨を行う。この研磨の際の圧力は 50 kg / cm<sup>2</sup> ~ 150 kg / cm<sup>2</sup> 程度の範囲から選択することができる。また研磨を行う表面と研磨パッドとの隙間は 0.1 μm として研磨を行う。

30

【0155】

上記構成によって、TFT のオフ電流を抑えることができ、なおかつ半導体層の結晶性が不均一になるのを防ぐことができる。

【0156】

なお本実施例では EL 層から発せられる光が基板側に向いている例について説明したが、本発明はこれに限定されず、EL 層から発せられる光が基板の上に向いているような構成であっても良い。この場合 EL 素子の陰極が画素電極となり、電流制御用 TFT は n チャネル型 TFT であることが望ましい。

【0157】

40

なお本実施例は実施例 3、実施例 4 と組み合わせて実施することが可能である。

【0158】

（実施例 6）

本実施例は、ソース信号線を形成した後にゲート信号線を形成する例について説明する。

【0159】

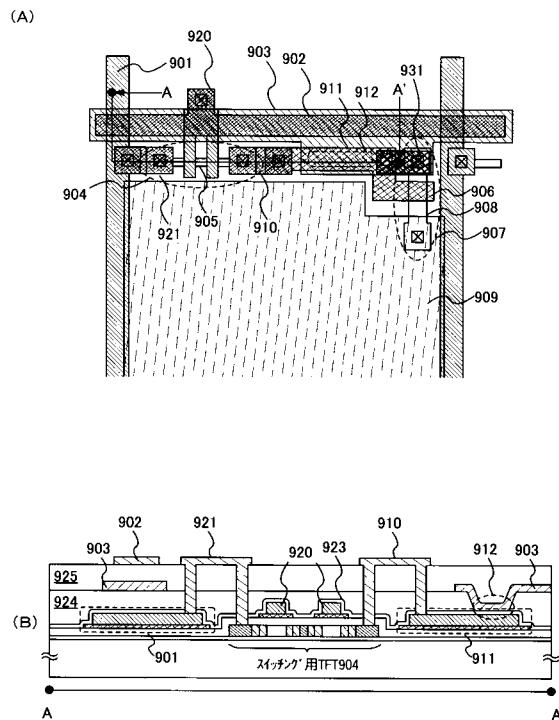

図 11 (A) に本実施例の EL 表示装置の上面図を示す。なお図 11 (B) は図 11 (A) の A - A' における断面図である。901 はソース信号線、902 はゲート信号線である。ゲート信号線 902 の下に設けられている配線 903 は電源供給線であり、絶縁膜を間に挟んでゲート信号線 902 と重なっている。

【0160】

50

904 はスイッチング用 TFT であり、半導体層 905 を有している。半導体層 905 上にゲート信号線 902 に接続されたゲート電極 920 が設けられている。そして半導体層 905 のソース領域とドレイン領域は、一方はソース配線 921 によってソース信号線 901 に、もう一方はドレイン配線 910 によって容量配線 911 に接続されている。電源供給線 903 は、912 で示す部分で第 1 の層間絶縁膜 923 と接しており、電源供給線 903 と第 1 の層間絶縁膜 923 と容量配線 911 とで保持容量を形成している。

【 0161 】

容量配線 911 は電流制御用 TFT 907 のゲート電極 906 と接続されている。電流制御用 TFT 907 は半導体層 908 を有しており、半導体層 908 が有するソース領域はソース配線 931 を介して電源供給線 903 に接続されており、ドレイン領域は画素電極 909 に接続されている。

10

【 0162 】

本発明は電源供給線 903 を第 2 の層間絶縁膜 924 と第 3 の層間絶縁膜 925 の間に設けている。そのために電源供給線をゲート信号線と重ねて設けることができる、開口率を上げることができる。

【 0163 】

( 実施例 7 )

本実施例では、実施の形態において半導体層として用いる結晶質半導体膜を、触媒元素を用いた熱結晶化法により形成する例を示す。触媒元素を用いる場合、特開平 7 - 130652 号公報、特開平 8 - 78329 号公報で開示された技術を用いることが望ましい。

20

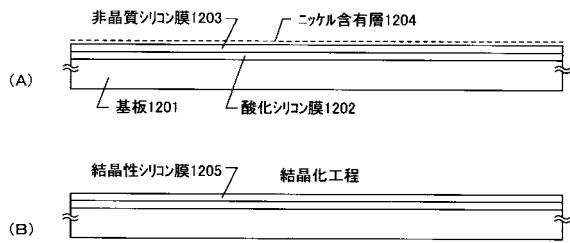

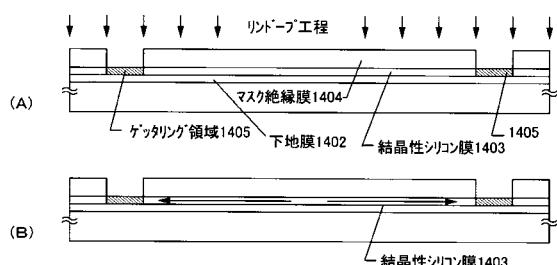

【 0164 】

ここで、特開平 7 - 130652 号公報に開示されている技術を本発明に適用する場合の例を図 12 に示す。まず基板 1201 に酸化シリコン膜 1202 を設け、その上に非晶質シリコン膜 1203 を形成した。さらに、重量換算で 10 ppm のニッケルを含む酢酸ニッケル塩溶液を塗布してニッケル含有層 1204 を形成した。( 図 12 ( A ) )

【 0165 】

次に、500 、1 時間の脱水素工程の後、500 ~ 650 で 4 ~ 12 時間、例えば 550 、8 時間の熱処理を行い、結晶質シリコン膜 1205 を形成した。こうして得られた結晶質シリコン膜 1205 は非常に優れた結晶質を有した。( 図 12 ( B ) )

30

【 0166 】

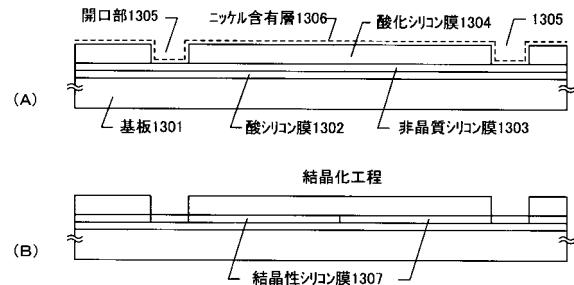

また、特開平 8 - 78329 号公報で開示された技術は、触媒元素を選択的に添加することによって、非晶質半導体膜の選択的な結晶化を可能としたものである。同技術を本発明に適用した場合について、図 13 で説明する。

【 0167 】

まず、ガラス基板 1301 に酸化シリコン膜 1302 を設け、その上に非晶質シリコン膜 1303 、酸化シリコン膜 1304 を連続的に形成した。この時、酸化シリコン膜 1304 の厚さは 150 nm とした。

【 0168 】

次に酸化シリコン膜 1304 をパターニングして、選択的に開孔部 1305 を形成し、その後、重量換算で 10 ppm のニッケルを含む酢酸ニッケル塩溶液を塗布した。これにより、ニッケル含有層 1306 が形成され、ニッケル含有層 1306 は開孔部 1305 の底部のみで非晶質シリコン膜 1302 と接触した。( 図 13 ( A ) )

40

【 0169 】

次に、500 ~ 650 で 4 ~ 24 時間、例えば 570 、14 時間の熱処理を行い、結晶質シリコン膜 1307 を形成した。この結晶化の過程では、ニッケルが接した非晶質シリコン膜の部分が最初に結晶化し、そこから横方向へと結晶化が進行する。こうして形成された結晶質シリコン膜 1307 は棒状または針状の結晶が集合して成り、その各々の結晶は巨視的に見ればある特定の方向性をもって成長しているため、結晶性が揃っているという利点がある。( 図 13 ( B ) )

【 0170 】

50

尚、上記 2 つの技術において使用可能な触媒元素は、ニッケル (Ni) の以外にも、ゲルマニウム (Ge)、鉄 (Fe)、パラジウム (Pd)、スズ (Sn)、鉛 (Pb)、コバルト (Co)、白金 (Pt)、銅 (Cu)、金 (Au)、といった元素を用いても良い。

【0171】

以上のような技術を用いて結晶質半導体膜（結晶質シリコン膜や結晶質シリコンゲルマニウム膜などを含む）を形成し、パターニングを行えば、結晶質 TFT の半導体層を形成することができる。本実施例の技術を用いて、結晶質半導体膜から作製された TFT は、優れた特性が得られるが、そのため高い信頼性を要求されてあいた。しかしながら、本発明の TFT 構造を採用することで、本実施例の技術を最大限に生かした TFT を作製することが可能となった。

10

【0172】

本実施例は、実施例 1 で用いられる半導体層を形成する方法として、非晶質半導体膜から、前記触媒元素を用いて結晶質半導体膜を形成した後で、その触媒元素を結晶質半導体膜から除去する工程を行った例を示す。本実施例ではその方法として、特開平 10-135468 号公報または特開平 10-135469 号公報に記載された技術を用いた。

【0173】

同公報に記載された技術は、非晶質半導体膜の結晶化に用いた触媒元素を結晶化後にリンのゲッタリング作用を用いて除去する技術である。同技術を用いることで、結晶質半導体膜中の触媒元素の濃度を  $1 \times 10^{17} \text{ atm}^3/\text{cm}^3$  以下、好ましくは  $1 \times 10^{16} \text{ atm}^3/\text{cm}^3$  にまで低減することができる。

20

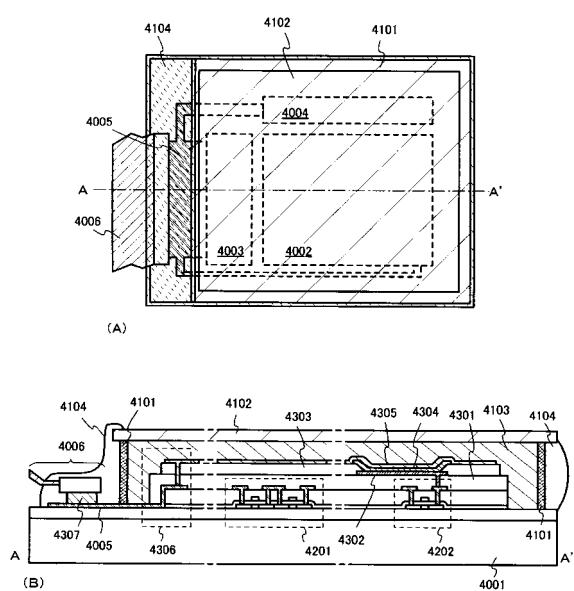

【0174】

本実施例の構成について図 14 を用いて説明する。ここではコーニング社の 1737 基板に代表される無アルカリガラス基板を用いた。図 14 (A) では、実施例 4 で示した結晶化の技術を用いて、下地 1402、結晶質シリコン膜 1403 が形成された状態を示している。そして、結晶質シリコン膜 1403 の表面にマスク用の酸化シリコン膜 1404 が 150 nm の厚さに形成され、パターニングにより開孔部が設けられ、結晶質シリコン膜を露出させた領域を設けてある。そして、リンを添加する工程を実施して、結晶質シリコン膜にリンが添加された領域 1405 が設けられた。

【0175】

この状態で、窒素雰囲気中で 550 ~ 800 、 5 ~ 24 時間、例えば 600 、 12 時間の熱処理を行うと、結晶質シリコン膜にリンが添加された領域 1405 がゲッタリングサイトとして働き、結晶質シリコン膜 1403 に残存していた触媒元素はリンが添加された領域 1405 に偏析させることができた。

30

【0176】

そして、マスク用の酸化シリコン膜 1404 と、リンが添加された領域 1405 とをエッティングして除去することにより、結晶化の工程で使用した触媒元素の濃度を  $1 \times 10^{17} \text{ atm}^3/\text{cm}^3$  以下にまで低減された結晶質シリコン膜を得ることができた。この結晶質シリコン膜はそのまま実施の形態で示した本発明の TFT の半導体層として使用することができた。

40

【0177】

(実施例 8)

本実施例では、本発明を用いて EL（エレクトロルミネンス）表示装置を作製した例について説明する。なお、図 15 (A) は本発明の EL 表示装置の上面図であり、図 15 (B) はその断面図である。

【0178】

図 15 (A)、(B) において、4001 は基板、4002 は画素部、4003 はソース信号線駆動回路、4004 はゲート信号線駆動回路であり、それぞれの駆動回路は配線 4005 を経て FPC（フレキシブルプリントサーキット）4006 に至り、外部機器へと接続される。

【0179】

50

このとき、画素部 4002、ソース信号線駆動回路 4003 及びゲート信号線駆動回路 4004 を囲むようにして第 1 シール材 4101、カバー材 4102、充填材 4103 及び第 2 シール材 4104 が設けられている。

【0180】

図 15 (B) は図 15 (A) を A - A' で切断した断面図に相当し、基板 4001 の上にソース信号線駆動回路 4003 に含まれる駆動回路用 TFT ( 但し、ここでは n チャネル型 TFT と p チャネル型 TFT を図示している。 ) 4201 及び画素部 4002 に含まれる電流制御用 TFT ( EL 素子への電流を制御する TFT ) 4202 が形成されている。

【0181】

本実施例では、駆動回路用 TFT 4201 には公知の方法で作製された p チャネル型 TFT または n チャネル型 TFT が用いられ、電流制御用 TFT 4202 には公知の方法で作製された p チャネル型 TFT が用いられる。また、画素部 4002 には電流制御用 TFT 4202 のゲートに接続された保持容量 ( 図示せず ) が設けられる。

【0182】

駆動回路用 TFT 4201 及び電流制御用 TFT 4202 の上には樹脂材料でなる層間絶縁膜 ( 平坦化膜 ) 4301 が形成され、その上に電流制御用 TFT 4202 のドレインと電気的に接続する画素電極 ( 陽極 ) 4302 が形成される。画素電極 4302 としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したものを用いても良い。

【0183】

そして、画素電極 4302 の上には絶縁膜 4303 が形成され、絶縁膜 4303 は画素電極 4302 の上に開口部が形成されている。この開口部において、画素電極 4302 の上には EL ( エレクトロルミネッセンス ) 層 4304 が形成される。EL 層 4304 は公知の有機 EL 材料または無機 EL 材料を用いることができる。また、有機 EL 材料には低分子系 ( モノマー系 ) 材料と高分子系 ( ポリマー系 ) 材料があるがどちらを用いても良い。

【0184】

EL 層 4304 の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、EL 層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

【0185】

EL 層 4304 の上には遮光性を有する導電膜 ( 代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜 ) からなる陰極 4305 が形成される。また、陰極 4305 と EL 層 4304 の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中で両者を連続成膜するか、EL 層 4304 を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極 4305 を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式 ( クラスターツール方式 ) の成膜装置を用いることで上述のような成膜を可能とする。

【0186】

そして陰極 4305 は 4306 で示される領域において配線 4005 に電気的に接続される。配線 4005 は陰極 4305 に所定の電圧を与えるための配線であり、異方導電性フィルム 4307 を介して FPC 4006 に電気的に接続される。

【0187】

以上のようにして、画素電極 ( 陽極 ) 4302、EL 層 4304 及び陰極 4305 からなる EL 素子が形成される。この EL 素子は、第 1 シール材 4101 及び第 1 シール材 4101 によって基板 4001 に貼り合わされたカバー材 4102 で囲まれ、充填材 4103 と共に封入されている。

【0188】

カバー材 4102 としては、ガラス材、金属材 ( 代表的にはステンレス材 ) 、セラミック

10

20

30

40

50

ス材、プラスチック材（プラスチックフィルムも含む）を用いることができる。プラスチック材としては、F R P（F i b e r g l a s s - R e i n f o r c e d P l a s t i c s）板、P V F（ポリビニルフルオライド）フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをP V Fフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

【0189】

但し、E L素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

【0190】

また、充填材4103としては紫外線硬化樹脂または熱硬化樹脂を用いることができ、P V C（ポリビニルクロライド）、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、P V B（ポリビニルブチラル）またはE V A（エチレンビニルアセテート）を用いることができる。この充填材4103の内部に吸湿性物質（好ましくは酸化バリウム）もしくは酸素を吸着しうる物質を設けておくとE L素子の劣化を抑制できる。

【0191】

また、充填材4103の中にスペーサを含有させてもよい。このとき、スペーサを酸化バリウムで形成すればスペーサ自体に吸湿性をもたせることが可能である。また、スペーサを設けた場合、スペーサからの圧力を緩和するバッファ層として陰極4305上に樹脂膜を設けることも有効である。

【0192】

また、配線4005は異方導電性フィルム4307を介してF P C 4 0 0 6に電気的に接続される。配線4005は画素部4002、ソース信号線駆動回路4003及びゲート信号線駆動回路4004に送られる信号をF P C 4 0 0 6に伝え、F P C 4 0 0 6により外部機器と電気的に接続される。

【0193】

また、本実施例では第1シール材4101の露呈部及びF P C 4 0 0 6の一部を覆うように第2シール材4104を設け、E L素子を徹底的に外気から遮断する構造となっている。こうして図15（B）の断面構造を有するE L表示装置となる。

【0194】

（実施例9）

本発明のE L表示装置は画素内にいくつのT F Tを設けた構造としても良い。例えば、一つ乃至六つまたはそれ以上のT F Tを設けても構わない。本発明はE L表示装置の画素構造に限定されずに実施することが可能である。

【0195】

（実施例10）

【0196】

本実施例では、本発明のE L表示装置の駆動部について、図18を用いて説明する。

【0197】

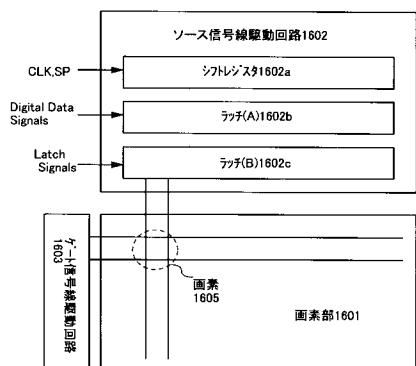

図18に本発明のE L表示装置のブロック図の一例を示す。図18のE L表示装置は、基板上に形成されたT F Tによって画素部1601、画素部の周辺に配置されたソース信号線駆動回路1602、ゲート信号線駆動回路1603を有している。なお、本実施例でE L表示装置はソース信号線駆動回路とゲート信号線駆動回路とを1つづつ有しているが、本発明においてソース信号線駆動回路とゲート信号線駆動回路の数はこれに限定されない。

【0198】

ソース信号線駆動回路1602は基本的にシフトレジスタ1602a、ラッチ（A）1602b、ラッチ（B）1602cを有している。

【0199】

ソース信号線駆動回路1602において、シフトレジスタ1602aにクロック信号（C

10

20

30

40

50

L K ) およびスタートパルス ( S P ) が入力される。シフトレジスタ 1602a は、これらのクロック信号 ( C L K ) およびスタートパルス ( S P ) に基づきタイミング信号を順に発生させ、バッファ等 ( 図示せず ) を通して後段の回路へタイミング信号を順次供給する。

【 0 2 0 0 】

シフトレジスタ 1602a からのタイミング信号は、バッファ等によって緩衝増幅される。タイミング信号が供給される配線には、多くの回路あるいは素子が接続されているために負荷容量 ( 寄生容量 ) が大きい。この負荷容量が大きいために生ずるタイミング信号の立ち上がりまたは立ち下がりの " 鈍り " を防ぐために、このバッファが設けられる。

【 0 2 0 1 】

バッファによって緩衝増幅されたタイミング信号は、ラッチ ( A ) 1602b に供給される。ラッチ ( A ) 1602b は、画像情報を有するデジタルデータ信号 ( digital data signals ) を処理する複数のステージのラッチを有している。ラッチ ( A ) 1602b は、前記タイミング信号が入力されると、基板の外部から供給されるデジタルデータ信号を順次取り込み、保持する。

10

【 0 2 0 2 】

なお、ラッチ ( A ) 1602b にデジタルデータ信号を取り込む際に、ラッチ ( A ) 1602b が有する複数のステージのラッチに、順にデジタルデータ信号を入力しても良い。しかし本発明はこの構成に限定されない。ラッチ ( A ) 1602b が有する複数のステージのラッチをいくつかのグループに分け、各グループごとに並行して同時にデジタルデータ信号を入力する、いわゆる分割駆動を行っても良い。なおこのときのグループの数を分割数と呼ぶ。例えば 4 つのステージごとにラッチをグループに分けた場合、4 分割で分割駆動すると言う。

20

【 0 2 0 3 】

ラッチ ( A ) 1602b の全てのステージのラッチにデジタルデータ信号の書き込みが一通り終了するまでの時間を、ライン期間と呼ぶ。すなわち、ラッチ ( A ) 1602b 中で一番左側のステージのラッチにデジタルデータ信号の書き込みが開始される時点から、一番右側のステージのラッチにデジタルデータ信号の書き込みが終了する時点までの時間間隔がライン期間である。実際には、上記ライン期間に水平帰線期間が加えられた期間をライン期間に含むことがある。

30

【 0 2 0 4 】

1 ライン期間が終了すると、ラッチ ( B ) 1602c にラッチシグナル ( Latch Signal ) が供給される。この瞬間、ラッチ ( A ) 1602b に書き込まれ保持されているデジタルデータ信号は、ラッチ ( B ) 1602c に一斉に送出され、ラッチ ( B ) 1602c の全ステージのラッチに書き込まれ、保持される。

【 0 2 0 5 】

デジタルデータ信号をラッチ ( B ) 1602c に送出し終えたラッチ ( A ) 1602b には、シフトレジスタ 1602a からのタイミング信号に基づき、再びデジタルデータ信号の書き込みが順次行われる。

40

【 0 2 0 6 】

この 2 順目の 1 ライン期間中には、ラッチ ( B ) 1602b に書き込まれ、保持されているデジタルデータ信号がソース信号線に入力される。

【 0 2 0 7 】

ソース信号線に入力されたデジタルデータ信号によって、画素部に画像が表示される。

【 0 2 0 8 】

( 実施例 1 1 )

実施例 1 では、第 1 の形状の導電層を形成する第 1 のエッチング処理を 1 回のエッチング条件で行ったが、ゲート絶縁膜の膜減り及び形状の均一性を向上させるため、複数回のエッチング条件で行ってもよい。本実施例では第 1 のエッチング処理を 2 回のエッチング条件で第 1 の形状の導電層を形成する例を示す。

50

## 【0209】

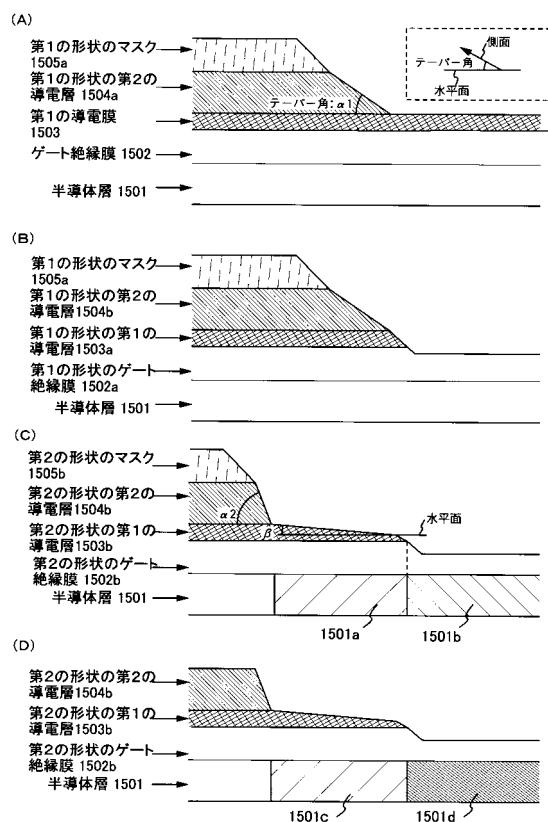

また、本発明は、導電層の両側がテーパーになるように形成され、チャネル形成領域の両側にLDD領域が形成されるが、本実施例は、駆動回路用nチャネル型i TFTにおける導電層近傍の片側の断面拡大図である図19を用い、作製工程に従って説明する。なお、簡略化のため、下地膜と基板は図示していない。

## 【0210】

まず、実施例1に従って、図3(B)と同じ状態を得る。ただし、実施例1では第1の導電膜としてTaを用いたが、本実施例では第1の導電膜として非常に耐熱性の高いTaNを用いた。第1の導電膜は、膜厚20~100nmとし、第2の導電膜は、膜厚100~400nmとすればよく、本実施例では、膜厚30nmのTaNからなる第1の導電膜と膜厚370nmのWからなる第2の導電膜を積層形成した。

10

## 【0211】

次いで、レジストからなる第1の形状のマスク1505aを形成し、ICP法によりエッチングを行って第1の形状の第2の導電層1504aを形成する。ここでは、TaNと選択比が高いエッチングガスとしてCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>からなる混合ガスを用いたため、図19(A)に示した状態を得ることができる。表1に様々なエッチング条件と第2の導電層(W)のエッチングレート、第1の導電層(TaN)のエッチングレート、または第2の導電層(W)のテーパー角との関係を示す。

## 【0212】

## 【表1】

20

W及びTaNのエッチングレート(E.R.)及びWテーパー角度

| 条件 | ICP<br>[W] | バイアス<br>[W] | 圧力<br>[Pa] | CF <sub>4</sub><br>[sccm] | Cl <sub>2</sub><br>[sccm] | O <sub>2</sub><br>[sccm] | W E.R. ①<br>[nm/min] | TaN E.R. ②<br>[nm/min] | W/TaN選択比<br>①÷② | Wテーパー角度<br>[deg.] |

|----|------------|-------------|------------|---------------------------|---------------------------|--------------------------|----------------------|------------------------|-----------------|-------------------|

| 1  | 500        | 20          | 1.0        | 30                        | 30                        | 0                        | 58.97                | 66.43                  | 0.889           | 80                |

| 2  | 500        | 60          | 1.0        | 30                        | 30                        | 0                        | 88.71                | 118.46                 | 0.750           | 25                |

| 3  | 500        | 100         | 1.0        | 30                        | 30                        | 0                        | 111.66               | 168.03                 | 0.667           | 18                |

| 4  | 500        | 20          | 1.0        | 25                        | 25                        | 10                       | 124.62               | 20.67                  | 6.049           | 70                |

| 5  | 500        | 60          | 1.0        | 25                        | 25                        | 10                       | 161.72               | 35.81                  | 4.528           | 35                |

| 6  | 500        | 100         | 1.0        | 25                        | 25                        | 10                       | 176.90               | 56.32                  | 3.008           | 32                |

| 7  | 500        | 150         | 1.0        | 25                        | 25                        | 10                       | 200.39               | 80.32                  | 2.495           | 26                |

| 8  | 500        | 200         | 1.0        | 25                        | 25                        | 10                       | 218.20               | 102.87                 | 2.124           | 22                |

| 9  | 500        | 250         | 1.0        | 25                        | 25                        | 10                       | 232.12               | 124.97                 | 1.860           | 19                |

| 10 | 500        | 20          | 1.0        | 20                        | 20                        | 20                       | -                    | 14.83                  | -               | -                 |

| 11 | 500        | 60          | 1.0        | 20                        | 20                        | 20                       | 193.02               | 14.23                  | 13.695          | 37                |

| 12 | 500        | 100         | 1.0        | 20                        | 20                        | 20                       | 235.27               | 21.81                  | 10.856          | 29                |

| 13 | 500        | 150         | 1.0        | 20                        | 20                        | 20                       | 276.74               | 38.61                  | 7.219           | 26                |

| 14 | 500        | 200         | 1.0        | 20                        | 20                        | 20                       | 290.10               | 45.30                  | 6.422           | 24                |

| 15 | 500        | 250         | 1.0        | 20                        | 20                        | 20                       | 304.34               | 50.25                  | 6.091           | 22                |

(\*) セル内の - はエッチング時にW表面が変質したため測定不可。

30

## 【0213】

40

なお、本明細書においてテーパー角とは、図19(A)の右上図に示したように、水平面と材料層の側面とがなす角を指している。また、本明細書中では便宜上、テーパー角を有している形状を側面をテーパーになっているとし、テーパーを有している部分をテーパー部と呼ぶ。

## 【0214】

また、水平面と第2の導電層(W)の側面とがなす角(テーパー角1)は、第1のエッチング条件を、例えば表1中の条件4~15のいずれかに設定することで19度~70度の範囲で自由に設定することができる。なお、エッチング時間は実施者が適宜設定すればよい。

## 【0215】

50

また、図19(A)において、1501は半導体層、1502はゲート絶縁膜、1503は第1の導電膜である。

【0216】

次いで、マスク1505aをそのままにした状態で、第2のエッチング条件とし、エッチングを行って、第1の形状の第1の導電層1503aを形成する。なお、第2のエッチング条件でのエッチングの際、ゲート絶縁膜1502も若干エッチングされて第1の形状のゲート絶縁膜1502aとなる。ここでは、第2のエッチング条件のエッチングガスとしてCF<sub>4</sub>とCl<sub>2</sub>からなる混合ガスを用いた。第2のエッチング条件として、例えば、表1の条件1~3のいずれか一を用いればよい。このように第1のエッチング処理を2回のエッチング条件で行うことによって、ゲート絶縁膜1502の膜減りを抑えることができる。

10 (図19(B))

【0217】

なお、図19(B)では、第2のエッチング条件のエッチングを行った際、第1の形状の第2の導電層1504aも若干、エッチングされるが微小(約0.15μm程度、即ち線幅全体で0.3μm程度)であるため図19(A)と同一形状として図示した。

【0218】

次いで、マスク1505aをそのままにした状態で、第2のエッチング処理を行い、図19(C)に示した第2の形状の導電層を得る。本実施例では、第2のエッチング処理として、CF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>からなる混合ガスを用いたエッチング条件でエッチングを行った。

20 ここでのエッチング条件は、表1中の条件4~15のいずれか一条件を用い、エッチング時間を適宜設定すればよい。また、各導電層のチャネル長方向の幅もエッチング条件によって自由に設定することができる。この第2のエッチング処理によって、第2の形状のマスク1505b、第2の形状の第1の導電層1503b、第2の形状の第2の導電層1504b、及び第2の形状のゲート絶縁膜1502bが形成される。

【0219】

なお本実施例では、第2の形状の第1の導電層1503bが第1のゲート電極、第2の形状の第2の導電層1504bが第2のゲート電極に相当する。

【0220】

第2の形状の第2の導電層1504bは、テーパー角1よりも大きいテーパー角2を形成し、第2の形状の第1の導電層1503bは非常に小さいテーパー角を形成する。

30

【0221】

次いで、マスク1505bをそのままの状態としたまま、第1のドーピング処理を行う。

(図19(C))ここでは、n型を付与するリンをイオンドーピング法を用い、第2の形状の第2の導電層1504bをマスクとして半導体層1501に添加する。また、ここではマスク1505bをそのままの状態としたまま第1のドーピング処理を行ったが、マスク1505bを除去した後に第1のドーピング処理を行ってもよい。

【0222】

この第1のドーピング処理により不純物領域1501a、1501bが形成される。また、ゲート絶縁膜及び第1の導電層を挟んで第2の導電層と重なる半導体層は、チャネル形成領域となる。なお、図示しないが、チャネル形成領域を挟んで両側に不純物領域1501a、1501bが左右対称に形成される。

40

【0223】

また、ドーピングにおいて、半導体層上に位置する材料層の膜厚が厚くなればなるほどイオンの注入される深さが浅くなる。従って、ゲート絶縁膜を挟んで第1の導電層と重なる不純物領域1501a、即ち第1のLDD領域(Lov領域)は、テーパー角の側面を有するテーパーの部分の影響を受けて、半導体層中に添加される不純物元素の濃度が変化する。膜厚が厚くなればなるほど不純物濃度が低減し、薄くなればなるほど不純物濃度が増加している。

【0224】

また、第2のエッチング処理の際、エッチングの条件によってはゲート絶縁膜にテーパー

50

の部分が形成される場合もある。その場合もテーパーの部分の影響を受けて、半導体層中に添加される不純物元素の濃度が変化する。

【0225】

一方、第1の導電層と重ならない不純物領域1501b、第2のLDD領域(Loff領域)において、ゲート絶縁膜の膜厚は、ほぼ一定であるので不純物濃度もほぼ一定となる。

【0226】

次いで、図示しないが、スイッチング用TFTの一部を覆うレジストマスクを形成する。スイッチング用TFTにおいては、ここでレジストマスクのサイズを制御することでLoff領域の長さが決定する。

【0227】

次いで、第2のドーピング処理を行う。半導体に一導電型を付与する不純物元素、ここでは、n型を付与するリンをイオンドーピング法を用い、第2の形状の第1の導電層1503b及び第2の形状の第2の導電層1504bをマスクとして半導体層1501に添加する。第2のドーピング処理は、第1のドーピング処理よりも高濃度のドーピングを行い、不純物領域1501c、1501dを形成する。

10

【0228】

不純物領域1501d、即ちソース領域またはドレイン領域は、第1のドーピング処理により添加された不純物濃度に加え、さらに第2のドーピング処理により高濃度となる。

【0229】

また、第1の導電層と重なっているため不純物領域1501cにはドーピングされず、不純物領域1501aと同一の濃度分布を有する。従って、不純物領域1501cも第1のLDD領域である。ただし、ドーピング条件によっては、さらに高濃度となる。その場合には、第2のドーピング処理においても第1のドーピング処理と同様にテーパー角の側面を有するテーパーの部分の影響を受けて、半導体層中に添加される。

20

【0230】

一方、スイッチング用TFTにおいては、レジストマスクで覆われなかった領域のみにドーピングされてソース領域またはドレイン領域が形成される。また、レジストマスクで覆われ、且つ導電層と重ならない第2のLDD領域1501bはそのままの状態である。

【0231】

次いで、スイッチング用TFTのレジストマスクを除去する。

30

【0232】

以降の工程は、実施例1の図4(C)以降の工程に従って図6(B)に示すELパネルを作製すればよい。

【0233】

上記方法により駆動回路用nチャネルTFTと、スイッチング用TFTとが作り分けられる。

【0234】

駆動回路用nチャネルTFTは、ゲート絶縁膜を間に挟んで第2の導電層と重なるチャネル形成領域と、該チャネル形成領域の両側に第1のLDD領域と、該第1のLDD領域に接するソース領域またはドレイン領域とを備え、スイッチング用TFTは、ゲート絶縁膜を間に挟んで第2の導電層と重なるチャネル形成領域と、該チャネル形成領域の両側に第1のLDD領域と、該第1のLDD領域に接する第2のLDD領域と、該第2のLDD領域に接するソース領域またはドレイン領域を備える。

40

【0235】

また、ゲート絶縁膜を間に挟んで第1の導電層と重なる第1のLDD領域は、チャネル形成領域からの距離が増大するとともに不純物濃度が増加する濃度分布を備えている。なお、第1のLDD領域における不純物濃度は、少なくとも $1 \times 10^{17} \sim 1 \times 10^{18} / \text{cm}^3$ の範囲で濃度勾配を有する領域を含んでいる。このようにLDD領域において連続的な濃度勾配を有していれば、オフ電流の低減に効果がある。また、第1のLDD領域におけるチャネル長方向の長さが長ければ長いほど信頼性が向上する。

50

## 【0236】

また、電流制御用 TFT にボロンをドーピングする工程（図 4（C）において、実際には、149～152に含まれるボロンは、第1のドーピング処理と同様に半導体層上に位置するテーパーとなっている第1の導電層の膜厚による影響を受け、不純物領域中に添加される不純物元素の濃度は変化している。膜厚が厚くなればなるほど不純物濃度が低減し、薄くなればなるほど不純物濃度が増加している。

## 【0237】

また、本実施例は、実施例1～10のいずれか一と自由に組み合わせることができる。

## 【0238】

また、本実施例のエッティングガス用ガス（ $\text{CF}_4$ と $\text{Cl}_2$ の混合ガス）に代えて $\text{SF}_6$ と $\text{Cl}_2$ の混合ガスを用いた場合、あるいは $\text{CF}_4$ と $\text{Cl}_2$ と $\text{O}_2$ の混合ガスに代えて $\text{SF}_6$ と $\text{Cl}_2$ と $\text{O}_2$ の混合ガスを用いた場合、ゲート絶縁膜1502との選択比が非常に高いのでさらに膜減りを抑えることができる。10

## 【0239】

## （実施例12）

本発明において、三重項励起子からの熒光を発光に利用できるEL材料を用いることで、外部発光量子効率を飛躍的に向上させることができる。これにより、EL素子の低消費電力化、長寿命化、および軽量化が可能になる。

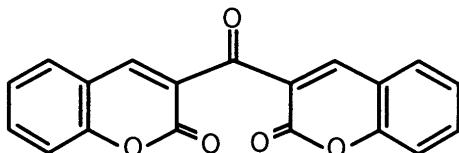

## 【0240】

ここで、三重項励起子を利用し、外部発光量子効率を向上させた報告を示す。（T.Tsutsui, C.Adachi, S.Saito, Photochemical Processes in Organized Molecular Systems, ed. K.Honda, (Elsevier Sci.Pub., Tokyo,1991) p.437.）20

## 【0241】

上記の論文により報告されたEL材料（クマリン色素）の分子式を以下に示す。

## 【0242】

## 【化1】

30

## 【0243】

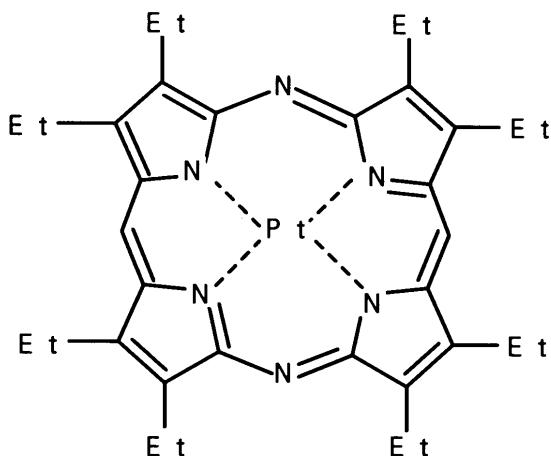

（M.A.Baldo, D.F.O'Brien, Y.You, A.Shoustikov, S.Sibley, M.E.Thompson, S.R.Forrest, Nature 395 (1998) p.151.）

## 【0244】

上記の論文により報告されたEL材料（Pt錯体）の分子式を以下に示す。

## 【0245】

## 【化2】

10

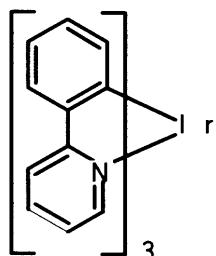

## 【0246】

(M.A.Baldo, S.Lamansky, P.E.Burrows, M.E.Thompson, S.R.Forrest, Appl.Phys.Lett., 75 (1999) p.4.) (T.Tsutsui, M.-J.Yang, M.Yahiro, K.Nakamura, T.Watanabe, T.tsutsui, Y.Fukuda, T.Wakimoto, S.Mayaguchi, Jpn.Appl.Phys., 38 (12B) (1999) L1502.)

## 【0247】

上記の論文により報告された E L 材料 (Ir錯体) の分子式を以下に示す。

20

## 【0248】

## 【化3】

30

## 【0249】

以上のように三重項励起子からの発光を利用できれば原理的には一重項励起子からの発光を用いる場合より 3 ~ 4 倍の高い外部発光量子効率の実現が可能となる。

## 【0250】

なお、本実施例の構成は、実施例 1 ~ 実施例 11 のいずれの構成とも自由に組み合わせて実施することが可能である。

## 【0251】

## (実施例 13)

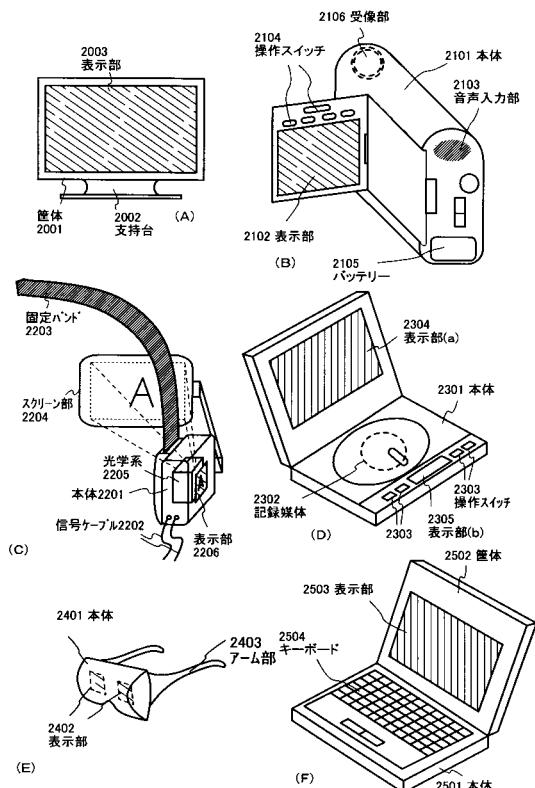

本発明を実施して形成された E L 表示装置は、自発光型であるため液晶表示装置に比べて明るい場所での視認性に優れ、しかも視野角が広い。従って、様々な電子機器の表示部に用いることができる。例えば、TV放送等を大画面で鑑賞するには対角 30 インチ以上 (典型的には 40 インチ以上) の E L 表示装置 (E L パネルを筐体に組み込んだ表示装置) の表示部として本発明の E L 表示装置を用いるとよい。

40

## 【0252】

なお、E L 表示装置には、パソコン用ディスプレイ、TV放送受信用ディスプレイ、広告表示用ディスプレイ等の全ての情報表示用ディスプレイが含まれる。また、その他にも様々な電子機器の表示部として本発明の E L 表示装置を用いることができる。

## 【0253】

その様な本発明の電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディス

50

プレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パソコン、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはデジタルビデオディスク(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。特に、斜め方向から見ることの多い携帯情報端末は視野角の広さが重要視されるため、EL表示装置を用いることが望ましい。それら電子機器の具体例を図16、図17に示す。

【0254】

図16(A)はEL画像表示装置であり、筐体2001、支持台2002、表示部2003等を含む。本発明のEL表示装置は表示部2003に用いることができる。EL表示装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることが可能である。10

【0255】

図16(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。本発明のEL表示装置は表示部2102に用いることができる。

【0256】

図16(C)は頭部取り付け型の表示装置の一部(右片側)であり、本体2201、信号ケーブル2202、頭部固定バンド2203、スクリーン部2204、光学系2205、表示部2206等を含む。本発明のEL表示装置は表示部2206に用いることができる。20

【0257】

図16(D)は記録媒体を備えた画像再生装置(具体的にはDVD再生装置)であり、本体2301、記録媒体(DVD等)2302、操作スイッチ2303、表示部(a)2304、表示部(b)2305等を含む。表示部(a)2304は主として画像情報を表示し、表示部(b)2305は主として文字情報を表示するが、本発明のEL表示装置はこれら表示部(a)、(b)2304、2305に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

【0258】

図16(E)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2401、表示部2402、アーム部2403を含む。本発明のEL表示装置は表示部2402に用いることができる。30

【0259】

図16(F)はパソコンコンピュータであり、本体2501、筐体2502、表示部2503、キーボード2504等を含む。本発明のEL表示装置は表示部2503に用いることができる。

【0260】

なお、将来的にEL材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。

【0261】

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増してきている。EL材料の応答速度は非常に高いため、EL表示装置は動画表示に好ましい。40

【0262】

また、EL表示装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生装置のような文字情報を主とする表示部にEL表示装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

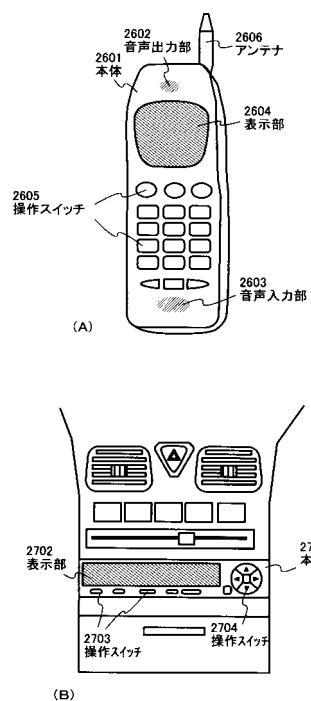

【0263】

10

20

30

40

50

ここで図17(A)は携帯電話であり、本体2601、音声出力部2602、音声入力部2603、表示部2604、操作スイッチ2605、アンテナ2606を含む。本発明のEL表示装置は表示部2604に用いることができる。なお、表示部2604は黒色の背景に白色の文字を表示することで携帯電話の消費電力を抑えることができる。

【0264】

また、図17(B)は音響再生装置、具体的にはカーオーディオであり、本体2701、表示部2702、操作スイッチ2703、2704を含む。本発明のEL表示装置は表示部2702に用いることができる。また、本実施例では車載用オーディオを示すが、携帯型や家庭用の音響再生装置に用いても良い。なお、表示部2702は黒色の背景に白色の文字を表示することで消費電力を抑えられる。これは携帯型の音響再生装置において特に有効である。10

【0265】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例の電子機器は実施例1~12に示したいずれの構成のEL表示装置を用いても良い。

【0266】

(実施例14)

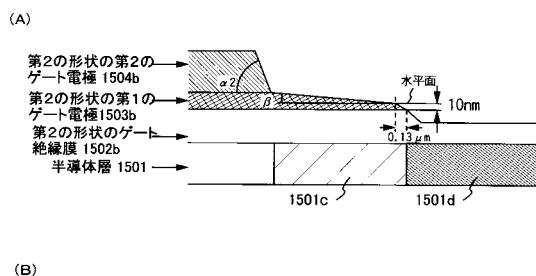

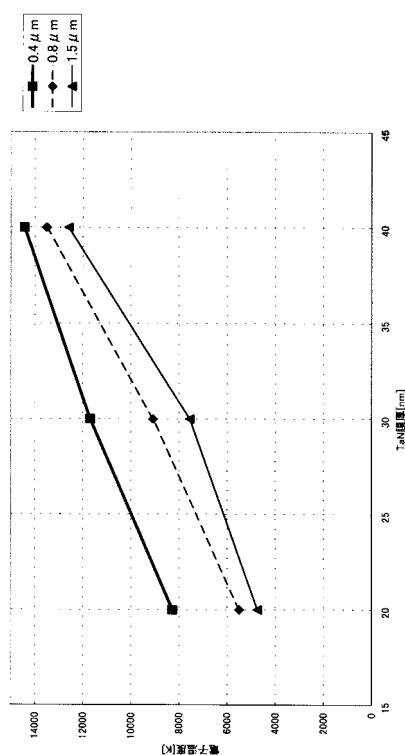

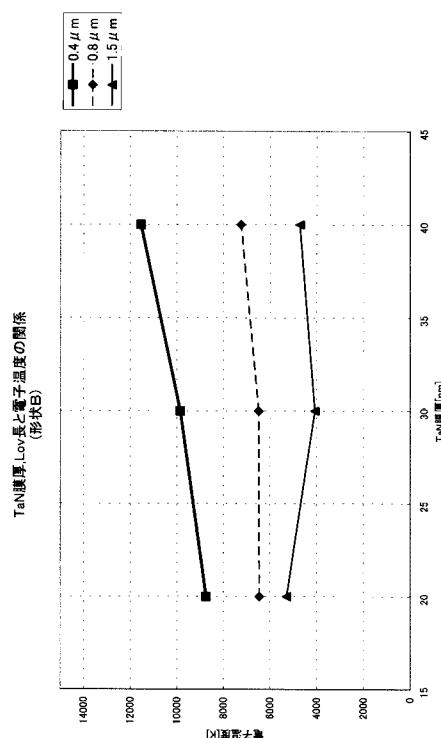

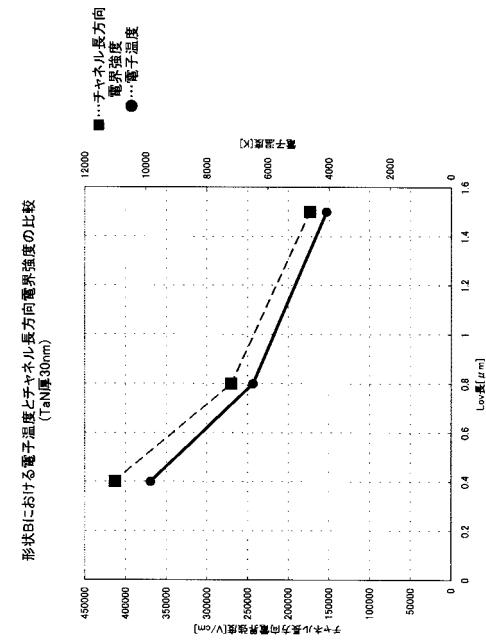

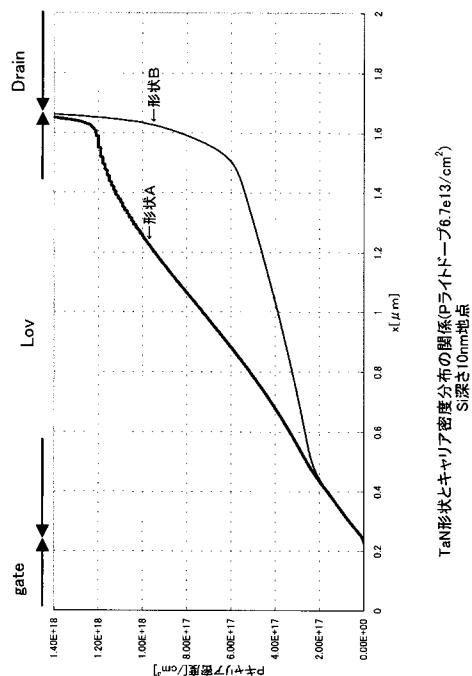

実施例11に記述したようにエッティング条件によって第2の形状の第1のゲート電極(TaN)は様々な形状となる。本実施例では、図20(A)の形状Aと図20(B)の形状Bとでシミュレーションを行い、比較を行った。20

【0267】

図20(A)に実施例11に示した形状Aを示した。図20(A)は、図19(D)と同一であるので同じ符号を用いた。図21は、図20(A)において第1のゲート電極(TaN)の膜厚を15nm~40nmとし、Lov長(Lov領域のチャネル長方向の長さ)を0.4μm、0.8μm、1.5μmとした場合における電子温度との関係を示すグラフである。なお、チャネル長方向における不純物元素の濃度分布(半導体層表面から深さ10nmの濃度分布)は、図24に示したもの用いてシミュレーションを行った。ただし、第1のゲート電極側面の一部でテーパー角が変化しており、その変化している箇所は、断面から見てゲート絶縁膜から10nmの膜厚の位置であり、かつ、上面からみて第1のゲート電極の端部から0.13μm離れた位置としてシミュレーションを行った。30

【0268】

また、図20(B)に本実施例の形状Bを示す。図20(B)は、図20(A)とは異なっており、側面の一部でテーパー角が変化している箇所はなく、テーパー角が形成されている。

【0269】

図20(B)に示した第1のゲート電極1700においても同様にシミュレーションを行い、第1のゲート電極(TaN)の膜厚を15nm~40nmとし、Lov長を0.4μm、0.8μm、1.5μmとした場合における電子温度との関係を図22に示す。なお、チャネル長方向における不純物元素の濃度分布は、図24に示したもの用いてシミュレーションを行った。40

【0270】

また、図20(B)に示した第1のゲート電極1700、即ちTaN膜厚が30nmの時、図23にチャネル長方向の電界強度とLov長との関係と、Lov長と電子温度との関係を示した。図23において、電界強度と電子温度の示す傾向が、近似している。従って、電子温度が低ければ、それだけTFTの劣化の程度が小さくなる傾向を示すと言える。

【0271】

図22と図21を比較した場合、図22に示した図20(B)の形状のほうが低い電子温度を示している。即ち、TFTの劣化の点から見れば、図20(B)の形状とすると、電子温度を低下させることができるため望ましい。

【0272】

10

20

30

40

50

また、 $1.5 \mu m$  の  $L_{ov}$  長である時に電子温度が低いことから、 $L_{ov}$  長は長いほうがよいことが読み取れる。

【0273】

本実施例は実施例 1 ~ 13 と自由に組み合わせて実施することが可能である。

【0274】

【発明の効果】

上述したように本発明では、ゲート電極のチャネル長方向の長さ（以下単にゲート電極の幅と呼ぶ）が異なっているため、ゲート電極をマスクとしてイオン注入を行うことにより、ゲート電極の厚さが異なることによるイオンの侵入深さの違いを利用して、第1のゲート電極の下に位置する半導体層中のイオン濃度を、第1のゲート電極の下に位置しない半導体層中のイオン濃度より低くすることが可能である。

10

【0275】

またマスクを用いて  $L_{off}$  領域を形成するために、エッチングで制御しなくてはならないのは第1のゲート電極と第2のゲート電極の幅のみであり、 $L_{off}$  領域と  $L_{ov}$  領域の位置の制御が従来に比べて容易になった。よって、 $L_{ov}$  領域と  $L_{off}$  領域の微妙な位置あわせが容易になり、所望の特性を有する TFT を作製することも容易になった。

【0276】

また従来ゲート信号線またはソース信号線と同じ膜から形成されていた電源供給線を第2の層間絶縁膜と第3の層間絶縁膜の間に設けている。そのために電源供給線をゲート信号線と重ねて設けることができるので、開口率を上げることができる。

20

【図面の簡単な説明】

【図1】 本発明のEL表示装置の作製行程を示す図。

【図2】 TFT ゲート電極の拡大図。

【図3】 本発明のEL表示装置の作製行程を示す図。

【図4】 本発明のEL表示装置の作製行程を示す図。

【図5】 本発明のEL表示装置の作製行程を示す図。

【図6】 本発明のEL表示装置の作製行程を示す図。

【図7】 本発明のEL表示装置の画素の上面図及び回路図。

【図8】 本発明のEL表示装置の断面図。

【図9】 本発明のEL表示装置の断面図。

30

【図10】 本発明のEL表示装置の断面図。

【図11】 本発明のEL表示装置の画素の上面図及び断面図。

【図12】 半導体層の結晶化方法を示す図。

【図13】 半導体層の結晶化方法を示す図。

【図14】 半導体層の結晶化方法を示す図。

【図15】 本発明のEL表示装置の外観図及び断面図。

【図16】 本発明のEL表示装置を用いた電子機器。

【図17】 本発明のEL表示装置を用いた電子機器。

【図18】 本発明のEL表示装置のブロック図。

【図19】 TFT ゲート電極の拡大図。

40

【図20】 TFT ゲート電極の拡大図。

【図21】 形状AにおけるTaN膜厚と電子温度の関係を示すグラフ。

【図22】 形状BにおけるTaN厚と電子温度の関係を示すグラフ。

【図23】 形状Bにおける電子温度と横方向電界強度との比較。

【図24】 形状A及び形状Bにおけるリンの濃度分布を示す図。

【符号の説明】

501 ソース信号線

502 ゲート信号線

503 電源供給線

504 スイッチング用TFT

50

- 5 0 5 スイッチング用 TFT の半導体層

5 0 6 電流制御用 TFT のゲート電極

5 0 7 電流制御用 TFT

5 0 8 電流制御用 TFT の半導体層

5 0 9 画素電極

5 1 0 ドレイン配線

5 1 1 容量配線

5 1 2 保持容量

【図 1】

【図 2】

【 3 】

【 图 4 】

【 四 5 】

【図6】

【 四 7 】

【 図 8 】

【図9】

【 図 1 0 】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

---

フロントページの続き

| (51)Int.Cl. |                 | F I     |         |

|-------------|-----------------|---------|---------|

| H 0 5 B     | 33/08 (2006.01) | H 0 4 N | 5/70 Z  |

| H 0 1 L     | 51/50 (2006.01) | H 0 5 B | 33/08   |

|             |                 | H 0 5 B | 33/14 A |

(72)発明者 荒尾 達也

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 棚田 一也

(56)参考文献 特開平08-274336 (JP, A)

特開2000-036598 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

G09F 9/30

H01L 27/32

H01L 29/786

H01L 51/50

H04N 5/70

H05B 33/08