(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 699 09 467 T2 2004.02.26

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 078 317 B1

(21) Deutsches Aktenzeichen: 699 09 467.4

(86) PCT-Aktenzeichen: PCT/US99/09988

(96) Europäisches Aktenzeichen: 99 922 840.6

(87) PCT-Veröffentlichungs-Nr.: WO 99/059065

(86) PCT-Anmeldetag: 07.05.1999

(87) Veröffentlichungstag

der PCT-Anmeldung: 18.11.1999

(97) Erstveröffentlichung durch das EPA: 28.02.2001

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 09.07.2003

(47) Veröffentlichungstag im Patentblatt: 26.02.2004

(51) Int Cl.<sup>7</sup>: G06F 11/20

G06F 13/14

(30) Unionspriorität:

79091 14.05.1998 US

(84) Benannte Vertragsstaaten:

DE, DK, FI, FR, GB, IT, NL, SE

(73) Patentinhaber:

Motorola, Inc., Schaumburg, Ill., US

(72) Erfinder:

McKAY, Brent, Chandler, US; ROSENKRANTZ, Bruce, Tempe, US; LANUS, Mark, Tempe, US

(74) Vertreter:

SCHUMACHER & WILLSAU,

Patentanwaltssozietät, 80335 München

(54) Bezeichnung: UMSCHALTSVERFAHREN ZWISCHEN MEHREREN SYSTEMPROZESSOREN

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Gebiet der Erfindung**

[0001] Die vorliegende Erfindung betrifft Busarchitekturen im Allgemeinen.

**Hintergrund der Erfindung**

[0002] Ein herkömmliches Rechnersystem verwendet zur Datenübertragung zwischen Komponenten eines Systems einen Bus. Eine populäre Busarchitektur ist die PCI-Busarchitektur (PCI = Peripheral Component Interconnect = Peripheriekomponentenverbindung), die zahlreiche wünschenswerte, in der Technik wohlbekannte Eigenschaften aufweist. Die PCI-Busarchitektur wird beispielsweise in PCI Local Bus Specification von der PCI Special Interest Group, 5300 N. E. Elam Young Parkway, Hillsborough, Oregon, beschrieben. Die erst kürzlich entwickelte CompactPCI® Busarchitektur ist eine Implementierung von für industrielle und/oder eingebetteten Anwendungen konstruierter PCI-Technologie. Die Compact-PCI-Busarchitektur wird in CompactPCI Specification von PCI Industrial Computer Manufacturers Group (PCIMG®), 301 Edgewater Place Suite 220, Wakefield, Massachusetts, beschrieben. CompactPCI und PCIMG sind eingetragene Marken der PCI Industrial Computer Manufacturers Group.

[0003] Es wäre vorteilhaft, die Vorteile der Compact-PCI-Busarchitektur in einem hochverfügbaren oder fehlertoleranten System bereitzustellen, das zur Ausführung kritischer Anwendungen geeignet ist, wie etwa Telefonvermittlungssysteme oder Datenbanksysteme, ohne die Anwendungen durch das Risiko eines Systemausfalls zu gefährden. Ein Ausfall des Systemprozessors kann einen solchen Systemausfall zur Folge haben. Dementsprechend wäre es wünschenswert, in einer CompactPCI-Busarchitektur über ein hochverfügbares und fehlertolerantes System zu verfügen, das einen Systemprozessorausfall ohne Unterbrechung des Betriebs des Systems verkraften kann.

[0004] Die US-A-0 500 945 offenbart ein Verfahren zur Steuerung eines Multiprozessorsystems durch Verwenden eines Systembus des Multiprozessorsystems steuernden Busarbiters, wobei das Verfahren das Ermitteln einer Abnormalität in dem Multiprozessorsystem und das Ergreifen von Maßnahmen zum Reinitialisieren des Systems zum Neustarten des Busarbiters im Falle einer ermittelten Abnormalität umfasst. Der Systembus wird gestoppt und neu gestartet, um das Umschalten zu vollbringen. Das Umschalten zwischen Multiprozessoren in einem kontinuierlichen Betrieb wird dort nicht offenbart.

**Zusammenfassung der Erfindung**

[0005] Die vorliegende Erfindung stellt ein Verfahren zum Umschalten zwischen mehreren Systempro-

zessoren auf einem Bus bereit, wie in Anspruch 1 beansprucht.

**Kurze Beschreibung der Zeichnungen**

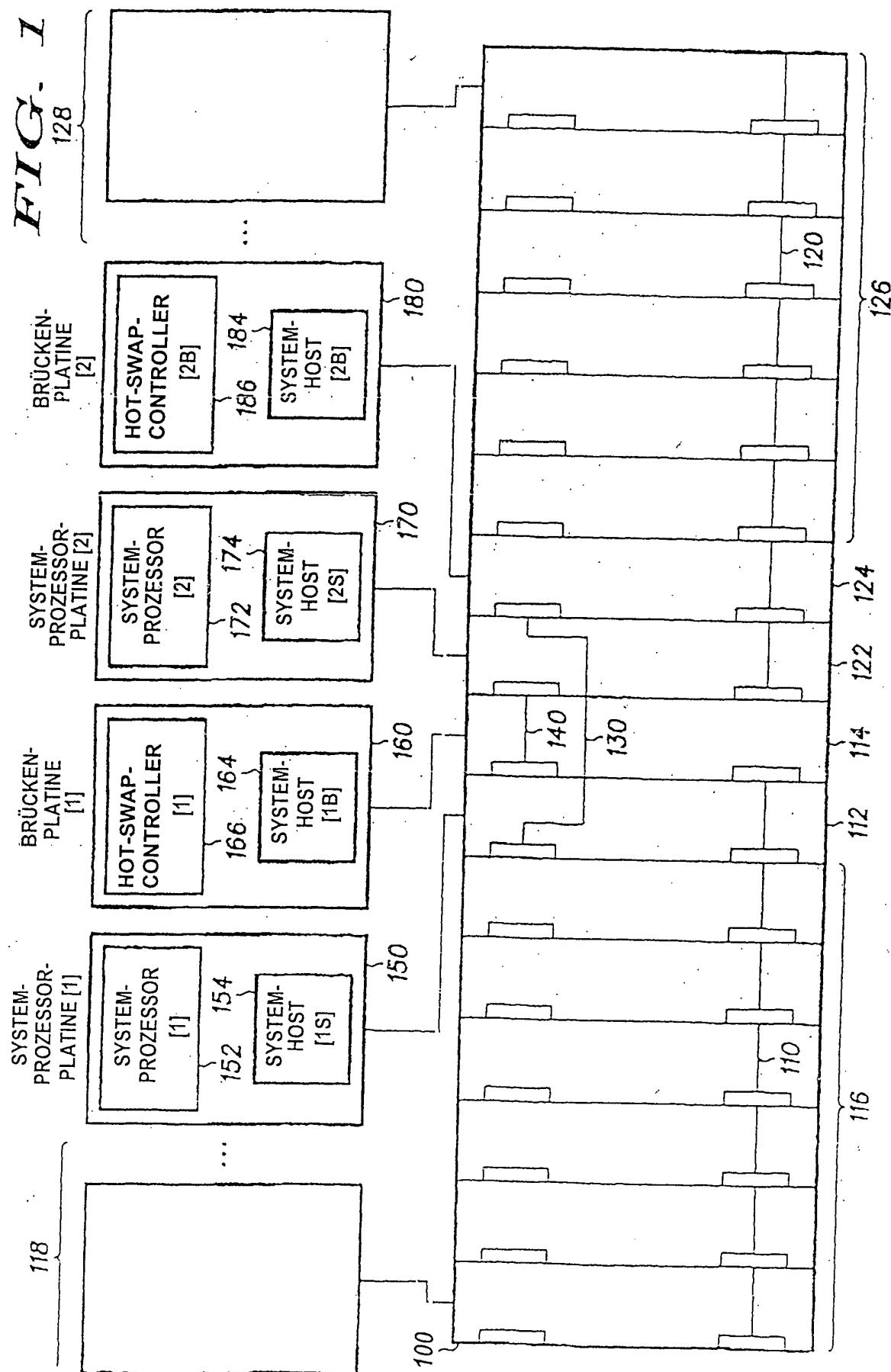

[0006] **Fig. 1** ist ein Schaltdiagramm der Multikonfigurations-Rückwandplatine der bevorzugten Ausführungsform der Erfindung;

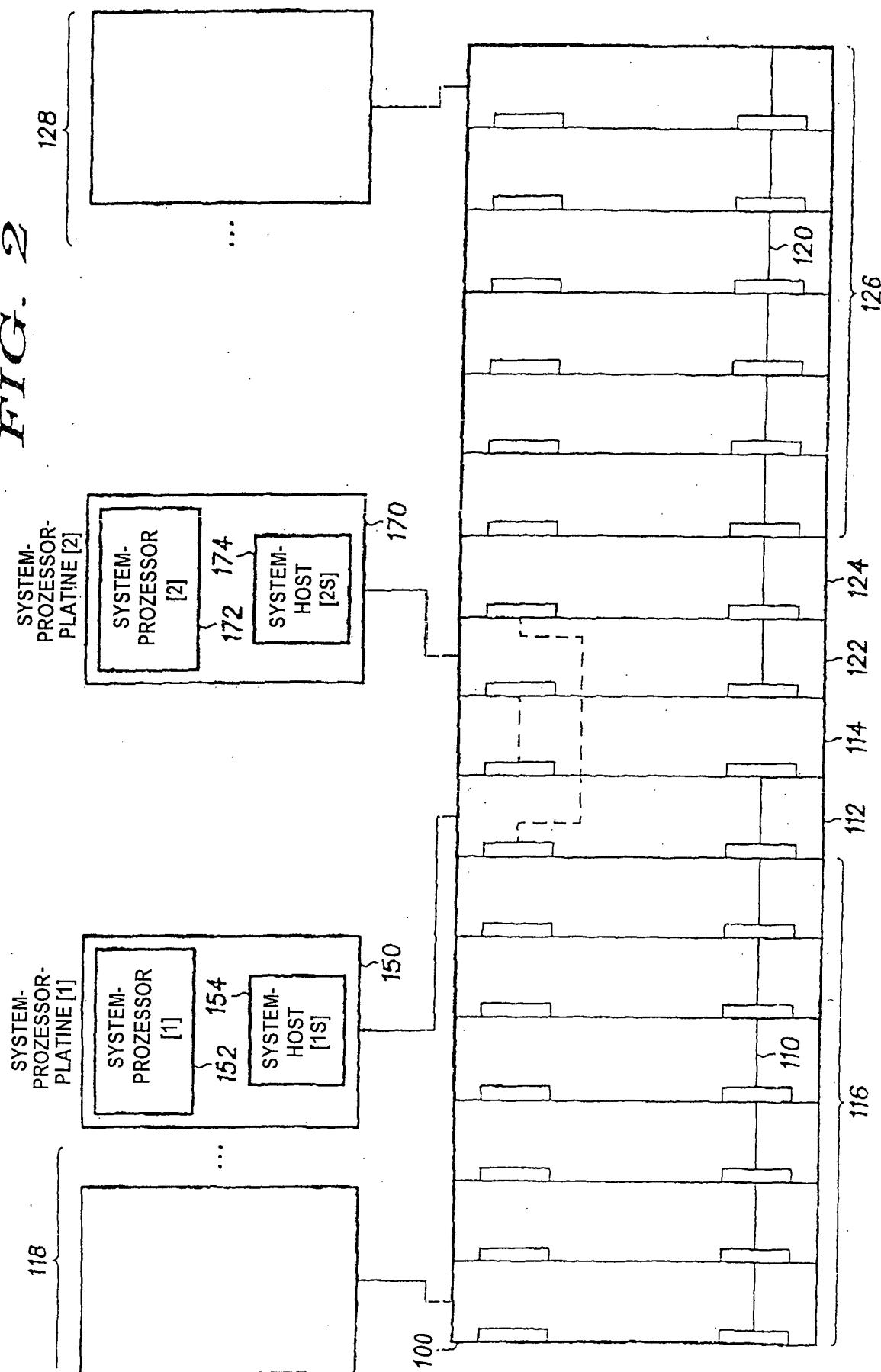

[0007] **Fig. 2** ist ein Schaltdiagramm einer Dualkonfiguration der Multikonfigurations-Rückwandplatine;

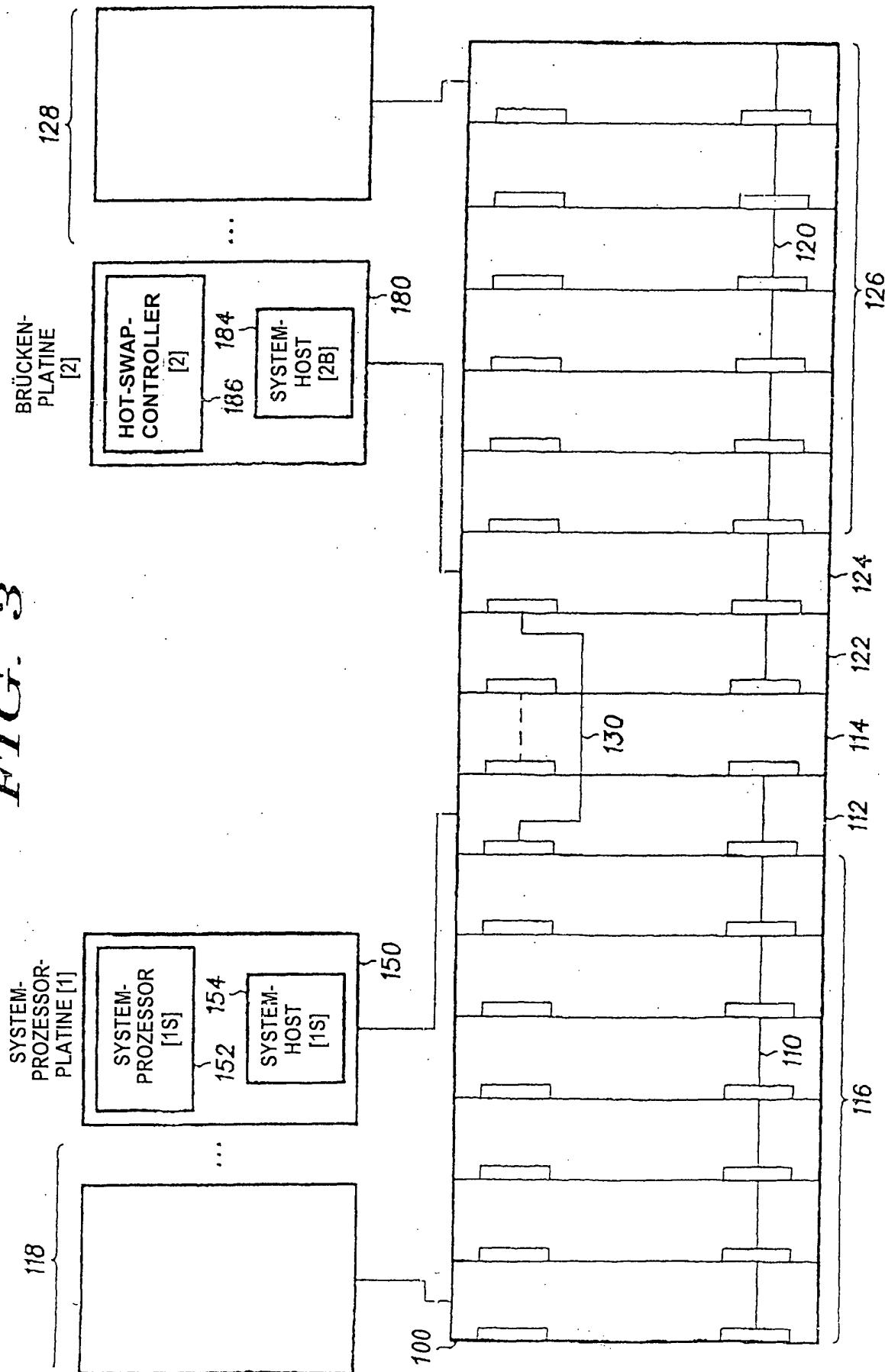

[0008] **Fig. 3** ist ein Schaltdiagramm einer erweiterten Konfiguration der Multikonfigurations-Rückwandplatine;

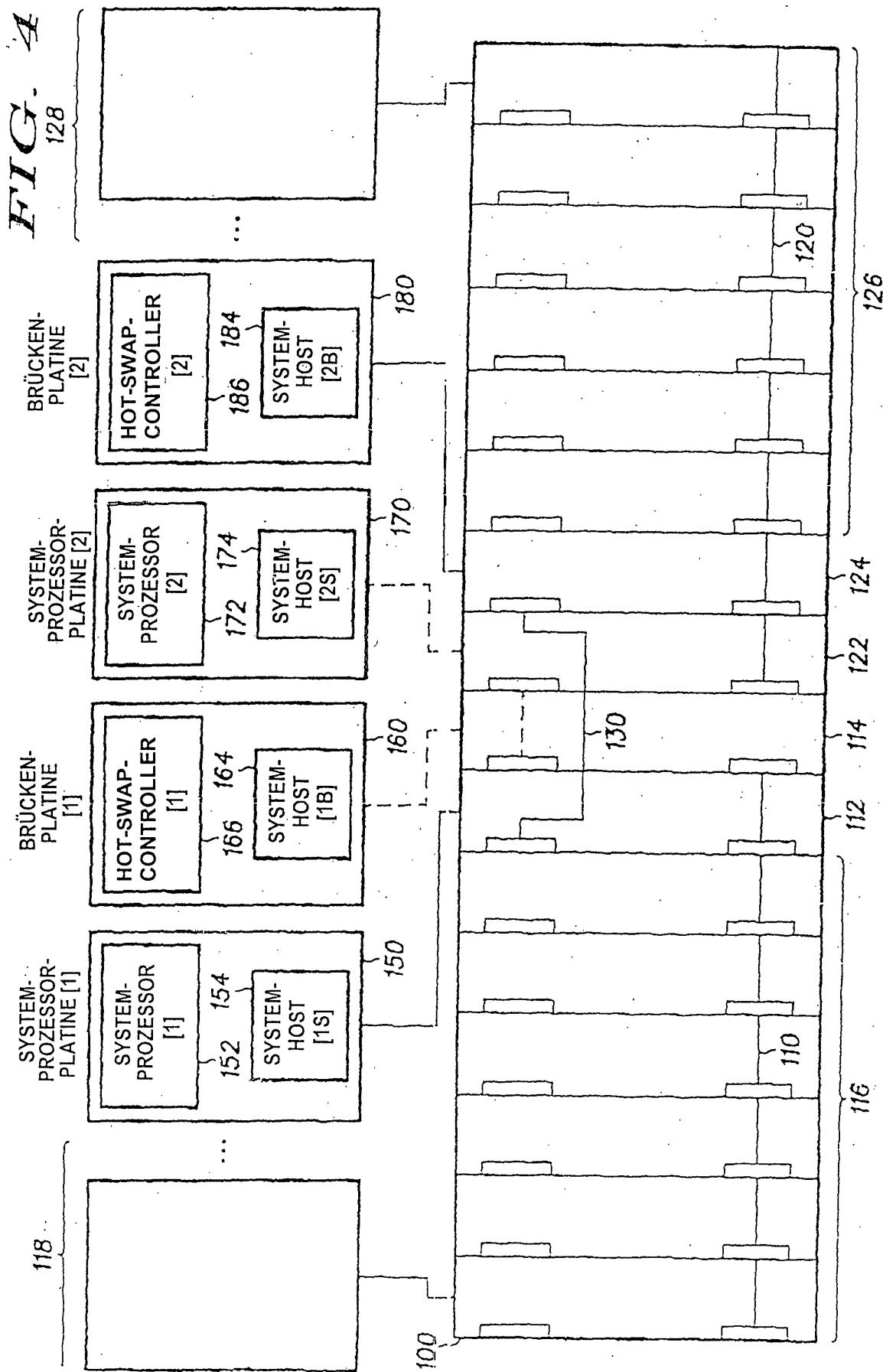

[0009] **Fig. 4** ist ein Schaltdiagramm einer Aktiv/Standby-Konfiguration der Multikonfigurations-Rückwandplatine in einem Aktiv/Standby-Modus;

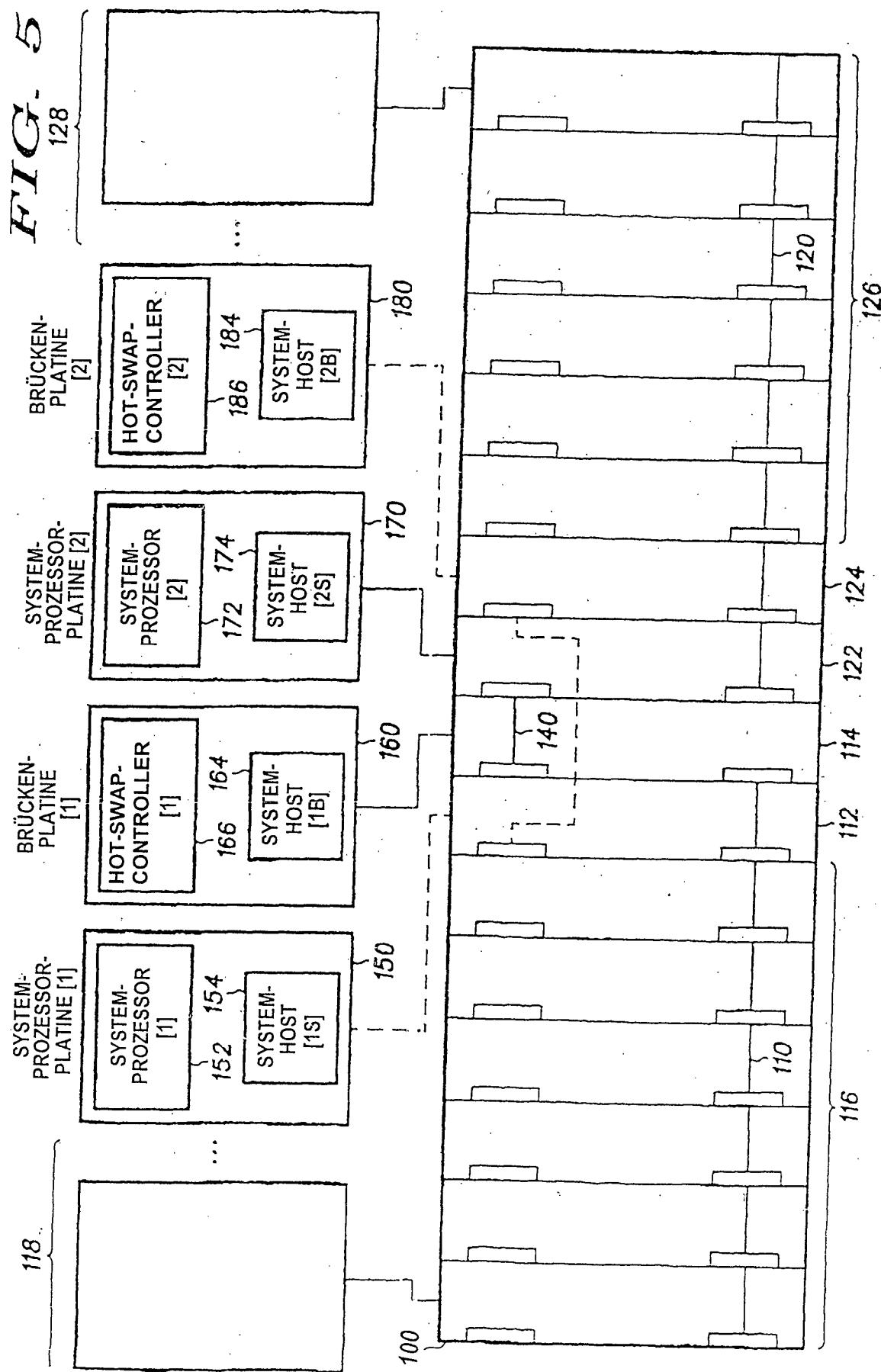

[0010] **Fig. 5** ist ein Schaltdiagramm einer Aktiv/Standby-Konfiguration der Multikonfigurations-Rückwandplatine in einem Aktiv/Aktiv-Modus;

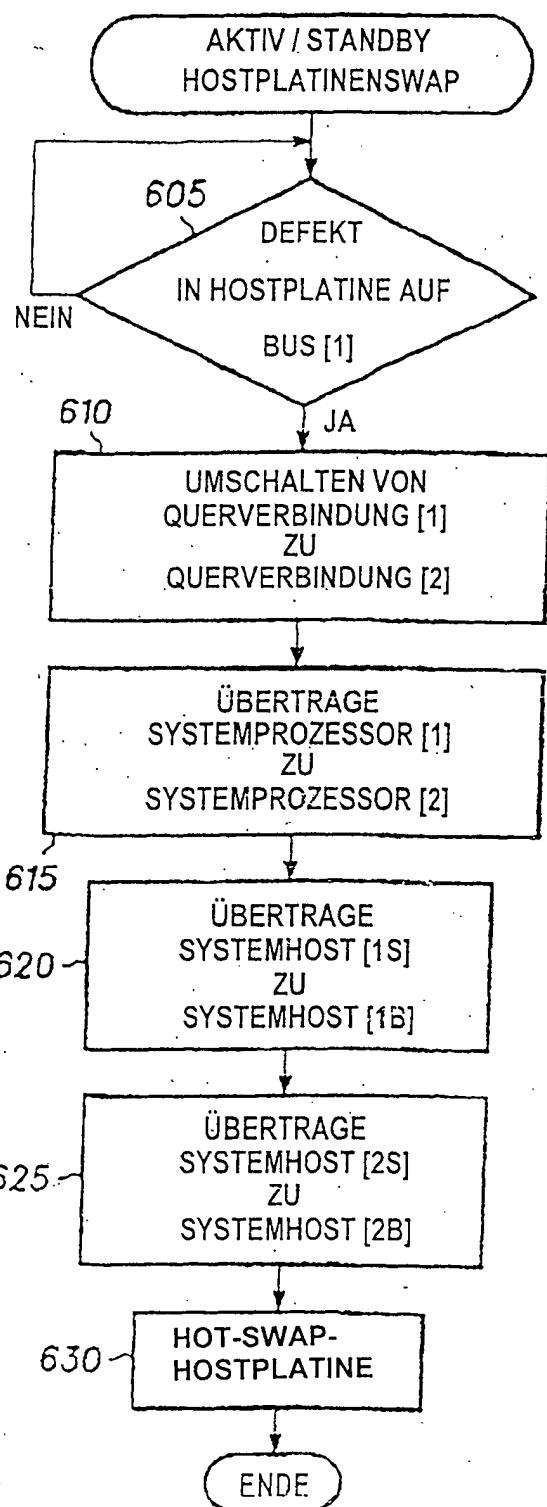

[0011] **Fig. 6** ist ein Flussdiagramm des Prozesses des Swappings der Hostplatine in eine Aktiv/Standby-Konfiguration;

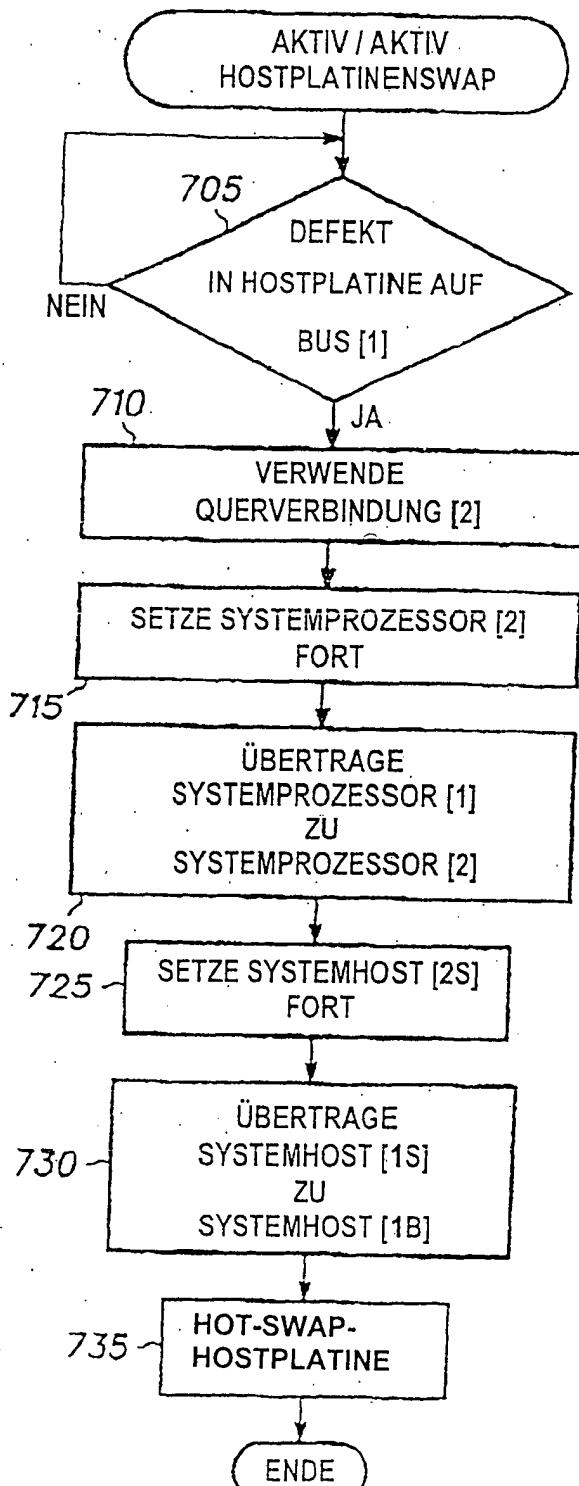

[0012] **Fig. 7** ist ein Flussdiagramm des Prozesses des Swappings der Hostplatine in eine Aktiv/Aktiv-Konfiguration;

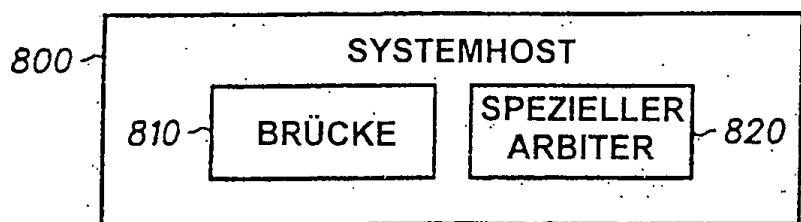

[0013] **Fig. 8** ist ein Schaltdiagramm des Systemhosts;

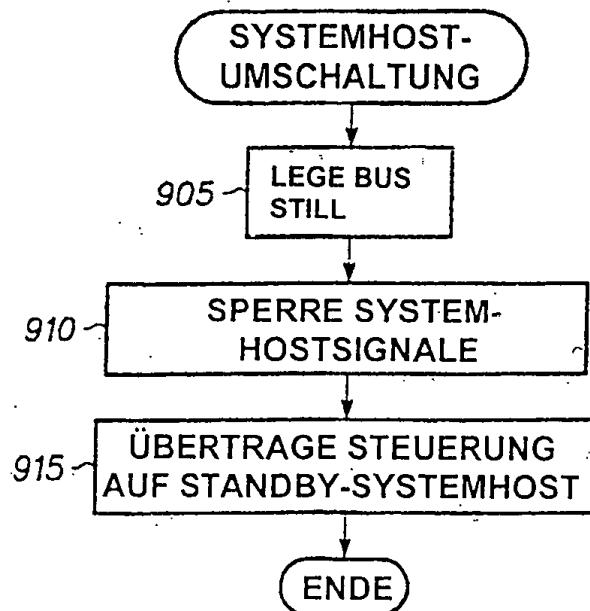

[0014] **Fig. 9** ist ein Flussdiagramm des Prozesses des Umschaltens des Systemhosts; und

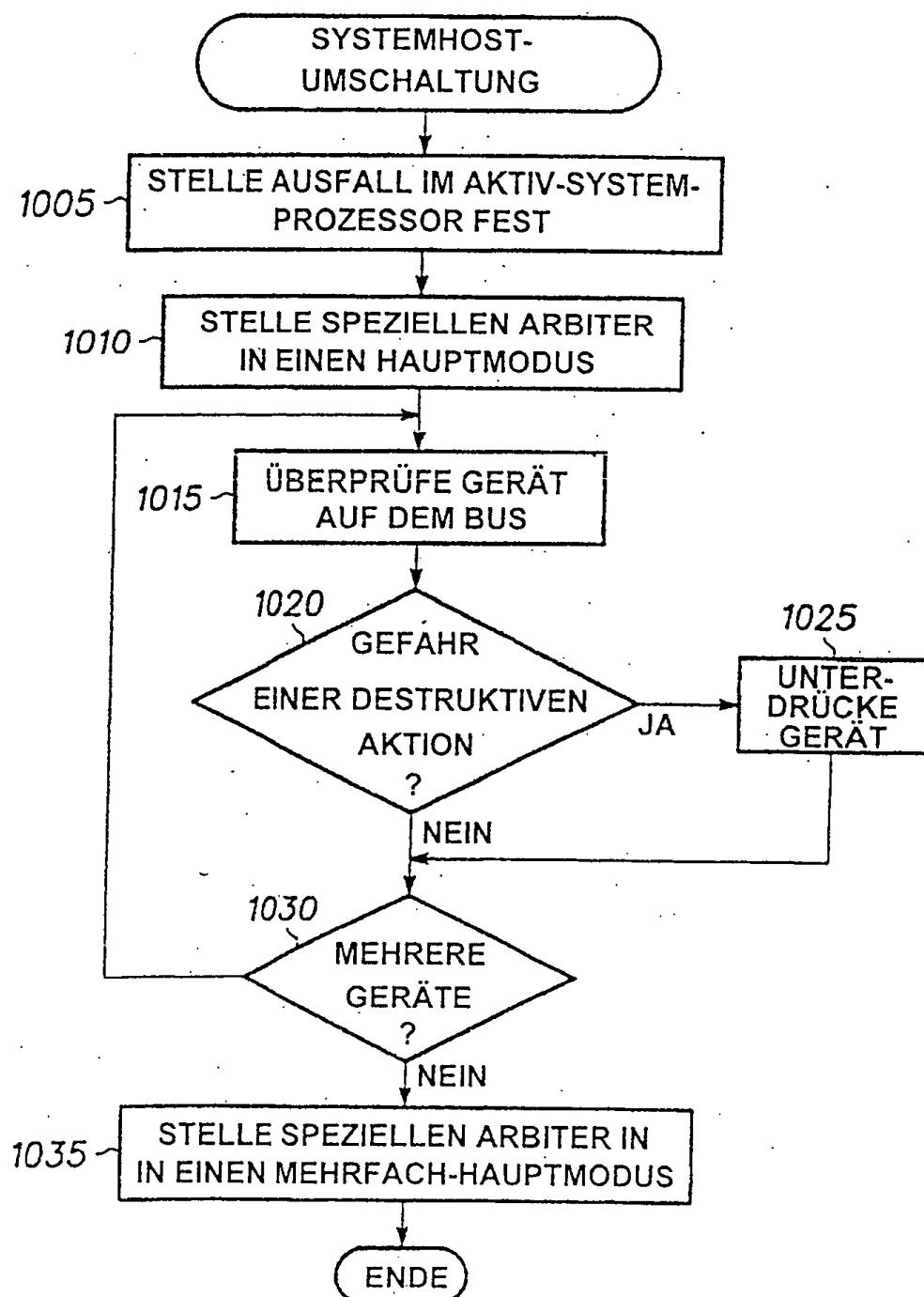

[0015] **Fig. 10** ist ein Flussdiagramm des Prozesses des Umschaltens des Systemprozessors.

**Beschreibung einer bevorzugten Ausführungsform**

[0016] In einer bevorzugten Ausführungsform der Erfindung wird ein Verfahren zum Umschalten zwischen mehreren Systemprozessoren auf einem CompactPCI-Bus zur Verfügung gestellt. Wenn ein Standby-Systemprozessor einen Ausfall feststellt, der einen Aktiv-Systemprozessor auf dem CompactPCI-Bus beeinträchtigt, stellt der Standby-Systemprozessor einen speziellen Arbiter in einen Ein-Mastermodus. Dann stellt der Standby-Prozessor fest, ob jedes Gerät auf dem CompactPCI-Bus Gefahr läuft, eine destruktive Aktion auszuführen, indem beispielsweise festgestellt wird, ob Interrupts an das Gerät möglich sind, ob das Gerät über die Fähigkeit des Ausführens eines direkten Speicherzugriffs auf den Aktiv-Systemprozessor verfügt und/oder ob sich das Gerät auf einer ausgefallenen Platine befindet. Falls der Standby-Systemprozessor feststellt, dass ein Gerät Gefahr läuft, eine destruktive Aktion auszuführen, unterdrückt der Standby-Systemprozessor das Gerät beispielsweise durch Programmieren des Geräts auf Einstellung des Betriebs oder durch Verändern einer Adresse, an die das Gerät schreibt. Dann stellt der Standby-Systemprozessor den speziellen Arbiter in einen Mehrfach-Mastermodus.

## Multikonfigurations-Rückwandplatine

[0017] **Fig.** 1 ist ein Schaltdiagramm einer Multikonfigurations-Rückwandplatine der bevorzugten Ausführungsform der Erfindung. In **Fig.** 1 weist eine Rückwandplatine **100** einen CompactPCI-Bus [1] **110** und einen CompactPCI-Bus [2] **120** auf. Mit dem CompactPCI-Bus [1] **110** sind ein Systemprozessorslot [1] **112**, ein Brückenslot [1] **114** und Ein-/Ausgabe-Slots [1] **116** verbunden. Die Ein-/Ausgabe-Slots [1] **116** sind zum Einsetzen der Ein-/Ausgabe-Platinen [1] **118** zur Implementierung entsprechender Geräte vorgesehen. Mit dem CompactPCI-Bus [2] **120** sind ein Systemprozessorslot [2] **122**, ein Brückenslot [2] **124** und Ein-/Ausgabe-Slots [2] **126** verbunden. Die Ein-/Ausgabe-Slots [2] sind zum Einsetzen der Ein-/Ausgabe-Platinen [2] **128** zum Implementieren entsprechender Geräte vorgesehen. Eine Querverbindung [1] **130** koppelt den Systemprozessorslot [1] **112** an den Brückenslot [2] **124**. Eine Querverbindung [2] **140** koppelt den Systemprozessorslot [2] **122** an den Brückenslot [1] **114**. Vorzugsweise ist die Querverbindung [1] **130** ein erster lokaler Peripheriekomponentenverbundungs (PCI)-Bus und die Querverbindung [2] **140** ein zweiter lokaler PCI-Bus.

[0018] In **Fig.** 1 sind ebenfalls die Systemprozessorplatten und die Brückenplatten gezeigt, die zur Bildung des gesamten Rechnersystems mit der Rückwandplatine **100** verbunden sind. Wie oben angemerkt, sieht die Rückwandplatine **100** mehrere potentielle Konfigurationen von Rechnersystemen vor. Je nach der ausgewählten Konfiguration der Rückwandplatine **100**, wird irgendeine Kombination der in **Fig.** 1 gezeigten Systemprozessorplatten und Brückenplatten vorliegen und/oder aktiv sein. Eine Systemprozessorplatine [1] **150** mit einem Systemprozessor [1] **152** und einem Systemhost [1S] **154** wird in den Systemprozessorslot [1] **112** eingefügt. Eine Brückenplatine [1] **160** mit einem Systemhost [1B] **164** und einem Hot-Swap-Controller [1] **166** ist optional in den Brückenslot [1] **114** eingefügt. Eine Systemprozessorplatine [2] **170** mit einem Systemprozessor [2] **172** und einem Systemhost [2S] **174** wird in den Systemprozessorslot [2] **122** eingefügt. Eine Brückenplatine [2] **180** mit einem Systemhost [2B] **184** und einem Hot-Swap-Controller [2] **186** ist optional in den Brückenslot [2] **124** eingefügt. Der Systemprozessor ist zum Beispiel das Motorola-MPC750-Prozessorsystem.

[0019] **Fig.** 2 ist ein Schaltdiagramm einer Dualkonfiguration der Multikonfigurations-Rückwandplatine. In der Dualkonfiguration funktionieren ein erstes und ein zweites Teilsystem unabhängig voneinander. In **Fig.** 2 wird die Systemprozessorplatine [1] **150** in den Systemprozessorslot [1] **112** eingefügt und die Systemprozessorplatine [2] **170** wird in den Systemprozessorslot [2] **122** eingefügt. Der Systemprozessor [1] **152** steuert die Ein-/Ausgabe-Platinen [1] **118** auf dem CompactPCI-Bus [1] **110**, um die damit imple-

mentierten Geräte in einem ersten Teilsystem zu steuern. Der Systemhost [1S] **154** steuert die Busfunktionen des CompactPCI-Busses [1] **110**. Der Systemprozessor [2] **172** steuert die Ein-/Ausgabe-Platinen [2] **128** auf dem CompactPCI-Bus [2] **120**, um die damit implementierten Geräte in einem zweiten Teilsystem zu steuern. Der Systemhost [2S] **174** steuert die Busfunktionen des CompactPCI-Busses [2] **120**. Weder die Querverbindung [1] **130** noch die Querverbindung [2] **140** werden verwendet.

[0020] **Fig.** 3 ist ein Schaltdiagramm einer erweiterten Konfiguration der Multikonfigurations-Rückwandplatine. In der erweiterten Konfiguration steuert ein einzelner Systemprozessor die auf beiden Bussen implementierten Geräte. In **Fig.** 3 wird die Systemprozessorplatine [1] **150** in den Systemprozessorslot [1] **112** eingefügt, und die Brückenplatine [2] **180** wird in den Brückenslot [2] **124** eingefügt. Der Systemprozessor [1] **152** steuert die Ein-/Ausgabe-Platinen [1] **118** auf dem CompactPCI-Bus [1] **110**, um die damit implementierten Geräte zu steuern. Der Systemhost [1S] **154** steuert die Busfunktionen des CompactPCI-Busses [1] **110**. Der Systemprozessor [1] **152** steuert über die Querverbindung [1] **130** ebenfalls die Ein-/Ausgabe-Platinen [2] **128** auf dem CompactPCI-Bus [2] **120**, um die damit implementierten Geräte zu steuern. Der Systemhost [2B] **184** steuert die Busfunktionen des CompactPCI-Busses [2] **120**. Die Querverbindung [2] **140** wird nicht verwendet.

[0021] **Fig.** 4 ist ein Schaltdiagramm einer Aktiv/Standby-Konfiguration der Multikonfigurations-Rückwandplatine in einem Aktiv-Modus. In dem Aktiv/Standby-System steuert ein einzelner Aktiv-Systemprozessor die auf beiden Bussen implementierten Geräte in einem Aktiv-Modus. Im Fall eines Ausfalls in dem Aktiv-Systemprozessor übernimmt ein Standby-Prozessor die Steuerung der Geräte in einem Standby-Modus. In **Fig.** 4 wird die Systemprozessorplatine [1] **150** in den Systemprozessorslot [1] **112** eingefügt, und die Systemprozessorplatine [2] **170** wird in den Systemprozessorslot [2] **122** eingefügt. Die Brückenplatine [1] **160** wird in den Brückenslot [1] **114** eingefügt, und die Brückenplatine [2] **180** wird in den Brückenslot [2] **124** eingefügt. In einem Aktiv-Modus werden die Systemprozessorplatten [1] **150** und die Brückenplatten [2] **180** als Anschlussplatten verwendet. Der Systemprozessor [1] **152** steuert die Ein-/Ausgabe-Platinen [1] **118** auf dem CompactPCI-Bus [1] **110** und steuert über die Querverbindung [1] **130** ebenfalls die Ein-/Ausgabe-Platinen [2] **128** auf dem CompactPCI-Bus [2] **120**. Der Systemhost [1S] **154** steuert die Busfunktionen des CompactPCI-Busses [1] **110**, und der Systemhost [2B] **184** steuert die Busfunktionen des CompactPCI-Busses [2] **120**. Die Querverbindung [2] **140** wird nicht verwendet.

[0022] **Fig.** 5 ist ein Schaltdiagramm der Aktiv/Standby-Konfiguration der Multikonfigurations-Rückwandplatine in einem Standby-Modus. In dem Standby-Modus werden die Systemprozessor-

platine [2] 170 und die Brückenplatine [1] 160 als Anschlussplatinen verwendet. Der Systemprozessor [2] 172 steuert die Ein-/Ausgabe-Platinen [2] 128 auf dem CompactPCI-Bus [1] 110 und steuert über die Querverbindung [2] 140 ebenfalls die Ein-/Ausgabe-Platinen [1] 118 auf dem CompactPCI-Bus [2] 120. Der Systemhost [1B] 164 steuert die Busfunktionen des CompactPCI-Busses [1] 110, und der Systemhost [2S] 174 steuert die Busfunktionen des CompactPCI-Busses [2] 120. Die Querverbindung [1] 130 wird nicht verwendet.

[0023] In einer Aktiv/Aktiv-Konfiguration werden beide Systemprozessorplatinen und beide Brückenplatinen eingefügt, wie in **Fig. 1** gezeigt. Die Systemprozessorplatine [1] 150 wird in den Systemprozessorslot [1] 112 eingefügt, und die Systemprozessorplatine [2] 170 wird in den Systemprozessorslot [2] 122 eingefügt. Die Brückenplatine [1] 160 wird in den Brückenslot [1] 114 eingefügt, und die Brückenplatine [2] 180 wird in den Brückenslot [2] 124 eingefügt. In einem Dualmodus funktionieren ein erstes und ein zweites System, wie in der oben beschriebenen Dualkonfiguration, unabhängig voneinander. Der Systemprozessor [1] 152 steuert die Ein-/Ausgabe-Platinen [1] 118 auf dem CompactPCI-Bus [1] 110, um die damit implementierten Geräte in einem ersten System zu steuern. Der Systemprozessor [2] 172 steuert die Ein-/Ausgabe-Platinen [2] 128 auf dem CompactPCI-Bus [2] 120, um die damit implementierten Geräte in einem zweiten System zu steuern. Der Systemhost [1S] 154 steuert die Busfunktionen des CompactPCI-Busses [1] 110, und der Systemhost [2S] 174 steuert die Busfunktionen des CompactPCI-Busses [2] 120. Weder die Querverbindung [1] 130 noch die Querverbindung [2] 140 werden verwendet.

[0024] Falls in der Aktiv/Aktiv-Konfiguration in dem Systemprozessor auf dem CompactPCI-Bus [2] 120 ein Ausfall vorliegt, wird die Verarbeitungsbelastung in einem ersten gemeinsamen ("shared") Modus zu dem Systemprozessor [1] 152 verschoben. Der erste gemeinsame Modus arbeitet auf eine mit dem oben besprochenen und in **Fig. 4** gezeigten Aktiv-Modus der Aktiv/Standby-Konfiguration identische Weise. Falls in dem Systemprozessor auf dem CompactPCI-Bus [1] 110 ein Ausfall vorliegt, wird die Verarbeitungsbelastung in einem zweiten gemeinsamen Modus zu dem Systemprozessor [2] 172 verschoben. Der zweite gemeinsame Modus arbeitet auf eine mit dem oben besprochenen und in **Fig. 5** gezeigten Standby-Modus der Aktiv/Standby-Konfiguration identische Weise.

#### Hostplatinen-Swap

[0025] Wie oben gezeigt, werden auf jedem Bus mehrere Systemhosts bereitgestellt. Die Systemprozessorplatine [1] 150, die Brückenplatine [1] 160, die Systemprozessorplatine [2] 170 und die Brückenplatine [2] 180 sind jede eine Hostplatine ("host board"), auf der ein Systemhost residiert. Als Folge kann im

Falle eines Ausfalls auf der Aktiv-Systemhostplatine die Steuerung der Busfunktionen auf jedem Bus von einem Aktiv-Systemhost zu einem Standby-Systemhost umgeschaltet werden. Herkömmliche CompactPCI-Busarchitektur berücksichtigt den "Hot-Swap" einer Nichthostplatine auf einem CompactPCI-Bus, wie etwa einer der Ein-/Ausgabe-Platinen 118 oder einer der Ein-/Ausgabe-Platinen 128. Das heisst, dass die Platine entfernt und ausgewechselt werden kann, ohne den Betrieb des Rechners durch ein Zurücksetzen ("resetting") der Geräte zu unterbrechen. Dies wird zum Beispiel in CompactPCI Hot Swap Specification von PCI Industrial Computer Manufacturers Group, 301 Edgewater Place Suite 220, Wakefield, Massachusetts, beschrieben. Dementsprechend schafft die bevorzugte Ausführungsform der Erfindung durch das Bereitstellen mehrerer Systemhosts auf jedem CompactPCI-Bus die Fähigkeit für das Hot-Swapping der Hostplatine, was während der Fortführung von Operationen den Austausch einer ausgefallenen Hostplatine zulässt. Als Folge können die Vorteile der CompactPCI-Busarchitektur einer hochverfügbaren oder fehlertoleranten Anwendung zur Verfügung gestellt werden.

[0026] **Fig. 6** ist ein Flussdiagramm des durch das Rechnersystem der bevorzugten Ausführungsform für das Swapping in einer Aktiv/Standby-Konfiguration durchgeföhrten Prozesses. Die in **Fig. 6** beschriebenen Grundfunktionen werden durch eine Kombination des Systemprozessors 152 oder 172, des Systemhosts 154, 164, 174 oder 184 und des Hot-Swap-Controllers 166 oder 186 durchgeführt, und diese werden später in der Beschreibung näher erläutert. Dem Fachmann ist klar, wie diese Funktionen in einer für die vorliegende Anwendung am Besten geeigneten Weise, jedoch auf der Grundlage der vorliegenden Beschreibung zu implementieren sind. Wenn bei Schritt 605 in der Hostplatine ein Ausfall ermittelt wird, schreitet die Steuerung zu Schritt 610. Bei Schritt 610 wird die Querverbindung [2] 140 anstelle der Querverbindung [1] 130 verwendet. Bei Schritt 615 wird die Systemverarbeitung von dem Systemprozessor [1] 152 an den Systemprozessor [2] 172 übertragen. Der Schritt 615 wird später ausführlicher erläutert. Bei Schritt 620 wird die Steuerung der Busfunktionen des CompactPCI-Busses [1] 110 von dem Systemhost [1S] 154 an den Systemhost [1B] 164 übertragen. Bei Schritt 625 wird die Steuerung der Busfunktionen des CompactPCI-Busses [2] 120 von dem Systemhost [2B] 184 an den Systemhost [2S] 174 übertragen. Die Systemhostübertragung wird später mit Bezug auf **Fig. 8** und **Fig. 9** ausführlicher erläutert. Bei Schritt 630 wird die ausgefallene Hostplatine Hot-Swap-ausgewechselt und der Hostplatinenausfall wird ohne Unterbrechung des Betriebs des Systems behoben.

[0027] **Fig. 7** ist ein Flussdiagramm des Prozesses des Swappings der Hostplatine in einer Aktiv/Aktiv-Konfiguration. Wie in **Fig. 6** werden die in **Fig. 7** beschriebenen Grundfunktionen durch eine Kombi-

nation des Systemprozessors **152** oder **172**, des Systemhosts **154**, **164**, **174** oder **184** und des Hot-Swap-Controllers **166** oder **186** durchgeführt, und dies wird später in der Beschreibung näher erläutert. Dem Fachmann ist klar, wie diese Funktionen in einer für die vorliegende Anwendung am Besten geeignete Weise, jedoch auf der Grundlage der vorliegenden Beschreibung zu implementieren sind. Wenn bei Schritt **705** in der Hostplatine ein Ausfall ermittelt wird, schreitet die Steuerung zu Schritt **710**. Bei Schritt **710** wird die Querverbindung [2] **140** verwendet. Wie bei Schritt **715** angegeben, fährt der Systemprozessor [2] **172** mit der Steuerung der Verarbeitung auf dem CompactPCI-Bus [2] **120** fort. Bei Schritt **720** wird die Verarbeitungssteuerung der Geräte auf dem CompactPCI-Bus [1] **110** an den Systemprozessor [2] **172** übertragen. Die Systemprozessorübertragung wird später mit Bezug auf Fig. 10 ausführlicher erläutert. Wie bei Schritt **725** angegeben, fährt der Systemhost [2S] **174** mit der Steuerung der Busfunktionen des CompactPCI-Busses [2] **120** fort. Bei Schritt **730** wird die Steuerung der Busfunktionen des CompactPCI-Busses [1] **110** von dem Systemhost [1S] **154** an den Systemhost [1B] **164** übertragen. Bei Schritt **735** wird die ausgefallene Hostplatine Hot-Swap-ausgewechselt und der Hostplatinenausfall wird ohne Unterbrechung des Systembetriebs behoben.

[0028] Wie oben erwähnt, stellt der herkömmliche CompactPCI-Standard eine Hot-Swap-Fähigkeit zur Verfügung. Somit basieren der Hot-Swap-Controller [1] **166** auf der Brückenplatine [1] **160** und der Hot-Swap-Controller [2] **186** auf der Brückenplatine [2] **180** auf einem herkömmlichen CompactPCI Hot Swap, wie in der oben zitierten CompactPCI Hot Swap Specification definiert. Dem Fachmann wird es leichtfallen, auf der Grundlage der vorliegenden Beschreibung, auf der Grundlage der CompactPCI Hot Swap Specification und auf der Grundlage von Konstruktionspräferenz und Eignung für die vorliegende Anwendung, den Hot-Swap-Controller zu implementieren. Das Hot-Swapping der Hostplatine erfordert jedoch einige Modifikationen an dem herkömmlichen CompactPCI-Systemhost, um sicherzustellen, dass die Busfunktionen durch die Existenz von zwei Systemhosts auf einem Bus nicht gestört werden.

[0029] Fig. 8 ist ein Schaltdiagramm eines derartige Modifikationen aufweisenden Systemhosts. Der Systemhost **800** in Fig. 8 entspricht dem Systemhost [1S] **154**, dem Systemhost [1B] **164**, dem Systemhost [2S] **174** oder dem Systemhost [2B] **184**. Der Systemhost **800** enthält eine herkömmliche PCI-PCI-Brücke **810**, welche den CompactPCI-Bus mit einem örtlichen PCI-Bus auf der Hostplatine verbindet. Die Brücke **810** ist zum Beispiel ein DEC-21154-PCI-Brückenarbiter. Weiterhin enthält der Systemhost **800** einen speziellen Arbiter **820**. Der spezielle Arbiter **820** ersetzt die Funktion des in der Brücke **810** enthaltenen herkömmlichen Busarbiters, der gesperrt wird. Der spezielle Arbiter **820** gleicht

dem herkömmlichen PCI-Busarbiter, mit der Ausnahme, dass verschiedene zusätzliche Eigenschaften bereitgestellt werden, die ein Systemhostumschalten berücksichtigen. Diese Eigenschaften werden nachstehend mit Bezug auf Fig. 9 erläutert.

[0030] Fig. 9 ist ein Flussdiagramm des Prozesses des Umschaltens des Systemhosts. wie in den verschiedenen oben beschriebenen Szenarien, wird der Prozess zum Umschalten zwischen dem Systemhost [1S] **154** und dem Systemhost [1B] **164** auf dem CompactPCI-Bus [1] **110** durch den Hot-Swap-Controller **166** und den speziellen Arbiter **820** in dem Systemhost [1S] **154** oder in dem Systemhost [1B] **164** durchgeführt, oder er wird zum Umschalten zwischen dem Systemhost [2S] **174** und dem Systemhost [2B] **184** auf dem CompactPCI-Bus [2] **120** durch den Hot-Swap-Controller **186** und den speziellen Arbiter **820** in dem Systemhost [2S] **174** oder in dem Systemhost [2B] **184** durchgeführt. Bei Schritt **905** unterdrückt der Hot-Swap-Controller den Bus. Genauer gesagt, übermittelt der Hot-Swap-Controller dem speziellen Arbiter **820** ein Anforderungssignal von hoher Dringlichkeit-, dem der spezielle Arbiter **820** nur stattgibt, wenn sich der Bus im Ruhezustand befindet. Ein spezielles Paar von Anforderungs/Bewilligungsleitungen werden in dem speziellen Arbiter **820** für den Hot-Swap-Controller zur Verwendung für diesen Zweck bereitgestellt.

[0031] Bei Schritt **910** sperrt das Rechnersystem die durch den Aktiv-Systemhost übermittelten Systemhostsignale. Im Besonderen übermittelt der Hot-Swap-Controller dem speziellen Arbiter **820** ein Schwebe ("float")-Signal, das den speziellen Arbiter **820** veranlasst, das Systemhostsignal zu sperren, das er in seinem Aktiv-Zustand übermittelt. Eine spezielle Floatleitung wird dem speziellen Arbiter **820** für den Hot-Swap-Controller zur Verwendung für diesen Zweck hinzugefügt. Die Systemhostsignale, die durch das Floatsignal gesperrt werden, enthalten Bewilligungssignale zum Bewilligen eines Buszugriffs auf Geräte auf dem Bus, Reset-Signale zum Zurücksetzen von Geräten auf dem Bus und Taktsignale und Interrupts, die an die Geräte auf dem Bus übermittelt werden. Der spezielle Arbiter **820** definiert seine Bewilligungssignale, Reset-Signale und Taktsignale als Dreiphasensignale, wobei eine hochohmige Phase als dritte Phase hinzugefügt wird. Das Floatsignal veranlasst den speziellen Arbiter **820**, die Bewilligungssignale, die Reset-Signale und die Taktsignale in der dritten Phase zu setzen und die Unterbrechungen zu sperren. Bei Schritt **915** überträgt der Hot-Swap-Controller die Steuerung von dem ausgefallenen Aktiv-Systemhost auf den Standby-Systemhost. Obwohl zur Vereinfachung der Beschreibung in der gezeigten Reihenfolge beschrieben, überträgt die bevorzugte Ausführungsform der Erfindung die Reset-Signale und Taktsignale an den Standby-Systemhost bevor sie durch den Aktiv-Systemhost gesperrt werden, so dass nicht zugelassen wird, dass die Reset- und Taktsignale eine Zwischenphase erreichen,

in der ein unerwünschtes Signal zu irgendeinem der Geräte gesendet werden könnte. Weiterhin werden die Taktsignale zur Verhinderung von kurzen Zyklen in der dritten Phase vorzugsweise auf die Abschlusskante gesetzt.

#### Systemprozessorplatinen-Swap

[0032] Das Swapping der Systemprozessorplatine macht das Umschalten der Steuerung des Systemprozessors erforderlich. Zum Beispiel wird, im Falle eines die Systemprozessorplatine [1] **150** beeinträchtigenden Ausfalls, die Steuerung von dem Systemprozessor [1] **152** an den Systemprozessor [2] **172** oder, im Falle eines die Systemprozessorplatine [2] **170** beeinträchtigenden Ausfalls, von dem Systemprozessor [2] **172** an den Systemprozessor [1] **152** übertragen. Hochverfügbare oder fehlertolerante Anwendungen erfordern, dass die Systemprozessorumschaltung ohne Zurücksetzen der Geräte auf dem System oder anderweitig den Betrieb des Systems unterbrechend bewerkstelligt wird. Da jedoch der Systemprozessor [1] **152** und der Systemprozessor [2] **172** unabhängig operieren, gefährdet eine solche Umschaltung das System. Zum Beispiel kann ein Gerät auf dem CompactPCI-Bus während der Umschaltung einen direkten Speicherzugriff auf den Speicher des Systemprozessors durchführen. Der Standby-Systemprozessor könnte jedoch nicht das gleiche Adressierschema verwenden, so dass kritische Daten beschädigt werden würden, wenn das Gerät an die ursprünglich vorgesehene Adresse schreibt. Zur Verhinderung einer derartigen Beschädigung, stellt die bevorzugte Ausführungsform der Erfindung durch den Standby-Systemprozessor eine nahtlose Umschaltung der Systemprozessorsteuerung bereit. [0033] **Fig. 10** ist ein Flussdiagramm einer nahtlosen Umschaltung des Systemprozessors. Die Funktionen von **Fig. 10** werden zum Umschalten von dem Aktiv-Systemprozessor zu dem Standby-Systemprozessor durch den Standby-Systemprozessor durchgeführt. Bei Schritt **1005** stellt der Standby-Systemprozessor fest, ob ein den Aktiv-Systemprozessor beeinträchtigender Ausfall besteht, wie etwa ein Ausfall auf der Aktiv-Systemprozessorplatine oder auf einer Anschlussbrückenplatine, der, wie oben beschrieben wurde, das Umschalten von dem Aktiv-Systemprozessor zu dem Standby-Systemprozessor erforderlich macht. Bei Schritt **1010** stellt der Standby-Systemprozessor den speziellen Arbiter **800** so in einen Ein-Mastermodus, dass er mit Ausnahme des Standby-Systemprozessors keinem Gerät eine Busbewilligung erteilen wird. Bei Schritt 1015 überprüft der Standby-Systemprozessor ein Gerät auf dem Bus und stellt bei Schritt **1020** fest, ob das Gerät Gefahr läuft, eine destruktive Aktion durchzuführen. Zum Beispiel greift der Standby-Systemprozessor auf Informationen auf dem Gerät zu und stellt fest, ob Interrupts an das Gerät freigegeben sind, stellt fest, ob das Gerät über die Fähigkeit des Durch-

föhrens eines direkten Speicherzugriffs auf den Aktiv-Systemprozessor verfügt und/oder stellt fest, ob sich das Gerät auf einer ausgefallenen Platine befindet, wie etwa bei einem Ausfall auf der Aktiv-Systemprozessorplatine oder einer Begleitplatine.

[0034] Wenn der Standby-Systemprozessor bei Schritt 1025 feststellt, dass das Gerät Gefahr läuft, eine destruktive Aktion durchzuführen, dann unterdrückt der Standby-Systemprozessor das Gerät. Zum Beispiel programmiert der Standby-Systemprozessor das Gerät zum Einstellen des Betriebs oder er verändert eine Adresse, an die das Gerät schreibt. So lange es mehrere bei Schritt **1030** zu überprüfende Geräte gibt, wiederholt der Standby-Systemprozessor die Schritte **1015** bis **1030**. Letztendlich sind bei Schritt **1035** alle Geräte unterdrückt worden, die Gefahr laufen, eine destruktive Aktion durchzuführen, und der Standby-Systemprozessor stellt den speziellen Arbiter **800** in einen Mehrfach-Mastermodus, der es ihm gestattet, anderen Geräten als dem Standby-Systemprozessor eine Busbewilligungen zu erteilen.

[0035] Es sollte klar sein, dass die hierin beschriebene Erfindung den Vorteil eines nahtlosen Umschaltens zwischen mehreren Prozessoren auf einem Bus zur Verfügung stellt. Die vorliegende Erfindung ist oben mit Bezug auf die bevorzugten Ausführungsformen beschrieben worden. Jedoch ist Fachleuten klar, dass Veränderungen und Modifikationen dieser bevorzugten Ausführungsformen durchgeführt werden können, ohne von dem Rahmen der vorliegenden Erfindung abzuweichen.

#### Patentansprüche

1. Verfahren für das Umschalten zwischen mehreren Systemprozessoren auf einem Bus (**120**), wobei das Verfahren durch einen Standby-Systemprozessor bei kontinuierlichem Betrieb durchgeführt wird und die folgenden Schritte umfasst:

Feststellen eines einen Aktiv-Systemprozessor auf dem Bus beeinträchtigenden Ausfalls mittels eines funktionellen Aktiv-Prozessors;

Versetzen eines speziellen Arbiters (**800**) in einen Ein-Mastermodus, wobei der spezielle Arbiter lediglich dem Standby-Systemprozessor eine Busbewilligung erteilt;

Feststellen, ob ein Gerät auf dem Bus (**120**) Gefahr läuft, eine destruktive Aktion durchzuführen;

Stilllegen des Geräts, wenn festgestellt wird, dass das Gerät Gefahr läuft, eine destruktive Aktion durchzuführen; und

Versetzen des speziellen Arbiters (**800**) in einen Mehrfach-Mastermodus ohne Zurücksetzen des funktionellen Aktiv-Prozessors, wobei der spezielle Arbiter die Busbewilligung zumindest dem Standby-Systemprozessor erteilt.

2. Verfahren nach Anspruch 1, das weiterhin den Schritt des Wiederholens der Schritte des Feststel-

lens, ob ein Gerät auf dem Bus (**120**) Gefahr läuft, eine destruktive Aktion durchzuführen, und des Stilllegens des Geräts, wenn festgestellt wird, dass das Gerät Gefahr läuft, eine destruktive Aktion durchzuführen, für jedes Gerät auf dem Bus (**120**) umfasst.

3. Verfahren nach Anspruch 1, das den Schritt des Wiederholens der Schritte des Feststellens, ob ein Gerät auf dem Bus (**120**) Gefahr läuft, eine destruktive Aktion durchzuführen und des Stilllegens des Geräts, wenn festgestellt wird, dass das Gerät Gefahr läuft, eine destruktive Aktion durchzuführen, für jedes Gerät auf mehreren Bussen umfasst.

4. Verfahren nach Anspruch 1, wobei der Schritt des Feststellens, ob ein Gerät auf dem Bus (**120**) Gefahr läuft, eine destruktive Aktion durchzuführen, umfasst, dass festgestellt wird, ob Interrupts an das Gerät ermöglicht sind.

5. Verfahren nach Anspruch 1, wobei der Schritt des Feststellens, ob ein Gerät auf dem Bus (**120**) Gefahr läuft, eine destruktive Aktion durchzuführen, umfasst, dass festgestellt wird, ob das Gerät über eine Fähigkeit zum Durchführen eines direkten Speicherzugriffs auf den Aktiv-Systemprozessor verfügt.

6. Verfahren nach Anspruch 1, wobei der Schritt des Feststellens, ob ein Gerät auf dem Bus (**120**) Gefahr läuft, eine destruktive Aktion durchzuführen, umfasst, dass festgestellt wird, ob sich das Gerät auf einer ausgefallenen Platine befindet.

7. Verfahren nach Anspruch 1, wobei der Schritt des Stilllegens des Geräts das Programmieren des Geräts zum Einstellen des Betriebs umfasst.

8. Verfahren nach Anspruch 1, wobei der Schritt des Stilllegens des Geräts das Verändern einer Adresse, an die das Gerät schreibt, umfasst.

9. Verfahren nach einem der Ansprüche 1 bis 8, wobei der Bus (**120**) ein CompactPCI-Bus ist.

Es folgen 8 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 2

FIG. 3

FIG. 6

FIG. 7

*FIG. 8*

*FIG. 9*

FIG. 10