(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4670177号

(P4670177)

(45) 発行日 平成23年4月13日(2011.4.13)

(24) 登録日 平成23年1月28日(2011.1.28)

(51) Int.Cl.

F 1

|                |           |              |       |

|----------------|-----------|--------------|-------|

| G 11 C 11/22   | (2006.01) | G 11 C 11/22 | 501 A |

| H 01 L 27/10   | (2006.01) | G 11 C 11/22 | 501 F |

| H 01 L 27/105  | (2006.01) | G 11 C 11/22 | 501 L |

| H 01 L 21/8246 | (2006.01) | G 11 C 11/22 | 501 Z |

|                |           | H 01 L 27/10 | 481   |

請求項の数 9 (全 108 頁) 最終頁に続く

(21) 出願番号

特願2001-147475 (P2001-147475)

(22) 出願日

平成13年5月17日 (2001.5.17)

(65) 公開番号

特開2002-197857 (P2002-197857A)

(43) 公開日

平成14年7月12日 (2002.7.12)

審査請求日

平成20年1月18日 (2008.1.18)

(31) 優先権主張番号

特願2000-156089 (P2000-156089)

(32) 優先日

平成12年5月26日 (2000.5.26)

(33) 優先権主張国

日本国 (JP)

(31) 優先権主張番号

特願2000-247143 (P2000-247143)

(32) 優先日

平成12年8月17日 (2000.8.17)

(33) 優先権主張国

日本国 (JP)

(31) 優先権主張番号

特願2000-252080 (P2000-252080)

(32) 優先日

平成12年8月23日 (2000.8.23)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094363

弁理士 山本 孝久

(72) 発明者 西原 利幸

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 渡部 浩司

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 加藤 俊哉

最終頁に続く

(54) 【発明の名称】強誘電体型不揮発性半導体メモリ及びその駆動方法

(57) 【特許請求の範囲】

【請求項 1】

- (A) ビット線と、

- (B) 選択用トランジスタと、

- (C) それぞれがM個(但し、M ≥ 2)のメモリセルから構成された、N個(但し、N ≥ 2)のメモリユニットと、

- (D) M × N本のプレート線、

- から成り、

N個のメモリユニットは、層間絶縁層を介して積層されており、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

10

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、該共通の第1の電極は、選択用トランジスタを介してビット線に接続され、

第n番目(但し、n = 1, 2, ..., N)のメモリユニットにおいて、第m番目(但し、m = 1, 2, ..., M)のメモリセルの第2の電極は、第[(n-1)M + m]番目のプレート線に接続されており、

第[(n-1)M + m]番目のプレート線の内、mを共通とするプレート線は互いに前記層間絶縁層を介して積層されており、nを共通とするプレート線は互いに同一階層に配されていることを特徴とする強誘電体型不揮発性半導体メモリ。

【請求項 2】

上方に位置するメモリユニットのメモリセルを構成する強誘電体層の結晶化温度は、下

20

方に位置するメモリユニットのメモリセルを構成する強誘電体層の結晶化温度よりも低いことを特徴とする請求項1に記載の強誘電体型不揮発性半導体メモリ。

【請求項3】

(A) ビット線と、

(B) N個(但し、N > 2)の選択用トランジスタと、

(C) それがM個(但し、M > 2)のメモリセルから構成された、N個のメモリユニットと、

(D) M本のプレート線、

から成り、

N個のメモリユニットは層間絶縁層を介して積層されており、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、

第n番目(但し、n = 1, 2, ..., N)のメモリユニットにおける共通の第1の電極は、第n番目の選択用トランジスタを介してビット線に接続され、

第n番目のメモリユニットにおいて、第m番目(但し、m = 1, 2, ..., M)のメモリセルの第2の電極は、メモリユニット間で共通とされた第m番目のプレート線に接続されていることを特徴とする強誘電体型不揮発性半導体メモリ。

【請求項4】

(A) ビット線と、

(B) 2N個(但し、N > 1)の選択用トランジスタと、

(C) それがM個(但し、M > 2)のメモリセルから構成された、2N個のメモリユニットと、

(D) M本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、

第(2n - 1)番目(但し、n = 1, 2, ..., N)のメモリユニットにおける共通の第1の電極は、第(2n - 1)番目の選択用トランジスタを介してビット線に接続され、

第2n番目のメモリユニットにおける共通の第1の電極は、第2n番目の選択用トランジスタを介してビット線に接続され、

第(2n - 1)番目のメモリユニットを構成する第m番目(但し、m = 1, 2, ..., M)のメモリセルと、第2n番目のメモリユニットを構成する第m番目のメモリセルは、第2の電極を共有し、第(2n - 1)番目のメモリユニットを構成する第m番目のメモリセルの第1の電極と第2n番目のメモリユニットを構成する第m番目のメモリセルの第1の電極とは、第2の電極を介して積層されており、該共有された第m番目の第2の電極は第m番目のプレート線に接続されていることを特徴とする強誘電体型不揮発性半導体メモリ。

【請求項5】

(A - 1) 第1のビット線と、

(B - 1) N個(但し、N > 1)の第1の選択用トランジスタと、

(C - 1) それがM個(但し、M > 2)の第1のメモリセルから構成された、N個の第1のサブメモリユニットと、

(D - 1) N個の第1のサブメモリユニット間において、N個の第1のサブメモリユニットのそれぞれを構成する第1のメモリセルで共通とされたM本のプレート線、

から成る第1のメモリユニット、並びに、

(A - 2) 第2のビット線と、

(B - 2) N個の第2の選択用トランジスタと、

(C - 2) それがM個の第2のメモリセルから構成された、N個の第2のサブメモリユニットと、

(D - 2) N個の第2のサブメモリユニット間において、N個の第2のサブメモリユニ

10

20

30

40

50

ットのそれぞれを構成する第2のメモリセルで共通とされ、且つ、前記第1のメモリユニットを構成するM本のプレート線と共にM本のプレート線、

から成る第2のメモリユニットから構成され、

第1のサブメモリユニットは、層間絶縁層を介して、第2のサブメモリユニットと積層されており、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

第1のメモリユニットにおいて、第n番目（但し、n = 1, 2, ..., N）の第1のサブメモリユニットを構成する第1のメモリセルの第1の電極は、第n番目の第1のサブメモリユニットにおいて共通であり、該共通の第1の電極は、第n番目の第1の選択用トランジスタを介して第1のビット線に接続され、第m番目（但し、m = 1, 2, ..., M）の第1のメモリセルの第2の電極は共通の第m番目のプレート線に接続されており、10

第2のメモリユニットにおいて、第n番目の第2のサブメモリユニットを構成する第2のメモリセルの第1の電極は、第n番目の第2のサブメモリユニットにおいて共通であり、該共通の第1の電極は、第n番目の第2の選択用トランジスタを介して第2のビット線に接続され、第m番目の第2のメモリセルの第2の電極は共通の第m番目のプレート線に接続されていることを特徴とする強誘電体型不揮発性半導体メモリ。

【請求項6】

上方に位置するサブメモリユニットのメモリセルを構成する強誘電体層の結晶化温度は、下方に位置するサブメモリユニットのメモリセルを構成する強誘電体層の結晶化温度よりも低いことを特徴とする請求項5に記載の強誘電体型不揮発性半導体メモリ。20

【請求項7】

第1のビット線及び第2のビット線は同一のセンスアンプに接続されていることを特徴とする請求項5に記載の強誘電体型不揮発性半導体メモリ。

【請求項8】

（A-1）第1のビット線と、

（B-1）N個（但し、N > 1）の第1の選択用トランジスタと、

（C-1）それがM個（但し、M > 2）の第1のメモリセルから構成された、N個の第1のサブメモリユニットと、30

（D-1）N個の第1のサブメモリユニット間において、N個の第1のサブメモリユニットのそれを構成する第1のメモリセルで共通とされたM本のプレート線、

から成る第1のメモリユニット、並びに、

（A-2）第2のビット線と、

（B-2）N個の第2の選択用トランジスタと、

（C-2）それがM個の第2のメモリセルから構成された、N個の第2のサブメモリユニットと、40

（D-2）N個の第2のサブメモリユニット間において、N個の第2のサブメモリユニットのそれを構成する第2のメモリセルで共通とされ、且つ、前記第1のメモリユニットを構成するM本のプレート線と共にM本のプレート線、

から成る第2のメモリユニットから構成され、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

第1のメモリユニットにおいて、第n番目（但し、n = 1, 2, ..., N）の第1のサブメモリユニットを構成する第1のメモリセルの第1の電極は、第n番目の第1のサブメモリユニットにおいて共通であり、該共通の第1の電極は、第n番目の第1の選択用トランジスタを介して第1のビット線に接続され、

第2のメモリユニットにおいて、第n番目の第2のサブメモリユニットを構成する第2のメモリセルの第1の電極は、第n番目の第2のサブメモリユニットにおいて共通であり、該共通の第1の電極は、第n番目の第2の選択用トランジスタを介して第2のビット線に接続され、

第1のメモリユニットにおける第n番目の第1のサブメモリユニットを構成する第m番目（但し、m = 1, 2, ..., M）の第1のメモリセルと、第2のメモリユニットにおける50

第n番目の第2のサブメモリユニットを構成する第m番目の第2のメモリセルは、第2の電極を共有し、第1のメモリユニットにおける第n番目の第1のサブメモリユニットを構成する第m番目の第1のメモリセルの第1の電極と、第2のメモリユニットにおける第n番目の第2のサブメモリユニットを構成する第m番目の第2のメモリセルの第1の電極とは、第2の電極を介して積層されており、該共有された第2の電極は第m番目のプレート線に接続されていることを特徴とする強誘電体型不揮発性半導体メモリ。

#### 【請求項9】

第1のビット線及び第2のビット線は同一のセンスアンプに接続されていることを特徴とする請求項8に記載の強誘電体型不揮発性半導体メモリ。

#### 【発明の詳細な説明】

10

#### 【0001】

#### 【発明の属する技術分野】

本発明は、強誘電体型不揮発性半導体メモリ（所謂F E R A M）、及び、その駆動方法に関する。

#### 【0002】

#### 【従来の技術】

近年、大容量の強誘電体型不揮発性半導体メモリに関する研究が盛んに行われている。強誘電体型不揮発性半導体メモリ（以下、不揮発性メモリと略称する場合がある）は、高速アクセスが可能で、しかも、不揮発性であり、また、小型で低消費電力であり、更には、衝撃にも強く、例えば、ファイルのストレージやレジューム機能を有する各種電子機器、例えば、携帯用コンピュータや携帯電話、ゲーム機の主記憶装置としての利用、あるいは、音声や映像を記録するための記録メディアとしての利用が期待されている。

20

#### 【0003】

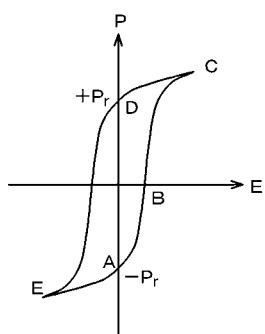

この不揮発性メモリは、強誘電体薄膜の高速分極反転とその残留分極を利用し、強誘電体層を有するキャパシタ部の蓄積電荷量の変化を検出する方式の、高速書き換えが可能な不揮発性メモリであり、基本的には、キャパシタ部（メモリセル）と選択用トランジスタ（スイッチング用トランジスタ）とから構成されている。キャパシタ部は、例えば、下部電極、上部電極、及び、これらの電極間に挟まれた高比誘電率 $\epsilon$ を有する強誘電体層から構成されている。この不揮発性メモリにおけるデータの書き込みや読み出しが、図53に示す強誘電体のP-Eヒステリシスループを応用して行われる。即ち、強誘電体層に外部電界を加えた後、外部電界を除いたとき、強誘電体層は自発分極を示す。そして、強誘電体層の残留分極は、プラス方向の外部電界が印加されたとき $+P_r$ 、マイナス方向の外部電界が印加されたとき $-P_r$ となる。ここで、残留分極が $+P_r$ の状態（図53の「D」参照）の場合を「0」とし、残留分極が $-P_r$ の状態（図53の「A」参照）の場合を「1」とする。

30

#### 【0004】

「1」あるいは「0」の状態を判別するために、強誘電体層に例えばプラス方向の外部電界を印加する。これによって、強誘電体層の分極は図53の「C」の状態となる。このとき、データが「0」であれば、強誘電体層の分極状態は、「D」から「C」の状態に変化する。一方、データが「1」であれば、強誘電体層の分極状態は、「A」から「B」を経由して「C」の状態に変化する。データが「0」の場合には、強誘電体層の分極反転は生じない。一方、データが「1」の場合には、強誘電体層に分極反転が生じる。その結果、キャパシタ部の蓄積電荷量に差が生じる。選択された不揮発性メモリの選択用トランジスタをオンにすることで、この蓄積電荷を信号電流として検出する。データの読み出し後、外部電界を0にすると、データが「0」のときでも「1」のときでも、強誘電体層の分極状態は図53の「D」の状態となってしまう。即ち、読み出し時、データ「1」は、一旦、破壊されてしまう。それ故、データが「1」の場合、マイナス方向の外部電界を印加して、「D」、「E」という経路で「A」の状態とし、データ「1」を再度書き込む。

40

#### 【0005】

現在主流となっている不揮発性メモリの構造及びその動作は、米国特許第4873664

50

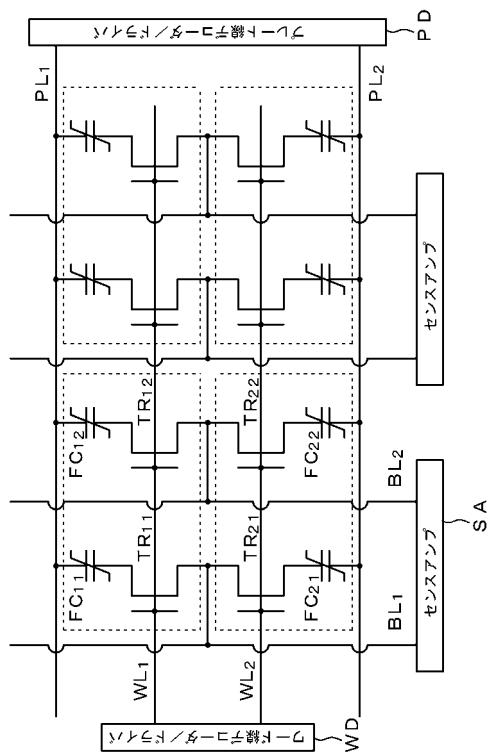

号において、S. Sheffiedらが提案したものである。この不揮発性メモリは、図54に回路図を示すように、2つの不揮発性メモリセルから構成されている。尚、図54において、1つの不揮発性メモリを点線で囲った。各不揮発性メモリは、例えば、選択用トランジスタTR<sub>11</sub>, TR<sub>12</sub>、キャパシタ部(メモリセル)FC<sub>11</sub>, FC<sub>12</sub>から構成されている。

#### 【0006】

尚、2桁あるいは3桁の添字、例えば添字「11」は、本来、添字「1, 1」と表示すべき添字であり、例えば「111」は、本来、添字「1, 1, 1」と表示すべき添字であるが、表示の簡素化のため、2桁あるいは3桁の添字で表示する。また、添字「M」を、例えば複数のメモリセルやプレート線を総括的に表示する場合に使用し、添字「m」を、例えば複数のメモリセルやプレート線を個々に表示する場合に使用し、添字「N」を、例えば選択用トランジスタやサブメモリユニットを総括的に表示する場合に使用し、添字「n」を、例えば選択用トランジスタやサブメモリユニットを個々に表示する場合に使用する。

10

#### 【0007】

そして、それぞれのメモリセルに相補的なデータを書き込むことにより、1ビットを記憶する。図54において、符号「WL」はワード線を示し、符号「BL」はビット線を示し、符号「PL」はプレート線を意味する。1つの不揮発性メモリに着目すると、ワード線WL<sub>1</sub>は、ワード線デコーダ/ドライバWDに接続されている。また、ビット線BL<sub>1</sub>, BL<sub>2</sub>は、センスアンプSAに接続されている。更には、プレート線PL<sub>1</sub>は、プレート線デコーダ/ドライバPDに接続されている。

20

#### 【0008】

このような構造を有する不揮発性メモリにおいて、記憶されたデータを読み出す場合、ワード線WL<sub>1</sub>を選択し、更には、プレート線PL<sub>1</sub>を駆動すると、相補的なデータが、対となったキャパシタ部FC<sub>11</sub>, FC<sub>12</sub>から選択用トランジスタTR<sub>11</sub>, TR<sub>12</sub>を介して対となったビット線BL<sub>1</sub>, BL<sub>2</sub>に電圧(ビット線電位)として現れる。かかる対となったビット線BL<sub>1</sub>, BL<sub>2</sub>の電圧(ビット線電位)を、センスアンプSAで検出する。

#### 【0009】

1つの不揮発性メモリは、ワード線WL<sub>1</sub>、及び、対となったビット線BL<sub>1</sub>, BL<sub>2</sub>によって囲まれた領域を占めている。従って、仮に、ワード線及びビット線が最短ピッチで配置されるとすると、1つの不揮発性メモリの最小面積は、加工最小寸法をFとしたとき、8F<sup>2</sup>である。従って、このような構造を有する不揮発性メモリの最小面積は8F<sup>2</sup>である。

30

#### 【0010】

このような構造の不揮発性メモリを大容量化しようとした場合、その実現は加工寸法の微細化に依存するしかない。また、1つの不揮発性メモリを構成するために2つの選択用トランジスタ及び2つのキャパシタ部が必要とされる。更には、ワード線と同じピッチでプレート線を配設する必要がある。それ故、不揮発性メモリを最小ピッチで配置することは殆ど不可能であり、現実には、1つの不揮発性メモリの占める面積は、8F<sup>2</sup>よりも大幅に増加してしまう。

40

#### 【0011】

しかも、不揮発性メモリと同等のピッチで、ワード線デコーダ/ドライバWD及びプレート線デコーダ/ドライバPDを配設する必要がある。言い換えれば、1つのロー・アドレスを選択するために2つのデコーダ/ドライバが必要とされる。従って、周辺回路のレイアウトが困難となり、しかも、周辺回路の占有面積も大きなものとなる。

#### 【0012】

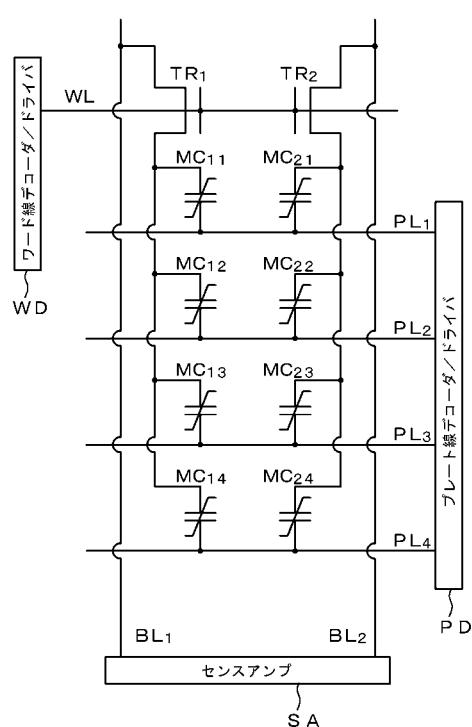

不揮発性メモリの面積を縮小する手段の1つが、特開平9-121032号公報から公知である。図55に等価回路を示すように、この特許公開公報に開示された不揮発性メモリは、1つの選択用トランジスタTR<sub>1</sub>の一端に並列にそれぞれの一端が接続された複数のメモリセルMC<sub>1M</sub>(例えば、M=4)から構成され、かかるメモリセルと対となったメモ

50

リセルも、1つの選択用トランジスタ  $TR_2$  の一端に並列にそれぞれの一端が接続された複数のメモリセル  $MC_{2m}$  から構成されている。選択用トランジスタ  $TR_1$ ,  $TR_2$  の他端は、それぞれ、ビット線  $BL_1$ ,  $BL_2$  に接続されている。対となったビット線  $BL_1$ ,  $BL_2$  は、センスアンプ  $SA$  に接続されている。また、メモリセル  $MC_{1m}$ ,  $MC_{2m}$  ( $m = 1, 2 \dots M$ ) の他端はプレート線  $PL_m$  に接続されており、プレート線  $PL_m$  はプレート線デコーダ/ドライバ  $PD$  に接続されている。更には、ワード線  $WL$  は、ワード線デコーダ/ドライバ  $WD$  に接続されている。

#### 【0013】

そして、対となったメモリセル  $MC_{1m}$ ,  $MC_{2m}$  ( $m = 1, 2 \dots M$ ) に相補的なデータが記憶される。例えば、メモリセル  $MC_{1k}$ ,  $MC_{2k}$  (ここで、 $k$  は  $1, 2, 3, 4$  のいずれか) に記憶されたデータを読み出す場合、ワード線  $WL$  を選択し、プレート線  $PL_m$  ( $m = k$ ) には  $(1/2)V_{cc}$  の電圧を印加した状態で、プレート線  $PL_k$  を駆動する。ここで、 $V_{cc}$  は、例えば、電源電圧である。これによって、相補的なデータが、対となったメモリセル  $MC_{1k}$ ,  $MC_{2k}$  から選択用トランジスタ  $TR_1$ ,  $TR_2$  を介して対となったビット線  $BL_1$ ,  $BL_2$  に電圧 (ビット線電位) として現れる。そして、かかる対となったビット線  $BL_1$ ,  $BL_2$  の電圧 (ビット線電位) を、センスアンプ  $SA$  で検出する。

#### 【0014】

対となった不揮発性メモリにおける一対の選択用トランジスタ  $TR_1$  及び  $TR_2$  は、ワード線  $WL$ 、及び、対となったビット線  $BL_1$ ,  $BL_2$  によって囲まれた領域を占めている。従って、仮に、ワード線及びビット線が最短ピッチで配置されるとすると、対となった不揮発性メモリにおける一対の選択用トランジスタ  $TR_1$  及び  $TR_2$  の最小面積は、 $8 F^2$  である。しかしながら、一対の選択用トランジスタ  $TR_1$ ,  $TR_2$  を、 $M$  組の対となったメモリセル  $MC_{1m}$ ,  $MC_{2m}$  ( $m = 1, 2 \dots M$ ) で共有するが故に、1ビット当たりの選択用トランジスタ  $TR_1$ ,  $TR_2$  の数が少なくて済み、また、ワード線  $WL$  の配置も緩やかなので、不揮発性メモリの縮小化を図り易い。しかも、周辺回路についても、1本のワード線デコーダ/ドライバ  $WD$  と  $M$  本のプレート線デコーダ/ドライバ  $PD$  で  $M$  ビットを選択することができる。従って、このような構成を採用することで、セル面積が  $8 F^2$  に近いレイアウトを実現可能であり、DRAM 並のチップサイズを実現することができる。

#### 【0015】

【発明が解決しようとする課題】

従来のような構造で不揮発性メモリを大容量化しようとした場合、その容量は最小加工寸法によって規定される。上述の従来例でわかるように、その最小セル面積は  $8 F^2$  である。この限界値は DRAM においても同様である。また、EPROM などのあらゆる半導体メモリを考慮した場合、ビット線とワード線とを最小ピッチで配置し、ビット線 1 本、ワード線 1 本が占有する領域にメモリセルを配置したときのセルの面積は、 $4 F^2$  がその限界とされる。

#### 【0016】

しかしながら、このような最小加工寸法  $F$ 、即ち、デザインルールの縮小は、リソグラフィーを中心とする微細加工技術の進展を待つほかない。しかも、その微細加工技術は世代を経るに従って困難さが増し、投資額も巨大化しており、チップコストの増大につながっている。従って、半導体メモリにおいても、現状から短期間で飛躍的な記憶容量の向上を果たすことは難しい。

#### 【0017】

上述のように半導体メモリの集積度の上限が規定されてしまう本質的理由として、以下の 2 点を挙げることができる。

#### 【0018】

第 1 に、半導体メモリにおける各メモリセルは半導体基板表面上に二次元的に配置されており、三次元的に積層されることがない。これは、従来の半導体メモリは、その殆どが記憶単位に 1 つ以上のトランジスタ (FET) を含んでいることに由来する。トランジスタは良質な半導体基板上にしか作製することができないため、メモリセルを半導体基板上に

10

20

30

40

50

二次元配置せざるを得ない。現在、エピタキシャル成長技術やレーザアニール技術による結晶化などで半導体単結晶層を積層する試みもなされているが、未だ十分な歩留まりと性能が得られていない。また、たとえ、これらが実現されたとしても、結局、半導体単結晶層に再度メモリセルを作り込もうとすると、工程数が倍近くに増加し、コストメリットが失われることになる。

【0019】

第2に、半導体メモリへのアクセスは、互いに交差したワード線（ロー方向）とビット線（カラム方向）による二次元マトリクスによりなされている。従来の半導体メモリにおいては、ワード線により一次元的にロー方向の選択を行い、各ビット線に読み出されたデータ列からカラム選択を行っている。尚、図54及び図55に示した従来例では、プレート線によってロー方向の選択を行うが、実質的に一次元の選択になっていることに変わりはない。

10

【0020】

ここで、仮にページ長を同一に保ったまま半導体メモリの集積度を2倍にした場合、当然2倍の本数のワード線やプレート線が必要になる。従って、ワード線やプレート線のデコードやドライブを行う周辺回路の集積度も2倍にする必要がある。これらの回路は、当然、トランジスタを必要とするので、セルアレイの周辺に二次元的に配置される。これに伴って、今度は、周辺回路のレイアウトが困難になる。

【0021】

以上のように、メモリセル自体が二次元配置に制限される上、仮にメモリセルを縮小できても、現在のアドレス選択方法では周辺回路のレイアウトが困難である。従って、半導体メモリの大容量化は、デザインルールの進展に依存するしかなかった。

20

【0022】

また、特開平9-121032号公報に開示された不揮発性メモリの面積を縮小する手法は、非常に効果的な手法であるが、以下に述べる問題点を有する。

【0023】

即ち、例えば、対となったメモリセルMC<sub>11</sub>、MC<sub>21</sub>において、メモリセルMC<sub>11</sub>にデータ「1」を書き込む場合、プレート線PL<sub>1</sub>をグランドレベル（0ボルト）とし、ビット線BL<sub>1</sub>をV<sub>cc</sub>とすることによって、強誘電体層を分極させるが、このとき、メモリセルMC<sub>21</sub>にデータ「0」を保持しておくために、ビット線BL<sub>2</sub>をグランドレベル（0ボルト）とする必要がある。

30

【0024】

一方、非選択のプレート線PL<sub>m</sub>（m=2, 3, 4）に接続されたメモリセルMC<sub>1m</sub>、MC<sub>2m</sub>（m=2, 3, 4）に記憶されたデータの破壊を防止するために、非選択のプレート線PL<sub>m</sub>（m=2, 3, 4）を、ビット線BL<sub>1</sub>、BL<sub>2</sub>の中間の電圧である（1/2）V<sub>cc</sub>に固定し、非選択のメモリセルMC<sub>1m</sub>、MC<sub>2m</sub>のキャパシタ部を構成する強誘電体層に加わる電界を緩和する。即ち、非選択のメモリセルMC<sub>1m</sub>、MC<sub>2m</sub>には、（1/2）V<sub>cc</sub>のディスターブが加わる。

【0025】

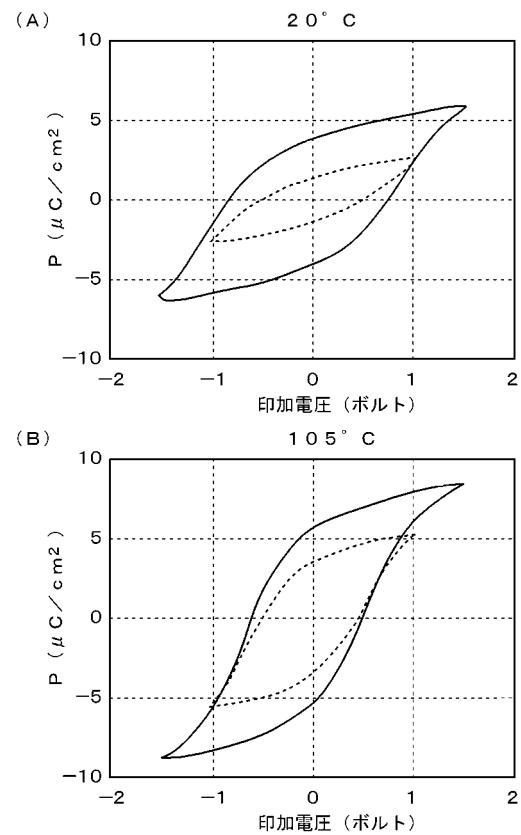

ところで、強誘電体層を構成する強誘電体材料は、本質的な物性として、反転電圧が負の温度特性を有する。図56の（A）及び（B）に、20°C及び105°Cにおける強誘電体材料のP-Eヒステリシスループを例示する。尚、図56の（A）及び（B）において、実線のP-EヒステリシスループはV<sub>cc</sub>=1.5ボルトの場合を示し、点線のP-EヒステリシスループはV<sub>cc</sub>=1.0ボルトの場合を示す。0ボルトにおけるデータ「1」状態、データ「0」状態の分極量の差が2P<sub>r</sub>として示されており、この2P<sub>r</sub>の値が信号量（信号電荷）に相当する。図56において、動作温度20°Cにおける反転電圧は±0.9ボルト程度である。従って、V<sub>cc</sub>=1.5ボルトで不揮発性メモリを動作させれば、ディスターブの電圧である（1/2）V<sub>cc</sub>では、非選択のキャパシタ部に記憶されたデータが破壊されることなく、7.9 μC/cm<sup>2</sup>の信号電荷を保持できる。これに対して、105°Cにおける反転電圧は±0.55ボルト程度である。従って、V<sub>cc</sub>=1.5ボル

40

50

トで不揮発性メモリを動作させれば、 $11 \mu C / cm^2$ の信号電荷を保持できるものの、ディスターべの電圧である(1/2)V<sub>cc</sub>では、非選択のキャパシタ部の電荷が反転し、記憶されたデータが破壊される。

【0026】

これとは逆に、動作温度 $105^\circ C$ で非選択のキャパシタ部の電荷を反転させないために、 $V_{cc} = 1$ ボルト程度とする必要がある。この場合、 $6.9 \mu C / cm^2$ の信号電荷を保持できるものの、 $20^\circ C$ では、 $2.8 \mu C / cm^2$ の信号電荷しか保持できなくなり、信号量が極端に小さくなってしまう。

【0027】

このように、不揮発性メモリの抗電圧は大きな負の温度依存性を有している。即ち、温度が上昇すると、不揮発性メモリの抗電圧が減少し、非選択のキャパシタ部の電荷が反転し易くなる。それ故、このような強誘電体層を構成する強誘電体材料の反転電圧が負の温度特性を有するといった特性に何らかの対策を施さないと、LSIに要求される温度範囲での不揮発性メモリの動作を保証できなくなる虞がある。

【0028】

また、これらの構造を有する不揮発性メモリに対して微細化を進めた場合、キャパシタ部の面積を小さくせざるを得ない。しかも、強誘電体層において分極に基づきデータを記憶するので、DRAMにおける絶縁膜のように、強誘電体層の膜厚を薄くしても、強誘電体層における蓄積電荷量が増加せず、蓄積電荷量は、キャパシタ部の面積に比例して少なくなっていく。

【0029】

例えば、256Mビットの不揮発性メモリを実現する場合、キャパシタ部の面積は $0.1 \mu m^2$ 程度となる。このとき、蓄積電荷量は $10 fC$ 程度となり、ビット線容量を $200 fF$ とした場合、 $50 mV$ 程度のセンス信号量(読み出し動作時にビット線に現れる電位)しか得ることができない。このようなセンス信号量では、センスマージンが不十分であり、更に不揮発性メモリに対して微細化を進めた場合、ついには不揮発性メモリに記憶されたデータの読み出しができなくなってしまう。

【0030】

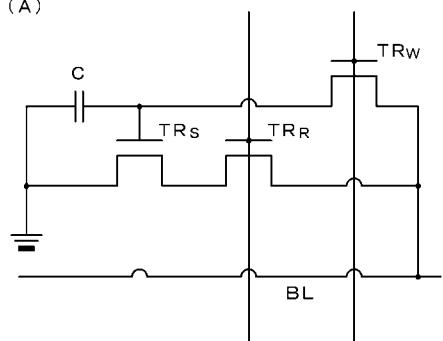

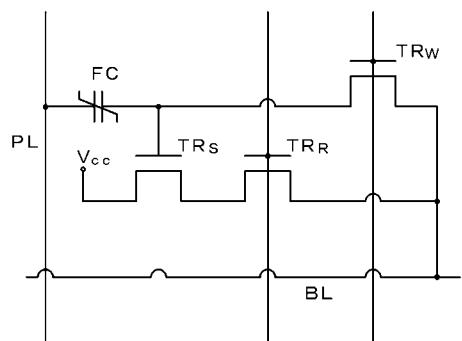

DRAMにおけるセンス信号量の減少に対処する方策の1つに、ゲインセルと呼ばれる増幅型のメモリセルがある(例えば、特開昭62-67861号公報、特開平1-255269号公報参照)。回路図を図57の(A)に示すゲインセルは、書込用トランジスタTR<sub>W</sub>と、読出用トランジスタTR<sub>R</sub>と、検出用トランジスタTR<sub>S</sub>と、キャパシタ部Cから構成されている。ゲインセルへのデータの書き込み時、書込用トランジスタTR<sub>W</sub>をオン状態とし、キャパシタ部Cに電荷を蓄積させる。ゲインセルからのデータの読み出し時、読出用トランジスタTR<sub>R</sub>をオン状態とする。一方、検出用トランジスタTR<sub>S</sub>は、キャパシタ部Cに記憶されたデータに依存して、オン状態あるいはオフ状態となる。

【0031】

このような構成のゲインセルを従来の米国特許第4873664号に開示された不揮発性メモリに適用した場合の回路図を、図57の(B)に示す。このようなゲインセルタイプの不揮発性メモリセルは、書込用トランジスタTR<sub>W</sub>、読出用トランジスタTR<sub>R</sub>、検出用トランジスタTR<sub>S</sub>、及び、キャパシタ部FCから構成することができる。書込用トランジスタTR<sub>W</sub>の一方のソース/ドレイン領域はビット線BLに接続され、他方のソース/ドレイン領域はキャパシタ部FCの下部電極に接続されている。検出用トランジスタTR<sub>S</sub>の一端は所定の電位V<sub>cc</sub>を有する配線(例えば、不純物層から構成された電源線)に接続され、他端は読出用トランジスタTR<sub>R</sub>を介してビット線BLに接続されている。更には、キャパシタ部FCの下部電極は、検出用トランジスタTR<sub>S</sub>のゲート電極に接続されている。

【0032】

このような構成の不揮発性メモリセルにおいては、データの読み出し時、プレート線PLにパルス電圧を印加し、キャパシタ部FCにおける分極反転の有無に起因した蓄積電荷量

10

20

30

40

50

に依存して、ディプレッショング型のN M O S F E Tから構成された検出用トランジスタT R<sub>S</sub>の動作状態が制御される。即ち、ビット線B Lを0ボルトにイコライズした後、読み出用トランジスタT R<sub>R</sub>をオン状態とすると、電源V<sub>cc</sub>から検出用トランジスタT R<sub>S</sub>及び読み出用トランジスタT R<sub>R</sub>を介して電流が流れ、ビット線B Lに電位が現れるが、かかるビット線B L上の電位は、不揮発性メモリセルに記憶されたデータに依存する。これによって、キャパシタ部F Cに記憶されたデータが「1」であるか「0」であるかを知ることができる。即ち、キャパシタ部F Cにおける小さな蓄積電荷に基づき、大きなビット線負荷を駆動することができる。

【0033】

しかしながら、このような構成の不揮発性メモリにおいては、1つの不揮発性メモリセル当たり、3つのトランジスタが必要とされ、1ビット当たりのセル面積が大幅に増加し、ビット当たりのコストが増加するという問題がある。

【0034】

また、データの読み出し時、プレート線P Lにパルス電圧を印加した際、キャパシタ部を構成する、プレート線P Lに接続された上部電極と、検出用トランジスタT R<sub>S</sub>のゲート電極に接続された下部電極との間に十分な電位差が生じないと、キャパシタ部F Cに分極反転が生じない。然るに、データの読み出し時、検出用トランジスタT R<sub>S</sub>のゲート電極に接続された下部電極は浮遊状態であり、その負荷容量は検出用トランジスタT R<sub>S</sub>のゲート容量分程度しかない。従って、プレート線P Lにパルス電圧を印加した際、上部電極と下部電極とのカップリングにより、下部電極の電位が大きく上昇してしまい、上部電極と下部電極との間に十分なる電界が形成されず、強誘電体層に分極反転が生じないといった問題がある。逆に、このようなカップリングによる下部電極の電位上昇を抑制するためには、下部電極にキャパシタ部F Cの数倍程度の負荷容量を追加する必要があり、そのためには、別途、キャパシタを追加しなければならなくなる。しかしながら、これでは、セル面積が大幅に増加してしまう。

【0035】

従って、本発明の第1の目的は、最小加工寸法に制限されずに大容量化を図ることができ、より一層、高集積化された強誘電体型不揮発性半導体メモリを提供することにある。

また、本発明の第2の目的は、アドレス選択における駆動配線数を削減することで周辺回路の縮小を図ることができる強誘電体型不揮発性半導体メモリを提供することにある。

【0036】

更に、本発明の第3の目的は、メモリセルの縮小と周辺回路の削減とを両立させることができ、デバイス全体として整合のとれた集積度向上が可能になる強誘電体型不揮発性半導体メモリを提供することにある。

【0037】

また、本発明の第4の目的は、強誘電体層を構成する強誘電体材料の反転電圧が負の温度特性を有するといった特性、即ち、強誘電体型不揮発性半導体メモリの抗電圧の負の温度依存性に対する対策を備え、要求される温度範囲での動作を確実に保証し得る強誘電体型不揮発性半導体メモリを提供することにある。

【0038】

更に、本発明の第5の目的は、1ビット当たりの面積が縮小することができ、しかも、記憶されたデータを確実に読み出すことができる、即ち、十分なセンス信号量を得ることを可能にする、所謂ゲインセルタイプの強誘電体型不揮発性半導体メモリを提供することにある。

【0039】

また、本発明の第6の目的は、より一層、高集積化され、しかも、ディスターブ耐性に優れ、高速動作、低消費電力を可能とする強誘電体型不揮発性半導体メモリ及びその駆動方法を提供することにある。

【0040】

【課題を解決するための手段】

10

20

30

40

50

上記の第1～第3の目的を達成するための本発明の第1の態様に係る強誘電体型不揮発性半導体メモリは、

- (A) ピット線と、

- (B) 選択用トランジスタと、

- (C) それぞれがM個（但し、 $M \geq 2$ ）のメモリセルから構成された、N個（但し、 $N \geq 2$ ）のメモリユニットと、

- (D)  $M \times N$ 本のプレート線、

から成り、

N個のメモリユニットは、層間絶縁層を介して積層されており、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

10

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、該共通の第1の電極は、選択用トランジスタを介してピット線に接続され、

第n番目（但し、 $n = 1, 2, \dots, N$ ）のメモリユニットにおいて、第m番目（但し、 $m = 1, 2, \dots, M$ ）のメモリセルの第2の電極は、第 $[(n-1)M+m]$ 番目のプレート線に接続されていることを特徴とする。

#### 【0041】

上記の第1～第3の目的を達成するための本発明の第2の態様に係る強誘電体型不揮発性半導体メモリは、選択用トランジスタの構成、プレート線の構成が、本発明の第1の態様に係る強誘電体型不揮発性半導体メモリと相違している。即ち、本発明の第2の態様に係る強誘電体型不揮発性半導体メモリは、

20

- (A) ピット線と、

- (B) N個（但し、 $N \geq 2$ ）の選択用トランジスタと、

- (C) それぞれがM個（但し、 $M \geq 2$ ）のメモリセルから構成された、N個のメモリユニットと、

- (D) M本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、

第n番目（但し、 $n = 1, 2, \dots, N$ ）のメモリユニットにおける共通の第1の電極は、第n番目の選択用トランジスタを介してピット線に接続され、

30

第n番目のメモリユニットにおいて、第m番目（但し、 $m = 1, 2, \dots, M$ ）のメモリセルの第2の電極は、メモリユニット間で共通とされた第m番目のプレート線に接続されていることを特徴とする。

#### 【0042】

尚、第2の態様に係る強誘電体型不揮発性半導体メモリの好ましい形態においては、N個のメモリユニットは層間絶縁層を介して積層されていることが望ましい。

#### 【0043】

上記の第1～第3の目的を達成するための本発明の第3の態様に係る強誘電体型不揮発性半導体メモリは、第2の電極の構成が、本発明の第2の態様に係る強誘電体型不揮発性半導体メモリと相違している。即ち、本発明の第3の態様に係る強誘電体型不揮発性半導体メモリは、

40

- (A) ピット線と、

- (B)  $2N$ 個（但し、 $N \geq 1$ ）の選択用トランジスタと、

- (C) それぞれがM個（但し、 $M \geq 2$ ）のメモリセルから構成された、 $2N$ 個のメモリユニットと、

- (D) M本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、

第 $(2n-1)$ 番目（但し、 $n = 1, 2, \dots, N$ ）のメモリユニットにおける共通の第1

50

の電極は、第(2n-1)番目の選択用トランジスタを介してビット線に接続され、第2n番目のメモリユニットにおける共通の第1の電極は、第2n番目の選択用トランジスタを介してビット線に接続され、

第(2n-1)番目のメモリユニットを構成する第m番目(但し、m=1, 2, ..., M)のメモリセルと、第2n番目のメモリユニットを構成する第m番目のメモリセルは、第2の電極を共有しており、該共有された第m番目の第2の電極は第m番目のプレート線に接続されていることを特徴とする。

#### 【0044】

上記の第1～第3の目的を達成するための本発明の第4の態様に係る強誘電体型不揮発性半導体メモリは、

10

(A-1) 第1のビット線と、

(B-1) N個(但し、N>1)の第1の選択用トランジスタと、

(C-1) それがM個(但し、M>2)の第1のメモリセルから構成された、N個の第1のサブメモリユニットと、

(D-1) N個の第1のサブメモリユニット間において、N個の第1のサブメモリユニットのそれを構成する第1のメモリセルで共通とされたM本のプレート線、

から成る第1のメモリユニット、並びに、

(A-2) 第2のビット線と、

(B-2) N個の第2の選択用トランジスタと、

(C-2) それがM個の第2のメモリセルから構成された、N個の第2のサブメモリユニットと、

20

(D-2) N個の第2のサブメモリユニット間において、N個の第2のサブメモリユニットのそれを構成する第2のメモリセルで共通とされ、且つ、前記第1のメモリユニットを構成するM本のプレート線と共通のM本のプレート線、から成る第2のメモリユニットから構成され、

第1のサブメモリユニットは、層間絶縁層を介して、第2のサブメモリユニットと積層されており、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

第1のメモリユニットにおいて、第n番目(但し、n=1, 2, ..., N)の第1のサブメモリユニットを構成する第1のメモリセルの第1の電極は、第n番目の第1のサブメモリユニットにおいて共通であり、該共通の第1の電極は、第n番目の第1の選択用トランジスタを介して第1のビット線に接続され、第m番目(但し、m=1, 2, ..., M)の第1のメモリセルの第2の電極は共通の第m番目のプレート線に接続されており、

30

第2のメモリユニットにおいて、第n番目の第2のサブメモリユニットを構成する第2のメモリセルの第1の電極は、第n番目の第2のサブメモリユニットにおいて共通であり、該共通の第1の電極は、第n番目の第2の選択用トランジスタを介して第2のビット線に接続され、第m番目の第2のメモリセルの第2の電極は共通の第m番目のプレート線に接続されていることを特徴とする。

#### 【0045】

上記の第1～第3の目的を達成するための本発明の第5の態様に係る強誘電体型不揮発性半導体メモリは、第2の電極の構成が、本発明の第4の態様に係る強誘電体型不揮発性半導体メモリと相違している。即ち、本発明の第5の態様に係る強誘電体型不揮発性半導体メモリは、

40

(A-1) 第1のビット線と、

(B-1) N個(但し、N>1)の第1の選択用トランジスタと、

(C-1) それがM個(但し、M>2)の第1のメモリセルから構成された、N個の第1のサブメモリユニットと、

(D-1) N個の第1のサブメモリユニット間において、N個の第1のサブメモリユニットのそれを構成する第1のメモリセルで共通とされたM本のプレート線、

から成る第1のメモリユニット、並びに、

50

( A - 2 ) 第 2 のビット線と、

( B - 2 ) N 個の第 2 の選択用トランジスタと、

( C - 2 ) それぞれが M 個の第 2 のメモリセルから構成された、 N 個の第 2 のサブメモリユニットと、

( D - 2 ) N 個の第 2 のサブメモリユニット間ににおいて、 N 個の第 2 のサブメモリユニットのそれぞれを構成する第 2 のメモリセルで共通とされ、且つ、前記第 1 のメモリユニットを構成する M 本のプレート線と共に M 本のプレート線、から成る第 2 のメモリユニットから構成され、

各メモリセルは、第 1 の電極と強誘電体層と第 2 の電極とから成り、

第 1 のメモリユニットにおいて、第 n 番目 ( 但し、  $n = 1, 2 \dots N$  ) の第 1 のサブメモリユニットを構成する第 1 のメモリセルの第 1 の電極は、第 n 番目の第 1 のサブメモリユニットにおいて共通であり、該共通の第 1 の電極は、第 n 番目の第 1 の選択用トランジスタを介して第 1 のビット線に接続され、

第 2 のメモリユニットにおいて、第 n 番目の第 2 のサブメモリユニットを構成する第 2 のメモリセルの第 1 の電極は、第 n 番目の第 2 のサブメモリユニットにおいて共通であり、該共通の第 1 の電極は、第 n 番目の第 2 の選択用トランジスタを介して第 2 のビット線に接続され、

第 1 のメモリユニットにおける第 n 番目の第 1 のサブメモリユニットを構成する第 m 番目 ( 但し、  $m = 1, 2 \dots M$  ) の第 1 のメモリセルと、第 2 のメモリユニットにおける第 n 番目の第 2 のサブメモリユニットを構成する第 m 番目の第 2 のメモリセルは、第 2 の電極を共有しており、該共有された第 2 の電極は第 m 番目のプレート線に接続されていることを特徴とする。

#### 【 0046 】

本発明の本発明の第 4 の態様若しくは第 5 の態様に係る強誘電体型不揮発性半導体メモリにおいては、第 1 のビット線及び第 2 のビット線は同一のセンスアンプに接続されていることが好ましい。そして、この場合、第 n 番目の第 1 の選択用トランジスタと、第 n 番目の第 2 の選択用トランジスタとは、同一のワード線に接続されていてもよいし、異なるワード線に接続されていてもよい。強誘電体型不揮発性半導体メモリの駆動方法に依り、1 つのメモリセルに 1 ビットを記憶させることもできるし、対となったメモリセルに相補的なデータを記憶させることもできる。

#### 【 0047 】

本発明の本発明の第 1 の態様若しくは第 2 の態様に係る強誘電体型不揮発性半導体メモリにおいては、  $M^2$  を満足すればよく、実際的な M の値として、例えば、2 のべき数 ( 2, 4, 8 \dots ) を挙げることができる。また、  $N^2$  を満足すればよく、実際的な N の値として、例えば、2 のべき数 ( 2, 4, 8 \dots ) を挙げることができる。

#### 【 0048 】

また、本発明の本発明の第 3 の態様～第 5 の態様に係る強誘電体型不揮発性半導体メモリにおいては、  $M^2$  を満足すればよく、実際的な M の値として、例えば、2 のべき数 ( 2, 4, 8 \dots ) を挙げることができる。また、  $N^1$  を満足すればよく、実際的な N の値として、例えば、1 あるいは 2 のべき数 ( 2, 4, 8 \dots ) を挙げることができる。

#### 【 0049 】

本発明の第 1 の態様～第 5 の態様に係る強誘電体型不揮発性半導体メモリにおいては、複数のメモリセルに 1 つの選択用トランジスタを共有させる。そして、メモリユニットあるいはサブメモリユニットを三次元積層構造とすることにより、半導体基板表面を占有するトランジスタの数に制約されることが無くなり、従来の強誘電体型不揮発性半導体メモリに比べて飛躍的に記憶容量を増大させることができ、ビット記憶単位の実効占有面積を大幅に縮小することが可能となる。

#### 【 0050 】

本発明の第 2 の態様～第 5 の態様に係る強誘電体型不揮発性半導体メモリにおいては、更には、ロー方向のアドレス選択は選択用トランジスタとプレート線とによって構成された

10

20

30

40

50

二次元マトリクスにて行う。例えば、8個の選択用トランジスタとプレート線8本とでロードアドレスの選択単位を構成すれば、16個のデコーダ／ドライバ回路で、例えば、64ビットのメモリセルを選択することができる。従って、強誘電体型不揮発性半導体メモリの集積度が従来と同等でも、記憶容量は4倍とすることができる。また、アドレス選択における周辺回路や駆動配線数を削減することができる。

【0051】

本発明の第1の態様～第5の態様に係る強誘電体型不揮発性半導体メモリにおいては、メモリユニットあるいはサブメモリユニットを2層構成、4層構成、8層構成等の $2^p$ 層構成( $p = 1, 2, 3 \dots$ )とすることが好ましい。

【0052】

本発明の第1の態様及び第2の態様に係る強誘電体型不揮発性半導体メモリの好ましい形態においては、上方に位置するメモリユニットのメモリセルを構成する強誘電体層の結晶化温度は、下方に位置するメモリユニットのメモリセルを構成する強誘電体層の結晶化温度よりも低いことが好ましく、本発明の第3の態様に係る強誘電体型不揮発性半導体メモリにおいては、N=2の場合、上方に位置するメモリユニットの組のメモリセルを構成する強誘電体層の結晶化温度は、下方に位置するメモリユニットの組のメモリセルを構成する強誘電体層の結晶化温度よりも低いことが好ましく、本発明の第4の態様～第5の態様に係る強誘電体型不揮発性半導体メモリにおいては、上方に位置するサブメモリユニットのメモリセルを構成する強誘電体層の結晶化温度は、下方に位置するサブメモリユニットのメモリセルを構成する強誘電体層の結晶化温度よりも低いことが好ましい。

【0053】

上記の第1の目的を達成するための本発明の第6の態様に係る強誘電体型不揮発性半導体メモリは、

第1の電極と強誘電体層と第2の電極とから成るメモリセルが、層間絶縁層を介して積層されて成る強誘電体型不揮発性半導体メモリであって、

上方に位置するメモリセルを構成する強誘電体層の結晶化温度は、下方に位置するメモリセルを構成する強誘電体層の結晶化温度よりも低いことを特徴とする。

【0054】

本発明の第6の態様に係る強誘電体型不揮発性半導体メモリにおいては、メモリセルを、例えば2層構成、4層構成、8層構成等の $2^p$ 層構成( $p = 1, 2, 3 \dots$ )とすることができる。

【0055】

本発明の第6の態様、若しくは、本発明の第1の態様～第5の態様に係る強誘電体型不揮発性半導体メモリにおける好ましい態様において、メモリセルを構成する強誘電体層の結晶化温度は、例えば、X線回折装置や表面走査型電子顕微鏡を用いて調べることができる。具体的には、例えば、強誘電体材料層を形成した後、強誘電体材料層の結晶化を行うための熱処理温度を種々変えて結晶化促進のための熱処理を行い、熱処理後の強誘電体材料層のX線回折分析を行い、強誘電体材料に特有の回折パターン強度(回折ピークの高さ)を評価することによって、強誘電体層の結晶化温度を求めることができる。

【0056】

ところで、後述するキャパシタ部や、メモリユニット、サブメモリユニットが積層された構成を有する強誘電体型不揮発性半導体メモリを製造する場合、強誘電体層、あるいは、強誘電体層を構成する強誘電体薄膜の結晶化のために、熱処理(結晶化熱処理と呼ぶ)を積層されたキャパシタ部やメモリユニット、サブメモリユニットの段数だけ行わなければならない。従って、下段に位置するキャパシタ部やメモリユニット、サブメモリユニットほど、長時間の結晶化熱処理を受け、上段に位置するほど、キャパシタ部やメモリユニット、サブメモリユニットは短時間の結晶化熱処理を受けることになる。それ故、上段に位置するキャパシタ部やメモリユニット、サブメモリユニットに対して最適な結晶化熱処理を施すと、下段に位置するキャパシタ部やメモリユニット、サブメモリユニットは過度の熱負荷を受ける虞があり、下段に位置するキャパシタ部やメモリユニット、サブメモリユ

10

20

30

40

50

ニットの特性劣化が生じる虞がある。尚、多段のキャパシタ部やメモリユニット、サブメモリユニットを作製した後、一度で結晶化熱処理を行う方法も考えられるが、結晶化の際に強誘電体層に大きな体積変化が生じたり、各強誘電体層から脱ガスが生じる可能性が高く、強誘電体層にクラックや剥がれが生じるといった問題が発生し易い。

【0057】

本発明の第6の態様、若しくは、本発明の第1の態様～第5の態様に係る強誘電体型不揮発性半導体メモリにおける好ましい態様において、上方に位置するキャパシタ部やメモリユニット、サブメモリユニットを構成する強誘電体層の結晶化温度は、下方に位置するキャパシタ部やメモリユニット、サブメモリユニットを構成する強誘電体層の結晶化温度よりも低いので、積層されたキャパシタ部やメモリユニット、サブメモリユニットの段数だけ結晶化熱処理を行っても、下方に位置するキャパシタ部やメモリユニット、サブメモリユニットを構成するメモリセルの特性劣化といった問題は生じない。また、各段におけるキャパシタ部やメモリユニット、サブメモリユニットを構成するメモリセルに対して、最適な条件での結晶化熱処理を行うことができ、特性の優れた強誘電体型不揮発性半導体メモリを得ることができる。

【0058】

上記の第4の目的を達成するための本発明の第7の態様に係る強誘電体型不揮発性半導体メモリは、

強誘電体層を有するキャパシタ部を備えたメモリセルが、複数、配列されて成るメモリユニットを備え、選択されたメモリセルへのアクセス時、非選択のメモリセルにディスターブが発生する構造を有する強誘電体型不揮発性半導体メモリであって、

キャパシタ部に接続され、出力が負の温度特性を有する電源電圧回路を備えていることを特徴とする。

【0059】

尚、本発明の第7の態様に係る強誘電体型不揮発性半導体メモリに、好ましい形態を含む本発明の第1の態様～第6の態様に係る強誘電体型不揮発性半導体メモリを適用することができる。

【0060】

このように、本発明の第7の態様に係る強誘電体型不揮発性半導体メモリにあっては、キャパシタ部に接続され、出力が負の温度特性を有する電源電圧回路が備えられているので、動作温度が高くなり、抗電圧が減少しても、電源電圧回路から出力される電圧も減少する結果、 $(1/2)V_{cc}$ の値が減少し、非選択のメモリセルにおけるキャパシタ部の電荷反転を防止することができる。ここで、ディスターブとは、非選択のメモリセルのキャパシタ部の強誘電体層に対して、分極が反転する方向に、即ち、保存されていたデータが劣化若しくは破壊される方向に、電界が加わる現象を指す。

【0061】

本発明の第7の態様に係る強誘電体型不揮発性半導体メモリにおいては、キャパシタ部の一端はビット線に接続され、他端はプレート線に接続され、電源電圧回路は、ビット線に接続され、若しくは、プレート線に接続され、若しくは、ビット線及びプレート線に接続されている構成とすることができる。

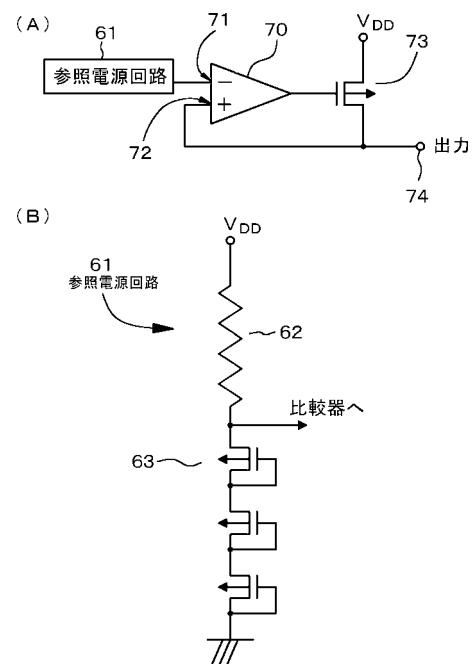

【0062】

本発明の第7の態様に係る強誘電体型不揮発性半導体メモリにあっては、電源電圧回路は、

(a) 参照電圧回路と、

(b) 参照電圧回路から出力された参照電圧が第1の入力部に入力される比較器と、

(c) 比較器からの出力電圧に従って、比較器からの出力電圧に負のフィードバックをかける回路、例えば、比較器からの出力電圧がゲート部に入力され、ドレイン領域が比較器の第2の入力部及びキャパシタ部に接続されたPMOS型FET、から成る構成とすることが望ましいが、電源電圧回路を参照電圧回路のみから構成することも可能である。尚、PMOS型FETのドレイン領域がキャパシタ部に接続されている

10

20

30

40

50

とは、具体的には、ビット線に接続され、あるいは又、プレート線に接続され、あるいは又、ビット線及びプレート線に接続されていることを意味する。

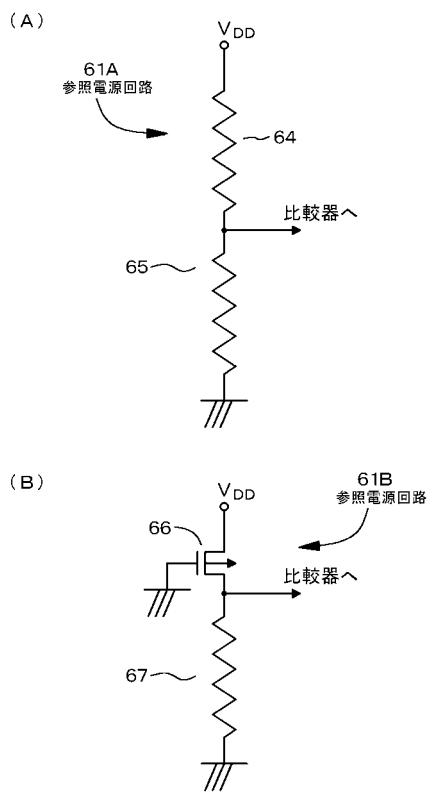

【0063】

ここで、参照電圧回路は、一端が電源に接続された第1の抵抗素子と、一端が第1の抵抗素子の他端に接続され、他端が接地された第2の抵抗素子から成り、第1の抵抗素子と第2の抵抗素子との接続部から参照電圧が outputされる構成とすることが、回路の簡素化の観点から好ましい。

【0064】

そして、この場合、第1の抵抗素子及び第2の抵抗素子は負の温度特性を有し（即ち、温度が上昇するに従い、抵抗値が減少し）、第2の抵抗素子の抵抗値の温度変化量の絶対値は、第1の抵抗素子の抵抗値の温度変化量の絶対値よりも大きい構成とすることができます。ここで、抵抗値の温度変化量の絶対値とは、温度  $t_1$  °C における電気抵抗値を  $r_1$ 、温度  $t_2$  °C ( $t_2 > t_1$ ) における電気抵抗値を  $r_2$  としたとき、 $|r_2 - r_1|$  で表すことができる。具体的には、第1の抵抗素子及び第2の抵抗素子を抵抗体から構成することができます。より具体的には、例えば、第1の抵抗素子は不純物がドープされた半導体層から成り、第2の抵抗素子は、第1の抵抗素子を構成する半導体層の不純物濃度よりも低い濃度の不純物がドープされた半導体層から成る構成；第1の抵抗素子は Si - Ge 半導体層から成り、第2の抵抗素子は Si 半導体層から成る構成とすることができます。但し、第1の抵抗素子及び第2の抵抗素子は、これらの構成に限定するものではない。尚、第1の抵抗素子及び第2の抵抗素子は正の温度特性を有し（即ち、温度が上昇するに従い、抵抗値が増加し）、第2の抵抗素子の抵抗値の温度変化量の絶対値は、第1の抵抗素子の抵抗値の温度変化量の絶対値よりも小さい構成とすることもできる。

【0065】

あるいは又、この場合、第1の抵抗素子は抵抗体から成り、第2の抵抗素子は、ドレイン部とゲート部が短絡された少なくとも1つのPMOS型FET（場合によっては、かかるPMOS型FETを直列に接続した構造）から成る構成することもできる。

【0066】

あるいは又、この場合、第1の抵抗素子は正の温度特性を有し（即ち、温度が上昇するに従い、抵抗値が増加し）、第2の抵抗素子は負の温度特性を有する（即ち、温度が上昇するに従い、抵抗値が減少する）構成とすることができます。具体的には、第1の抵抗素子はゲート部が接地されたPMOS型FETから成り、第2の抵抗素子は抵抗体から成る構成とすることができますが、これらの構成に限定するものではない。

【0067】

上記の第4の目的を達成するための本発明の第8の態様に係る強誘電体型不揮発性半導体メモリは、

強誘電体層を有するキャパシタ部を備えたメモリセルが、複数、配列されて成るメモリユニットを備え、選択されたメモリセルへのアクセス時、非選択のメモリセルにディスタークタが発生する構造を有する強誘電体型不揮発性半導体メモリであって、

キャパシタ部の一端はビット線に接続され、他端はプレート線に接続され、

ビット線に接続された、クランプ電圧が負の温度特性を有するクランプ回路を備えていることを特徴とする。

【0068】

尚、本発明の第8の態様に係る強誘電体型不揮発性半導体メモリに、好ましい形態を含む本発明の第1の態様～第6の態様に係る強誘電体型不揮発性半導体メモリを適用することができる。また、本発明の第7の態様に係る強誘電体型不揮発性半導体メモリと本発明の第8の態様に係る強誘電体型不揮発性半導体メモリとを組み合わせることもできる。

【0069】

このように、本発明の第8の態様に係る強誘電体型不揮発性半導体メモリにあっては、クランプ電圧が負の温度特性を有する（即ち、温度が上昇するに従い、クランプ電圧が減少、あるいは低下する）クランプ回路がビット線に接続されているので、動作温度が高くな

10

20

30

40

50

り、抗電圧が減少しても、ピット線の電圧（電位）が低い電圧（電位）にクランプされる結果、非選択のキャパシタ部の電荷反転を防止することができる。

【0070】

本発明の第8の態様に係る強誘電体型不揮発性半導体メモリにおいては、プレート線に接続された電源電圧回路を更に備え、該電源電圧回路の出力は負の温度特性を有する構成とすることができる。プレート線に接続された電源電圧回路の構成としては、本発明の第7の態様に係る強誘電体型不揮発性半導体メモリにおけるプレート線に接続された電源電圧回路の構成と同様とすることができる。

【0071】

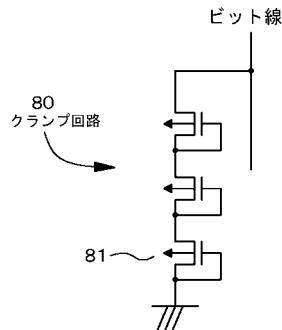

本発明の第8の態様に係る強誘電体型不揮発性半導体メモリにあっては、クランプ回路は

、ドレイン部とゲート部が短絡されたP M O S型F E Tを直列に接続した構造を有する構成とすることが望ましいが、これに限定するものではない。

【0072】

上記の第5の目的を達成するための本発明の第9の態様に係る強誘電体型不揮発性半導体メモリは、

(A) ピット線と、

(B) 選択用トランジスタと、

(C) M個（但し、M>2）のメモリセルから構成されたメモリユニットと、

(D) M本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

メモリユニットにおいて、メモリセルの第1の電極は共通であり、該共通の第1の電極は、選択用トランジスタを介してピット線に接続され、各メモリセルを構成する第2の電極はプレート線に接続されている強誘電体型不揮発性半導体メモリであって、

(E) 共通の第1の電極の電位変化を検出し、該検出結果をピット線に電流又は電圧として伝達する信号検出回路、

を備えていることを特徴とする。

【0073】

本発明の第9の態様に係る強誘電体型不揮発性半導体メモリにおいては、選択用トランジスタ及び信号検出回路は半導体基板上に設けられており、メモリユニットは半導体基板上に形成された絶縁層上に設けられていることが好ましい。尚、メモリユニットの数は1であっても、2以上であってもよい。後者の場合、複数のメモリユニットが、層間絶縁層を介して積層されている構成とすることが好ましい。

【0074】

上記の第5の目的を達成するための本発明の第10の態様に係る強誘電体型不揮発性半導体メモリは、所謂ゲインセルタイプの強誘電体型不揮発性半導体メモリであり、

(A) ピット線と、

(B) 書込用トランジスタと、

(C) M個（但し、M>2）のメモリセルから構成されたメモリユニットと、

(D) M本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

メモリユニットにおいて、メモリセルの第1の電極は共通であり、該共通の第1の電極は、書込用トランジスタを介してピット線に接続され、各メモリセルを構成する第2の電極はプレート線に接続されている強誘電体型不揮発性半導体メモリであって、

(E) 検出用トランジスタ、及び、

(F) 読出用トランジスタ、

を更に備え、

検出用トランジスタの一端は所定の電位を有する配線に接続され、他端は読出用トランジスタを介してピット線に接続され、

10

20

30

40

50

各メモリセルに記憶されたデータの読み出し時、読み出用トランジスタが導通状態とされ、各メモリセルに記憶されたデータに基づき共通の第1の電極に生じた電位により、検出用トランジスタの動作が制御されることを特徴とする。

【0075】

上記の第5の目的を達成するための本発明の第11の態様に係る強誘電体型不揮発性半導体メモリは、所謂ゲインセルタイプの強誘電体型不揮発性半導体メモリであり、

(A) ビット線と、

(B) 書込用トランジスタと、

(C) それぞれがM個(但し、M>2)のメモリセルから構成された、N個(但し、N>2)のメモリユニットと、

(D) N個の選択用トランジスタと、

(E) N個のメモリユニットのそれぞれを構成するメモリセルで共通とされたM本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

第n番目(n=1, 2, ..., N)のメモリユニットにおいて、メモリセルの第1の電極は共通であり、該共通の第1の電極は、第n番目の選択用トランジスタ及び書込用トランジスタを介してビット線に接続され、(m=1, 2, ..., M)メモリセルを構成する第2の電極は共通の第m番目のプレート線に接続されている強誘電体型不揮発性半導体メモリであって、

(F) 検出用トランジスタ、及び、

(G) 読出用トランジスタ、

を更に備え、

検出用トランジスタの一端は所定の電位を有する配線に接続され、他端は読み出用トランジスタを介してビット線に接続され、

第n番目のメモリユニットを構成する各メモリセルに記憶されたデータの読み出し時、第n番目の選択用トランジスタ及び読み出用トランジスタが導通状態とされ、各メモリセルに記憶されたデータに基づき共通の第1の電極に生じた電位により、検出用トランジスタの動作が制御されることを特徴とする。

【0076】

本発明の第11の態様に係る強誘電体型不揮発性半導体メモリにおいては、N>2を満足すればよく、実際的なNの値として、例えば2のべき数(2, 4, 8, ...)を挙げることができる。

【0077】

本発明の第9の態様、第10の態様若しくは第11の態様に係る強誘電体型不揮発性半導体メモリにおいては、Mの値は、2≤M≤128、好ましくは、4≤M≤32を満足することが望ましい。

【0078】

本発明の第10の態様若しくは第11の態様に係る強誘電体型不揮発性半導体メモリにおいては、例えば、シリコン半導体基板に各種のトランジスタを作製し、かかる各種のトランジスタ上に絶縁層を形成し、この絶縁層上にメモリセルを形成することが、セル面積の縮小化といった観点から好ましい。場合によっては、複数のメモリユニットを層間絶縁層を介して積層してもよい。即ち、本発明の第10の態様あるいは第11の態様に係る強誘電体型不揮発性半導体メモリに、更には、メモリユニットの数が2以上である本発明の第9の態様に係る強誘電体型不揮発性半導体メモリに、好ましい形態を含む本発明の第1の態様～第6の態様に係る強誘電体型不揮発性半導体メモリを適用することができる。ここで、絶縁層あるいは層間絶縁層を構成する材料として、酸化シリコン(SiO<sub>2</sub>)、窒化シリコン(SiN)、SiON、SOG、NSG、BPSG、PSG、BSG及びLTOを例示することができる。更には、本発明の第9の態様、第10の態様若しくは第11の態様に係る強誘電体型不揮発性半導体メモリと、本発明の第7の態様若しくは第8の態様

10

20

30

40

50

に係る強誘電体型不揮発性半導体メモリとを組み合わせることもできる。

【0079】

本発明の第10の態様に係る強誘電体型不揮発性半導体メモリの具体的な構成として、各種のトランジスタをFETから構成する場合、書込用トランジスタの一方のソース／ドレイン領域はビット線に接続され、他方のソース／ドレイン領域は共通の第1の電極に接続され、検出用トランジスタの一方のソース／ドレイン領域は、所定の電位を有する配線（例えば、不純物層から構成された電源線）に接続され、他方のソース／ドレイン領域は、読出用トランジスタの一方のソース／ドレイン領域に接続され、読出用トランジスタの他方のソース／ドレイン領域はビット線に接続され、更に、共通の第1の電極（あるいは、書込用トランジスタの他方のソース／ドレイン領域）は、検出用トランジスタのゲート電極に接続されている構成とすることができます。尚、検出用トランジスタの他方のソース／ドレイン領域が読出用トランジスタの一方のソース／ドレイン領域に接続された構成には、検出用トランジスタの他方のソース／ドレイン領域と読出用トランジスタの一方のソース／ドレイン領域とが1つのソース／ドレイン領域を占める構成が含まれる。

【0080】

本発明の第11の態様に係る強誘電体型不揮発性半導体メモリの具体的な構成として、各種のトランジスタをFETから構成する場合、書込用トランジスタの一方のソース／ドレイン領域はビット線に接続され、他方のソース／ドレイン領域は、N個の選択用トランジスタのそれぞれの一方のソース／ドレイン領域に接続され、第n番目の選択用トランジスタの他方のソース／ドレイン領域は、第n番目のメモリユニットを構成する共通の第1の電極に接続され、検出用トランジスタの一方のソース／ドレイン領域は、所定の電位を有する配線に接続され、他方のソース／ドレイン領域は、読出用トランジスタの一方のソース／ドレイン領域に接続され、読出用トランジスタの他方のソース／ドレイン領域はビット線に接続され、更に、各メモリユニットを構成する共通の第1の電極（あるいは、書込用トランジスタの他方のソース／ドレイン領域）は、検出用トランジスタのゲート電極に接続されている構成とすることができます。尚、検出用トランジスタの他方のソース／ドレイン領域が読出用トランジスタの一方のソース／ドレイン領域に接続された構成には、検出用トランジスタの他方のソース／ドレイン領域と読出用トランジスタの一方のソース／ドレイン領域とが1つのソース／ドレイン領域を占める構成が含まれる。

【0081】

本発明の第9の態様に係る強誘電体型不揮発性半導体メモリにおいては、1つの選択用トランジスタと信号検出回路とに対して、M個のメモリセルが設けられているが故に、1ビット当たりのセル面積を減少させることができる。また、本発明の第10の態様に係る強誘電体型不揮発性半導体メモリにおいては、1つの書込用トランジスタと1つの検出用トランジスタと1つの読出用トランジスタに対して、M個のメモリセルが設けられているが故に、1ビット当たりのセル面積を減少させることができる。更には、本発明の第11の態様に係る強誘電体型不揮発性半導体メモリにおいては、1つの書込用トランジスタと1つの検出用トランジスタと1つの読出用トランジスタとN個の選択用トランジスタに対して、M×N個のメモリセルが設けられているが故に、1ビット当たりのセル面積を一層減少させることができる。しかも、共通の第1の電極の電位変化を信号検出回路によって検出し、あるいは又、各メモリセルに記憶されたデータに基づき共通の第1の電極に生じた電位により検出用トランジスタの動作が制御されるが、第1の電極はM個のメモリセルに共通であるが故に、第1の電極に一種の追加の負荷容量が付加された状態となっている。その結果、データの読み出し時、プレート線に電圧を印加した際、第1の電極の電位上昇を抑制することができ、第1の電極と第2の電極との間に十分な電位差が生じる結果、強誘電体層に確実に分極反転が発生する。

【0082】

上記の第6の目的を達成するための本発明の第1の態様に係る強誘電体型不揮発性半導体メモリの駆動方法は、

（A-1）第1のビット線と、

10

20

30

40

50

( B - 1 ) N 個 ( 但し、 N 1 ) の第 1 の選択用トランジスタと、

( C - 1 ) それぞれが M 個 ( 但し、 M 2 ) の第 1 のメモリセルから構成された、 N 個の第 1 のサブメモリユニットと、

( D - 1 ) N 個の第 1 のサブメモリユニット間ににおいて、 N 個の第 1 のサブメモリユニットのそれぞれを構成する第 1 のメモリセルで共通とされた M 本のプレート線、から成る第 1 のメモリユニット、並びに、

( A - 2 ) 第 2 のビット線と、

( B - 2 ) N 個の第 2 の選択用トランジスタと、

( C - 2 ) それぞれが M 個の第 2 のメモリセルから構成された、 N 個の第 2 のサブメモリユニットと、

( D - 2 ) N 個の第 2 のサブメモリユニット間ににおいて、 N 個の第 2 のサブメモリユニットのそれぞれを構成する第 2 のメモリセルで共通とされ、且つ、前記第 1 のメモリユニットを構成する M 本のプレート線と共に M 本のプレート線、から成る第 2 のメモリユニットから構成され、

各メモリセルは、第 1 の電極と強誘電体層と第 2 の電極とから成り、

第 1 のメモリユニットにおいて、第 n 番目 ( 但し、 n = 1 , 2 ··· N ) の第 1 のサブメモリユニットを構成する第 1 のメモリセルの第 1 の電極は、第 n 番目の第 1 のサブメモリユニットにおいて共通であり、該共通の第 1 の電極は、第 n 番目の第 1 の選択用トランジスタを介して第 1 のビット線に接続され、第 m 番目 ( 但し、 m = 1 , 2 ··· M ) の第 1 のメモリセルの第 2 の電極は共通の第 m 番目のプレート線に接続されており、

第 2 のメモリユニットにおいて、第 n 番目の第 2 のサブメモリユニットを構成する第 2 のメモリセルの第 1 の電極は、第 n 番目の第 2 のサブメモリユニットにおいて共通であり、該共通の第 1 の電極は、第 n 番目の第 2 の選択用トランジスタを介して第 2 のビット線に接続され、第 m 番目の第 2 のメモリセルの第 2 の電極は共通の第 m 番目のプレート線に接続されている強誘電体型不揮発性半導体メモリの駆動方法であって、

プレート線を共有した第 1 のサブメモリユニットにおける第 1 のメモリセル及び第 2 のサブメモリユニットにおける第 2 のメモリセルに記憶されたデータの読み出し及びデータの再書き込みを、1 回のプレート線の電位立ち上げ及び電位立ち下げにて行うことを特徴とする。

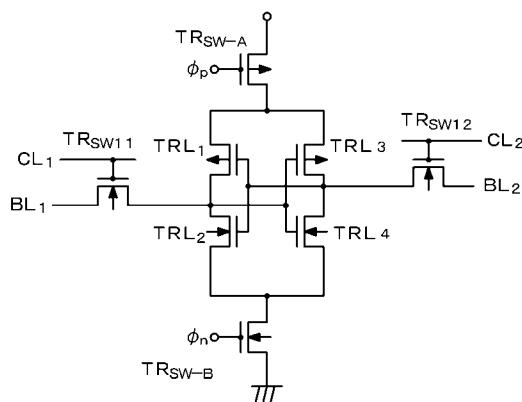

### 【 0083 】

本発明の第 1 の態様に係る強誘電体型不揮発性半導体メモリの駆動方法 ( 以下、本発明の第 1 の態様に係る駆動方法と略称する ) においては、

第 1 のビット線と第 2 のビット線との間に、第 1 のメモリセル及び第 2 のメモリセルのそれぞれに記憶されたデータをラッチするための 2 N 個のラッチ回路が設けられており、

第 ( 2 n - 1 ) 番目のラッチ回路にラッチされたデータに基づき、第 n 番目の第 1 のサブメモリユニットを構成する第 1 のメモリセルへのデータの再書き込みを行い、第 2 n 番目のラッチ回路にラッチされたデータに基づき、第 n 番目の第 2 のサブメモリユニットを構成する第 2 のメモリセルへのデータの再書き込みを行う構成とすることができる。即ち、プレート線を共有した ( 即ち、対となった ) 第 n 番目の第 1 のサブメモリユニットを構成する第 1 のメモリセル及び第 n 番目の第 2 のサブメモリユニットを構成する第 2 のメモリセルのそれぞれに、1 ビットを記憶することができ、これによって、強誘電体型不揮発性半導体メモリの高集積化を図ることができる。尚、このような構成の本発明の第 1 の態様に係る駆動方法を、本発明の第 1 の構成に係る駆動方法と呼ぶ。

### 【 0084 】

本発明の第 1 の構成に係る駆動方法においては、第 1 のメモリセルに記憶されたデータの読み出しを行うとき、第 1 の選択用トランジスタをオン状態とし、第 2 の選択用トランジスタをオフ状態とし、且つ、第 2 のビット線に参照電位を印加し、第 2 のメモリセルに記憶されたデータの読み出しを行うとき、第 2 の選択用トランジスタをオン状態とし、第 1 の選択用トランジスタをオフ状態とし、且つ、第 1 のビット線に参照電位を印加する構成とすることができる。

## 【0085】

尚、本発明の第1の構成に係る駆動方法においては、選択用トランジスタがオフ状態において、プレート線を共有した第1のサブメモリユニットにおける第1のメモリセル及び第2のサブメモリユニットにおける第2のメモリセルに記憶されたデータの読み出し及びデータの再書き込みを行うために、プレート線の電位立ち上げを行い、その後、選択用トランジスタをオン状態とすることが望ましい。また、プレート線を共有した第1のサブメモリユニットにおける第1のメモリセル及び第2のサブメモリユニットにおける第2のメモリセルに記憶されたデータの読み出しを行った後、データをラッチ回路にラッチし、一旦、これらのメモリセルに2値データの一方（例えば、データ「0」）を書き込み、その後、プレート線の電位立ち下げを行い、次いで、これらのメモリセルへのデータ（例えば、データ「1」）の再書き込みを行うことが望ましい。

10

## 【0086】

あるいは又、本発明の第1の態様に係る駆動方法においては、

N 2 であり、

第1のビット線と第2のビット線との間には、第1のメモリセル及び第2のメモリセルに記憶されたデータをラッチするためのN個のラッチ回路が設けられており、

第n番目のラッチ回路にラッチされたデータに基づき、第n番目の第1のサブメモリユニットを構成する第1のメモリセル及び第n番目の第2のサブメモリユニットを構成する第2のメモリセルへのデータの再書き込みを行う構成とすることができます。即ち、プレート線を共有した（即ち、対となつた）第n番目の第1のサブメモリユニットを構成する第1のメモリセル及び第n番目の第2のサブメモリユニットを構成する第2のメモリセルに、相補的なデータ構成の1ビットを記憶することができる。尚、このような構成の本発明の第1の態様に係る駆動方法を、本発明の第2の構成に係る駆動方法と呼ぶ。

20

## 【0087】

本発明の第2の構成に係る駆動方法においては、第n番目の第1のサブメモリユニットを構成する第m番目（但し、m = 1, 2, ..., M）の第1のメモリセルと、第n番目の第2のサブメモリユニットを構成する第m番目の第2のメモリセルとは、対となって相補的なデータを記憶する構成とすることができます。

## 【0088】

尚、本発明の第2の構成に係る駆動方法においても、選択用トランジスタがオフ状態において、プレート線を共有した第1のサブメモリユニットにおける第1のメモリセル及び第2のサブメモリユニットにおける第2のメモリセルに記憶されたデータの読み出し及びデータの再書き込みを行うために、プレート線の電位立ち上げを行い、その後、選択用トランジスタをオン状態とすることが望ましい。また、プレート線を共有した第1のサブメモリユニットにおける第1のメモリセル及び第2のサブメモリユニットにおける第2のメモリセルに記憶されたデータの読み出しを行った後、データをラッチ回路にラッチし、一旦、これらのメモリセルに2値データの一方（例えば、データ「0」）を書き込み、その後、プレート線の電位立ち下げを行い、次いで、これらのメモリセルへのデータ（例えば、データ「1」）の再書き込みを行うことが望ましい。

30

## 【0089】

上記の第6の目的を達成するための本発明の第12の態様に係る強誘電体型不揮発性半導体メモリは、

（A-1）第1のビット線と、

（B-1）N個（但し、N 1）の第1の選択用トランジスタと、

（C-1）それがM個（但し、M 2）の第1のメモリセルから構成された、N個の第1のサブメモリユニットと、

（D-1）N個の第1のサブメモリユニット間ににおいて、N個の第1のサブメモリユニットのそれぞれを構成する第1のメモリセルで共通とされたM本のプレート線、

から成る第1のメモリユニット、並びに、

（A-2）第2のビット線と、

40

50

( B - 2 ) N 個の第 2 の選択用トランジスタと、

( C - 2 ) それぞれが M 個の第 2 のメモリセルから構成された、 N 個の第 2 のサブメモリユニットと、

( D - 2 ) N 個の第 2 のサブメモリユニット間ににおいて、 N 個の第 2 のサブメモリユニットのそれぞれを構成する第 2 のメモリセルで共通とされ、且つ、前記第 1 のメモリユニットを構成する M 本のプレート線と共通の M 本のプレート線、から成る第 2 のメモリユニットから構成され、

各メモリセルは、第 1 の電極と強誘電体層と第 2 の電極とから成り、

第 1 のメモリユニットにおいて、第 n 番目（但し、  $n = 1, 2 \dots N$  ）の第 1 のサブメモリユニットを構成する第 1 のメモリセルの第 1 の電極は、第 n 番目の第 1 のサブメモリユニットにおいて共通であり、該共通の第 1 の電極は、第 n 番目の第 1 の選択用トランジスタを介して第 1 のビット線に接続され、第 m 番目（但し、  $m = 1, 2 \dots M$  ）の第 1 のメモリセルの第 2 の電極は共通の第 m 番目のプレート線に接続されており、

第 2 のメモリユニットにおいて、第 n 番目の第 2 のサブメモリユニットを構成する第 2 のメモリセルの第 1 の電極は、第 n 番目の第 2 のサブメモリユニットにおいて共通であり、該共通の第 1 の電極は、第 n 番目の第 2 の選択用トランジスタを介して第 2 のビット線に接続され、第 m 番目の第 2 のメモリセルの第 2 の電極は共通の第 m 番目のプレート線に接続されている強誘電体型不揮発性半導体メモリであって、

更に、第 1 のビット線と第 2 のビット線との間には、第 1 のメモリセル及び第 2 のメモリセルに記憶されたデータをラッチするための P 個のラッチ回路が設けられていることを特徴とする。

#### 【 0090 】

本発明の第 1 2 の態様に係る強誘電体型不揮発性半導体メモリにおいては、  $N = 1$  であり、  $P = 2 N$  を満たす構成とすることができます。尚、このような構成の本発明の強誘電体型不揮発性半導体メモリを、本発明の第 1 2 A の態様に係る強誘電体型不揮発性半導体メモリと呼ぶ。このような構成とすることで、本発明の第 1 の構成に係る駆動方法を実行することができる。尚、本発明の第 1 2 A の態様に係る強誘電体型不揮発性半導体メモリにおいては、第 ( 2 n - 1 ) 番目のラッチ回路は、第 n 番目の第 1 のサブメモリユニットを構成する第 1 のメモリセルに記憶されたデータをラッチし、第 2 n 番目のラッチ回路は、第 n 番目の第 2 のサブメモリユニットを構成する第 2 のメモリセルに記憶されたデータをラッチすることが好ましい。

#### 【 0091 】

あるいは又、本発明の第 1 2 の態様に係る強誘電体型不揮発性半導体メモリにおいては、  $N = 2$  であり、  $P = N$  を満たす構成とすることができます。尚、このような構成の本発明の強誘電体型不揮発性半導体メモリを、本発明の第 1 2 B の態様に係る強誘電体型不揮発性半導体メモリと呼ぶ。このような構成とすることで、本発明の第 2 の構成に係る駆動方法を実行することができる。尚、本発明の第 1 2 B の態様に係る強誘電体型不揮発性半導体メモリにおいては、第 n 番目のラッチ回路は、第 n 番目の第 1 のサブメモリユニットを構成する第 1 のメモリセル及び第 n 番目の第 2 のサブメモリユニットを構成する第 2 のメモリセルに記憶されたデータをラッチすることが好ましい。

#### 【 0092 】

上記の第 6 の目的を達成するための本発明の第 2 の態様に係る強誘電体型不揮発性半導体メモリの駆動方法（以下、本発明の第 2 の態様に係る駆動方法と呼ぶ場合がある）は、

( A ) ビット線と、

( B ) N 個（但し、  $N = 2$  ）の選択用トランジスタと、

( C ) それぞれが M 個（但し、  $M = 2$  ）のメモリセルから構成された、 N 個のメモリユニットと、

( D ) M 本のプレート線、

から成り、

各メモリセルは、第 1 の電極と強誘電体層と第 2 の電極とから成り、

10

20

30

40

50

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、

第n番目(但し、 $n = 1, 2 \dots N$ )のメモリユニットにおける共通の第1の電極は、

第n番目の選択用トランジスタを介してビット線に接続され、

第n番目のメモリユニットにおいて、第m番目(但し、 $m = 1, 2 \dots M$ )のメモリセルの第2の電極は、メモリユニット間で共通とされた第m番目のプレート線に接続されている強誘電体型不揮発性半導体メモリの駆動方法であって、

N個のメモリユニットにおいて、プレート線を共有したメモリセルに記憶されたデータの読み出し及びデータの再書き込みを、1回のプレート線の電位立ち上げ及び電位立ち下げにて行うことを特徴とする。

## 【0093】

10

上記の第6の目的を達成するための本発明の第3の態様に係る強誘電体型不揮発性半導体メモリの駆動方法(以下、本発明の第3の態様に係る駆動方法と呼ぶ場合がある)は、

(A)ビット線と、

(B)N個(但し、 $N \geq 2$ )の選択用トランジスタと、

(C)それぞれがM個(但し、 $M \geq 2$ )のメモリセルから構成された、N個のメモリユニットと、

(D)M本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、

20

第n番目(但し、 $n = 1, 2 \dots N$ )のメモリユニットにおける共通の第1の電極は、

第n番目の選択用トランジスタを介してビット線に接続され、

第n番目のメモリユニットにおいて、第m番目(但し、 $m = 1, 2 \dots M$ )のメモリセルの第2の電極は、メモリユニット間で共通とされた第m番目のプレート線に接続されている強誘電体型不揮発性半導体メモリの駆動方法であって、

N個のメモリユニットにおいて、プレート線を共有したメモリセルに記憶されたデータの読み出しを、先ず、該プレート線にパルスを与え、次いで、N個の選択用トランジスタを順次選択して行うことを特徴とする。

## 【0094】

30

本発明の第2の態様若しくは第3の態様に係る駆動方法にあっては、N個のメモリユニットは層間絶縁層を介して積層されていることが好ましい。そして、この場合、好ましい形態を含む本発明の第6の態様に係る強誘電体型不揮発性半導体メモリを適用することができる。

## 【0095】

上記の第6の目的を達成するための本発明の第13の態様に係る強誘電体型不揮発性半導体メモリは、

(A)ビット線と、

(B)N個(但し、 $N \geq 2$ )の選択用トランジスタと、

(C)それぞれがM個(但し、 $M \geq 2$ )のメモリセルから構成された、N個のメモリユニットと、

(D)M本のプレート線、

から成り、

各メモリセルは、第1の電極と強誘電体層と第2の電極とから成り、

各メモリユニットにおいて、メモリセルの第1の電極は共通であり、

第n番目(但し、 $n = 1, 2 \dots N$ )のメモリユニットにおける共通の第1の電極は、

第n番目の選択用トランジスタを介してビット線に接続され、

第n番目のメモリユニットにおいて、第m番目(但し、 $m = 1, 2 \dots M$ )のメモリセルの第2の電極は、メモリユニット間で共通とされた第m番目のプレート線に接続されている強誘電体型不揮発性半導体メモリであって、

更に、ビット線には、メモリセルに記憶されたデータをラッチするため、少なくともN個

40

50

のラッチ回路が接続されていることを特徴とする。

【0096】

本発明の第13の態様に係る強誘電体型不揮発性半導体メモリにあっては、第n番目(但し、 $n = 1, 2 \cdots N$ )のラッチ回路は、第n番目のメモリユニットのそれぞれを構成するメモリセルに記憶されたデータをラッチすることが好ましい。また、N個のメモリユニットは層間絶縁層を介して積層されていることが望ましい。

【0097】

尚、本発明の第12の態様若しくは第13の態様の好ましい形態に係る強誘電体型不揮発性半導体メモリに、好ましい形態を含む本発明の第1の態様～第6の態様に係る強誘電体型不揮発性半導体メモリを適宜適用することができる。

10

【0098】

即ち、例えば、本発明の第12Aの態様に係る強誘電体型不揮発性半導体メモリにおいては、一層の高集積化を達成するために、強誘電体型不揮発性半導体メモリを構成する第1のメモリユニットと、この強誘電体型不揮発性半導体メモリと第1のピット線の延在する方向に隣接した強誘電体型不揮発性半導体メモリを構成する第1のメモリユニットとを層間絶縁層を介して積層し、強誘電体型不揮発性半導体メモリを構成する第2のメモリユニットと、この強誘電体型不揮発性半導体メモリと第2のピット線の延在する方向に隣接した強誘電体型不揮発性半導体メモリを構成する第2のメモリユニットとを層間絶縁層を介して積層した構成とができる。

【0099】

20

また、例えば、本発明の第12Bの態様に係る強誘電体型不揮発性半導体メモリにおいては、一層の高集積化を達成するために、第1のメモリユニットを構成する第1のサブメモリユニットのそれぞれは層間絶縁層を介して積層されており、第2のメモリユニットを構成する第2のサブメモリユニットのそれぞれは層間絶縁層を介して積層されている構成とができる。あるいは又、第1のメモリユニットを構成する第1のサブメモリユニットと第2のメモリユニットを構成する第2のサブメモリユニットとは、層間絶縁層を介して積層されている構成とすることもできる。

【0100】

あるいは又、本発明の第12の態様若しくは第13の態様に係る強誘電体型不揮発性半導体メモリに、好ましい形態を含む本発明の第7の態様～第11の態様に係る強誘電体型不揮発性半導体メモリを適用することもできる。

30

【0101】

本発明の第12の態様若しくは第13の態様に係る強誘電体型不揮発性半導体メモリあるいは又、本発明の第2の態様若しくは第3の態様に係る駆動方法において、 $M \geq 2$ を満足すればよく、実際的なMの値として、例えば、2のべき数(2, 4, 8, ...)を挙げることができる。また、本発明の第12Aの態様に係る強誘電体型不揮発性半導体メモリあるいは第1の構成に係る駆動方法では、 $N \geq 1$ を満足すればよく、実際的なNの値として、例えば、1、及び、2のべき数(2, 4, 8, ...)を挙げることができる。また、本発明の第12Bの態様に係る強誘電体型不揮発性半導体メモリあるいは第2の構成に係る駆動方法では、 $N \geq 2$ を満足すればよく、実際的なNの値として、例えば2のべき数(2, 4, 8, ...)を挙げることができる。

40

【0102】

本発明の第12の態様若しくは第13の態様に係る強誘電体型不揮発性半導体メモリあるいは強誘電体型不揮発性半導体メモリの駆動方法におけるラッチ回路は、周知のラッチ回路から構成すればよい。

【0103】

本発明の第12の態様に係る強誘電体型不揮発性半導体メモリあるいは本発明の第1の態様に係る駆動方法においては、第1及び第2の選択用トランジスタに複数の第1及び第2のメモリセルが並列に接続されており、しかも、第1及び第2のメモリセルにおいてブレート線が共通化されているので、強誘電体型不揮発性半導体メモリの高集積化を達成する

50

ことができる。しかも、本発明の第1の態様に係る駆動方法においては、プレート線を共有した第1のメモリセル及び第2のメモリセルに記憶されたデータの読み出し及びデータの再書き込みを1回のプレート線の電位立ち上げ及び電位立ち下げにて行うので、各メモリセルがディスターブを受ける回数を少なくすることができるし、高速動作、低消費電力が可能となる。また、本発明の第12の態様若しくは第13の態様に係る強誘電体型不揮発性半導体メモリにおいては、ラッチ回路を備えているので、メモリセルへのデータの再書き込み、あるいは又、第1及び第2のメモリセルへのデータの再書き込みを確実に行うことができる。

【0104】

本発明の第2の態様に係る駆動方法においては、N個のメモリユニットにおいて、プレート線を共有したメモリセルに記憶されたデータの読み出し及びデータの再書き込みを、1回のプレート線の電位立ち上げ及び電位立ち下げにて行うので、各メモリセルがディスターブを受ける回数を少なくすることができるし、高速動作、低消費電力が可能となる。また、本発明の第3の態様に係る駆動方法においては、N個のメモリユニットにおいて、プレート線を共有したメモリセルに記憶されたデータの読み出しを、先ず、該プレート線にパルスを与え、次いで、N個の選択用トランジスタを順次選択して行うので、各メモリセルがディスターブを受ける回数を少なくすることができるし、高速動作、低消費電力が可能となる。

【0105】

本発明の強誘電体型不揮発性半導体メモリにおける強誘電体層を構成する材料として、ビスマス層状化合物、より具体的には、Bi系層状構造ペロブスカイト型の強誘電体材料を挙げることができる。Bi系層状構造ペロブスカイト型の強誘電体材料は、所謂不定比化合物に属し、金属元素、アニオン(O等)元素の両サイトにおける組成ずれに対する寛容性がある。また、化学量論的組成からやや外れたところで最適な電気的特性を示すことも珍しくない。Bi系層状構造ペロブスカイト型の強誘電体材料は、例えば、一般式( $Bi_2O_2$ )<sup>2+</sup>( $A_{m-1}B_mO_{3m+1}$ )<sup>2-</sup>で表すことができる。ここで、「A」は、Bi、Pb、Ba、Sr、Ca、Na、K、Cd等の金属から構成された群から選択された1種類の金属を表し、「B」は、Ti、Nb、Ta、W、Mo、Fe、Co、Crから成る群から選択された1種類、若しくは複数種の任意の比率による組み合わせを表す。また、mは1以上の整数である。

【0106】

あるいは又、強誘電体層を構成する材料は、

(但し、 $0.9 \leq X \leq 1.0, 0.7 \leq Y \leq 1.0, 0 \leq Z \leq 1.0, 8.7 \leq d \leq 9.3$ )で表される結晶相を主たる結晶相として含んでいることが好ましい。あるいは又、強誘電体層を構成する材料は、

(但し、 $X + Y = 3, 0.7 \leq Y \leq 1.3, 8.7 \leq d \leq 9.3$ )で表される結晶相を主たる結晶相として含んでいることが好ましい。これらの場合、式(1)若しくは式(2)で表される結晶相を主たる結晶相として85%以上含んでいることが一層好ましい。尚、式(1)中、( $Bi_x, Sr_{1-x}$ )の意味は、結晶構造における本来Biが占めるサイトをSrが占め、このときのBiとSrの割合が $X : (1 - X)$ であることを意味する。また、( $Sr_Y, Bi_{1-Y}$ )の意味は、結晶構造における本来Srが占めるサイトをBiが占め、このときのSrとBiの割合が $Y : (1 - Y)$ であることを意味する。式(1)若しくは式(2)で表される結晶相を主たる結晶相として含む強誘電体層を構成する材料には、Biの酸化物、TaやNbの酸化物、Bi、TaやNbの複合酸化物が若干含まれている場合もあり得る。

【0107】

あるいは又、強誘電体層を構成する材料は、

10

20

30

40

50

(但し、1.7 X 2.5、0.6 Y 1.2、0 Z 1.0、8.0 d 10

.0)で表される結晶相を含んでいてもよい。尚、「(Sr, Ca, Ba)」は、Sr、Ca及びBaから構成された群から選択された1種類の元素を意味する。これらの各式で表される強誘電体層を構成する材料の組成を化学量論的組成で表せば、例えば、Bi<sub>2</sub>SrTa<sub>2</sub>O<sub>9</sub>、Bi<sub>2</sub>SrNb<sub>2</sub>O<sub>9</sub>、Bi<sub>2</sub>BaTa<sub>2</sub>O<sub>9</sub>、Bi<sub>2</sub>SrTaNbO<sub>9</sub>等を挙げることができる。あるいは又、強誘電体層を構成する材料として、Bi<sub>4</sub>SrTi<sub>4</sub>O<sub>15</sub>、Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub>、Bi<sub>2</sub>PbTa<sub>2</sub>O<sub>9</sub>等を例示することができるが、これらの場合においても、各金属元素の比率は、結晶構造が変化しない程度に変化させ得る。即ち、金属元素及び酸素元素の両サイトにおける組成ずれがあつてもよい。

## 【0108】

10

あるいは又、強誘電体層を構成する材料として、PbTiO<sub>3</sub>、ペロブスカイト型構造を有するPbZrO<sub>3</sub>とPbTiO<sub>3</sub>の固溶体であるチタン酸ジルコン酸鉛[PZT, Pb(Zr<sub>1-y</sub>, Ti<sub>y</sub>)O<sub>3</sub>(但し、0 < y < 1)]、PZTにLaを添加した金属酸化物であるPLZT、あるいはPZTにNbを添加した金属酸化物であるPNZTといったPZT系化合物を挙げることができる。

## 【0109】

以上に説明した強誘電体層を構成する材料において、これらの組成を化学量論的組成から外すことによって、結晶化温度を変化させることができる。

## 【0110】

20

本発明の第6の態様、若しくは、本発明の第1の態様～第5の態様及び第7の態様～第12の態様に係る強誘電体型不揮発性半導体メモリにおける好ましい態様においては、上述した強誘電体層を構成する材料を適宜選択することによって、上方に位置するメモリセルを構成する強誘電体層の結晶化温度を、下方に位置するメモリセルを構成する強誘電体層の結晶化温度よりも低くすることができ、あるいは又、上方に位置するメモリユニットあるいはサブメモリユニットを構成するメモリセルの強誘電体層の結晶化温度を、下方に位置するメモリユニットあるいはサブメモリユニットを構成するメモリセルの強誘電体層の結晶化温度よりも低くすることができる。以下の表1に、強誘電体層を構成する代表的な材料の結晶化温度を示すが、強誘電体層を構成する材料をかかる材料に限定するものではない。

## 【0111】

30

## [表1]

| 材料名                                                                      | 結晶化温度     |

|--------------------------------------------------------------------------|-----------|

| Bi <sub>2</sub> SrTa <sub>2</sub> O <sub>9</sub>                         | 700～800°C |

| Bi <sub>2</sub> Sr(Ta <sub>1.5</sub> , Nb <sub>0.5</sub> )O <sub>9</sub> | 650～750°C |

| Bi <sub>4</sub> Ti <sub>3</sub> O <sub>12</sub>                          | 600～700°C |

| Pb(Zr <sub>0.48</sub> , Ti <sub>0.52</sub> )O <sub>3</sub>               | 550～650°C |

| PbTiO <sub>3</sub>                                                       | 500～600°C |

## 【0112】

本発明の各種の態様の強誘電体型不揮発性半導体メモリにおいては、強誘電体層の下に第1の電極を形成し、強誘電体層の上に第2の電極を形成する構成(即ち、第1の電極は下部電極に相当し、第2の電極は上部電極に相当する)とすることもできるし、強誘電体層の上に第1の電極を形成し、強誘電体層の下に第2の電極を形成する構成(即ち、第1の電極は上部電極に相当し、第2の電極は下部電極に相当する)とすることもできる。プレート線は、第2の電極から延在している構成とすることもできるし、第2の電極とは別途に形成され、第2の電極と接続された構成とすることもできる。後者の場合、プレート線を構成する配線材料として、例えばアルミニウムやアルミニウム系合金を例示することができる。第1の電極が共通である構造として、具体的には、ストライプ状の第1の電極を形成し、かかるストライプ状の第1の電極の全面を覆うように強誘電体層を形成する構成を挙げることができる。尚、このような構造においては、第1の電極と強誘電体層と第2の電極の重複領域がメモリセルあるいはキャパシタ部に相当する。第1の電極が共通であ

40

50

る構造として、その他、第1の電極の所定の領域に、それぞれの強誘電体層が形成され、強誘電体層上に第2の電極が形成された構造、あるいは又、配線層の所定の表面領域に、それぞれの第1の電極が形成され、かかるそれぞれの第1の電極上に強誘電体層が形成され、強誘電体層上に第2の電極が形成された構造を挙げることができるが、これらの構成に限定するものではない。

#### 【0113】

強誘電体層を得るためには、強誘電体薄膜を形成した後の工程において、強誘電体薄膜をパターニングすればよい。場合によっては、強誘電体薄膜のパターニングは不要である。強誘電体薄膜の形成は、例えば、MOCVD法、パルスレーザアブレーション法、スパッタ法、ゾル-ゲル法といった強誘電体薄膜を構成する材料に適宜適した方法にて行うことができる。また、強誘電体薄膜のパターニングは、例えば異方性イオンエッチング(RIE)法にて行うことができる。

#### 【0114】

本発明において、第1の電極及び第2の電極を構成する材料として、例えば、Ir、IrO<sub>2-x</sub>、SrIrO<sub>3</sub>、Ru、RuO<sub>2-x</sub>、SrRuO<sub>3</sub>、Pt、Pt/IrO<sub>2-x</sub>、Pt/RuO<sub>2-x</sub>、Pd、Pt/Tiの積層構造、Pt/Taの積層構造、Pt/Ti/Taの積層構造、La<sub>0.5</sub>Sr<sub>0.5</sub>CoO<sub>3</sub>(LSCO)、Pt/LSCOの積層構造、YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7</sub>を挙げることができる。ここで、Xの値は、0 < X < 2である。尚、積層構造においては、「/」の前に記載された材料が上層を構成し、「/」の後ろに記載された材料が下層を構成する。第1の電極と第2の電極は、同じ材料から構成されていてもよいし、同種の材料から構成されていてもよいし、異種の材料から構成されていてもよい。第1の電極あるいは第2の電極を形成するためには、第1の電極材料層あるいは第2の電極材料層を形成した後の工程において、第1の電極材料層あるいは第2の電極材料層をパターニングすればよい。第1の電極材料層あるいは第2の電極材料層の形成は、例えばスパッタ法、反応性スパッタ法、電子ビーム蒸着法、MOCVD法、あるいはパルスレーザアブレーション法といった第1の電極材料層や第2の電極材料層を構成する材料に適宜適した方法にて行うことができる。また、第1の電極材料層や第2の電極材料層のパターニングは、例えばイオンミーリング法やRIE法にて行うことができる。

#### 【0115】

本発明において、層間絶縁層を構成する材料として、酸化シリコン(SiO<sub>2</sub>)、窒化シリコン(SiN)、SiON、SOG、NSG、BPSG、PSG、BSGあるいはLTOを例示することができる。

#### 【0116】

選択用トランジスタ(スイッチング用トランジスタ)や各種のトランジスタは、例えば、周知のMIS型FETやMOS型FETから構成することができる。ビット線を構成する材料として、不純物がドーピングされたポリシリコンや高融点金属材料を挙げることができる。共通の第1の電極と選択用トランジスタとの電気的な接続は、共通の第1の電極と選択用トランジスタとの間に形成された絶縁層に設けられた接続孔(コンタクトホール)を介して、あるいは又、かかる絶縁層に設けられた接続孔(コンタクトホール)及び絶縁層上に形成された配線層を介して行うことができる。尚、絶縁層を構成する材料として、酸化シリコン(SiO<sub>2</sub>)、窒化シリコン(SiN)、SiON、SOG、NSG、BPSG、PSG、BSGあるいはLTOを例示することができる。

#### 【0117】

##### 【発明の実施の形態】

以下、図面を参照して、発明の実施の形態(以下、実施の形態と略称する)に基づき本発明を説明する。

#### 【0118】

##### (実施の形態1)

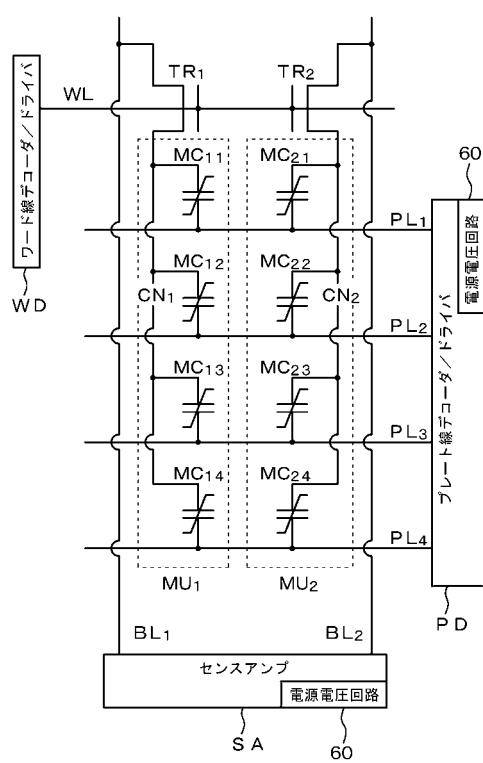

実施の形態1は、本発明の第1の態様及び第6の態様に係る強誘電体型不揮発性半導体メモリ(以下、不揮発性メモリと略称する)に関する。実施の形態1の不揮発性メモリの回

10

20

30

40

50

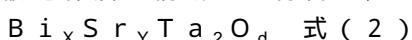

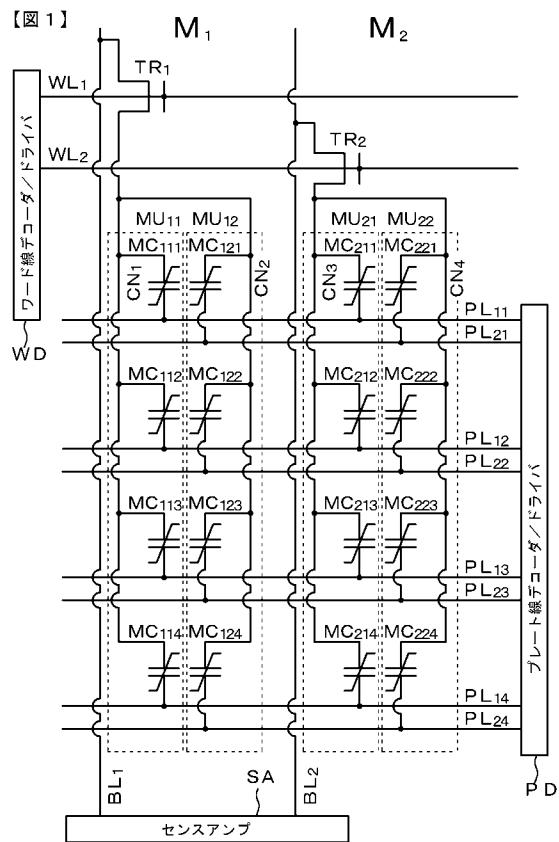

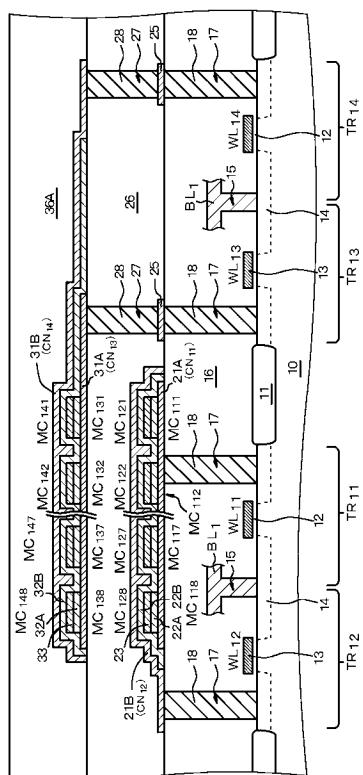

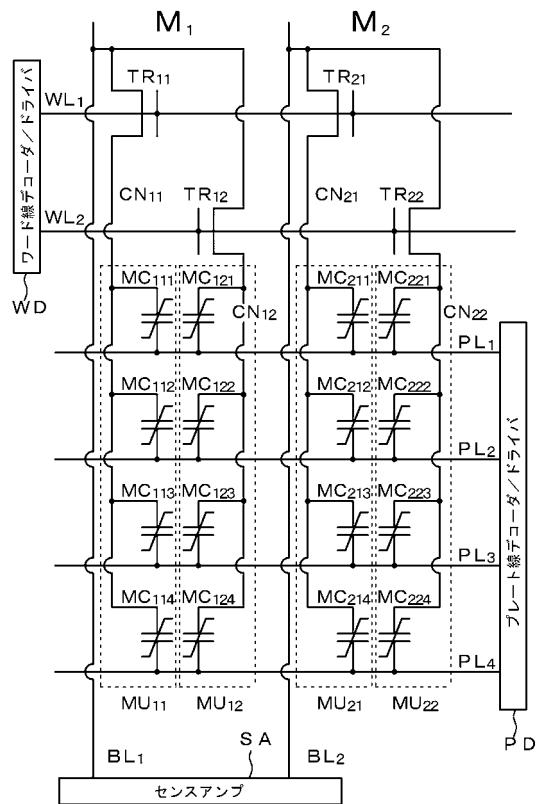

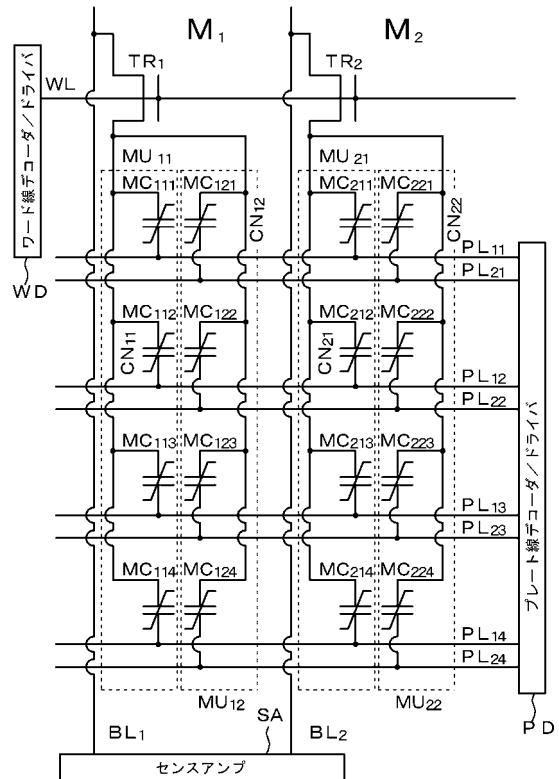

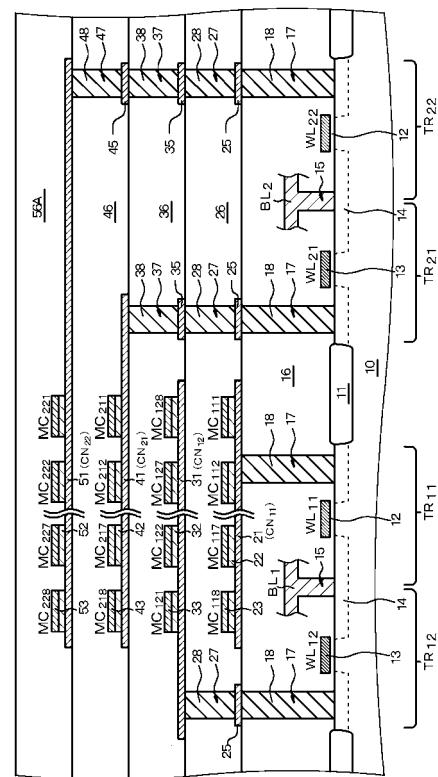

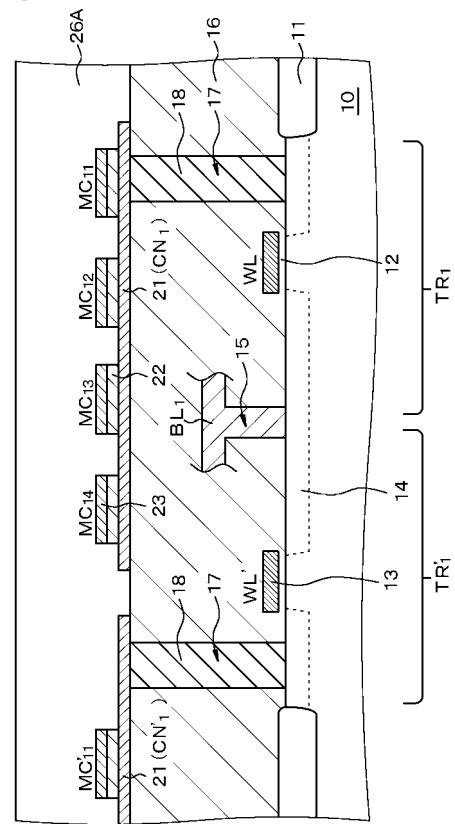

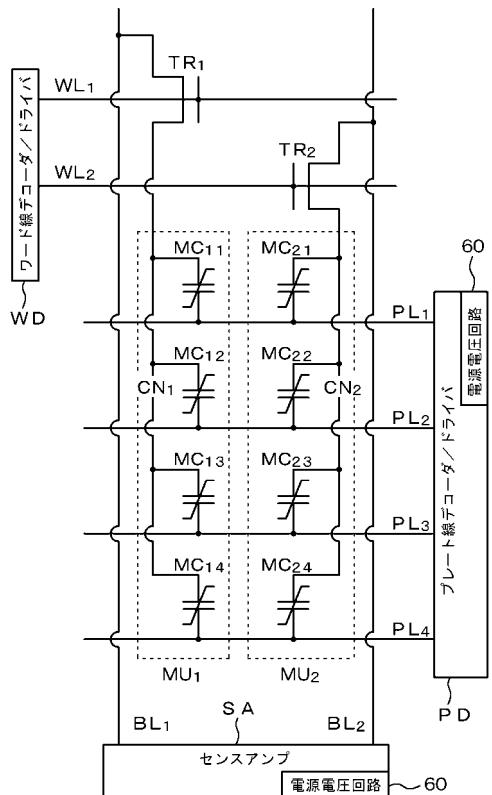

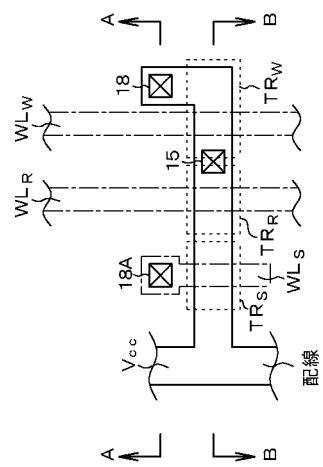

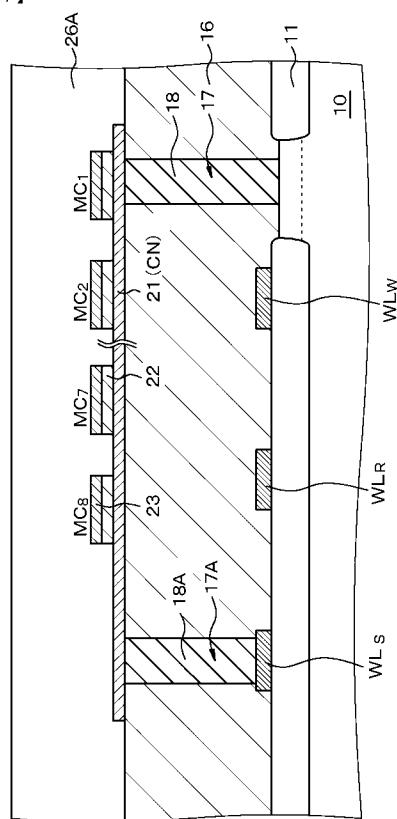

路図を図1に示し、模式的な一部断面図を図2に示す。尚、図1には、2つの不揮発性メモリM<sub>1</sub>、M<sub>2</sub>を示すが、これらの不揮発性メモリは同じ回路である。以下の説明においては、不揮発性メモリM<sub>1</sub>についての説明を行う。

#### 【0119】

この不揮発性メモリM<sub>1</sub>は、ビット線B L<sub>1</sub>と、MOS型FETから構成された選択用トランジスタT R<sub>1</sub>と、N個（但し、N=2であり、実施の形態1においてはN=2）のメモリユニットM U<sub>11</sub>、M U<sub>12</sub>と、プレート線から構成されている。メモリユニットM U<sub>11</sub>は、M個（但し、M=2であり、実施の形態1においてはM=4）のメモリセルM C<sub>11m</sub>（m=1, 2, 3, 4）から構成されている。また、メモリユニットM U<sub>12</sub>も、M個（M=4）のメモリセルM C<sub>12m</sub>（m=1, 2, 3, 4）から構成されている。プレート線の数は、M×N本（実施の形態1においては、8本）であり、P L<sub>1m</sub>、P L<sub>2m</sub>（m=1, 2, 3, 4）で表している。選択用トランジスタT R<sub>1</sub>のゲート電極に接続されたワード線W L<sub>1</sub>は、ワード線デコーダ／ドライバW Dに接続されている。一方、各プレート線P L<sub>1m</sub>、P L<sub>2m</sub>は、プレート線デコーダ／ドライバP Dに接続されている。

#### 【0120】

また、メモリユニットM U<sub>11</sub>を構成する各メモリセルM C<sub>11m</sub>は、第1の電極21と強誘電体層22と第2の電極23とから成り、メモリユニットM U<sub>12</sub>を構成する各メモリセルM C<sub>12m</sub>は、第1の電極31と強誘電体層32と第2の電極33とから成る。そして、各メモリユニットM U<sub>11</sub>、M U<sub>12</sub>において、メモリセルM C<sub>11m</sub>、M C<sub>12m</sub>の第1の電極21、31は共通である。この共通の第1の電極21、31を、便宜上、共通ノードC N<sub>11</sub>、C N<sub>12</sub>と呼ぶ。共通ノードC N<sub>11</sub>、C N<sub>12</sub>（共通の第1の電極21、31）は、選択用トランジスタT R<sub>1</sub>を介してビット線B L<sub>1</sub>に接続されている。また、第n番目（但し、n=1, 2, ..., N）のメモリユニットM U<sub>11</sub>、M U<sub>12</sub>において、第m番目（但し、m=1, 2, ..., M）のメモリセルM C<sub>11m</sub>、M C<sub>12m</sub>の第2の電極23、33は、第[(n-1)M+m]番目のプレート線P L<sub>1m</sub>、P L<sub>2m</sub>に接続されている。具体的には、メモリユニットM U<sub>11</sub>におけるメモリセルM C<sub>11m</sub>の第2の電極23は、それぞれ、プレート線P L<sub>1m</sub>に接続されており、メモリユニットM U<sub>12</sub>におけるメモリセルM C<sub>12m</sub>の第2の電極33は、それぞれ、プレート線P L<sub>2m</sub>に接続されている。

#### 【0121】

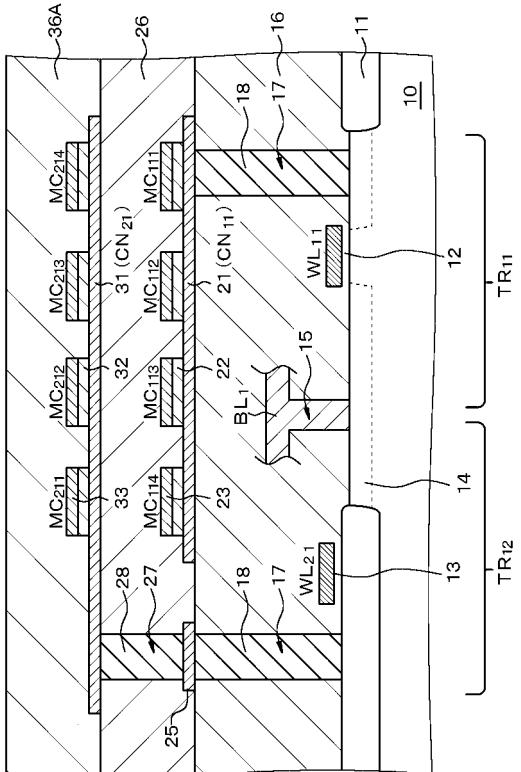

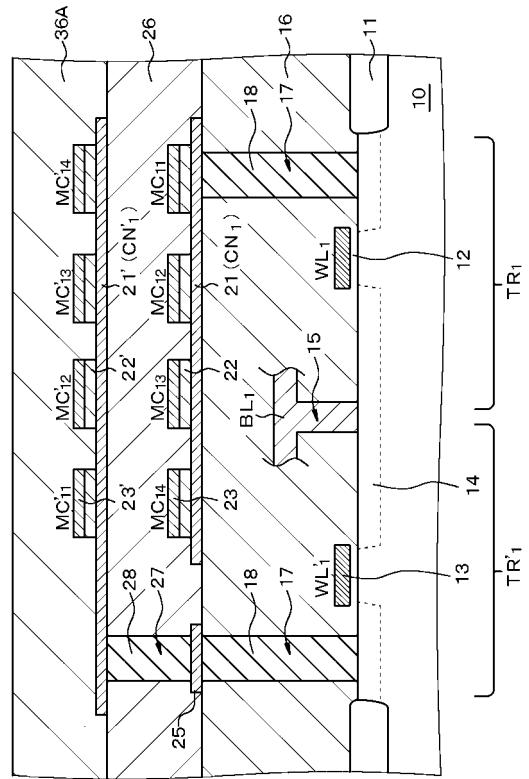

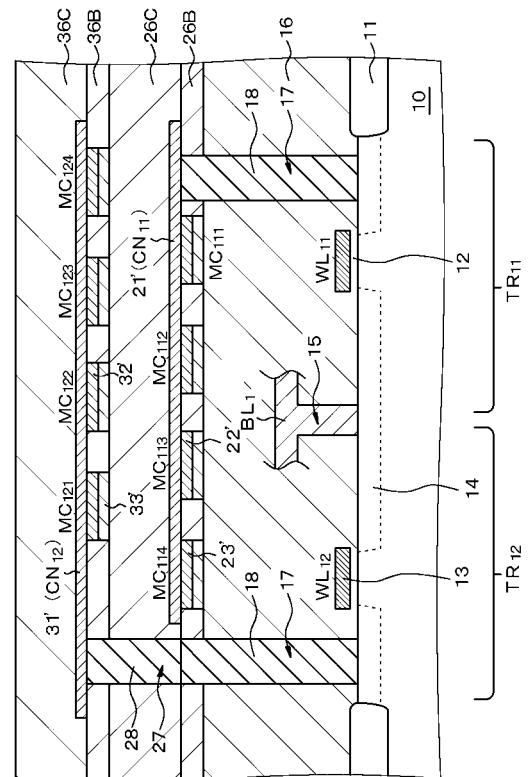

実施の形態1においては、2つのメモリユニットM U<sub>11</sub>、M U<sub>12</sub>は、それぞれ、層間絶縁層26を介して積層されている。メモリユニットM U<sub>12</sub>は絶縁膜36Aで被覆されている。また、メモリユニットM U<sub>11</sub>は、半導体基板10の上方に絶縁層16を介して形成されている。半導体基板10には素子分離領域11が形成されている。また、選択用トランジスタT R<sub>1</sub>は、ゲート電極13、ゲート絶縁膜12、ソース／ドレイン領域14から構成されている。そして、一方のソース／ドレイン領域14はコンタクトホール15を介してビット線B L<sub>1</sub>に接続されている。また、他方のソース／ドレイン領域14は、絶縁層16に形成された開口部17中に設けられた接続孔18を介して共通ノードC N<sub>11</sub>に接続され、更に、層間絶縁層26に形成された開口部27中に設けられた接続孔28を介して共通ノードC N<sub>12</sub>に接続されている。

#### 【0122】

ここで、ワード線W L<sub>1</sub>は、図2の紙面垂直方向に延びている。また、第2の電極23は、図2の紙面垂直方向に隣接するメモリユニットM U<sub>21</sub>を構成するメモリセルと共に接続され、プレート線P L<sub>1m</sub>を兼ねている。更には、第2の電極32も、図2の紙面垂直方向に隣接するメモリユニットM U<sub>22</sub>を構成するメモリセルと共に接続され、プレート線P L<sub>2m</sub>を兼ねている。各メモリセルを結ぶこれらの各プレート線は、図2の紙面垂直方向に延びており、図示しない領域において接続孔を介して接続されている。また、メモリセルM C<sub>11m</sub>とメモリセルM C<sub>12m</sub>とは、垂直方向に揃っている。このような構造にすることによって、メモリユニットの占有面積を小さくすることができ、集積度の向上を図ることができる。

#### 【0123】

10

20

30

40

50

尚、図1に示した不揮発性メモリM<sub>2</sub>は、図2の模式的な一部断面図において、上述のとおり、不揮発性メモリM<sub>1</sub>と紙面垂直方向に隣接している。

#### 【0124】

更には、ビット線B L<sub>1</sub>は、センスアンプSAに接続されている。尚、ビット線B L<sub>2</sub>も同じセンスアンプSAに接続されているが、ビット線B L<sub>2</sub>は、異なるセンスアンプSAに接続されていてもよい。また、ビット線B L<sub>1</sub>、B L<sub>2</sub>は、ビット線B L<sub>1</sub>、B L<sub>2</sub>の伸びる方向に隣接する他の不揮発性メモリとも共有されている。

#### 【0125】

そして、各メモリセルMC<sub>11m</sub>、MC<sub>12m</sub>(m=1, 2, 3, 4)に1ビットがデータとして記憶される。実際の不揮発性メモリにおいては、この8ビットを記憶するメモリユニットの集合がアクセス単位ユニットとしてアレイ状に配設されている。10

#### 【0126】

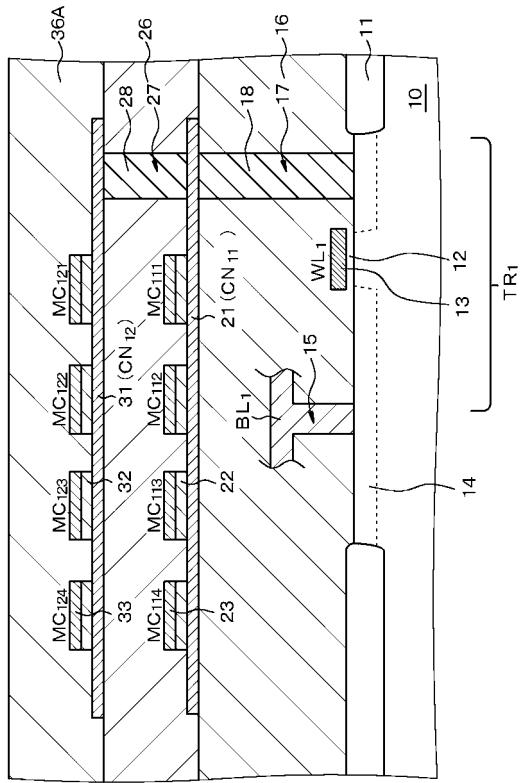

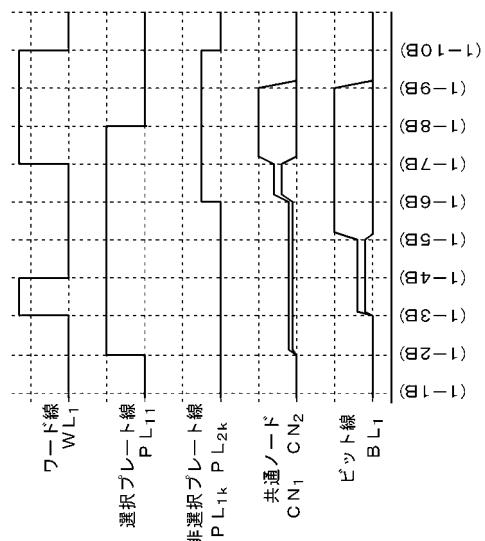

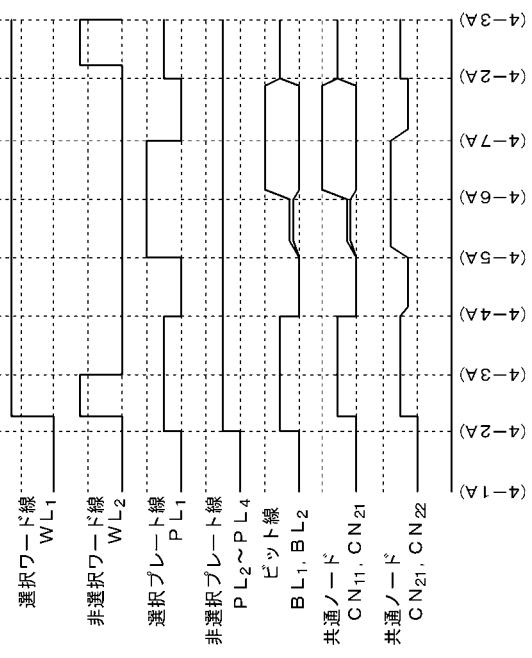

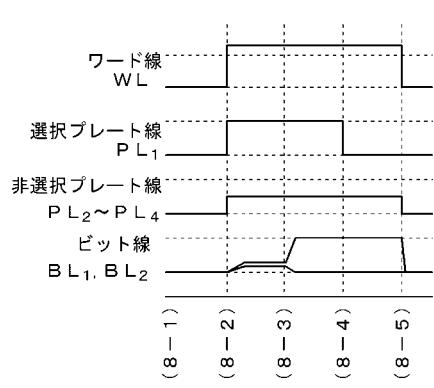

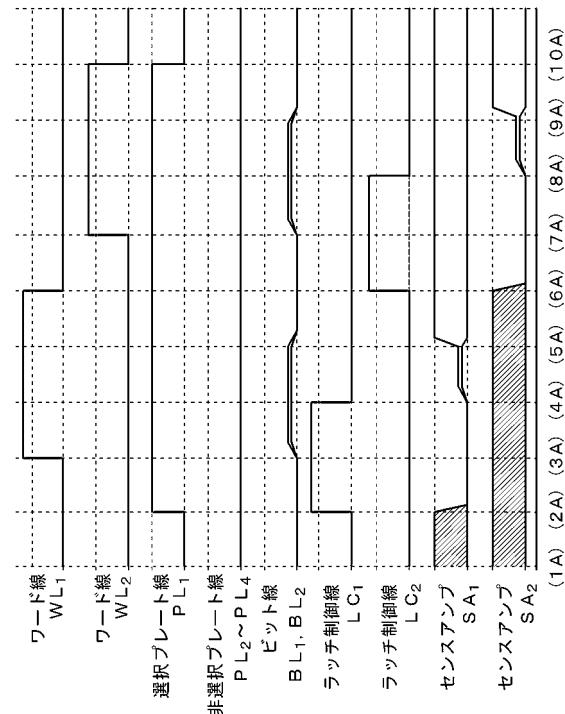

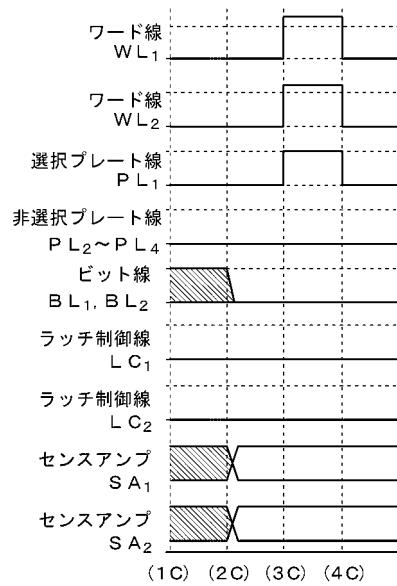

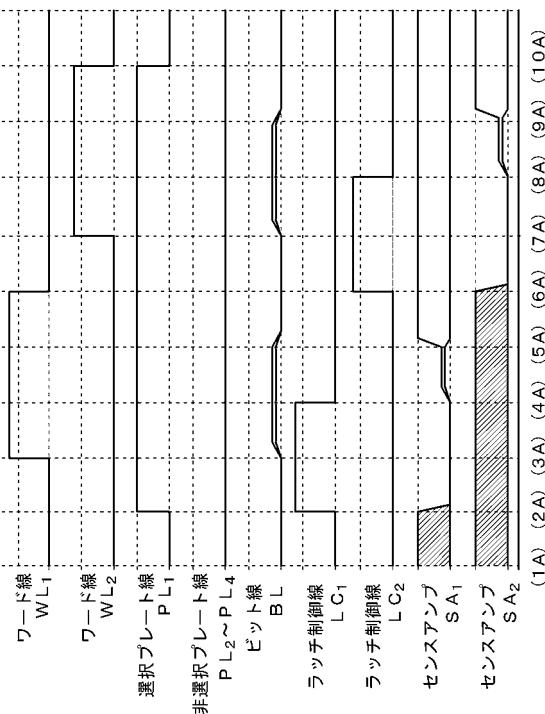

実施の形態1の不揮発性メモリにデータを書き込む方法の一例を、以下、説明する。尚、一例として、メモリセルMC<sub>111</sub>にデータを書き込むものとする。図3に動作波形を示す。尚、図3中、括弧内の数字は、以下に説明する工程の番号と対応している。

#### 【0127】

(1-1A) 待機状態では、ビット線B L<sub>1</sub>、ワード線WL<sub>1</sub>、全プレート線PL<sub>1m</sub>、PL<sub>2m</sub>が0ボルトとなっている。更には、共通ノードCN<sub>11</sub>、CN<sub>12</sub>も0ボルトで浮遊状態となっている。

#### 【0128】

(1-2A) データ書き込みの開始時、選択プレート線PL<sub>11</sub>の電位をV<sub>cc</sub>とし、非選択プレート線PL<sub>1k</sub>(k=2, 3, 4)、PL<sub>2k</sub>(k=1, 2, 3, 4)の電位を(1/2)V<sub>cc</sub>とする。これによって、浮遊状態の共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位は、プレート線PL<sub>1M</sub>、PL<sub>2M</sub>とのカップリングにより、概ね(1/2)V<sub>cc</sub>近傍まで上昇する。また、選択メモリセルMC<sub>111</sub>にデータ「1」を書き込む場合には、ビット線B L<sub>1</sub>の電位をV<sub>cc</sub>とし、データ「0」を書き込む場合には、ビット線B L<sub>1</sub>の電位を0ボルトとする。20

#### 【0129】

(1-3A) その後、選択用トランジスタTR<sub>1</sub>をオン状態とする。これによって、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位は、選択メモリセルMC<sub>111</sub>にデータ「1」を書き込む場合には、V<sub>cc</sub>となり、データ「0」を書き込む場合には、0ボルトとなる。尚、選択プレート線PL<sub>11</sub>にはV<sub>cc</sub>が印加された状態にあるので、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位が0ボルトの場合、選択メモリセルMC<sub>111</sub>にデータ「0」が書き込まれる。一方、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位がV<sub>cc</sub>の場合、選択メモリセルMC<sub>111</sub>には何らデータが書き込まれない。30

#### 【0130】

(1-4A) 次いで、選択プレート線PL<sub>11</sub>の電位を0ボルトとする。共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位がV<sub>cc</sub>の場合、選択メモリセルMC<sub>111</sub>にデータ「1」が書き込まれる。選択メモリセルMC<sub>111</sub>に既にデータ「0」が書き込まれている場合には、選択メモリセルMC<sub>111</sub>に何ら変化は生じない。

#### 【0131】

(1-5A) その後、ビット線B L<sub>1</sub>を0ボルトと印加する。40

#### 【0132】

(1-6A) 更に、非選択プレート線PL<sub>1k</sub>、PL<sub>2k</sub>を0ボルトとし、選択用トランジスタTR<sub>1</sub>をオフ状態とする。

#### 【0133】

他のメモリセルMC<sub>11m</sub>(m=2, 3, 4)、MC<sub>12m</sub>(m=1, 2, 3, 4)にデータを書き込む場合には、同様の操作を繰り返す。このような書き込み動作においては、非選択メモリセルMC<sub>11k</sub>、MC<sub>12k</sub>に(±1/2)V<sub>cc</sub>のディスターブが発生するが、V<sub>cc</sub>の値を適切に設定することによって、非選択メモリセルMC<sub>11k</sub>、MC<sub>12k</sub>におけるデータの破壊を確実に防止することができる。50

## 【0134】

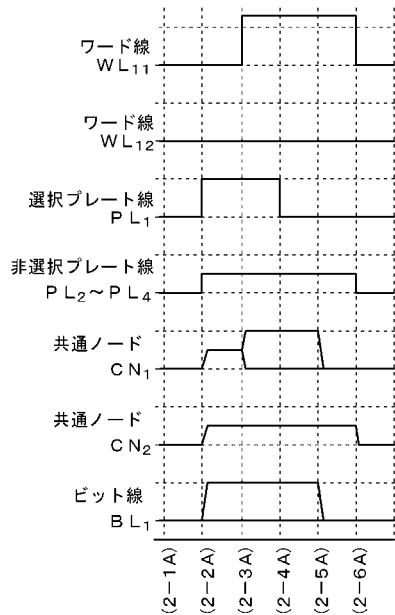

次に、実施の形態1の不揮発性メモリからデータを読み出し、データを再書き込みする動作を、以下、説明する。尚、一例として、プレート線PL<sub>11</sub>に接続されたメモリセルMC<sub>111</sub>からデータを読み出し、データを再書き込みするものとする。図4に動作波形を示す。

## 【0135】

(1-1B) 待機状態では、ビット線BL<sub>1</sub>、ワード線WL<sub>1</sub>、全プレート線PL<sub>1m</sub>、PL<sub>2m</sub>が0ボルトとなっている。更には、共通ノードCN<sub>11</sub>、CN<sub>12</sub>も0ボルトで浮遊状態となっている。

## 【0136】

(1-2B) データ読み出し時、選択プレート線PL<sub>11</sub>にV<sub>cc</sub>を印加する。このとき、選択メモリセルMC<sub>111</sub>にデータ「1」が記憶されていれば、強誘電体層に分極反転が生じ、蓄積電荷量が増加し、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位が上昇する。一方、選択メモリセルMC<sub>111</sub>にデータ「0」が記憶されていれば、強誘電体層に分極反転が生ぜず、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位は殆ど上昇しない。即ち、共通ノードCN<sub>11</sub>、CN<sub>12</sub>は、非選択メモリセルの強誘電体層を介して複数の非選択プレート線PL<sub>1k</sub>(k=2,3,4), PL<sub>2k</sub>(k=1,2,3,4)にカップリングされているので、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位は0ボルトに比較的近いレベルに保たれる。このようにして、選択メモリセルMC<sub>111</sub>に記憶されたデータに依存して共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位に変化が生じる。従って、選択メモリセルMC<sub>111</sub>の強誘電体層には、分極反転に十分な電界を与えることができる。

10

## 【0137】

(1-3B) 次に、ビット線BL<sub>1</sub>を浮遊状態とし、選択用トランジスタTR<sub>1</sub>をオン状態とする。これによって、選択メモリセルMC<sub>111</sub>に記憶されたデータに基づき共通の第1の電極(共通ノードCN<sub>11</sub>、CN<sub>12</sub>)に生じた電位により、ビット線BL<sub>1</sub>に電位が生じる。

20

## 【0138】

(1-4B) 次いで、選択用トランジスタTR<sub>1</sub>をオフ状態とする。そして、かかるビット線BL<sub>1</sub>の電位をセンスアンプSAにてラッチし、センスアンプSAを活性化してデータを増幅し、データの読み出し動作を完了する。

30

## 【0139】

以上の動作によって、選択メモリセルに記憶されていたデータが一旦破壊されてしまうので、データの再書き込み動作を行う。

## 【0140】

(1-5B) そのために、先ず、ビット線BL<sub>1</sub>をセンスアンプSAによって充放電させ、ビット線BL<sub>1</sub>にV<sub>cc</sub>又は0ボルトを印加する。

## 【0141】

(1-6B) そして、非選択プレート線PL<sub>1k</sub>(k=2,3,4), PL<sub>2k</sub>(k=1,2,3,4)の電位を(1/2)V<sub>cc</sub>とする。

## 【0142】

(1-7B) その後、選択用トランジスタTR<sub>1</sub>をオン状態とする。これによって、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位はビット線BL<sub>1</sub>の電位と等しくなる。即ち、選択メモリセルMC<sub>111</sub>に記憶されていたデータが「1」の場合には、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位はV<sub>cc</sub>となり、選択メモリセルMC<sub>111</sub>に記憶されていたデータが「0」の場合には、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位は0ボルトとなる。選択プレート線PL<sub>11</sub>の電位はV<sub>cc</sub>のままであるが故に、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位が0ボルトの場合、選択メモリセルMC<sub>111</sub>にはデータ「0」が再書き込みされる。

40

## 【0143】

(1-8B) 次に、選択プレート線PL<sub>11</sub>の電位を0ボルトとする。これによって、選択メモリセルMC<sub>111</sub>に記憶されていたデータが「1」の場合には、共通ノードCN<sub>11</sub>、CN<sub>12</sub>の電位が0ボルトとなる。

50

$N_{12}$ の電位が $V_{cc}$ であるが故に、データ「1」が再書き込みされる。選択メモリセル $MC_{111}$ にデータ「0」が既に再書き込みされていた場合には、選択メモリセル $MC_{111}$ に変化は生じない。

【0144】

(1-9B) その後、ピット線 $BL_1$ を0ボルトとする。

【0145】

(1-10B) 最後に、非選択プレート線 $PL_{1k}, PL_{2k}$ を0ボルトとし、選択用トランジスタ $TR_1$ をオフ状態とする。

【0146】

他のメモリセル $MC_{11m}$  ( $m = 2, 3, 4$ ),  $MC_{12m}$  ( $m = 1, 2, 3, 4$ ) からデータを読み出し、データを再書き込みする場合には、同様の操作を繰り返す。 10

【0147】

実施の形態1の不揮発性メモリにおいては、メモリユニット $MU_{11}$ を構成する各メモリセル $MC_{11m}$ における強誘電体層22と、メモリユニット $MU_{12}$ を構成する各メモリセル $MC_{12m}$ における強誘電体層32とを同一の材料から構成してもよいが、本発明の第6の態様に係る不揮発性メモリのように、上方に位置するメモリセルを構成する強誘電体層32の結晶化温度は、下方に位置するメモリセルを構成する強誘電体層22の結晶化温度よりも低い構成とすることが好ましい。具体的には、強誘電体層22, 32を、以下の表2に例示する材料から構成することができる。

【0148】

20

【表2】

|         | 材料                            | 結晶化温度 |

|---------|-------------------------------|-------|

| 強誘電体層32 | $Bi_2Sr(Ta_{1.5}Nb_{0.5})O_9$ | 700°C |

| 強誘電体層22 | $Bi_2SrTa_2O_9$               | 750°C |

【0149】

以下、このような構成の不揮発性メモリの製造方法を説明するが、他の実施の形態あるいはその変形における不揮発性メモリも、実質的に同様の方法で製造することができる。

【0150】

30

【工程-100】

先ず、不揮発性メモリにおける選択用トランジスタとして機能するMOS型トランジスタを半導体基板10に形成する。そのために、例えばLOCOS構造を有する素子分離領域11を公知の方法に基づき形成する。尚、素子分離領域は、トレンチ構造を有していてもよいし、LOCOS構造とトレンチ構造の組合せとしてもよい。その後、半導体基板10の表面を例えばパイロジェニック法により酸化し、ゲート絶縁膜12を形成する。次いで、不純物がドーピングされたポリシリコン層をCVD法にて全面に形成した後、ポリシリコン層をパターニングし、ゲート電極13を形成する。このゲート電極13はワード線を兼ねている。尚、ゲート電極13をポリシリコン層から構成する代わりに、ポリサイドや金属シリサイドから構成することもできる。次に、半導体基板10にイオン注入を行い、LDD構造を形成する。その後、全面にCVD法にて $SiO_2$ 層を形成した後、この $SiO_2$ 層をエッチバックすることによって、ゲート電極13の側面にゲートサイドウォール(図示せず)を形成する。次いで、半導体基板10にイオン注入を施した後、イオン注入された不純物の活性化アニール処理を行うことによって、ソース/ドレイン領域14を形成する。 40

【0151】

【工程-110】

次いで、 $SiO_2$ から成る下層絶縁層をCVD法にて形成した後、一方のソース/ドレイン領域14の上方の下層絶縁層に開口部をRIE法にて形成する。そして、かかる開口部内を含む下層絶縁層上に不純物がドーピングされたポリシリコン層をCVD法にて形成す

50

る。これによって、コンタクトプラグ 15 が形成される。次に、下層絶縁層上のポリシリコン層をパターニングすることによって、ビット線 BL を形成する。その後、BPSG から成る上層絶縁層を CVD 法にて全面に形成する。尚、BPSG から成る上層絶縁層の形成後、窒素ガス雰囲気中で例えば  $900^{\circ}\text{C} \times 20$  分間、上層絶縁層をリフローさせることが好ましい。更には、必要に応じて、例えば化学的機械的研磨法 (CMP 法) にて上層絶縁層の頂面を化学的及び機械的に研磨し、上層絶縁層を平坦化することが望ましい。尚、下層絶縁層と上層絶縁層を纏めて、絶縁層 16 と呼ぶ。

## 【0152】

## [工程 - 120]

次に、他方のソース / ドレイン領域 14 の上方の絶縁層 16 に開口部 17 を RIE 法にて形成した後、かかる開口部 17 内を、不純物をドーピングしたポリシリコンで埋め込み、接続孔 (コンタクトプラグ) 18 を完成させる。ビット線 BL は、下層絶縁層上を、図の左右方向に接続孔 18 と接触しないように延びている。

## 【0153】

尚、接続孔 18 は、絶縁層 16 に形成された開口部 17 内に、例えば、タングステン、Ti、Pt、Pd、Cu、TiW、TiNW、WSi<sub>2</sub>、MoSi<sub>2</sub> 等の高融点金属や金属シリサイドから成る金属配線材料を埋め込むことによって形成することもできる。接続孔 18 の頂面は絶縁層 16 の表面と略同じ平面に存在していてもよいし、接続孔 18 の頂部が絶縁層 16 の表面に延在していてもよい。タングステンにて開口部 17 を埋め込み、接続孔 18 を形成する条件を、以下の表 3 に例示する。尚、タングステンにて開口部 17 を埋め込む前に、Ti 層及び TiN 層を順に例えばマグнетロンスパッタ法にて開口部 17 内を含む絶縁層 16 の上に形成することが好ましい。ここで、Ti 層及び TiN 層を形成する理由は、オーミックな低コンタクト抵抗を得ること、プランケットタングステン CVD 法における半導体基板 10 の損傷発生の防止、タングステンの密着性向上のためである。

## 【0154】

## [表 3]

Ti 層 (厚さ : 20 nm) のスパッタ条件

プロセスガス : Ar = 35 sccm

圧力 : 0.52 Pa

R F パワー : 2 kW

基板の加熱 : 無し

TiN 層 (厚さ : 100 nm) のスパッタ条件

プロセスガス : N<sub>2</sub> / Ar = 100 / 35 sccm

圧力 : 1.0 Pa

R F パワー : 6 kW

基板の加熱 : 無し

タングステンの CVD 形成条件

使用ガス : WF<sub>6</sub> / H<sub>2</sub> / Ar = 40 / 400 / 2250 sccm

圧力 : 10.7 kPa

形成温度 : 450 °C

タングステン層及び TiN 層、Ti 層のエッチング条件

第 1 段階のエッチング : タングステン層のエッチング

使用ガス : SF<sub>6</sub> / Ar / He = 110 : 90 : 5 sccm

圧力 : 4.6 Pa

R F パワー : 275 W

第 2 段階のエッチング : TiN 層 / Ti 層のエッチング

使用ガス : Ar / Cl<sub>2</sub> = 75 / 5 sccm

圧力 : 6.5 Pa

R F パワー : 250 W

## 【0155】

10

20

30

40

50

## [工程 - 130]

次に、絶縁層16上に、酸化チタンから成る密着層(図示せず)を形成することが望ましい。そして、密着層上にIrから成る第1の電極(下部電極)21を構成する第1の電極材料層を、例えばスパッタ法にて形成し、第1の電極材料層及び密着層をフォトリソグラフィ技術及びドライエッチング技術に基づきパターニングすることによって、第1の電極21を得ることができる。尚、以下の工程においても、第1の電極材料層を形成する前に、層間絶縁層上に密着層を形成することが望ましい。

## 【0156】

## [工程 - 140]

その後、例えば、MOCVD法によって、Bi系層状構造ペロブスカイト型の強誘電体材料(具体的には、例えば、結晶化温度750°CのBi<sub>2</sub>SrTa<sub>2</sub>O<sub>9</sub>)から成る強誘電体薄膜を全面に形成する。その後、250°Cの空気中で乾燥処理を行った後、750°Cの酸素ガス雰囲気で1時間の熱処理を施し、結晶化を促進させる。

10

## 【0157】

## [工程 - 150]

次に、IrO<sub>2-x</sub>層、Pt層を、スパッタ法にて、順次、全面に形成した後、フォトリソグラフィ技術、ドライエッチング技術に基づき、Pt層、IrO<sub>2-x</sub>層、Bi<sub>2</sub>SrTa<sub>2</sub>O<sub>9</sub>薄膜を順次、パターニングして、第2の電極23及び強誘電体層22を形成する。エッチングによって、強誘電体層22にダメージが加わる場合には、ダメージ回復に必要とされる温度にて、熱処理を行えばよい。

20

## 【0158】

## [工程 - 160]

その後、

- ・層間絶縁層26の形成及び平坦化処理

- ・開口部27の形成及び接続孔28の形成

- ・第1の電極31、結晶化温度700°CのBi<sub>2</sub>Sr(Ta<sub>1.5</sub>Nb<sub>0.5</sub>)O<sub>9</sub>から成る強誘電体層32、及び第2の電極33の形成

- ・絶縁膜36Aの形成

を、順次、行う。尚、Bi<sub>2</sub>Sr(Ta<sub>1.5</sub>Nb<sub>0.5</sub>)O<sub>9</sub>から成る強誘電体層32に対して、結晶化促進のための熱処理を、700°Cの酸素ガス雰囲気で1時間、行えばよい。

30

## 【0159】

尚、各第2の電極はプレート線を兼ねていなくともよい。この場合には、絶縁膜36Aの形成完了後、第2の電極23、第2の電極33を接続孔(ビアホール)によって接続し、併せて、絶縁膜36A上に、かかる接続孔と接続したプレート線を形成すればよい。

## 【0160】

例えば、Bi<sub>2</sub>SrTa<sub>2</sub>O<sub>9</sub>から成る強誘電体薄膜の形成条件を以下の表4に例示する。

尚、表4中、「thd」は、テトラメチルヘプタンジオンの略である。また、表4に示したソース原料はテトラヒドロフラン(THF)を主成分とする溶媒中に溶解されている。

## 【0161】

## [表4]

## MOCVD法による形成

ソース材料 : Sr (thd) 2-tetraglyme

Bi (C<sub>6</sub>H<sub>5</sub>) 3Ta (O-iC<sub>3</sub>H<sub>7</sub>) 4 (thd)

形成温度 : 400~700°C

プロセスガス : Ar/O<sub>2</sub> = 1000/1000 cm<sup>3</sup>

形成速度 : 5~20 nm/分

## 【0162】

あるいは又、Bi<sub>2</sub>SrTa<sub>2</sub>O<sub>9</sub>から成る強誘電体薄膜をパルスレーザアブレーション法、ゾル-ゲル法、あるいはRFスパッタ法にて全面に形成することもできる。これらの場合の形成条件を以下に例示する。尚、ゾル-ゲル法によって厚い強誘電体薄膜を形成する場合、所望の回数、スピンドル及び乾燥、あるいはスピンドル及び焼成（又は、アニール処理）を繰り返せばよい。

## 【0163】

## [表5]

## パルスレーザアブレーション法による形成

ターゲット : Bi<sub>2</sub>SrTa<sub>2</sub>O<sub>9</sub>

使用レーザ : KrFエキシマレーザ（波長248 nm、パルス幅25 ns、5 Hz）

形成温度 : 400~800°C

酸素濃度 : 3 Pa

## 【0164】

## [表6]

## ゾル-ゲル法による形成

原料 : Bi (CH<sub>3</sub>(CH<sub>2</sub>)<sub>3</sub>CH(C<sub>2</sub>H<sub>5</sub>)COO)<sub>3</sub>[ビスマス・2エチルヘキサン酸, Bi (OOC)<sub>3</sub>]Sr (CH<sub>3</sub>(CH<sub>2</sub>)<sub>3</sub>CH(C<sub>2</sub>H<sub>5</sub>)COO)<sub>2</sub>[ストロンチウム・2エチルヘキサン酸, Sr (OOC)<sub>2</sub>]Ta (OEt)<sub>5</sub> [タンタル・エトキシド]

スピンドル条件 : 3000 rpm × 20秒

乾燥 : 250°C × 7分

焼成 : 700~800°C × 1時間（必要に応じてRTA処理を加える）

## 【0165】

## [表7]

## RFスパッタ法による形成

ターゲット : Bi<sub>2</sub>SrTa<sub>2</sub>O<sub>9</sub>セラミックターゲットRFパワー : 1.2 W ~ 2.0 W / ターゲット 1 cm<sup>2</sup>

雰囲気圧力 : 0.2 ~ 1.3 Pa

形成温度 : 室温 ~ 600°C

プロセスガス : Ar / O<sub>2</sub>の流量比 = 2 / 1 ~ 9 / 1

## 【0166】

10

20

40

50

強誘電体層を、P Z TあるいはP L Z Tから構成するときの、マグネットロンスパッタ法によるP Z TあるいはP L Z Tの形成条件を以下の表8に例示する。あるいは又、P Z TやP L Z Tを、反応性スパッタ法、電子ビーム蒸着法、ゾル-ゲル法、又はM O C V D法にて形成することもできる。

## 【0167】

## [表8]

ターゲット : P Z TあるいはP L Z T

プロセスガス : Ar / O<sub>2</sub> = 90 体積% / 10 体積%

圧力 : 4 Pa

パワー : 50 W

形成温度 : 500 °C

10

## 【0168】

更には、P Z TやP L Z Tをパルスレーザアブレーション法にて形成することもできる。この場合の形成条件を以下の表9に例示する。

## 【0169】

## [表9]

ターゲット : P Z T又はP L Z T

使用レーザ : KrFエキシマレーザ(波長248 nm、パルス幅25 ns、3 Hz)

出力エネルギー : 400 mJ (1.1 J / cm<sup>2</sup>)

形成温度 : 550 ~ 600 °C

20

酸素濃度 : 40 ~ 120 Pa

## 【0170】

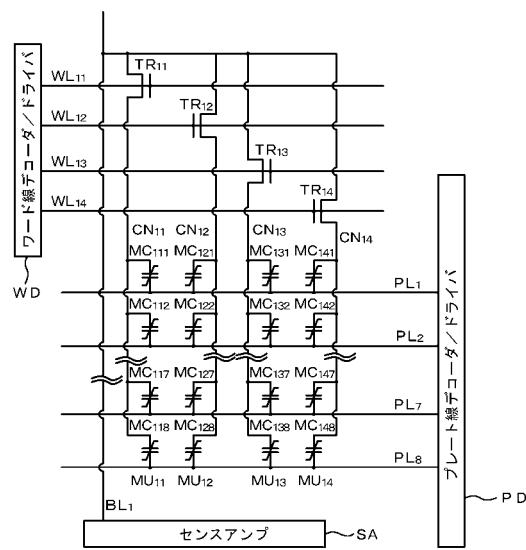

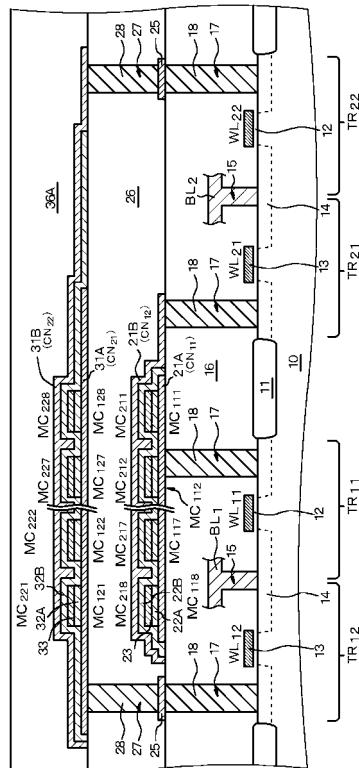

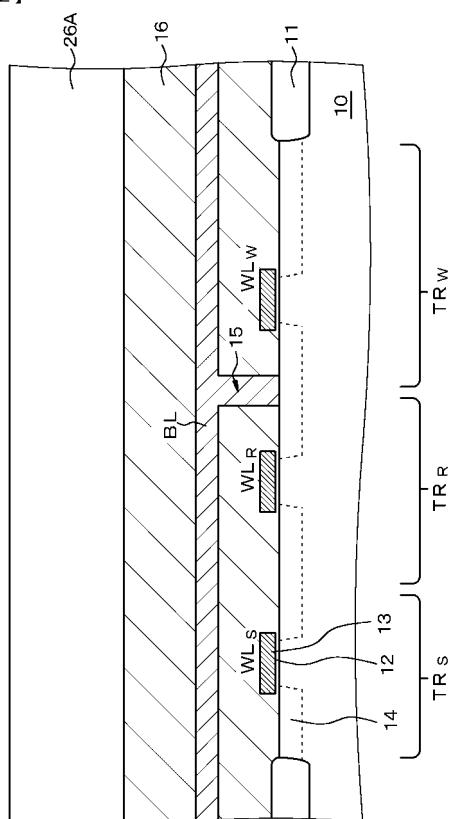

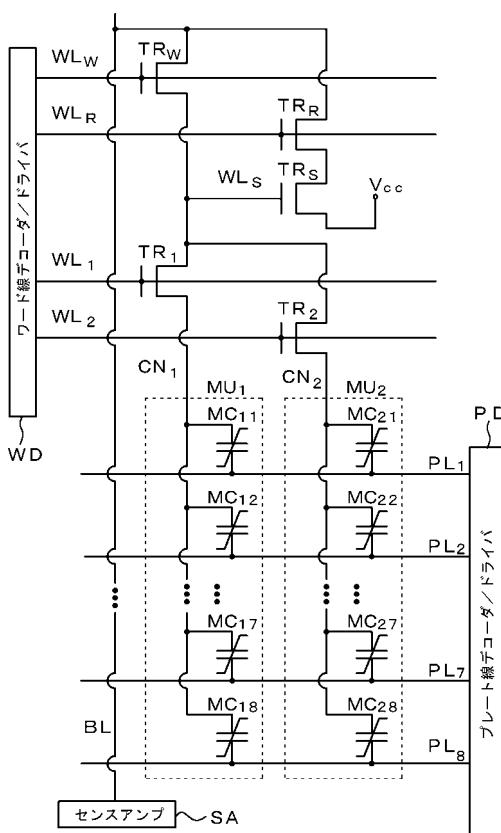

## (実施の形態2)

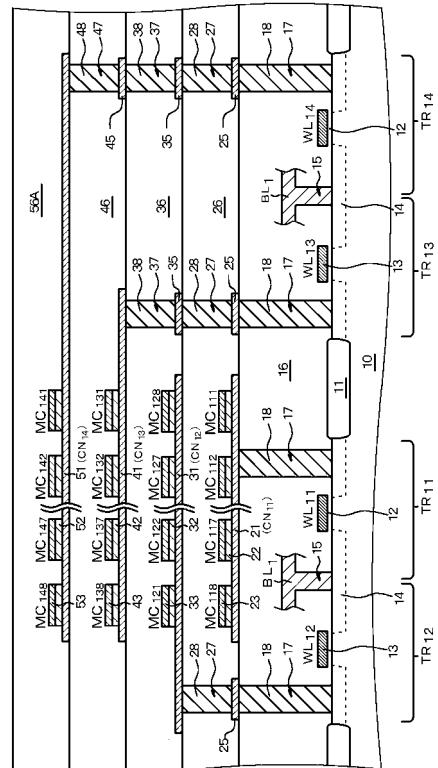

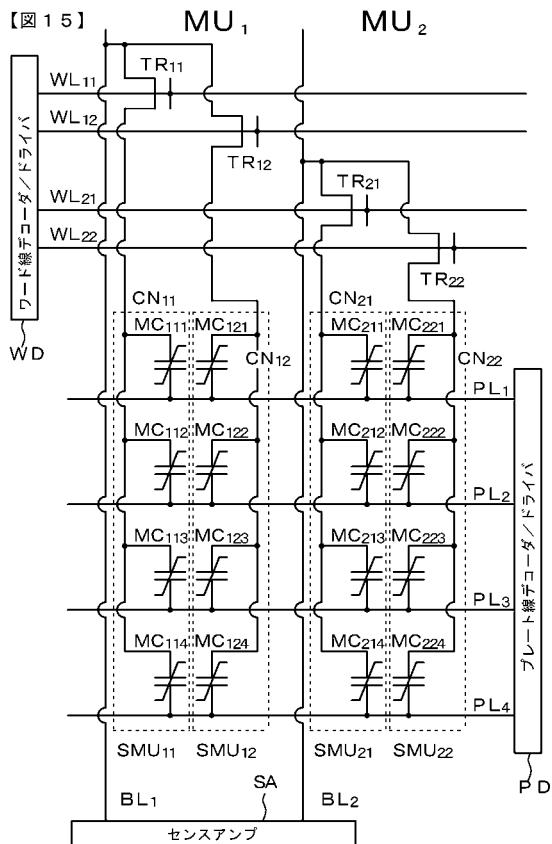

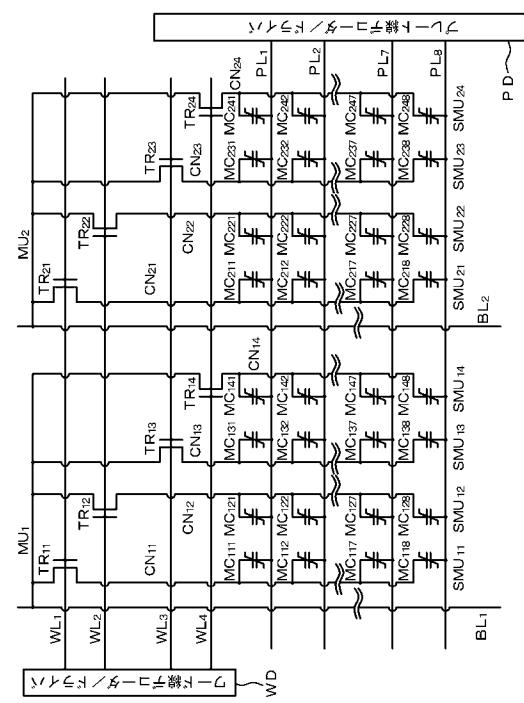

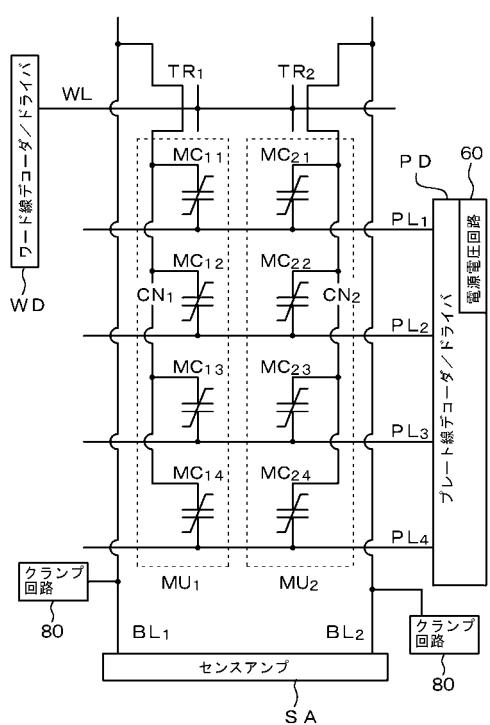

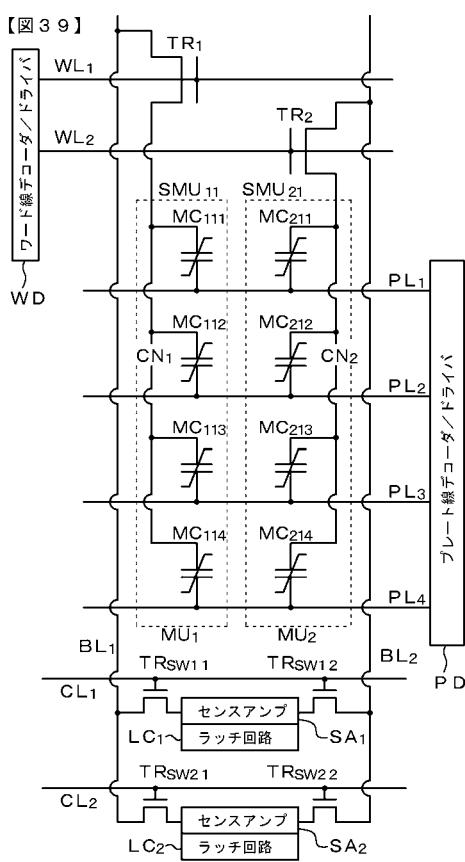

実施の形態2は、本発明の第2の態様に係る不揮発性メモリに関する。実施の形態2の不揮発性メモリの回路図を図5に示し、模式的な一部断面図を図6に示す。尚、図5には、2つの不揮発性メモリM<sub>1</sub>, M<sub>2</sub>を示すが、これらの不揮発性メモリは同じ回路である。以下の説明においては、不揮発性メモリM<sub>1</sub>についての説明を行う。

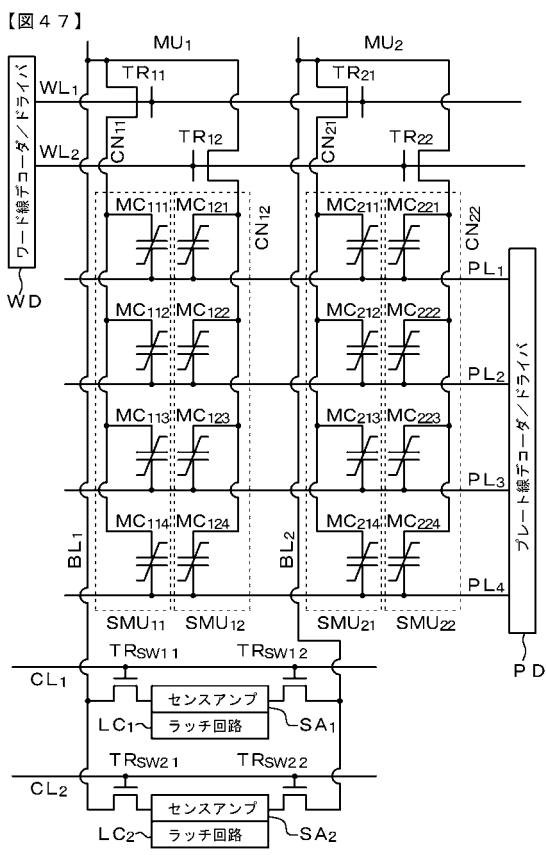

## 【0171】

この不揮発性メモリM<sub>1</sub>は、ビット線B L<sub>1</sub>と、MOS型FETから構成されたN個(但し、N = 2であり、実施の形態2においてはN = 2)の選択用トランジスタT R<sub>11</sub>, T R<sub>12</sub>と、N個(実施の形態2においてはN = 2)のメモリユニットM U<sub>11</sub>, M U<sub>12</sub>と、プレート線から構成されている。第1番目のメモリユニットM U<sub>11</sub>は、M個(但し、M = 2であり、実施の形態2においてはM = 4)のメモリセルM C<sub>11m</sub>(m = 1, 2, 3, 4)から構成されている。また、第2番目のメモリユニットM U<sub>12</sub>も、M個(M = 4)のメモリセルM C<sub>12m</sub>(m = 1, 2, 3, 4)から構成されている。プレート線の数は、M本(実施の形態2においては4本)であり、P L<sub>m</sub>(m = 1, 2, 3, 4)で表している。第1の選択用トランジスタT R<sub>11</sub>のゲート電極に接続されたワード線W L<sub>11</sub>、第2の選択用トランジスタT R<sub>12</sub>のゲート電極に接続されたワード線W L<sub>12</sub>は、ワード線デコーダ/ドライバW Dに接続されている。一方、各プレート線P L<sub>m</sub>は、プレート線デコーダ/ドライバP Dに接続されている。

30

## 【0172】

また、第1のメモリユニット第1のM U<sub>11</sub>を構成する各メモリセルM C<sub>11m</sub>は、第1の電極21と強誘電体層22と第2の電極23とから成り、第2のメモリユニットM U<sub>12</sub>を構成する各メモリセルM C<sub>12m</sub>は、第1の電極31と強誘電体層32と第2の電極33とから成る。そして、各メモリユニットM U<sub>11</sub>, M U<sub>12</sub>において、メモリセルの第1の電極21, 31は共通である。この共通の第1の電極21, 31を、便宜上、共通ノードC N<sub>11</sub>, C N<sub>12</sub>と呼ぶ。第1番目のメモリユニットM U<sub>11</sub>における共通の第1の電極21(第1の共通ノードC N<sub>11</sub>)は、第1番目の選択用トランジスタT R<sub>11</sub>を介してビット線B L<sub>1</sub>に接続されている。また、第2番目のメモリユニットM U<sub>12</sub>における共通の第1の電極31(第2の共通ノードC N<sub>12</sub>)は、第2番目の選択用トランジスタT R<sub>12</sub>を介してビット

40

50

線  $B L_1$  に接続されている。更には、第  $n$  番目（但し、 $n = 1, 2 \dots N$ ）のメモリユニット  $M U_{1n}$  において、第  $m$  番目（但し、 $m = 1, 2 \dots M$ ）のメモリセル  $M C_{1nm}$  の第 2 の電極は、メモリユニット間 ( $M U_{11}, M U_{12}$ ) で共通とされた第  $m$  番目のプレート線  $P L_m$  に接続されている。具体的には、第 1 番目のメモリユニット  $M U_{11}$  において、メモリセル  $M C_{11m}$  の第 2 の電極 23 は、プレート線  $P L_m$  に接続されている。また、第 2 番目のメモリユニット  $M U_{12}$  において、メモリセル  $M C_{12m}$  の第 2 の電極 33 は、プレート線  $P L_m$  に接続されている。

【 0 1 7 3 】

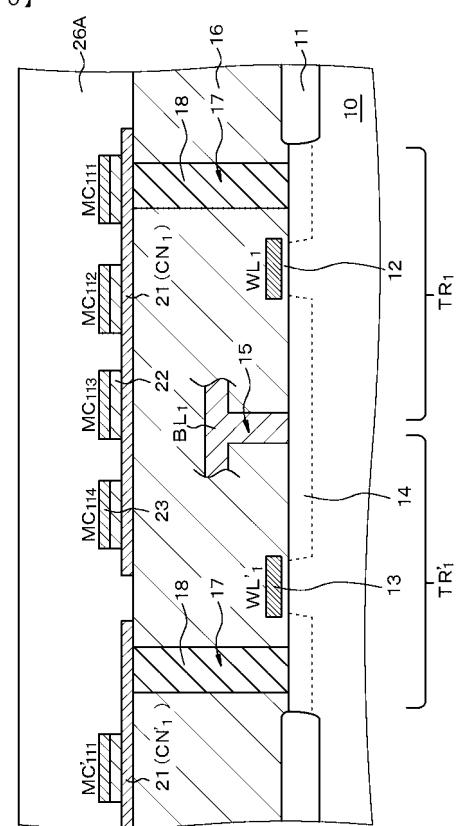

実施の形態 2 の不揮発性メモリにおいては、第 1 のメモリユニット  $M U_{11}$  を構成する各メモリセル  $M C_{11m}$  における強誘電体層 22 と、第 2 のメモリユニット  $M U_{12}$  を構成する各メモリセル  $M C_{12m}$  における強誘電体層 32 とを同一の材料から構成してもよいが、本発明の第 6 の態様に係る不揮発性メモリのように、上方に位置するメモリセルを構成する強誘電体層 32 の結晶化温度は、下方に位置するメモリセルを構成する強誘電体層 22 の結晶化温度よりも低い構成とすることが好ましい。具体的には、強誘電体層 22, 32 を、表 2 に例示した材料から構成することができる。

【 0 1 7 4 】

実施の形態 2 においては、2 つのメモリユニット  $M U_{11}, M U_{12}$  は、それぞれ、層間絶縁層 26 を介して積層されている。メモリユニット  $M U_{12}$  は絶縁膜 36 A で被覆されている。また、メモリユニット  $M U_{11}$  は、半導体基板 10 の上方に絶縁層 16 を介して形成されている。半導体基板 10 には素子分離領域 11 が形成されている。また、選択用トランジスタ  $T R_{11}, T R_{12}$  は、ゲート電極 13、ゲート絶縁膜 12、ソース／ドレイン領域 14 から構成されている。そして、第 1 の選択用トランジスタ  $T R_{11}$  及び第 2 の選択用トランジスタ  $T R_{12}$  の一方のソース／ドレイン領域 14 はコンタクトホール 15 を介してビット線  $B L_1$  に接続されている。また、第 1 の選択用トランジスタ  $T R_{11}$  の他方のソース／ドレイン領域 14 は、絶縁層 16 に形成された開口部 17 中に設けられた接続孔 18 を介して第 1 の共通ノード  $C N_{11}$  に接続されている。更には、第 2 の選択用トランジスタ  $T R_{12}$  の他方のソース／ドレイン領域 14 は、接続孔 18、絶縁層 16 上に形成された接続部 25、層間絶縁層 26 に形成された開口部 27 中に設けられた接続孔 28 を介して第 2 の共通ノード  $C N_{12}$  に接続されている。

【 0 1 7 5 】

ここで、ワード線  $W L_1$  は、図 6 の紙面垂直方向に延びている。また、第 2 の電極 23 は、図 6 の紙面垂直方向に隣接するメモリユニット  $M U_{21}$  を構成するメモリセルと共に通であり、プレート線  $P L_m$  を兼ねている。更には、第 2 の電極 32 も、図 6 の紙面垂直方向に隣接するメモリユニット  $M U_{22}$  を構成するメモリセルと共に通であり、プレート線  $P L_m$  を兼ねている。各メモリセルを結ぶこれらの各プレート線は、図 6 の紙面垂直方向に延びてあり、図示しない領域において接続孔を介して接続されている。また、メモリセル  $M C_{11m}$  とメモリセル  $M C_{12m}$  とは、垂直方向に揃っている。このような構造にすることによって、メモリユニットの占有面積を小さくすることができ、集積度の向上を図ることができる。

【 0 1 7 6 】

尚、図 5 に示した不揮発性メモリ  $M_2$  は、図 6 の模式的な一部断面図において、上述のとおり、不揮発性メモリ  $M_1$  と紙面垂直方向に隣接している。

【 0 1 7 7 】

更には、ビット線  $B L_1$  は、センスアンプ  $S A$  に接続されている。尚、ビット線  $B L_2$  も同じセンスアンプ  $S A$  に接続されているが、ビット線  $B L_2$  は、異なるセンスアンプ  $S A$  に接続されていてもよい。また、ビット線  $B L_1, B L_2$  は、ビット線  $B L_1, B L_2$  の延びる方向に隣接する他の不揮発性メモリとも共有されている。

【 0 1 7 8 】

そして、各メモリセル  $M C_{11m}, M C_{12m}$  ( $m = 1, 2, 3, 4$ ) に 1 ビットがデータとして記憶される。実際の不揮発性メモリにおいては、この 8 ビットを記憶するメモリユニッ

10

20

30

40

50

トの集合がアクセス単位ユニットとしてアレイ状に配設されている。

【0179】

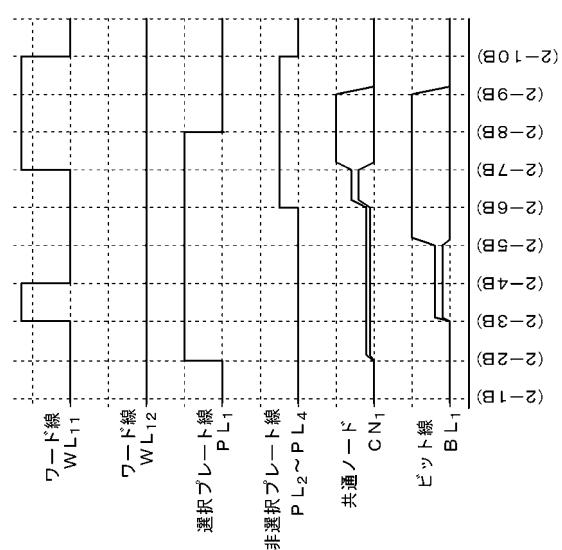

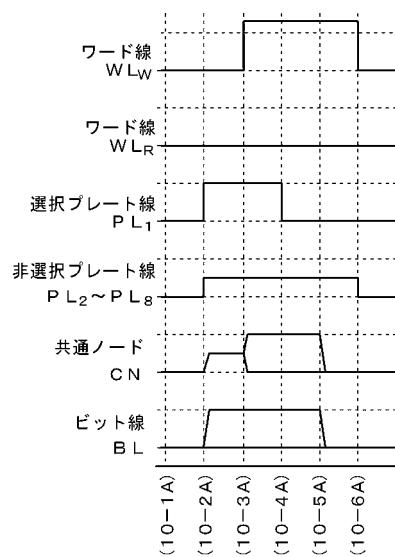

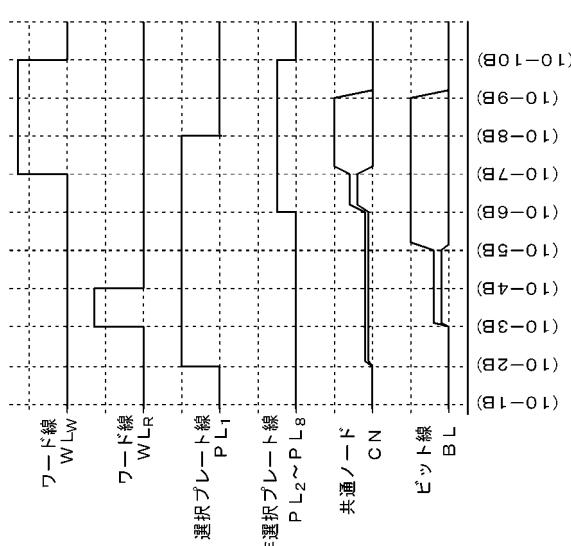

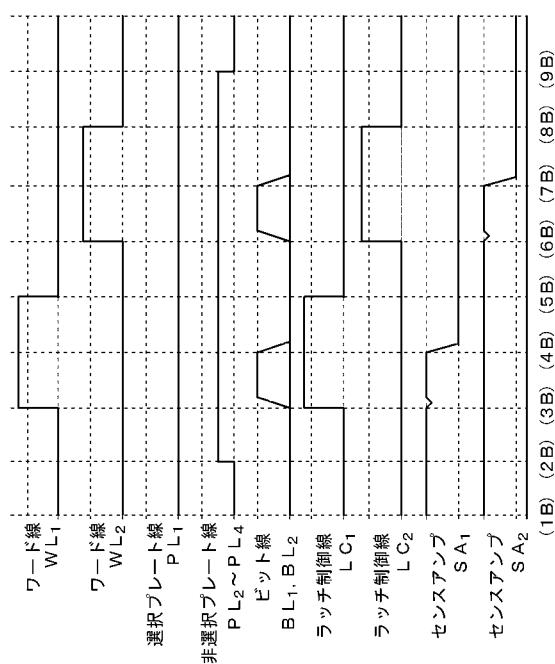

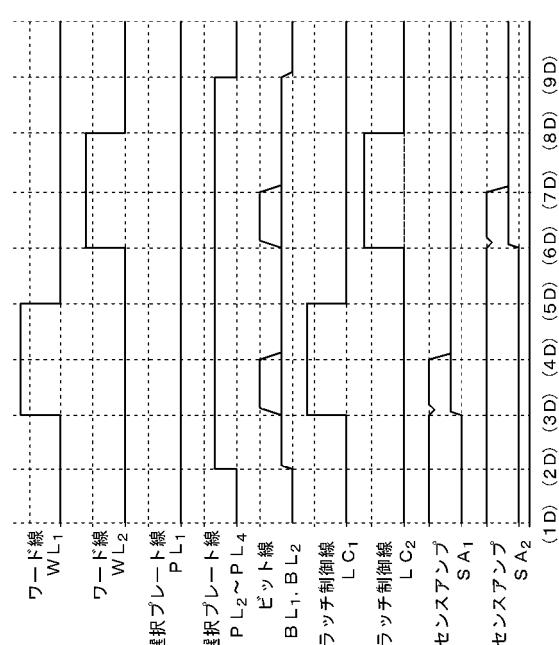

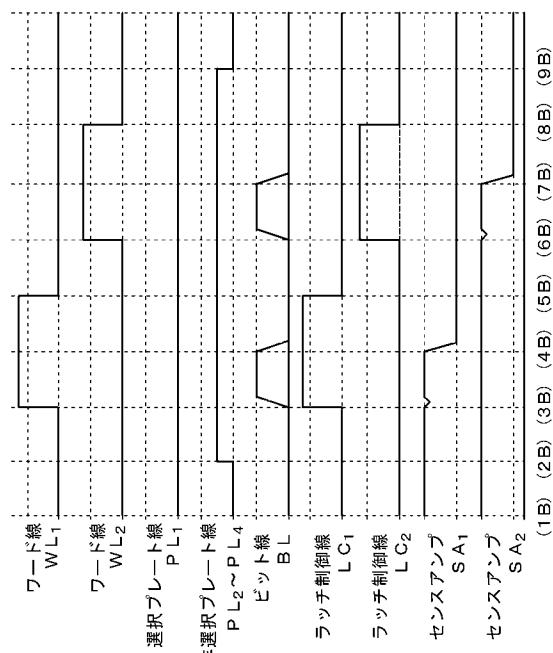

実施の形態2の不揮発性メモリにデータを書き込む方法の一例を、以下、説明する。尚、一例として、メモリセルMC<sub>111</sub>にデータを書き込むものとする。図7に動作波形を示す。尚、図7中、括弧内の数字は、以下に説明する工程の番号と対応している。

【0180】

(2-1A) 待機状態では、ビット線BL<sub>1</sub>、ワード線WL<sub>11</sub>, WL<sub>12</sub>、全プレート線PL<sub>m</sub>が0ボルトとなっている。更には、共通ノードCN<sub>11</sub>, CN<sub>12</sub>も0ボルトで浮遊状態となっている。

【0181】

(2-2A) データ書き込みの開始時、選択プレート線PL<sub>1</sub>の電位をV<sub>cc</sub>とし、非選択プレート線PL<sub>k</sub>(k=2, 3, 4)の電位を(1/2)V<sub>cc</sub>とする。これによって、浮遊状態の共通ノードCN<sub>11</sub>, CN<sub>12</sub>の電位は、プレート線PL<sub>M</sub>とのカップリングにより、概ね(1/2)V<sub>cc</sub>近傍まで上昇する。また、選択メモリセルMC<sub>111</sub>にデータ「1」を書き込む場合には、ビット線BL<sub>1</sub>の電位をV<sub>cc</sub>とし、データ「0」を書き込む場合には、ビット線BL<sub>1</sub>の電位を0ボルトとする。

10

【0182】

(2-3A) その後、第1の選択用トランジスタTR<sub>11</sub>をオン状態とする。これによって、第1の共通ノードCN<sub>11</sub>の電位は、選択メモリセルMC<sub>111</sub>にデータ「1」を書き込む場合には、V<sub>cc</sub>となり、データ「0」を書き込む場合には、0ボルトとなる。尚、選択プレート線PL<sub>1</sub>にはV<sub>cc</sub>が印加された状態にあるので、第1の共通ノードCN<sub>11</sub>の電位が0ボルトの場合、選択メモリセルMC<sub>111</sub>にデータ「0」が書き込まれる。一方、第1の共通ノードCN<sub>11</sub>の電位がV<sub>cc</sub>の場合、選択メモリセルMC<sub>111</sub>には何らデータが書き込まれない。浮遊状態にある第2の共通ノードCN<sub>12</sub>の電位は概ね(1/2)V<sub>cc</sub>近傍のままであるが故に、非選択メモリセルMC<sub>121</sub>にディスターべは発生しない。

20

【0183】

(2-4A) 次いで、選択プレート線PL<sub>1</sub>の電位を0ボルトとする。第1の共通ノードCN<sub>11</sub>の電位がV<sub>cc</sub>の場合、選択メモリセルMC<sub>111</sub>にデータ「1」が書き込まれる。選択メモリセルMC<sub>111</sub>に既にデータ「0」が書き込まれている場合には、選択メモリセルMC<sub>111</sub>に何ら変化は生じない。

30

【0184】

(2-5A) その後、ビット線BL<sub>1</sub>を0ボルトと印加する。

【0185】

(2-6A) 更に、非選択プレート線PL<sub>k</sub>を0ボルトとし、第1の選択用トランジスタTR<sub>11</sub>をオフ状態とする。

【0186】

他のメモリセルMC<sub>11m</sub>(m=2, 3, 4), MC<sub>12m</sub>(m=1, 2, 3, 4)にデータを書き込む場合には、同様の操作を繰り返す。このような書き込み動作においては、非選択メモリセルMC<sub>11k</sub>, MC<sub>12k</sub>に(±1/2)V<sub>cc</sub>のディスターべが発生するが、V<sub>cc</sub>の値を適切に設定することによって、非選択メモリセルMC<sub>11k</sub>, MC<sub>12k</sub>におけるデータの破壊を確実に防止することができる。

40

【0187】

次に、実施の形態2の不揮発性メモリからデータを読み出し、データを再書き込みする動作を、以下、説明する。尚、一例として、プレート線PL<sub>1</sub>に接続されたメモリセルMC<sub>111</sub>からデータを読み出し、データを再書き込みするものとする。図8に動作波形を示す。

【0188】

(2-1B) 待機状態では、ビット線BL<sub>1</sub>、ワード線WL<sub>11</sub>, WL<sub>12</sub>、全プレート線PL<sub>m</sub>が0ボルトとなっている。更には、共通ノードCN<sub>11</sub>, CN<sub>12</sub>も0ボルトで浮遊状態となっている。

【0189】

50

(2-2B) データ読み出し時、選択プレート線  $P_{L_1}$  に  $V_{cc}$  を印加する。このとき、選択メモリセル  $MC_{111}$  にデータ「1」が記憶されていれば、強誘電体層に分極反転が生じ、蓄積電荷量が増加し、第1の共通ノード  $CN_{11}$  の電位が上昇する。一方、選択メモリセル  $MC_{111}$  にデータ「0」が記憶されていれば、強誘電体層に分極反転が生ぜず、第1の共通ノード  $CN_{11}$  の電位は殆ど上昇しない。即ち、第1の共通ノード  $CN_{11}$  は、非選択メモリセルの強誘電体層を介して複数の非選択プレート線  $P_{L_k}$  にカップリングされているので、第1の共通ノード  $CN_{11}$  の電位は0ボルトに比較的近いレベルに保たれる。このようにして、選択メモリセル  $MC_{111}$  に記憶されたデータに依存して第1の共通ノード  $CN_{11}$  の電位に変化が生じる。従って、選択メモリセル  $MC_{111}$  の強誘電体層には、分極反転に十分な電界を与えることができる。

10

## 【0190】

(2-3B) 次に、ビット線  $BL_1$  を浮遊状態とし、第1の選択用トランジスタ  $TR_{11}$  をオン状態とする。これによって、選択メモリセル  $MC_{111}$  に記憶されたデータに基づき共通の第1の電極（第1の共通ノード  $CN_{11}$ ）に生じた電位により、ビット線  $BL_1$  に電位が生じる。

## 【0191】

(2-4B) 次いで、第1の選択用トランジスタ  $TR_{11}$  をオフ状態とする。そして、かかるビット線  $BL_1$  の電位をセンスアンプ  $SA$  にてラッチし、センスアンプ  $SA$  を活性化してデータを增幅し、データの読み出し動作を完了する。

## 【0192】

以上の動作によって、選択メモリセルに記憶されていたデータが一旦破壊されてしまうので、データの再書き込み動作を行う。

20

## 【0193】

(2-5B) そのために、先ず、ビット線  $BL_1$  をセンスアンプ  $SA$  によって充放電させ、ビット線  $BL_1$  に  $V_{cc}$  又は0ボルトを印加する。

## 【0194】

(2-6B) そして、非選択プレート線  $P_{L_k}$  ( $k = 2, 3, 4$ ) の電位を  $(1/2)V_c$  とする。

## 【0195】

(2-7B) その後、第1の選択用トランジスタ  $TR_{11}$  をオン状態とする。これによって、第1の共通ノード  $CN_{11}$  の電位はビット線  $BL_1$  の電位と等しくなる。即ち、選択メモリセル  $MC_{111}$  に記憶されていたデータが「1」の場合には、第1の共通ノード  $CN_{11}$  の電位は  $V_{cc}$  となり、選択メモリセル  $MC_{111}$  に記憶されていたデータが「0」の場合には、第1の共通ノード  $CN_{11}$  の電位は0ボルトとなる。選択プレート線  $P_{L_1}$  の電位は  $V_{cc}$  のままであるが故に、第1の共通ノード  $CN_{11}$  の電位が0ボルトの場合、選択メモリセル  $MC_{111}$  にはデータ「0」が再書き込みされる。

30

## 【0196】

(2-8B) 次に、選択プレート線  $P_{L_1}$  の電位を0ボルトとする。これによって、選択メモリセル  $MC_{111}$  に記憶されていたデータが「1」の場合には、第1の共通ノード  $CN_{11}$  の電位が  $V_{cc}$  であるが故に、データ「1」が再書き込みされる。選択メモリセル  $MC_{111}$  にデータ「0」が既に再書き込みされていた場合には、選択メモリセル  $MC_{111}$  に変化は生じない。

40

## 【0197】

(2-9B) その後、ビット線  $BL_1$  を0ボルトとする。

## 【0198】

(2-10B) 最後に、非選択プレート線  $P_{L_k}$  を0ボルトとし、第1の選択用トランジスタ  $TR_{11}$  をオフ状態とする。

## 【0199】

他のメモリセル  $MC_{11m}$  ( $m = 2, 3, 4$ ) ,  $MC_{12m}$  ( $m = 1, 2, 3, 4$ ) からデータを読み出し、データを再書き込みする場合には、同様の操作を繰り返す。

50

## 【0200】

実施の形態2の不揮発性メモリにおいて、ワード線WL<sub>11</sub>又はワード線WL<sub>12</sub>を選択した場合、メモリユニットMU<sub>11</sub>又はメモリユニットMU<sub>12</sub>がアクセスされ、ビット線BL<sub>1</sub>にのみ、記憶されたデータに相当する電位が出現する。ここで、同じセンスアンプSAに接続されたビット線BL<sub>2</sub>に、データ「1」の読み出し電位と、データ「0」の読み出し電位の中間の参照電位を与えてもよい。一方、ワード線WL<sub>21</sub>又はワード線WL<sub>22</sub>を選択した場合、メモリユニットMU<sub>21</sub>又はメモリユニットMU<sub>22</sub>がアクセスされ、ビット線BL<sub>2</sub>にのみ、記憶されたデータに相当する電位が出現する。ここで、同じセンスアンプSAに接続されたビット線BL<sub>1</sub>に、データ「1」の読み出し電位と、データ「0」の読み出し電位の中間の参照電位を与えてもよい。

10

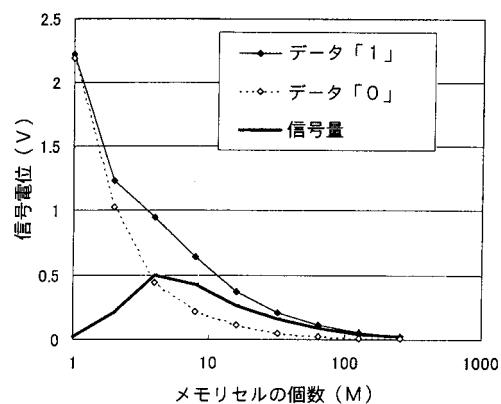

## 【0201】

実施の形態2の不揮発性メモリにおいては、信号量（電位差）が後述する実施の形態5と比較して約半分となり、しかも、参照電位のばらつき等から動作マージンは低下するが、不揮発性メモリの集積度は約2倍になる。

## 【0202】

尚、この場合にも、プレート線PL<sub>m</sub>を共有する非アクセスのメモリセルにもディスター

ブが発生するので、4つのメモリユニットMU<sub>11</sub>, MU<sub>12</sub>, MU<sub>21</sub>, MU<sub>22</sub>を一括して、且つ、連続的にアクセスすることが望ましい。即ち、ワード線WL<sub>11</sub>をアクセスした場合は、共通ノードCN<sub>11</sub>におけるメモリセルMC<sub>11m</sub>の全てを順次アクセスし、次に、ワード線WL<sub>12</sub>をアクセスする。更に、同様に、ワード線WL<sub>21</sub>、ワード線WL<sub>22</sub>を連続してアクセスする。これによって、共通ノードCN<sub>11</sub>, CN<sub>12</sub>, CN<sub>21</sub>, CN<sub>22</sub>におけるメモリセルMC<sub>11m</sub>, MC<sub>12m</sub>, MC<sub>21m</sub>, MC<sub>22m</sub>の全てからデータを読み出し、再書き込みを行ってディスター

ブによる劣化を回復させる。

20

## 【0203】

実施の形態2のメモリアレイの構成上の限界寸法は、ワード線WL<sub>11</sub>, WL<sub>12</sub>, WL<sub>21</sub>, WL<sub>22</sub>、若しくはプレート線PL<sub>m</sub>のピッチと、ビット線BL<sub>1</sub>, BL<sub>2</sub>のピッチとで規定され、プレート線1本とビット線1本で囲まれた領域に2ビットが記憶される。従って、限界寸法は2F<sup>2</sup>である。

## 【0204】

また、実施の形態2の不揮発性メモリにおいては、4本のワード線と4本のプレート線との2次元マトリックスにより、ロー・アドレスの選択が行われる。即ち、ワード線4本、プレート線4本の組み合わせで、ロー方向の16ビットのアクセスが可能であり、ロー・アドレスの選択に必要とされるドライバは、1アドレス当たり0.5本でよい。従って、従来型のメモリセル構造と比較して、駆動用の信号線を大幅に減少させることができ、周辺回路を大幅に削減することができる。

30

## 【0205】

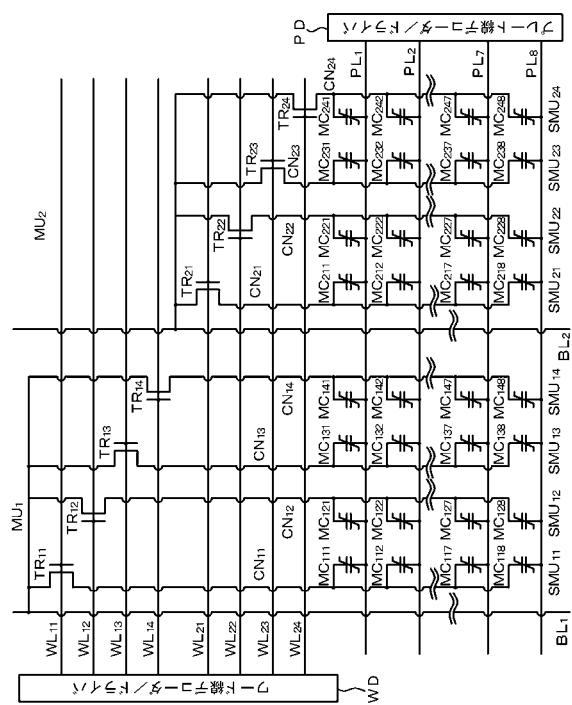

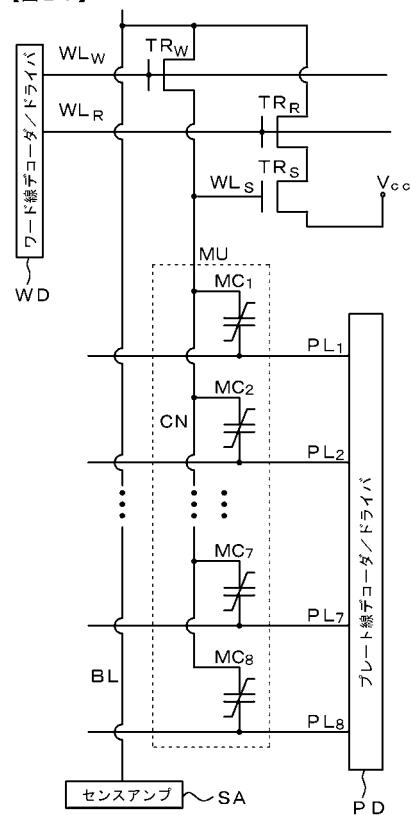

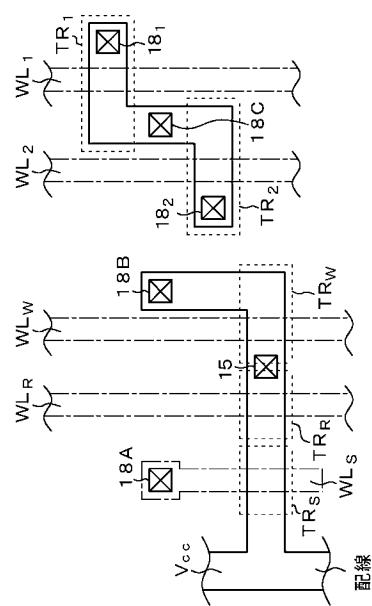

## (実施の形態3)

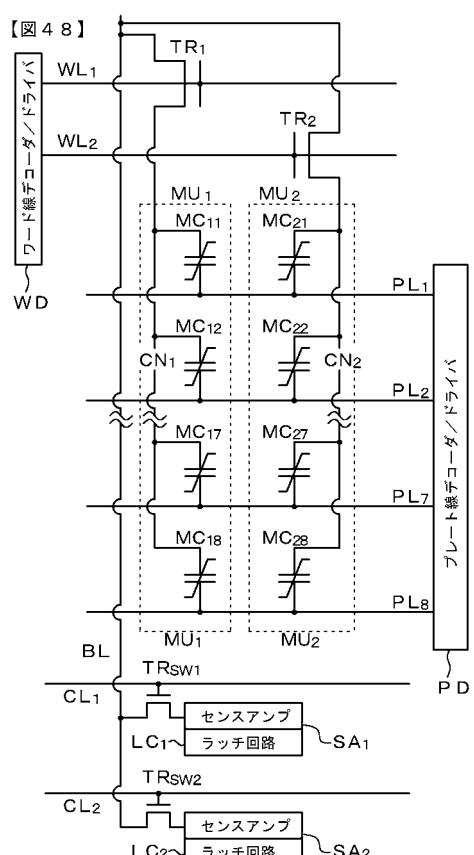

実施の形態3は、実施の形態2の不揮発性メモリの変形例である。その回路図を図9に示し、模式的な一部断面図を図10に示す。実施の形態3の不揮発性メモリにおいては、メモリユニット数Nが4である。即ち、この不揮発性メモリは、ビット線BL<sub>1</sub>と、4個の選択用トランジスタTR<sub>1N</sub>と、それぞれが8個のメモリセルMC<sub>1NM</sub>から構成された、4個のメモリユニットMU<sub>1N</sub>と、8本のプレート線PL<sub>M</sub>から構成されている。

40

## 【0206】

また、各メモリセルMC<sub>1nm</sub>は、第1の電極21, 31, 41, 51と強誘電体層22, 32, 42, 52と第2の電極23, 33, 43, 53とから成る。各メモリユニットMU<sub>1n</sub>において、メモリセルMC<sub>1nm</sub>の第1の電極は共通である。即ち、共通ノードCN<sub>1n</sub>を構成する。

## 【0207】

また、メモリユニットMU<sub>1n</sub>における共通の第1の電極（共通ノードCN<sub>1n</sub>）は、選択用トランジスタTR<sub>1n</sub>を介してビット線BL<sub>1</sub>に接続されている。更には、メモリユニット

50

$MU_{1n}$ において、メモリセル $MC_{1nm}$ の第2の電極は、メモリユニット間( $MU_{11}, MU_{12}, MU_{13}, MU_{14}$ )で共通とされたプレート線 $PL_m$ に接続されている。

#### 【0208】

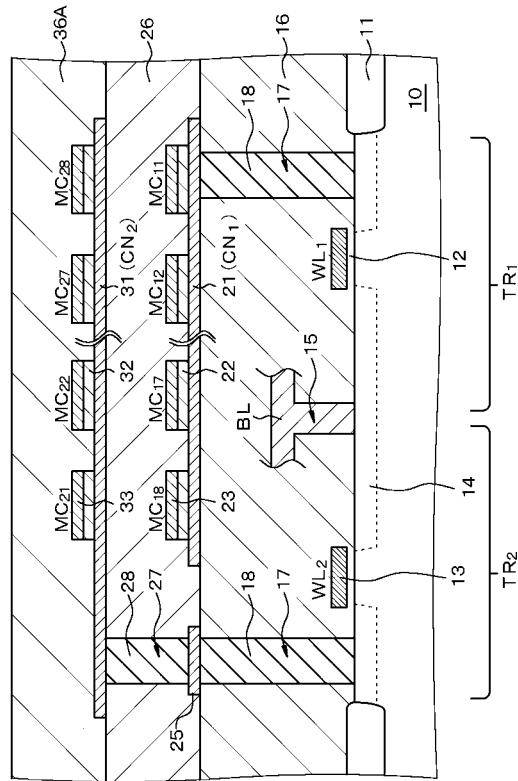

実施の形態3においては、4つのメモリユニット $MU_{11}, MU_{12}, MU_{13}, MU_{14}$ は、それぞれ、層間絶縁層26, 36, 46を介して積層されている。メモリユニット $MU_{14}$ は絶縁膜56Åで被覆されている。また、メモリユニット $MU_{11}$ は、半導体基板10の上方に絶縁層16を介して形成されている。半導体基板10には素子分離領域11が形成されている。また、MOS型FETから構成された選択用トランジスタ $TR_{11}, TR_{12}, TR_{13}, TR_{14}$ は、ゲート電極13、ゲート絶縁膜12、ソース/ドレイン領域14から構成されている。そして、第1の選択用トランジスタ $TR_{11}$ 、第2の選択用トランジスタ $TR_{12}$ 、第3の選択用トランジスタ $TR_{13}$ 、第4の選択用トランジスタ $TR_{14}$ の一方のソース/ドレイン領域14はコンタクトホール15を介してピット線 $BL_1$ に接続されている。

また、第1の選択用トランジスタ $TR_{11}$ の他方のソース/ドレイン領域14は、絶縁層16に形成された開口部17中に設けられた接続孔18を介して第1の共通ノード $CN_{11}$ に接続されている。更には、第2の選択用トランジスタ $TR_{12}$ の他方のソース/ドレイン領域14は、接続孔18、絶縁層16上に形成された接続部25、層間絶縁層26に形成された開口部27中に設けられた接続孔28を介して第2の共通ノード $CN_{12}$ に接続されている。また、第3の選択用トランジスタ $TR_{13}$ の他方のソース/ドレイン領域14は、接続孔18、接続部25、接続孔28、層間絶縁層26上に形成された接続部35、層間絶縁層36に形成された開口部37中に設けられた接続孔38を介して第3の共通ノード $CN_{13}$ に接続されている。更には、第4の選択用トランジスタ $TR_{14}$ の他方のソース/ドレイン領域14は、接続孔18、接続部25、接続孔28、接続部35、接続孔38、層間絶縁層36上に形成された接続部45、層間絶縁層46に形成された開口部47中に設けられた接続孔48を介して第4の共通ノード $CN_{14}$ に接続されている。

#### 【0209】

ワード線 $WL_{11}, WL_{12}, WL_{13}, WL_{14}$ は、図10の紙面垂直方向に延びている。また、第2の電極21は、図10の紙面垂直方向に隣接するメモリセル $MC_{21m}$ と共にあり、プレート線 $PL_m$ を兼ねている。更には、第2の電極33, 43, 53も、図10の紙面垂直方向に隣接するメモリセル $MC_{22m}, MC_{23m}, MC_{24m}$ と共に、プレート線 $PL_m$ を兼ねている。各メモリセル $MC_{11m}, MC_{12m}, MC_{13m}, MC_{14m}, MC_{21m}, MC_{22m}, MC_{23m}, MC_{24m}$ を結ぶこれらの各プレート線 $PL_m$ は、図10の紙面垂直方向に延びてあり、図示しない領域において接続孔を介して接続されている。また、メモリユニット $MU_{1n}$ は、垂直方向に揃っている。このような構造にすることによって、メモリセルの占有面積をより一層小さくすることができ、集積度のより一層の向上を図ることができる。

#### 【0210】

実施の形態3の不揮発性メモリの動作は、実施の形態2の不揮発性メモリの動作と実質的に同一とすることができますので、詳細な説明は省略する。尚、各メモリセル $MC_{1nm}$ ( $n = 1 \sim 4, m = 1 \sim 8$ )に1ビットがデータとして記憶される。実際の不揮発性メモリにおいては、この32ビットを記憶するメモリユニットの集合がアクセス単位ユニットとしてアレイ状に配設されている。そして、このアレイ構成では、プレート線 $PL_m$ の最小ピッチでロー方向の寸法が規定され、プレート線1本、ビット線2本が囲む領域に4ビットが記憶される。従って、アレイ構成上の限界セル面積は $2F^2$ である。また、4本のワード線 $WL_{11} \sim WL_{14}$ と8本のプレート線 $PL_m$ ( $m = 1 \sim 8$ )との2次元マトリクスにより、ロードレスの選択が行われるようになっている。即ち、ワード線4本、プレート線8本の組み合わせで、口向の32ビットのアクセスが可能であり、ロードレスの選択に必要なドライバは、1アドレス当たり0.375本と少ない。従って、従来型セル選択に比較して駆動する信号線を低減することができ、周辺回路を大幅に削減することができる。

#### 【0211】

実施の形態3の不揮発性メモリにおいては、第1のメモリユニット $MU_{11}$ を構成する各メ

10

20

30

40

50

モリセルMC<sub>11m</sub>における強誘電体層22と、第2のメモリユニットMU<sub>12</sub>を構成する各メモリセルMC<sub>12m</sub>における強誘電体層32と、第3のメモリユニットMU<sub>13</sub>を構成する各メモリセルMC<sub>13m</sub>における強誘電体層42と、第4のメモリユニットMU<sub>14</sub>を構成する各メモリセルMC<sub>14m</sub>における強誘電体層52とを、同一の材料から構成してもよいが、本発明の第6の態様に係る不揮発性メモリのように、上方に位置するメモリセルを構成する強誘電体層の結晶化温度は、下方に位置するメモリセルを構成する強誘電体層の結晶化温度よりも低い構成とすることが好ましい。具体的には、強誘電体層22, 32, 42, 52を、以下の表10あるいは表11に例示する材料から構成することができる。

【0212】

[表10]

10

|         | 材料                                                                         | 結晶化温度 |

|---------|----------------------------------------------------------------------------|-------|

| 強誘電体層52 | Bi <sub>2</sub> Sr (Ta <sub>1.5</sub> Nb <sub>0.5</sub> ) O <sub>9</sub>   | 700°C |

| 強誘電体層42 | Bi <sub>2</sub> Sr (Ta <sub>1.65</sub> Nb <sub>0.35</sub> ) O <sub>9</sub> | 715°C |

| 強誘電体層32 | Bi <sub>2</sub> Sr (Ta <sub>1.8</sub> Nb <sub>0.2</sub> ) O <sub>9</sub>   | 730°C |

| 強誘電体層22 | Bi <sub>2</sub> SrTa <sub>2</sub> O <sub>9</sub>                           | 750°C |

【0213】

[表11]

20

|         | 材料                                                                       | 結晶化温度 |

|---------|--------------------------------------------------------------------------|-------|

| 強誘電体層52 | PbTiO <sub>3</sub>                                                       | 600°C |

| 強誘電体層42 | Pb (Zr <sub>0.48</sub> Ti <sub>0.52</sub> ) O <sub>3</sub>               | 650°C |

| 強誘電体層32 | Bi <sub>2</sub> Sr (Ta <sub>1.5</sub> Nb <sub>0.5</sub> ) O <sub>9</sub> | 700°C |

| 強誘電体層22 | Bi <sub>2</sub> SrTa <sub>2</sub> O <sub>9</sub>                         | 750°C |

【0214】

尚、強誘電体薄膜を構成する材料として、例えば、Bi<sub>2</sub>Sr (Ta<sub>1.8</sub>Nb<sub>0.2</sub>) O<sub>9</sub>を使用する場合、結晶化促進のための熱処理を、730°Cの酸素ガス雰囲気で1時間、行い、例えば、Bi<sub>2</sub>Sr (Ta<sub>1.5</sub>Nb<sub>0.5</sub>) O<sub>9</sub>を使用する場合、結晶化促進のための熱処理を、700°Cの酸素ガス雰囲気で1時間、行う。また、強誘電体薄膜を構成する材料として、例えば、Bi<sub>2</sub>Sr (Ta<sub>1.65</sub>Nb<sub>0.35</sub>) O<sub>9</sub>を使用する場合、結晶化促進のための熱処理を、715°Cの酸素ガス雰囲気で1時間、行い、例えば、Pb (Zr<sub>0.48</sub>Ti<sub>0.52</sub>) O<sub>3</sub>を使用する場合、結晶化促進のための熱処理を、650°Cの酸素ガス雰囲気で1時間、行い、PbTiO<sub>3</sub>を使用する場合、結晶化促進のための熱処理を、600°Cの酸素ガス雰囲気で1時間、行う。

30

【0215】

(実施の形態4)

40

実施の形態4は、本発明の第3の態様に係る不揮発性メモリに関する。実施の形態4の不揮発性メモリの模式的な一部断面図を図11に示す。尚、実施の形態4の不揮発性メモリの回路図は、図9に示したと同様である。

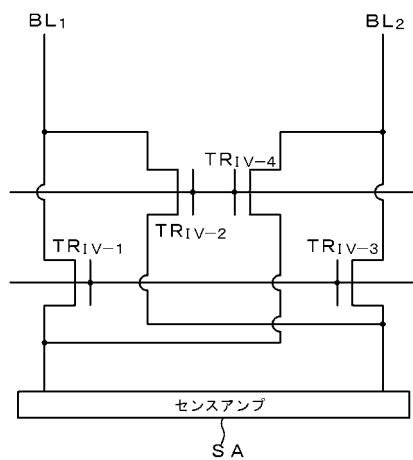

【0216】