(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6031252号

(P6031252)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年10月28日(2016.10.28)

(51) Int.Cl.

F 1

H01L 21/8242 (2006.01)

H01L 27/108 (2006.01)

H01L 27/10

321

請求項の数 8 (全 35 頁)

(21) 出願番号 特願2012-104552 (P2012-104552)

(22) 出願日 平成24年5月1日 (2012.5.1)

(65) 公開番号 特開2012-253327 (P2012-253327A)

(43) 公開日 平成24年12月20日 (2012.12.20)

審査請求日 平成27年4月9日 (2015.4.9)

(31) 優先権主張番号 特願2011-103766 (P2011-103766)

(32) 優先日 平成23年5月6日 (2011.5.6)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 坂田 淳一郎

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 上田 智志

最終頁に続く

(54) 【発明の名称】半導体装置、記憶装置および半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面上のソース電極及びドレイン電極と、

前記絶縁表面上、前記ソース電極上及び前記ドレイン電極上の酸化物半導体層と、

前記酸化物半導体層を介して、前記ソース電極または前記ドレイン電極の一方と重なる

第1の電極と、

前記酸化物半導体層及び前記第1の電極に接するゲート絶縁層と、

前記ゲート絶縁層を介して、前記第1の電極と重なるゲート電極と、を有し、

前記酸化物半導体層の前記ソース電極または前記ドレイン電極の一方と前記ソース電極

または前記ドレイン電極の他方とに挟まれた領域は、チャネル形成領域としての機能を有

し、

前記第1の電極と、前記ソース電極または前記ドレイン電極の一方と、前記酸化物半導

体とが重なる領域は、容量素子としての機能を有し、

前記第1の電極は、前記ソース電極または前記ドレイン電極の他方とは重ならず、

前記ゲート電極は、前記ソース電極または前記ドレイン電極の他方とは重ならない半導

体装置。

## 【請求項 2】

絶縁表面上のソース電極及びドレイン電極と、

前記絶縁表面上、前記ソース電極上及び前記ドレイン電極上の酸化物半導体層と、

前記酸化物半導体層を介して、前記ソース電極または前記ドレイン電極の一方と重なる

10

20

第 1 の電極と、

前記酸化物半導体層及び前記第 1 の電極に接するゲート絶縁層と、

前記ゲート絶縁層を介して、前記第 1 の電極と重なるゲート電極と、

前記ゲート電極上の層間絶縁層と、

前記層間絶縁層の開口部において、前記ゲート電極と電気的に接続される配線と、を有し、

前記酸化物半導体層の前記ソース電極または前記ドレイン電極の一方と前記ソース電極または前記ドレイン電極の他方とに挟まれた領域は、チャネル形成領域としての機能を有し、

前記第 1 の電極と、前記ソース電極または前記ドレイン電極の一方と、前記酸化物半導体とが重なる領域は、容量素子としての機能を有し、

前記第 1 の電極は、前記ソース電極または前記ドレイン電極の他方とは重ならず、

前記ゲート電極は、前記ソース電極または前記ドレイン電極の他方とは重ならない半導体装置。

【請求項 3】

請求項 1 または 2 において、

前記第 1 の電極が定電位または接地電位に接続された半導体装置。

【請求項 4】

請求項 1 乃至 3 のいずれか一において、

前記酸化物半導体層が、I n、G a、S n 及び Z n から選ばれた一種以上の元素を含んでなる酸化物半導体材料を有する半導体装置。

【請求項 5】

請求項 1 乃至 4 のいずれか一に記載の半導体装置を有する記憶装置。

【請求項 6】

絶縁表面上にソース電極及びドレイン電極を形成し、

前記絶縁表面上、前記ソース電極上及び前記ドレイン電極上に酸化物半導体層を形成し、

、前記酸化物半導体層を介して、前記ソース電極または前記ドレイン電極の一方と重なり、前記ソース電極または前記ドレイン電極の他方と重ならない第 1 の電極を形成し、

前記酸化物半導体層及び前記第 1 の電極に接するゲート絶縁層を形成し、

前記第 1 の電極と重なり、前記ソース電極または前記ドレイン電極の他方と重ならないように、前記ゲート絶縁層上に、ゲート電極を形成し、

前記ゲート絶縁層及び前記ゲート電極上に層間絶縁層を形成し、

前記層間絶縁層に、前記ゲート電極に達するコンタクトホールを形成し、

前記酸化物半導体層の前記ソース電極または前記ドレイン電極の一方と前記ソース電極または前記ドレイン電極の他方とに挟まれた領域は、チャネル形成領域としての機能を有し、

前記第 1 の電極と、前記ソース電極または前記ドレイン電極の一方と、前記酸化物半導体とが重なる領域は、容量素子としての機能を有する半導体装置の作製方法。

【請求項 7】

絶縁表面上にソース電極及びドレイン電極を形成し、

前記絶縁表面上、前記ソース電極上及び前記ドレイン電極上に酸化物半導体層を形成し、

、前記酸化物半導体層を介して、前記ソース電極または前記ドレイン電極の一方と重なり、前記ソース電極または前記ドレイン電極の他方と重ならない第 1 の電極を形成し、

前記酸化物半導体層及び前記第 1 の電極に接するゲート絶縁層を形成し、

前記第 1 の電極と重なり、前記ソース電極または前記ドレイン電極の他方と重ならないように、前記ゲート絶縁層上に、ゲート電極を形成し、

前記ゲート絶縁層及び前記ゲート電極上に層間絶縁層を形成し、

前記層間絶縁層の表面に平坦化処理を行い、

10

20

30

40

50

前記酸化物半導体層の前記ソース電極または前記ドレイン電極の一方と前記ソース電極または前記ドレイン電極の他方とに挟まれた領域は、チャネル形成領域としての機能を有し、

前記第1の電極と、前記ソース電極または前記ドレイン電極の一方と、前記酸化物半導体とが重なる領域は、容量素子としての機能を有する半導体装置の作製方法。

**【請求項8】**

請求項7において、

前記平坦化処理は化学機械的研磨によって行う半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

10

**【0001】**

本発明は、半導体装置、記憶装置および半導体装置の作製方法に関するものである。

**【背景技術】**

**【0002】**

半導体素子を利用した半導体装置、例えば記憶装置では、電力の供給が停止されると記憶内容が失われる揮発性の記憶装置と、電力の供給が停止しても記憶内容が保持される不揮発性の記憶装置とに大別され、データ保持および低消費電力化の観点から、不揮発性の記憶装置が注目を浴びている。

**【0003】**

20

不揮発性記憶装置の代表例としては、フラッシュメモリがある。フラッシュメモリは、トランジスタのゲート電極とチャネル形成領域との間にフローティングゲートを有し、当該フローティングゲートに電荷を保持させることで記憶を行うため、データの保持期間は極めて長く（半永久的）、揮発性記憶装置で必要なリフレッシュ動作が不要であるという利点を有している（例えば、特許文献1参照）。

**【0004】**

しかし、トランジスタを構成するゲート絶縁層が、書き込みの際に生じるトンネル電流によって劣化するため、繰り返し書き込み動作や消去動作を行うことによりゲート絶縁層が劣化し、記憶素子が機能しなくなるという問題が生じる。この問題の影響を緩和するために、例えば、各記憶素子の書き込み回数を均一化する手法が採られるが、これを実現するためには、複雑な周回路が必要となり、又、寿命の問題が根本的に解消されるには至らない。つまり、フラッシュメモリは、情報の書き換え頻度が高い用途には不向きであるといえる。

30

**【0005】**

また、揮発性記憶装置の代表的な例としては、DRAM (Dynamic Random Access Memory) がある。DRAMの記憶素子は、書き込みおよび読み出し用のトランジスタとキャパシタによって構成されており、書き込みおよび読み出しの動作によりゲート絶縁層が劣化するということはない。しかし、情報を電荷としてキャパシタに蓄えているため、トランジスタをオフ状態としていてもソースとドレイン間でリーク電流が生じるなどにより、トランジスタが選択されていない状況においても電荷が流出、または流入するため、データの保持時間が短いという問題がある。このため、所定の周期で再度の書き込み動作（リフレッシュ動作）が必要であり、消費電力を十分に低減することは困難である。

40

**【0006】**

揮発性記憶装置の別の例としてはSRAM (Static Random Access Memory) がある。SRAMは、フリップフロップなどの回路を用いて記憶内容を保持するためリフレッシュ動作が不要であるという特徴を有している反面、半導体装置中における記憶装置の専有面積が大きくなってしまうという問題がある。また、電力の供給がなくなると記憶内容が失われるという点については、DRAMと変わることはない。

**【先行技術文献】**

**【特許文献】**

50

## 【0007】

【特許文献1】特開昭57-105889号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

前述のように、フラッシュメモリ等の不揮発性メモリに用いられているトランジスタは、フローティングゲートを有するため記憶内容の保持特性に優れている反面、記憶内容の書き換えに高い消費電力が必要、書き換えの際にゲート電極が劣化するため書き込み回数に制限があるといった問題がある。また、DRAM等の揮発性メモリに用いられているトランジスタは、書き込み回数の制限はないが、キャパシタに蓄えられた記憶内容（電荷）を保持することが難しく、記憶内容を保持するためには定期的にリフレッシュ動作を行う必要がある。10

## 【0009】

加えて、記憶装置には今後更なる高集積化が求められる。

## 【0010】

そこで、本発明の一態様は、書き込み回数に制限がなく、消費電力が低く、記憶内容（電荷）の保持特性が改善され、かつ小型化に適した構造の半導体装置を提供することを目的の一とする。また、該半導体装置を有する、消費電力が低く、かつ高集積化の成された記憶装置を提供することを目的の一とする。

【課題を解決するための手段】20

## 【0011】

本発明では、トランジスタのオフ電流を十分に小さくすることができる酸化物半導体材料を半導体膜として用いてトランジスタを構成する。酸化物半導体材料を用いることで、トランジスタがオフ状態（ゲート電極に加わる電圧がしきい値電圧以下の状態）における、ソースとドレイン間でのリーコンダクション電流を極めて低くすることができるため、消費電力の低減が可能となる。

## 【0012】

また、本発明では、酸化物半導体層を挟んでソース電極（またはドレイン電極。）と重なる位置に第1の電極を設け、ゲート電極を、第1の電極方向に延在して第1の電極と重なる構造とし、加えて、第1の電極と重なる位置において、層間絶縁層上に設けられた配線とゲート電極が接続する構造とした。30

## 【0013】

上述構造では、第1の電極と、トランジスタの構成要素の一部であるソース電極（またはドレイン電極。）および酸化物半導体層を用いて、トランジスタと重なる位置に容量素子を設けることができ、加えて、第1の電極と重なる位置（つまり、容量素子と重なる位置。）でゲート電極と層間絶縁層上に設けられた配線を接続することができる。これにより、半導体装置の製造時間や製造コストを低減でき、また、半導体装置を高集積化できる。

## 【0014】

また、酸化物半導体材料を用いて形成された半導体層はリーコンダクション電流が極めて低いため、トランジスタのソース電極（またはドレイン電極。）と容量素子が接続された構造を有する記憶装置は、容量素子に蓄えられた記憶内容（電荷）を長時間保持することができるため、記憶内容（電荷）の保持特性改善を図ることができる。40

## 【0015】

すなわち、本発明の一態様は、絶縁表面上のソース電極およびドレイン電極と、絶縁表面、ソース電極およびドレイン電極上の酸化物半導体層と、ソース電極またはドレイン電極の一方と重なる、酸化物半導体層上の第1の電極と、酸化物半導体層および第1の電極を覆うゲート絶縁層と、第1の電極と重なる、ゲート絶縁層上のゲート電極と、ゲート絶縁層およびゲート電極上の層間絶縁層を有し、少なくとも第1の電極と重なるゲート電極の一部が層間絶縁層に設けられたコンタクトホールから露出する半導体装置である。

【0016】50

また、本発明の一態様は、上記構成において、第1の電極が接地電位や共通電極などの固定電位に接続された半導体装置である。

【0017】

当該構造では第1の電極が定電位（好ましくは接地電位。）となることにより、ゲート電極の電位が変化した場合でも容量素子に印加される電位は変化しないため、容量素子には安定した電荷を蓄えることができる。

【0018】

また、本発明の一態様は、上記構成において、酸化物半導体層は、In、Ga、Sn及びZnから選ばれた一種以上の元素を含んでいる半導体装置である。

【0019】

また、本発明の一態様は、上記各構成の半導体装置を有する記憶装置である。

10

【0020】

また、本発明の一態様は、絶縁表面上にソース電極およびドレイン電極を形成し、絶縁表面、ソース電極およびドレイン電極上に酸化物半導体層を形成し、酸化物半導体層上に、ソース電極またはドレイン電極の一方と重なる第1の電極を形成し、酸化物半導体層および第1の電極を覆うゲート絶縁層を形成し、ゲート絶縁層上に第1の電極と重なるゲート電極を形成し、ゲート絶縁層およびゲート電極上に層間絶縁層を形成する。そして、ゲート電極の一部が層間絶縁層の表面に露出するように平坦化処理を行う半導体装置の作製方法である。

【0021】

なお、本明細書等において、「概略垂直」及び「概略平行」の用語は、厳密な垂直及び平行を要しない意味で用いる。

20

【0022】

なお、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

【0023】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

30

【0024】

また、本明細書等において「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0025】

また、本明細書等において「第1」、「第2」等の数詞の付く用語は、要素を区別するために便宜的に用いているものであり、数的に限定するものではなく、また配置及び段階の順序を限定するものでもない。なお、本明細書では2枚の基板に対して膜、層、材料及び基板などを形成していく工程を説明するため、同じ膜、層、材料及び基板でも異なる数詞を用いている場合がある。

40

【0026】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

50

## 【発明の効果】

## 【0027】

酸化物半導体材料を半導体層として用いてトランジスタを構成することで、ソースとドレイン間でのリーク電流を極めて低くすることができるため、消費電力の低減が可能となる。

## 【0028】

また、酸化物半導体層を挟んでソース電極（またはドレイン電極）と重なる位置に第1の電極を設け、ゲート電極を、第1の電極と重なるようにゲート絶縁層上に設ける。第1の電極は接地電位や共通電位などの固定電位に接続する構造とした。これにより、トランジスタと重なる位置に容量素子を設けることができ、加えて、容量素子と重なる位置でゲート電極と層間絶縁層上に設けられた配線とを接続することができるため、半導体装置を高集積化できる。そして、当該半導体装置を少なくとも一部に用いた記憶装置は、消費電力の低減および小型化を実現できる。

10

## 【0029】

また、酸化物半導体材料を用いて形成された半導体層はリーク電流が極めて低いため、トランジスタのソース電極（またはドレイン電極。）と容量素子が接続された構造を有する記憶装置は、容量素子に蓄えられた記憶内容（電荷）を長時間保持することができるため、記憶内容（電荷）の保持特性改善を実現できる。

## 【図面の簡単な説明】

## 【0030】

20

【図1】実施の形態1に記載された半導体装置の構成を説明する図。

【図2】実施の形態1に記載された半導体装置の作製方法を説明する図。

【図3】実施の形態1に記載された半導体装置の作製方法を説明する図。

【図4】実施の形態1の半導体装置との比較説明に用いる半導体装置の構成図。

【図5】実施の形態2に記載された半導体装置の構成を説明する図。

【図6】実施の形態2に記載された半導体装置の作製方法を説明する図。

【図7】半導体装置を用いた記憶装置の説明図。

【図8】酸化物半導体層の結晶成長を説明する図。

【図9】半導体装置を用いた記憶装置の説明図。

【図10】記憶装置を少なくとも一部に用いたCPUの説明図。

30

【図11】電子機器の説明図。

## 【発明を実施するための形態】

## 【0031】

開示する発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

## 【0032】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

40

## 【0033】

（実施の形態1）

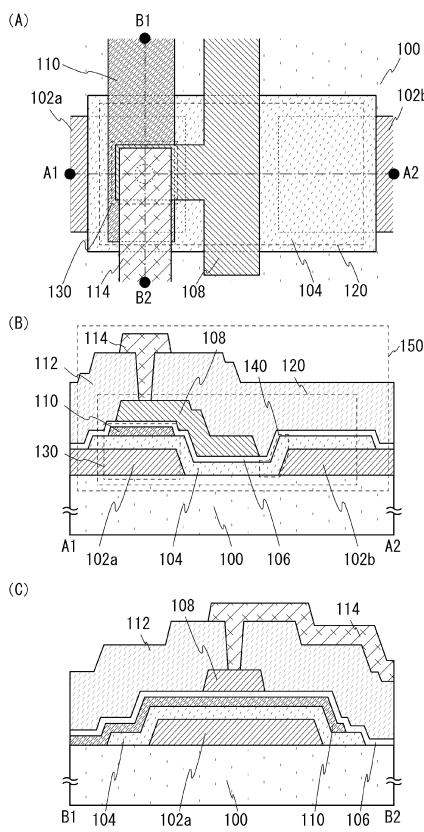

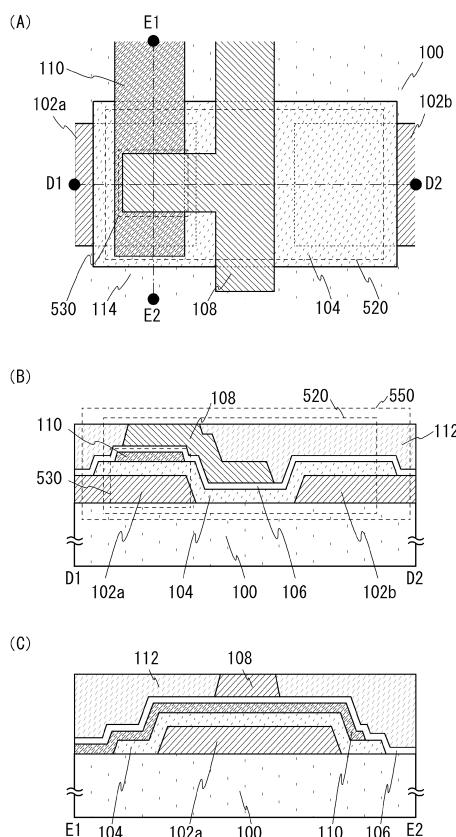

本実施の形態では、本発明の一態様に係る半導体装置の構造を図1に示すと共に、当該半導体装置の作製方法について、図2および図3を用いて説明する。

## 【0034】

<半導体装置の構成例>

図1は、本実施の形態の方法にて作製された半導体装置150の構成例であり、図1(A)は半導体装置150の上面図、図1(B)は図1(A)の一点鎖線部A1-A2の断面図、図1(C)は図1(A)の一点鎖線B1-B2の断面図である。なお、図1(A)の

50

上面図については、構造を分かり易くするため、ゲート絶縁層 106 および層間絶縁層 112 を省略して記載している。

【0035】

図1に示す半導体装置 150 は、トランジスタ 120 および容量素子 130 を備えている。トランジスタ 120 は、絶縁表面を有する基板 100 上に設けられたソース電極 102a およびドレイン電極 102b と、基板 100 上、ソース電極 102a 上およびドレイン電極 102b 上に設けられた酸化物半導体層 104 と、ドレイン電極 102b および酸化物半導体層 104 と重なる、酸化物半導体層 104 上の第1の電極 110 と、酸化物半導体層 104 および第1の電極 110 を覆うゲート絶縁層 106 と、ソース電極 102a とドレイン電極 102b の間隙部と重なり、かつ第1の電極 110 方向に延在し第1の電極 110 と重なる、ゲート絶縁層 106 上のゲート電極 108 を有しており、またゲート電極 108 上には、ゲート絶縁層 106 およびゲート電極 108 を覆う層間絶縁層 112 と、ゲート電極 108 と電気的に接続された、層間絶縁層 112 上の配線 114 を有している。また、ドレイン電極 102b (容量素子の下部電極として機能する。)、第1の電極 110 (容量素子の上部電極として機能する。) および、酸化物半導体層 104 (上部電極と下部電極間の絶縁層として機能する。) により形成された容量素子 130 を有している。なお、酸化物半導体層 104 のうちソース電極 102a とドレイン電極 102b に挟まれた部分はチャネル形成領域として機能する。また、第1の電極 110 (下部電極として機能する。)、ゲート絶縁層 106 (誘電体膜として機能する。) およびゲート電極 108 (上部電極として機能する。) によっても容量素子 (以下、第2の容量素子と記載する場合もある。) が形成されることになる。

【0036】

なお、本実施の形態では、ゲート電極 108 と配線 114 を別の構成要素として記載しているが、配線 114 はゲート電極 108 と電気的に接続されているためゲート電極 108 の一部と見なすこともできる。

【0037】

トランジスタ 120 と容量素子 130 は構成要素の一部を共有しており、少ない工程で効率よく半導体装置を形成できるため、半導体装置の作製時間や作製コストを低減できる。また、容量素子 130 をトランジスタ 120 の一部と重ねて設けることができるため、半導体装置 150 の高集積化が可能となる。

【0038】

図1 (B) のように、容量素子 130 の誘電体膜およびトランジスタ 120 の半導体層として用いる膜を、同じ材料かつ一続きの半導体層により形成する場合、一般的な半導体層、例えばシリコン膜などでは、容量素子 130 に電荷を蓄えようとしても、電荷は横方向 (例えば、ソース電極 102a およびドレイン電極 102b の間隙部に形成されたシリコン膜部分など) に流れてしまうため、容量素子として機能しない。これに対し、本実施の形態等のように、i型化 (真性化) または実質的に i型化された酸化物半導体層 104 を用いることにより、ゲート電極 108 に加わる電圧がトランジスタ 120 のしきい値電圧以下の場合、トランジスタ 120 のリーク電流は極めて小さいため、容量素子 130 の電荷減少も極めて少量となる。したがって、容量素子 130 に長時間に渡って電荷を保持することが可能となる。

【0039】

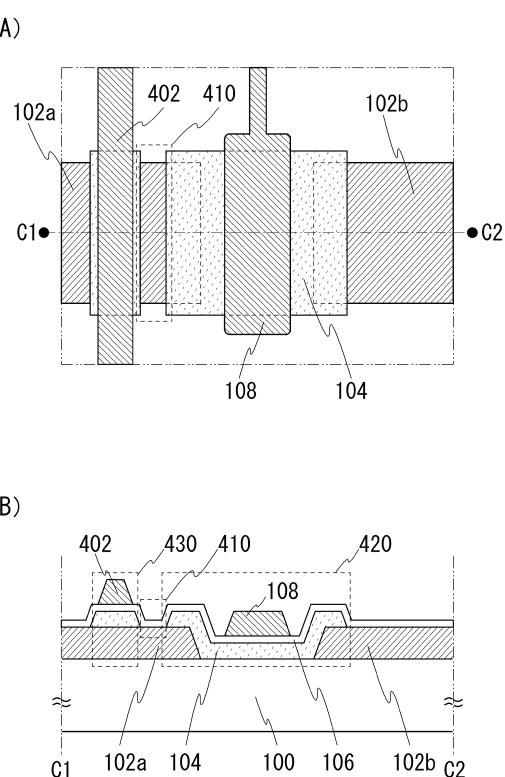

トランジスタと容量素子を別々に形成する場合、例えば図4 (A) および図4 (B) に示すように、トランジスタ 420 と容量素子 430 (酸化物半導体層 104 およびゲート絶縁層 106 が、ソース電極 102a および導電層 402 に挟まれた構造) の間に、トランジスタと容量素子を分離するための溝部 410 を形成する必要がある。溝部 410 を形成するにあたり、トランジスタ 420 と容量素子 430 の間隔は、レジスト露光処理の際に装置起因よりズレが生じる、エッチング処理の際に溝部 410 が設計値以上に広がる、などといった現象を考慮して設計する必要があるため、半導体装置の集積度が低下する要因となりうる。これに対し、本実施の形態のように、トランジスタ 120 と容量素子 130

10

20

30

40

50

が一体形成された構造の半導体装置 150 では、前述の溝部 410 や、レジスト露光処理の際に装置起因よりズレが生じる、およびエッチング処理の際に溝部 410 が広がるなどといった現象を考慮した設計を行う必要がない。このため、本実施の形態のようにトランジスタ 120 と容量素子 130 の少なくとも一部が重なる構造の半導体装置 150 は、トランジスタと容量素子を別々に設けるよりも小さな面積で形成でき、半導体装置の高集積化に寄与することができる。

【0040】

また、半導体装置 150 において、図 1 (B) のように、ソース電極 102a とゲート電極 108 が重畠しない構造とすることが好ましい。酸化物半導体層 104 において、ソース電極 102a とゲート電極 108 が重畠しない領域 (図 1 (B) の領域 140 に相当) は、ゲート電極 108 と重畠している領域と比較してチャネル領域が形成されにくいため、ソース電極 102a とドレイン電極 102b 間のリーク電流を更に小さくすることができる。

【0041】

なお、トランジスタ 120 と一体形成された容量素子 130 とは別に、更に異なる容量素子を設けても良い。

【0042】

ここで、半導体装置 150 に用いられる酸化物半導体層 104 は、水素などの不純物が十分に除去され、また、十分な酸素が供給されることにより、高純度化された半導体膜であることが望ましい。具体的には、例えば、酸化物半導体層 104 の水素濃度は  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、望ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より望ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。なお、上述の酸化物半導体層 104 中の水素濃度は、二次イオン質量分析法 (SIMS: Secondary Ion Mass Spectrometry) で測定されるものである。このように、水素濃度が十分に低減され、また、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層 104 では、キャリア濃度が  $1 \times 10^{12}$  / cm<sup>3</sup> 未満、望ましくは、 $1 \times 10^{11}$  / cm<sup>3</sup> 未満、より望ましくは  $1 \times 10^{10}$  / cm<sup>3</sup> 未満となる。このような酸化物半導体層 104 を用いることにより、半導体装置 150 中のトランジスタ 120 は、例えば室温 (25) でのオフ電流 (ここでは、単位チャネル幅 (1 μm)あたりの値) は 100 zA (1 zA (ゼプトアンペア) は  $1 \times 10^{-21}$  A) 以下、望ましくは 10 zA 以下となる。このように、i型化 (真性化) または実質的に i型化された酸化物半導体層 104 を用いることで、極めてオフ電流の低いトランジスタ 120 を得ることができる。

【0043】

また、酸化物半導体層 104 のナトリウム濃度は  $5 \times 10^{16}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以下とする。また、酸化物半導体層 104 のリチウム濃度は  $5 \times 10^{15}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以下とする。また、酸化物半導体層 104 のカリウム濃度は  $5 \times 10^{15}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以下とする。なお、上述の酸化物半導体層 104 中のナトリウム濃度、リチウム濃度およびカリウム濃度は、二次イオン質量分析法で測定されるものである。アルカリ金属、およびアルカリ土類金属は酸化物半導体にとっては悪性の不純物であり、少ない方がよい。特にアルカリ金属のうち、ナトリウムは酸化物半導体に接する絶縁膜が酸化物であった場合、その中に拡散し、Na<sup>+</sup>となる。また、酸化物半導体内において、ナトリウムは金属と酸素の結合を分断し、あるいは結合中に割り込む。その結果、トランジスタ特性の劣化 (例えば、ノーマリーオン化 (しきい値電圧の負へのシフト)、移動度の低下等) をもたらす。加えて、特性のばらつきの原因となる。このような問題は、特に酸化物半導体中の水素の濃度が十分に低い場合において顕著となる。したがって、酸化物半導体中の水素の濃度が  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、特に  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下である場合には、アルカリ金属の濃度を上記の値にす

10

20

30

40

50

ることが強く求められる。

【0044】

なお、酸化物半導体層104は、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態をとる。

【0045】

好みしくは、酸化物半導体層104は、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0046】

CAAC-OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS膜は、非晶質相に結晶部および非晶質部を有する結晶-非晶質混相構造の酸化物半導体膜である（本明細書では、「酸化物半導体層」と記載しているが、同義の言葉である。）。なお、当該結晶部は、一辺が100nm未満の立方体内に收まる大きさであることが多い。また、透過型電子顕微鏡（TEM:Transmission Electron Microscope）による観察像では、CAAC-OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には粒界（グレインバウンダリーともいう。）は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0047】

CAAC-OS膜に含まれる結晶部は、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつa b面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

【0048】

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0049】

CAAC-OS膜に含まれる結晶部のc軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0050】

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0051】

<半導体装置の作製方法>

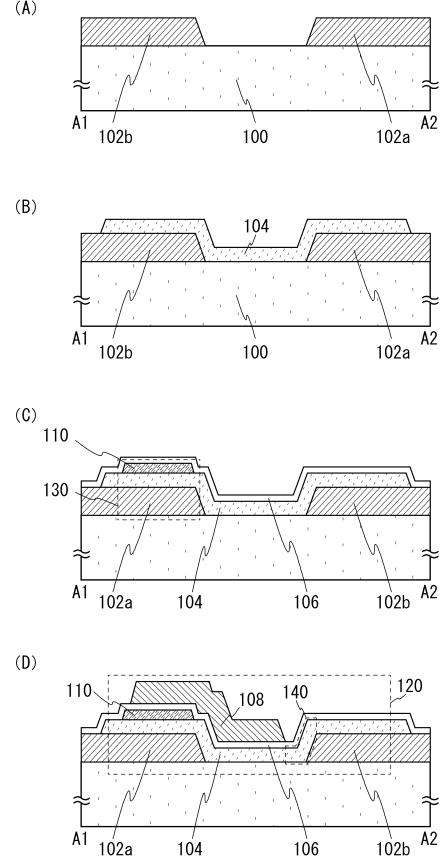

本実施の形態に記載する半導体装置150の作製方法について、図2から図4を用いて以下の文章にて説明する。

【0052】

まず、基板100を準備し、基板100上にソース電極102aおよびドレイン電極102bを形成する（図2（A）参照）。

【0053】

基板100としては、例えば、ガラス基板（バリウムホウケイ酸ガラス基板やアルミニウム

10

20

30

40

50

ウケイ酸ガラス基板等)、絶縁体でなる基板(セラミック基板、石英基板、サファイア基板等)、結晶化ガラス基板、プラスチック基板、または、半導体基板(シリコン基板等)を用いることができる。

【0054】

ソース電極102aおよびドレイン電極102bを形成する方法としては、まず基板100上に抵抗加熱蒸着やスパッタリングなどのPVD法により導電層を形成し、当該導電層上にフォトリソグラフィ法やインクジェット法などの公知の技術を用いて、加工したいパターン形状に応じたレジストを形成し、ドライエッティング法やウェットエッティング法などの公知の技術を用いて導電層の不要部分を選択的に除去して、ソース電極102aおよびドレイン電極102bを形成すればよい。なお、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクスチル、マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムから選ばれた元素や、上述した元素を主成分とする合金等を用いることができる。

【0055】

なお、導電層は、単層構造であっても良いし、2層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、アルミニウム膜上にチタン膜が積層された2層構造、窒化チタン膜上にチタン膜が積層された2層構造、チタン膜によりアルミニウム膜を挟んだ3層構造、モリブデン膜によりアルミニウム膜を挟んだ3層構造などが挙げられる。

【0056】

また、導電層は、導電性の金属酸化物を用いて形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ( $In_2O_3-SnO_2$ 、ITOと略記する場合がある)、酸化インジウム酸化亜鉛( $In_2O_3-ZnO$ )、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。

【0057】

導電性の金属酸化物は一般的に、金属膜と比較して抵抗値は大きいが、透光性を有するという特徴を備えているため、金属酸化膜を用いてソース電極102aおよびドレイン電極102bを形成し、かつ、後の工程にて形成するゲート電極108を、金属酸化膜を用いて形成することにより、本実施の形態等で作製される半導体装置150は、透光性を有するという特徴を備えることができる。このような透光性を有する半導体素子を用いて半導体装置を作製することにより、透光性を有する半導体装置を作製することも可能となる。

【0058】

なお、絶縁表面を有する基板100上には、加熱処理により酸素を放出する膜(以下、酸素供給膜と記載する。)が形成されていることが好ましい。以下に理由を記載する。

【0059】

トランジスタ120において、チャネル形成領域に酸素欠損が存在すると、酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体層104の酸素欠損は一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そこで、絶縁表面を有する基板100上には酸素供給膜が形成されていることが好ましい。

【0060】

絶縁表面を有する基板100上に酸素供給膜が存在する場合、後述する酸化物半導体層104の成膜後、加熱処理によって酸素供給膜中の酸素の一部を放出できるので、酸化物半導体層に酸素を供給し、酸化物半導体層中の酸素欠損を補填することができるため、トランジスタのしきい値電圧のマイナス方向へのシフトを抑制できる。特に、酸素供給膜中に少なくとも化学量論的組成比を超える量の酸素が存在することが好ましい。例えば、酸素供給膜として酸化シリコンを用いる場合、 $SiO_{2+x}$ (ただし、 $x > 0$ )で表される酸化シリコン膜を用いることが好ましい。なお、このような化学量論的組成比よりも酸素を過剰に含む領域(以下、酸素過剰領域と記載する場合もある。)は、酸素供給膜の少なく

10

20

30

40

50

とも一部に存在していればよい。

【0061】

なお、上述の「加熱処理により酸素を放出する膜」とは、TDS (Thermal Desorption Spectroscopy: 昇温脱離ガス分光法) 分析にて、酸素原子に換算しての酸素の放出量が  $1.0 \times 10^{19}$  atoms/cm<sup>3</sup> 以上、好ましくは  $3.0 \times 10^{19}$  atoms/cm<sup>3</sup> 以上、さらに好ましくは  $1.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以上、さらに好ましくは  $3.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以上であることをいう。

【0062】

ここで、TDS 分析にて、酸素原子に換算しての酸素の放出量の測定方法について、以下 10 に説明する。

【0063】

TDS 分析による気体の放出量は、イオン強度の時間積分値に比例する。このため、測定したイオン強度の時間積分値と標準試料の基準値との比により、気体の放出量を計算することができる。標準試料の基準値は、所定の原子密度を有する試料において、イオン強度の時間積分値に対する原子密度の割合である。

【0064】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS 分析結果、および絶縁膜のTDS 分析結果から、絶縁膜の酸素分子の放出量 ( $N_{O_2}$ ) は、式(1)で求めることができる。ここで、TDS 分析で得られる質量電荷比 ( $M/z$ ) が 32 で検出されるスペクトルの全てが酸素分子由来と仮定する。 $M/z$  が 32 のものとしてほかに  $CH_3OH$  があるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である  $M/z$  が 17 の酸素原子および  $M/z$  が 18 の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0065】

【数1】

$$N_{O_2} = \frac{N_{H_2}}{S_{H_2}} \times S_{O_2} \times \alpha \quad \dots \quad (1)$$

【0066】

$N_{H_2}$  は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$  は、標準試料を TDS によるイオン強度の時間積分値である。ここで、標準試料の基準値を、 $N_{H_2}/S_{H_2}$  とする。 $S_{O_2}$  は、絶縁膜を TDS 分析によるイオン強度の時間積分値である。

は、TDS におけるスペクトル強度に影響する係数である。式(1)の詳細に関しては、特開平 6-275697 公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置 EMD-WA1000S/W を用い、標準試料として  $1 \times 10^{16}$  atoms/cm<sup>3</sup> の水素原子を含むシリコンウェハを用いて測定する。

【0067】

また、TDS 分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の は酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

【0068】

なお、 $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の 2 倍となる。

【0069】

膜中への酸素の導入は、酸素雰囲気下による熱処理や、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、酸素を含む雰囲気下で行うプラズマ処理などを用いることができる。

【0070】

また、過剰酸素を含む絶縁膜（以下、酸素供給膜とも記載する。）の水素濃度が、7.2 50

$\times 10^{20}$  atoms /  $\text{cm}^3$  以上である場合には、トランジスタの初期特性のバラツキの増大、トランジスタの電気特性に関するL長依存性の増大、さらにBTストレス試験において、大きく劣化するため、酸素供給膜の水素濃度は、 $7.2 \times 10^{20}$  atoms /  $\text{cm}^3$  未満とすることが好ましい。即ち、酸化物半導体層の水素濃度は $5 \times 10^{19}$  atoms /  $\text{cm}^3$  以下、かつ、酸素供給膜の水素濃度は、 $7.2 \times 10^{20}$  atoms /  $\text{cm}^3$  未満とすることが好ましい。水素濃度の低い膜を形成する方法については、後述にて詳細を記載する。

【0071】

なお、加熱処理により酸素供給膜から酸化物半導体層に酸素を供給する場合、酸素供給膜から放出される酸素が酸化物半導体層に効率的に供給されるように、酸素供給膜の下層に酸素透過性や水蒸気透過性（水分透過性とも表現できる。）の低い膜（以下、バリア膜と記載する場合もある。）を形成することが好ましい。例えば、酸素供給膜の下層にバリア膜として、酸化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜などを形成すればよい。なお、酸化アルミニウム膜を用いる場合、膜を高密度（膜密度 $3.2 \text{ g/cm}^3$  以上、好ましくは $3.6 \text{ g/cm}^3$  以上）とすることが好ましい。

10

【0072】

次に、基板100上、ソース電極102a上およびドレイン電極102b上に酸化物半導体層104を形成する（図2（B）参照）。

【0073】

酸化物半導体層104は、スパッタリング法、MBE（Molecular Beam Epitaxy）法、CVD法、パルスレーザ堆積法、ALD（Atomic Layer Deposition）法等を用いて酸化物半導体膜を成膜し、当該酸化物半導体膜上にフォトリソグラフィ法やインクジェット法などの公知の技術を用いて、加工したいパターン形状に応じたレジストを形成し、ドライエッ칭法やウェットエッ칭法などの公知の技術を用いて酸化物半導体膜の不要部分を選択的に除去して、酸化物半導体層104を形成すればよい。なお、酸化物半導体膜は、スパッタリングターゲット表面に対し、概略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタリング装置、所謂CPスパッタリング装置（Columnar Plasma Sputtering system）を用いて成膜してもよい。なお、酸化物半導体膜の膜厚は $5 \text{ nm}$ より大きく $200 \text{ nm}$ 以下とし、 $10 \text{ nm}$ 以上 $30 \text{ nm}$ 以下とすることが好ましい。

20

【0074】

酸化物半導体層104中の酸素欠損をできるだけ少なくするためには、酸化物半導体層104の形成に用いる酸化物半導体膜を、成膜雰囲気中のガス種に占める酸素ガスの割合が高い状態で成膜することが好ましいため、装置内に酸素を導入することが可能で、かつ、ガス流量の調整ができるスパッタリング装置を用いることが好ましいといえる。そして、スパッタリング装置の成膜チャンバー内への導入ガスは、全体の90%以上を酸素ガスとして、酸素ガスに加えて他のガスを用いる場合は、当該ガスは希ガスを用いることが望ましい。また、より好ましくは成膜チャンバー内への導入ガスを酸素ガスのみとし、成膜雰囲気中のガス種に占める酸素ガスの割合を極力100%に近づけることが望ましい。

30

【0075】

また、酸化物半導体層104に水素が多量に含まれると、水素が酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体層104において、水素濃度は、 $5 \times 10^{18}$  atoms /  $\text{cm}^3$  未満、好ましくは $1 \times 10^{18}$  atoms /  $\text{cm}^3$  以下、より好ましくは $5 \times 10^{17}$  atoms /  $\text{cm}^3$  以下、更に好ましくは $1 \times 10^{16}$  atoms /  $\text{cm}^3$  以下とすることが望ましい。なお、上述の酸化物半導体層中の水素濃度は、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）で測定されるものである。

40

【0076】

50

上述の理由により、酸化物半導体膜を成膜する際に用いるガスとしては、水、水素、水酸基又は水素化物などの不純物が含まれないことが好ましい。または、純度が 6 N 以上好ましくは 7 N 以上（即ち、ガス中の不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下）のガスを用いることが好ましい。

【0077】

また、酸化物半導体膜を成膜するにあたり、成膜室内の水分（水、水蒸気、水素、水酸基または水酸化物を含む）を除去するために、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段は、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水（H<sub>2</sub>O）など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体層 104 に含まれる水素、水分などの不純物の濃度を低減できる。

10

【0078】

一方、酸化物半導体層 104 に、アルカリ金属またはアルカリ土類金属が含まれると、酸化物半導体と結合することによって、キャリアが生成されることがあり、トランジスタのオフ電流が上昇する原因となる。そのため、酸化物半導体層 104 において、アルカリ金属またはアルカリ土類金属の濃度は、 $1 \times 10^{-8}$  atoms/cm<sup>3</sup> 以下、好ましくは $2 \times 10^{-6}$  atoms/cm<sup>3</sup> 以下とすることが望ましい。

【0079】

なお、スパッタリング装置にて用いるターゲットは、相対密度が 90% 以上、好ましくは 95% 以上であることが望ましい。相対密度の高いターゲットを用いることにより、酸化物半導体層 104 の形成用いる酸化物半導体膜を緻密な膜とできる。

20

【0080】

酸化物半導体層 104 に用いる酸化物半導体材料としては、少なくともインジウム（In）を含む。特に In と亜鉛（Zn）を含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム（Ga）を有することが好ましい。また、スタビライザーとしてスズ（Sn）を有することが好ましい。また、スタビライザーとしてハフニウム（Hf）を有することが好ましい。また、スタビライザーとしてアルミニウム（Al）を有することが好ましい。また、スタビライザーとしてジルコニウム（Zr）を有することが好ましい。

30

【0081】

また、他のスタビライザーとして、ランタノイドである、ランタン（La）、セリウム（Ce）、プラセオジム（Pr）、ネオジム（Nd）、サマリウム（Sm）、ユウロピウム（Eu）、ガドリニウム（Gd）、テルビウム（Tb）、ジスプロシウム（Dy）、ホルミウム（Ho）、エルビウム（Er）、ツリウム（Tm）、イッテルビウム（Yb）、ルテチウム（Lu）のいずれか一種あるいは複数種を有してもよい。

【0082】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である In - Zn 系酸化物、In - Mg 系酸化物、In - Ga 系酸化物、三元系金属の酸化物である In - Ga - Zn 系酸化物（IGZO とも表記する）、In - Al - Zn 系酸化物、In - Sn - Zn 系酸化物、In - Hf - Zn 系酸化物、In - La - Zn 系酸化物、In - Ce - Zn 系酸化物、In - Pr - Zn 系酸化物、In - Nd - Zn 系酸化物、In - Sm - Zn 系酸化物、In - Eu - Zn 系酸化物、In - Gd - Zn 系酸化物、In - Tb - Zn 系酸化物、In - Dy - Zn 系酸化物、In - Ho - Zn 系酸化物、In - Er - Zn 系酸化物、In - Tm - Zn 系酸化物、In - Yb - Zn 系酸化物、In - Lu - Zn 系酸化物、四元系金属の酸化物である In - Sn - Ga - Zn 系酸化物、In - Hf - Ga - Zn 系酸化物、In - Al - Ga - Zn 系酸化物、In - Sn - Al - Zn 系酸化物、In - Sn - Hf - Zn 系酸化物、In - Hf - Al - Zn 系酸化物を用いることができる。

40

【0083】

50

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0084】

また、酸化物半導体として、 $InMO_3 (ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素又は複数の金属元素を示す。また、酸化物半導体として、 $In_2SnO_5 (ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。

【0085】

成膜された酸化物半導体膜は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。 10

【0086】

酸化物半導体膜は、好ましくは、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜とする。なお、CAAC-OS膜についての説明は、上述の内容を参照することができる。

【0087】

また、CAAC-OSのように結晶部を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができます。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ( $R_a$ )が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。そのため、酸化物半導体を形成する面に対して平坦化処理を行うことができる。平坦化処理としては、化学機械研磨(CMP: Chemical Mechanical Polishing)処理、またはドライエッキング法などを用いればよい。なお、CMP処理を行う場合は、1回のみ行ってもよいし、複数回行ってもよい。複数回に分けてCMP処理を行う場合は、高い研磨レートの一次研磨を行った後、低い研磨レートの仕上げ研磨を行うことが好ましい。このように研磨レートの異なる研磨を組み合わせることによって、酸化物半導体を形成する面の平坦性をより向上させることができる。 20

【0088】

なお、 $R_a$ は、JIS B 0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。 30

【0089】

【数2】

$$R_a = \frac{1}{S_0} \int_{y1}^{y2} \int_{x1}^{x2} |f(x, y) - Z_0| dx dy \quad \dots \quad (2)$$

【0090】

上記において、 $S_0$ は、測定面(座標( $x_1, y_1$ ) ( $x_1, y_2$ ) ( $x_2, y_1$ ) ( $x_2, y_2$ ) で表される4点によって囲まれる長方形の領域)の面積を指し、 $Z_0$ は測定面の平均高さを指す。 $R_a$ は原子間力顕微鏡(AFM: Atomic Force Microscope)にて評価可能である。 40

【0091】

上述のように、酸化物半導体膜の被成膜面を平坦化すると、酸化物半導体膜中の結晶が被形成面に対して概略垂直な方向に成長しやすい。

【0092】

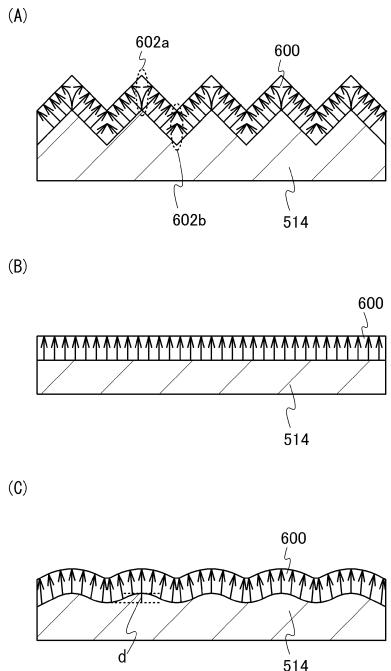

ここで、図8を用いて、酸化物半導体膜を形成するために被形成面514上に成膜する酸化物半導体膜600の結晶性が、被形成面514の平坦性に応じてどのように変化するか説明する。図8(A)から図8(C)に被形成面514と酸化物半導体膜600の拡大図を示す。なお、図8(A)から図8(C)の酸化物半導体膜600中の矢印は酸化物半導体膜600に含まれる結晶の成長方向を示す。 50

## 【0093】

図8(A)に示すように、被形成面514の表面の平坦性が低い場合には、被形成面514表面の凹凸の斜面に概略垂直に結晶が成長することになる。よって、被形成面514表面の凹凸の斜面に対して概略平行な層状に形成される。しかし、被形成面514表面の凹凸の山頂にあたる領域602aでは結晶の成長方向が場所により異なる。故に、被形成面514表面の凹凸の斜面に概略平行な層状に形成された結晶の配列が領域602aで分断されてしまうことになる。また、被形成面514表面の凹凸の谷底にあたる領域602bでは、領域602b周囲の結晶の成長方向が互いにぶつかり合うことになる。故に、被形成面514表面の凹凸の斜面に概略平行な層状に形成された結晶の配列が、領域602bで分断されてしまうことになる。

10

## 【0094】

このように、酸化物半導体膜の層状に形成された結晶の配列が分断されると結晶粒界が生じる。そして結晶粒界にはダンギングボンド(原子未結合手)が存在し酸化物半導体膜のバンドギャップ中に欠陥準位を形成する。これらは主にキャリアのトラップとして働き、キャリアの移動度を低下させるため酸化物半導体膜の抵抗を大きくする。また、ダンギングボンドが水素原子などと結合すると酸化物半導体膜のバンドギャップ中にドナー準位が形成される。従って、当該酸化物半導体膜をトランジスタなどの半導体装置に用いると、領域602aや領域602bに相当する部分で電気伝導度が変動するとともに、当該半導体装置の移動度が低下してしまう。

## 【0095】

20

しかし、図8(B)に示すように、被形成面514の表面の平坦性が十分に高い場合には、図8(A)に示す領域602aおよび領域602bに相当する部分が形成されないので、被形成面514表面に概略平行に層状に形成された結晶の配列を連続的に設けることができる。このような酸化物半導体膜600をトランジスタなどの半導体装置に設けることにより、当該半導体装置の電気的安定性が得られるとともに、移動度の低下を抑制することができる。

## 【0096】

また、図8(C)に示すように、被形成面514の表面に凹凸が形成されていても、当該凹凸が十分になだらかな場合には、図8(A)に示す領域602aおよび領域602bに相当する部分において、被形成面514表面の凹凸の斜面に概略平行に層状に形成された結晶の配列が分断されず連続的に設けられる。具体的には、先に記載したとおり、平均面粗さ( $R_a$ )が1nm以下、好ましくは0.3nm以下の表面上に形成するとよい。

30

## 【0097】

以上のように表面粗さが低減された被形成面514上に接して結晶性を有する酸化物半導体膜を形成することにより、酸化物半導体膜600中の粒界欠陥密度を低下させることができる。よって、酸化物半導体膜600の結晶性をさらに向上させることができるので、酸化物半導体膜600より形成される酸化物半導体層104を用いる半導体装置150の電気的安定性および移動度を向上させることができる。

## 【0098】

40

なお、被形成面514の平坦化は、化学的機械的研磨(Chemical Mechanical Polishing: CMP)処理を用いて行うことが好ましい。ここで、CMP処理とは、被加工物の表面を基準にし、それにならって表面を化学的・機械的な複合作用により、平坦化する手法である。一般的に研磨ステージの上に研磨布を貼り付け、被加工物と研磨布との間にスラリー(研磨剤)を供給しながら研磨ステージと被加工物とを各々回転または揺動させて被加工物の表面を、スラリーと被加工物表面との間での化学反応と、研磨布と被加工物との機械的研磨の作用により、被加工物の表面を研磨する方法である。

## 【0099】

CMP処理は、1回行ってもよいし、複数回行ってもよい。複数回に分けてCMP処理を行う場合は、高い研磨レートの一次研磨を行った後、低い研磨レートの仕上げ研磨を行う

50

のが好ましい。このように研磨レートの異なる研磨を組み合わせることによって、被形成面 514 の表面の平坦性をさらに向上させることができる。

【0100】

また、被形成面 514 を平坦化させる処理としては、CMP 处理の他にドライエッティング処理などを適用することも可能である。エッティングガスとしては、塩素、塩化硼素、塩化珪素または四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄または弗化窒素などのフッ素系ガス、酸素などを適宜用いることができる。例えば、反応性イオンエッティング (RIE : Reactive Ion Etching) 法、ICP (Inductive Coupled Plasma) エッティング法、ECR (Electron Cyclotron Resonance) エッティング法、平行平板型 (容量結合型) エッティング法、マグネットロンプラズマエッティング法、2 周波プラズマエッティング法またはヘリコン波プラズマエッティング法等のドライエッティング法を用いることができる。特に被形成面 514 として窒化シリコンや窒化酸化シリコンのような、窒素を多く含む無機絶縁材料が含まれる場合、CMP 处理だけでは窒素を多く含む無機絶縁材料の除去が困難な場合があるので、ドライエッティングなどを併用することが好ましい。

【0101】

また、被形成面 514 を平坦化させる処理としては、CMP 处理の他にプラズマ処理などを適用することも可能である。プラズマ処理は、真空のチャンバーに不活性ガス、例えばアルゴンガスを導入し、被処理面を陰極とする電界をかけて行う。その原理としてはプラズマドライエッチ法と同等であるが、不活性ガスを用いることで、通常のスパッタ成膜チャンバーにて処理可能であり簡便な方法である。すなわち、このプラズマ処理は、被処理面に不活性ガスのイオンを照射して、スパッタリング効果により表面の微細な凹凸を平坦化する処理である。このことから本明細書では、このプラズマ処理を「逆スパッタ」ともいう。

【0102】

なお、酸化物半導体層 104 に CAAc - OS 膜を用いる場合、以下の三つの方法で形成すればよい。第 1 の方法は、200 以上 450 以下の成膜温度で酸化物半導体膜を成膜する方法である。第 2 の方法は、酸化物半導体膜を成膜した後、当該膜に対して 200 以上 700 以下の熱処理を行う方法である。第 3 の方法は、2 層に分けて酸化物半導体膜を成膜する方法である。すなわち、1 層目の酸化物半導体膜を薄く成膜した後、200 以上 700 以下の熱処理を行い 1 層目の膜を CAAc - OS 膜とし、当該膜上に 2 層目の成膜を行うことで、1 層目の結晶を種結晶として 2 層目の酸化物半導体膜を CAAc - OS 膜とする方法である。

【0103】

なお、酸化物半導体層 104 は、複数の酸化物半導体膜が積層された構造でもよい。例えば、酸化物半導体層 104 を、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜の積層として、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜に、異なる組成の金属酸化物を用いてもよい。例えば、第 1 の酸化物半導体膜に三元系金属の酸化物を用い、第 2 の酸化物半導体膜に二元系金属の酸化物を用いてもよい。また、例えば、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜を、どちらも三元系金属の酸化物としてもよい。

【0104】

また、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜の構成元素を同一とし、両者の組成比を異ならせててもよい。例えば、第 1 の酸化物半導体膜の原子数比を In : Ga : Zn = 1 : 1 : 1 とし、第 2 の酸化物半導体膜の原子数比を In : Ga : Zn = 3 : 1 : 2 としてもよい。また、第 1 の酸化物半導体膜の原子数比を In : Ga : Zn = 1 : 3 : 2 とし、第 2 の酸化物半導体膜の原子数比を In : Ga : Zn = 2 : 1 : 3 としてもよい。

【0105】

また、酸化物半導体層 104 を 3 層以上の積層構造とし、複数層の結晶性を有する酸化物半導体膜で非晶質酸化物半導体膜を挟む構造としてもよい。また、結晶性を有する酸化物半導体膜と非晶質酸化物半導体膜を交互に積層する構造としてもよい。酸化物半導体層 1

10

20

30

40

50

04を複数層の積層構造とする場合の上記構成は、それぞれを適宜組み合わせて用いることができる。

【0106】

なお、酸化物半導体層104を複数層の積層構造とし、各酸化物半導体膜の形成後に酸素を導入してもよい。酸素の導入は、絶縁表面を有する基板100の酸素供給膜にて記載した方法を用いることができる。なお、酸素を含む雰囲気下でのプラズマ処理では、基板側(基板側に設置されたバイアス印加装置や基板自体。)に直流バイアスを印加した状態でプラズマ処理を行うことにより、酸素プラズマが酸化物半導体層104中に侵入しやすくなるため好ましいといえる。どの程度のバイアスを印加するかについては、酸化物半導体層104の膜厚や膜へのダメージなどを考慮して、実施者が適宜調整すればよい。

10

【0107】

各酸化物半導体膜の形成毎に酸素を導入することで、酸化物半導体内の酸素欠損を低減する効果を高めることができる。

【0108】

なお、酸化物半導体層のエッチングとしてドライエッチングを用いる場合、エッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(C1<sub>2</sub>)、三塩化硼素(BC1<sub>3</sub>)、四塩化珪素(SiCl<sub>4</sub>)、四塩化炭素(CC1<sub>4</sub>)など)が好ましい。また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF<sub>4</sub>)、六弗化硫黄(SF<sub>6</sub>)、三弗化窒素(NF<sub>3</sub>)、トリフルオロメタン(CHF<sub>3</sub>)など)、臭化水素(HBr)、酸素(O<sub>2</sub>)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いることができる。

20

【0109】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

【0110】

ウェットエッチングに用いるエッチング液として、磷酸と酢酸と硝酸を混ぜた溶液、クエン酸やシュウ酸などの有機酸を用いることができる。本実施の形態では、ITO-07N(関東化学社製)を用いる。

30

【0111】

なお、酸化物半導体膜をスパッタリング法により成膜する前には、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、成膜面の付着物を除去することが好ましい。ここで、逆スパッタとは、通常のスパッタリング法においては、スパッタターゲットにイオンを衝突させるところを、逆に、処理表面にイオンを衝突させることによってその表面を改質することをいう。処理表面にイオンを衝突させる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、被処理物付近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などによる雰囲気を適用してもよい。

40

【0112】

なお、前述の方法により形成された酸化物半導体層104には、不純物としての水分又は水素(水酸基を含む)が含まれていることがある。水分又は水素はドナー準位を形成しやすいため、酸化物半導体にとって不純物である。そこで、酸化物半導体層104中の水分又は水素などの不純物を低減(脱水化または脱水素化)するために、酸化物半導体層104に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、などにおいて、脱水化または脱水素化の加熱処理(以下、第1の加熱処理と略記する)を行ってもよい。

【0113】

酸化物半導体層104に第1の加熱処理を行うことで、酸化物半導体層104中の水分又

50

は水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

【0114】

加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置等のRTA (Rapid Thermal Anneal) 装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0115】

第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水分又は水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0116】

また、第1の加熱処理を行った酸化物半導体層104に、第2の加熱処理を行ってもよい。第2の加熱処理は、酸化性雰囲気にて加熱処理することにより酸化物半導体層104中に酸素を供給して、第1の加熱処理の際に酸化物半導体層104中に生じた酸素欠損を補填する目的がある。このため、第2の加熱処理は加酸素化処理ということもできる。第2の加熱処理は、例えば200以上基板の歪み点未満で行えばよい。好ましくは、250以上450以下とする。処理時間は3分~24時間とする。処理時間を長くするほど非晶質領域に対して結晶領域の割合の多い酸化物半導体層104を形成することができるが、24時間を超える熱処理は生産性の低下を招くため好ましくない。

【0117】

酸化性雰囲気とは酸化性ガスを含む雰囲気である。酸化性ガスとは、酸素、オゾンまたは亜酸化窒素などであって、水、水素などが含まれないことが好ましい。例えば、熱処理装置に導入する酸素、オゾン、亜酸化窒素の純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm未満、好ましくは0.1ppm未満)とする。酸化性雰囲気は、酸化性ガスを不活性ガスと混合して用いてよい。その場合、酸化性ガスが少なくとも10ppm以上含まれるものとする。また、不活性雰囲気とは、窒素、希ガス(ヘリウム、ネオン、アルゴン、クリプトン、キセノン)などの不活性ガスを主成分とする雰囲気である。具体的には、酸化性ガスなどの反応性ガスが10ppm未満とする。

【0118】

なお、第2の加熱処理に用いる熱処理装置およびガス種は、第1の加熱処理と同じ物を用いることができる。また、脱水化または脱水素化の加熱処理である第1の加熱処理と、加酸素化の加熱処理である第2の加熱処理は連続して行うことが好ましい。連続して行うことで、半導体装置の生産性を向上させることができる。

【0119】

次に、酸化物半導体層104上に、ドレイン電極102bおよび酸化物半導体層104と重なる第1の電極110を形成し、その後、第1の電極110および酸化物半導体層104上にゲート絶縁層106を形成する。これにより、ドレイン電極102bを下部電極、酸化物半導体層104を誘電体膜、第1の電極110を上部電極とする容量素子130が

10

20

30

40

50

形成される(図2(C)参照)。

【0120】

第1の電極110は、ソース電極102aおよびドレイン電極102bと同様の材料および方法を用いて形成すればよい。そして、図示していないが、接地電位や共通電位などの固定電位に電気的に接続されている。容量素子130はトランジスタの一部(図2(C)ではドレイン電極102b。)を構成要素として共用しているため、トランジスタ120と一部が重なる状態に容量素子130を形成できる。このため、トランジスタ120と容量素子130を異なる場所に形成する場合と比較して、半導体装置150の集積度を高めることができる。

【0121】

ゲート絶縁層106は、十分な耐圧および絶縁性を有する酸化物絶縁膜を用いることが好ましい。ゲート絶縁層106としては、例えば、真空蒸着法やスパッタリング法などの物理気相成長法(PVD: Physical Vapor Deposition)やプラズマCVD法などの化学気相成長法(CVD: Chemical Vapor Deposition)を用いて、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ガリウム膜、酸化イットリウム膜、酸化ランタン膜などを、単層でまたは積層して形成することができる。また、酸化ハフニウム膜、ハフニウムシリケート膜( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート膜( $HfSiO_xN_y$  ( $x > 0$ ,  $y > 0$ ))、ハフニウムアルミネート膜( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))などのhigh-k材料をゲート絶縁層106の少なくとも一部として用いてもよい。これによりゲートリーク電流を低減することができる。

【0122】

ゲート絶縁層106の厚さは特に限定されないが、半導体装置を微細化する場合には、半導体装置150の動作を確保するために薄くすることが望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。例えば、絶縁膜として酸化シリコンを30nm成膜した上に酸化アルミニウムを10nm成膜した積層膜を用いて、ゲート絶縁層106を形成すればよい。

【0123】

なお、ゲート絶縁層106として酸化物絶縁膜(酸素供給膜とも言える。)を用いることにより、上述の絶縁表面を有する基板100上に成膜した酸素供給膜と同様に、加熱処理によって酸化物絶縁膜中の酸素の一部を放出させて酸化物半導体層104に酸素を供給し、酸化物半導体層104中の酸素欠損を補填することができるため好ましいと言える。なお、ゲート絶縁層106に対して加熱処理を行うタイミングについては、ゲート絶縁層106の成膜後であれば特段の限定はない。

【0124】

特に、ゲート絶縁層106中(バルク中)に少なくとも化学量論比を超える量の酸素が存在することが好ましく、例えば、ゲート絶縁層106として、 $SiO_{2+}$ (ただし、 $> 0$ )で表される酸化シリコン膜を用いることが好ましい。このような酸化シリコン膜をゲート絶縁層106として用いることで、酸化物半導体層104に酸素を供給することができ、酸化物半導体層104を用いたトランジスタ120のトランジスタ特性を良好にすることができる。

【0125】

ゲート絶縁層106は、水素、水などの不純物を混入させない方法で成膜した膜を用いて形成することが好ましい。ゲート絶縁層106に水素、水などの不純物が含まれると、前述の工程にて形成された酸化物半導体層104に水素、水などの不純物が浸入する、水素や水などの不純物により酸化物半導体層104中の酸素が引き抜きられる、などによって酸化物半導体層104のチャネルが低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがあるためである。よって、ゲート絶縁層106はできるだけ水素、水などの不純物が含まれないように作製することが好ましい。例えば、スパッタリング法によつ

10

20

30

40

50

て成膜するのが好ましい。成膜する際に用いるスパッタガスとしては、水素、水などの不純物が除去された高純度ガスを用いることが好ましい。

#### 【0126】

なお、酸化物半導体層104に用いられる酸化物半導体材料には、13族元素を含むものが多い。このため、13族元素および酸素を含む材料を用いて、酸化物半導体層104と接するゲート絶縁層106を形成する場合には、酸化物半導体層104との界面の状態を良好に保つことができる。これは、ゲート絶縁層106の形成に用いる13族元素および酸素を含む材料と、酸化物半導体層104の形成に用いる酸化物半導体材料との相性が良いことによる。例えば、酸化ガリウムを用いたゲート絶縁層106を酸化物半導体層104と接して設けることにより、酸化物半導体層104とゲート絶縁層106との界面における水素のパイルアップを低減することができる。

#### 【0127】

また、酸化アルミニウムをゲート絶縁層106として用いる場合、酸化アルミニウムは水分（水、水蒸気、水素を含む。）を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体層104への水分浸入防止という点においても好ましい。加えて、酸化アルミニウムは酸素を透過させにくいという特性も有しているため、後の工程にて行う第3の加熱処理の際に、ゲート絶縁層106中に含まれる酸素（過剰酸素を含む）がゲート電極108側に放出されることを抑制し、酸化物半導体層104中の酸素欠損を効果的に補填することができる。また、酸化物半導体層104に接して酸素供給膜（例えば、過剰酸素を有する酸化珪素膜。）を形成し、酸素供給膜上にバリア膜（例えば、酸化アルミニウム膜）が形成された積層構造の膜をゲート絶縁層106として用いてもよい。当該構造とすることにより、加熱処理等により酸素供給膜から放出された酸素を、酸化物半導体層104側に効率的に供給できる。

#### 【0128】

なお、上述のように、ゲート絶縁層106の膜厚を薄くすると、トンネル効果などに起因するゲートリークが問題となる。ゲートリークの問題を解消するためには、ゲート絶縁層106に、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート（ $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムシリケート（ $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムアルミニネート（ $HfAl_xO_y$  ( $x > 0$ 、 $y > 0$ ))、などの高誘電率（ $high-k$ ）材料を用いると良い。 $high-k$ 材料をゲート絶縁層106に用いることで、ゲート絶縁層106の電気的特性を確保しつつ、ゲートリークを抑制するために膜厚を大きくすることが可能になる。なお、 $high-k$ 材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。

#### 【0129】

なお、酸化物半導体層104の形成後、及びゲート絶縁層106の形成後のいずれか一方または両方において、酸化物半導体層104に酸素添加処理を行ってもよい。酸素添加処理とは、酸素（少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む）を酸化物半導体層104のバルクに添加することをいう。なお、当該「バルク」の用語は、酸素を、薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、「酸素添加」には、プラズマ化した酸素をバルクに添加する「酸素プラズマドープ」が含まれる。酸素添加処理を行うことにより、酸化物半導体層104やゲート絶縁層106に含まれる酸素を、化学量論的組成比より多くすることができる。

#### 【0130】

酸素添加処理は、酸素雰囲気下による熱処理や、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、酸素を含む雰囲気下で行うプラズマ処理などを用いることができる。ゲート絶縁層106へのダメージが少なく、過剰酸素を十分に添加する観点から考えると、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）方式を用いて、マイクロ波（例えば、周波数2.45GHz）により励起された酸素プラズマを用いて行うことが好ましい。

10

20

30

40

50

## 【0131】

ゲート絶縁層106の形成後には、不活性ガス雰囲気下、または酸素雰囲気下で第3の加熱処理を行うことが望ましい。第3の加熱処理の温度は、200以上450以下、好ましくは250以上350以下とすることが望ましい。例えば、窒素雰囲気下で250、1時間の熱処理を行えばよい。第3の加熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減することができる。また、酸化物半導体層104に接する膜、例えばゲート絶縁層106が酸素を含む場合、酸化物半導体層104に酸素を供給し、該酸化物半導体層104の酸素欠損を補填して、i型(真性半導体)またはi型に限りなく近い酸化物半導体層を形成することもできる。なお、酸化物半導体層104に接して酸素を含む下地膜などがある場合は、下地膜側からも酸素欠損を補填することができる。

10

## 【0132】

なお、本実施の形態では、ゲート絶縁層106の形成後に第3の加熱処理を行っているが、第3の加熱処理のタイミングはこれに限定されない。例えば、ゲート電極108の形成後に第3の加熱処理を行っても良い。

## 【0133】

上述のように、第3の加熱処理を適用することで、酸化物半導体層104を、水素原子を含む物質が極力含まれないように高純度化することができる。

## 【0134】

次に、ゲート絶縁層106上に、ソース電極102aとドレイン電極102bの間隙部と重なり、かつ第1の電極110方向に延在第1の電極110と重なるゲート電極108を形成する。これにより、トランジスタ120が形成される(図2(D)参照)。

20

## 【0135】

ゲート電極108を形成する方法としては、まず、ゲート絶縁層106上に蒸着法やスパッタリング法などの物理気相成長法(PVD: Physical Vapor Deposition)やプラズマCVD法などの化学気相成長法(CVD: Chemical Vapor Deposition)により導電膜を形成し、当該導電膜上にフォトリソグラフィ法やインクジェット法などの公知の技術を用いて、加工したいパターン形状に応じたレジストを形成し、ドライエッティング法やウェットエッティング法などの公知の技術を用いて導電膜の不要部分を選択的に除去して、ゲート電極108を形成すればよい。

## 【0136】

なお、導電膜の材料としては、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、マグネシウム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いることができる。また、導電性の金属酸化物を用いて形成しても良い。導電性の金属酸化物としては酸化インジウム(Indium Oxide: In<sub>2</sub>O<sub>3</sub>)、酸化スズ(SnO<sub>2</sub>)、酸化亜鉛(ZnO)、インジウムスズ酸化物(Indium Tin Oxide: In<sub>2</sub>O<sub>3</sub> - SnO<sub>2</sub>、ITOと略記する場合がある)、インジウム亜鉛酸化物(Indium Zinc Oxide: In<sub>2</sub>O<sub>3</sub> - ZnO)、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。なお、ゲート電極108は、単層構造としても良いし、上記の材料を組み合わせて積層構造としても良い。

30

## 【0137】

また、その厚さは特に限定されないが、厚くしすぎると半導体装置の生産性低下の要因となりうるため、10nm以上1000nm以下、好ましくは50nm以上500nm以下とすることが望ましい。例えば、導電膜としてチタンを100nm成膜した上にアルミニウムを300nm成膜した積層膜を用いて、ゲート電極108を形成すればよい。

40

## 【0138】

次に、ゲート絶縁層106およびゲート電極108を覆う層間絶縁層112を成膜し、第1の電極110およびゲート電極108と重なる層間絶縁層112に、ゲート電極108の少なくとも一部が露出する開口部113を形成する(図3(A)参照。)。

## 【0139】

層間絶縁層112は、ゲート絶縁層106と同一の方法および材料を用いて形成すること

50

ができる。また、層間絶縁層 112 として、絶縁性を有する有機材料を、スピンドルコート法、印刷法、ディスペンス法またはインクジェット法などを用いて塗布し、塗布した材料に応じた硬化処理（例えば、加熱処理や光照射処理など。）を行い形成してもよい。絶縁性を有する有機材料としては、例えば、アクリル樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリアミドイミド樹脂、エポキシ樹脂等の有機樹脂を用いて形成することができる。また、低誘電率材料（low-k 材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させてもよい。なお、上述の有機材料は水分などの不純物を比較的多く含んでいる場合が多いため、有機材料を用いて形成する膜の下に、バリア膜のような水蒸気透過性の低い膜（例えば、酸化アルミニウムや酸化アルミニウムを含む積層膜など）を形成することが好ましい。これにより、層間絶縁層 112 中に含まれる、あるいは、層間絶縁層 112 を通して外部から侵入する、トランジスタ 120 の電気特性に悪影響を及ぼし得る不純物（例えば、水分など。）の、酸化物半導体層 104 への拡散を防止できるため、トランジスタ 120 の電気特性を良好なものとできる。10

#### 【0140】

次に、層間絶縁層 112 上に、第 1 の電極 110 およびゲート電極 108 と重なり、ゲート電極 108 と電気的に接続された配線 114（開口部 113 を通してゲート電極 108 と電気的に接続された配線 114、とも言える。）を形成する。以上の工程により、トランジスタ 120 および容量素子 130 を備える半導体装置 150 が完成する（図 3（B）参照。）。トランジスタ 120 と容量素子 130 は構成要素の一部を共有しており、少ない工程で効率よく半導体装置 150 を形成できるため、半導体装置 150 の作製時間や作製コストを低減できる。また、容量素子 130 をトランジスタ 120 の一部と重ねて設けることができるため、半導体装置 150 の高集積化が可能となる。20

#### 【0141】

なお、通常、ゲート電極 108 をコンタクトホールを介して層間絶縁層 112 上に設けられた配線と接続する場合、ゲート電極 108 がドレイン電極 102b と重なると寄生容量として機能するため、トランジスタや半導体装置に悪影響が及ぼし得る場合がある。しかし、本実施の形態のように、接地電位や共通電位などの固定電位に接続された第 1 の電極がドレイン電極 102b とゲート電極 108 の間に存在することにより、当該影響を抑制することができ、容量素子 130 と重なる位置からゲート電極 108 を上層に取り出すことができるため、半導体装置 150 の更なる高集積化が可能となる。30

#### 【0142】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0143】

##### （実施の形態 2）

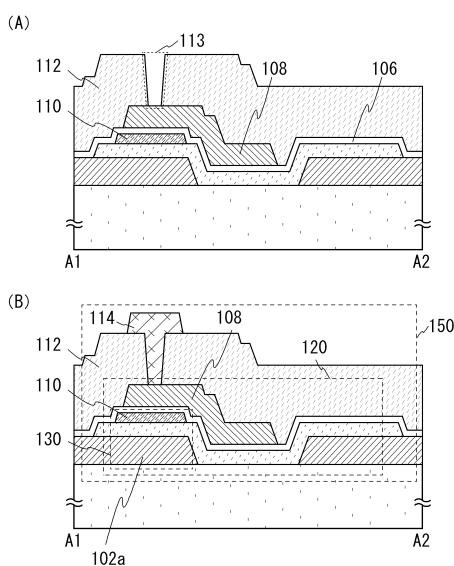

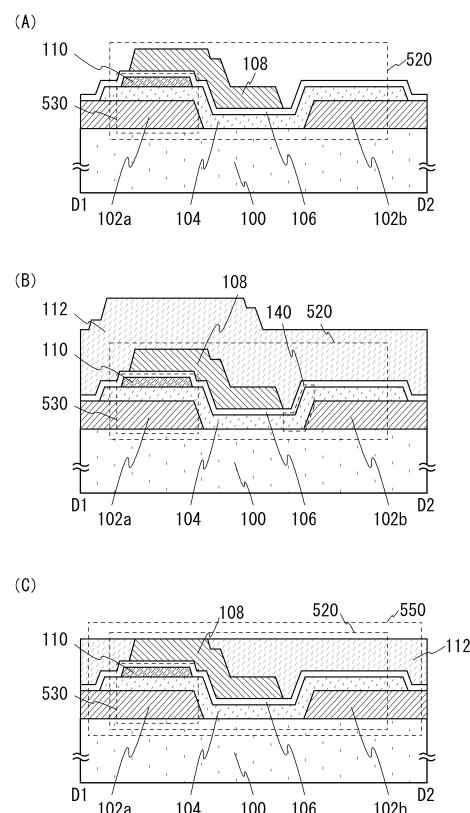

本実施の形態では、実施の形態 1 にて記載した構造とは異なる構造の半導体装置について、その構造および作製方法の一態様を図 5 および図 6 を用いて説明する。

#### 【0144】

##### <半導体装置の構成例>

図 5 は、本実施の形態の方法にて作製された半導体装置 550 の構成例であり、図 5（A）は半導体装置 550 の上面図、図 5（B）は図 5（A）の一点鎖線部 D1 - D2 の断面図、図 5（C）は図 5（A）の一点鎖線 E1 - E2 の断面図である。なお、図 5（A）の上面図については、構造を分かり易くするため、ゲート絶縁層 106 および層間絶縁層 112 を省略して記載している。40

#### 【0145】

図 5 に示す半導体装置 550 は、トランジスタ 520 および容量素子 530 を備えている。なお、トランジスタ 520 および容量素子 530 は、実施の形態 1 にて記載したトランジスタ 120 および容量素子 130 と同じ構成要素から成っている。

#### 【0146】

10

20

30

40

50

本実施の形態に記載の半導体装置 550 は、ゲート電極 108 と層間絶縁層上の配線との接続をコンタクトホールを用いて行うのではなく、層間絶縁層 112 形成後に、層間絶縁層 112 に対して平坦化処理を行い、ゲート電極 108 の一部が層間絶縁層 112 の表面から露出している構成が、実施の形態 1 と異なっている。すなわち、本実施の形態の構造ではマスクを用いることなく、ゲート電極 108 と層間絶縁層上の配線を接続することができる。これは、第 1 の電極 110 上 (容量素子 530 上とも言える。) に位置するゲート電極が最も高い状態になっている (凸状態になっている、とも表現できる。) ことを利用したものであり、ゲート電極 108 上に層間絶縁層 112 を形成した後、層間絶縁層 112 に対して平坦化処理を行うと、第 1 の電極 110 上 (容量素子 530 上とも言える。) に位置するゲート電極 108 が露出する。したがって、層間絶縁層 112 の所定箇所に開口部を形成するといった、マスクを必要とするプロセスを行うことなく、層間絶縁層 112 上の配線にゲート電極 108 を接続することができ、半導体装置の作製時間や作製コストを更に低減することができる。

#### 【0147】

また、マスクを用いた開口部形成を行わないため、装置により開口部の形成位置がずれ、トランジスタが機能しないといった問題も原理的に発生しないため、半導体装置の作製歩留まりを向上できる。

#### 【0148】

<半導体装置の作製方法>

本実施の形態に記載する半導体装置 550 の作製方法について、図 6 を用いて以下の文章にて説明する。

20

#### 【0149】

まず、図 2 (A) 乃至図 2 (D) および当該図面に対応する説明内容を参照して、基板 100 上にトランジスタ 520 および容量素子 530 を形成する (図 6 (A) 参照。)。なお、トランジスタ 520 および容量素子 530 の各構成要素 (例えば、ソース電極 102a やドレイン電極 102b など。) の作製方法や使用材料は、実施の形態 1 参照することができる。

#### 【0150】

次に、トランジスタ 520 および容量素子 530 上に層間絶縁層 112 を形成する (図 6 (B) 参照)。なお、層間絶縁層 112 の作製方法や使用材料は、実施の形態 1 を参照することができる。

30

#### 【0151】

次に、層間絶縁層 112 に対して平坦化処理を行い、少なくとも第 1 の電極 110 上 (容量素子 530 上とも言える。) に位置するゲート電極 108 を露出させる。平坦化処理としては、化学機械研磨 (CMP : Chemical Mechanical Polishing) 処理、またはドライエッキング法などを用いればよい。なお、CMP 処理を行う場合は、1 回のみ行ってもよいし、複数回行ってもよい。複数回に分けて CMP 処理を行う場合は、高い研磨レートの一次研磨を行った後、低い研磨レートの仕上げ研磨を行うことが好ましい。

#### 【0152】

40

以上の工程により、図 5 に記載した半導体装置 550 を作製できる (図 6 (C) 参照。)

。

#### 【0153】

(実施の形態 3)

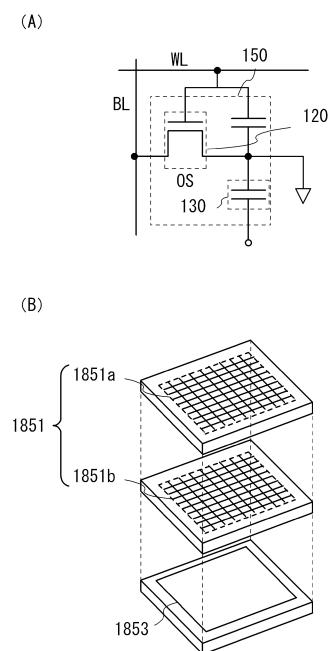

本実施の形態では、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置 (記憶装置とも言える。) として、上述実施の形態に示す半導体装置を使用した場合の一例を、図 7 を用いて説明する。なお、本実施の形態では、記憶装置に、実施の形態 1 に記載した半導体装置 150 を用いているが、勿論、実施の形態 2 に記載の半導体装置 550 を用いてもよい。

#### 【0154】

50

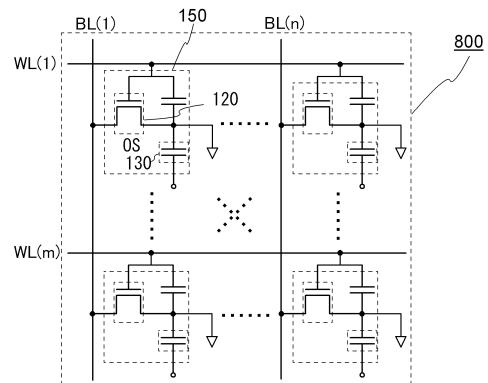

図7(A)は、半導体装置の回路構成の一例を示し、図7(B)は半導体装置の一例を示す概念図である。まず、図7(A)に示す半導体装置について説明を行い、続けて図7(B)に示す半導体装置について、以下説明を行う。

【0155】

図7(A)に示す半導体装置において、ビット線BLとトランジスタ120のソース電極又はドレイン電極とは電気的に接続され、ワード線WLとトランジスタ120のゲート電極とは電気的に接続され、トランジスタ120のソース電極又はドレイン電極と容量素子130の第1の端子とは電気的に接続されている。

【0156】

次に、図7(A)に示す半導体装置150(メモリセルとして機能する。)に、情報の書き込みおよび保持を行う場合について説明する。 10

【0157】

まず、ワード線WLの電位を、トランジスタ120がオン状態となる電位として、トランジスタ120をオン状態とする。これにより、ビット線BLの電位が、容量素子130の第1の端子に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ120がオフ状態となる電位として、トランジスタ120をオフ状態とすることにより、容量素子130の第1の端子の電位が保持される(保持)。

【0158】

半導体層として酸化物半導体を用いたトランジスタ120は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ120をオフ状態とすることで、容量素子130の第1の端子の電位(あるいは、容量素子130に蓄積された電荷)を極めて長時間にわたって保持することが可能である。なお、容量素子130とワード線WL間に容量素子(実施の形態1にて記載した、第1の電極110、ゲート絶縁層106およびゲート電極108により形成される容量素子。)が設けられているため、容量素子130に蓄積された電荷がワード線WLから抜けてしまうことはない。 20

【0159】

次に、情報の読み出しについて説明する。トランジスタ120がオン状態となると、浮遊状態であるビット線BLと容量素子130とが導通し、ビット線BLと容量素子130の間で電荷が再分配される。その結果、ビット線BLの電位が変化する。ビット線BLの電位の変化量は、容量素子130の第1の端子の電位(あるいは容量素子130に蓄積された電荷)によって、異なる値をとる。 30

【0160】

例えば、容量素子130の第1の端子の電位をV、容量素子130の容量をC、ビット線BLが有する容量成分(以下、ビット線容量とも呼ぶ)をCB、電荷が再分配される前のビット線BLの電位をVB<sub>0</sub>とすると、電荷が再分配された後のビット線BLの電位は、(CB × VB<sub>0</sub> + C × V) / (CB + C)となる。従って、メモリセル1850の状態として、容量素子130の第1の端子の電位がV<sub>1</sub>とV<sub>0</sub>(V<sub>1</sub> > V<sub>0</sub>)の2つの状態をとるとすると、電位V<sub>1</sub>を保持している場合のビット線BLの電位(=CB × VB<sub>0</sub> + C × V<sub>1</sub>) / (CB + C)は、電位V<sub>0</sub>を保持している場合のビット線BLの電位(=CB × VB<sub>0</sub> + C × V<sub>0</sub>) / (CB + C)よりも高くなることがわかる。 40

【0161】

そして、ビット線BLの電位を所定の電位と比較することで、情報を読み出すことができる。

【0162】

このように、図7(A)に示す半導体装置は、トランジスタ120のオフ電流が極めて小さいという特徴から、容量素子130に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することができる。 50

## 【0163】

次に、図7(B)に示す半導体装置について、説明を行う。

## 【0164】

図7(B)に示す半導体装置は、上部に記憶回路として図7(A)に示した半導体装置150を複数有するメモリセルアレイ1851a及び1851bを有し、下部に、メモリセルアレイ1851(メモリセルアレイ1851a及び1851b)を動作させるために必要な周辺回路1853を有する。なお、周辺回路1853は、メモリセルアレイ1851と電気的に接続されている。

## 【0165】

図7(B)に示した構成とすることにより、周辺回路1853をメモリセルアレイ1851(メモリセルアレイ1851a及び1851b)の直下に設けることができるため半導体装置の小型化を図ることができる。

10

## 【0166】

周辺回路1853に設けられるトランジスタは、実施の形態1のトランジスタ120とは異なる半導体材料を用いるのがより好ましい。例えば、シリコン、ゲルマニウム、シリコングルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、該トランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することが可能である。

20

## 【0167】

なお、図7(B)に示した半導体装置では、2つのメモリセルアレイ1851(メモリセルアレイ1851aと、メモリセルアレイ1851b)が積層された構成を例示したが、積層するメモリセルの数はこれに限定されない。3つ以上のメモリセルアレイを積層する構成としても良い。

## 【0168】

以上のように、上部に多層に形成された複数のメモリセルアレイは、酸化物半導体を用いたトランジスタにより形成されている。酸化物半導体を用いたトランジスタは、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。

30

## 【0169】

また、実施の形態1に記載したように、半導体装置150はトランジスタ120と容量素子130の構成要素の一部を共有できる、トランジスタ120のゲート電極と層間絶縁層112上に設けられた配線との接続を、容量素子130と重なる位置で行うことができる、といった特徴を有しているため、半導体装置の占有面積の低減を図ることができ、高集積化を図ることができる。

## 【0170】

このように、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)により形成された周辺回路と、酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)により形成された記憶回路とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

40

## 【0171】

なお、本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

## 【0172】

(実施の形態4)

本実施の形態では、実施の形態3に示す半導体装置を用いた応用例の一例として、記憶媒

50

体（メモリ素子）について、図9を用いて説明する。なお、本実施の形態の記憶媒体の説明では、トランジスタ120をトランジスタ520に、容量素子130を容量素子530に、半導体装置150を半導体装置550に置き換えてよい。

【0173】

図9には、いわゆるDRAM（Dynamic Random Access Memory）に相当する構成の半導体装置の一例を示す。図9に示すメモリセルアレイ800は、複数のメモリセルがマトリクス状に配列された構成を有している。また、メモリセルアレイ800は、m本の第1の配線（ワード線WL）、およびn本の第2の配線（ビット線BL）を有する。なお、本実施の形態においては、第1の配線をビット線BLとよび、第2の配線をワード線WLとよぶ。

10

【0174】

メモリセルは、トランジスタ120と容量素子130から構成されており、当該メモリセルに実施の形態1に記載した半導体装置150を用いることができる。トランジスタ120のゲート電極は、第1の配線（ワード線WL）と接続されている。また、トランジスタ120のソース電極またはドレイン電極の一方は、第2の配線（ビット線BL）と接続されており、トランジスタ120のソース電極またはドレイン電極の他方は、容量素子130の電極の一方と接続されている。また、容量素子130の電極の他方は容量線CLと接続され、一定の電位が与えられている。

【0175】

先の実施の形態で示した半導体装置150は、トランジスタ120の半導体層に高純度化され、真性化された酸化物半導体層を用いているため、当該半導体装置のオフ電流を十分に低減することができる。さらに、表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体層を形成することにより、電気伝導度の安定した酸化物半導体層を形成することができる。このような酸化物半導体層を半導体装置150のトランジスタ120に用いることにより、安定した電気的特性が付与された、信頼性の高い半導体装置とすることができる。そして、このような半導体装置150を用いることで、いわゆるDRAMとして認識されている図9に示す半導体装置を実質的な不揮発性メモリとして使用することが可能になる。

20

【0176】

また、半導体装置150は、トランジスタ120と容量素子130の構成要素の一部を共有することができ、トランジスタ120と容量素子130を重畠した状態に形成できるため、半導体装置のサイズを小型化できる。これにより、メモリセルアレイ800を小型化することができる。さらに、トランジスタ120の備えるゲート電極を上層に取り出すにあたり、容量素子130と重なる位置で取り出すことができるため、メモリセルアレイ800を更に小型化することができる。

30

【0177】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0178】

（実施の形態5）

40

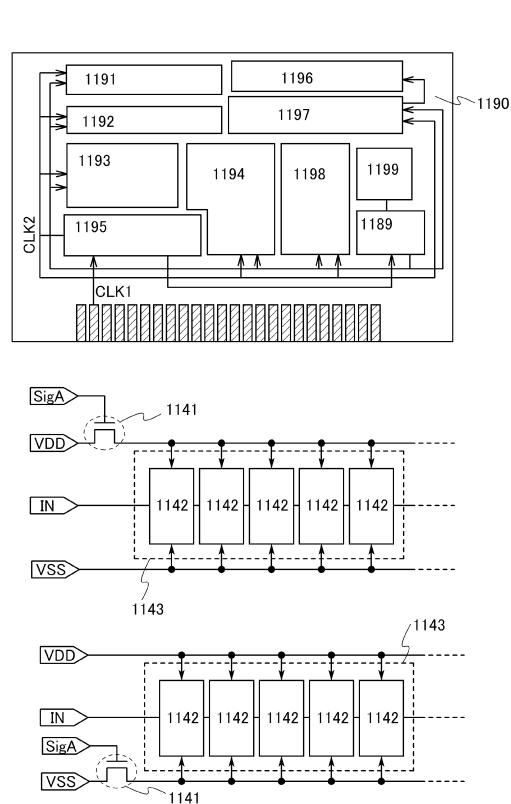

本実施の形態では、上述実施の形態にて説明した記憶装置を少なくとも一部に用いたCPU（Central Processing Unit）について、図10を用いて説明する。

【0179】

図10（A）は、CPUの具体的な構成を示すブロック図である。図10（A）に示すCPUは、基板1190上に、演算回路1191（ALU：Arithmetic logic unitともいう）、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198（Bus I/Fともいう）、書き換え可能なROM1199、およびROMインターフェース1

50

189 (ROM I/Fともいう)を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けても良い。勿論、図10(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

【0180】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インターラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0181】

ALUコントローラ1192、インターラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、演算回路1191の動作を制御するための信号を生成する。また、インターラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

【0182】

また、タイミングコントローラ1195は、演算回路1191、ALUコントローラ1192、インストラクションデコーダ1193、インターラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。

【0183】

図10(A)に示すCPUでは、レジスタ1196に、記憶装置が設けられている。レジスタ1196の記憶装置には、上述実施の形態に記載されている記憶装置を用いることができる。

【0184】

図10(A)に示すCPUにおいて、レジスタコントローラ1197は、演算回路1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有する記憶装置において、位相反転素子によるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。位相反転素子によるデータの保持が選択されている場合、レジスタ1196内の記憶装置への、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内の記憶装置への電源電圧の供給を停止することができる。レジスタ1196に先の実施の形態にて記載した記憶装置を用いることにより、記憶装置への電源電圧の供給を停止した後において、より長期に渡ってデータを保持することが可能となる。

【0185】

電源停止に関しては、図10(B)または図10(C)に示すように、記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設けることにより行なうことができる。以下に図10(B)および図10(C)の回路の説明を行う。

【0186】

図10(B)および図10(C)では、記憶素子への電源電位の供給を制御するスイッチング素子に、酸化物半導体をチャネル形成領域に用いたトランジスタを含む記憶回路の構成の一例を示す。

【0187】

10

20

30

40

50

図10( B )に示す記憶装置は、スイッチング素子1141と、記憶素子1142を複数有する記憶素子群1143とを有している。具体的に、各記憶素子1142の一部には、実施の形態1および実施の形態2に記載されている半導体装置の構造を用いることができる。記憶素子群1143が有する各記憶素子1142には、スイッチング素子1141を介して、ハイレベルの電源電位VDDが供給されている。さらに、記憶素子群1143が有する各記憶素子1142には、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

【0188】

図10( B )では、スイッチング素子1141として、酸化物半導体をチャネル形成領域に有するトランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号SigAによりスイッチングが制御される。

10

【0189】

なお、図10( B )では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、特に限定されず、トランジスタを複数有していても良い。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されても良いし、直列に接続されても良いし、直列と並列が組み合わされて接続されても良い。

【0190】

また、図10( B )では、スイッチング素子1141により、記憶素子群1143が有する各記憶素子1142への、ハイレベルの電源電位VDDの供給が制御されているが、スイッチング素子1141により、ローレベルの電源電位VSSの供給が制御されても良い。

20

【0191】

また、図10( C )には、記憶素子群1143が有する各記憶素子1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、記憶素子群1143が有する各記憶素子1142への、ローレベルの電源電位VSSの供給を制御することができる。

【0192】

記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。具体的には、例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減することができる。

30

【0193】

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)等のLSIにも応用可能である。

【0194】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

40

【0195】

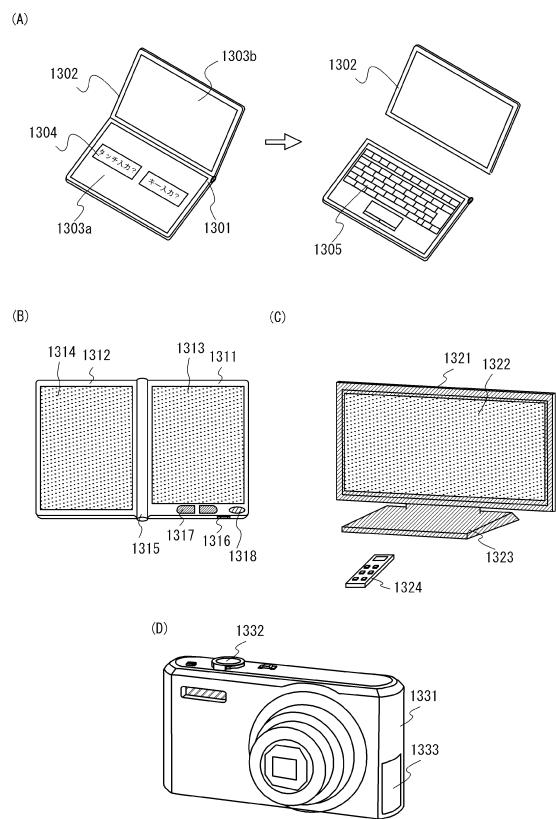

(実施の形態6)

本実施の形態では、先の実施の形態で説明した記憶装置を電子機器に適用する場合について、図11を用いて説明する。本実施の形態では、コンピュータ、携帯情報端末(携帯電話、携帯型ゲーム機、音響再生装置なども含む)、電子ペーパー、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、デジタルビデオカメラなどの電子機器に、上述の半導体装置を適用する場合について説明する。

【0196】

図11( A )は、携帯型の情報端末であり、筐体1301、筐体1302、第1の表示部

50

1303a、第2の表示部1303bなどによって構成されている。筐体1301と筐体1302の内部には、様々な電子部品（例えば、CPU、MPU、記憶素子など。）が組み込まれている。また、第1の表示部1303aと第2の表示部1303bには、画像を表示するために必要な電子回路（例えば、駆動回路や選択回路など。）が搭載されている。これら電子部品や電子回路の中に、先の実施の形態に示す半導体装置を適用することにより、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された携帯型の情報端末が実現される。なお、先の実施の形態に記載された半導体装置は、筐体1301、筐体1302の少なくとも一に設けられていればよい。

#### 【0197】

なお、第1の表示部1303aおよび第2の表示部1303bの少なくとも一方はタッチ入力機能を有するパネルとなっており、例えば図11(A)の左図のように、第1の表示部1303aに表示される選択ボタン1304により「タッチ入力」を行うか、「キーボード入力」を行うかを選択できる。選択ボタンは様々な大きさで表示できるため、幅広い世代の人が使いやすさを実感できる。ここで、例えば「タッチ入力」を選択した場合、図11(A)の右図のように第1の表示部1303aにはキーボード1305が表示される。これにより、従来の情報端末と同様に、キー入力による素早い文字入力などが可能となる。

10

#### 【0198】

また、図11(A)に示す携帯型の情報端末は、図11(A)の右図のように、筐体1301および筐体1302のうち、一方を取り外すことができる。第1の表示部1303aもタッチ入力機能を有するパネルとし、持ち運びの際、さらなる軽量化を図ることができ、また、筐体1301を壁に設置した状態で、筐体1302を用いて画面情報を操作するといった使用方法ができるため非常に便利である。

20

#### 【0199】

図11(A)は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB端子など）、記録媒体挿入部などを備える構成としてもよい。

#### 【0200】

30

また、図11(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

#### 【0201】

さらに、図11(A)に示す筐体1302にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

#### 【0202】

図11(B)は、電子ペーパーを実装した電子書籍であり、筐体1311と筐体1312の2つの筐体で構成されている。筐体1311および筐体1312には、それぞれ表示部1313および表示部1314が設けられている。筐体1311と筐体1312は、軸部1315により接続されており、該軸部1315を軸として開閉動作を行うことができる。また、筐体1311は、電源1316、操作キー1317、スピーカー1318などを備えている。筐体1311、筐体1312の少なくとも一には、先の実施の形態に示す半導体装置が設けられている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された電子書籍が実現される。

40

#### 【0203】

図11(C)は、テレビジョン装置であり、筐体1321、表示部1322、スタンド1323などで構成されている。テレビジョン装置1320の操作は、筐体1321が備えるスイッチや、リモコン操作機1324により行うことができる。筐体1321およびリモコン操作機1324には、先の実施の形態に示す半導体装置が搭載されている。そのた

50

め、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減されたテレビジョン装置が実現される。

【0204】

図11(D)は、デジタルカメラであり、本体1331、操作スイッチ1332、バッテリー1333などを備えており、また、背面には表示部(本体の裏面にあるため図示しない)などを備えている。本体1331内には、先の実施の形態に示す半導体装置が設けられている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減されたデジタルカメラが実現される。

【0205】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭載されている。このため、消費電力を低減した電子機器が実現される。 10

【符号の説明】

【0206】

|       |               |    |

|-------|---------------|----|

| 100   | 基板            |    |

| 102 a | ソース電極         |    |

| 102 b | ドレイン電極        |    |

| 104   | 酸化物半導体層       |    |

| 106   | ゲート絶縁層        |    |

| 108   | ゲート電極         |    |

| 110   | 第1の電極         | 20 |

| 112   | 層間絶縁層         |    |

| 113   | 開口部           |    |

| 114   | 配線            |    |

| 120   | トランジスタ        |    |

| 130   | 容量素子          |    |

| 140   | 領域            |    |

| 150   | 半導体装置         |    |

| 402   | 導電層           |    |

| 410   | 溝部            |    |

| 420   | トランジスタ        | 30 |

| 430   | 容量素子          |    |

| 514   | 被形成面          |    |

| 520   | トランジスタ        |    |

| 530   | 容量素子          |    |

| 550   | 半導体装置         |    |

| 600   | 酸化物半導体膜       |    |

| 602 a | 領域            |    |

| 602 b | 領域            |    |

| 800   | メモリセルアレイ      |    |

| 114 1 | スイッチング素子      | 40 |

| 114 2 | 記憶素子          |    |

| 114 3 | 記憶素子群         |    |

| 118 9 | ROMインターフェース   |    |

| 119 0 | 基板            |    |

| 119 1 | 演算回路          |    |

| 119 2 | ALUコントローラ     |    |

| 119 3 | インストラクションデコーダ |    |

| 119 4 | インタラプトコントローラ  |    |

| 119 5 | タイミングコントローラ   |    |

| 119 6 | レジスタ          | 50 |

|           |            |    |

|-----------|------------|----|

| 1 1 9 7   | レジスタコントローラ |    |

| 1 1 9 8   | バスインターフェース |    |

| 1 1 9 9   | R O M      |    |

| 1 3 0 1   | 筐体         |    |

| 1 3 0 2   | 筐体         |    |

| 1 3 0 3 a | 第 1 の表示部   |    |

| 1 3 0 3 b | 第 2 の表示部   |    |

| 1 3 0 4   | 選択ボタン      |    |

| 1 3 0 5   | キー ボード     |    |

| 1 3 1 1   | 筐体         | 10 |

| 1 3 1 2   | 筐体         |    |

| 1 3 1 3   | 表示部        |    |

| 1 3 1 4   | 表示部        |    |

| 1 3 1 5   | 軸部         |    |

| 1 3 1 6   | 電源         |    |

| 1 3 1 7   | 操作キー       |    |

| 1 3 1 8   | スピーカー      |    |

| 1 3 2 0   | テレビジョン装置   |    |

| 1 3 2 1   | 筐体         |    |

| 1 3 2 2   | 表示部        | 20 |

| 1 3 2 3   | スタンド       |    |

| 1 3 2 4   | リモコン操作機    |    |

| 1 3 3 1   | 本体         |    |

| 1 3 3 2   | 操作スイッチ     |    |

| 1 3 3 3   | バッテリー      |    |

| 1 8 5 1   | メモリセルアレイ   |    |

| 1 8 5 1 a | メモリセルアレイ   |    |

| 1 8 5 1 b | メモリセルアレイ   |    |

| 1 8 5 3   | 周辺回路       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開2010-166030(JP, A)

特開2006-060209(JP, A)

特開2006-237586(JP, A)

米国特許出願公開第2008/0128689(US, A1)

(58)調査した分野(Int.Cl. , DB名)

H01L 21/8242

H01L 27/108