## ITALIAN PATENT OFFICE

Document No.

102011901962134A1

**Publication Date**

20130108

**Applicant**

STMICROELECTRONICS S.R.L.

Title

DISPOSITIVO ELETTRONICO BASATO SU UN COMPOSTO DI GALLIO SU UN SUBSTRATO DI SILICIO, E RELATIVO METODO DI FABBRICAZIONE

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo: "DISPOSITIVO ELETTRONICO BASATO SU UN COMPOSTO DI GALLIO SU UN SUBSTRATO DI SILICIO, E RELATIVO METODO DI FABBRICAZIONE" di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

Inventore: ABAGNALE Giovanni

\* \* \*

La presente invenzione è relativa ad un dispositivo elettronico a semiconduttore basato su un composto ("compound") di gallio, ad esempio nitruro di gallio (GaN), formato su un substrato in silicio (Si), e ad un metodo di fabbricazione dello stesso.

Il nitruro di gallio ha avuto e sta avendo crescente interesse nel campo dei semiconduttori grazie alle proprietà chimiche e fisiche che ne fanno uno dei migliori candidati nella realizzazione di dispositivi di alta potenza e frequenza, nonché optoelettronici operanti in condizioni ambientali ostili (alte temperature, radiazioni ad alta energia, alte frequenze, ecc.). Uno dei principali motivi che ostacolano lo sviluppo di dispositivi in GaN è la scarsa qualità dei layer deposti o cresciuti su substrati in materiale diverso dal nitruro di gallio.

Questo è verificato in particolar modo per quanto riguarda strati di GaN cresciuti su un substrato di silicio.

Attualmente non sono disponibili "bulk" in GaN su cui crescere omoepitassialmente uno strato di GaN. Alcuni dei substrati utilizzati comprendono substrati in carburo di silicio (SiC) o zaffiro, ma questi substrati sono costosi, di natura isolante e non disponibili su grandi diametri.

Il maggior ostacolo nella realizzazione di dispositivi in nitruro di gallio su silicio è dovuto al disaccoppiamento ("mismatch") reticolare tra GaN e Si, e al differente coefficiente termico. Questi fattori causano una alta densità di difetti cristallografici (dislocazioni ed incrinature) dell'intero strato di GaN, influenzando il funzionamento dei dispositivi elettronici così ottenuti.

Per ovviare a quanto detto, sono state sviluppate una pluralità di tecniche allo scopo di minimizzare gli effetti di questi mismatch, ad esempio descritte in "Investigation of buffer growth temperatures for MOVPE of GaN on Si(111)", Journal of Crystal Growth 248 (2003) 578-582, e in "Growth and Characterisation of AlGaN/GaN HEMTon Silicon Substrates", phys. stat. sol. (a) 194, No. 2, 464-467 (2002).

L'inconveniente di queste tecniche è quello di creare delle zone molto difettose all'interfaccia (strato di transizione o "transition layer") e/o strati isolanti che

non possono essere utilizzati come parte attiva dei dispositivi elettronici che le comprendono.

inoltre noto realizzare fori passanti ("through vias") attraverso il substrato in silicio (0, alternativamente, substrato in SiC), per tutto lo spessore del substrato arrivando a contattare una metallizzazione formata sul retro del substrato. Tali fori passanti sono generalmente riempiti mediante metallo. In queste soluzioni, caso essendo i fori passanti molto profondi, il riempimento totale dei fori passanti con metallo non è tecnicamente fattibile; la metallizzazione avviene dunque solo lungo le pareti dei fori passanti, lasciando inevitabilmente zone cave in cui la presenza di aria non favorisce la dissipazione termica. Si ha dunque ulteriore problema legato alla scarsa dissipazione termica.

Scopo della presente invenzione è fornire un dispositivo elettronico basato su un composto di gallio, ad esempio nitruro di gallio, formato su substrato di silicio in grado di superare gli inconvenienti dell'arte nota.

Secondo la presente invenzione vengono forniti ("provided") un dispositivo elettronico basato su un composto di gallio, ad esempio nitruro di gallio, formato su substrato di silicio, e ad un metodo di fabbricazione dello stesso, come definiti nelle rivendicazioni allegate.

Per una migliore comprensione della presente

invenzione, ne vengono ora descritte forme di realizzazione preferite, a puro titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

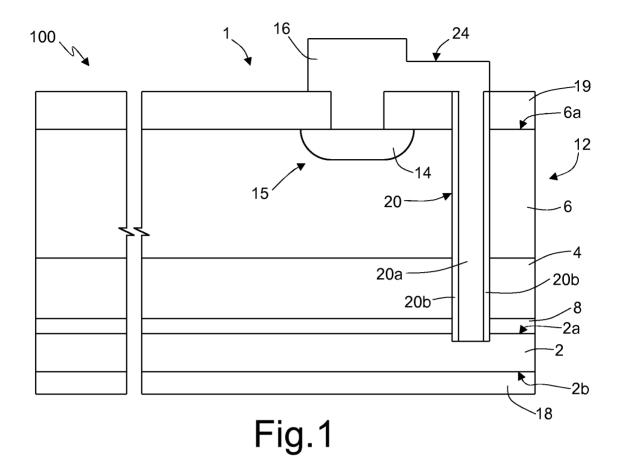

- la figura 1 mostra una vista in sezione di un generico dispositivo elettronico secondo una forma di realizzazione della presente invenzione;

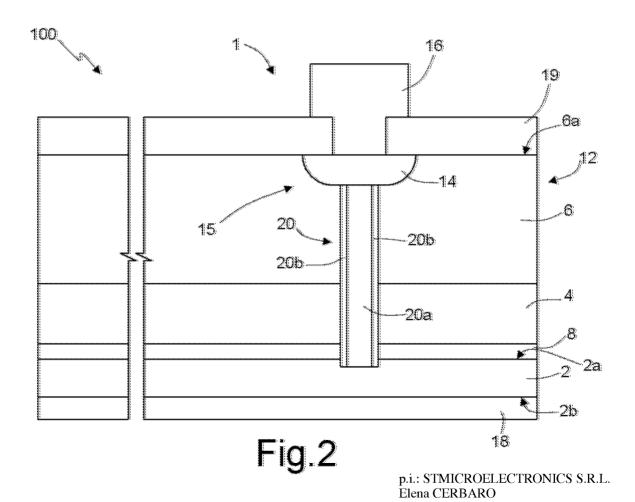

- la figura 2 mostra una vista in sezione di un generico dispositivo elettronico secondo una ulteriore forma di realizzazione della presente invenzione;

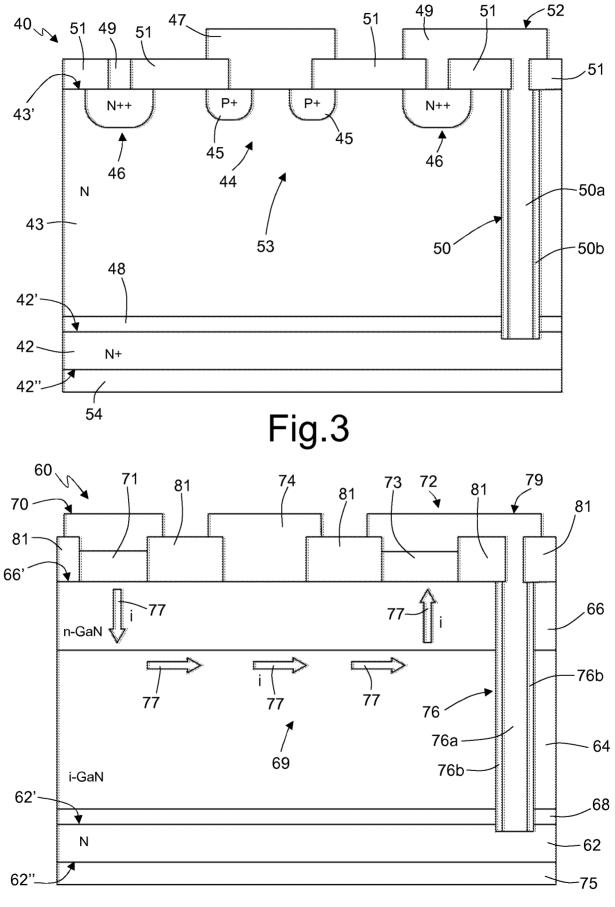

- la figura 3 mostra un diodo Schottky formato secondo una forma di realizzazione della presente invenzione;

- la figura 4 mostra un transistore HEMT formato secondo una forma di realizzazione della presente invenzione;

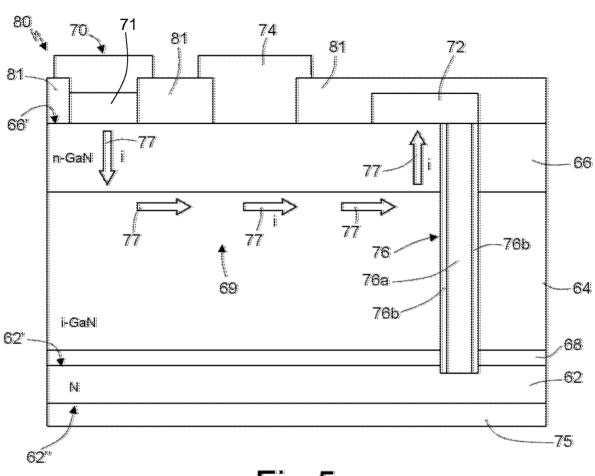

- la figura 5 mostra un transistore HEMT formato secondo una ulteriore forma di realizzazione della presente invenzione; e

- le figura 6a-6d mostrano fasi di fabbricazione successive del transistore HEMT di figura 5.

La figura 1 mostra, in vista in sezione, un dispositivo elettronico 1 secondo una forma di realizzazione della presente invenzione.

Il dispositivo elettronico 1 è formato in una fetta ("wafer") 100 comprendente un substrato 2 di materiale semiconduttore, in particolare silicio, su un cui lato

frontale 2' sono formati (per mezzo di fasi di crescita epitassiale e/o deposito) uno o più strati di nitruro di gallio (GaN) e/o leghe di nitruro di gallio, ad esempio nitruro di gallio alluminio (AlGaN). Il substrato 2 è un substrato a bassa resistività elettrica (alta conduttività) ed è, secondo una forma di realizzazione, drogato mediante specie droganti di tipo N (la dose di impianto è scelta secondo necessità). Secondo una diversa forma di realizzazione, il substrato 2 è drogato mediante specie droganti di tipo P.

Gli strati di nitruro di gallio comprendono almeno uno tra uno strato di buffer 4 di nitruro di gallio di tipo intrinseco (non drogato), ed uno strato di barriera ("barrier layer") 6 di nitruro di gallio drogato. La figura 1 mostra una forma di realizzazione comprendente entrambi gli strati di buffer 4 e di barriera 6, in cui lo strato di barriera 6 è formato al di sopra dello, ed adiacente allo, strato di buffer 4.

All'interfaccia tra il substrato 2 e lo strato di buffer 4 sono presenti uno o più strati di transizione 8 (un solo strato di transizione è mostrato in figura 1), di nitruro di gallio e sui composti come AlGaN, o di AlN arrangiati in numero e combinazioni tali da ridurre il disallineamento reticolare tra i diversi materiali. Lo strato di transizione 8 è uno strato con elevata

difettosità reticolare, dovuta alle tecniche impiegate per ridurre i mismatch reticolari, come già verificato dall'arte nota.

Gli strati di buffer 4 e di barriera 6 formano uno 12 del dispositivo elettronico attivo 1. formazione dello strato attivo 12 comprende, ad esempio, fasi di crescita epitassiale di nitruro di gallio e/o leghe di nitruro di gallio. Processi noti di crescita di nitruro di gallio su silicio portano, come detto, alla formazione uno o più strati in interfaccia aventi difettosità (in figura questi uno o più strati difettosi sono indicati complessivamente con il numero di riferimento 8, e sono indicati nel seguito come strato di transizione 8). Infatti, allo scopo di ridurre il mismatch reticolare tra il silicio ed il GaN, vengono interposti tra questi due strati, uno o più strati di materiali compositi, ad esempio una pluralità di strati di AlN e/o AlGaN, ciascuno avente spessore compreso tra circa 30nm a 400nm e composizione variabili per quanto riguarda il contenuto di alluminio (variabile tra circa 5% e 99% per ogni strato). Questo processo ha l'effetto di generare difetti planari e/o dislocazioni che si propagano fino alla superficie della fetta ("wafer"), partendo dal substrato. Allo scopo di evitare tali difettosità, durante la crescita dell'epitassia vengono formati strati intermedi, detti strati di buffer, in cui avviene l'annichilimento dei difetti ma lasciando, ovviamente, una regione dell'intera epitassia fortemente difettosa.

Lo strato di barriera 6 è drogato di tipo P o N a seconda della particolare forma di realizzazione del dispositivo elettronico 1, in modo dipendente dalle caratteristiche elettriche che si desidera ottenere per il dispositivo elettronico 1.

Secondo una forma di realizzazione della presente invenzione, in corrispondenza di una regione superficiale 6a dello strato di barriera 6, sono formati uno o più terminali di conduzione del dispositivo elettronico comprendenti regioni impiantate 14 e/o terminali contatto frontale 16 (in particolare, metallizzazioni) in contatto elettrico con le regioni impiantate 14, definenti un'area attiva 15 del dispositivo elettronico 1. Ai fini della presente invenzione si intende come area attiva 15, genericamente, la regione del dispositivo elettronico 1 in cui avvengono fenomeni di trasporto di carica elettrica. attiva 15 può pertanto comprendere regioni L'area impiantate o generici terminali di conduzione del dispositivo elettronico 1. Risulta evidente che dispositivo elettronico 1 può avere una pluralità di aree attive 15, separate tra loro da regioni di isolamento di campo (non mostrate).

Il dispositivo elettronico 1 comprende inoltre uno strato di passivazione 19, a protezione della regione superficiale 6a dello strato di barriera 6.

Inoltre, in corrispondenza di un lato retro ("back side") 2" del substrato 2 sono formati uno o più terminali di contatto di retro 18 (in particolare, metallizzazioni, una sola è mostrata in figura 1).

Il dispositivo elettronico 1 comprende inoltre uno o più fori ("via holes"), o trincee ("trenches"), (uno solo è mostrato in figura 1 ed è indicato con il numero di riferimento 20), configurati per collegare i terminali di contatto frontale 16 con il substrato 2, attraversando lo strato di barriera 6, lo strato di buffer 4, e lo strato di transizione 8. Ciascun via hole 20 può essere formato indifferentemente all'interno o all'esterno dell'area attiva 15 del dispositivo elettronico 1.

Il via hole 20 mostrato in figura 1 comprende una porzione di riempimento interna di materiale conduttivo, ad esempio metallo o polisilicio drogato, formante una regione conduttiva 20a che si estende dalla regione superficiale 6a fino a raggiungere e contattare elettricamente il substrato 2. Una collegamento elettrico superficiale 24 è inoltre formato in modo tale da collegare elettricamente la regione conduttiva 20a del via hole 20 con un rispettivo terminale di contatto frontale 16.

Opzionalmente, a seconda della particolare applicazione del dispositivo elettronico 1 e dalle caratteristiche elettriche degli strati di buffer 4 e di barriera 6, il via hole 20 comprende inoltre una regione isolante 20b circondante la regione conduttiva 20a, e configurata in modo da isolare elettricamente la regione conduttiva 20a dagli strati di buffer 4 e di barriera 6.

In questo modo, si realizza un collegamento conduttivo tra il terminale di contatto di retro 18 e il rispettivo terminale di contatto frontale 16, attraverso il via hole 20.

Secondo una diversa forma di realizzazione della presente invenzione, mostrata nella figura 2, uno o più via hole 20 aventi una rispettiva regione conduttiva 20a (un solo via hole 20 è mostrato in figura 2) sono formati in corrispondenza di un rispettivo terminale di contatto frontale 16, in modo tale che la regione conduttiva 20a del via hole 20 sia in contatto elettrico con il terminale di contatto frontale 16 tramite la regione impiantata 14. In vista dall'alto, dunque, il via hole 20 è formato parzialmente o totalmente allineato con almeno una porzione di un rispettivo terminale di contatto frontale 16. In questo caso, il collegamento elettrico superficiale 24 non è presente.

La realizzazione di strutture del tipo mostrato nelle figure 1 e 2 consente la fabbricazione di dispositivi elettronici in nitruro di gallio (e leghe di nitruro di gallio) su un substrato di silicio aventi basso costo ma mantenendo le prestazioni elettriche tipiche del nitruro di gallio.

I vantaggi delle forme di realizzazione mostrate nelle figure 1 e 2 risiedono nel fatto che strati di GaN possono essere cresciuti su strati altamente isolanti sia termicamente che elettricamente (quale ossidi o nitruri) e/o altamente difettosi senza che questo comporti una riduzione delle prestazioni del dispositivo e/o una ridotta dissipazione di calore e/o difficoltà di integrazione in circuiti o package di tipo noto. Infatti, la conduzione elettrica e/o termica può avvenire tra il fronte e il retro della fetta attraverso i "via hole" formati come prima descritto, superando i principali problemi che ostacolano lo sviluppo di dispositivi in GaN su silicio.

Il substrato 2 è, secondo forme di realizzazione della presente invenzione, Si <111> e/o Si <100> a bassa resistività (ad esempio con valore compreso tra circa 0,005  $\Omega \cdot \text{cm}$  e circa 0.5  $\Omega \cdot \text{cm}$ ), con spessore compreso tra circa 500 $\mu$ m e circa 1500 $\mu$ m. La struttura del dispositivo elettronico 1 con collegamento verticale tra il fronte del dispositivo elettronico 1 (es., in corrispondenza dell'area

attiva) e il substrato consente il passaggio di barriera evitando lo strato di transizione 8 ad alta densità di difetti, e senza che questo influisca sul rendimento del dispositivo elettronico 1. Si migliora inoltre la dissipazione di calore attraverso il substrato 2, tramite la regione conduttiva 20a del via hole 20 in contatto con il substrato 2. In questo modo, il substrato 2 di silicio è parte integrante del dispositivo elettronico 1, e non un mero substrato avente la funzione di supporto per lo strato attivo 12 in nitruro di gallio.

Lo strato di transizione 8 ha tipicamente spessore compreso tra circa 1  $\mu m$  e circa 5  $\mu m$ . Lo strato attivo 12 comprende, come detto, uno o più strati di GaN, o leghe di GaN, che costituiscono la parte attiva del dispositivo, con spessore, concentrazione di barriera e tipologia di lega (ad esempio, GaN e/o  $Al_xGa_yN$ ) scelti opportunamente a seconda del dispositivo da realizzare (ad esempio, ma non solo, HEMTs, diodi Schottky, MESFET, ecc).

Le metallizzazioni dei contatti sul fronte 6a può essere effettuata utilizzando diverse variante note in letteratura, come ad esempio formazione di contatti in AlSiCu/Ti, in Al/Ti, o W-plug, o altri ancora.

Il contatto elettrico con il retro 2" del substrato 2 viene realizzato attraverso metallizzazione del retro

wafer, eventualmente formando "bumps" atti a consentire un'integrazione verticale del dispositivo elettronico 1.

Oltre al nitruro di gallio, i vantaggi della presente invenzione si estendono a dispositivi elettronici comprendenti uno strato ad elevata difettosità disposto tra il substrato ed uno strato, includente l'area attiva del dispositivo elettronico, formato al di sopra dello strato difettoso.

Si fa qui notare che il problema è tuttavia particolarmente sentito nel caso di strati di GaN cresciuti su un substrato di silicio. Forme di realizzazione che presentano substrati in germanio (Ge) su cui vengono cresciuti strati di arsenuro di gallio (GaAs) non presentano lo stesso problema, o lo presentano in modo minimo, in quanto il mismatch reticolare tra Ge e GaAs è minimo.

La figura 3 mostra un dispositivo elettronico del tipo descritto con riferimento alle figure 1 e 2 configurato in modo da operare come diodo Schottky, secondo una forma di realizzazione della presente invenzione.

Il diodo Schottky 40 comprende un substrato 42 di silicio drogato di tipo N+ su un cui lato frontale 42' è cresciuto uno strato di 43 di AlN/AlGaN/GaN. Il diodo Schottky 40 comprende inoltre, formata nello strato di corpo 43 e affacciata alla superficie superiore ("top

surface") 43' dello strato di corpo 43, una regione di anodo 44, definita da una struttura ad anello 45 realizzata mediante impianto di specie droganti di tipo P, e collegata ad un terminale di polarizzazione di anodo attraverso una metallizzazione di anodo 47. Il diodo Schottky 40 comprende inoltre una regione di catodo 46, formata nello strato di corpo 43, affacciata alla superficie superiore 43' dello strato di corpo 43, e circondante esternamente la regione di anodo 44. La regione di catodo 46 è formata, ad esempio, mediante impianto di specie droganti di tipo N, a formare una regione drogata N++. La regione di catodo 46 è inoltre elettricamente collegata ad un terminale di polarizzazione di catodo attraverso una metallizzazione di catodo 49, formata al di sopra dello strato di corpo 43. Le regioni di anodo 44 e di catodo 46 definiscono una regione di area attiva 53 del diodo Schottky 40.

Lo strato di corpo 43 comprende uno strato di transizione 48, disposto all'interfaccia con il substrato 42, analogo allo strato di transizione 8. In modo non mostrato in figura, lo strato di corpo 43 può comprendere una pluralità di strati successivi, ad esempio con differente valore di drogaggio, di nitruro di gallio o sue leghe.

Le metallizzazioni di catodo e di anodo 49, 47 sono isolate tra loro mediante uno strato di passivazione 51,

formato sulla superficie superiore 43' dello strato di corpo 43.

Il diodo Schottky 40 comprende inoltre un via hole, o trincea ("trench"), 50, estendentesi a partire dalla superficie superiore 43' dello strato di corpo 43 fino a raggiungere il substrato 42, attraversando lo strato di transizione 48. Secondo una forma di realizzazione della presente invenzione, il via hole 50 è formato, in vista dall'alto, in una porzione della superficie superiore 43' dello strato di corpo 43 esterna all'area definita dalla regione di catodo 46. Il via hole 50 include una porzione conduttiva 50a, ad esempio metallo (ad esempio Al, AlCu, W, AlSiCu, AlTi, o altri ancora), o polisilicio drogato, elettricamente collegata alla metallizzazione di anodo 47 mediante un collegamento elettrico superficiale 52.

Secondo una forma di realizzazione della presente invenzione, lo strato di corpo 43 ha uno spessore compreso tra circa 2 µm e circa 5 µm; lo strato di transizione 48 ha uno spessore compreso tra circa 0,4 µm e circa 3 µm esempio; pertanto, il via hole 50 si estende per una profondità compresa tra circa 2 µm e circa 5 µm. Su un lato posteriore 42" del substrato 42, opposto rispetto al lato frontale 42', è inoltre formata una metallizzazione posteriore ("back metallization") 54, in contatto elettrico con il substrato 42. La metallizzazione posteriore 54 ha la

funzione di contatto di catodo e consente la polarizzazione della regione di catodo 46 dal retro del substrato 42.

Secondo una diversa forma di realizzazione della presente invenzione (non mostrata), il via hole 50 è elettricamente collegato alla regione di anodo 44. In questo caso, il contatto per la polarizzazione della regione di catodo 46 è disposto in corrispondenza del lato frontale del diodo Schottky 30 (cioè in corrispondenza della superficie superiore 43'), mentre il contatto per la polarizzazione della regione di anodo 44 è realizzato in corrispondenza del lato posteriore 42" del substrato 42, elettricamente collegato alla metallizzazione posteriore 54, ad esempio nella forma di bump conduttivo.

Indipendentemente dalla forma di realizzazione, il via hole 50 può includere, opzionalmente, uno strato di isolamento 50b che ricopre le pareti interne del via hole 50 ed è atto ad isolare elettricamente la porzione conduttiva 50a del via hole 50 dallo strato di corpo 43. Lo strato di isolamento 50b è, ad esempio, ossido di silicio, o nitruro di silicio, o polimmide.

Lo strato di isolamento 50b può essere omesso se il dispositivo elettronico viene realizzato per applicazioni a radio frequenza e non per potenza.

La figura 4 mostra un transistore 60 configurato in modo da operare come dispositivo HEMT ("High electron

mobility transistore"), secondo una ulteriore forma di realizzazione della presente invenzione.

I transistori HEMT, anche noti come transistori HFETTransistore") ("Heterostructure Field Effect sono elettronici noti. includenti dispositivi una eterogiunzione, cioè una giunzione tra due semiconduttori con differente "band gap". Semiconduttori utilizzati a questo scopo sono, ad esempio, il nitruro di gallio (GaN) e il nitruro di gallio alluminio (AlGaN). Il transistore HEMT sfrutta la formazione di elettroni ad alta mobilità elettronica presenti nella buca di potenziale generata dall'eterogiunzione tra i due semiconduttori. Questo strato di elettroni ad alta mobilità è detto strato 2DEG (gas bidimensionale di elettroni, "2-Dimensional Electron Gas"), e costituisce il canale del transistore HEMT.

Il transistore 60 della figura 4 comprende un substrato 62 di silicio, ad esempio drogato di tipo N; uno strato di buffer 64, ad esempio di GaN di tipo intrinseco, formato su un lato superiore 62' del substrato 62; e uno strato di barriera 66, formato al di sopra dello strato di buffer, ad esempio di AlGaN. È inoltre mostrato in figura 4 uno strato di transizione 68, disposto tra il substrato 62 e lo strato di buffer 64. Lo strato di transizione 68 si genera durante le fasi di formazione dello strato di buffer

64 sul substrato di silicio 62, come precedentemente descritto.

Il transistore 60 comprende inoltre, in modo noto, una regione (o terminale) di sorgente 70, in contatto con una regione di separazione 71 in AlGaN, ed in collegamento elettrico per effetto tunnel con il canale sottostante identificato da frecce 77; una regione (o terminale) di pozzo ("drain") 72, in contatto con una regione di separazione 73 in AlGaN, ed in collegamento elettrico per effetto tunnel con il canale sottostante identificato dalle frecce 77; e una regione (o terminale) di porta ("gate") 74. Questi ultimo sono formati in corrispondenza di un lato frontale 66' del transistore 60 (cioè sul lato libero dello strato di barriera 66). In uso, polarizzando opportunamente la regione di porta 74, una corrente i fluisce tra le regioni di sorgente 70 e di porta 74 secondo il percorso definito dalle frecce 77.

Le regioni di sorgente 70, di pozzo 72, e di porta 74, insieme con le porzioni dello strato di buffer 64 e di barriera 66 in cui fluisce la corrente  $\underline{i}$  definiscono un'area attiva 69 del transistore 60.

Le regioni di sorgente 70, di pozzo 72, e di porta 74 sono isolate tra loro mediante uno strato di passivazione 81, formato lato frontale 66' del transistore 60.

Secondo un aspetto della presente invenzione, il transistore 60 comprende inoltre una metallizzazione posteriore 75, formata su un lato posteriore 62" del substrato 62, in contatto elettrico con il substrato 62.

ulteriore Secondo un aspetto della presente invenzione, il transistore 60 comprende una trincea 76 estendentesi dal lato frontale 66' del transistore 60 verso il substrato 62, fino a raggiungere il substrato 62, attraversando lo strato di barriera 66, lo strato di buffer 64, e lo strato di transizione 68. Il via hole 76 comprende una porzione interna conduttiva 76a, ad esempio di metallo o di polisilicio drogato, in contatto elettrico diretto con substrato 62. Secondo un aspetto della presente invenzione, il via hole 76 comprende inoltre una porzione interna isolante 76b, formata adiacente alle pareti laterali del via hole 76 in modo tale da isolare elettricamente la porzione interna conduttiva 76a dallo strato di barriera 66, dallo strato di buffer 64, e dallo strato di transizione 68.

La porzione interna isolante 76b può essere omessa se il dispositivo elettronico viene realizzato per applicazioni a radio frequenza e non per potenza.

Il via hole 76 (e in particolare la porzione interna conduttiva 76a) è inoltre elettricamente collegato, mediante una striscia conduttiva 79, ad una tra la regione

di sorgente 70, la regione di pozzo 72 e la regione di porta 74. La figura 4 mostra il transistore 60 in cui la porzione interna conduttiva 76a del via hole 76 è collegata alla regione di pozzo 72, mediante una opportuna metallizzazione.

5 mostra una forma di realizzazione La figura alternativa del transistore 60 di figura 4, secondo un ulteriore aspetto della presente invenzione. In figura 5 è mostrato un transistore 80 dello stesso tipo transistore 60 descritto con riferimento alla figura 4, ma in questo caso il via hole 76 è formato in corrispondenza di una tra la regione di sorgente 70 e la regione di pozzo 72. Più in particolare, il via hole 76 parzialmente allineato, in vista dall'alto, con una tra la regione di sorgente 70 e la regione di pozzo 72. porzione interna conduttiva 76a del via hole 76 è contatto elettrico con la regione di pozzo 72, e forma un collegamento elettrico tra la regione di pozzo 72 e la metallizzazione posteriore 75, sfruttando il substrato 62.

La metallizzazione superiore della regione di pozzo 72 e la striscia conduttiva 79 non sono presenti.

In uso, il transistore 60 o il transistore 80 operano in modo noto.

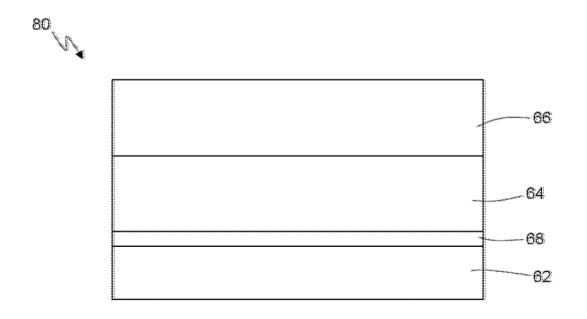

Le figure 6a-6d mostrano fasi di un metodo di fabbricazione utilizzabile per fabbricare il transistore 80 di figura 5.

La figura 6a mostra il transistore 80 in una fase intermedia di fabbricazione, in seguito ad una serie di fasi di fabbricazione di tipo noto.

Con maggiore dettaglio, il transistore 80 di figura 6a è ottenuto mediante le seguenti fasi di processo.

Si dispone ("provide") un substrato 62, di materiale semiconduttore, in particolare silicio.

Quindi, si forma, ad esempio mediante crescita epitassiale di nitruro di gallio sul substrato 62, uno strato di buffer 64 di tipo non drogato (i-GaN) avente spessore compreso tra circa 0.6 µm e circa 1 µm. Questa fase porta alla formazione dello strato di transizione 68, all'interfaccia con il substrato 62. In questa fase si formano e si propagano i difetti dovuti al mismatch reticolare.

Quindi, si forma, al di sopra dello strato di buffer 64, uno strato di barriera 66, ad esempio mediante crescita epitassiale, avente spessore compreso tra circa 1 µm e circa 1,5 µm. Lo strato di barriera 66 è, secondo una forma di realizzazione della presente invenzione, di nitruro di gallio drogato di tipo N, oppure, secondo una ulteriore

forma di realizzazione, di nitruro di gallio alluminio (AlGaN).

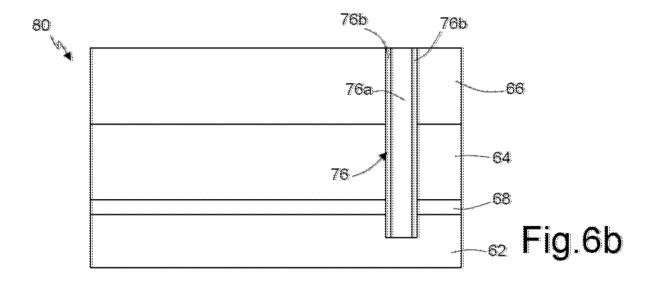

seguito, figura secondo 6b, una forma di realizzazione della presente invenzione, lo strato di barriera 66 viene selettivamente attaccato in corrispondenza di una porzione in cui sarà formata, durante fasi successive, la regione di pozzo 72. L'attacco è, ad esempio, ti tipo secco ("dry") (ad esempio un attacco RIE, "reactive ion etching", o DRIE, "deep reactive etching").

L'attacco dello strato di barriera 66 è volto alla formazione del via hole 76 di figura 5. A tal l'attacco dello strato di barriera 66 è, ad esempio, effettuato utilizzando una soluzione a base di cloro, fino a raggiungere lo strato di buffer 64. Anche lo strato di buffer 64 viene attaccato utilizzando 10 stesso procedimento. Si continua quindi con l'attacco dello strato di transizione 68 mediante lo stesso procedimento, fino a raggiungere il substrato 62. Il procedimento di attacco può essere monitorato in modo tale da raggiungere il substrato 62 e fermarsi al substrato 62, oppure in modo da attaccare solo parzialmente il substrato 62.

Quindi, uno strato di materiale isolante viene formato sulle pareti interne del via hole 76, formando la

porzione interna isolante 76b (ad esempio tramite processo di deposizione PECVD).

Infine, si esegue una fase di deposito di materiale conduttore internamente al via hole 76, formando la porzione interna conduttiva 76a. La porzione interna conduttiva 76a può essere formata mediante varie tecniche di deposizione di tipo noto, non facenti parte della presente invenzione.

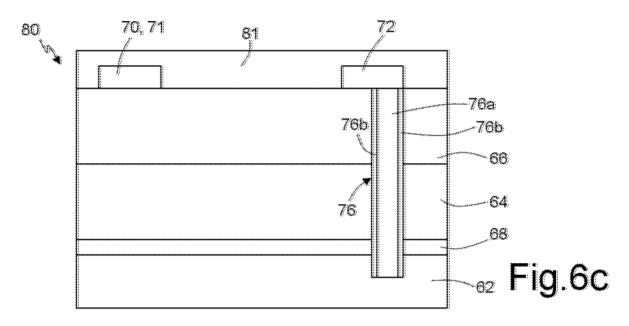

Quindi, figura 6c, il procedimento di fabbricazione del transistore 80 continua secondo fasi di per sé note. In particolare, vengono formate le regioni di sorgente 70 e di pozzo 72. La regione di sorgente 70 comprende una porzione 71 di GaAl, e la regione di pozzo 72 è formata almeno parzialmente sovrapposta alla porzione conduttiva 76a del via hole 76, in modo tale che sia in contatto elettrico con essa. Uno strato isolante, o di passivazione, 81 è quindi formato sul fronte della fetta che porta il transistore 80, in modo tale da isolare lateralmente tra loro le regioni di sorgente 70 e di pozzo 72.

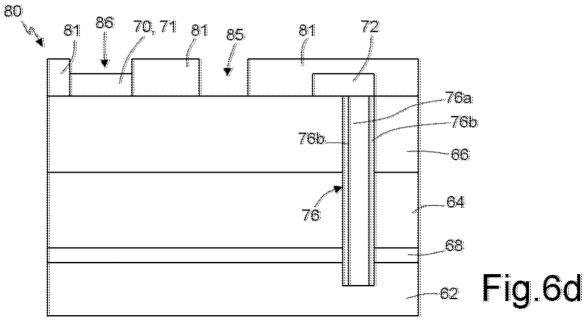

Le fasi del procedimento descritto comprendono inoltre formare (figura 6d) la regione di porta 74. A questo fine, lo strato di passivazione 81 viene selettivamente attaccato in corrispondenza della porzione del lato frontale 66' in cui si desidera formare la regione di porta 74, formando un'apertura 85. Contestualmente a questa fase, lo strato di

passivazione 81 viene inoltre attaccato in corrispondenza della regione di sorgente 70, per definire un'apertura 86 in cui formare la metallizzazione di sorgente.

Una fase di deposito di uno strato di metallo, ad esempio mediante evaporazione o sputtering, ed una successiva fase di definizione fotolitografica, porta alla formazione della regione di porta 74 e della metallizzazione di sorgente, ottenendo il transistore 80 di figura 5.

Risulta evidente che, secondo una ulteriore forma di realizzazione della presente invenzione (non mostrate in figura), il via hole 76 può essere formato in contatto elettrico con la regione di sorgente 70, e non con la regione di pozzo 72. In questo caso, la metallizzazione di sorgente non è formata, e viene formata invece una metallizzazione di pozzo.

Il procedimento descritto può essere applicato, con le opportune varianti, per la formazione del transistore 60 di figura 4. In questo caso, la fase di formazione del via hole 76 è eseguita dopo la fase di formazione dello strato di passivazione 81 e comprende, prima della fase di attaccare lo strato di barriera 66, la fase di attaccare lo strato di passivazione 81. Inoltre, lo strato di passivazione 81 viene anche attaccato in corrispondenza della regione di pozzo 72, per formare un'apertura atta a

consentire la formazione del contatto elettrico con il via hole 76, tramite la striscia conduttiva 79.

Risulta evidente che il procedimento di formazione del via hole 76 descritto non è limitato alla fabbricazione di un transistore HEMT, ma può essere integrato in fasi di processo fabbricazione di qualsiasi tipo di dispositivo elettronico.

Da un esame delle caratteristiche del trovato realizzato secondo la presente invenzione sono evidenti i vantaggi che essa consente di ottenere.

In particolare, secondo la presente invenzione, è possibile fabbricare dispositivi in GaN su substrati a basso costo (fette in silicio) superando gli ostacoli insiti nella crescita eteroepitassiale di GaN su silicio, che causa la formazione di interfacce altamente difettose e/o interlayer a bassa conducibilità termica ed elettrica.

Questo consente di realizzare eterostrutture tramite crescita epitassiale con elevata flessibilità di progetto, senza limitare in alcun modo la scelta della migliore metodologia di crescita di GaN (o sue leghe) a seconda del particolare necessità, e su scala industriale.

Inoltre, secondo la presente invenzione, il substrato di silicio è parte attiva del dispositivo elettronico fabbricato, e non è solo un supporto su cui realizzare l'epitassia.

presente invenzione, inoltre, permette efficiente dissipazione del calore generato dal dispositivo elettronico durante l'uso, grazie alla possibilità di realizzare contatti metallici all'interno dell'area attiva del dispositivo elettronico stesso. Sono inoltre evitati problemi relativi alla formazione di sacche di aria, che limitano la dissipazione termica. Infatti, essendo i via hole secondo la presente invenzione poco profondi particolare aventi profondità definita dallo spessore dell'epitassia cresciuta al di sopra del substrato, ed indipendente dallo spessore del substrato stesso). qualunque sia la tecnica utilizzata per il riempimento del via hole, il via hole è sempre completamente riempito. In questo modo si evitano zone vuote che si formerebbero nel caso di trench o vias molto profondi (in particolare attraversanti l'intero substrato oltre che l'epitassia formata al di sopra di esso).

Infine, la formazione di contatti metallici verso il substrato all'interno dell'area attiva, consente di ridurre il "pitch" del dispositivo.

Risulta infine chiaro che a quanto qui descritto ed illustrato possono essere apportate modifiche e varianti senza per questo uscire dall'ambito di protezione della presente invenzione, come definito nelle rivendicazioni allegate.

In particolare, la presente invenzione non è limitata a strutture in gallio (o sue leghe, ad esempio GaN) cresciute su silicio, ma può essere estesa a generiche strutture in cui il substrato è elettricamente e/o termicamente isolato da uno strato attivo sovrastante (ad esempio a causa della presenza di uno strato di interfaccia indesiderato elettricamente e/o termicamente isolante).

Inoltre, l'insegnamento secondo la presente invenzione non è limitato ad un particolare dispositivo elettronico, come ad esempio il diodo Schottky di figura 3 o il transistore HEMT delle figure 4 e 5, ma può essere esteso a qualsiasi dispositivo elettronico avente una struttura tale per cui in cui il substrato è elettricamente isolato da uno strato attivo sovrastante (ad esempio, ma non solo, un transistore MOSFET in GaN integrato su un substrato in silicio).

## RIVENDICAZIONI

- 1. Dispositivo elettronico (1; 40; 60; 80) comprendente:

- un substrato (2; 42; 62) di un primo materiale semiconduttore avente un primo (2'; 42'; 62') e un secondo (2"; 42"; 62") lato ("side");

- uno strato strutturale (12), di un secondo materiale semiconduttore diverso dal primo materiale semiconduttore, formato sul primo lato (2'; 42'; 62') del substrato (2; 42; 62) e includente un'area attiva (15; 53; 69) di detto dispositivo elettronico;

- uno strato di transizione (8; 48; 68), interposto tra il substrato e lo strato strutturale, lo strato di transizione isolando elettricamente e/o termicamente tra loro il substrato e lo strato strutturale,

caratterizzato dal fatto di comprendere inoltre un via hole (20; 76), di tipo conduttivo, estendentesi attraverso lo strato strutturale (12) e lo strato di transizione (8; 48; 68), ed essendo configurato in modo da collegare elettricamente e/o termicamente l'area attiva del dispositivo elettronico al substrato (2; 42; 62).

2. Dispositivo elettronico secondo la rivendicazione 1, in cui il via hole (20; 76) comprende una porzione conduttiva (20a) estendentesi tra e in contatto elettrico con l'area attiva (15; 53; 69) del dispositivo elettronico

- e il substrato (2; 42; 62).

- 3. Dispositivo elettronico secondo la rivendicazione 2, in cui il via hole (20; 76) comprende una porzione isolante (20b), estendentesi tra una parete interna del via hole (20; 76) e la porzione conduttiva (20a), configurata in modo da isolare elettricamente la porzione conduttiva (20a) dallo strato strutturale (12).

- 4. Dispositivo elettronico secondo una qualsiasi delle rivendicazioni precedenti, in cui il primo materiale semiconduttore è silicio ed il secondo materiale semiconduttore è un composto ("compounds") del gallio, in particolare scelto tra nitruro di gallio e nitruro di gallio alluminio.

- 5. Dispositivo elettronico secondo una qualsiasi delle rivendicazioni precedenti, comprendente inoltre un primo terminale di conduzione (18; 54; 75), formato in corrispondenza del secondo lato (2"; 42"; 62") del substrato e in contatto elettrico con il substrato, detta area attiva (12) essendo elettricamente collegata al primo terminale di conduzione (18; 54; 75) tramite il via hole (20; 76) e il substrato (2; 42; 62).

- 6. Dispositivo elettronico secondo la rivendicazione 5, in cui lo strato strutturale (12) include un secondo terminale di conduzione (44; 70) e un terzo terminale di conduzione (46; 72), detto terzo terminale di conduzione

- (46; 72) essendo elettricamente collegato all'area attiva (15; 53; 69) e al via hole (20; 76) in modo tale che, in uso, una corrente elettrica fluisca tra il secondo (44; 70) e il primo (54; 75) terminale di conduzione attraverso detti area attiva (15; 53; 69), terzo terminale di conduzione (46; 72), via hole (20; 76), e substrato (2; 42; 62).

- 7. Dispositivo elettronico secondo la rivendicazione 6, in cui il secondo terminale di conduzione (44) è un terminale di anodo e il terzo terminale di conduzione (44) è un terminale di catodo, detto dispositivo elettronico essendo configurato per operare come un diodo Schottky (40).

- 8. Dispositivo elettronico secondo la rivendicazione 6, in cui il secondo terminale di conduzione (70) è un terminale di sorgente e il terzo terminale di conduzione (72) è un terminale di pozzo, detto dispositivo elettronico comprendendo inoltre un terminale di controllo ed essendo configurato per operare come un transistore (60; 80).

- 9. Metodo di fabbricazione di un dispositivo elettronico (1; 40; 60; 80) comprendente le fasi di:

- disporre ("providing") un substrato (2; 42; 62) di un primo materiale semiconduttore avente un primo (2'; 42'; 62') e un secondo (2"; 42"; 62") lato ("side");

- formare uno strato strutturale (12) di un secondo

materiale semiconduttore diverso dal primo materiale semiconduttore, comprendente un'area attiva (15; 53; 69), sul primo lato (2'; 42'; 62') del substrato (2; 42; 62);

- formare uno strato di transizione (8; 48; 68), tra il substrato e lo strato strutturale, lo strato di transizione isolando elettricamente e/o termicamente tra loro il substrato e lo strato strutturale,

caratterizzato dal fatto di comprendere inoltre la fase di formare un via hole (20; 76), di tipo conduttivo, attraverso lo strato strutturale (12) e lo strato di transizione (8; 48; 68), così da collegare elettricamente e/o termicamente l'area attiva del dispositivo elettronico con il substrato (2; 42; 62).

- 10. Metodo secondo la rivendicazione 9, in cui la fase di formare il via hole (20; 76) comprende:

- rimuovere porzioni selettive dello strato strutturale (12) e dello strato di transizione (8; 48; 68);

- formare internamente al via hole una porzione conduttiva (20a) estendentesi tra e in contatto elettrico con l'area attiva (15; 53; 69) del dispositivo elettronico e il substrato (2; 42; 62).

- 11. Metodo secondo la rivendicazione 10, in cui la fase di formare il via hole (20; 76) comprende inoltre formare una porzione isolante (20b) tra la parete interna del via hole (20; 76) e la porzione conduttiva (20a), così

da isolare elettricamente la porzione conduttiva (20a) dallo strato strutturale (12).

- 12. Metodo secondo una qualsiasi delle rivendicazioni 9-11, in cui il primo materiale semiconduttore è silicio e in cui la fase di formare lo strato strutturale (12) comprende formare uno strato o più strati sovrapposti di uno o più composti ("compounds") di gallio, in particolare scelti tra nitruro di gallio e nitruro di gallio alluminio.

- 13. Metodo secondo una qualsiasi delle rivendicazioni 9-12, comprendente inoltre le fasi di:

- formare un primo terminale di conduzione (18; 54; 75) in corrispondenza del secondo lato (2"; 42"; 62") del substrato e in contatto elettrico con il substrato; e

- collegare elettricamente l'area attiva (15; 53; 69) al primo terminale di conduzione (18; 54; 75) tramite il via hole (20; 76) e il substrato (2; 42; 62).

- 14. Metodo secondo la rivendicazione 13, comprendente inoltre le fasi di:

- formare un secondo (44; 70) e un terzo (46; 72) terminale di conduzione nell'area attiva (15; 53; 69);

- collegare elettricamente detto terzo terminale di conduzione (46; 72) all'area attiva (15; 53; 69) e al via hole (20; 76);

- operare, durante l'uso, il dispositivo elettronico (1; 40; 60; 80) in modo tale che una corrente elettrica

fluisca tra il secondo (44; 70) e il primo (54; 75) terminale di conduzione attraverso detti area attiva (15; 53; 69), terzo terminale di conduzione (46; 72), via hole (20; 76), e substrato (2; 42; 62).

p.i.: STMICROELECTRONICS S.R.L.

Elena CERBARO

## CLAIMS

- 1. An electronic device (1; 40; 60; 80) comprising:

- a substrate (2; 42; 62) of a first semiconductor material having a first side (2'; 42'; 62') and a second side (2"; 42"; 62");

- a structural layer (12), of a second semiconductor material different from the first semiconductor material, formed on the first side (2'; 42'; 62') of the substrate (2; 42; 62) and including an active area (15; 53; 69) of said electronic device; and

- a transition layer (8; 48; 68), arranged between the substrate and the structural layer, the transition layer insulating electrically and/or thermally the substrate and the structural layer from one another,

- characterized in that it further comprises a via hole (20; 76), of a conductive type, extending through the structural layer (12) and the transition layer (8; 48; 68), and being configured so as to connect electrically and/or thermally the active area of the electronic device to the substrate (2; 42; 62).

- 2. The electronic device according to claim 1, wherein the via hole (20; 76) comprises a conductive portion (20a) extending between and in electrical contact with the active area (15; 53; 69) of the electronic device and the substrate (2; 42; 62).

- 3. The electronic device according to claim 2, wherein the via hole (20; 76) comprises an insulating portion (20b), which extends between an internal wall of the via hole (20; 76) and the conductive portion (20a) and is configured so as to insulate the conductive portion (20a) electrically from the structural layer (12).

4. The electronic device according to any one of the preceding  $% \left( 1\right) =\left( 1\right) \left( 1\right)$

10

15

claims, wherein the first semiconductor material is silicon and the second semiconductor material is a gallium compound, in particular chosen between gallium nitride and aluminum gallium nitride.

5

10

- 5. The electronic device according to any one of the preceding claims, further comprising a first conduction terminal (18; 54; 75), formed at the second side (2"; 42"; 62") of the substrate and in electrical contact with the substrate, said active area (12) being electrically connected to the first conduction terminal (18; 54; 75) by means of the via hole (20; 76) and the substrate (2; 42; 62).

- 6. The electronic device according to claim 5, wherein the structural layer (12) includes a second conduction terminal (44; 70) and a third conduction terminal (46; 72), said third conduction terminal (46; 72) being electrically connected to the active area (15; 53; 69) and to the via hole (20; 76) in such a way that, in use, an electric current flows between the second conduction terminal (44; 70) and the first conduction terminal (54; 75) through said active area (15; 53; 69), said third conduction terminal (46; 72), said via hole (20; 76), and said substrate (2; 42; 62).

- 7. The electronic device according to claim 6, wherein the second conduction terminal (44) is an anode terminal and the third conduction terminal (44) is a cathode terminal, said electronic device being configured for operating as a Schottky diode (40).

30

35

8. The electronic device according to claim 6, wherein the second conduction terminal (70) is a source terminal and the third conduction terminal (72) is a drain terminal, said electronic device further comprising a control terminal and being configured for operating as a transistor (60; 80).

- 9. A method for manufacturing an electronic device (1; 40; 60; 80) comprising the steps of:

- providing a substrate (2; 42; 62) of a first semiconductor material having a first side (2'; 42'; 62') and a second side (2"; 42"; 62");

5

35

- forming a structural layer (12) of a second semiconductor material different from the first semiconductor material, comprising an active area (15; 53; 69), on the first side (2'; 42'; 62') of the substrate (2; 42; 62); and

- forming a transition layer (8; 48; 68), between the substrate and the structural layer, the transition layer insulating electrically and/or thermally the substrate and the structural layer from one another,

- characterized by further comprising the step of forming a via 15 hole (20; 76), of a conductive type, through the structural layer (12) and the transition layer (8; 48; 68) so as to connect electrically and/or thermally the active area of the electronic device with the substrate (2; 42; 62).

- 20 10. The method according to claim 9, wherein the step of forming the via hole (20; 76) comprises:

- removing selective portions of the structural layer (12) and of the transition layer  $(8;\ 48;\ 68)$ ; and

- forming inside the via hole a conductive portion (20a) extending between and in electrical contact with the active area (15; 53; 69) of the electronic device and the substrate (2; 42; 62).

- 11. The method according to claim 10, wherein the step of forming the via hole (20; 76) further comprises forming an insulating portion (20b) between the internal wall of the via hole (20; 76) and the conductive portion (20a) so as to insulate electrically the conductive portion (20a) from the structural layer (12).

12. The method according to any one of claims 9-11, wherein

the first semiconductor material is silicon and wherein the step of forming the structural layer (12) comprises forming one or more layer made of one or more gallium compounds, in particular chosen between gallium nitride and aluminum gallium nitride.

- 13. The method according to any one of claims 9-12, further comprising the steps of:

- forming a first conduction terminal (18; 54; 75) in an area corresponding to the second side (2"; 42"; 62") of the substrate and in electrical contact with the substrate; and

- connecting the active area (15; 53; 69) electrically to the first conduction terminal (18; 54; 75) by means of the via hole (20; 76) and the substrate (2; 42; 62).

- 14. The method according to claim 13, further comprising the steps of:

- forming a second conduction terminal (44; 70) and a third conduction terminal (46; 72) in the active area (15; 53; 69);

- electrically connecting said third conduction terminal (46; 72) to the active area (15; 53; 69) and to the via hole (20; 76);

- operating, during use, the electronic device (1; 40; 60; 80) in such a way that an electric current flows between the second conduction terminal (44; 70) and the first conduction terminal (54; 75) through said active area (15; 53; 69), said third conduction terminal (46; 72), said via hole (20; 76), and said substrate (2; 42; 62).

p.i.: STMICROELECTRONICS S.R.L.

30

25

5

15

Elena CERBARO

(Iscrizione Albo nr. 426/BM)

Fig.4

p.i.: STMICROELECTRONICS S.R.L. Elena CERBARO (Iscrizione Albo nr. 426/BM)

Fig.5

Fig.6a

p.i.: STMICROELECTRONICS S.R.L. Elena CERBARO (Iscrizione Albo nr. 426/BM)