(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6231704号

(P6231704)

(45) 発行日 平成29年11月15日(2017.11.15)

(24) 登録日 平成29年10月27日(2017.10.27)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| G06F 13/10 | (2006.01) | G06F 13/10 | 340A |

| G06F 3/08  | (2006.01) | G06F 3/08  | 330C |

| G06F 3/06  | (2006.01) | G06F 3/06  | H    |

| G06F 12/00 | (2006.01) | G06F 12/00 | 301F |

G06F 12/00 597U

請求項の数 16 (全 20 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-570297 (P2016-570297)  |

| (86) (22) 出願日 | 平成27年6月3日(2015.6.3)           |

| (65) 公表番号     | 特表2017-518574 (P2017-518574A) |

| (43) 公表日      | 平成29年7月6日(2017.7.6)           |

| (86) 國際出願番号   | PCT/US2015/033970             |

| (87) 國際公開番号   | W02015/187824                 |

| (87) 國際公開日    | 平成27年12月10日(2015.12.10)       |

| 審査請求日         | 平成29年8月8日(2017.8.8)           |

| (31) 優先権主張番号  | 62/007,123                    |

| (32) 優先日      | 平成26年6月3日(2014.6.3)           |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 14/728,400                    |

| (32) 優先日      | 平成27年6月2日(2015.6.2)           |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                |

| (72) 発明者  | アサフ・シャチャム<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドラ<br>イブ・5775                    |

早期審査対象出願

最終頁に続く

(54) 【発明の名称】 フラッシュメモリベースのストレージデバイスの入力／出力仮想化 (IOV) ホストコントローラ (HC) (IOV-HC) におけるコマンドトラッピング

## (57) 【特許請求の範囲】

## 【請求項 1】

入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)であって、

対応する複数のクライアントレジスタインターフェース(CRI)を介して複数の入力/出力

(I/O)クライアントに、およびフラッシュメモリベースのストレージデバイスに通信可能

に結合された入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)であって、

前記IOV-HCが要求トラップを備え、

前記IOV-HCが、

前記IOV-HCの要求フィルタ回路によって、前記複数のCRIのうちの1つのCRIから前記

フラッシュメモリベースのストレージデバイスを対象とする要求を受信することと、

10

前記要求フィルタ回路によって、前記要求の内容を検査することと、

前記要求フィルタ回路によって、前記内容に基づいて、前記要求が処理のために前記

フラッシュメモリベースのストレージデバイスに転送されるべきか、またはトラップされ

るべきかどうかを決定することであって、前記要求フィルタ回路が、前記要求が読出しコ

マンド、書込みコマンド、または電力モード変更コマンドのうちの1つであることを前記

内容が示しているかどうかを決定するように構成される、決定することと、

処理のために、前記要求が前記フラッシュメモリベースのストレージデバイスに転送

されるべきであるという決定に応答して、前記要求を前記フラッシュメモリベースのスト

レージデバイスに転送することと、

前記要求がトラップされるべきであるという決定に応答して、前記要求を前記要求ト

20

ラップ内にトラップすることと

前記要求フィルタ回路による、前記要求が前記読出しコマンドまたは前記書込みコマンドのうちの1つであることを前記内容が示すという決定に応答して、前記IOV-HCのアクセス制御回路によって、前記要求が有効であるかどうかを決定することと、

前記要求が有効であるという決定に応答して、前記要求を前記フラッシュメモリベースのストレージデバイスに転送することと、

前記要求が有効ではないという決定に応答して、前記要求を前記要求トラップ内にトラップすることと

を行うように構成される、IOV-HC。

#### 【請求項 2】

10

前記要求トラップが、

コマンドミラー制御レジスタ(CMCR)と、

複数のコマンドミラー(CM)とを備え、前記複数のコマンドミラー(CM)の各々が、

複数のコマンドミラーステータスレジスタ(CMSR)であって、各々が前記複数のCRIのうちの1つのCRIに対応するコマンドミラーステータスレジスタ(CMSR)と、

複数のコマンドミラーデータレジスタアレイ(CMDAT)であって、各々が前記複数のCRIのうちの1つのCRIに対応するコマンドミラーデータレジスタアレイとを備え、

前記IOV-HCが、

要求のステータスを前記複数のCMSRのうちの前記CRIに対応するCMSRに記憶することと、

20

前記要求のプロトコル情報ユニット(PIU)を前記複数のCMDATのうちの前記CRIに対応するCMDATに記憶することと、

前記要求がトラップされることを示す仮想マシンマネージャ(VMM)への割込みを生成することと、

前記CMCRを介して前記VMMから処理命令を受信することと

を行うように構成されることによって、前記要求を前記要求トラップ内にトラップするように構成される、請求項1に記載のIOV-HC。

#### 【請求項 3】

30

応答生成器制御レジスタ(RGCR)と、

応答生成器プロトコル情報ユニット(RGPIU)とを備える応答生成回路をさらに備え、

前記IOV-HCが、前記要求を前記要求トラップ内にトラップすることに応答して、

前記応答生成回路によって、前記要求をトラップすることへの応答を受信することと、

前記応答のPIUを前記RGPIUに記憶することと、

前記RGCRを介してVMMから応答生成命令を受信することと

を行うようにさらに構成される、請求項1に記載のIOV-HC。

#### 【請求項 4】

前記要求フィルタ回路による、前記要求が前記電力モード変更コマンドであることを前記内容が示すという決定に応答して、

40

前記要求を、処理のために前記IOV-HCのマルチホスト電力コントローラ(MHPC)に転送することと、

前記MHPCによって前記要求が正常に処理されたかどうかを決定することとを行うようにさらに構成され、

前記IOV-HCが、前記MHPCによって前記要求が正常に処理されなかったという決定に応答して、前記要求を前記要求トラップ内にトラップするように構成される、請求項1に記載のIOV-HC。

#### 【請求項 5】

前記要求フィルタ回路による、前記要求が前記読出しコマンド、前記書込みコマンド、または前記電力モード変更コマンドのうちの1つではないことを前記内容が示すという決

50

定に応答して、前記要求を前記要求トラップ内にトラップするようにさらに構成される、請求項1に記載のIOV-HC。

**【請求項6】**

組込みマルチメディアカード(eMMC)規格に従って、前記フラッシュメモリベースのストレージデバイスに通信可能に結合される、請求項1に記載のIOV-HC。

**【請求項7】**

ユニバーサルフラッシュストレージ(UFS)規格に従って、前記フラッシュメモリベースのストレージデバイスに通信可能に結合される、請求項1に記載のIOV-HC。

**【請求項8】**

集積回路(IC)に統合される、請求項1に記載のIOV-HC。

10

**【請求項9】**

セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイル電話、セルラー電話、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、およびポータブルデジタルビデオプレーヤで構成されるグループから選択されるデバイスに統合される、請求項1に記載のIOV-HC。

**【請求項10】**

20

複数のホストのためのフラッシュメモリベースのストレージデバイスにコマンドトラッピングを提供するための方法であって、

入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)の要求フィルタ回路によって、複数のクライアントレジスタインターフェース(CRI)のうちの1つのCRIから前記フラッシュメモリベースのストレージデバイスを対象とする要求を受信するステップと、

前記要求フィルタ回路によって、前記要求の内容を検査するステップと、

前記要求フィルタ回路によって、前記要求が読み出しコマンド、書き込みコマンド、および電力モード変更コマンドのうちの1つであることを前記内容が示すかどうかを決定することによって、前記内容に基づいて、前記要求が処理のために前記フラッシュメモリベースのストレージデバイスに転送されるべきか、または要求トラップ内にトラップされるべきかどうかを決定するステップと、

30

処理のために、前記要求が前記フラッシュメモリベースのストレージデバイスに転送されるべきであるという決定に応答して、前記要求を前記フラッシュメモリベースのストレージデバイスに転送するステップと、

前記要求がトラップされるべきであるという決定に応答して、前記要求を前記要求トラップ内にトラップするステップと

前記要求が前記読み出しコマンドまたは前記書き込みコマンドのうちの1つであることを前記内容が示すという決定に応答して、前記IOV-HCのアクセス制御回路によって、前記要求が有効であるかどうかを決定するステップと

を備え、

40

前記要求を前記フラッシュメモリベースのストレージデバイスに転送するステップが、前記要求が有効であるという決定に応答し、

前記要求を前記要求トラップ内にトラップするステップが、前記要求が有効ではないという決定に応答する、方法。

**【請求項11】**

前記要求をトラップするステップが、

前記要求のステータスを、前記要求トラップの複数のコマンドミラーステータスレジスター(CMSR)のうちの前記CRIに対応するCMSRに記憶するステップと、

前記要求のプロトコル情報ユニット(PIU)を、前記要求トラップの複数のコマンドミラーデータレジスタアレイ(CMDAT)のうちの前記CRIに対応するCMDATに記憶するステップと

50

前記要求がトラップされることを示す仮想マシンマネージャ(VMM)への割込みを生成するステップと、

前記要求トラップのコマンドミラー制御レジスタ(CMCR)を介して前記VMMから処理命令を受信するステップと

を備える、請求項10に記載の方法。

**【請求項12】**

前記要求を前記要求トラップ内にトラップすることに応答して、

応答生成回路によって、前記要求をトラップすることへの応答を受信するステップと、

前記応答を前記応答生成回路の応答生成器プロトコル情報ユニット(RGPIU)に記憶する

10

ステップと、

前記応答生成回路の応答生成器制御レジスタ(RGCR)を介してVMMから応答生成命令を受

信するステップと

をさらに備える、請求項10に記載の方法。

**【請求項13】**

前記要求フィルタ回路による、前記要求が前記電力モード変更コマンドであることを前

記内容が示すという決定に応答して、

前記要求を、処理のために前記IOV-HCのマルチホスト電力コントローラ(MHPC)に転送す

るステップと、

前記MHPCによって前記要求が正常に処理されたかどうかを決定するステップと

20

をさらに備え、

前記要求を前記要求トラップ内にトラップするステップが、前記MHPCによって前記要求

が正常に処理されなかったという決定に応答する、請求項10に記載の方法。

**【請求項14】**

前記要求を前記要求トラップ内にトラップするステップが、前記要求フィルタ回路によ

る、前記要求が前記読み出しコマンド、前記書き込みコマンド、または前記電力モード変更コ

マンドのうちの1つではないことを前記内容が示すという決定に応答する、請求項10に記

載の方法。

**【請求項15】**

前記フラッシュメモリベースのストレージデバイスが、組込みマルチメディアカード(e

MMC)デバイスを備える、請求項10に記載の方法。

**【請求項16】**

前記フラッシュメモリベースのストレージデバイスが、ユニバーサルフラッシュストレ

ージ(UFS)デバイスを備える、請求項10に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

**優先権主張**

本出願は、2014年6月3日に出願された、「COMMAND TRAPPING IN A MULTI-CLIENT UNIVE

RSAL FLASH STORAGE (UFS) HOST CONTROLLER」と題する米国仮特許出願第62/007,123号の

優先権を主張し、その内容は、参照によりその全体が本明細書に組み込まれる。

**【0002】**

本出願はまた、2015年6月2日に出願された、「COMMAND TRAPPING IN AN INPUT/OUTPUT

VIRTUALIZATION (IOV) HOST CONTROLLER (HC)(IOV-HC) OF A FLASH-MEMORY-BASED STORAG

E DEVICE」と題する米国特許出願第14/728,400号の優先権を主張し、その内容は、参照に

よりその全体が本明細書に組み込まれる。

**【0003】**

本開示の技術は、一般に、モバイルコンピューティングデバイスにおけるフラッシュメ

モリベースのストレージに関する。

**【背景技術】**

10

20

30

40

50

**【0004】**

フラッシュメモリは、データが電子的に書き込まれ、消去され得る不揮発性データ記憶媒体である。フラッシュメモリは、現在、メモリカード、ソリッドステートドライブ、およびユニバーサルシリアルバス(USB)フラッシュドライブを含む、様々なフラッシュメモリベースのストレージデバイスで使用されている。フラッシュメモリベースのストレージデバイスは、従来のハードディスクよりも高い耐久性と耐衝撃性を提供しながら、ダイナミックランダムアクセスメモリ(RAM)と比較して迅速な読み出しおよび書き込み時間を提供し得る。

**【0005】**

10

フラッシュメモリベースのストレージデバイスの普及を促進するために、多くの規格が開発されているか、現在開発中である。そのような1つの規格は、スマートフォンおよびタブレットコンピュータなどのモバイルコンピューティングデバイスにおけるフラッシュメモリベースのストレージのための、電子素子技術連合評議会(JEDEC)によって開発されたユニバーサルフラッシュストレージ(UFS)である。UFSは、小型コンピュータシステムインターフェース(SCSI)アーキテクチャモデルと、コマンドキューリング機能を備えた複数のコマンドをサポートするコマンドプロトコルとを採用しており、それによってマルチスレッドプログラミングパラダイムを可能にする。JEDECによって開発された別の規格は、単純化されたアプリケーションインターフェース設計、小さいパッケージサイズ、および低消費電力を提供する、組込みマルチメディアカード(eMMC)規格である。eMMCフラッシュメモリベースのストレージデバイスは、現在、モバイルデバイスにおけるストレージの主要な形態のうちの1つである。

**【0006】**

UFSおよびeMMCなどの従来のフラッシュメモリベースのストレージデバイス規格は、現在、単一の入力/出力(I/O)クライアントによる管理および使用のために設計されている。しかしながら、多くの現代のコンピューティングデバイスは、仮想化環境を使用して、複数のI/Oクライアント(たとえば、ホストまたは他のプロセッササブシステム)を同時にサポートすることが可能である。そのような仮想化環境では、複数のI/Oのクライアントは、各々がフラッシュメモリベースのストレージデバイスの唯一のホストであるかのように、単一のフラッシュメモリベースのストレージデバイスと相互作用する必要がある場合がある。同様に、フラッシュメモリベースのストレージデバイスは、実際は複数のI/Oのクライアントと通信しているときに、単一のI/Oクライアントだけと通信しているかのように動作する必要がある。

**【0007】**

具体的には、フラッシュメモリベースのストレージ規格がマルチホスト環境に拡張される場合、複数のI/Oクライアントからの要求および/またはコマンドは、追加の処理および/またはフィルタリングを必要とする場合がある。たとえば、要求は、要求がフラッシュメモリベースのストレージデバイスに送信され得るかどうか、あるいは要求が変更または破棄されるべきかどうかを決定するために、処理される必要がある場合がある。

**【発明の概要】****【課題を解決するための手段】****【0008】**

詳細な説明において開示される態様は、フラッシュメモリベースのストレージデバイスの入力/出力仮想化(IoV)ホストコントローラ(HC)(IoV-HC)におけるコマンドトラッピングを含む。一態様では、IoV-HCは、複数の入力/出力(I/O)クライアントのうちの1つに対応するクライアントレジスタインターフェース(CRI)から、要求(たとえば、非限定的な例として、転送要求(TR)またはタスク管理要求(TMR))を受信するように構成されている。IoV-HCは、要求がトランスポートプロトコルエンジンに渡される前に、要求の内容を検査する。要求の内容に基づいて、IoV-HCは、要求がさらに処理されるべきかどうか(たとえば、非限定的な例として、アクセス制御回路によって、またはマルチホスト電力コントローラ(MHPC)によって)、または要求がトラップされるべきかどうかを決定し得る。IoV-HCが、

10

20

30

40

50

要求はトラップされるべきであると決定した場合、IOV-HCは、要求トラップを使用して要求をトラップして、いくつかの態様では、要求がトラップされたことを仮想マシンマネージャ(VMM)に通知するために、VMMへの割込みを生成し得る。IOV-HCのいくつかの態様はまた、VMMが、トラップされた要求が発信されたCRIへの応答を生成するようにIOV-HCに指示することを可能にする応答生成回路を提供し得る。このようにして、IOV-HCは、フラッシュメモリベースのストレージデバイスの機能を複数のI/Oクライアントに拡張し得る。

#### 【0009】

別の態様では、IOV-HCが提供される。IOV-HCは、対応する複数のCRIを介して複数のI/Oクライアントに、およびフラッシュメモリベースのストレージデバイスに、通信可能に結合される。IOV-HCは、要求トラップを備える。IOV-HCは、IOV-HCの要求フィルタ回路によって、複数のCRIのうちの1つのCRIからフラッシュメモリベースのストレージデバイスを対象とする要求を受信するように構成されている。IOV-HCは、要求フィルタ回路によって、要求の内容を検査するようにさらに構成されている。IOV-HCはまた、要求フィルタ回路によって、内容に基づいて、要求が処理のためにフラッシュメモリベースのストレージデバイスに転送されるべきか、またはトラップされるべきかどうかを決定するように構成されている。IOV-HCは、要求が処理のためにフラッシュメモリベースのストレージデバイスに転送されるべきであるという決定に応答して、要求をフラッシュメモリベースのストレージデバイスに転送するようにさらに構成されている。IOV-HCは、要求がトラップされるべきであるという決定に応答して、要求を要求トラップ内にトラップするようにさらに構成されている。10

#### 【0010】

別の態様では、複数のホストのためのフラッシュメモリベースのストレージデバイスにコマンドトラッピングを提供するための方法が提供される。本方法は、IOV-HCの要求フィルタ回路によって、複数のCRIのうちの1つのCRIから、フラッシュメモリベースのストレージデバイスを対象とする要求を受信するステップを備える。本方法は、要求フィルタ回路によって、要求の内容を検査するステップをさらに備える。本方法はまた、要求フィルタ回路によって、内容に基づいて、要求が処理のためにフラッシュメモリベースのストレージデバイスに転送されるべきか、または要求トラップ内にトラップされるべきかどうかを決定するステップを備える。本方法は、要求が処理のためにフラッシュメモリベースのストレージデバイスに転送されるべきであるという決定に応答して、要求をフラッシュメモリベースのストレージデバイスに転送するステップをさらに備える。本方法は、要求がトラップされるべきであるという決定に応答して、要求を要求トラップ内にトラップするステップをさらに備える。20

#### 【0011】

別の態様では、IOV-HCが提供される。IOV-HCは、複数のCRIのうちの1つのCRIから、フラッシュメモリベースのストレージデバイスを対象とする要求を受信するための手段を備える。IOV-HCは、要求の内容を検査するための手段をさらに備える。IOV-HCはまた、内容に基づいて、要求が処理のためにフラッシュメモリベースのストレージデバイスに転送されるべきか、または、トラップされるべきかどうかを決定するための手段を備える。IOV-HCは、要求が処理のためにフラッシュメモリベースのストレージデバイスに転送されるべきであるという決定に応答して、要求をフラッシュメモリベースのストレージデバイスに転送するための手段をさらに備える。IOV-HCは、要求がトラップされるべきであるという決定に応答して、要求を要求トラップ内にトラップするための手段をさらに備える。30

#### 【図面の簡単な説明】

#### 【0012】

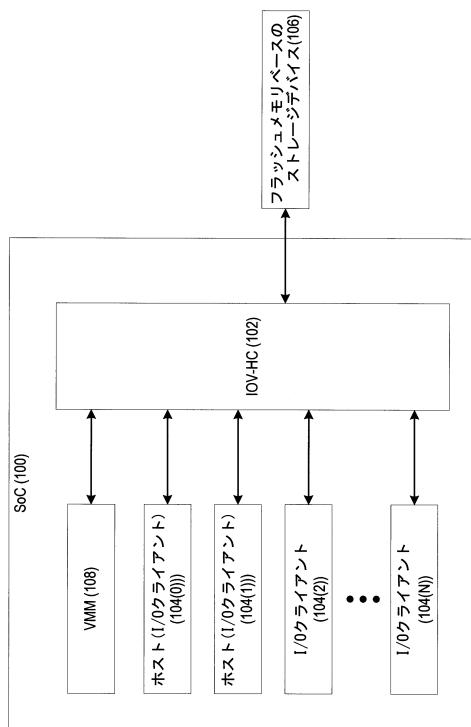

【図1】例示的な入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)を介して例示的なフラッシュメモリベースのストレージデバイスに通信可能に結合された複数の入力/出力(I/O)クライアントを含む、例示的なシステムオンチップ(SoC)のブロック図である。

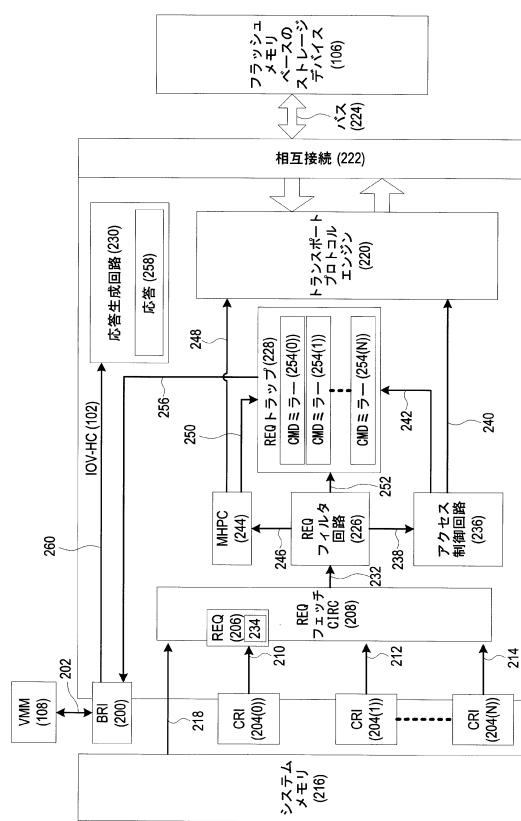

【図2】複数のI/Oクライアントにコマンドトラッピングを提供するための、図1のIOV-HC内の例示的な要素および通信フローのブロック図である。40

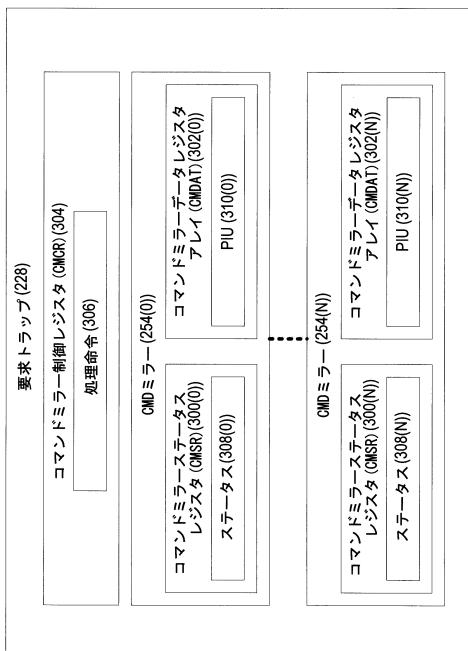

【図3】トラップされた要求を記憶するための、図1のIOV-HCの例示的な要求トラップの要素を示すブロック図である。

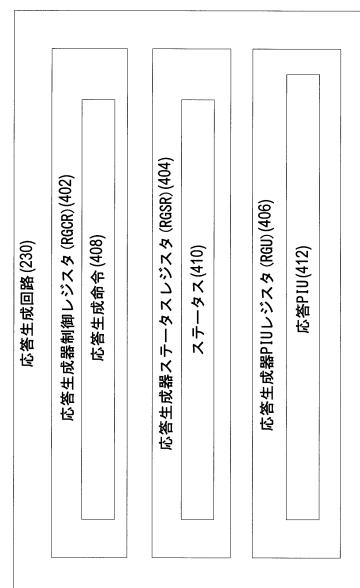

【図4】複数のI/Oクライアントに送信されるべき応答を生成するための、図1のIOV-HCの例示的な応答生成回路の要素を示すブロック図である。

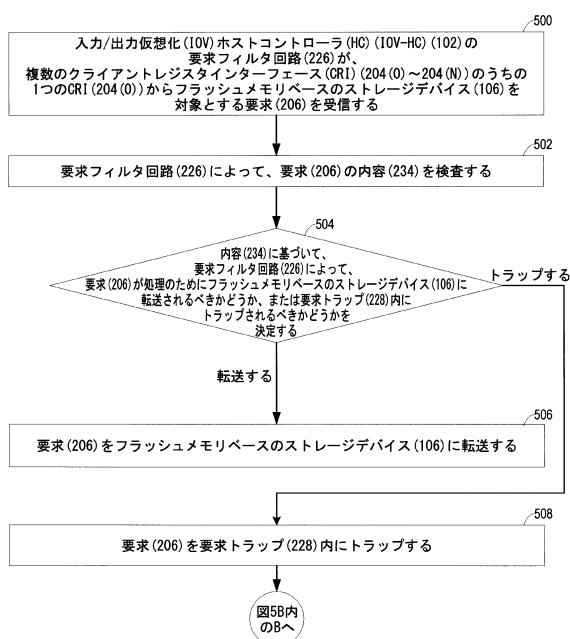

【図5 A】複数のI/Oクライアントにコマンドトラッピングを提供するための、図1のIOV-HCの例示的な動作を示すフローチャートである。

【図5 B】複数のI/Oクライアントにコマンドトラッピングを提供するための、図1のIOV-HCの例示的な動作を示すフローチャートである。

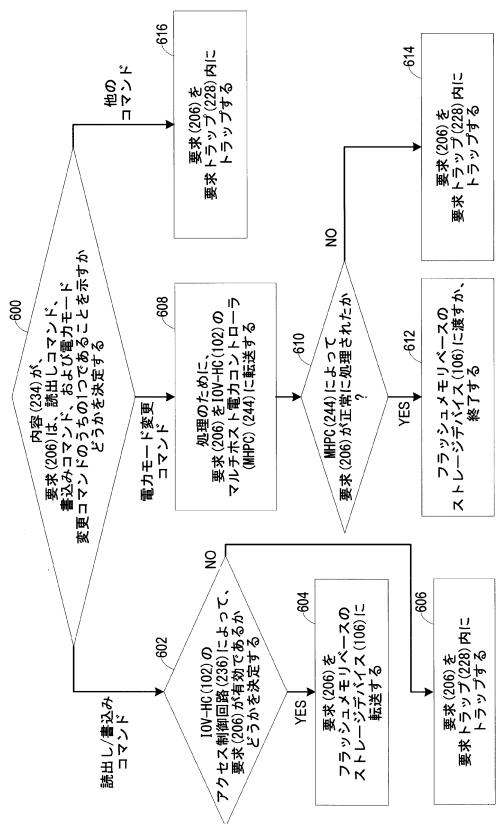

【図6】受信された要求が処理および/またはトラップされ得る方法を決定するための、図1のIOV-HCの例示的な動作を示すフローチャートである。

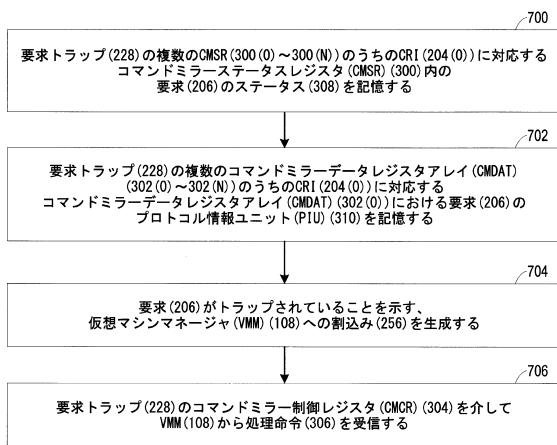

【図7】図2および図3の要求トラップを使用するコマンドトラッピングのための、図1のIOV-HCの例示的な動作を示すフローチャートである。

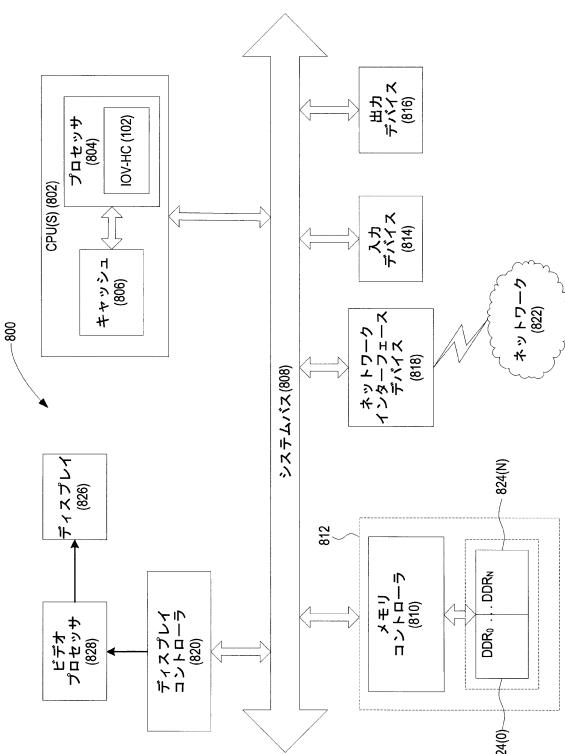

【図8】図1のIOV-HCを採用するSoCを含み得る例示的なコンピューティングデバイスのブロック図である。

#### 【発明を実施するための形態】

##### 【0013】

次に図面を参照すると、本開示のいくつかの例示的な態様が説明されている。「例示的」という語は、本明細書では「一例、事例、または例示としての役割を果たすこと」を意味するために使用される。「例示的」として本明細書において説明されるいずれの態様も、必ずしも他の態様よりも好ましいか、または有利であると解釈されるとは限らない。

##### 【0014】

詳細な説明において開示される態様は、フラッシュメモリベースのストレージデバイスの入力/出力仮想化(IOV)ホストコントローラ(HC)(IOV-HC)におけるコマンドトラッピングを含む。一態様では、IOV-HCは、複数の入力/出力(I/O)クライアントのうちの1つに対応するクライアントレジスタインターフェース(CRI)から、要求(たとえば、非限定的な例として、転送要求(TR)またはタスク管理要求(TMR))を受信するように構成されている。IOV-HCは、要求がトランスポートプロトコルエンジンに渡される前に、要求の内容を検査する。要求の内容に基づいて、IOV-HCは、要求がさらに処理されるべきかどうか(たとえば、非限定的な例としてアクセス制御回路によって、またはマルチホスト電力コントローラ(MHPC)によって)、または、要求がトラップされるべきかどうかを決定し得る。IOV-HCが、要求がトラップされるべきであると決定した場合、IOV-HCは、要求トラップを使用して要求をトラップして、いくつかの態様では、要求がトラップされたことをVMMに通知するために、仮想マシンマネージャ(VMM)への割込みを生成し得る。IOV-HCのいくつかの態様はまた、VMMが、トラップされた要求が発信されたCRIへの応答を生成するようにIOV-HCに指示することを可能にする応答生成回路を提供し得る。このようにして、IOV-HCは、フラッシュメモリベースのストレージデバイスの機能を複数のI/Oクライアントに拡張することができる。

##### 【0015】

この点で、図1は、IOV-HC102を含む例示的なシステムオンチップ(SoC)100のブロック図である。図1の例では、IOV-HC102は、複数のI/Oクライアント104(0)～104(N)が単一のフラッシュメモリベースのストレージデバイス106にアクセスすることを可能にするために提供される。いくつかの態様では、フラッシュメモリベースのストレージデバイス106は、非限定的な例として、ユニバーサルフラッシュストレージ(UFS)デバイス、または組込みマルチメディアカード(eMMC)デバイスを備え得る。特に、この態様では、フラッシュメモリベースのストレージデバイス106はモバイルデバイス内のSoC100に隣接して組み込まれているが、他の態様は、フラッシュメモリベースのストレージデバイス106をリムーバブルメモリデバイスとして採用した場合、同様の機能を達成し得る。

##### 【0016】

SoC100はまた、I/Oクライアント104(0)～104(N)に仮想化機能と管理とを提供する仮想マシンマネージャ(VMM)108を含む。VMM108は、SoC100のプロセッサによって実行されるソ

10

20

30

40

50

ソフトウェアモジュールでもよく、必要または所望に応じてSoC100のシステムメモリ(図示せず)または他のメモリ位置に存在する。I/Oクライアント104(0)～104(N)の各々は、SoC100のプロセッサ上、および/またはSoC100内のプロセッササブシステム(図示せず)上で実行される、ホストソフトウェアエンティティ(図1のI/Oクライアント104(0)およびI/Oクライアント104(1)など)を備え得る。IOV-HC102は、I/Oクライアント104(0)～104(N)とフラッシュメモリベースのストレージデバイス106との間の仲介として作用し得る。このように、IOV-HC102は、フラッシュメモリベースのストレージデバイス106と通信しているのはI/Oクライアント104(0)～104(N)だけであるかのように、I/Oクライアント104(0)～104(N)が各々フラッシュメモリベースのストレージデバイス106と相互作用するように、I/Oクライアント104(0)～104(N)とフラッシュメモリベースのストレージデバイス106との間の相互作用を制御し得る。同様に、IOV-HC102は、実際は複数のI/Oクライアント104(0)～104(N)と通信しているときに、フラッシュメモリベースのストレージデバイス106が、単一のI/Oクライアント104(0)～104(N)だけと通信しているかのように動作することを可能にするように構成され得る。

#### 【0017】

いくつかの態様による図1のIOV-HC102内の例示的な構成要素と通信フローとをより良く説明するために、図2が提供される。IOV-HC102は、使用されているフラッシュメモリベースのストレージデバイス106規格(たとえば、非限定的な例として、UFSまたはeMMC)のニーズに応じて、図2に示されるよりも多数または少数の要素を含み得ることを理解されたい。図2に見られるように、IOV-HC102は、それを通じて矢印202によって示されるように図1のVMM108がIOV-HC102と通信することができる、ベースレジスタインターフェース(BRI)200を含む。IOV-HC102はまた、クライアントレジスタインターフェース(CRI)204(0)～204(N)を含む。CRI204(0)～204(N)の各々は、CRI204(0)によってIOV-HC102に送信される要求206などの要求を送信するために、図1のI/Oクライアント104(0)～104(N)のうちの1つに対応するためのインターフェースを表す。非限定的な例として、要求206は、転送要求(TR)および/またはタスク管理要求(TMR)を備え得る。本明細書に開示されるいくつかの態様によれば、要求206は、読み出し要求、書き込み要求、電力制御要求(たとえば、小型コンピュータシステムインターフェース(SCSI)START\_STOP\_UNIT(SSU)要求、またはeMMCスリープ要求)、および/または他の要求を備え得る。CRI204(0)～204(N)はまた、クエリ要求またはノーラペレーション(NOP)命令など、他のタイプの要求またはコマンド206を送信するために使用され得る。

#### 【0018】

図2に見られるように、CRI204(0)～204(N)は、矢印210、212、および214によってそれぞれ示されるように、IOV-HC102の要求フェッチ回路(REQ\_FETCH CIRC)208に通信可能に結合されている。いくつかの態様では、要求フェッチ回路208は、UFSトランSPORTプロトコル(UTP)転送要求記述子(UTRD)(図示せず)、またはeMMCタスク記述子(TD)などのトランSPORTプロトコル記述子をシステムメモリ216からフェッチし、UTPコマンド記述子(UCD)(図示せず)などのコマンド記述子の位置を決定するためにトランSPORTプロトコル記述子を復号する責任を負うことができる。次いで、要求フェッチ回路208は、矢印218によって示されるように、コマンド記述子のTRセクション(図示せず)をシステムメモリ216からフェッチし得る。

#### 【0019】

従来のUFSまたはeMMCホストコントローラでは、要求フェッチ回路208は、次にフェッチされた要求206からパラメータを抽出し、フェッチされた要求206全体を処理のためにトランSPORTプロトコルエンジン220(たとえば、非限定的な例として、UTPエンジンまたはeMMCトランSPORTプロトコルエンジン)に転送することになる。次いで、フェッチされた要求206は、相互接続222およびバス224を介して、フラッシュメモリベースのストレージデバイス106に送信され得る。しかしながら、マルチクライアント環境では、要求206の追加の検査および処理が必要とされる場合がある。たとえば、異なるタイプの要求206のためのカスタム処理を提供する、あるいはフェッチされた要求206をトラップおよび/または

終了することが望ましい場合がある。

#### 【0020】

したがって、IOV-HC102は、コマンドトラッピング機能を提供するように構成されている。したがって、IOV-HC102は、要求206を受信、検査、および処理するための要求フィルタ回路(REQ FILTER CIRCUIT)226と、コマンドトラッピングのための要求トラップ228と、I/Oクライアント104(0)～104(N)への応答の送信を容易にするための応答生成回路230とを含み得る。要求フィルタ回路226、要求トラップ228、および応答生成回路230の動作は、以下でより詳細に説明される。

#### 【0021】

図2の参照を続けると、要求フェッチ回路208によってフェッチされたすべての要求206は、矢印232によって示されるように、IOV-HC102の要求フィルタ回路226によって受信される。要求フィルタ回路226は、要求206を検査および処理する責任を負う。具体的には、要求フィルタ回路226は、要求206の内容234に基づいて要求206が処理されるべき方法を決定する。非限定的な例として、UFS規格に基づくいくつかの態様では、要求フィルタ回路226は、要求206が処理されるべき方法を決定するために、要求206の内容234のトランザクションコード(TC)およびSCSIオペレーションコード(OTP)を検査し得る。同様に、eMMC規格に基づく態様では、要求フィルタ回路226は、要求206が処理されるべき方法を決定するために、要求206の内容234のコマンドインデックスとコマンド引数とを検査し得る。要求206の内容234に基づいて、要求フィルタ回路226は、要求206が処理のためにフラッシュメモリベースのストレージデバイス106に転送されるべきであると決定してもよく、要求206はトラップされるべきであると決定してもよい。その後、VMM108は、トラップされた要求206が修正されてフラッシュメモリベースのストレージ装置106に再発行されるべきかどうか、またはトラップされた要求206が終了されるべきかどうかを決定し得る。

10

20

#### 【0022】

いくつかの態様では、要求フィルタ回路226は、要求206が、読み出しコマンド、書き込みコマンド、電力モード変更コマンド、または別のタイプのコマンドであるかどうかを決定するために、要求206の内容234を検査し得る。要求206の内容234が、要求206が読み出しされた書込みコマンドに対応することを示している場合、要求206は、矢印238によって示されるように、要求フィルタ回路226によってアクセス制御回路236に転送され得る。いくつかの態様によるアクセス制御回路236は、論理ユニット(図示せず)への読み出し/書き込みアクセスルールのハードウェア強制を提供する。その後、要求206がアクセス制御回路236によって検証される場合、矢印240によって示されるように、要求206はトランスポートプロトコルエンジン220に渡される。しかしながら、矢印242によって示されるように、アクセス制御回路236によって拒否された要求206は、ソフトウェア処理のためにトラップされる。要求206のトラッピングに関連付けられる動作は、以下でより詳細に説明される。

30

#### 【0023】

いくつかの態様によれば、要求206の内容234は、要求206が電力モード変更コマンドに対応することを示し得る。非限定的な例として、UFS規格に基づく態様では、内容234は、要求206がSCSI SSUコマンドであることを示し得、eMMC規格に基づく態様では、内容234は、要求206がeMMCスリープ(CMD5)コマンドであることを示し得る。その結果、フェッチされた要求206は、矢印246によって示されるように、要求フィルタ回路226によってMHPC244に送信され得る。いくつかの態様によるMHPC244は、フラッシュメモリベースのストレージデバイス106の電力モードを制御するために、図1のI/Oクライアント104(0)～104(N)間の投票メカニズムを実装するハードウェアステートマシン(図示せず)を備える。フェッチされた要求206がMHPC244によって正常に処理されている場合、フェッチされた要求206は、矢印248によって示されるように、トランスポートプロトコルエンジン220に渡され得る。正常に処理されていない場合、MHPC244は静かにフェッチされた要求206を終了してもよく、矢印250によって示されるように、さらなる処理のためにフェッチされた要求206をトラップしてもよい。フェッチされた要求206が、読み出しコマンド、書き込みコマンド、または電力モード変更コマンド以外のコマンドに対応する場合、矢印252によって示されるよ

40

50

うに、要求フィルタ回路226はフェッチされた要求206を傍受して要求トラップ228内にトラップし得る。

#### 【 0 0 2 4 】

要求トラップ228は、要求206などのトラップされた要求を記憶するためにIOV-HC102によって提供される。いくつかの態様によれば、要求トラップ228内にはコマンドミラー(CM)254(0)～254(N)があり、各々がCRI204(0)～204(N)のうちの1つに関連付けられている。

トラップされた要求206は、そこから要求206が受信される、対応するCRI204～204(N)のCM254(0)～254(N)に記憶され得る。いくつかの態様は、要求トラップ228が、要求206がトラップされることを示すために、BRI200を介してVMM108への割込み256を生成し得ることを提供し得る。次いで、VMM108は、情報を抽出するためにBRI200を介して適切なCM254(0)～254(N)の内容を読み出すことによって、トラップされた要求206をさらに処理し得る。VMM108はまた、BRI200を介して、矢印260によって示されるように、応答生成回路230を使用して、発信しているCRI204(0)～204(N)への応答258を生成するようにIOV-HC102に指示し得る。10

#### 【 0 0 2 5 】

いくつかの態様によれば、一旦要求206がトラップされると、要求フェッチ回路208はその処理を完了して、別のCRI204(0)～204(N)のための次の要求206をフェッチするステップに進むことができる。トラップされた要求206がVMM108によって処理されるまで、トラップされた要求206に関連付けられるCRI204(0)～204(N)のうちの特定のCRIが、要求フェッチアービトレーションから削除される。IOV-HC102に要求206を転送または廃棄するように指示することによってVMM108が要求206を処理するときのみ、CRI204(0)～204(N)のうちの同じCRIからの後続の要求206は要求フェッチ回路208によってフェッチされ得る。20

#### 【 0 0 2 6 】

トラップされた要求206を記憶するための、図2のIOV-HC102の要求トラップ228の例示的な構成要素を説明するために、図3が提供される。図3を説明する際に、明確化のために図1および図2の要素が参照される。図3に見られるように、要求トラップ228は、図2のCM254(0)～254(N)を含み、それらの各々が図2のCRI204(0)～204(N)のうちの1つに対応する。CM254(0)～254(N)の各々は、対応するコマンドミラーステータスレジスタ(CMSR)300(0)～300(N)と、コマンドミラーデータレジスタアレイ(CMDAT)302(0)～302(N)とを提供する。要求トラップ228は、コマンドミラーアクセスレジスタ(CMCR)304をさらに含む。要求トラップ228の各例示的な要素の機能は、以下でより詳細に説明される。30

#### 【 0 0 2 7 】

CMCR304は、要求トラップ228内にトラップされた要求206が処理されるべき方法についてIOV-HC102に指示するために、図2のVMM108によって使用され得るレジスタである。非限定的な例として、VMM108は、トラップされた要求206をトランスポートプロトコルエンジン220に渡すように、またはトラップされた要求206完全に終了するようにIOV-HC102に指示するために、CMCR304を介して処理命令306を送信し得る。いくつかの態様によれば、CMCR304はすべてのCM254(0)～254(N)の間で共有される。

#### 【 0 0 2 8 】

上述したように、要求206などのトラップされた要求は、そこから要求206が受信されるCRI204(0)～204(N)に対応するCM254(0)～254(N)に記憶され得る。トラップされた要求206の記憶を容易にするために、CM254(0)～254(N)のCMSR300(0)～300(N)の各々は、各トラップされた要求206に関する情報を表すそれぞれのステータス308(0)～308(N)を記憶し得る。各ステータス308(0)～308(N)は、いくつかの態様によれば、要求206に関連付けられるスロット番号(図示せず)および/または転送要求記述子(TRD)情報(図示せず)などのデータを備え得る。40

#### 【 0 0 2 9 】

CM254(0)～254(N)のCMDAT302(0)～302(N)はレジスタアレイであり、それらの各々は、各トラップされた要求206の対応するプロトコル情報ユニット(PIU)310(0)～310(N)を記憶するために使用され得る。いくつかの態様では、CMDAT302(0)～302(N)の各々は、図2のCR50

I204(0)～204(N)ごとに32バイトの空間を割り振ることができる。要求206が32バイトよりも大きい場合(たとえば、非限定的な例として、記述子書き込みクエリ要求)、要求206の長さは対応するCMSR300(0)～300(N)内に示され得る。次いで、VMM108は、システムメモリ216内のコマンド記述子アドレス(UFS規格に基づく様式における、UFSコマンド記述子(UCD)など)を計算し、システムメモリ216内の元の位置から直接要求206を読み出すことができる。

#### 【0030】

図2に関して上述したように、I0V-HC102のいくつかの様式は、VMM108がI0V-HC102に、そこからトラップされた要求(要求206など)が発生するI/Oクライアント104(0)～104(N)に送信されるべき応答258を生成するように指示することを可能にするために応答生成回路230を提供する。図2の応答生成回路230の一様式の例示的な要素を説明するために、図4が提供される。図4の説明において、明確化のために図1および図2の要素が参照される。

10

#### 【0031】

図4に見られるように、応答生成回路230は、応答生成器制御レジスタ(RGCR)402と、応答生成器ステータスレジスタ(RGSR)404と、応答生成器PIUレジスタ(RGU)406とを備える。RGCR402は、いくつかの様式では、I0V-HC102に応答生成命令408を使用して応答258を送信するように指示するために、図2のVMM108によって使用され得る。非限定的な例として、応答生成命令408は、送信コマンド、応答送信方法、宛先CRI識別子、および/または全体的なコマンドステータス(OCS)を含み得る。応答生成回路230のRGSR404は、応答生成回路230のステータスに関するステータス410を記憶し得る。RGU406は、いくつかの様式では、I/Oクライアント104(0)～104(N)のうちの1つに送信されるべき応答258の応答PIU412を記憶するための32バイトのレジスタ空間を備え得る。

20

#### 【0032】

応答生成回路230のいくつかの様式は、2つの応答送信方法のうちの1つまたは両方を提供し得る。いくつかの様式では、応答送信方法は、要求トラップ228によってRGU406に書き込まれている応答PIU412を備え得る。次いで、応答PIU412は、応答258が対象とされるI/Oクライアント104(0)～104(N)のうちの1つのメモリ空間(図示せず)内のTRDで指定された位置にI0V-HC102によってコピーされ得る。あるいは、いくつかの様式は、VMM108は、I/Oクライアント104(0)～104(N)のメモリ空間内の位置に直接応答PIU412を書き込むことができることを提供し得る。いずれかの送信技法の下で、VMM108は、I/Oクライアント104(0)～104(N)のメモリ空間内のTRDにOCSフィールドを書き込むようにI0V-HC102に指示するために、およびI/Oクライアント104(0)～104(N)によって要求されるように割込み256を生成するために、RGCR402を書き込むことができる。応答258が32バイト(たとえば、記述子読み出しクエリ要求用)より大きいいくつかの様式では、VMM108は、I/Oクライアント104(0)～104(N)のメモリ空間内の位置に直接応答PIU412を書き込むことができる。

30

#### 【0033】

UFS規格に基づく本明細書に開示されるいくつかの様式によれば、VMM108がRGCR402に書き込むとき、I0V-HC102は以下の例示的な動作を実行し得る。応答のコピーが必要な場合、I0V-HC102は、CRI識別子およびスロット番号から宛先アドレス(図示せず)を計算し得る。たとえば、UFS規格に基づく様式では、宛先アドレスは、UCDまたはUTPタスク管理要求記述子(UTMRD)の応答セクションに基づいて計算され得る。次いで、I0V-HC102は、RGU406から宛先アドレスに、応答PIU412の内容をコピーし得る。I0V-HC102は、UTP TRD (UTRD)またはUTMRD内の宛先アドレスにOCSを書き込む。I0V-HC102は、コマンド完了を示すために、適切なCRI204(0)～204(N)にUTP転送要求リストドアベルレジスタ(UTRLDBR)、UTP転送要求リストクリアレジスタ(UTRLCLR)、および/またはUTPタスク管理要求リストドアベルレジスタ(UTMRLDBR)を設定する。次いで、I0V-HC102は、UTRDまたはUTMRDによって要求された場合、割込み256を生成し得る。eMMC規格に基づく本明細書に開示される様式では、応答PIU412は、VMM108によって適切なCRI204(0)～204(N)の応答レジスタに書き込まれ、その後、VMM108はI0V-HC102に割込み256を生成するよう指示する。上述のUFSとeMMCとに基づく様式は、非限定的な例であることを理解されたい。

40

50

## 【0034】

複数のI/Oクライアント104(0)～104(N)にコマンドトラッピングを提供するために、図2のIOV-HC102の例示的な動作を説明するために、図5Aおよび図5Bが提供される。図5Aおよび図5Bを説明する際に、明確化のために図1、図2、および図4の要素が参照される。図5Aでは、動作は、IOV-HC102の要求フィルタ回路226が、複数のCRI204(0)～204(N)のうちのCRI204(0)からフラッシュメモリベースのストレージデバイス106を対象とする要求206を受信することで開始する(ブロック500)。この点で、要求フィルタ回路226は、本明細書では「CRIからフラッシュメモリベースのストレージデバイスを対象とする要求を受信するための手段」と呼ばれ得る。要求フィルタ回路226は、要求206の内容234を検査する(ブロック502)。非限定的な例として、UFS規格に基づくいくつかの態様では、要求フィルタ回路226は、要求206の内容234のトランザクションコード(TC)とSCSIオペレーションコード(OPC)を検査し得、eMMC規格に基づく態様では、要求フィルタ回路226は、要求206の内容234のコマンドインデックスとコマンド引数とを検査し得る。したがって、要求フィルタ回路226は、本明細書では「要求の内容を検査するための手段」と呼ばれ得る。

## 【0035】

内容234に基づいて、要求フィルタ回路226は、要求206が処理のためにフラッシュメモリベースのストレージデバイス106に転送されるべきかどうか、または要求206が要求トラップ228内にトラップされるべきかどうかを決定する(ブロック504)。したがって、要求フィルタ回路226は、本明細書では「要求が処理のためにフラッシュメモリベースのストレージデバイスに転送されるべきか、またはトラップされるべきかどうかを決定するための手段」と呼ばれ得る。決定ブロック504で、要求フィルタ回路226が要求206は転送されるべきであると決定した場合、要求フィルタ回路226は要求206をフラッシュメモリベースのストレージデバイス106に転送する(ブロック506)。この点で、要求フィルタ回路226は、本明細書では「要求をフラッシュメモリベースのストレージデバイスに転送するための手段」と呼ばれ得る。決定ブロック504で、要求フィルタ回路226が要求206はトラップされるべきであると決定した場合、要求フィルタ回路226は要求206を要求トラップ228内にトラップする(ブロック508)。したがって、要求フィルタ回路226は、本明細書では「要求を要求トラップ内にトラップするための手段」と呼ばれ得る。図6に関して以下でより詳細に記述されるように、いくつかの態様は、要求206を転送またはトラップする決定は、内容234で示されるように、要求206のタイプに基づき得ることを提供し得る。次いで、処理が図5Bのブロック510で再開する。

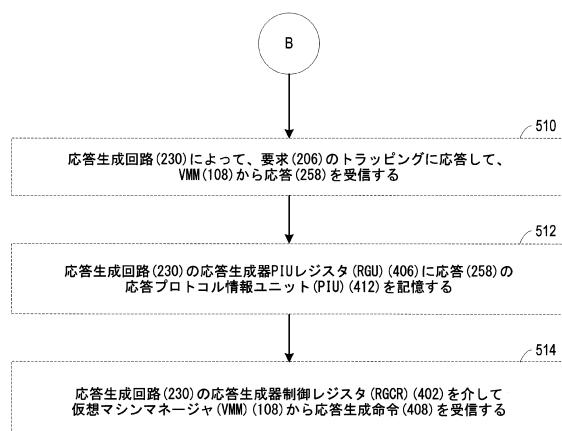

## 【0036】

次に図5Bを参照すると、いくつかの態様では、IOV-HC102の応答生成回路230は、要求206のトラッピングに応答して、VMM108から応答258を受信し得る(ブロック510)。この点で、応答生成回路230は、本明細書では「要求をトラップすることへの応答を受信するための手段」と呼ばれ得る。応答生成回路230は、応答生成回路230のRGU406に応答258の応答P|IU412を記憶し得る(ブロック512)。したがって、応答生成回路230は、本明細書では「RGPIUに応答を記憶するための手段」と呼ばれ得る。次いで、IOV-HC102は、応答生成回路230のRGCR402を介してVMM108から応答生成命令408を受信し得る(ブロック514)。したがって、IOV-HC102は、本明細書では「RGCRを介してVMMから応答生成命令を受信するための手段」と呼ばれ得る。いくつかの態様(たとえば、eMMC規格に基づく態様)では、RGCR402は採用されない場合があり、したがって、ブロック514の任意の動作が省略され得る。

## 【0037】

図6は、受信された要求が処理および/またはトラップされ得る方法を決定するため、図2のIOV-HC102の例示的な動作を示すフローチャートである。図6を説明する際に、明確化のために図1および図2の要素が参照される。いくつかの態様では、図6に示されるいくつかの動作は、要求206が処理のためにフラッシュメモリベースのストレージデバイス106に転送されるべきかどうか、または要求206が要求トラップ228内にトラップされるべきかどうかを決定するために、図5Aのブロック504の動作に対応し得る。

## 【0038】

10

20

30

40

50

図6の動作は、要求フィルタ回路226が、内容234が、要求206は、読み出しコマンド、書き込みコマンド、または電力モード変更コマンドのうちの1つであることを示すかどうかを決定することで開始する(ブロック600)。ブロック600で、要求206が、読み出しコマンドまたは書き込みコマンドと決定された場合、要求206はIOV-HC102のアクセス制御回路236に渡され得、要求206が有効であるかどうかを決定する(ブロック602)。この点で、アクセス制御回路236は、本明細書では「要求が有効であるかどうかを決定するための手段」と呼ばれ得る。ブロック602で、要求206が有効であると決定された場合、要求206がフラッシュメモリベースのストレージデバイス106に転送される(ブロック604)。ブロック602で、アクセス制御回路236によって要求206は有効ではないと決定された場合、要求206は要求トラップ228内にトラップされる(ブロック606)。

10

#### 【0039】

決定ブロック600で、要求フィルタ回路226が、要求206は電力モード変更コマンドであると決定されたと決定した場合、処理のために、要求206がIOV-HC102のMHPC244に転送される(ブロック608)。したがって、要求フィルタ回路226は、本明細書では「処理のために要求をIOV-HCのMHPCに転送するための手段」と呼ばれ得る。次いで、MHPC244によって要求206が正常に処理されたかどうかに関して決定が行われる(ブロック610)。したがって、MHPC244は、本明細書では「MHPCによって要求が正常に処理されたかどうかを決定するための手段」と呼ばれ得る。MHPC244が要求206を正常に処理した場合、MHPC244は、要求206をフラッシュメモリベースのストレージデバイス106に渡すか、MHPC244の内部ロジックに基づいて要求206を終了する(ブロック612)。MHPC244によって要求206が正常に処理されていない場合、要求206は要求トラップ228内にトラップされる(ブロック614)。決定ブロック600に戻って、要求206が、読み出しコマンド、書き込みコマンド、または電力モード変更コマンドではないと決定された場合、要求206は要求トラップ228内にトラップされる(ブロック616)。したがって、要求フィルタ回路226は、「内容が、要求は読み出しコマンド、書き込みコマンド、または電力モード変更コマンドのうちの1つではないという決定に応答して、要求を要求トラップ内にトラップするための手段」と呼ばれ得る。

20

#### 【0040】

図2の要求トラップ228を使用するコマンドトラッピングのためのいくつかの態様におけるIOV-HC102の例示的な動作をさらに説明するために、図7が提供される。図7を説明する際に、明確化のために図1～図3の要素が参照される。図7における動作は、要求トラップ228が、要求206のステータス308を要求トラップ228の複数のCMSR300(0)～300(N)のうちのCR1204(0)に対応するCMSR300に記憶することで開始する(ブロック700)。この点で、要求トラップ228は、本明細書では「要求のステータスをCR1に対応するCMSRに記憶するための手段」と呼ばれ得る。要求トラップ228はまた、要求206のPIU310(0)を、要求トラップ228の複数のCMDAT302(0)～302(N)のうちのCR1204(0)に対応するCMDAT302(0)に記憶する(ブロック702)。したがって、要求トラップ228は、本明細書では「要求のPIUをCR1に対応するCMDATに記憶するための手段」と呼ばれ得る。次に、要求トラップ228は、要求206がトラップされていることを示す、VMM108への割込み256を生成し得る(ブロック704)。したがって、要求トラップ228は、本明細書では「要求がトラップされることを示すVMMへの割込みを生成するための手段」と呼ばれ得る。次いで、IOV-HC102は、要求トラップ228のCMCR304を介してVMM108から処理命令306を受信し得る(ブロック706)。この点で、IOV-HC102は、本明細書では「要求トラップのCMCRを介してVMMから処理命令を受信するための手段」と呼ばれ得る。これは、図7に示される例示的な動作は、eMMC規格に基づく態様などの、本明細書に開示されるいくつかの態様に適用されない場合があることを理解されたい。

30

#### 【0041】

本明細書に開示される態様による、フラッシュメモリベースのストレージデバイスのIOV-HCにおけるコマンドトラッピングは、任意のプロセッサベースのデバイスに提供または統合され得る。例としては、限定するものではないが、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイル電話、セルラー電話、コンピ

40

50

ユータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、およびポータブルデジタルビデオプレーヤを含む。

#### 【0042】

この点で、図8は、図1の10V-HC102とともにSoC100を採用し得るプロセッサベースのシステム800の一例を示す。この例では、プロセッサベースのシステム800は1つまたは複数の中央処理装置(CPU)802を含み、各々が1つまたは複数のプロセッサ804を含む。CPU802は、一時的に記憶されたデータへの迅速なアクセスのためにプロセッサ804に結合されたキャッシュメモリ806を有し得る。CPU802はシステムバス808に結合され、プロセッサベースのシステム800に含まれるデバイスを相互に連結し得る。よく知られているように、CPU802は、システムバス808を介してアドレス、制御、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、CPU802は、スレーブデバイスの一例として、メモリコントローラ810にバストランザクション要求を通信し得る。図8に示されていないが、複数のシステムバス808を設けることができる。

10

#### 【0043】

他のデバイスがシステムバス808に接続され得る。図8に示されるように、これらのデバイスは、例として、メモリシステム812、1つまたは複数の入力デバイス814、1つまたは複数の出力デバイス816、1つまたは複数のネットワークインターフェースデバイス818、および1つまたは複数のディスプレイコントローラ820を含み得る。入力デバイス814は、限定はしないが、入力キー、スイッチ、音声プロセッサ等を含む、任意のタイプの入力デバイスを含み得る。出力デバイス816は、限定はしないが、音声、ビデオ、他の視覚インジケータ等を含む、任意のタイプの出力デバイスを含み得る。ネットワークインターフェースデバイス818は、ネットワーク822への、またはそこからのデータの交換を可能にするように構成された任意のデバイスであり得る。ネットワーク822は、限定はしないが、ワイヤードまたはワイヤレスネットワーク、プライベートまたはパブリックネットワーク、ローカルエリアネットワーク(LAN)、ワイドローカルエリアネットワーク、ワイヤレスローカルエリアネットワーク、BLUETOOTH(登録商標)(BT)、およびインターネットを含む、任意のタイプのネットワークであり得る。ネットワークインターフェースデバイス818は、任意のタイプの所望の通信プロトコルをサポートするように構成され得る。メモリシステム812は、1つまたは複数のメモリユニット824(0)～824(N)を含み得る。

20

#### 【0044】

CPU802はまた、1つまたは複数のディスプレイ826に送信された情報を制御するために、システムバス808を介してディスプレイコントローラ820にアクセスするように構成され得る。ディスプレイコントローラ820は、1つまたは複数のビデオプロセッサ828を介して表示されるべき情報をディスプレイ826に送信して、ディスプレイ826に適した形式に表示されるべき情報を処理する。ディスプレイ826は、限定はしないが、陰極線管(CRT)、液晶ディスプレイ(LCD)、発光ダイオード(LED)ディスプレイ、プラズマディスプレイ等の任意のタイプのディスプレイを含み得る。

30

#### 【0045】

当業者は、本明細書に開示された態様に関連して説明される様々な例示的な論理プロック、モジュール、回路、およびアルゴリズムは、電子ハードウェア、メモリまたは別のコンピュータ可読媒体に記憶された命令として実装され得、プロセッサまたは他の処理デバイス、あるいはその両方の組合せによって実行されることをさらに理解するだろう。本明細書に記載されたデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路(IC)、またはICチップで採用され得る。本明細書において開示されるメモリは、任意のタイプおよびサイズのメモリとすることができます、所望の任意のタイプの情報を記憶するように構成され得る。この互換性を明示的に説明するために、様々な例示的な構成要素、プロック、モジュール、回路、およびステップが、それらの機能の観点から一般的に上述され

40

50

ている。そのような機能がどのように実現されるかは、特定の用途、設計上の選択、および/または、システム全体に課された設計上の制約によって決まる。当業者は、説明された機能を特定の用途ごとに様々な方法で実装することができるが、そのような実装の決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

#### 【0046】

本明細書に開示された態様に関連して説明される様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)または他のプログラマブル論理デバイス、ディスクリートゲートまたはトランジスタロジック、ディスクリートハードウェア構成要素、あるいは本明細書に記載の機能を実行するように設計されたそれらの任意の組合せで実装または実行され得る。プロセッサはマイクロプロセッサであり得るが、代替実施形態では、プロセッサは、任意の従来型プロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであり得る。プロセッサはまた、コンピューティングデバイスの組合せ、たとえばDSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、1つまたは複数のマイクロプロセッサとDSPコア、あるいは任意の他のそのような構成として実装され得る。10

#### 【0047】

本明細書に開示された態様は、ハードウェアにおいて、およびハードウェアに記憶された命令において具体化され得、たとえば、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み出し専用メモリ(ROM)、電気的プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られているコンピュータ可読媒体の他の任意の形態に存在し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるようプロセッサに結合される。代替として、記憶媒体はプロセッサと一緒に構成であってもよい。プロセッサおよび記憶媒体はASIC内に存在し得る。ASICは、遠隔局に存在し得る。代替として、プロセッサおよび記憶媒体は、遠隔局、基地局、またはサーバにおけるディスクリート構成要素として存在し得る。20

#### 【0048】

また、本明細書の例示的な態様のいずれかに記載の動作ステップは、実施例および説明を提供するために記載されていることに留意されたい。説明した動作は、図示した順序以外の多数の異なる順序で実行され得る。さらに、単一の動作ステップで説明した動作は、実際にはいくつかの異なるステップで実行され得る。さらに、例示的な態様で説明した1つまたは複数の動作ステップが組み合わされ得る。当業者には容易に明らかになるよう、フローチャート図に示す動作ステップは、多数の異なる修正を受ける場合があることを理解されたい。当業者はまた、情報および信号が、様々な異なる技術および技法のいずれかを用いて表され得ることを理解するだろう。たとえば、上記の説明全体にわたって言及され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁性粒子、光場または光学粒子、またはそれらの任意の組合せによって表され得る。30

#### 【0049】

本開示の前の説明は、当業者が本開示を作成または使用することを可能にするために提供される。本開示に対する様々な修正は当業者には容易に明らかになり、本明細書で定義された一般的な原理は、本開示の趣旨または範囲から逸脱することなしに他の変形形態に適用され得る。したがって、本開示は、本明細書で説明する例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴と一致する最も広い範囲を与えられるべきである。40

#### 【符号の説明】

#### 【0050】

100 システムオンチップ(SoC)

102 IOV-HC

50

|                 |                              |    |

|-----------------|------------------------------|----|

| 104(0) ~ 104(N) | I/Oクライアント                    |    |

| 106             | フラッシュメモリベースのストレージデバイス        |    |

| 108             | 仮想マシンマネージャ(VMM)              |    |

| 200             | ベースレジスタインターフェース(BRI)         |    |

| 204(0) ~ 204(N) | クライアントレジスタインターフェース(CRI)、VLCI |    |

| 206             | コマンド                         | 10 |

| 206             | フェッチされた要求                    |    |

| 206             | トラップされた要求                    |    |

| 208             | 要求フェッチ回路                     |    |

| 210             | 矢印                           |    |

| 212             | 矢印                           |    |

| 214             | 矢印                           |    |

| 216             | システムメモリ                      |    |

| 218             | 矢印                           |    |

| 220             | トランスポートプロトコルエンジン             |    |

| 222             | 相互接続                         |    |

| 224             | バス                           |    |

| 226             | 要求フィルタ回路                     |    |

| 228             | 要求トラップ                       |    |

| 230             | 応答生成回路                       | 20 |

| 232             | 矢印                           |    |

| 234             | 内容                           |    |

| 236             | アクセス制御回路                     |    |

| 240             | 矢印                           |    |

| 242             | 矢印                           |    |

| 244             | MHPC                         |    |

| 246             | 矢印                           |    |

| 248             | 矢印                           |    |

| 250             | 矢印                           |    |

| 252             | 矢印                           | 30 |

| 254(0) ~ 254(N) | コマンドミラー                      |    |

| 256             | 割込み                          |    |

| 258             | 応答                           |    |

| 260             | 矢印                           |    |

| 300(0) ~ 300(N) | コマンドミラーステータスレジスタ(CMSR)       |    |

| 302(0) ~ 302(N) | コマンドミラーデータレジスタアレイ(CMDAT)     |    |

| 304             | コマンドミラー制御レジスタ(CMCR)          |    |

| 306             | 処理命令                         |    |

| 308(0) ~ 308(N) | ステータス                        |    |

| 402             | 応答生成器制御レジスタ(RGCR)            | 40 |

| 404             | 応答生成器ステータスレジスタ(RGSR)         |    |

| 406             | 応答生成器PIUレジスタ(RGU)            |    |

| 408             | 応答生成命令                       |    |

| 410             | ステータス                        |    |

| 412             | 応答PIU                        |    |

| 800             | プロセッサベースのシステム                |    |

| 802             | 中央処理装置(CPU)                  |    |

| 804             | プロセッサ                        |    |

| 806             | キャッシュメモリ                     |    |

| 808             | システムバス                       | 50 |

810 メモリコントローラ

812 メモリシステム

814 入力デバイス

816 出力デバイス

818 ネットワークインターフェースデバイス

820 ディスプレイコントローラ

822 ネットワーク

824(1) ~ 824(N) メモリユニット

826 ディスプレイ

828 ビデオプロセッサ

【図1】

【図2】

【 四 3 】

【 図 4 】

【図5A】

【図5B】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 マヤ・ハイム

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 リー・スマン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 デイヴィッド・テブ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 桜井 茂行

(56)参考文献 国際公開第2013/171789 (WO, A1)

特表2015-519619 (JP, A)

特開平1-145717 (JP, A)

国際公開第2013/109640 (WO, A1)

米国特許出願公開第2013/0060981 (US, A1)

米国特許出願公開第2013/0290606 (US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 13/10 - 13/14

G 06 F 3/06 - 3/08

G 06 F 12/00