(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5921822号

(P5921822)

(45) 発行日 平成28年5月24日(2016.5.24)

(24) 登録日 平成28年4月22日(2016.4.22)

|                |           |

|----------------|-----------|

| (51) Int.Cl.   | F 1       |

| HO 1 L 21/3205 | (2006.01) |

| HO 1 L 21/768  | (2006.01) |

| HO 1 L 23/522  | (2006.01) |

| HO 1 L 21/822  | (2006.01) |

| HO 1 L 27/04   | (2006.01) |

| HO 1 L         | 21/88     |

| HO 1 L         | 27/04     |

| HO 1 L         | 25/08     |

| HO 1 L         | 27/10     |

|                | 4 6 1     |

請求項の数 24 (全 31 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2011-113410 (P2011-113410) |

| (22) 出願日     | 平成23年5月20日 (2011.5.20)       |

| (65) 公開番号    | 特開2012-9847 (P2012-9847A)    |

| (43) 公開日     | 平成24年1月12日 (2012.1.12)       |

| 審査請求日        | 平成26年5月16日 (2014.5.16)       |

| (31) 優先権主張番号 | 10-2010-0061080              |

| (32) 優先日     | 平成22年6月28日 (2010.6.28)       |

| (33) 優先権主張国  | 韓国 (KR)                      |

| (31) 優先権主張番号 | 12/913,748                   |

| (32) 優先日     | 平成22年10月27日 (2010.10.27)     |

| (33) 優先権主張国  | 米国 (US)                      |

|           |                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 100110364<br>弁理士 実広 信哉                                                                                                                                          |

| (72) 発明者  | 文 光辰<br>大韓民国京畿道水原市靈通区網浦洞 (番地<br>なし) ヌルブルンビョクサンアパート 1<br>18 棟 902 号                                                                                              |

最終頁に続く

(54) 【発明の名称】半導体素子及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

## 基板と、

前記基板に埋め込まれ、平坦部及び前記平坦部に取り囲まれた突出部を含む表面を有し、前記基板よりも大きな熱膨張係数を有する材料からなるビア構造物と、

前記ビア構造物の前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない導電構造物と、を含む半導体素子。

## 【請求項 2】

前記導電構造物は、前記平坦部上のみに形成されて前記突出部上には形成されないことを特徴とする請求項 1 に記載の半導体素子。

10

## 【請求項 3】

前記導電構造物は、前記ビア構造物の前記表面領域の 5 ~ 80 % に形成されることを特徴とする請求項 1 に記載の半導体素子。

## 【請求項 4】

前記ビア構造物の前記突出部上のみに形成されるバッファ膜をさらに含むことを特徴とする請求項 1 に記載の半導体素子。

## 【請求項 5】

前記ビア構造物の前記突出部上に形成され、及び前記導電構造物を取り囲む誘電膜をさらに含むことを特徴とする請求項 4 に記載の半導体素子。

## 【請求項 6】

20

前記ビア構造物は、少なくとも一つの誘電膜及び半導体基板を貫通する開口内に形成されたT S Vであることを特徴とする請求項4に記載の半導体素子。

【請求項7】

前記T S Vは、

前記開口の内壁上に形成された絶縁膜と、

前記開口内の前記絶縁膜上に形成されたバリア膜と、

前記バリア膜が形成された前記開口内に形成されて前記バリア膜によって少なくとも一部が取り囲まれる導電パターンと、を含むことを特徴とする請求項6に記載の半導体素子。

【請求項8】

10

前記T S Vは、前記導電パターンが形成された前記開口内に形成されて、前記導電パターンによって少なくとも一部が取り囲まれる中心充填部を含むことを特徴とする請求項7に記載の半導体素子。

【請求項9】

前記中心充填部は、前記導電パターンに比べて低い熱膨張係数を有し、これによって、前記突出部はリング形状を有することを特徴とする請求項8に記載の半導体素子。

【請求項10】

前記T S Vは、また他の半導体素子のコンタクト構造物と結合して積層型半導体素子を形成することを特徴とする請求項6に記載の半導体素子。

【請求項11】

20

前記積層型半導体素子は、メモリ素子であることを特徴とする請求項10に記載の半導体素子。

【請求項12】

前記ビア構造物の前記平坦部の少なくとも一部上に形成され、前記突出部上には形成されない他の導電構造物と、

前記導電構造物及び前記他の導電構造物を結合する接続構造物と、をさらに含むことを特徴とする請求項1に記載の半導体素子。

【請求項13】

前記導電構造物は、前記ビア構造物の前記突出部の少なくとも一部上に形成された開口を含むことを特徴とする請求項1に記載の半導体素子。

30

【請求項14】

平坦部及び突出部を含む表面を有する他のビア構造物をさらに含むが、

前記導電構造物は前記複合ビア構造物の平坦部上に形成され、前記突出部上には形成されないことを特徴とする請求項1に記載の半導体素子。

【請求項15】

各々が平坦部及び突出部を含む各表面を有する複数個のビア構造物と、

前記複数個のビア構造物のうち、少なくとも二つを含む各セットの平坦部上には形成され、突出部上には形成されない複数個の導電構造物をさらに含むことを特徴とする請求項1に記載の半導体素子。

【請求項16】

40

前記複数個の導電構造物を結合する結合構造物をさらに含むことを特徴とする請求項15に記載の半導体素子。

【請求項17】

基板と、前記基板に埋め込まれ、平坦部及び前記平坦部に取り囲まれた突出部を含む表面を有し、前記基板よりも大きな熱膨張係数を有する材料からなるビア構造物と、前記ビア構造物の前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない導電構造物とを含む第1集積回路チップと、

前記第1集積回路チップの前記ビア構造物に結合されるコンタクト構造物を含む第2集積回路チップを具備する積層型半導体素子。

【請求項18】

50

前記導電構造物は、前記平坦部上のみに形成されて前記突出部上には形成されないことを特徴とする請求項17に記載の積層型半導体素子。

【請求項19】

前記導電構造物は、前記ビア構造物の前記表面領域の5~80%に形成されることを特徴とする請求項17に記載の積層型半導体素子。

【請求項20】

前記ビア構造物の前記突出部上に形成されるバッファ膜と、

前記ビア構造物の前記突出部上に形成され、及び前記導電構造物を取り囲む誘電膜と、をさらに含むことを特徴とする請求項17に記載の積層型半導体素子。

【請求項21】

前記ビア構造物は、前記第1集積回路チップの少なくとも一つの誘電膜及び半導体基板を貫通する開口内に形成されたTSVであることを特徴とする請求項17に記載の積層型半導体素子。

【請求項22】

前記積層型半導体素子は、メモリ素子であることを特徴とする請求項17に記載の積層型半導体素子。

【請求項23】

平坦である中心部、平坦である外郭部、及び前記中心部と前記外郭部との間に配置された突出部を含む表面を有し、半導体基板を貫通する、前記半導体基板よりも大きな熱膨張係数を有する材料からなるビア構造物と、

前記ビア構造物の前記外郭部のうち、少なくとも一部上に形成され、前記中心部上には形成されない導電構造物を含む半導体素子。

【請求項24】

中心部及び平坦である外郭部を含む表面を有し、半導体基板を貫通する、前記半導体基板よりも大きな熱膨張係数を有する材料からなるビア構造物と、

前記ビア構造物の前記外郭部のうち、少なくとも一部上に形成され、前記中心部上には形成されない導電構造物を含み、

前記ビア構造物の前記中心部は、前記外郭部から突出していることを特徴とする半導体素子。

【発明の詳細な説明】

30

【技術分野】

【0001】

本発明は半導体素子及びその製造方法に関する。より詳細には、ビア(via)構造物上面に部分的に形成される導電構造物を含む半導体素子及びその製造方法に関する。

【背景技術】

【0002】

導電性ライン及びビアは共通的に相互連結された構造物で使われて半導体装置の集積回路を形成する。ビアは多層の相互連結膜上に形成された導電性ラインを連結することに使われる。

【0003】

40

さらに、TSV(through silicon via)は複合集積回路チップをカップリングするために、シリコン基板を貫通し形成して積層された半導体装置を形成する。そのような積層半導体装置は、高性能及び低面積を有する集積回路を提供する。

【0004】

いかなる形態のビアに対しても、導電性ラインは高品質の接触性を有するビア上に形成されることが望ましい。そういう高品質の接触性は低抵抗及び高電流性能を有するビアと導電性ラインとの間の連結のために望ましい。

【先行技術文献】

【特許文献】

【0005】

50

【特許文献1】特開2009-111082号公報

【特許文献2】特開平11-251316号公報

【特許文献3】特許第4165133号

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、高信頼性及び優秀な動作特性を有する半導体素子を提供することにある。

【0007】

発明の他の目的は、上述の半導体素子の製造方法を提供することにある。

10

【課題を解決するための手段】

【0008】

上述の目的を達成するための本発明の実施形態に係る半導体素子は、ピア構造物及び導電構造物を含む。前記ピア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は、前記ピア構造物の前記平坦部のうち少なくとも一部上に形成され、前記突出部のうち少なくとも一部上には形成されない。

【0009】

一実施形態によると、前記導電構造物は前記平坦部上のみに形成され、前記突出部上には形成されない。例えば、前記導電構造物は、前記ピア構造物の前記表面領域の5~80%に形成される。

20

【0010】

一実施形態によると、前記半導体素子は、前記ピア構造物の前記突出部上のみに形成されるバッファ膜をさらに含む。さらに、前記半導体素子は、前記ピア構造物の前記突出部上に形成され、及び前記導電構造物を取り囲む誘電膜をさらに含む。

【0011】

一実施形態によると、前記ピア構造物は、少なくとも一つの誘電膜及び半導体基板を貫通する開口内に形成されたTSV (through silicon via) である。例えば、前記TSVは、前記開口の内壁上に形成された絶縁膜、前記開口内の前記絶縁膜上に形成されたバリア膜及び前記バリア膜が形成された前記開口内に形成されて前記バリア膜によって少なくとも一部が囲まれる導電パターンを含む。

30

【0012】

一実施形態によると、前記TSVは、前記導電パターンが形成された前記開口内に形成されて前記導電パターンによって少なくとも一部が囲まれる中心充填部を含む。前記中心充填部は、前記導電パターンに比べて低い熱膨張係数を有し、これによって、前記突出部はリング形状を有する。

【0013】

一実施形態によると、前記TSVは、他の半導体素子のコンタクト構造物と結合して積層型半導体素子を形成する。例えば、前記積層型半導体素子はメモリ素子である。

【0014】

一実施形態によると、前記半導体素子は、前記ピア構造物の前記平坦部の少なくとも一部上に形成され、前記突出部上には形成されない他の導電構造物を含む。さらに、前記半導体素子は、前記導電構造物及び前記他の導電構造物を結合する連結構造物をさらに含む。

40

【0015】

一実施形態によると、前記導電構造物は、前記ピア構造物の前記突出部の少なくとも一部上に形成された開口を含む。

【0016】

一実施形態によると、前記半導体素子は、平坦部及び突出部を含む表面を有する他のピア構造物をさらに含む。前記導電構造物は前記複合ピア構造物の平坦部上に形成され、前記突出部上には形成されない。

50

**【0017】**

一実施形態によると、前記半導体素子は、複数個のビア構造物及び複数個の導電構造物をさらに含む。前記複数個のビア構造物は、各々が平坦部及び突出部を含む各表面を有する。前記導電構造物は、前記複数個のビア構造物のうち、少なくとも二つを含む各セットの平坦部上には形成されて突出部上には形成されない。さらに、前記半導体素子は前記複数個の導電構造物を結合する結合構造物をさらに含む。

**【0018】**

上述の目的を達成するための本発明の他の実施形態に係る半導体素子は、第1集積回路チップ及び第2集積回路チップを含む。前記第1集積回路チップは、ビア構造物及び導電構造物を含む。前記ビア構造物は平坦部及び突出部を含む表面を有する。前記導電構造物は、前記ビア構造物の前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。前記第2集積回路チップは前記第1集積回路チップの前記ビア構造物に結合されるコンタクト構造物を含む。10

**【0019】**

上述の目的を達成するための本発明のまた他の実施形態に係る半導体素子は、半導体基板を貫通して形成するビア構造物を含む。前記ビア構造物は中心部及び外郭部を含む表面を有する。前記半導体素子は、前記ビア構造物の前記外郭部のうち、少なくとも一部上に形成され、前記中心部上には形成されない導電構造物を含む。

**【0020】**

一実施形態によると、前記中心部は、前記外郭部とともに平坦に形成され、これによつて、前記中心部及び前記外郭部は同一平面上に形成される。これとは異なり、前記中心部は前記外郭部から突出することもできる。20

**【0021】**

上述の他の目的を達成するための本発明の実施形態に係る半導体素子の製造方法は、平坦部及び突出部を含む表面を有するビア構造物を形成する段階、並びに前記ビア構造物の前記平坦部のうち少なくとも一部上に形成され、前記突出部のうち少なくとも一部上には形成されない導電構造物を形成する段階を含む。

**【0022】**

前記導電構造物は、前記平坦部上のみに形成されて前記突出部上には形成されない。これによつて、前記導電構造物は前記ビア構造物に低抵抗及び高電流性能を有して連結されることができる。30

**【図面の簡単な説明】****【0023】**

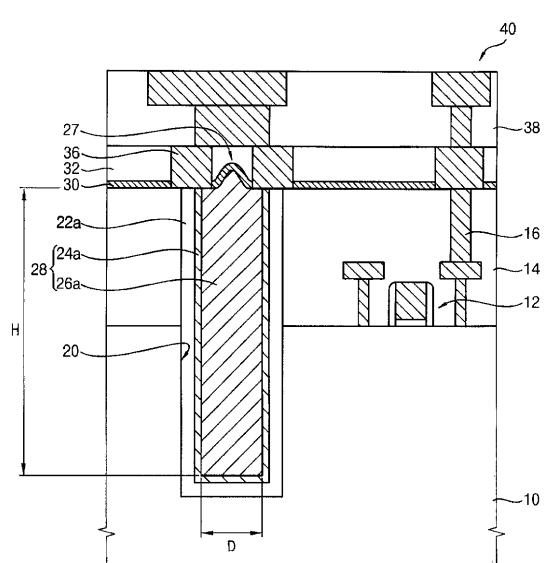

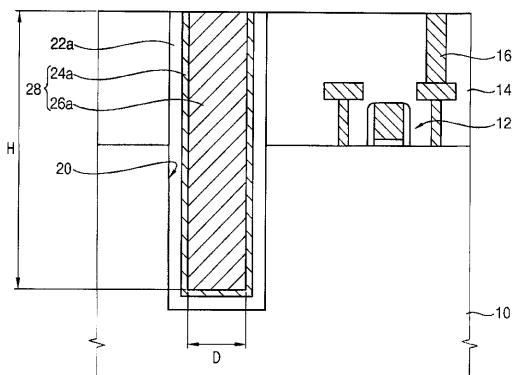

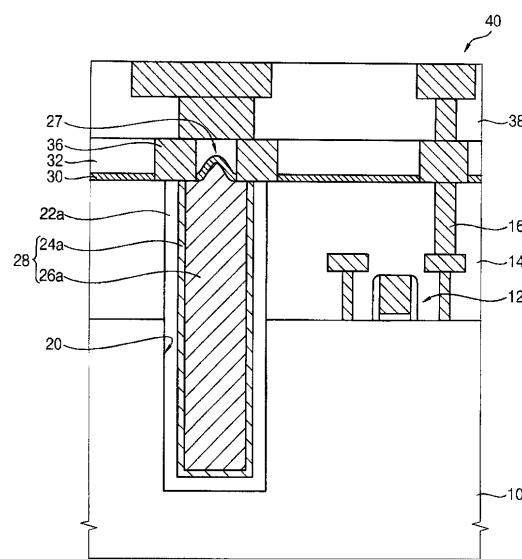

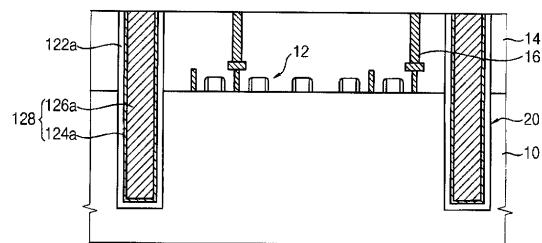

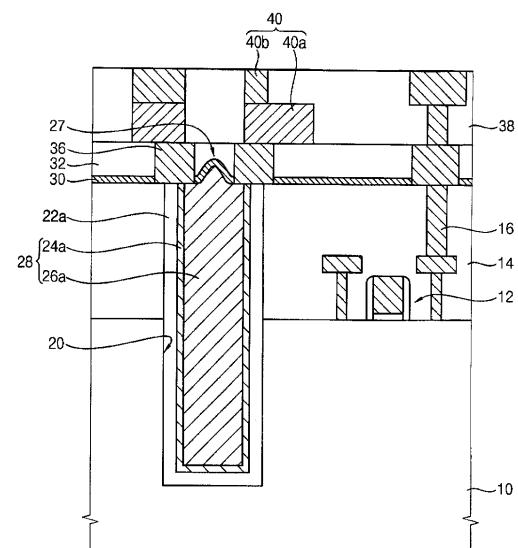

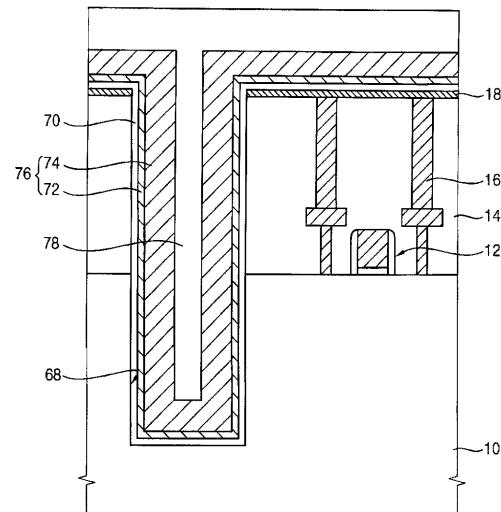

【図1】本発明の一実施形態に係るビアと導電構造物を有する半導体素子の断面図である。

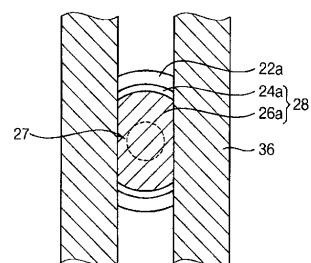

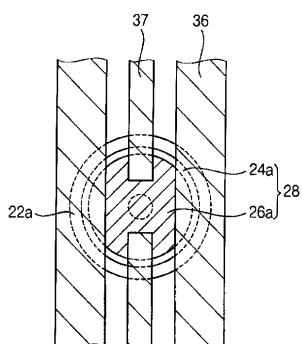

【図2】図1の半導体素子の平面図である。

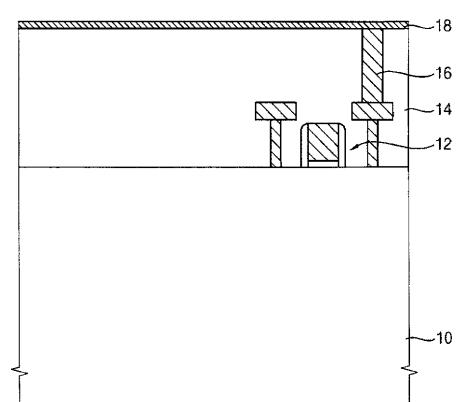

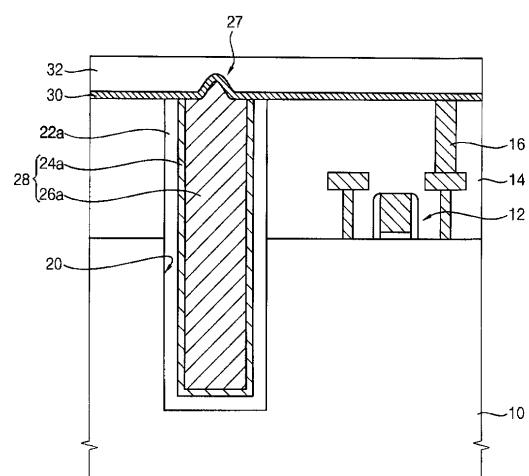

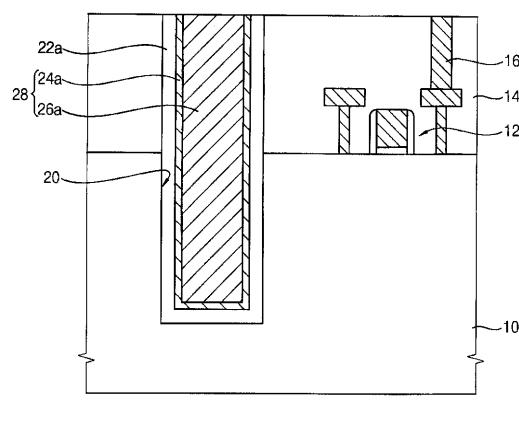

【図3】一実施形態に従つて図1に示した半導体素子を製造する方法を示す断面図である。

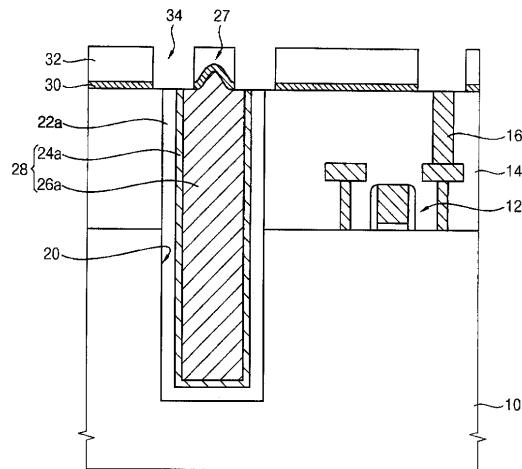

【図4】一実施形態に従つて図1に示した半導体素子を製造する方法を示す断面図である。

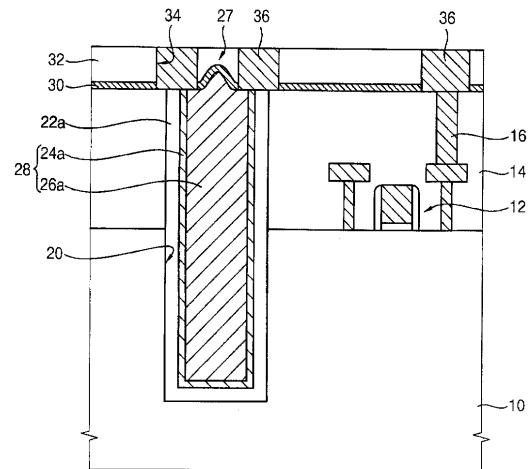

【図5】一実施形態に従つて図1に示した半導体素子を製造する方法を示す断面図である。

【図6】一実施形態に従つて図1に示した半導体素子を製造する方法を示す断面図である。

【図7】一実施形態に従つて図1に示した半導体素子を製造する方法を示す断面図である。

【図8】一実施形態に従つて図1に示した半導体素子を製造する方法を示す断面図である。

【図9】一実施形態に従つて図1に示した半導体素子を製造する方法を示す断面図である。

10

20

30

40

50

【図10】一実施形態に従って図1に示した半導体素子を製造する方法を示す断面図である。

【図11】他の実施形態による図1に示した半導体素子を製造する方法を示す断面図である。

【図12】他の実施形態による図1に示した半導体素子を製造する方法を示す断面図である。

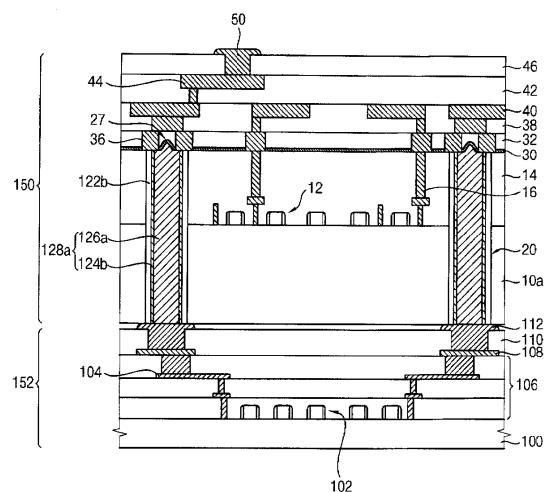

【図13】本発明の一実施形態によるTSV構造物を有する積層型半導体素子を示す断面図である。

【図14】図13に示した積層型半導体素子の製造方法を示す断面図である。

【図15】図13に示した積層型半導体素子の製造方法を示す断面図である。

10

【図16】図13に示した積層型半導体素子の製造方法を示す断面図である。

【図17】図13に示した積層型半導体素子の製造方法を示す断面図である。

【図18】図13に示した積層型半導体素子の製造方法を示す断面図である。

【図19】本発明の一実施形態に係るピア構造物上に形成された開口を有する導電構造物を説明するための平面図である。

【図20】本発明の一実施形態に係るピア構造物上に形成された開口を有する導電構造物を説明するための平面図である。

【図21】本発明の一実施形態に係る複合ピア構造物上に形成された複合導電構造物を説明するための平面図である。

20

【図22】本発明の一実施形態に係る複合ピア構造物上に形成された複合導電構造物を説明するための平面図である。

【図23】本発明の一実施形態に係る半導体素子内のピア構造物上に形成された追加導電構造物を含む断面図である。

【図24】本発明の一実施形態に係る中心充填部を有するピア構造物を含む半導体素子の断面図である。

【図25】本発明の一実施形態に係る中心充填部を有するピア構造物を含む半導体素子の平面図である。

【図26】図24及び図25に示した半導体素子を製造する方法を示す断面図である。

【図27】図24及び図25に示した半導体素子を製造する方法を示す断面図である。

【図28】本発明の一実施形態に係る複合ピア構造物上に形成された複合導電構造物を有する半導体素子の平面図である。

30

【図29】本発明の一実施形態に係る複合ピア構造物上に形成された複合導電構造物を有する半導体素子の平面図である。

【図30】本発明の一実施形態に係る複合ピア構造物上に形成された複合導電構造物を有する半導体素子の平面図である。

【図31】本発明の一実施形態に係る各積層半導体素子を有するシステムのブロックダイアグラムである。

【図32】本発明の一実施形態に係る各積層半導体素子を有するシステムのブロックダイアグラムである。

【図33】本発明の一実施形態に係る各積層半導体素子を有するシステムのブロックダイアグラムである。

40

【図34】本発明の一実施形態に係る互いに同一平面上に位置する中心部及び外郭部を有する半導体素子を説明するための断面図である。

【図35】本発明の一実施形態に係る互いに同一平面上に位置する中心部及び外郭部を有する半導体素子を説明するための断面図である。

【図36】本発明の一実施形態に係るリング型ピア構造物を有する半導体素子を説明するための平面図である。

【図37】本発明の一実施形態に係るリング型ピア構造物を有する半導体素子を説明するための断面図である。

【発明を実施するための最良の形態】

50

**【0024】**

以下、図面を参照しつつ、本発明の望ましい実施形態をより詳しく説明する。

**【0025】**

本発明の添付図面において、構造物のサイズは本発明の明確性に基づくために実際より拡大して示した。

**【0026】**

本発明において第1、第2などの用語は多様な構成要素を説明するにあたって使用することができるが、各構成要素は使用される用語によって限定されるものではない。各用語は1つの構成要素を他の構成要素と区別する目的のみで使用される。

**【0027】**

本明細書で使用する用語は、単に、特定実施形態を説明するために使用したものであつて、本発明を限定しようとしていることではない。単数表現は文脈上、明白に異なる意味を有しない限り、複数の表現を含む。本明細書において、「含む」または「有する」などの用語は、明細書上に記載された特徴、数字、段階、動作、構成要素、部分品、またはこれらを組み合わせたものが存在することを指定しようとしていることであつて、1つまたはそれ以上の別の特徴、数字、段階、動作、構成要素、部分品、またはこれらを組み合わせたものの存在または付加可能性を予め排除しないことと理解されるべきである。

**【0028】**

本明細書において、各層（膜）、領域、電極、パターンまたは、構造物が対象物、基板、各層（膜）、領域、電極または、パターンの「上に」、「上部に」または「下部に」形成されると言及される場合には各階（膜）、領域、電極、パターンまたは、構造物が直接、基板、各階（膜）、領域、または、パターン上に形成されたり、下に位置することを意味したり、他の層（膜）、他の領域、他の電極、他のパターンまたは、他の構造物が対象物や基板上に追加的に形成することを意味する。

**【0029】**

本明細書に開示されている本発明の実施形態に対して、特定の構造的ないし機能的説明は単に本発明の実施形態を説明するための目的で例示されたもので、本発明の実施形態は多様な形態で実施可能で、本明細書に説明された実施形態に限定されるものではない。

**【0030】**

即ち、本発明は多様な変更を加えることができ、種々な形態を有することができるが、特定の実施形態を図面に例示し、本明細書に詳細に説明したものである。これは本発明を特定の開示形態に限定しようとするものではなく、本発明の思想及び技術範囲に含まれるすべての変更、均等物ないし代替物を含むと理解されるべきである。

**【0031】**

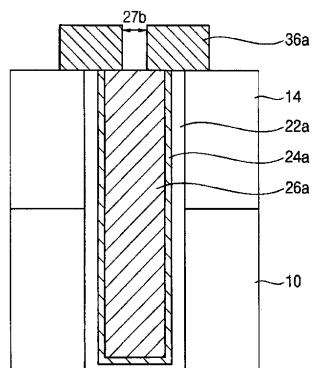

図1は本発明の一実施形態に係るピアと導電構造物を有する半導体素子の断面図である。図2は図1の半導体素子の平面図である。

**【0032】**

図1及び図2を参照すると、第1基板10上に第1回路パターン12が備わる。前記第1基板10は半導体物質で成り立った基板ができ、一例として、単結晶シリコン基板であることができる。前記第1回路パターン12は、トランジスタ、ダイオードなど集積回路を形成するものなどを含むことができる。

**【0033】**

前記第1基板10上には前記第1回路パターン12を覆う第1層間絶縁膜14が備わる。前記第1回路パターン12はドーピングされたポリシリコンまたは金属からなる下部配線16により電気的に接続されることができる。前記下部配線16のうち一部は上部面が前記第1層間絶縁膜14の上部面と同じ平面上に位置する。

**【0034】**

前記第1層間絶縁膜14及び第1基板10には、前記第1層間絶縁膜14を貫通して第1基板10内部まで延伸するピアホール20が生成されている。図示はしていないが、前記ピアホール20は複数個が備わることができる。前記ピアホール20の内壁について絶

10

20

30

40

50

縁膜パターン22aが備わる。前記絶縁膜パターン22aは第1基板10とビアホール20内の導電物質を含むTSVコンタクト28との間を絶縁させる役割をする。

【0035】

前記TSVコンタクト28は、導電性ライン構造物に接続されるものであって、ビア構造物の一例である。だが、本発明は導電性ライン構造物に接続されるいかなる形態のビア構造物にも適用することができる。

【0036】

前記絶縁膜パターン22a上には、バリア膜パターン24aが備わる。前記バリア膜パターン24aは、Ta、Ta<sub>N</sub>、Ti、Ti<sub>N</sub>、Ru、Co、Ni、NiB、WNなどの金属または金属窒化物を含むことができる。これらは単独または2つ以上を積層して使うことができる。

10

【0037】

前記バリア膜パターン24a上には前記ビアホール20の残りを埋める導電パターン26aが備わる。前記導電パターン26aは、低抵抗を有する金属からなることができる。また、前記導電パターン26aは前記第1基板10をなすシリコン物質の熱膨張係数の1.5倍以上の熱膨張係数を有する金属物質を含むことができる。

【0038】

一例として、前記導電パターン26aは銅、アルミニウム、金、インジウム、ニッケルなどからなることができ、これらは単独で形成することが望ましいが、2つ以上を含むことができる。本実施形態において、前記導電パターン26aは銅からなるとして説明する。即ち、前記ビアホール20内には前記バリア膜パターン24a及び導電パターン26aからなるTSVコンタクト28が備わる。

20

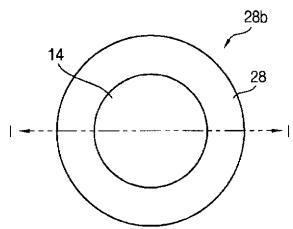

【0039】

前記ビア構造物28は、図2に示したように、基板10から離れて上に向く外郭部及び中心部27を有する表面を含む。図1及び図2を参照すると、前記外郭部は絶縁膜パターン22aのような少なくとも一つの取り囲む物質に隣接して配置され、中心部27は前記外郭部によって囲まれる。

【0040】

図1及び図2を参照すると、ビア構造物28の前記外郭部は、バリア膜パターン24a及び基板10表面と平行した上面を有する導電パターン26aの一部を含む。即ち、ビア構造物28の前記外郭部はバリア膜パターン24aと、取り囲んでいる第1層間絶縁膜14と同一平面上に位置する上面を有する導電パターン26a部分とを含む。

30

【0041】

ビア構造物28はビア構造物28の前記外郭部から突出した中心部27をさらに含む。即ち、中心部27は前記外郭部の平面及び取り囲んでいる第1層間絶縁膜14の平面から延伸する導電パターン26aの上面の部分(図2に示す)を含む。これによって、ビア構造物28の中心部はビア構造物28の突出部と命名されることができる。前記導電パターン26aが銅を含む場合、ビア構造物28の前記突出部は図1及び図2の半導体素子を製造する後続工程で銅熱膨張によって形成されることができる。

【0042】

前記導電パターン26aは10~100μmの高さ(H)、望ましくは、30~80μmの高さ(H)を有することができる。また、前記導電パターン26aは1~15μmの直径(D)、望ましくは1~10μmの直径(D)を有することができる。

40

【0043】

図1及び図2をさらに参照すると、TSV構造物28及び第1層間絶縁膜14上にバッファ膜30が備わる。バッファ膜30の一部はビア構造物28の突出部27上に残留する。前記バッファ膜30は前記TSV構造物28の導電物質が別の構造物に広がることを防止する役割をする。

【0044】

前記バッファ膜30はシリコン窒化物、シリコン炭素窒化物、及びSiCONなどから

10

20

30

40

50

なることができ、これらは単独または2つ以上が積層された形状を有することができる。前記バッファ膜30は300～1000の厚さを有することができる。

【0045】

前記バッファ膜30上には第1金属間絶縁膜32が備わる。前記第1金属間絶縁膜32は、低誘電率を有する物質からなることができ、例えば、シリコン酸化物、炭素ドーピングされたシリコン酸化物などからなることができる。

【0046】

前記バッファ膜30及び第1金属間絶縁膜32を貫通する導電性ライン36が備わる。即ち、前記導電性ライン36は前記TSV構造物28の平坦な上部面と少なくとも部分的に接触する導電性構造物の一例である。

10

【0047】

前記導電性ライン36と前記TSV構造物28の上部面が接触する部位の面積が、前記TSV構造物28上部面の面積の80%以上ならば、前記導電性ライン36が突出部27と接触しうる。また、前記導電性ライン36と前記TSV構造物28の上部面が接触する部位の面積が前記TSV構造物28上部面の面積の5%以下ならば、そのような狭い接触面積によってこれを介して流れる電流が不充分となりうる。従って、前記導電性ライン36と前記TSV構造物28の上部面が接触する部位の面積は、前記TSV構造物28上部面の面積の5～80%であることが望ましい。

【0048】

図2の実施形態において、一つの前記TSV構造物28の上部面には互いに平行するように配置される2つの導電性ライン36が備わる。前記導電性ライン36は前記TSV構造物28の突出部27と接触しないように前記TSV構造物28の外郭平坦部と接触する形状を有する。前記導電性ライン36はバリア膜及び金属膜を含むことができ、前記バリア膜及び金属膜は、低抵抗及びシリコンの1.5倍程度の熱膨張係数を有する金属を含むことができる。前記金属は銅、アルミニウム、金、インジウム、ニッケルなどを含むことができる。

20

【0049】

前記第1金属間絶縁膜32及び導電性ライン36上に第2金属間絶縁膜38が備わることができる。前記第2金属間絶縁膜38を貫通して前記導電性ライン36と接続する第1上部配線40が備わることができる。これによって、第1上部配線40は導電性ライン36を接続させる接続構造物の例を形成する。

30

【0050】

図示はしていないが、前記第1上部配線40及び第2金属間絶縁膜38上に層間絶縁膜及び配線がさらに積層されることができる。

【0051】

図3～図10は一実施形態により図1に示した半導体素子を製造する方法を示す断面図である。

【0052】

図3を参照すると、第1基板10上に第1回路パターン12を形成する。前記第1回路パターン12はCMOSトランジスタ、ダイオードなどを含むことができる。また、前記第1基板10上に前記第1回路パターン12を覆う第1層間絶縁膜14を形成する。前記第1層間絶縁膜14を貫通する下部配線16を形成する。以後、前記第1層間絶縁膜14及び下部配線16上にエッチング阻止膜18を形成する。前記工程を遂行することによって、FEOL工程が完了される。

40

【0053】

図4を参照すると、前記エッチング阻止膜18上にフォトレジスト膜(図示せず)を形成し、前記フォトレジスト膜をパターニングしてフォトレジストパターンを形成する。前記フォトレジストパターンは約2～5μmの厚さを有することができる。前記フォトレジストパターンをエッチングマスクとして使って前記エッチング阻止膜18及び第1層間絶縁膜14をエッチングし、続けて第1基板10を乾式エッチングする。よって、前記第1

50

層間絶縁膜14及びエッチング阻止膜18を貫通して第1基板10内部まで延伸するピアホール20を形成する。前記ピアホール20は複数個が備わることができる。前記ピアホール20内には後続工程を通じてTSV構造物が形成される。前記ピアホール20を形成した後に、前記フォトレジストパターンを除去する。

【0054】

前記ピアホール20の内壁及びエッチング阻止膜18上に絶縁膜22を形成する。前記絶縁膜22はシリコン酸化物または炭素ドーピングされたシリコン酸化物から形成することができる。一例として、前記絶縁膜22はプラズマ酸化工程または化学気相蒸着工程を通じて形成することができ、ステップカバレッジ特性が優秀なTEOS膜、オゾンTEOS膜などから形成することができる。

10

【0055】

図5を参照すると、前記絶縁膜22上にバリア膜24を形成する。前記バリア膜24はTa、TaN、Ti、TiN、Ru、Co、Ni、NiB、WNなどの物質から形成することができ、これらは単独または2つ以上が積層されることができる。前記バリア膜24は100～3000の厚さで形成することができる。

【0056】

前記バリア膜24上に導電膜26を形成するための電極を提供するためにシード膜(図示せず)を形成する。一例として、前記シード膜は、物理気相蒸着法を通じて銅を蒸着させて形成することができる。

20

【0057】

前記シード膜上に前記ピアホール20内部を埋めるように導電膜26を形成する。前記導電膜26は低抵抗の金属物質から形成される。本実施形態において、前記導電膜26は電解めっき法、無電解めっき法、電子融合法(Electrografting)、物理気相蒸着法などによって銅を蒸着させて形成することができる。前記導電膜26を形成した後、前記導電膜26を熱処理する工程をさらに遂行することもできる。

20

【0058】

これとは異なる例として、前記導電膜26は銅以外にも低抵抗を有する他の金属を蒸着させて形成することもできる。前記導電膜26は第1基板10をなすシリコン物質との熱膨張係数の2倍以上の熱膨張係数を有する金属物質を蒸着させて形成することができる。具体的に、前記導電膜26はアルミニウム、金、インジウム、ニッケルなどからなることもある。しかし、前記導電膜26は半導体製造工程に適合し、低抵抗を有する銅から形成することが望ましい。

30

【0059】

図6を参照すると、前記導電膜26、バリア膜24、絶縁膜22、及びエッチング阻止膜18を、第1層間絶縁膜14が露出する時まで化学機械的研磨工程を通じて研磨する。これに伴い、導電パターン26a、バリア膜パターン24a及び絶縁膜パターン22aがピアホール20内に残留する。導電パターン26aとバリア膜パターン24aは、TSV構造物28を形成する。前記エッチング阻止膜18は完全にエッチングされることもでき、一部が厚さほど残っていることもできる。

30

【0060】

図7を参照すると、前記絶縁膜パターン22a、TSV構造物28、及び下部配線16を覆うバッファ膜30を第1層間絶縁膜14上に形成する。前記バッファ膜30は絶縁物質からなり、前記TSV構造物28に含まれる金属物質の拡散を抑制するために提供する。前記バッファ膜30はシリコン窒化物、シリコン炭素窒化物、SiCONなどから形成することができ、これらは単独または2つ以上を積層して形成することができる。前記バッファ膜30は300～1000の厚さで形成することができる。

40

【0061】

前記バッファ膜30及び第1層間絶縁膜14上に第1金属間絶縁膜32を形成する。前記第1金属間絶縁膜32はシリコン酸化物または炭素ドーピングされたシリコン酸化物から形成することができる。前記蒸着工程を遂行する間前記導電パターン26aが熱膨張し

50

て、前記導電パターン26aは中心部位が突出し、これによって、突出部27を有することになる。

【0062】

図8を参照すると、前記第1金属間絶縁膜32及びバッファ膜30の一部分をエッチングして前記TSV構造物28の上部のうち、少なくとも平坦な部分の一部と下部配線16を露出する第1開口34を形成する。前記第1開口34はライン形状を有しながら延伸する。前記第1開口34の底面に露出するTSV構造物28の上部面の面積は前記TSV構造物28の上部面の面積の5~80%になるようとする。

【0063】

本実施形態においては、一つの前記TSV構造物28上部面のうち、平坦な部分上に2つの第1開口34が互いに平行するように配置される。これによって、前記TSV構造物28の中心突出部27上にはバッファ膜30及び前記第1金属間絶縁膜32の部分が残ることになる。

【0064】

図9を参照すると、前記第1開口34の内部を埋めるバリア膜及び導電膜を、TSV構造物28、下部配線16、及び第1金属間絶縁膜32の露出した部分上に形成し、前記第1金属間絶縁膜32が露出するように前記導電膜及び前記バリア膜を化学機械的に研磨して第1開口34内に導電性ライン36を形成する。

【0065】

前記導電性ライン36は前記TSV構造物28の中心突出部27とは接触しない。前記導電パターン26aが突出する高さ及び突出する部位は前記ビアホール20の直径及び深さと関連する。

【0066】

即ち、前記ビアホール20が数千μm以下程度で直径及び深さが小さい場合、前記ビアホール20内に形成される前記導電パターン26aの体積が大きくなくて前記導電パターン26aが突出する体積も非常に小さい。例えば、数千μm以下の直径を有する下部配線16の場合には、下部配線16がバッファ膜30及び第1金属間絶縁膜32の形成期間の間、熱的にあまり膨張しない。

【0067】

しかし、TSV構造物28は半導体素子に含まれる他の配線に比べて非常に大きいサイズを有するので、バッファ膜30及び第1金属間絶縁膜32の形成期間の間にTSV構造物28は熱的に非常に膨張することになる。例えば、前記導電パターン26aが1~15μmの直径及び10~100μmの深さを有する場合には、前記導電パターン26aが熱膨張することによって前記導電パターン26aの中心部位が上へ突出することになる。

【0068】

バッファ膜30及び第1金属間絶縁膜32が形成される時、バリア膜パターン24aに接触する導電パターン26aは、物質の間の相対的に高い接着によってあまり膨張しない。従って、導電パターン26aの中心部のみが膨張して中心突出部27を形成する。

【0069】

前記導電パターン26aが15~50μmの直径を有する場合、前記導電パターン26aとバリア膜パターン24aとの間の接着力が低い。この場合、導電パターン26aは上部面の全面にかけて上へ突出することになる。

【0070】

図10を参照すると、前記導電性ライン36及び第1金属間絶縁膜32上に第2金属間絶縁膜38が形成される。第1上部配線40が第2金属間絶縁膜38を貫通して形成されて前記導電性ライン36と電気的に接続される。具体的に、前記第2金属間絶縁膜38に第2開口(図示せず)を形成し、前記第2開口にバリア膜及び導電物質を埋め込んで第1上部配線40を形成する。前記第1上部配線40は銅を含む。

【0071】

図示はしていないが、上述した説明と同一方法で、層間絶縁膜及び配線をさらに形成す

10

20

30

40

50

ることができる。これで、導電構造物の例として導電性ライン 3 6 が T S V 構造物 2 8 の上面の外郭平坦部上のみに形成され、中心突出部 2 7 上には形成されない。従って、導電性ライン 3 6 は最小の接触抵抗を有し、T S V 構造物 2 8 上に形成される。

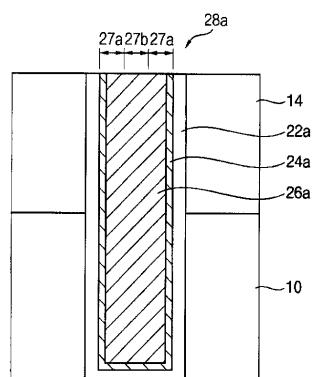

【 0 0 7 2 】

図 3 4 をさらに参照すると、本発明は絶縁膜パターン 2 2 a、バリア膜パターン 2 4 a、及び導電パターン 2 6 a と共に形成される T S V 構造物 2 8 a の他の例に適用することができる。図 3 4 を参照すると、T S V 構造物 2 8 a は T S V 構造物 2 8 a の上面の外郭部 2 7 a とともに平坦な中心部 2 7 b を有する。

【 0 0 7 3 】

図 3 4 において、T S V 構造物 2 8 a の上面の外郭部 2 7 a は絶縁膜パターン 2 2 a に近接して形成される。T S V 構造物 2 8 a 上面の中心部 2 7 b は外郭部 2 7 a によって囲まれる。図 3 5 を参照すると、導電性ライン 3 6 a は外郭部 2 7 a 上のみに形成され、中心部 2 7 b 上には形成されない。

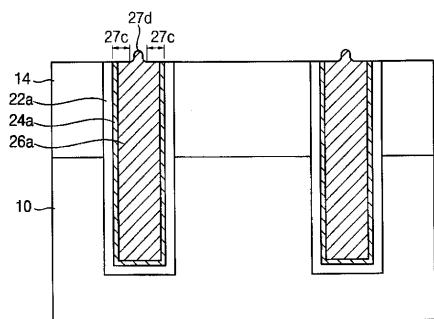

【 0 0 7 4 】

図 3 6 及び図 3 7 を参照すると、本発明はリング形状を有するリング型 T S V 構造物 2 8 b の実施形態にも適用される。図 3 7 は図 3 6 の I - I ' ラインに沿って切断した断面図である。T S V 構造物 2 8 b はビアホールをリング形状に埋める絶縁膜パターン 2 2 a、バリア膜パターン 2 4 a、及び導電パターン 2 6 a と共に形成される。

【 0 0 7 5 】

T S V 構造物 2 8 b は絶縁膜パターン 2 2 a に近接する T S V 構造物 2 8 a の上面の外郭部 2 7 c を有する。T S V 構造物 2 8 a の上面の中心部 2 7 d は外郭部 2 7 c によって囲まれ、リング形状の導電パターン 2 6 a の突出部を有する。図 3 6 及び図 3 7 の実施形態において、導電性ラインは外郭部 2 7 c の少なくとも一部上に形成され、リング型 T S V 構造物 2 8 b の中心突出部 2 7 d 上には形成されない。

【 0 0 7 6 】

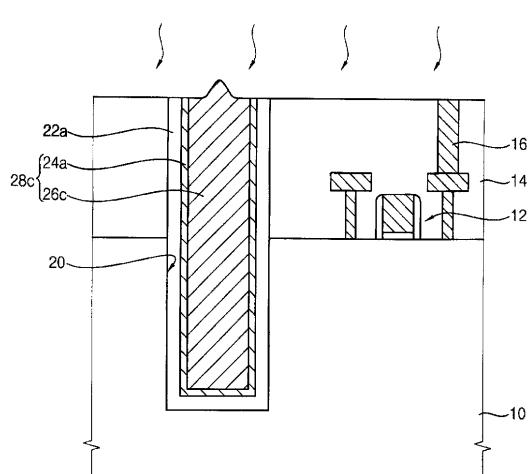

図 1 1 及び 1 2 は他の実施形態によって図 1 に示した半導体素子を製造する方法を示す断面図である。

【 0 0 7 7 】

以下にて説明する第 2 方法は、シリコン貫通ビアコンタクトの突出を抑制するために一部の工程がさらに追加されたことを除いては前記第 1 方法と同様である。従って、同一工程についての説明は省略する。

【 0 0 7 8 】

先に、図 3 ~ 図 6 を参照して説明した工程を遂行することによって、導電パターン 2 6 a 及びバリア膜パターン 2 4 a を有する T S V 構造物 2 8 を形成する。図 1 1 を参照すると、前記 T S V 構造物 2 8 が形成されている構造に対して熱処理工程を遂行することによって、前記 T S V 構造物 2 8 の上部面を人為的に突出させる。即ち、前記 T S V 構造物 2 8 に熱を加えて前記導電パターン 2 6 a の体積を膨張させて膨張した導電パターン 2 6 c を形成する。これによって、膨張した T S V 構造物 2 8 c が形成される。

【 0 0 7 9 】

前記熱処理工程が 1 0 0 以下で遂行される場合には、前記 T S V 構造物 2 8 を充分に熱膨張させることができない。また、前記熱処理工程が 6 0 0 以上で遂行される場合には、前記 T S V 構造物 2 8 が劣化されうる。従って、前記熱処理工程は 1 0 0 ~ 6 0 0 の温度で遂行されることが望ましい。

【 0 0 8 0 】

図 1 2 を参照すると、前記膨張した T S V 構造物 2 8 c の上部面が平坦になるように前記膨張した T S V 構造物 2 8 c を化学機械的に研磨する。前記研磨工程を通じて、平坦な上部面を有する T S V 構造物 2 8 が形成される。この時、前記 T S V 構造物 2 8 は熱処理工程を通じて充分に熱膨張されたので、後続して熱工程を通じてバッファ膜 3 0 及び第 1 金属間絶縁膜 3 2 を形成する時に突出する程度が非常に緩和されることがある。

【 0 0 8 1 】

10

20

30

40

50

続いて、図7～図10を参照して説明した工程を同一に遂行することによって、図10に示した半導体素子を製造することができる。

【0082】

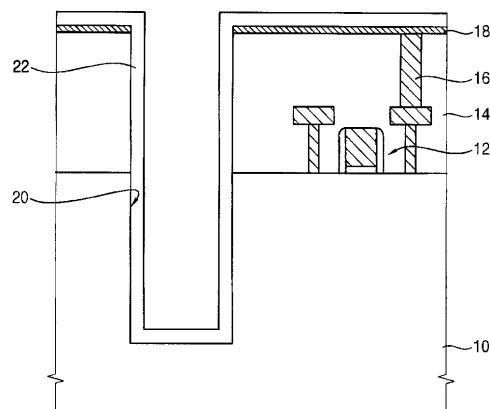

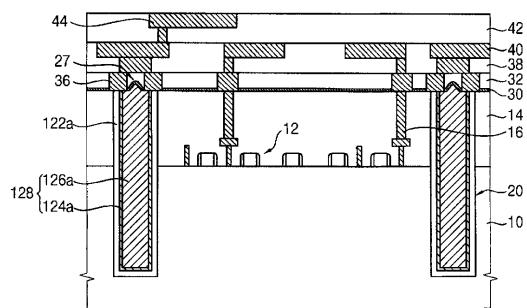

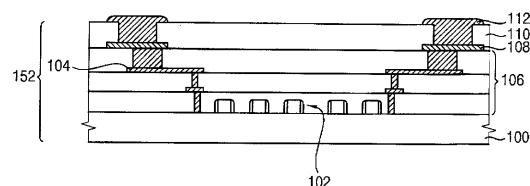

図13は本発明の一実施形態に係るTSV構造物を有する積層型半導体素子を示す断面図である。

【0083】

図13を参照すると、積層型半導体素子は第1集積回路チップ150、第2集積回路チップ152、はんだ50、及びコンタクト構造物112を含む。前記第1集積回路チップ150に含まれる素子はメモリ素子またはロジック素子でありうる。他の例として、前記第1集積回路チップ150に含まれる素子はイメージ素子でもある。

10

【0084】

TSV構造物128aの底面及び絶縁膜パターン122bの底面が第1基板10aの底面の外へ露出していることを除いては、第1集積回路チップ150は、図1に示した半導体素子と同じ構成を有することができる。図13のTSV構造物128a及び絶縁膜パターン122bは、図1及び図2のTSV構造物28及び絶縁膜パターン22aと類似するように形成される。

20

【0085】

これに加えて、最上部の第2配線44及び第3金属間絶縁膜42上には第1保護膜46が備わることができる。前記第1保護膜46を貫通してはんだ50が形成されることがある。

【0086】

前記第1集積回路チップ150は第1基板10a、第1回路パターン12、下部配線16、第1層間絶縁膜14、及び絶縁膜パターン122bを含む。第1集積回路チップ150はTSV構造物128a及び導電性ライン36を含む。前記TSV構造物128aは第1層間絶縁膜14及び第1基板10aを貫通して形成される。図1及び図2のように、導電性ライン36がTSV構造物128aの上面の外郭平坦部上に形成され、前記上面の中心突出部上には形成されない。前記導電性ライン36は第1金属間絶縁膜32に取り囲まれる。

【0087】

第1上部配線40及び第2上部配線44、並びに第2金属間絶縁膜38及び第3金属間絶縁膜42が、第1集積回路チップ150内に含まれる。また、前記第2上部配線44を覆う第1保護膜46が備わり、はんだ50は第1保護膜46を貫通して第2上部配線44に接触する。

30

【0088】

前記第1基板10aは単結晶シリコン基板でありうる。前記第1基板10aは10～100μmの厚さを有する。前記第1基板10aの底面がTSV構造物128aの底面と同じ平面に位置することができる。または、前記第1基板10a底面に比べて前記TSV構造物128aの底面が突出するように前記第1基板10aが位置することができる。

【0089】

以下においては、前記第1基板10aを貫通するTSV構造物128aを説明する。

40

【0090】

前記第1基板10aを貫通するピアホール20が備わる。前記ピアホール20の側壁には円筒形状の絶縁膜パターン122bが備わる。前記絶縁膜パターン122b上にはバリア膜パターン124b及びシードパターン(図示せず)が備わる。前記シードパターン上に前記ピアホール20の残りを埋める導電パターン126aが備わる。

【0091】

前記導電パターン126aは低抵抗を有しながら第1基板10aをなす物質との熱膨張係数の2倍以上の熱膨張係数を有する金属物質を含む。一例として、前記導電パターン126aは銅、アルミニウム、金、インジウム、ニッケルなどを含むことができる。本実施形態においては半導体工程に適合した銅を含む。

50

## 【0092】

前記 TSV 構造物 128a は、半導体チップでアドレスまたはチップイネーブルなどのような電気信号パッド、ピンパワーシグナルパッド、パワーアンプモジュールなどと連結して、第1集積回路 150 と第2集積回路チップ 152 との間の電気的信号を伝達することができる。第2金属間絶縁膜 38 及び第3金属間絶縁膜 42 が、第1金属間絶縁膜 32 上に次々と形成される。導電性ライン 36 並びに第1上部配線 40 及び第2上部配線 44 が絶縁膜 38、42 を貫通して形成される。

## 【0093】

前記第2上部配線 44 はパッド電極として使われることができ、これからは第1パッド電極 44 と言う。第2上部配線 44 をカバーする第1保護膜 46 が第3金属間絶縁膜 42 上に形成される。前記第1保護膜 46 は絶縁物質からなり、一例として、ポリイミド物質を含むことができる。

10

## 【0094】

前記第1パッド電極 44 と接触するはんだ 50 が備わることができる。図示はしていないが、前記はんだ 50 は印刷回路基板と接触することができる。これとは異なり、ワイヤーボンディングによって前記第1パッド電極 44 とリードフレームが電気的に連結されることができる。

## 【0095】

一方、第2集積回路チップ 152 は第2基板 100、前記第2基板 100 上に備わる第2回路パターン 102、配線 104、第2層間絶縁膜 106、第2パッド電極 108 を含む。

20

## 【0096】

前記第2集積回路チップ 152 に含まれた半導体素子は前記第1集積回路チップ 150 に含まれたものと同一の半導体素子であることもあり、互いに異なる半導体素子でもある。

## 【0097】

第2層間絶縁膜 106 上には配線 104 と接続される第2パッド電極 108 が備わる。前記第2パッド電極 108 は前記第1基板 10a の TSV 構造物 128a に電気的に接続されている。第2層間絶縁膜 106 及び第2パッド電極 108 上には第2保護膜 110 が備わる。前記第2保護膜 110 はポリイミド物質からなることができる。

30

## 【0098】

前記第1集積回路チップ 150 に含まれた TSV 構造物 128a と前記第2集積回路チップ 152 に含まれた第2パッド電極 108 との間には第2保護膜 110 を貫通して導電性を有するコンタクト構造物 112 が介在される。前記コンタクト構造物 112 で使われることのできる物質の例としては銀 (Ag) はんだペーストを挙げることができる。

## 【0099】

即ち、本実施形態に係る半導体素子は第1集積回路チップ 150 及び第2集積回路チップ 152 が積層された構造を有し、TSV 構造物 128a を通じて前記第1集積回路チップ 150 及び第2集積回路チップ 152 が電気的に接続される。また、本実施形態に係る積層型素子は TSV 構造物 128a と上部の導電性ライン 36 との間の接着特性が優れているため、信号伝達速度が速い。従って、半導体素子の電気的特性が良好、且つ高い信頼性を有する。

40

## 【0100】

図示はしていないが、第1集積回路チップと同一構造の TSV 構造物を含む 3 つ以上の集積回路チップが垂直に積層されることができる。

## 【0101】

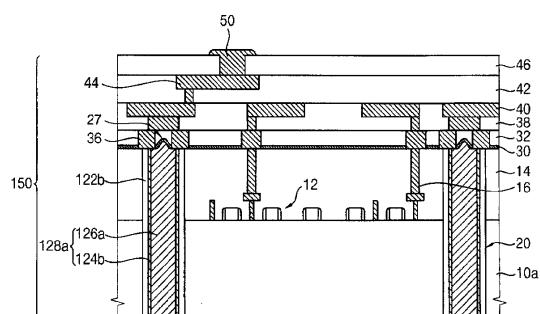

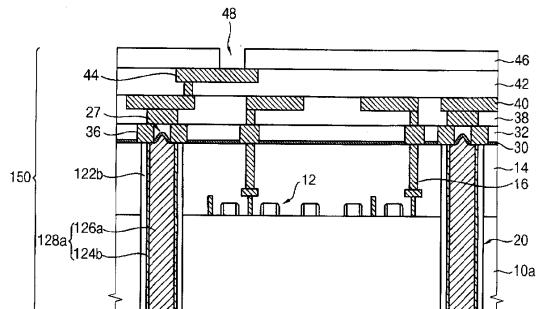

図 14 ~ 図 18 は、図 13 に示した積層型半導体素子の製造方法を示す断面図である。

## 【0102】

図 14 を参照すると、第1基板 10 上に第1回路パターン 12 を形成し、第1回路パターン 12 をカバーする第1層間絶縁膜 14 を第1基板 10 上に形成する。下部配線 16 が

50

第1層間絶縁膜14を貫通して形成される。

【0103】

第1層間絶縁膜14及び第1基板10がパターニングされて内部にピアホール20を形成する。絶縁膜パターン122aと、バリア膜パターン124a及び導電パターン126aを含むTSV構造物128が図6と類似するようにピアホール20内に形成される。導電パターン126aは図10と類似するように中心突出部27を有する。

【0104】

図15を参照すると、前記TSV構造物128及び第1層間絶縁膜14上にバッファ膜30を形成する。前記バッファ膜30上に第1金属間絶縁膜32を形成する。前記第1金属間絶縁膜32及びバッファ膜30を貫通して導電性ライン36を形成し、TSV構造物128の外郭平坦部と電気的に接続され、下部配線16上に形成される。

10

【0105】

前記導電性ライン36は、図10と類似するように、TSV構造物128の突出部27とは接触しないように形成される。図7～図10と類似するように、前記導電性ライン36及び第1金属間絶縁膜32上に第2金属間絶縁膜38及び第3金属間絶縁膜42、並びに第1上部配線40及び第2上部配線44を形成する。

【0106】

図16を参照すると、第1保護膜46が第3金属間絶縁膜42上に形成されて第2上部配線44をカバーする。前記第1保護膜46はポリイミド物質を含むことができる。前記第1保護膜46の一部分を除去して第2上部配線44を露出させる第3開口48を形成する。

20

【0107】

前記第1基板10、絶縁膜パターン122a、バリア膜パターン124a、及び導電パターン126aの底面をグラインディングを通じて除去して、前記導電パターン126aの底面を露出させる。前記工程を通して、第1基板10の厚さが減少する。残留する導電パターン126a及びバリア膜パターン124bはTSV構造物128aを定義する。絶縁膜パターン122bはピアホール内のTSV構造物128aを取り囲む。

【0108】

前記グラインディング工程を通して、導電パターン126aの底面が第1基板10aの底面と同一平面上に置かれることになる。しかし、本発明は導電パターン126aの底面が第1基板10aの底面から突出した実施形態にも適用される。

30

【0109】

絶縁膜パターン122bはピアホール20側壁上にシリンドラ形状を有する。バリア膜パターン124bは絶縁膜パターン122bの側壁上にシリンドラ形状を有する。バリア膜パターン124bは導電パターン126aを囲む。

【0110】

図17を参照すると、前記第1保護膜46に形成された第3開口48内にはんだ50を形成する。これで、TSV構造物128aを含む第1集積回路チップ150が完成される。

。

【0111】

図18を参照すると、第2基板100上に前記第1集積回路チップ150と接合するための第2集積回路チップ152を形成する。具体的に、前記第2基板100上に第2回路パターン102、配線104及び第2層間絶縁膜106を形成する。前記第2層間絶縁膜106上に前記配線104と電気的に接続する第2パッド電極108を形成する。前記第2パッド電極108は前記第1基板10aに形成されたTSV構造物128aと各々対向するように配置される。

40

【0112】

前記第2パッド電極108をカバーする第2保護膜110が第2層間絶縁膜106上に形成される。次に、第2保護膜110をパターニングして、第2パッド電極108を露出させる第4開口(図示せず)を形成する。コンタクト構造物112が前記第4開口内に形

50

成されて第2パット電極108に電気的に接続する。

【0113】

また、図13を参照すると、第1基板10aのTSV構造物128aの底面と第2基板100のコンタクト構造物112が互いに圧搾して第1集積回路チップ150及び第2集積回路チップ152を含む積層型半導体素子が完成される。

【0114】

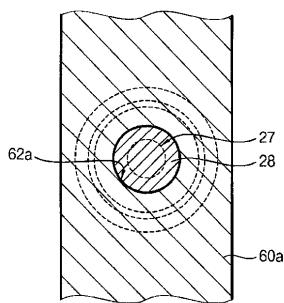

図19及び図20は各々本発明の一実施形態に係るビア構造物上に形成された開口を有する導電構造物を説明するための平面図である。

【0115】

以下にて説明する半導体素子は導電性ライン構造物の形状を除いては図1及び図2に示した半導体素子と同一である。

【0116】

図19及び図20を参照すると、第1導電性ライン60a及び第2導電性ライン60bは、TSV構造物28の中心突出部27を露出する第1開口62a及び第2開口62bを含む。

【0117】

開口62a、62bの大きさは突出部27の大きさに依存する。第1開口62aは突出部27の大きさより大きく、TSV構造物28の大きさより小さい。第2開口62bは突出部27の大きさより大きく、導電性ライン60b方向に沿って延伸する。第2開口62bもやはりバリア膜パターン24a、絶縁膜パターン22a、及び第1層間絶縁膜14の上面の部分を露出させる。

【0118】

いかなる場合でも、各導電性ライン60a、60bは、TSV構造物28上面の5~80%で接触する。

【0119】

図19及び図20に示した半導体素子は、図3~図8を参照して説明したことと同じ工程を遂行して形成される。ただし、第1開口34が形成される位置が異なる。次に、前記図9及び図10を参照で説明したのと同じ工程を遂行する。これで、図19及び図20の半導体素子を製造する。

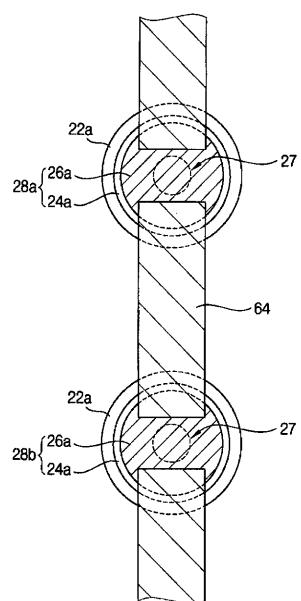

【0120】

図21及び図22は本発明の一実施形態に係る複合ビア構造物上に形成された複合導電構造物を説明するための平面図である。

【0121】

以下において説明する半導体素子はTSV構造物上に形成される導電性ラインの形状を除いては図1及び図2に示した半導体素子と同一である。

【0122】

図21を参照すると、複合TSV構造物28a、28b上に一方向に延伸する導電性ライン64は、前記方向に沿って二つに分離される。導電性ライン64の各部分はTSV構造物28a、28b中、少なくとも一つの上面のうち外郭平坦部に接触する。導電性ライン64の前記の部分はTSV構造物28a、28bによって電気的に接続される。

【0123】

例示的な実施形態によると、導電性ライン64は三部分に分離される。導電性ライン64の一部分は両TSV構造物28a、28bの上面の外郭平坦部に接触する。導電性ライン64の他の部分は第1TSV構造物28aの上面の外郭平坦部に接触し、導電性ライン64のまた他の部分は第2TSV構造物28bの上面の外郭平坦部に接触する。

【0124】

導電性ライン64の前記部分はTSV構造物28a、28bの全体上面の5~80%で接触する。

【0125】

図21に示した半導体素子は、図3~図10を参照して説明したのと同一工程を通して

10

20

30

40

50

形成することができる。ただし、第1開口34の位置と形状のみが異なる。

【0126】

図22は本発明の一実施形態に係る半導体素子の平面図である。

【0127】

図22に示した半導体素子は導電性ラインが追加的にさらに備わることを除いては、図1及び図2の半導体素子と同一構造を有する。

【0128】

図22を参照すると、二つの導電性ライン36がTSV構造物28の上面の外郭平坦部の第1部分に接触する。第2導電性ライン37はTSV構造物28の中心部上で第1導電性ライン36間に平行するように延伸する二部分を含む。第2導電性ライン37の前記部分は第1導電性ライン36間にTSV構造物28の上面の外郭平坦部の部分に接触する。

10

【0129】

図22に示した半導体素子は、図3～図10を参照して説明したのと同一工程を通して形成されることができる。ただし、第1開口34が形成される位置と形状が異なる。

【0130】

図23は本発明の一実施形態に係る半導体素子内のピア構造物上に形成された追加導電構造物を含む断面図である。

【0131】

以下において説明する半導体素子は、図1、図19、図20、図21、及び図22のように、導電性ライン36がTSV構造物28の外郭平坦部上で形成される。

20

【0132】

図23を参照すると、第1金属間絶縁膜32が導電性ライン構造物36を囲む。第2金属間絶縁膜38が第1金属間絶縁膜32及び導電性ライン構造物36上に形成される。上部配線40が第2金属間絶縁膜38を貫通して形成され、各々は上部導電性ライン40a及び上部コンタクト40bを含む。上部配線40は、図23のTSV構造物28の突出部27をオーバーラップしないように形成する。

【0133】

TSV構造物28の突出部27上に形成された第2金属間絶縁膜38部分は平坦でないこともある。従って、上部配線40は突出部27にオーバーラップされないように形成して平坦に形成することができる。

30

【0134】

図23に示した半導体素子は図3～図10を参照して説明したのと同一工程を通じて形成されることができる。ただし、上部配線40の位置のみが異なる。

【0135】

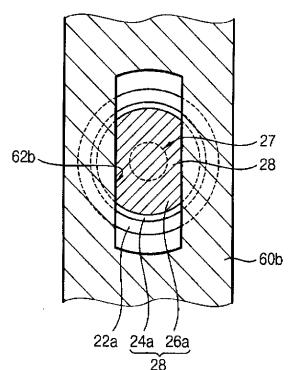

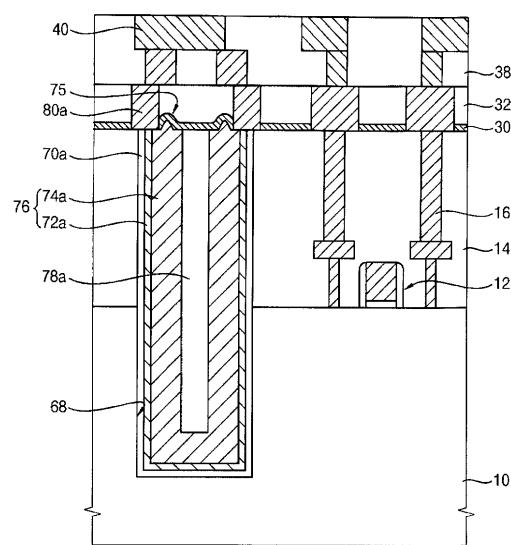

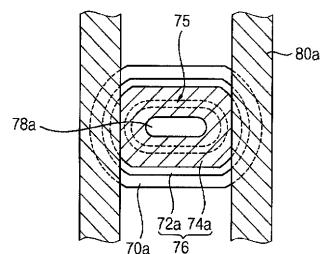

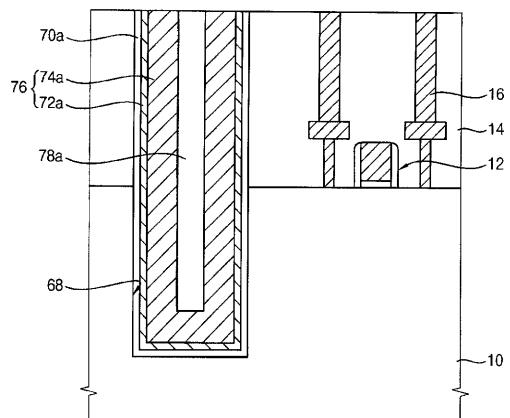

図24及び図25は本発明の一実施形態に係る中心充填部を有するピア構造物を含む半導体素子の断面図である。

【0136】

図24及び図25を参照すると、第1基板10上に第1回路パターン12が備わる。前記第1回路パターン12はトランジスタ、ダイオードなどを含むことができる。

【0137】

前記第1基板10上には前記第1回路パターン12を覆う第1層間絶縁膜14が備わる。下部配線16が第1層間絶縁膜14を貫通して第1回路パターン12に接続される。ピアホール68が第1層間絶縁膜14及び第1基板10の少なくとも一部を貫通して形成される。前記ピアホール68は橢円形状を有することができる。

40

【0138】

前記ピアホール68の内壁上に絶縁膜パターン70aが備わる。前記絶縁膜パターン70a上にはバリア膜パターン72aが備わる。前記バリア膜パターン72aは、Ta、TaN、Ti、TiN、Ru、Co、Ni、NiB、WNなどの物質から形成することができる。これらは単独または2つ以上を積層して使うことができる。

【0139】

10

20

30

40

50

前記バリア膜パターン72a上には前記ビアホール68の残りを埋める導電パターン74aが備わる。導電パターン74aは中心充填部78aを取り囲むカップ形状を有する。前記導電パターン74aは低抵抗を有し、第1基板10をなすシリコンの熱膨張係数の2倍以上の熱膨張係数を有する金属からなることができる。前記導電パターン74aは銅(Cu)、アルミニウム、金、インジウム、ニッケルなどからなることができる。本実施形態では前記導電パターン74aは半導体製造工程に最も適合して低抵抗を有する銅を含むことができる。導電パターン74a及びバリア膜パターン72aはTSV構造物76を定義する。

【0140】

中心充填部78aは前記ビアホール68の中心に形成される。前記中心充填部78aは絶縁物質または導電物質からなることができる。一例として、前記中心充填部78aはスピノングラス(SOG)系列の酸化物、フロアブルシリコン(Flowable Si)、チタニウム、アルミニウム、多孔質物質(porous material)等を挙げることができる。

【0141】

いかなる場合でも、中心充填部78aの物質は、導電パターン74a物質の熱膨張係数より3~4倍低い熱膨張係数を有する。例えば、導電パターン74aは、17PPMの熱膨張係数を有する銅を含むことができる。この場合、中心充填部78aは、3~4PPMの低い熱膨張係数を有する物質を含むことができる。

【0142】

導電パターン74aはカップ形状の導電パターン74aの上面中心部についてリング形状を有する突出部75を含む。中心充填部78a及び絶縁パターン70aに隣接するように配置される導電パターン74a上面の外郭部は第1層間絶縁膜14の上面と同一平面に位置することができる。

【0143】

TSV構造物76及び第1層間絶縁膜14上部面を覆うバッファ膜30が備わる。複数の導電性ライン80aが形成されてTSV構造物76上面の外郭平坦部と接触し、または第1金属間絶縁膜32及びバッファ膜30を貫通して下部配線16と接触する。導電性ライン80aは突出部75上に形成されず、これと接触することもない。

【0144】

二つの平行した導電性ライン80aがTSV構造物76の上面の外郭平坦部に接触する。これとは異なり、二個以上の導電性ライン80aがTSV構造物76の上面の平坦部に接触するように形成されることもできる。いかなる場合でも、導電性ライン80aは形成されてTSV構造物76の全体上面の5~80%で接触する。

【0145】

前記導電性ライン80aはバリア膜及び低抵抗を有する金属を含む導電膜を含む。前記金属は半導体製造工程に適合しながら低抵抗を有する銅を含むことができる。

【0146】

前記第1金属間絶縁膜32上に第2金属間絶縁膜38が備わることができる。前記第2金属間絶縁膜38を貫通して前記導電性ライン80aと接続する上部配線40が備わることができる。これによって、上部配線40は導電性ライン80aに電気的に接続される接続構造物を形成することができる。図示はしていないが、前記第1上部配線40及び第2金属間絶縁膜38上に層間絶縁膜及び配線がさらに積層されることができる。

【0147】

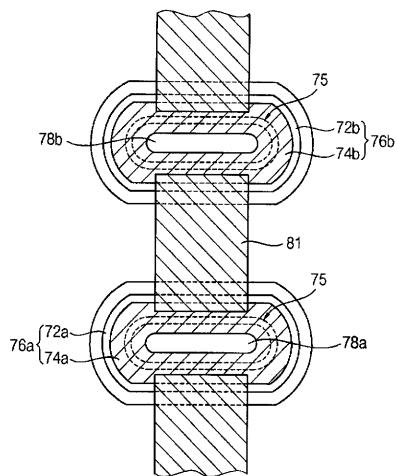

図26及び図27は、図24及び図25に示した半導体素子を製造する方法を示す断面図である。

【0148】

先に、図3及び図4を参照して説明したのと同一工程を遂行して、第1層間絶縁膜14にビアホール68及び絶縁膜70を形成する。この時、前記ビアホール68の上部面は円または楕円形状を有することができる。絶縁膜70はビアホール68の内壁上に形成され

10

20

30

40

50

、また、第1層間絶縁膜14及び下部配線16上に形成されたエッチング阻止膜18上にも形成される。

【0149】

図26を参照すると、前記絶縁膜70上にバリア膜72を形成する。前記バリア膜72上に導電膜74を形成する。前記導電膜74は低抵抗を有し、第1基板10をなすシリコンの熱膨張係数の2倍以上の熱膨張係数を有する金属からなることができる。前記導電膜74は銅(Cu)、アルミニウム、金、インジウム、ニッケルなどからなることができる。本実施形態においては前記導電膜74は半導体製造工程に最も適合し、且つ低抵抗を有する銅を含むことができる。

【0150】

前記導電膜74上に前記ビアホール68の残りを埋める中心充填膜78を形成する。前記中心充填膜78はスピンドルガラス(SOG)系列の酸化物、フロアブルシリコン(Flowable Si)、チタニウム、アルミニウム、多孔質物質(porous material)等を挙げることができる。一実施形態によると、導電膜74は17PPMの熱膨張係数を有する銅を含む。この場合、中心充填膜78は、3~4PPMの低い熱膨張係数を有する物質を含むことができる。従って、中心充填膜78は導電膜74の熱膨張を緩衝して、リング形状の突出部75の高さを最小化する。

【0151】

図27を参照すると、前記第1層間絶縁膜14の上部面が露出されるように前記中心充填膜78、導電膜74、バリア膜72、絶縁膜70及びエッチング阻止膜18を研磨する。これによって、TSV構造物76がビアホール68内に形成される。続いて、図7~図10を参照して説明した工程を遂行する。それによって、図24に示した半導体素子を製造することができる。

【0152】

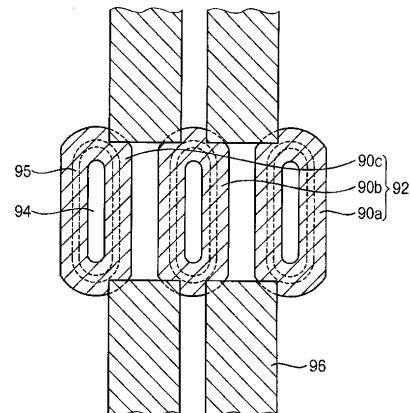

図28~図30は本発明の一実施形態に係る複合ビア構造物上に形成された複合導電構造物を有する半導体素子の平面図である。

【0153】

以下にて説明する半導体素子は、カップ形状で形成されたTSV構造物76a、76bが中心充填膜78a、78bを各々取り囲むことを除けば、図21に示した半導体素子と同一である。

【0154】

図28を参照すると、導電性ライン81は複数個に分離し、複数個のTSV構造物76a、76bに沿って延伸する。各TSV構造物76a、76bは図27と類似するように形成する。導電性ライン81の各部分はTSV構造物76a、76bのうち、少なくとも一つの外郭平坦部に接触する。前記導電性ライン81の部分はTSV構造物76a、76bにより電気的に接続される。

【0155】

図28に示した実施形態において、導電性ライン81は三部分に分けられる。導電性ライン81の一部分は、TSV構造物76a、76bの上面の外郭平坦面部分に接触する。導電性ライン81の他の部分は、第1TSV構造物76aの上面の外郭平坦面の一部に接触し、導電性ライン81のまた他の部分は、第2TSV構造物76bの上面の外郭平坦面の一部に接触する。

【0156】

第1TSV構造物76aは、第1導電パターン74a及び第1バリア膜パターン72aを含む。第2TSV構造物76bは、第2導電パターン74b及び第2バリア膜パターン72bを含む。各第1導電パターン74a及び第2導電パターン74bは、リング形状の中心突出部75を有する。

【0157】

第1中心充填部78aは、第1導電パターン74aによって取り囲まれて、第2中心充填部78bは第2導電パターン74bによって取り囲まれる。

10

20

30

40

50

## 【0158】

図28に示した半導体素子は図26及び図27を参照して説明したのと同一工程を通じて形成することができる。ただし、導電性ライン構造物81の位置と形状のみが異なる。

## 【0159】

図29は本発明の一実施形態に係る半導体素子の平面図である。図29においては説明の便宜のために、TSV構造物及び導電性ラインのみを図示し、残りの部材は図24に示したものと類似している。

## 【0160】

図29を参照すると、輪状の導電パターンを含むTSV構造物90a、90b、90cが備わる。前記TSV構造物90a、90b、90cは図24に示したTSV構造物76と同一形状を有する。

10

## 【0161】

本実施形態において、三つのTSV構造物90a、90b、90cはより大きい一つのTSV構造物92を形成することができる。即ち、直径が非常に広い一つのTSV構造物が要求される素子の場合、直径が非常に広い一つのTSV構造物を形成することが容易ではない。従って、狭い直径を有する複数のTSV構造物90a、90b、90cが実質的には一つのTSV構造物92の機能をするように提供する。相対的に小さい直径を有する各TSV構造物90a、90b、90cは最小化した突出部の高さを有する。

## 【0162】

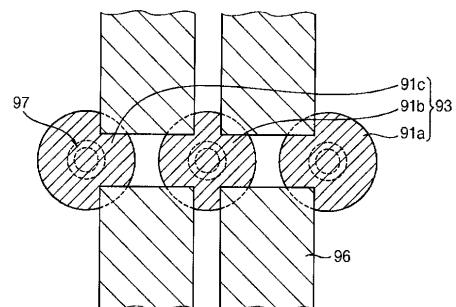

前記各TSV構造物90a、90b、90cは、各中心充填部94を取り囲んで、輪(annular)状の突出部95を有する。各導電性ライン構造物96は、TSV構造物90a、90b、90cのうち、少なくとも二つを含む各セットの上面の外郭平坦部に接触する。各導電性ライン構造物96は、TSV構造物90a、90b、90cの突出部95には接触しない。

20

## 【0163】

前記導電性ライン96は図29に示したように、互いに平行するように延長し、複数個の部分に分離する。導電性ライン96の前記の部分はTSV構造物92によって電気的に接続する。導電性ライン92はTSV構造物90a、90b、90cの全体上面の5~80%で接触する。

## 【0164】

30

図30は本発明の一実施形態に係る半導体素子の平面図である。説明の便宜のために図30にはTSV構造物及び導電性ラインだけが図示されている。しかし、図24と類似する追加構造物が図30の半導体素子のためにさらに形成されることもできる。一方、以下にて説明する半導体素子はTSV構造物93の形状を除いては図29に示した半導体素子と同一である。

## 【0165】

図30を参照すると、各TSV構造物91a、91b、91cは、図1に示したTSV構造物28と同じ形状を有する。本実施形態において、互いに隣接する複数のTSV構造物91a、91b、91cは、より大きい一つであるTSV構造物93を定義する。各TSV構造物91a、91b、91cは中心突出部97を含む。

40

## 【0166】

複数の導電性ライン構造物96がTSV構造物91a、91b、91cのうち、少なくとも二つを含むセットの外郭平坦部の部分上に形成されて接触する。導電性ライン96はTSV構造物91a、91b、91cの突出部97に接触しない。導電性ライン96は形成されてTSV構造物91a、91b、91cの間のラインに沿って延伸して互いに平行する。

## 【0167】

導電性ライン96は複数個の部分に分離され、各部分はTSV構造物91a、91b、91cのうち、少なくとも二つを含むセットの外郭平坦部の部分上に形成して接触する。導電性ライン96の前記の部分はTSV構造物93によって電気的に接続される。導電性

50

ライン 9 6 は T S V 構造物 9 1 a、9 1 b、9 1 c の全体上面の 5 ~ 8 0 % で接触する。図 2 8 ~ 図 3 0 の半導体素子において、上部配線（図示せず）もやはり導電性ラインの部分（8 1 或いは 9 6 ）を互いに接続する接続構造物として形成することが可能である。

【 0 1 6 8 】

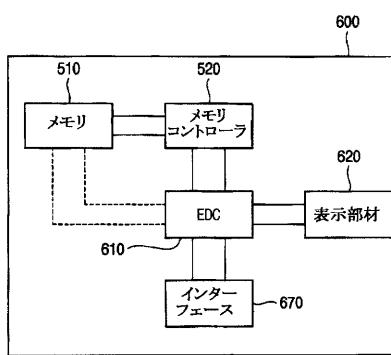

図 3 1 ~ 図 3 3 は本発明の一実施形態に係る各積層半導体素子を有するシステムのプロックダイアグラムである。

【 0 1 6 9 】

図 3 1 は例えば、図 1 3 に示した積層型半導体素子を有するシステムのプロックダイアグラムである。

【 0 1 7 0 】

図 3 1 を参照すると、システムはコントローラ 5 2 0 及びメモリ 5 1 0 を含む。メモリ 5 1 0 は例えば、図 1 3 に示した積層型メモリ素子を含む。前記メモリコントローラ 5 2 0 は、前記メモリの動作をコントロールするための入力信号を提供する。

【 0 1 7 1 】

図 3 2 は例えば、図 1 3 に示した積層型半導体素子を有するシステムのプロックダイアグラムである。

【 0 1 7 2 】

図 3 2 を参照すると、システムはホスト 7 0 0 及びメモリ 5 1 0 を含む。前記メモリ 5 1 0 は例えば、図 1 3 に示した積層型メモリ素子を含む。

【 0 1 7 3 】

前記ホスト 7 0 0 はパーソナルコンピュータ、カメラ、モバイル機器、ゲーム機、通信機器などのような電子製品を含む。前記ホスト 7 0 0 はメモリ 5 1 0 を調節して作動させるための入力信号を印加し、前記メモリ 5 1 0 はデータ保存媒体として使われる。

【 0 1 7 4 】

図 3 3 は例えば、図 1 3 に示した積層型半導体素子を有するシステム 6 0 0 のプロックダイアグラムである。

【 0 1 7 5 】

図 3 3 を参照すると、前記システムは携帯用装置 6 0 0 であることができる。携帯用装置 6 0 0 は M P 3 プレーヤ、ビデオプレーヤ、ビデオとオーディオプレーヤの複合器などであることができる。携帯用装置 6 0 0 は例えば、図 1 3 に示した積層型メモリ素子のようなメモリ 5 1 0 を含む。

【 0 1 7 6 】

図示したように、携帯用装置 6 0 0 はメモリ 5 1 0 、メモリコントローラ 5 2 0 、エンコーダ / デコーダ ( E D C ) 6 1 0 、表示部材 6 2 0 、及びインターフェース 6 7 0 を含むことができる。データ（オーディオ、ビデオなど）はエンコーダ / デコーダ ( E D C ) 6 1 0 によって前記メモリコントローラ 5 2 0 を経由して前記メモリ 5 1 0 から入 / 出力される。

【 0 1 7 7 】

エンコーダ / デコーダ ( E D C ) 6 1 0 は M P 3 プレーヤ或いは P M P プレーヤのようなメモリ 5 1 0 に保存されるオーディオ及び / または、ビデオデータをエンコーディングする方法等を通じてメモリ 5 1 0 に保存されるデータをエンコーディングする。さらに、エンコーダ / デコーダ ( E D C ) 6 1 0 は、メモリ 5 1 0 内にビデオデータを保存するための M P E G エンコーディングを行う。さらに、エンコーダ / デコーダ ( E D C ) 6 1 0 は複合エンコーダを含んでフォーマットにより互いに異なる類型のデータをエンコーディングする。例えば、エンコーダ / デコーダ ( E D C ) 6 1 0 はオーディオデータをエンコーディングするための M P 3 エンコーダ或いはビデオデータをエンコーディングするための M P E G エンコーダを含む。

【 0 1 7 8 】

エンコーダ / デコーダ ( E D C ) 6 1 0 は、 M P 3 プレーヤ或いは P M P プレーヤのようなメモリ 5 1 0 から M P 3 デコーディング或いは M P E G デコーディングする方法等を

10

20

30

40

50

通じてメモリ510から出力されたデータをデコーディングする。さらに、エンコーダ/デコーダ(EDC)610は複合デコーダを含んで、フォーマットにより互いに異なる類型のデータをデコーディングする。例えば、エンコーダ/デコーダ(EDC)610はオーディオデータをデコーディングするためのMP3デコーダ或いはビデオデータをデコーディングするためのMPEGデコーダを含む。

【0179】

他の実施形態によると、エンコーダ/デコーダ(EDC)610はデコーダのみを含む。例えば、エンコーディングしたデータはエンコーダ/デコーダ(EDC)610で入力され、以後、エンコーダ/デコーダ(EDC)610はメモリコントローラ520或いはメモリ510に伝送するために前記入力データをデコーディングすることができる。

10

【0180】

エンコーダ/デコーダ(EDC)610は、エンコーディングされるデータ或いはインターフェース670を通じてエンコーディングされるデータを受信することができる。インターフェース670は、確立されたインターフェース標準(例えば、FireWire、USBなど)にコンパイルしてFireWireインターフェース、USBインターフェースなどを含む。従って、データはインターフェース670を通じてメモリ510から出力されることができる。

【0181】

表示部材620はメモリ510から出力されてエンコーダ/デコーダ(EDC)610によりデコーディングされた使用者データを表示する。表示部材620の例として、オーディオデータを出力するスピーカー、ビデオデータを出力するディスプレースクリーンなどを挙げることができる。

20

【0182】

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特徴請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

【符号の説明】

【0183】

30

- 10 第1基板

- 12 第1回路パターン

- 14 第1層間絶縁膜

- 16 下部配線

- 18 エッチング阻止膜

- 20 ピアホール

- 22 絶縁膜

- 22a 絶縁膜パターン

- 24 バリア膜

- 24a バリア膜パターン

- 26 導電膜

- 26a 導電パターン

- 27 突出部

- 28 TSV構造物

- 30 パッファ膜

- 32 第1金属間絶縁膜

- 36 導電性ライン

- 38 第2金属間絶縁膜

- 40 第1上部配線

- 150 第1集積回路チップ

40

50

1 5 2 第2集積回路チップ

1 1 2 コンタクト構造物

4 2 第3金属間絶縁膜

4 4 第2上部配線

4 6 第1保護膜

5 0 はんだ

1 0 0 第2基板

1 0 2 第2回路パターン

1 0 4 配線

1 0 6 第2層間絶縁膜

1 0 8 第2パッド電極

1 1 0 第2保護膜

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【 図 9 】

【図10】

【 図 1 1 】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

【図18】

【図19】

【図21】

【図20】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図34】

【図33】

【図35】

【図3 6】

【図3 7】

## フロントページの続き

(51) Int.Cl. F I

H 01 L 25/065 (2006.01)

H 01 L 25/07 (2006.01)

H 01 L 25/18 (2006.01)

H 01 L 27/10 (2006.01)

(72) 発明者 朴 炳律

大韓民国ソウル特別市江南区閑浦洞（番地なし） 大峙アパート218棟108号

(72) 発明者 林 東燦

大韓民国京畿道水原市靈通区靈通洞（番地なし） ビヨッチョクゴルロッテアパート943棟1005号

(72) 発明者 鄭 德泳

大韓民国ソウル特別市龍山区二村洞203-65番地

(72) 発明者 崔 吉鉉

大韓民国ソウル特別市江南区大峙1洞（番地なし） チョンシルアパート15棟802号

(72) 発明者 ペ 大録

大韓民国ソウル特別市松坡区蚕室4洞（番地なし） パークリオアパート212棟2903号

(72) 発明者 姜 泌圭

大韓民国京畿道安養市東安区達安洞（番地なし） セピヨル漢陽アパート610棟1209号

審査官 河合 俊英

(56) 参考文献 特開2005-150299 (JP, A)

国際公開第2007/023947 (WO, A1)

特開平10-223833 (JP, A)

米国特許第06809421 (US, B1)

特開2007-123857 (JP, A)

米国特許出願公開第2007/0069364 (US, A1)

特開2011-228419 (JP, A)

米国特許出願公開第2011/0254165 (US, A1)

特開2004-356617 (JP, A)

米国特許出願公開第2005/0001326 (US, A1)

特開2001-068618 (JP, A)

(58) 調査した分野(Int.Cl., DB名)

H 01 L 21/3205

H 01 L 21/768

H 01 L 21/822

H 01 L 23/522

H 01 L 25/065

H 01 L 25/07

H 01 L 25/18

H 01 L 27/04

H 01 L 27/10