(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-86322

(P2006-86322A)

(43) 公開日 平成18年3月30日(2006.3.30)

| (51) Int.CI.             | F 1 | HO 1 L 27/105 (2006.01)  | HO 1 L 27/10  | 4 4 7   | 5 F 0 0 4 | テーマコード (参考) |

|--------------------------|-----|--------------------------|---------------|---------|-----------|-------------|

| HO 1 L 21/8246 (2006.01) |     | HO 1 L 21/8246 (2006.01) | HO 1 L 43/08  | P       | 5 F 0 4 3 |             |

| HO 1 L 43/08 (2006.01)   |     | HO 1 L 43/08 (2006.01)   | HO 1 L 43/08  | Z       | 5 F 0 8 3 |             |

| HO 1 L 43/12 (2006.01)   |     | HO 1 L 43/12 (2006.01)   | HO 1 L 43/12  |         |           |             |

| HO 1 L 21/3065 (2006.01) |     | HO 1 L 21/3065 (2006.01) | HO 1 L 21/302 | 1 0 5 A |           |             |

審査請求 未請求 請求項の数 8 O L (全 15 頁) 最終頁に続く

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2004-269273 (P2004-269273) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号 |

| (22) 出願日  | 平成16年9月16日 (2004.9.16)       | (74) 代理人 | 100089233<br>弁理士 吉田 茂明                          |

|           |                              | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                          |

|           |                              | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                          |

|           |                              | (72) 発明者 | 古田 陽雄<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内       |

|           |                              | (72) 発明者 | 上野 修一<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内       |

最終頁に続く

(54) 【発明の名称】磁気抵抗記憶素子およびその製造方法

## (57) 【要約】

【課題】歩留まりを向上させることが可能な磁気抵抗記憶素子およびその製造方法を提供する。

【解決手段】TMR素子60aは、磁性膜からなるピン層65、非磁性絶縁膜からなるトンネル絶縁層66および磁性膜からなるフリー層67をこの順に堆積した構成からなる。TMR素子60aは、それぞれ同一平面形状を有するピン層65、トンネル絶縁層66およびフリー層67において、トンネル絶縁層66の側壁に切れ込みを形成したサイドエッチ構造を有している。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

下部磁性層および上部磁性層並びに前記下部磁性層と前記上部磁性層との間に挟まれた非磁性絶縁膜を有する磁気抵抗記憶素子であって、

前記非磁性絶縁膜の側壁に第一の切れ込みを形成したことと特徴とする磁気抵抗記憶素子。

**【請求項 2】**

請求項 1 に記載の磁気抵抗記憶素子であって、

前記下部磁性層の側壁の上部に前記第一の切れ込みに連なる第二の切れ込みを形成したことと特徴とする磁気抵抗記憶素子。

10

**【請求項 3】**

請求項 2 に記載の磁気抵抗記憶素子であって、

前記上部磁性層の側壁の下部に前記第一の切れ込みに連なる第三の切れ込みを形成したことと特徴とする磁気抵抗記憶素子。

**【請求項 4】**

請求項 1 乃至請求項 3 のいずれかに記載の磁気抵抗記憶素子であって、

前記第一の切れ込みの長さは、前記下部磁性層又は前記上部磁性層の長さの 5 ~ 10 % である

ことを特徴とする磁気抵抗記憶素子。

**【請求項 5】**

請求項 1 に記載の磁気抵抗記憶素子の製造方法であって、

前記第一の切れ込みを形成するために、

CO と NH<sub>3</sub> とを含むガスを用いたスパッタによる異方性エッティングを行うことを特徴とする磁気抵抗記憶素子の製造方法。

20

**【請求項 6】**

請求項 2 に記載の磁気抵抗記憶素子の製造方法であって、

前記第一及び第二の切れ込みを形成するために、

Cl と Ar と O とを含むガスを用いたスパッタによる異方性エッティングをオーバーエッチになるように行う

ことを特徴とする磁気抵抗記憶素子の製造方法。

30

**【請求項 7】**

請求項 5 又は請求項 6 に記載の磁気抵抗記憶素子の製造方法であって、

前記異方性エッティングを行った後にウェットエッティングを行う

ことを特徴とする磁気抵抗記憶素子の製造方法。

**【請求項 8】**

請求項 3 に記載の磁気抵抗記憶素子の製造方法であって、

前記第一乃至第三の切れ込みを形成するために、

CO と NH<sub>3</sub> とを含むガス又は Cl と Ar と O とを含むガスを用いたスパッタによる異方性エッティングをオーバーエッチになるように行つた後に有機酸もしくはアミン系の有機溶媒を用いたウェットエッティングを行う

ことを特徴とする磁気抵抗記憶素子の製造方法。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、磁気抵抗記憶素子およびその製造方法に関し、特に、TMR (Tunnel Magneto-Resistance: トンネル磁気抵抗) 効果を用いた不揮発性メモリである MRAM (Magnetoresistive Random Access Memory) の歩留まりを向上させるための技術に関する。

**【背景技術】****【0002】**

従来から、スピン依存電気伝導による TMR 効果を用いた不揮発性メモリである MRA

50

Mが用いられている。MRAMは、無限回数の書き換え、TMR素子の微細化による大容量化、高速動作、および低電圧動作が可能等の優れた特性を持っている。メモリ動作を行う素子は、TMR構造と呼ばれる構造を持ち、2つの磁性膜が上下にトンネル絶縁層を挟む形状で配置されている。下部の磁性層はピン層、上部の磁性層はフリー層と呼ばれ、磁性を持つ合金の積層膜によって構成されている。メモリ動作としては、ピン層の磁性の向きを固定しておき、電流によって誘起された外部磁場をTMR素子に印加することにより、フリー層の磁性の向きをコントロールする。ピン層の磁性の向きに対して、フリー層の磁性の向きが平行な場合と半平行な場合において、トンネル絶縁膜を流れるトンネル電流の抵抗値が変化し、この変化がメモリ動作の“0”および“1”にそれぞれ対応する。

## 【0003】

10 このようなMRAMの例は、例えば、特許文献1～3等に開示されている。

## 【0004】

【特許文献1】特開2002-314170号公報

【特許文献2】特開2002-124717号公報

【特許文献3】特開2003-110162号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0005】

上述のメモリ動作において、トンネル絶縁膜にはトンネル電流が流れる必要があり、TMR膜のピン層とフリー層とが電気的に絶縁されている必要がある。

## 【0006】

しかしながら、従来のTMR素子においては、ピン層、トンネル絶縁層、およびフリー層それぞれの側面が、同一平面上に位置するように（言い換えれば、それぞれの側面が面一となるように）加工される。従って、制御良くピン層とフリー層とを絶縁して加工することが困難であるので、TMR素子のショートに起因して、メモリ動作に必要な抵抗変化率を確保できない場合がある。そのため、歩留まりが低下してしまう場合があるという問題点があった。

## 【0007】

本発明は、以上の問題点を解決するためになされたものであり、歩留まりを向上させることが可能な磁気抵抗記憶素子およびその製造方法を提供することを目的とする。

## 【課題を解決するための手段】

## 【0008】

上記の課題を解決するために、本発明に係る磁気抵抗記憶素子は、下部磁性層および上部磁性層並びに下部磁性層と上部磁性層との間に挟まれた非磁性絶縁膜を有する磁気抵抗記憶素子であって、非磁性絶縁膜の側壁に第一の切れ込みを形成したことを特徴とする。

## 【発明の効果】

## 【0009】

本発明に係る磁気抵抗記憶素子は、下部磁性層および上部磁性層並びに下部磁性層と上部磁性層との間に挟まれた非磁性絶縁膜を有する磁気抵抗記憶素子であって、非磁性絶縁膜の側壁に第一の切れ込みを形成したことを特徴とする。従って、下部磁性層と上部磁性層との間の絶縁性を高めることができる。よって、メモリ動作に必要な抵抗変化率を確保できるので、この磁気抵抗記憶素子を有するメモリセルの歩留まりを高めることができる。

## 【発明を実施するための最良の形態】

## 【0010】

## &lt;実施の形態1&gt;

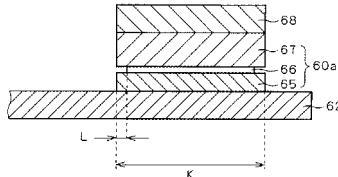

図1は、本発明の実施の形態1に係るメモリセルの構造を示す上面図である。図1においては、TMR下部電極膜62上にTMR素子60aが形成され、TMR素子60a上にピットライン72が形成されている。

## 【0011】

10

20

30

40

50

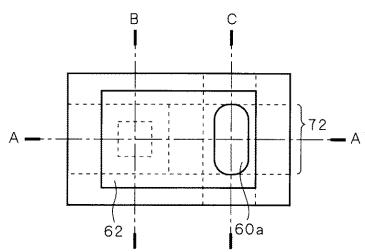

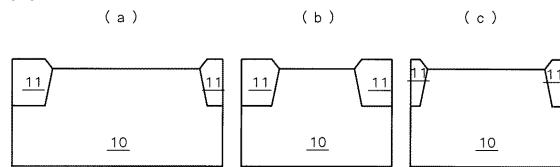

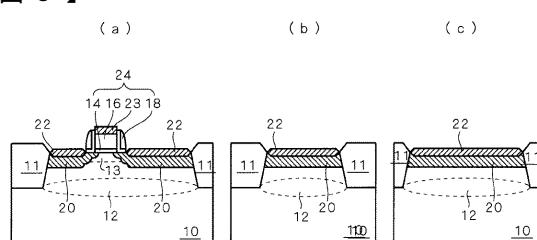

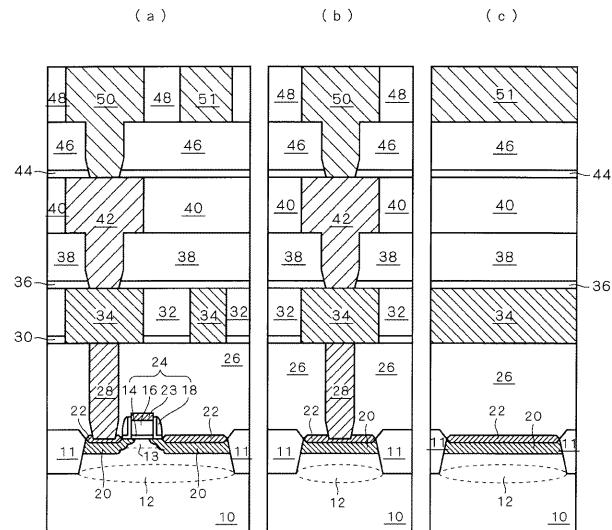

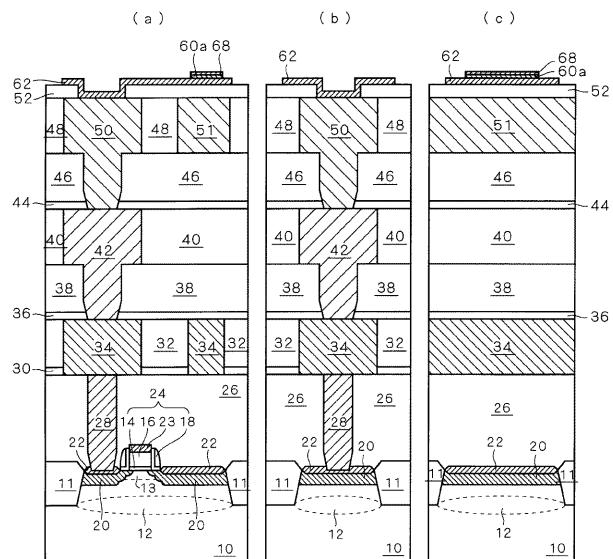

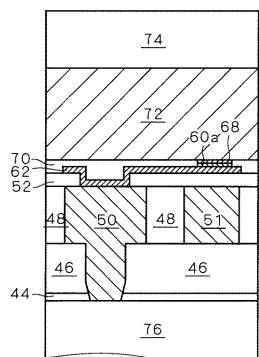

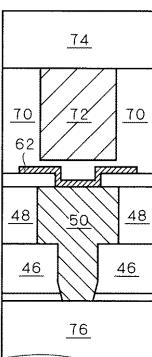

図2は、図1に示されるメモリセルの構造を示す断面図である。図2(a)～(c)は、それぞれ、図1におけるA-A断面、B-B断面およびC-C断面を示している。すなわち、図2(a)はビットライン72に平行な断面を示し、図2(b)、(c)はビットライン72に直交する断面をそれぞれ示している。

【0012】

図2において、半導体基板10は、厚さが約40nm程度の分離領域11により活性領域が分離されている。活性領域上には、ソース/ドレイン20およびゲート構造24を含むトランジスタ領域が形成されている。

【0013】

このゲート構造24は、厚さが約3nm程度のゲート酸化膜14上に厚さが約150nm程度のゲート電極16を形成しその両側面に幅が約150nm程度のサイドウォール18を形成させた構造からなる。また、このゲート電極16の上面は、約150nm×200nm程度であり、その上にコバルトシリサイド23が形成されている。

【0014】

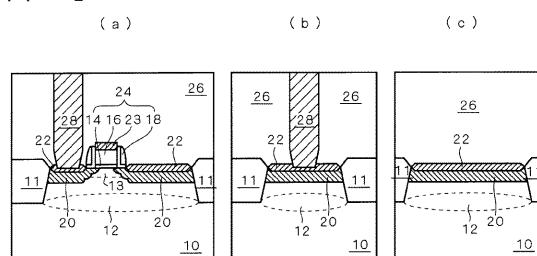

半導体基板10上には、酸化膜からなり厚さが約500nm程度の層間絶縁膜26が形成されており、層間絶縁膜26中にはコンタクトプラグ28が形成されている。層間絶縁膜26上には、窒化膜からなり厚さが約80nm程度の層間絶縁膜30および酸化膜からなり厚さが約400nm程度の層間絶縁膜32がこの順に形成されており、層間絶縁膜30、32中にはCu配線34が形成されている。層間絶縁膜32上には、窒化膜からなり厚さが約50nm程度の層間絶縁膜36、酸化膜からなり厚さが約400nm程度の層間絶縁膜38および酸化膜からなり厚さが約400nm程度の層間絶縁膜40がこの順に形成されており、層間絶縁膜36、38、40中にはCu配線42が形成されている。層間絶縁膜40上には、窒化膜からなり厚さが約80nm程度の層間絶縁膜44、酸化膜からなり厚さが約400nm程度の層間絶縁膜46および酸化膜からなり厚さが約400nm程度の層間絶縁膜48がこの順に形成されている。層間絶縁膜44、46、48中にはCu配線からなるディジットライン50が形成されており、層間絶縁膜48中には、Cu配線51が形成されている。

【0015】

層間絶縁膜48上には、窒化膜からなり厚さが約100nm程度の層間絶縁膜52が形成されており、層間絶縁膜52中および上にはTaからなるTMR下部電極膜62がディジットライン50に接するように形成されている。

【0016】

TMR下部電極膜62上の一領域には、TMR素子60aおよびTMR上部電極膜68がこの順に形成されている。また、TMR下部電極膜62上の他領域には、酸化膜からなり厚さが約500nm程度の層間絶縁膜70が形成されている。層間絶縁膜70中には、Cu配線からなり太さが約400nm程度のビットライン72が形成されている。層間絶縁膜70上には、窒化膜からなるパッシベーション膜74が形成されている。

【0017】

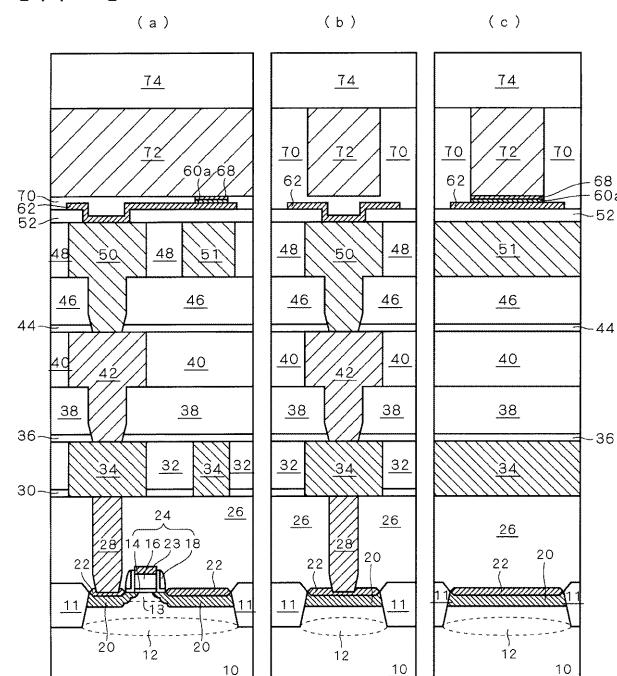

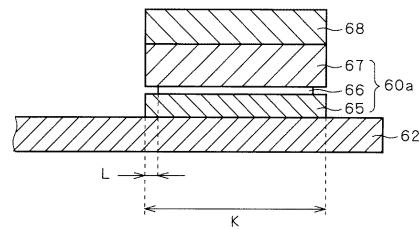

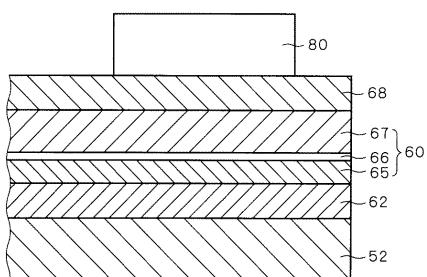

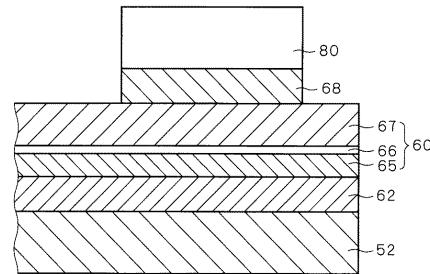

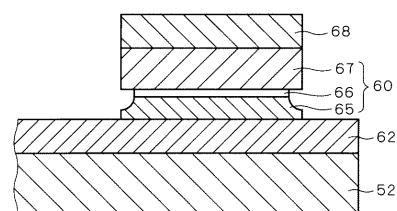

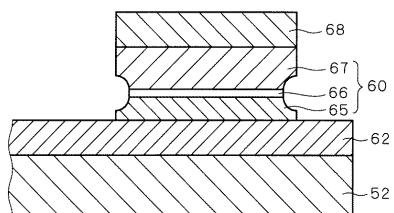

図3は、図1、2に示されるTMR素子60aの詳細な構造を示す断面図である。図3において、TMR素子(磁気抵抗記憶素子)60aは、厚みが約30～50nm程度であり、磁性膜からなるピン層(下部磁性層)65、非磁性絶縁膜からなるトンネル絶縁層66および磁性膜からなるフリー層(上部磁性層)67をこの順に堆積した構成からなる。また、TMR素子60aおよびTMR上部電極膜68は、いずれも同一平面形状を有し、約200nm×400nm程度である。

【0018】

図3に示すように、TMR素子60aは、それぞれ同一平面形状を有するピン層65、トンネル絶縁層66およびフリー層67において、トンネル絶縁層66の側壁に切れ込み(第一の切れ込み)を形成したサイドエッチ構造を有している。この切れ込みの長さLとしては、ピン層65又はフリー層67の長さKの5～10%であることが望ましい。このような切れ込みを形成することにより、ピン層65とフリー層67との間の絶縁性を高め

ことができる。従って、メモリ動作に必要な抵抗変化率を確保できるので、このようなメモリセルの歩留まりを高めることが可能となる。

【0019】

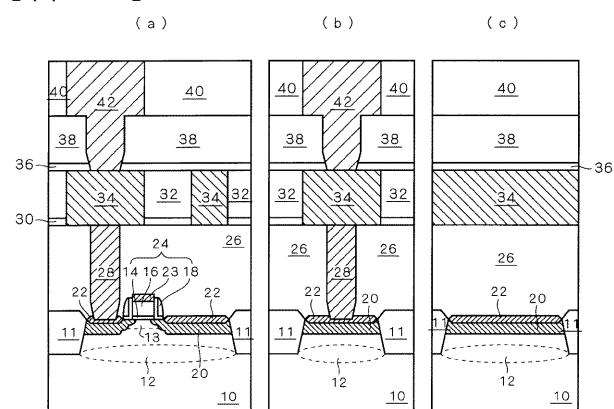

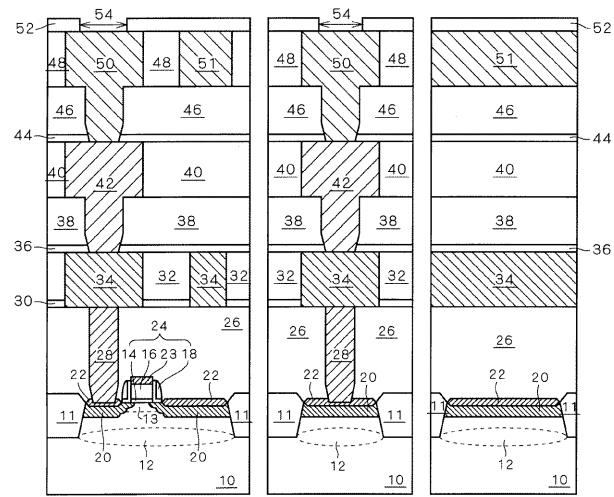

以下、図4～22に示される断面図を用いて、図1, 2に示されるメモリセルの製造方法について説明する。

【0020】

まず、図4に示すように、半導体基板10上に、活性領域および、STI(Shallow-Trench-Isolation: 浅いトレンチ分離)を用いた分離領域11を形成する。

【0021】

次に、図5に示すように、半導体基板10上に熱酸化膜(図示しない)を形成した後に、イオン注入を行うことにより、活性領域にウェル12およびチャンネル13を形成する。このとき、例えば、Pウェルとしては、不純物として、ボロンを、まず200～500keVおよび $5 \times 10^{12} \sim 1 \times 10^{14} / \text{cm}^2$ の条件で注入し、次に15～70keVおよび $3 \times 10^{12} \sim 5 \times 10^{13} / \text{cm}^2$ の条件で注入する。また、Nウェルとしては、不純物として、リンを300～1000keVおよび $5 \times 10^{12} \sim 1 \times 10^{14} / \text{cm}^2$ の条件で注入するとともに砒素を15～70keVおよび $3 \times 10^{12} \sim 5 \times 10^{13} / \text{cm}^2$ の条件で注入する。

【0022】

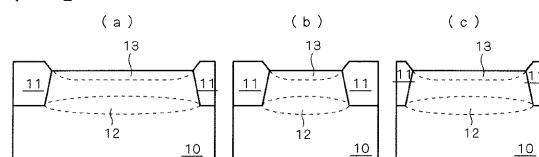

次に、図6に示すように、ゲート酸化を行うことにより半導体基板10上にゲート酸化膜14を形成した後に、ゲート酸化膜14上にゲート電極16を形成する。

【0023】

次に、図7に示すように、ゲート電極16の両側面にサイドウォール18を形成した後に、半導体基板10上にイオン注入を行うことによりソース/ドレイン20を形成する。このとき、例えば、Pウェルに対しては、不純物として、ボロンを、1～20keVおよび $5 \times 10^{13} \sim 5 \times 10^{15} / \text{cm}^2$ の条件で注入する。また、Nウェルに対しては、不純物として、砒素を、3～100keVおよび $5 \times 10^{13} \sim 5 \times 10^{15} / \text{cm}^2$ の条件で注入する。

【0024】

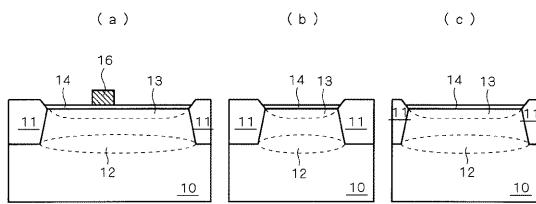

次に、図8に示すように、ソース/ドレイン20上およびゲート電極16上に、それぞれ、コバルトシリサイド22, 23を形成する。これにより、ゲート酸化膜14、ゲート電極16、サイドウォール18およびコバルトシリサイド23を含むゲート構造24が形成される。

【0025】

次に、図9に示すように、半導体基板10上に層間絶縁膜26を堆積した後に、層間絶縁膜26中にコンタクトプラグ28を形成する。

【0026】

次に、図10に示すように、層間絶縁膜26上に層間絶縁膜30, 32をこの順に堆積した後に、ダマシン技術を用いて、層間絶縁膜30, 32中にCu配線34を形成する。

【0027】

次に、図11に示すように、層間絶縁膜32上に、層間絶縁膜36, 38, 40をこの順に堆積した後に、ダマシン技術を用いて、層間絶縁膜36, 38, 40中にCu配線42を形成する。

【0028】

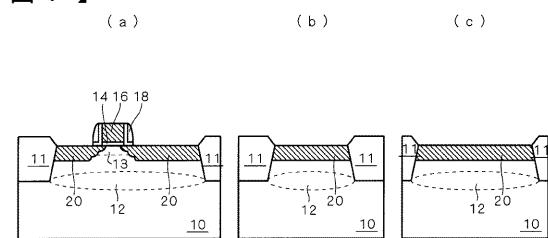

次に、図12に示すように、層間絶縁膜40上に、層間絶縁膜44, 46, 48をこの順に堆積する。その後に、ダマシン技術を用いて、層間絶縁膜44, 46, 48中にCu配線からなるディジットライン50を形成し、層間絶縁膜48中にCu配線51を形成する。

【0029】

次に、図13に示すように、層間絶縁膜48上に、層間絶縁膜52を堆積した後に、レジスト(図示しない)を塗布し、写真製版技術を用いてレジストパターン(図示しない)

10

20

30

40

50

を形成する。そして、このレジストパターンに異方性エッチングを行うことにより、ピア54を開口する。

【0030】

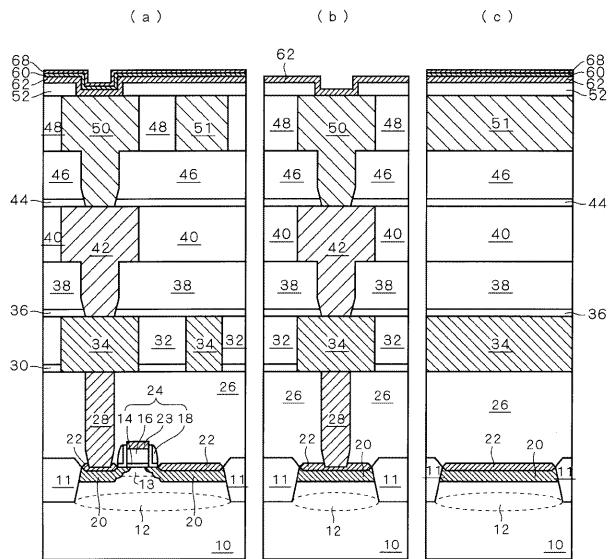

次に、図14に示すように、ピア54を開口された層間絶縁膜52上に、TaからなるTMR下部電極膜62を堆積する。そして、TMR下部電極膜62上に、ピン層65、トンネル絶縁層66、およびフリー層67をこの順に堆積することによりTMR膜60を形成する（図14においては、ピン層65、トンネル絶縁層66、およびフリー層67は図示していない）。さらに、TMR膜60上に、TaからなるTMR上部電極膜68を堆積する。

【0031】

次に、図15に示すように、TMR上部電極膜68およびTMR膜60を加工する。この加工において、TMR上部電極膜68およびTMR膜60は、図3に示されるようなサイドエッチ構造に加工される。これにより、TMR膜60からTMR素子60aが形成される。TMR上部電極膜68およびTMR膜60の詳細な加工手順については、図17～20を用いて後述する。

【0032】

次に、図16に示すように、TMR下部電極膜62の形状を加工する。TMR下部電極膜62の詳細な加工手順については、図21～22を用いて後述する。

【0033】

次に、層間絶縁膜52上およびTMR下部電極膜62上に層間絶縁膜70を堆積した後に、ダマシン技術を用いて、層間絶縁膜70に、Cu配線からなるビットライン72を形成する。そして、層間絶縁膜70上にパッシベーション膜74を形成する。これにより、図2に示されるようなメモリセルが形成される。

【0034】

以下、図17～22に示される断面図を用いて、TMR上部電極膜68、TMR膜60およびTMR下部電極膜62の詳細な加工手順について説明する。

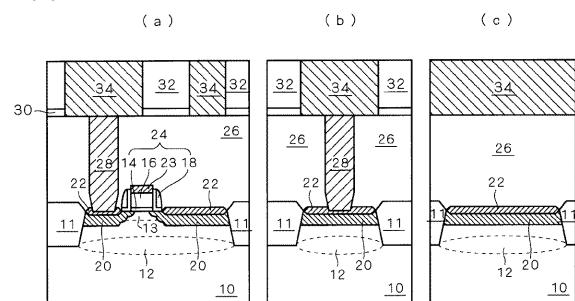

【0035】

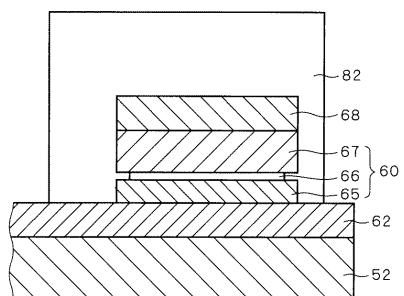

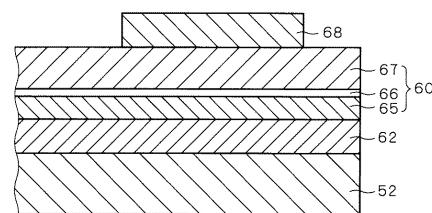

まず、図17に示すように、TMR上部電極膜68上にレジストを塗布し、写真製版技術を用いてレジストマスク80を形成する。

【0036】

次に、図18に示すように、レジストマスク80を用いて、TMR上部電極膜68をエッチングする。

【0037】

次に、図19に示すように、レジストマスク80を除去する。

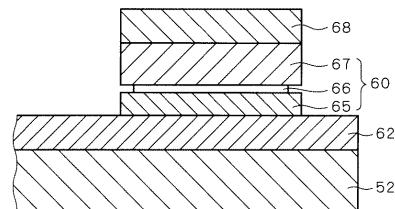

【0038】

次に、図20に示すように、TaからなるTMR上部電極膜68をハードマスクとしてスパッタによる異方性エッチングを行い、TMR膜60の形状を加工する。このとき、CO分子とNH<sub>3</sub>分子とを含むCO/NH<sub>3</sub>ガスを用いることにより、トンネル絶縁膜66の側壁に切れ込みを形成することができる。

【0039】

そして、スパッタによりTMR膜60の側壁に堆積された堆積物を、ウェットエッチングにより除去する。これにより、ピン層65とフリー層67との間の絶縁性を高めリーク電流を抑制することができる。

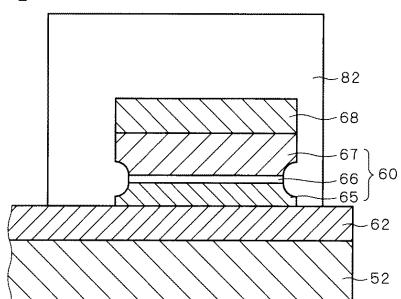

【0040】

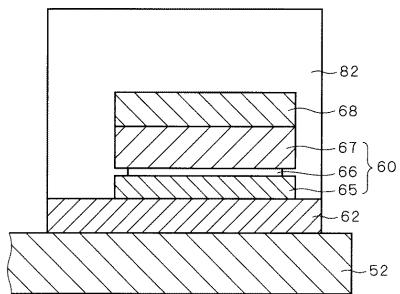

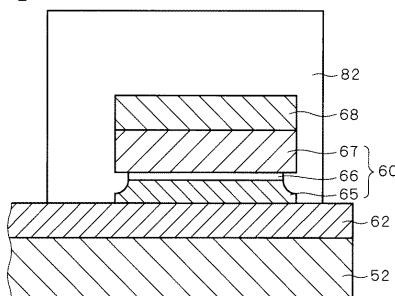

次に、図21に示すように、TMR上部電極膜68上にレジストを塗布し、写真製版技術を用いてレジストマスク82を形成する。

【0041】

次に、図22に示すように、レジストマスク82を用いて、スパッタによりTMR下部電極膜62の異方性エッチングを行う。

【0042】

10

20

30

40

50

次に、レジストマスク 8 2 を除去した後に、スパッタにより T M R 膜 6 0 の側壁に堆積された堆積物を、ウェットエッティングにより除去する。これにより、ピン層 6 5 とフリー層 6 7 との間の絶縁性を高めリーク電流を抑制することが可能となり、図 3 に示されるようなサイドエッチ構造を有する T M R 素子 6 0 a が形成される。

## 【0043】

このように、本実施の形態に係る磁気抵抗記憶素子およびその製造方法においては、C O / N H<sub>3</sub> ガスを用いてスパッタによる異方性エッティングを行うことにより、トンネル絶縁膜 6 6 の側壁に切れ込みを形成する。従って、ピン層 6 5 とフリー層 6 7 との間の絶縁性を高めることができる。よって、メモリ動作に必要な抵抗変化率を確保できるので、T M R 素子 6 0 a を有するメモリセルの歩留まりを高めることができる。

10

## 【0044】

また、スパッタにより T M R 膜 6 0 の側壁に堆積された堆積物を、ウェットエッティングにより除去する。これにより、ピン層 6 5 とフリー層 6 7 との間の絶縁性をさらに高めることができる。

## 【0045】

## &lt;実施の形態 2&gt;

実施の形態 1 においては、トンネル絶縁膜 6 6 に切れ込みを形成するが、トンネル絶縁膜 6 6 に加えてピン層 6 5 の上部に切れ込みを形成してもよい。

## 【0046】

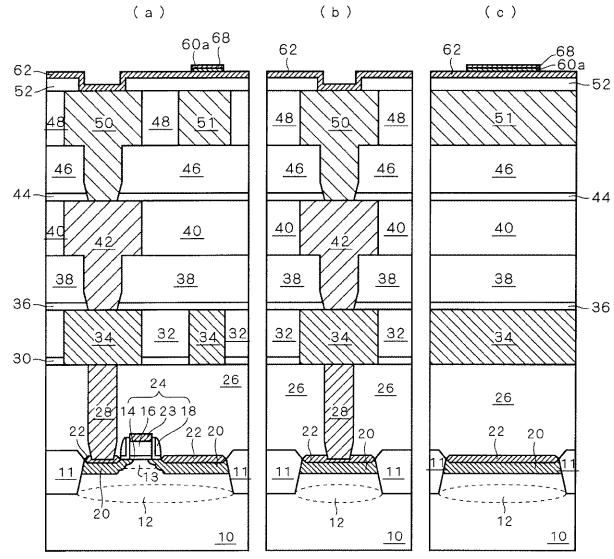

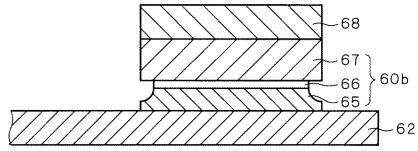

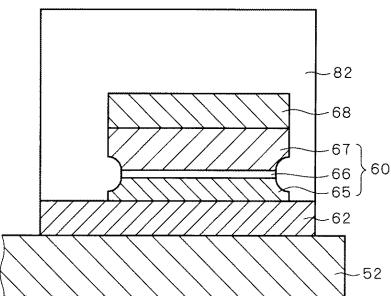

図 2 3 は、実施の形態 2 に係る T M R 素子 6 0 b の構造を示す断面図である。図 2 3 は、図 3 に示されるサイドエッチ構造において、トンネル絶縁膜 6 6 の側壁に加えてピン層 6 5 の側壁の上部にも切れ込み（第二の切れ込み）が形成されたものである。この第二の切れ込みは、第一の切れ込みに連なるように形成される。

20

## 【0047】

以下、図 2 4 ~ 2 6 に示される断面図を用いて、図 2 3 に示される T M R 素子 6 0 の製造方法について説明する。

## 【0048】

まず、図 1 7 ~ 図 1 9 と同様の手順で、T M R 上部電極膜 6 8 の形状を加工する。

## 【0049】

次に、図 2 4 に示すように、T a からなる T M R 上部電極膜 6 8 をハードマスクとしてスパッタによる異方性エッティングを行い、T M R 膜 6 0 の形状を加工する。このとき、C l イオンとA r イオンとO イオンとを含むC l / A r / O ガスを用いてオーバーエッチを行うことにより、トンネル絶縁膜 6 6 の側壁およびピン層 6 5 の側壁の上部に切れ込みを形成することができる。このオーバーエッチにおいては、T M R 下部電極膜 6 2 表面において散乱されたイオン等（リスペッタ成分）がエッティング成分として作用することにより、トンネル絶縁膜 6 6 に加えてピン層 6 5 をエッティングすることが可能となる。

30

## 【0050】

そして、スパッタにより T M R 膜 6 0 の側壁に堆積された堆積物を、ウェットエッティングにより除去する。これにより、ピン層 6 5 とフリー層 6 7 との間の絶縁性を高めリーク電流を抑制することができる。

40

## 【0051】

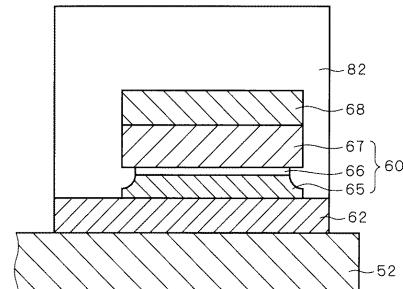

次に、図 2 5 に示すように、T M R 上部電極膜 6 8 上にレジストを塗布し、写真製版技術を用いてレジストマスク 8 2 を形成する。

## 【0052】

次に、図 2 6 に示すように、レジストマスク 8 2 を用いて、スパッタにより T M R 下部電極膜 6 2 の異方性エッティングを行う。

## 【0053】

次に、レジストマスク 8 2 を除去した後に、スパッタにより T M R 膜 6 0 の側壁に堆積された堆積物を、ウェットエッティングにより除去する。これにより、ピン層 6 5 とフリー層 6 7 との間の絶縁性を高めリーク電流を抑制することができる、図 2 3 に示される

50

のようなサイドエッチ構造を有するTMR素子60bが形成される。

【0054】

このように、本実施の形態では、実施の形態1におけるCO/NH<sub>3</sub>ガスに代えてC1/Ar/Oガスを用いて、オーバーエッチを行うことにより、トンネル絶縁膜66に加えてピン層65の上部に切れ込みを形成する。従って、実施の形態1の効果に加えて、メモリセルの歩留まりをさらに高めることが可能となるという効果を有する。

【0055】

<実施の形態3>

実施の形態2においては、トンネル絶縁膜66とピン層65の上部とに切れ込みを形成するが、トンネル絶縁膜66とピン層65の上部とに加えてフリー層67の下部に切れ込みを形成してもよい。

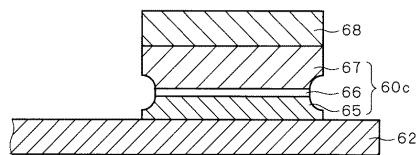

【0056】

図27は、実施の形態3に係るTMR素子60cの構造を示す断面図である。図27は、図23に示されるサイドエッチ構造において、トンネル絶縁膜66の側壁およびピン層65の側壁の上部に加えてフリー層67の側壁の下部にも切れ込み(第三の切れ込み)が形成されたものである。この第三の切れ込みは、第一の切れ込みに連なるように形成される。

【0057】

以下、図28～30に示される断面図を用いて、図27に示されるTMR素子60cの製造方法について説明する。

【0058】

まず、図17～図19と同様の手順で、TMR上部電極膜68の形状を加工する。

【0059】

次に、図28に示すように、TaからなるTMR上部電極膜68をハードマスクとしてスパッタによる異方性エッチングを行い、TMR膜60の形状を加工する。このとき、C1/Ar/Oガスを用いてオーバーエッチを行うことにより、トンネル絶縁膜66の側壁およびピン層65の側壁の上部に切れ込みを形成することができる。このオーバーエッチにおいては、TMR下部電極膜62表面において散乱されたイオン等(リスペッタ成分)がエッチング成分として作用することにより、トンネル絶縁膜66に加えてピン層65をエッチングすることが可能となる。

【0060】

そして、スパッタによりTMR膜60の側壁に堆積された堆積物を、ウェットエッチングにより除去する。このとき、エッチング液として有機酸もしくはアミン系の有機溶媒を用いることにより、トンネル絶縁膜66の側壁およびピン層65の側壁の上部に加えてフリー層67の側壁の下部に切れ込みを形成することができる。これにより、ピン層65とフリー層67との間の絶縁性を高めリーク電流を抑制することが可能となる。

【0061】

次に、図29に示すように、TMR上部電極膜68上にレジストを塗布し、写真製版技術を用いてレジストマスク82を形成する。

【0062】

次に、図30に示すように、レジストマスク82を用いて、スパッタによりTMR下部電極膜62の異方性エッチングを行う。

【0063】

次に、レジストマスク82を除去した後に、スパッタによりTMR膜60の側壁に堆積された堆積物を、ウェットエッチングにより除去する。これにより、ピン層65とフリー層67との間の絶縁性を高めリーク電流を抑制することが可能となり、図27に示されるようなサイドエッチ構造を有するTMR素子60cが形成される。

【0064】

このように、本実施の形態では、有機酸もしくはアミン系の有機溶媒を用いたウェットエッチングを行うことにより、トンネル絶縁膜66とピン層65の上部とに加えてフリー

10

20

30

40

50

層 6 7 の下部に切れ込みを形成する。従って、実施の形態 2 の効果に加えて、メモリセルの歩留まりをさらに高めることが可能となるという効果を有する。

【 0 0 6 5 】

なお、本実施の形態においては、エッチングガスとして、C l / A r / O ガスに代えて C O / N H<sub>3</sub> ガスを用いた場合にも、同様の効果を奏することが確認されている。すなわち、有機酸もしくはアミン系の有機溶媒を用いたウェットエッチングを行うことにより、ピン層 6 5 の側壁の上部とフリー層 6 7 の側壁の下部との両方がエッチングされると考えられる。

【 0 0 6 6 】

< 実施の形態 4 >

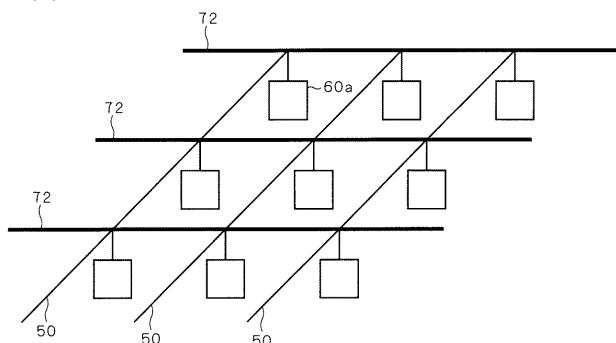

実施の形態 1 ~ 3 においては、ソース / ドレイン 2 0 およびゲート構造 2 4 を含むトランジスタ領域を形成し、それぞれ、このトランジスタ領域を用いて T M R 素子 6 0 a ~ c の選択を行っている。しかし、T M R 素子 6 0 a ~ 6 0 c をクロスポイント型に配置することにより、このトランジスタ領域を省いてもよい。

【 0 0 6 7 】

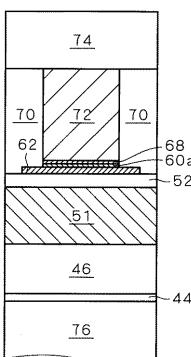

図 3 1 は、実施の形態 4 に係る半導体装置における T M R 素子（図 3 1 では T M R 素子 6 0 a を用いた場合を示している）の配置を示す模式図である。図 3 1 に示されるようなクロスポイント型配置においては、T M R 素子 6 0 a は、複数のディジットライン 5 0 と複数のビットライン 7 2 とのそれぞれの交点に配置され、ディジットライン 5 0 とビットライン 7 2 とを制御することにより、トランジスタを用いることなく選択されデータの書き込みが行われる。従って、T M R 素子 6 0 a をクロスポイント型に配置することにより、図 3 2 に示すように、メモリセルにおいてトランジスタ領域を省くことが可能となる。図 3 2 は、図 2 において、層間絶縁膜 4 0 および C u 配線 4 2 より下の領域を省いた構造を層間絶縁膜 7 6 上に形成したものである。

【 0 0 6 8 】

このように、本実施の形態においては、T M R 素子をクロスポイント型に配置することにより、メモリセルのトランジスタ領域を省いている。従って、メモリセルの面積を低減できるので、集積度を高めることができる。

【 図面の簡単な説明 】

【 0 0 6 9 】

10

20

30

40

50

【 図 1 】 本発明の実施の形態 1 に係るメモリセルの構造を示す断面図である。

【 図 2 】 本発明の実施の形態 1 に係るメモリセルの構造を示す上面図である。

【 図 3 】 本発明の実施の形態 1 に係る T M R 素子の構造を示す断面図である。

【 図 4 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 5 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 6 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 7 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 8 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 9 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 0 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 1 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 2 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 3 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 4 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 5 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 6 】 本発明の実施の形態 1 に係るメモリセルの製造方法を示す断面図である。

【 図 1 7 】 本発明の実施の形態 1 に係る T M R 素子の製造方法を示す断面図である。

【 図 1 8 】 本発明の実施の形態 1 に係る T M R 素子の製造方法を示す断面図である。

【 図 1 9 】 本発明の実施の形態 1 に係る T M R 素子の製造方法を示す断面図である。

【 図 2 0 】 本発明の実施の形態 1 に係る T M R 素子の製造方法を示す断面図である。

【図21】本発明の実施の形態1に係るTMR素子の製造方法を示す断面図である。

【図22】本発明の実施の形態1に係るTMR素子の製造方法を示す断面図である。

【図23】本発明の実施の形態2に係るTMR素子の構造を示す断面図である。

【図24】本発明の実施の形態2に係るTMR素子の製造方法を示す断面図である。

【図25】本発明の実施の形態2に係るTMR素子の製造方法を示す断面図である。

【図26】本発明の実施の形態2に係るTMR素子の製造方法を示す断面図である。

【図27】本発明の実施の形態3に係るTMR素子の構造を示す断面図である。

【図28】本発明の実施の形態3に係るTMR素子の製造方法を示す断面図である。

【図29】本発明の実施の形態3に係るTMR素子の製造方法を示す断面図である。

【図30】本発明の実施の形態3に係るTMR素子の製造方法を示す断面図である。

【図31】本発明の実施の形態4に係るメモリセルの配置を示す模式図である。

【図32】本発明の実施の形態4に係るメモリセルの構造を示す断面図である。

【符号の説明】

【0070】

10 半導体基板、11 分離領域、12 ウェル、13 チャンネル、14 ゲート

酸化膜、16 ゲート電極、18 サイドウォール、20 ソース／ドレイン、22, 2

3 コバルトシリサイド、24 ゲート構造、26, 30, 32, 36, 38, 40, 4

4, 46, 52, 76 層間絶縁膜、28 コンタクトプラグ、34, 42, 51 Cu

配線、50 ディジットライン、54 ピア、60 TMR膜、60a, 60b, 60c

TMR素子、62 TMR下部電極膜、65 ピン層、66 トンネル絶縁層、67

フリー層、68 TMR上部電極膜、72 ビットライン、74 パッシベーション膜、

80, 82 レジストマスク。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

(a)

(b)

(c)

【図13】

(a)

(b)

(c)

【図14】

(a)

(b)

(c)

【図15】

(a)

(b)

(c)

【 図 1 6 】

【図 17】

【図21】

【 図 2 2 】

【 図 2 3 】

【 図 1 8 】

【 図 1 9 】

【 図 2 0 】

【 図 2 4 】

〔 図 25 〕

【 図 2 6 】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

(a)

(b)

(c)

## フロントページの続き

(51)Int.Cl.

**H 01 L 21/306 (2006.01)**

F I

H 01 L 21/306

S

テーマコード(参考)

(72)発明者 黒岩 丈晴

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

F ターム(参考) 5F004 AA09 DA00 DA23 DB00 EA09 EB08

5F043 AA40 BB30 DD15 FF02 GG10

5F083 FZ10 JA35 JA37 JA39 JA56 MA06 MA16 MA19 NA01 NA08

PR03 PR05 PR22 PR36