## (12) 发明专利申请

(10) 申请公布号 CN 119024924 A

(43) 申请公布日 2024.11.26

(21) 申请号 202411125272.4

(22) 申请日 2018.01.31

### (30) 优先权数据

15/420,267 2017.01.31 US

### (62) 分案原申请数据

201880009131.2 2018.01.31

(71) 申请人 德克萨斯仪器股份有限公司

地址 美国德克萨斯州

(72) 发明人 M·索尼 R·苏瓦纳 N·卡雷

(74) 专利代理机构 北京纪凯知识产权代理有限公司 11245

专利代理人 张秀芬

### (51) Int.CI.

G06F 1/12 (2006.01)

G06F 13/24 (2006.01)

权利要求书2页 说明书6页 附图6页

### (54) 发明名称

用于缓慢外围设备的中断处理方法和设备

### (57) 摘要

本发明涉及用于缓慢外围设备的中断处理方法和设备。所描述的示例包括用于通过根据第二时钟信号操作的慢时钟域电路(102)管理根据第一时钟信号(FCLK)操作的快时钟域电路(101)的中断的中断处理电路(100)和方法(SCLK)，其中中断发生器电路(110)生成与第二时钟信号(SCLK)同步的中断输入信号(INT\_IN)，并且中断清除电路(114、116)响应于来自第一电路(101)的确认信号(ACK)，与第二时钟信号(SCLK)异步地选择性地复位中断发生器电路(110)。

1. 一种电路,所述电路包括:

包括第一输入以及输出的第一触发器,其中所述第一触发器被配置为:

在所述第一输入处接收表示中断请求的第一信号,以及

基于所述第一信号,在所述输出处生成第一输出信号;

包括第一输入以及输出的第二触发器,其中所述第二触发器被配置为:

在所述第一输入处接收表示对所述中断请求的确认的第二信号,以及

基于所述第二信号,在所述输出处生成第二输出信号;以及包括第一输入、第二输入以及输出的第三触发器,所述第一输入耦合到所述第一触发器的所述输出,并且所述第二输入耦合到所述第二触发器的所述输出,其中所述第三触发器被配置为:

基于所述第一输出信号和所述第二输出信号,在所述输出处生成第三输出信号。

2. 根据权利要求1所述的电路,其中所述第一触发器的所述第一输入是所述第一触发器的数据输入,其中所述第二触发器的所述第一输入是所述第二触发器的数据输入;并且其中所述第三触发器的所述第一输入是所述第三触发器的时钟输入,并且所述第三触发器的所述第二输入是所述第三触发器的清除输入。

3. 根据权利要求2所述的电路,其中所述第一触发器包括第二输入并且被配置为在所述第二输入处接收第一时钟信号,并且其中所述第二触发器包括第二输入并且被设置为在所述第二输入处接收第二时钟信号。

4. 根据权利要求3所述的电路,其中所述第一触发器的所述第二输入是所述第一触发器的时钟输入,并且其中所述第二触发器的所述第二输入是所述第二触发器的时钟输入。

5. 根据权利要求3所述的电路,其中,所述第一信号是根据所述第一时钟信号生成的,并且所述第二信号是根据所述第二时钟信号生成的。

6. 根据权利要求3所述的电路,其中所述第一时钟信号的频率不同于所述第二时钟信号的频率。

7. 根据权利要求6所述的电路,其中,所述第一时钟信号的所述频率小于所述第二时钟信号的所述频率。

8. 根据权利要求3所述的电路,还包括:

第四触发器,其包括第一输入以及输出,所述第一输入耦合到所述第三触发器的所述输出,其中所述第四触发器被配置为:

基于所述第三触发器的所述第三输出信号,在所述输出处生成第四输出信号。

9. 根据权利要求8所述的电路,其中所述第四触发器的所述第一输入是所述第四触发器的数据输入。

10. 根据权利要求8所述的电路,其中所述第四触发器包括第二输入,并且被配置为在所述第二输入处接收所述第二时钟信号。

11. 根据权利要求11所述的电路,其中所述第四触发器的所述第二输入是所述第四触发器的时钟输入。

12. 根据权利要求1所述的电路,其中所述第三触发器包括第三输入并且被配置为在所述第三输入处接收具有预定逻辑状态的信号。

13. 根据权利要求12所述的电路,其中所述第三触发器的所述第三输入是所述第三触发器的数据输入。

14. 根据权利要求12所述的电路,其中所述预定逻辑状态是逻辑高状态。

15. 一种方法,包括:

在第一触发器的第一输入处接收表示中断请求的第一信号,其中所述第一触发器包括所述第一输入和输出;

基于所述第一信号,在所述第一触发器的所述输出处生成第一输出信号;

在第二触发器的第一输入处,接收表示对所述中断请求的确认的第二信号,其中所述第二触发器包括所述第一输入和输出;

基于所述第二信号,在所述第二触发器的所述输出处生成第二输出信号;和

基于所述第一输出信号和所述第二输出信号,在第三触发器的输出处生成第三输出信号,其中所述第三触发器包括第一输入、第二输入和所述输出,并且其中所述第一输入耦合到所述第一触发器的所述输出,并且所述第二输入耦合到所述第二触发器的所述输出。

16. 根据权利要求15所述的方法,其中所述第一触发器的所述第一输入是所述第一触发器的数据输入,其中所述第二触发器的所述第一输入是所述第二触发器的数据输入;并且其中所述第三触发器的所述第一输入是所述第三触发器的时钟输入,并且所述第三触发器的所述第二输入是所述第三触发器的清除输入。

17. 根据权利要求16所述的方法,还包括:

在所述第一触发器的第二输入处接收第一时钟信号;和

在所述第二触发器的第二输入处接收第二时钟信号。

18. 根据权利要求17所述的方法,其中所述第一触发器的所述第二输入是所述第一触发器的时钟输入,并且其中所述第二触发器的所述第二输入是所述第二触发器的时钟输入。

19. 根据权利要求17所述的方法,其中所述第一信号是根据所述第一时钟信号生成的,并且所述第二信号是根据所述第二时钟信号生成的。

20. 根据权利要求17所述的方法,其中所述第一时钟信号具有小于所述第二时钟信号的频率。

## 用于缓慢外围设备的中断处理方法和设备

[0001] 本申请是国际申请日为2018年1月31日、进入国家阶段日为2019年7月30日的名称为“用于缓慢外围设备的中断处理方法和设备”的中国专利申请2018800091312 (PCT/US2018/016206) 的分案申请。

### 背景技术

[0002] 电子电路和系统通常包括以不同时钟速度操作的多个电路部分或时钟域。例如，处理器电路通常以高时钟速度操作，并与以非常低的时钟速度运行的一个或更多个外围电路相互作用。慢时钟域电路通常生成用于由快时钟域电路提供服务的中断服务请求。服务和清除来自慢时钟域电路的中断可能占用许多快时钟周期，并且可能导致快时钟域电路无法服务于其他中断。在一个示例中，来自以非常慢的频率(例如10-100KHz)操作的外围电路的中断由以1-100MHz或甚至更高的高时钟频率操作的CPU提供服务。由快时钟域处理器电路或CPU执行的应用软件可能需要响应于由计数器值到达预定值触发的中断，在低时钟速度脉冲宽度调制(PWM)控制电路的寄存器中更新或写入新的计数器值。先前的中断处理技术和电路将来自服务CPU的清除请求与慢时钟信号同步和/或使用握手(handshaking)方法来清除中断请求。这导致在外围电路接收到清除请求之前延迟两个或更多个慢时钟周期并移除中断请求信号。这种中断清除延迟可能很大，特别是对于快和慢时钟速度的巨大差异时来说。对于操作在10KHz功能时钟的外围设备，延迟至少为200微秒，这对于操作在100MHz的CPU来说非常巨大的。在此期间，快时钟域CPU必须等待以避免重新进入相同的服务路由。此外，如果在初始中断被清除之前外围电路中发生另一个中断事件，则来自相同外围设备的新中断事件将丢失。而且，传统的中断处理电路和技术生成具有一些延迟时间的中断请求。例如，慢时钟域中断生成条件可以基于上升慢时钟沿，并且中断请求信号根据上升慢时钟沿生成，反之亦然，其中与慢时钟信号的同步在服务中断事件时引入进一步的延迟。

### 发明内容

[0003] 所描述的示例包括用于通过慢时钟域第二电路管理快时钟域第一电路的中断的中断处理电路和方法，其中第一电路根据第一时钟信号操作而第二电路根据比第一时钟信号更慢的第二时钟信号操作。所描述的中断处理电路包括：中断发生器电路，其生成中断输入信号；以及中断清除电路，其响应于来自第一电路的确认信号，相对于第二时钟信号异步地复位中断发生器电路。

[0004] 在某些示例中，中断发生器电路包括第一输入，以用于接收中断请求信号的；第二输入，以用于接收中断清除信号；以及输出，以用于提供与中断请求信号同步的中断输入信号以选择性地中断第一电路。在一个示例中，中断清除电路包括与第一时钟信号同步的输出，以响应于来自第一电路的确认信号提供中断清除信号以复位中断发生器电路。

[0005] 描述了通过根据较慢的第二时钟信号操作的第二电路来管理根据第一时钟信号操作的第一电路的中断的方法。该方法包括生成与第二时钟信号同步的中断输入信号，响应于中断输入信号向第一电路提供中断输出信号，以及响应于来自第一电路的确认信号，

相对于第二时钟信号异步地清除中断输入和输出信号。

## 附图说明

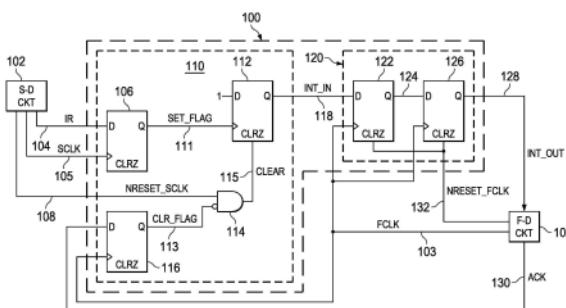

[0006] 图1是示出中断处理电路的示意图,该中断处理电路被配置为通过慢时钟域第二电路管理快时钟域第一电路的中断。

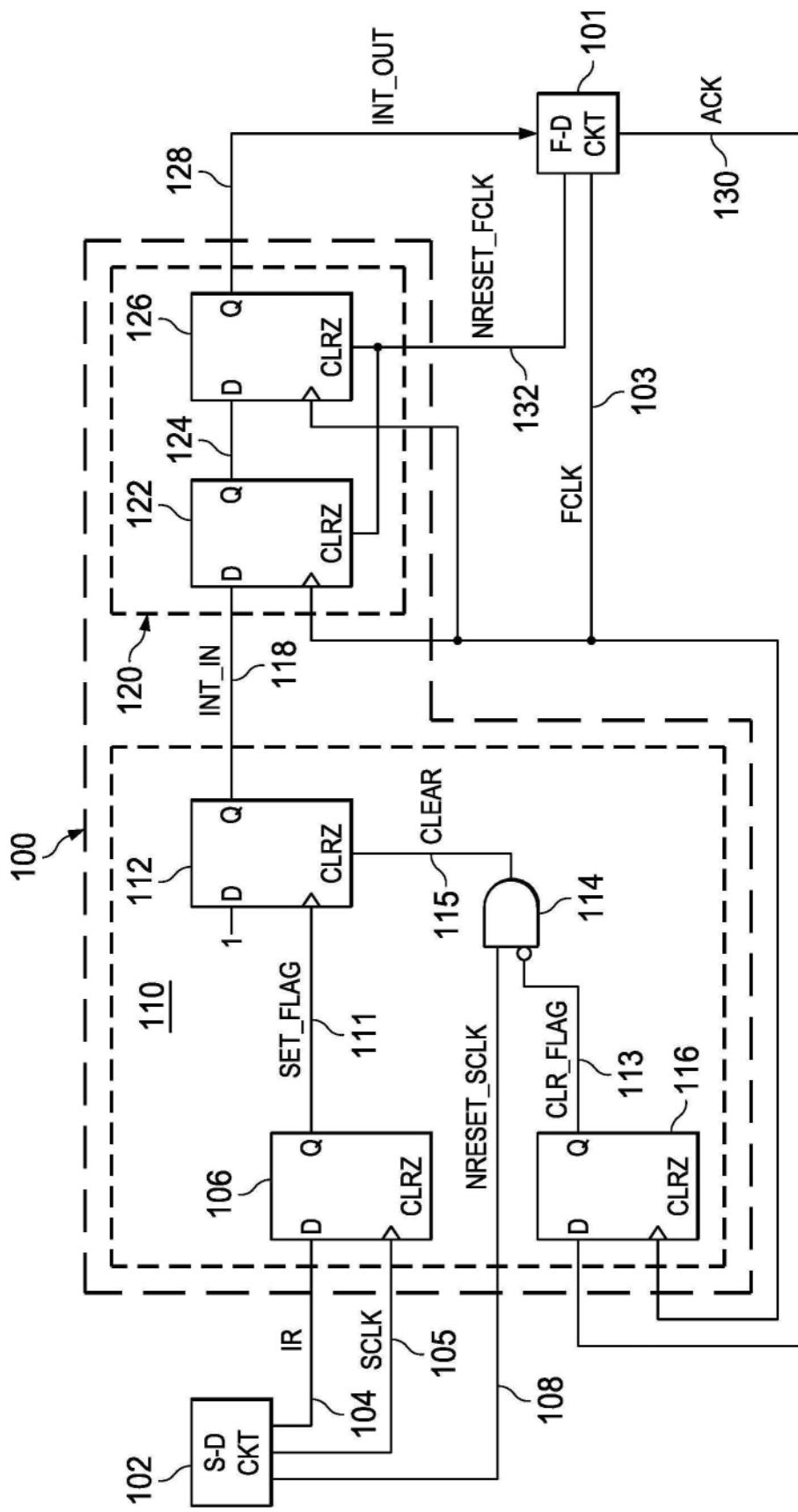

[0007] 图2是示出图1的电路中的用于快和慢时钟速度的任意比率的操作信号的信号图。

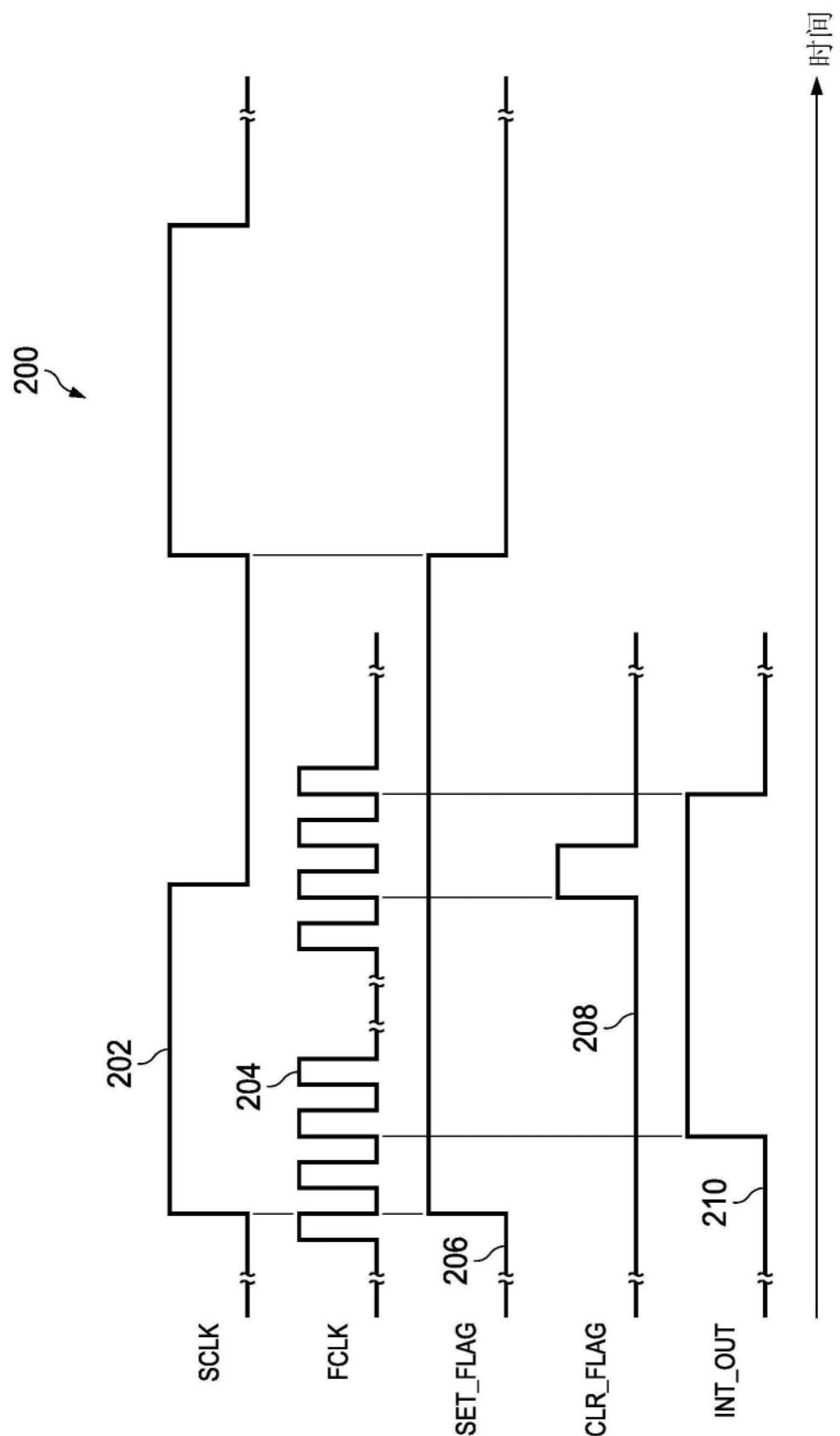

[0008] 图3是示出图1的电路中的用于快和慢时钟速度的一个示例比率的操作信号的信号图。

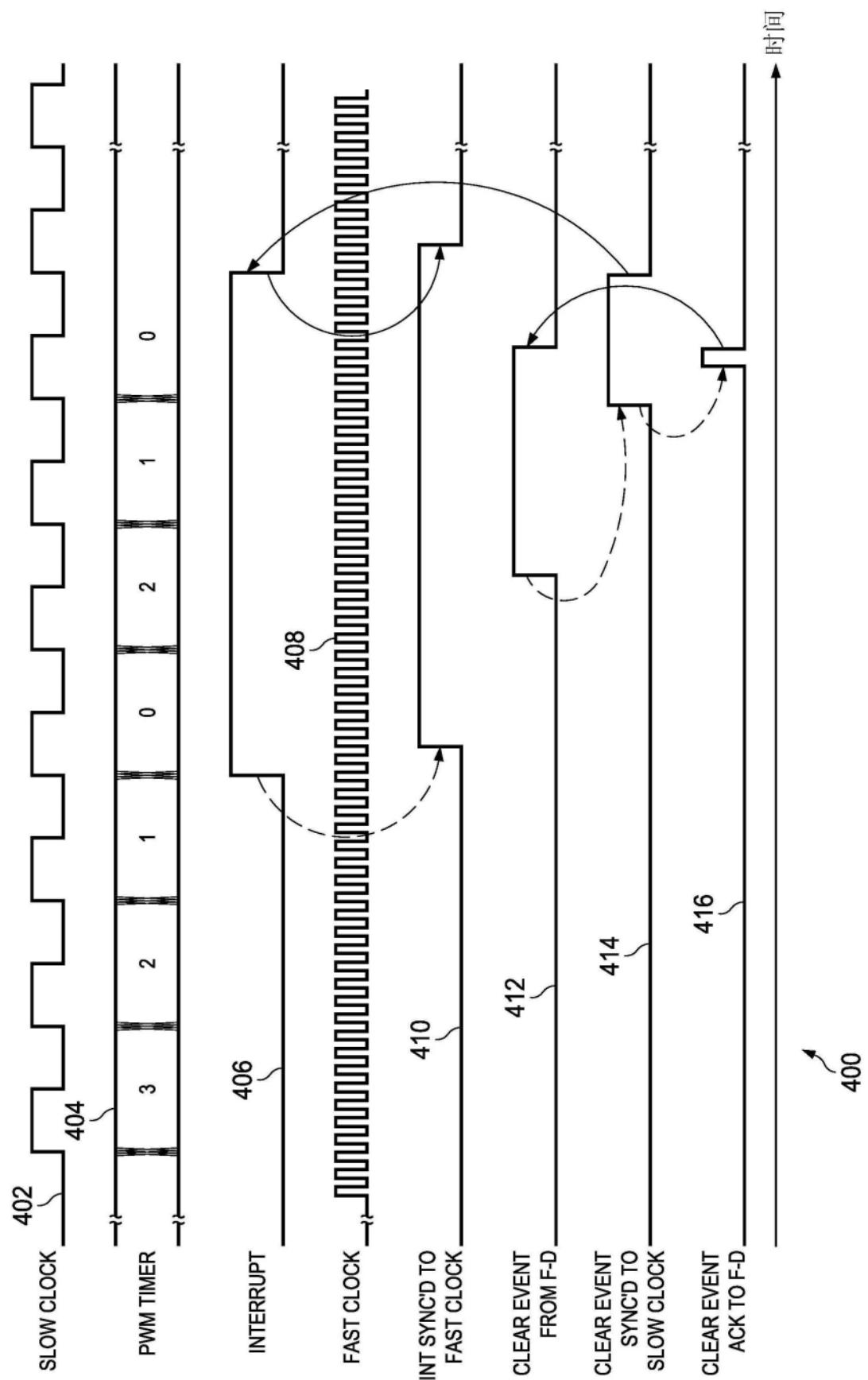

[0009] 图4是示出具有遗漏中断事件的握手确认中断处理技术的信号图。

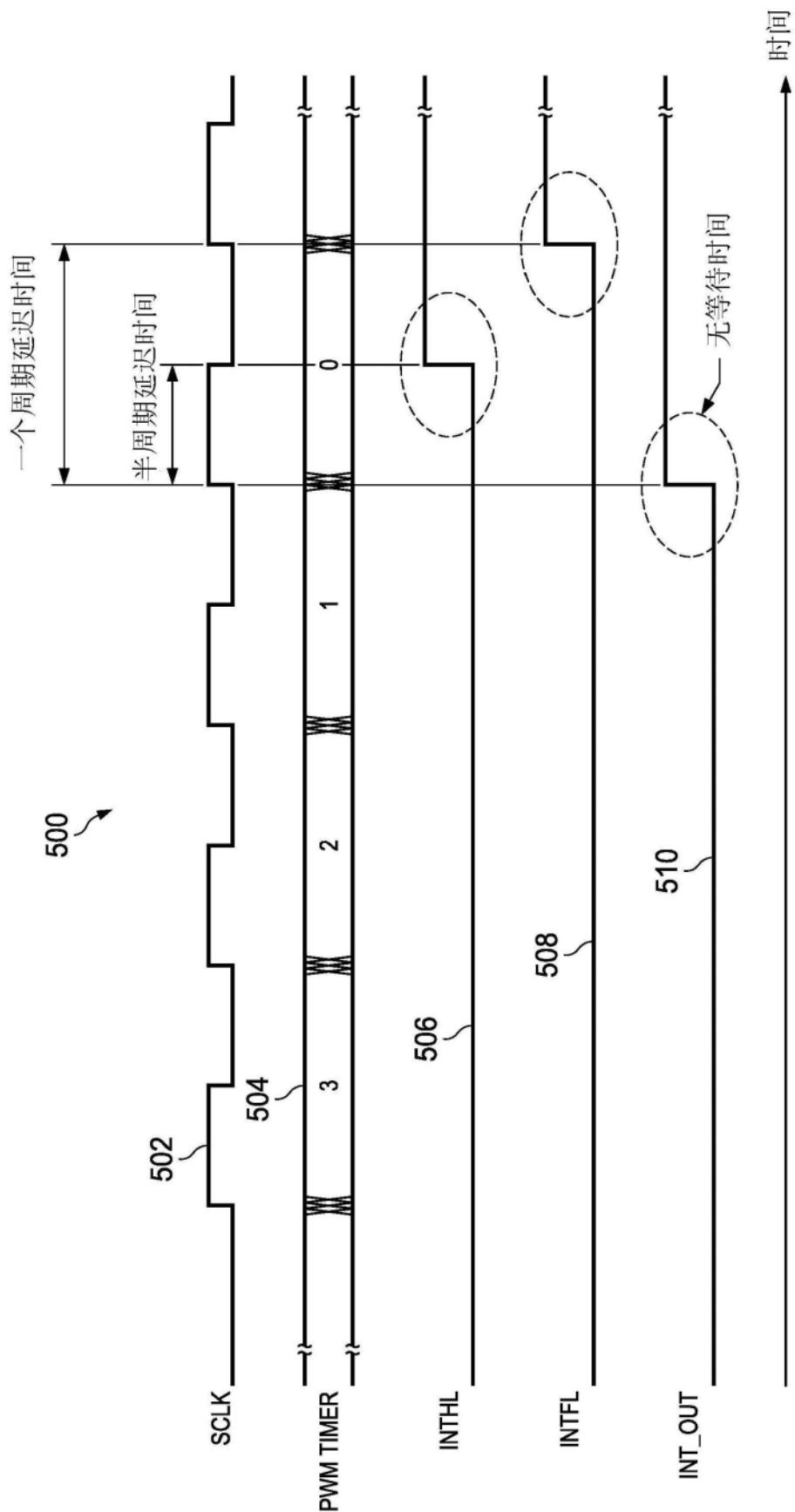

[0010] 图5是示出具有同步延迟的中断生成的信号图。

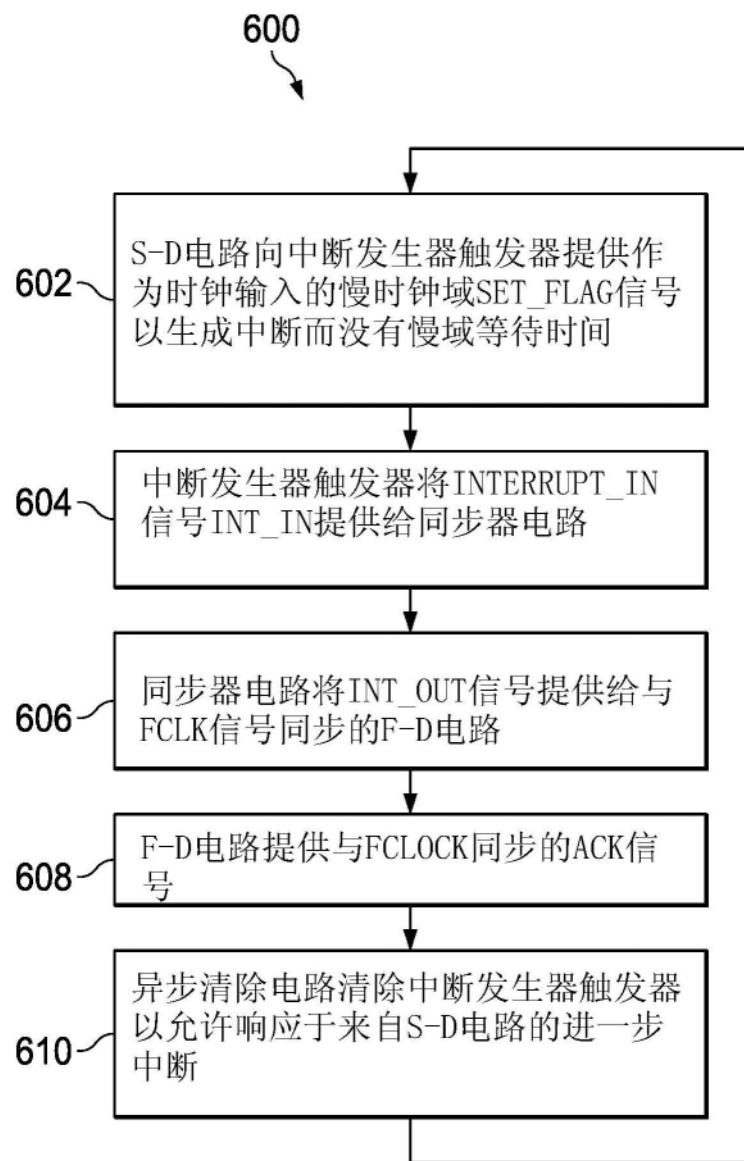

[0011] 图6是说明用于通过慢域电路管理快域电路的中断的过程或方法的流程图。

## 具体实施方式

[0012] 在附图中,相同的附图标记贯穿全文指代相同的元件,且各种特征件不必按比例绘制。在该说明书中,术语“耦合”包括间接或直接的电气或机械连接或其组合。例如,如果第一装置耦合到第二装置或与第二装置耦合,那么该连接可以通过直接的电气连接进行,或通过经由一个或更多个中间装置和连接的间接的电气连接进行。

[0013] 所描述的示例包括集成电路,以及用于通过根据较慢的第二时钟信号操作的第二电路管理根据第一时钟信号操作的第一电路的中断的中断处理电路和过程。所描述的技术可以用于各种不同的应用中,其中第一和第二时钟域或电路根据不同的时钟速度操作,这些时钟速度可以是彼此异步的或同步的。而且,所描述的示例提供了中断处理电路和方法,其可以用于与单个集成电路的第一和第二时钟域电路相关联,或者对应于单独的IC或其组合上的快和慢时钟域电路。

[0014] 图1示出了包括中断处理电路100、第一电路101(图中标记为F-D CKT的“快域电路”)和第二电路102(图1中标记为S-D CKT的“慢域电路”)的系统。第一和第二电路101和102分别根据不同的第一和第二时钟信号FCLK和SCLK操作。电路101和102可以形成在单独的集成电路(IC)中,或者可以是单个IC上的电路。电路101和102是通过根据对应的时钟信号FCLK和SCLK的操作的两个独立时钟域的部分。时钟信号FCLK和SCLK可以关于时钟相位和/或时钟频率独立于彼此操作,但者并不是对所有实施例的严格要求。第一时钟信号FCLK由电路节点103上的第一电路101的时钟源(未示出)提供,并且时钟信号SCLK由节点105上的第二电路102的时钟源(未示出)提供。在该示例中,第二时钟信号SCLK慢于第一时钟信号FCLK。

[0015] 中断处理电路100包括中断发生器电路110、同步器电路120和中断清除电路114、116,以管理与由第一电路101服务的第二电路102相关联的中断事件的信令和清除(clearance)。在该示例中,中断发生器电路110包括输入104和105以及输出118,并且相对于第一时钟信号FCLK同步地选择性地中断第一电路101。中断清除电路114、116包括触发器116和与门114,以及与第一时钟信号FCLK同步的输出115,以选择性地提供中断清除信号CLEAR以响应于来自第一电路101的确认信号ACK而重置中断发生器电路110。此外,中断清除电路114、116相对于第二时钟信号SCLK异步地清除或复位中断发生器电路110。以这种方

式,中断处理电路100减轻或避免与传统中断清除电路相关联的同步延迟,并且便于由中断发生器电路110对来自第二电路102的进一步中断的响应。

[0016] 在操作中,第二电路102在节点104上提供中断请求信号IR作为中断发生器电路110的输入。第二电路102还包括输出节点108以提供复位信号NRESET\_SCLK以复位中断发生器电路。中断发生器电路110在节点118处提供中断输入信号INT\_IN作为同步器电路120的输入。同步器电路120在连接到第一电路101的节点128处提供中断输出信号INT\_OUT。反过来,第一电路101为中断服务,并在电路节点130上生成确认信号ACK,作为输入提供给断清除电路114、116。中断清除电路114、116在节点115处生成中断清除信号CLEAR,以清除中断输入信号INT\_IN。

[0017] 传统的快/慢时钟域中断处理电路和技术通常在中断请求信令中引入延迟时间或延迟,并且由于慢时钟域清除信号同步而遭受显著延迟,这可能导致服务和清除中断的延迟和可能丢失或遗漏中断事件。

[0018] 为了解决第一个问题,本公开提供了可以在没有显著延迟时间的情况下生成中断的解决方案。在该示例中,中断发生器电路110包括中断标志或中断发生器触发器112,在这种情况下,是在从触发器106接收的电路节点111上根据同步中断请求信号SET\_FLAG生成中断输入信号INT\_IN的数据或“D”触发器。触发器106从节点104接收作为数据输入的中断请求信号IR,并且包括连接到慢时钟节点105的时钟输入。在操作中,第二电路102激活中断请求信号IR在有效高状态下,并且触发器106在慢时钟信号SCLK的下一个上升沿处在节点111上生成在高状态下的信号SET\_FLAG。中断发生器触发器112的数据(D)输入连接到逻辑高信号(图1中的“1”),并且触发器112的时钟输入被连接以从节点111接收同步的中断请求信号SET\_FLAG。与门114将CLEAR信号提供给触发器112的清除输入CLRZ,以响应于来自第一电路101的确认信号ACK选择性地复位中断发生器电路110。

[0019] 响应于第二中断发生器输入115接收在低第一状态下的中断清除信号CLEAR,中断发生器输出118提供在低第一状态下的中断输入信号INT\_IN。当中断清除信号CLEAR在高第二状态下时,输出118响应于低-高转换而提供在高第二状态下的中断输入信号INT\_IN和提供同步中断请求信号SET\_FLAG。当CLEAR信号为高时,当中断请求信号IR被断言在高状态下时,触发器112在慢时钟信号SCLK的上升沿处或之后不久生成在有效高状态中的中断输入信号INT\_IN。以这种方式,中断请求信号SET\_FLAG通过触发器106与第二时钟信号SCLK同步,以避免或减轻亚稳态问题。与经常遭受半周期或全周期同步延迟的其他中断生成电路相比,中断产生电路110提供了显著的优点,,如下文结合图5所描述的。电路110有利地相对于从第二电路102接收的中断请求信号IR的上升沿及时地断言中断输入信号INT\_IN。

[0020] 中断清除电路114、116提供在低第一状态下的中断清除信号CLEAR,以复位中断发生器电路110,以响应于来自第一电路101的确认信号ACK,将中断输入信号INT\_IN设置为低第一状态。该示例中的触发器116是D触发器,其中数据输入“D”连接到节点130以接收确认信号ACK,并且时钟输入连接到节点103以接收第一时钟信号FCLK。连接触发器116的输出“Q”以在节点113上提供清除标志信号CLR\_FLAG,如图1所示。与门114经由反相输入接收CLR\_FLAG信号,并且经由节点108从第二电路102接收复位信号NRESET\_SCLK。与门114的第二输入允许第二电路102重置与门114。在其他可能的实施方式中,可以省略与门114,并且CLR\_FLAG信号可以直接提供给中断发生器触发器112的CLRZ输入。在操作中,清除电路114、

116响应于ACK信号变高而快清除触发器112,而不同步与第二时钟信号SCLK相关联的延迟,从而导致中断输入信号INT\_IN和中断输出信号INT\_OUT相对于慢时钟信号SCLK异步地变低。以这种方式,一旦第一电路101已经服务了待处理中断,则待处理中断信号INT\_OUT被快清除,从而允许第一电路101接收并适当地服务来自第二电路102的其他后续中断。

[0021] 在该示例中,中断处理电路100还包括同步器电路120。在操作中,电路120相对于快第一时钟信号FCLK快速地同步中断输入信号INT\_IN,以避免与由中断发生器电路110生成的INT\_IN信号的任何亚稳态问题。同步器电路120包括与中断发生器输出118耦合以接收中断输入信号INT\_IN的输入,以及与第一时钟信号FCLK同步以将中断输出信号INT\_OUT提供到第一电路101的输出128。该示例中的电路120包括第一触发器122,其数据输入D连接到中断发生器输出118,时钟输入被连接以接收第一时钟信号FCLK。第一同步器触发器122的输出124(Q)连接到第二同步器触发器126的数据输入D,第二同步器触发器126还具有连接到节点103处的第一时钟信号FCLK的时钟输入。第二同步器触发器126的输出Q连接到第一电路101,以提供与第一时钟信号FCLK同步的中断输出信号INT\_OUT。同步器触发器122和126每个包括有效低清除输入CLRZ,其被连接以接收由第一电路101在电路节点132上提供的复位信号NRESET\_FCLK。

[0022] 图2示出了说明图1的中断处理电路100中的用于快和慢时钟速度的任意比率的操作信号的信号图200。在该示例中,第二时钟信号SCLK的两个示例周期被示为曲线202,并且FCLK曲线204可以具有任意数量的快时钟信号转变,其中第一和第二时钟信号FCLK和SCLK关于时钟速度和相位关系可以完全彼此不同步。如图2的示例中所示,中断发生器电路110的触发器106响应于来自第二电路102的中断请求信号IR的上升沿,而在第二时钟信号SCLK(曲线202)的上升沿断言SET\_FLAG信号(曲线206)有效高。中断发生器电路110生成中断输入信号INT\_IN,并且同步器电路120同步该信号,并在两个FCLK周期内相对于第二时钟信号SCLK异步地在中断输出信号INT\_OUT(曲线210)中生成上升沿。当快域第一电路101完成相关的中断服务程序时,第一电路101在节点130处断言确认信号ACK,其向中断清除触发器116提供有效的高数据输入。在第一时钟信号FCLK的下一个上升沿中,触发器116断言清除标志信号CLR\_FLAG(有效高,图2中的曲线208)。该信号转变清除信号发生器触发器112,使中断输入信号INT\_IN变低。同步器电路120在两个快时钟周期内同步该下降沿转换,导致在中断输出信号INT\_OUT中产生下降沿。以这种方式,中断处理电路100在确认信号ACK的两个FCLK周期内有效地清除提供给第一时钟101的中断信号INT\_OUT。

[0023] 图3示出了图1的电路中的用于快和慢时钟速度的一个示例比率(例如,大约8)的操作信号。在该示例中,慢域(第二)电路102是快域CPU或处理器第一电路101的PWM定时器外围服务。在该示例中,快域CPU在闭环控制应用中向PWM控制外围第二电路102提供计数器值,以用于控制功率转换器信号(未示出)的脉冲宽度。外围第二电路102递减计数值,并且当计数值达到预定值(例如,在该实施方式中为“1”)时发出并中断请求信号IR。图3中的曲线302说明了慢时钟信号SCLK,并且曲线304示意性地说明了PWM定时器/计数器数据值,在这种情况下,在由快时钟域CPU重新编程为另一个值2之前,首先值通过3、2、1递减然后到0。外围PWM定时器第二电路102然后从该值2递减到1然后再次递减到0。在该示例中,曲线306说明了从触发器106输出的SET\_FLAG信号,曲线308示出了快域时钟信号FCLK,曲线310说明来自同步器电路120的中断输出信号INT\_OUT,曲线312说明来自触发器116的CLEAR\_FLAG信

号。该示例中的第二电路102响应于计数器值达到“1”断言中断请求信号IR。如图3所见，中断输出信号INT\_OUT在SET\_FLAG信号的上升沿的两个快时钟周期内经历上升沿转变。响应于中断输出信号，第一电路101开始中断服务程序或过程。一旦第一电路101完成中断服务处理，第一电路101断言确认信号ACK，并且触发器116在CLEAR\_FLAG信号中生成上升沿，如曲线312所示。CLEAR\_FLAG信号转变清除中断发生器触发器112，并且同步器电路120在两个快时钟周期内在中断输出信号INT\_OUT(曲线310)中产生所得的下降沿。

[0024] 图2和图3的示例说明了中断处理电路100关于发生与第二电路102相关联的中断事件的第一电路101的快通知(例如，在两个快时钟周期内)的有利操作。而且，响应于第一电路101对确认信号ACK的断言，电路100(例如，在两个快时钟周期内)提供中断信号的快异步清除。所描述的中断处理电路101的这些快响应优点提供了显著的如图2和图3所示的益处。此外，当快和慢时钟速度之间的比率增加时，这些优点更加明显。因此，所描述的电路和技术的益处具有特定的用途，其与高速CPU或其他快时钟域电路与相对慢时钟速度第二电路102交互的相关联。

[0025] 图4提供了示出了具有遗漏中断事件的握手确认中断处理技术的信号图400。图4中的曲线402说明了示例慢时钟信号(图4中标记为LOW CLOCK)，曲线404说明了PWM定时器外围设备中的计数器或定时器值(PWM DATA)的另一示例，曲线406示出了来自快时钟域处理器电路的PWM定时器外围设备的中断信号(INTERRUPT)，并且曲线408示出了示例快时钟信号(FAST CLOCK)。图4中的曲线410示出了与快时钟信号同步的中断信号，曲线412示出了来自快时钟域电路的示例中断清除事件。另一曲线414说明了与慢时钟信号同步的中断清除事件信号，曲线416说明了从外围电路到快时钟域电路的中断清除事件确认握手信号。图4中的信号说明了快和慢时钟域电路之间的传统握手/基于确认的中断处理的不利后果。如曲线404和406所见，例如，慢域电路102响应于计数器值达到“1”而生成中断信号IR，并且随后的快域电路中断服务程序将慢域PWM计数器值重新编程为“2”。然而，中断清除事件与慢第二时钟信号的同步(在曲线412、414和416中示出)在提供信号(曲线414的下降沿)以实际终止中断信号(曲线406的下降沿)中引入显著的同步延迟。在中间的延迟中，在该示例中，PWM计数器值再次转变为1，但是快时钟域电路不能响应并正确地服务该第二中断事件。如上文结合图1-图3所描述的，所描述的中断处理电路100有利地提供中断请求信号的快异步清除，从而促进快时钟域电路101的适当中断服务处理，以避免或减轻图4中所说明的缺点。

[0026] 图5提供了说明中断处理电路100关于快中断请求信号生成的优点的信号图500。图5包括说明慢时钟信号SCLK的曲线502、说明PWM定时器外围计数器值的曲线504以及说明具有不同延迟时间的生成的中断信号的曲线506、508和510。具体地，曲线506说明了具有对应于慢时钟信号周期的一半的半周期延迟时间的中断信号(例如，提供给快时钟域服务电路的INTHL)，并且曲线508说明具有全部慢时钟周期延迟时间的中断信号INTFL。相反，曲线510示出了由上文描述的图1中的由中断发生器110和同步器120提供的快中断生成(INT\_OUT)。如前所述，先前的解决方案使用同步电路(未示出)来同步与慢时钟电路中的中断事件相关联的信号，这引入半周期延迟(例如，曲线506)或完全慢时钟周期延迟(曲线508)。相反，上面描述的电路100不使用慢时钟域同步器，并且在将中断请求信号SET\_FLAG与快时钟域同步为信号INT\_OUT之后，将中断请求信号SET\_FLAG作为中断请求线传送，使得异步逻辑完全遏制。在这方面，节点111上的SET\_FLAG信号用作生成中断输入信号INT\_IN的触发器

112的时钟，并且电路110、120生成中断输出信号INT\_OUT而在慢时钟域中没有任何损失。

[0027] 图6示出了通过根据比第一时钟信号慢的第二时钟信号操作的第二电路(例如，电路102)管理根据第一时钟信号操作的第一电路(例如，上文描述的电路101)的中断的方法600。方法600可以使用任何合适的中断处理电路来实施，诸如上文描述的电路100，或者在其他电路(未示出)中。在602处，生成中断信号，与第二时钟信号同步。在一个示例中，上文描述的慢时钟域电路102将SET\_FLAG信号提供给中断发生器触发器112，经由触发器106与SCLK信号同步。这在602处生成中断输入信号INT\_IN而没有慢时钟域延迟时间(例如，避免上文描述的图5的曲线506和508中所示的延迟)。

[0028] 在604和606处，响应于中断输入信号，将中断输出信号提供给第一电路101。在上文描述的示例中，在图6中的604处，中断发生器触发器112将中断输入信号INT\_IN提供给同步器电路120，并且在606处同步器电路120将与快时钟信号FCLK同步的中断输出信号INT\_OUT提供给第一电路101。在608处，第一电路提供与快时钟信号FCLK同步的确认信号(例如，上文描述的ACK)。方法600还包括在610处清除中断输入和输出信号。在某些示例中，响应于确认信号ACK，清除电路114、116相对于第二时钟信号SCLK异步地清除INT\_IN和INT\_OUT信号。在电路100中，在清除触发器116接收到确认信号ACK之后，在第一时钟信号FCLK的两个周期内快速清除中断输入和输出信号INT\_IN和INT\_OUT。

[0029] 与使用在快时钟域中生成的清除事件信号的慢时钟域同步的其他解决方案相比，所描述的示例提供了显著的响应时间优势。如图4所示，在实际清除提供给快时钟域电路的中断信号之前，这种替代解决方案消耗用于同步的两个附加的慢时钟周期。相反，所描述的电路100和方法600通过与慢时钟信号SCLK异步地清除慢时钟域中生成的中断来避免这种附加的中断清除延迟时间或延迟。例如，在电路100中，与清除生成中断输入信号INT\_IN的相同触发器112异步地使用来自快时钟域电路101的清除事件信号ACK，以可靠地清除中断输出信号INT\_OUT，而在慢时钟域中没有任何损失。对于中断生成，所描述的电路和方法使用同步器电路120相对于快时钟信号FCLK同步地传递中断输出信号INT\_OUT，以确保清除信号以避免任何异步路径(例如，亚稳态)。实际上这种同步是一个小延迟，特别是在第一时钟速度明显高于慢时钟速度的情况下。此外，在所描述的电路100中，实现快速异步清除路径，同时仍然保持最终中断线与快时钟域完全同步。

[0030] 在权利要求的范围内，在所描述的实施例中，修改是可能的，其他实施例也是可能的。

图1

图2

图3

图4

图5

图6